## UC Riverside UC Riverside Electronic Theses and Dissertations

## Title

Soft Underlayers for Next Generation Magnetic Recording Media and Nano Electrostatic Discharge Protection

**Permalink** https://escholarship.org/uc/item/6g89z8cx

Author ZHANG, Chen

Publication Date 2013

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

### Soft Underlayers for Next Generation Magnetic Recording Media and Nano Electrostatic Discharge Protection

# A Dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

**Electrical Engineering**

by

Chen Zhang

August 2013

Dissertation Committee:

Dr. Albert Wang, Chairperson Dr. Sheldon Tan Dr. Qi Zhu

Copyright by Chen Zhang 2013 The Dissertation of Chen Zhang is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgements

I would like to take this opportunity to express my deepest gratitude to my two advisors, Professor Albert Wang and Professor Sakhrat Khizroev, for their constant help and support throughout my Ph.D. studying. Without their constant academic guidance and encouragement this work would not have been possible. During the preparation of this dissertation, I have been receiving a lot of great encouragements and thorough directions from Professor Albert Wang. His wisdom, broad knowledge horizon, and rigorous scholarship will always inspire and guide me to pursue high achievements in both academic and industry. I would like to thank Prof. Sheldon Tan and Prof. Qi Zhu for their kindly consenting to be on my final defense committee and their time, suggestions and inputs that helped adding the value of my thesis.

I deeply appreciate the guidance and support from the scientists of Los Alamos National Laboratory. Special thanks to my mentor Jennifer Hollingsworth and Quanxi Jia for their help and support during my quantum dot novel devices fabrication and Kumaranand Palaniappan, Janardan Kundu, Allison Dennis and Yagna Ghosh for their assistance in my measurements.

Thanks to all my friends in the Laboratory for Integrated Circuits and Systems (LICS) group of UC Riverside: Dr. Xin Wang, Dr. Qiang Fang, Dr. Hui Zhao, Dr. Jian Liu, Dr. Zitao Shi, Ms. Li Wang, Ms. Rui Ma, Mr. Zongyu Dong, Mr. Xiao Shawn Wang and Mr. Fei Lu. Thank you all for the technical help and feedback in the past five years.

iv

Special thanks to my parents for their countless love, care, encouragement and sacrifice. It was their motivation and support that guides me through the years and made this journey possible.

I also want to thank Cisco System, Inc. for the support on my Ph.D. research.

#### ABSTRACT OF THE DISSERTATION

#### Soft Underlayers for Next Generation Magnetic Recording Media and Nano Electrostatic Discharge Protection

by

Chen Zhang

#### Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, August 2013 Dr. Albert Wang, Chairperson

In this dissertation, two sections were included to present my work. The first section concerns about soft underlayers (SULs) in magnetic recording media, and the other section introduces electrostatic discharge (ESD) protection devices.

Hard disk drives (HDDs) are still being widely used in consumer electronics applications to store information. Due to the scaling down, higher capacity with smaller size HDDs are highly desired in market. Recently, perpendicular recording caused more attention to overcome some of the potential problems with longitudinal recording. The progress from the materials and techniques may make perpendicular recording more competitive. In this dissertation, a novel amorphous SUL CoFeTaZr is discussed for its superior magnetic properties.

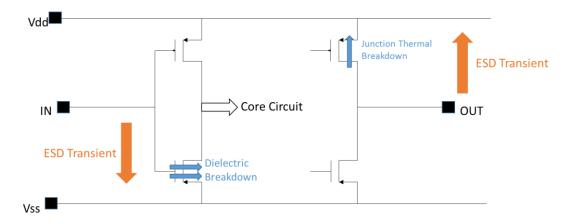

ESD is one of the most important reliability problems for ultra-scaled integrated circuit (IC). Transient high voltage (up to tens of kilovolts) and current generated by ESD

in a very short time could introduce very high electric field and current across semiconductor devices, which may result in dielectric damage or melting of semiconductors and contacts, which may affect circuit performance, shorten product life time and increase manufacturing and assembling cost. Therefore, it's necessary to design a protection circuit that discharges the ESD. As the scaling down continues, ESD protection design is facing severe challenges.

This dissertation presented two novel ESD protection structures. One is a new nano crossbar array ESD protection device consists of the  $Si_XO_yN_z$  composite, as dielectric layer between two metal electrodes. This device has extremely-low leakage current, fast response, good uniformity and robust ESD protection, ideal for mobile applications where power consumption is a great concern. The other one is a new non-volatile memory based ESD protection structure, two structures were introduced. One is with layers of nano crystal dots inside the floating gate film, the other one is with nitride floating gate layer in an MOSFET. Both structures has ultra-low leakage current, wide range of triggering voltage, ideal for multiple power domains.

In the last part, design and characterization of shallow trench isolation and poly-gated diode based ESD structures in a foundry 28 nm technology were reported. ESD-protected monitor circuits were used to evaluate chip-level ESD protection.

## Table of Contents

| List of Figures                                                                |

|--------------------------------------------------------------------------------|

| List of Tablesxxii                                                             |

| Section 1 Soft Underlayers for Next Generation Magnetic Recording Media 1      |

| Chapter 1.1 Introduction to Hard Disk Drives (HDDs)1                           |

| 1.1.1 Overview of Longitudinal Magnetic Recording                              |

| 1.1.1 Granular Media                                                           |

| 1.1.2 Orientation of Grains                                                    |

| 1.1.3 Challenges of Longitudinal Magnetic Recording7                           |

| 1.1.2 Overview of Perpendicular Magnetic Recording                             |

| 1.1.3 Description of Various Layers and Their Functions                        |

| 1.1.3.1 Soft Magnetic Underlayers 14                                           |

| 1.1.3.2 Intermediate Layers                                                    |

| 1.1.3.3 Recording Layers                                                       |

| Chapter 1.2 Magnetic Properties Optimization for Amorphous Soft Underlayers 26 |

| 1.2.1 Introduction                                                   |

|----------------------------------------------------------------------|

| 1.2.2 Experiment                                                     |

| 1.2.3 Results and Discussions                                        |

| 1.2.3.1 The Role of Ar Ion Milling on Substrate                      |

| 1.2.3.2 Comparison Between CoTaZr and CoFeTaZr Amorphous Thin Films  |

| 1.2.3.3 Pressure Dependence of CoFeTaZr Amorphous Thin Film          |

| 1.2.3.4 Thickness Dependence of CoFeTaZr Amorphous Thin Film         |

| 1.2.3.5 Capping Layer Dependence of CoFeTaZr Amorphous Thin Films    |

| 1.2.3.6 Seed Layer Dependence of CoFeTaZr Amorphous Thin Films       |

| 1.2.4 Conclusion                                                     |

| Section 2 Nano Electrostatic Discharge Protection                    |

| Chapter 2.1 Introduction to Electrostatic Discharge (ESD) Protection |

| 2.1.1 Overview of ESD and ESD Protection for IC                      |

| 2.1.2 ESD Protection Principles                                      |

| 2.1.2.1 ESD Protection Methods and Full-Direction ESD Protection     |

| 2.1.2.2 ESD Protection Mechanisms and ESD Design Window              |

| 2.1.3 ESD Test Models                              | . 49 |

|----------------------------------------------------|------|

| 2.1.3.1 Human Body Models (HBM)                    | . 49 |

| 2.1.3.2 Machine Model (MM)                         | . 51 |

| 2.1.3.3 Charged Device Model (CDM)                 | . 53 |

| 2.1.3.4 Transmission Line Pulse Model (TLP)        | . 54 |

| 2.1.4 ESD Protection Device Physics                | . 55 |

| 2.1.4.1 Diode and Diode Strings ESD Device         | . 55 |

| 2.1.4.2 BJT ESE Device                             | . 58 |

| 2.1.4.3 MOSFET ESD Protection                      | . 61 |

| 2.1.4.4 SCR ESD Protection                         | . 65 |

| Chapter 2.2 Novel ESD Protection Structures        | . 68 |

| 2.2.1 Filed Programmable ESD Protection Structure  | . 68 |

| 2.2.1.1 Introduction                               | . 68 |

| 2.2.1.2 New Programmable ESD Protection Mechanisms | . 69 |

| 2.2.1.2.1 NC-QD ESD Protection Mechanism           | . 69 |

| 2.2.1.2.2 SONOS ESD Protection Mechanism           | . 72 |

|                                                    |      |

|    | 2.2.1.3 Measurements and Discussions                                     | 74  |

|----|--------------------------------------------------------------------------|-----|

|    | 2.2.1.3.1 NC-QD ESD Protection Structure                                 | 74  |

|    | 2.2.1.3.2 SONOS ESD Protection Structure                                 | 81  |

|    | 2.2.1.4 Conclusion                                                       | 89  |

|    | 2.2.2 Dual-Direction Nanocrossbar Array ESD Protection Structures        | 89  |

|    | 2.2.2.1 Introduction                                                     | 89  |

|    | 2.2.2.2 Nanocrossbar Array ESD Protection                                | 90  |

|    | 2.2.2.3 Experiments and Discussions                                      | 91  |

|    | 2.2.2.4 Conclusion                                                       | 97  |

|    | Chapter 2.3 STI and Gated Diode ESD Protection in 28nm CMOS with Circuit |     |

| Mo | onitors                                                                  | 97  |

|    | 2.3.1 Introduction                                                       | 97  |

|    | 2.3.2 Diode ESD Protection in 28nm Cmos                                  | 98  |

|    | 2.3.2.1 STI Core and I/O Diode ESD Structures                            | 99  |

|    | 2.3.2.2 Poly-Gated Diode ESD Structures                                  | 100 |

|    |                                                                          | 101 |

| 2.3.3.1 Diode ESD Structure Design            |

|-----------------------------------------------|

| 2.3.3.2 ESD Monitor Dummy Circuit Design      |

| 2.3.4 Measurements and Analysis               |

| 2.3.4.1 Individual Diode ESD Characterization |

| 2.3.4.2 ESD Monitor Circuit Characterization  |

| 2.3.5 Conclusion                              |

| Section 3 Summary                             |

| References                                    |

#### List of Figures

Figure 1.1.1 (a) TEM image of a granular medium. (b) Illustration of grains, the Figure 1.1.2 The randomness of easy axis orientation: (a) three-dimensional (3D) random, Figure 1.1.3 Illustration of magnetic charges and the associated demagnetizing fields for Figure 1.1.4 Writing process in (a) longitudinal and (b) perpendicular recording. In perpendicular recording technology, the medium is virtually placed in the pole gaps between the head and the mirror image in SUL..... 11 Figure 1.1.5 Different functional layers of perpendicular recording medium with approximate thickness (layers are not to scale).....14 Figure 1.1.7 5×5  $\mu$ m2 MFM images of Permalloy thin films representing the growth in stripe domain periodicity due to increasing film thickness: (a) lack of stripe domain Figure 1.1.8 Spinstand-measured signal profiles along a track recorded into a perpendicular medium with (a) a non-biased SUL and (b) a biased SUL. ..... 19 Figure 1.1.9 Magnetization of two layers of antiferromagnetically coupled SUL during

| Figure 1.1.10 MFM images of a SUL corresponding to (a) the relatively "soft" and (b)        |

|---------------------------------------------------------------------------------------------|

| strongly biased ("hard") cases                                                              |

| Figure 1.1.11 (Top) Illustration of remanence magnetization state of grains of              |

| perpendicular media after it was saturated with a field into the plane. (a) Grains with a   |

| lower anisotropy constant show a reversal with remanent magnetization out of the plane      |

| showing instability. (b) Grains with a higher anisotropy constant show stable               |

| magnetization. (Middle) Illustration of hysteresis loops of the respective media that show  |

| (c) a positive Hn and (d) a negative Hn (bottom) hysteresis loop with relevant parameters.  |

|                                                                                             |

| Figure 1.2.1 Ar ion milling effect on the magnetic properties of amorphous (a) CoTaZr       |

| and (b) CoFeTaZr thin films sputtered at 5 mTorr Ar processing pressure                     |

| Figure 1.2.2 Magnetic moment comparison between CoTaZr and CoFeTaZr amorphous               |

| soft magnetic underlayers                                                                   |

| Figure 1.2.3 (a) Coercivity comparison between CoTaZr and CoFeTaZr amorphous soft           |

| magnetic underlayers fabricated under same sputtering conditions with 5 mTorr Ar            |

| sputtering pressure. (b) In-plane hysteresis loops of the hard-axis magnetization direction |

| on silicon substrates                                                                       |

| Figure 1.2.4 In-plane hysteresis loops of the hard-axis magnetization direction on (a)      |

| glass substrates, (b) silicon substrates, and (c) silicon oxide substrates                  |

| Figure 1.2.5 CoFeTaZr amorphous thin film coercivity dependence vs. processing Ar           |

| pressure sputtered on various substrates                                                    |

| Figure 1.2.6 Sputtering rate vs. processing Ar pressure                                     |

| Figure 1.2.7 Sputtering rate vs. coercivity dependence                                                             |

|--------------------------------------------------------------------------------------------------------------------|

| Figure 1.2.8 Coercivity vs. thickness dependence of CoFeTaZr amorphous thin films                                  |

| sputtered on different substrates                                                                                  |

| Figure 1.2.9 Coercivity vs. capping layer dependence of CoFeTaZr amorphous thin films                              |

| deposited on different substrates                                                                                  |

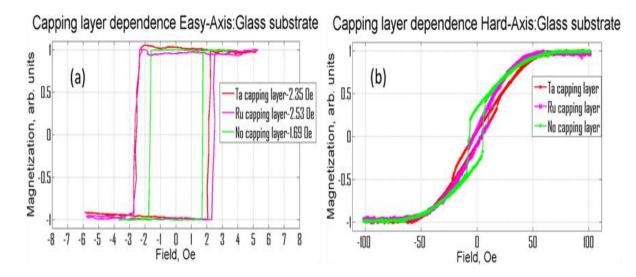

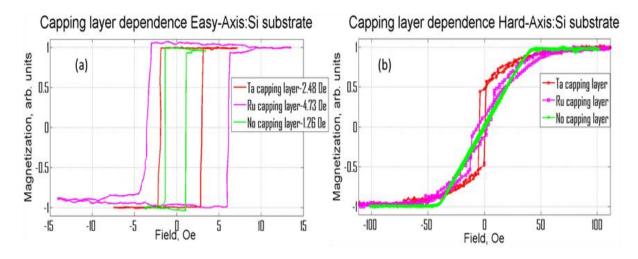

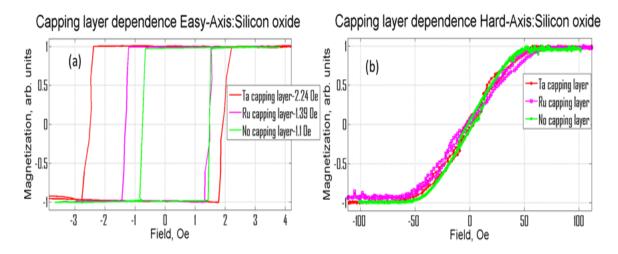

| Figure 1.2.10 Hysteresis loops of capping layer dependence of (a) easy-axis                                        |

| magnetization and (b) hard-axis magnetization of CoFeTaZr amorphous thin films                                     |

| deposited on glass substrates                                                                                      |

| Figure 1.2.11 Hysteresis loops of capping layer dependence of (a) easy-axis                                        |

| magnetization and (b) hard-axis magnetization of CoFeTaZr amorphous thin films                                     |

| deposited on silicon substrates                                                                                    |

| Figure 1.2.12 Hysteresis loops of capping layer dependence of (a) easy-axis                                        |

| magnetization and (b) hard-axis magnetization of CoFeTaZr amorphous thin films                                     |

| deposited on silicon oxide substrates                                                                              |

| deposited on sincon oxide substrates                                                                               |

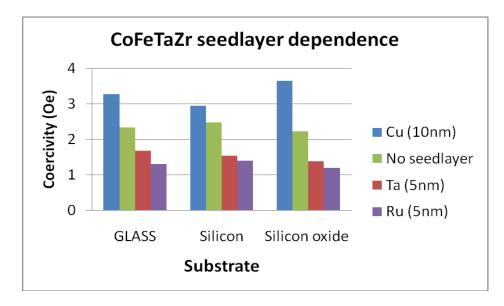

| Figure 1.2.13 Coercivity vs. seedlayer dependence of CoFeTaZr amorphous thin films                                 |

|                                                                                                                    |

| Figure 1.2.13 Coercivity vs. seedlayer dependence of CoFeTaZr amorphous thin films                                 |

| Figure 1.2.13 Coercivity vs. seedlayer dependence of CoFeTaZr amorphous thin films deposited on various substrates |

| Figure 1.2.13 Coercivity vs. seedlayer dependence of CoFeTaZr amorphous thin films deposited on various substrates |

| Figure 1.2.16 Hysteresis loop of seedlayer dependence of (a) easy-axis magnetization and  |

|-------------------------------------------------------------------------------------------|

| (b) hard-axis magnetization of CoFeTaZr thin films deposited on silicon oxide substrates. |

|                                                                                           |

| Figure 1.2.17 XRD patterns of (a) Cu seedlayer, (b) No seedlayer, (c) Ta seedlayer and    |

| (d) Ru seedlayer                                                                          |

| Figure 2.1.1 Possible ESD damages to IC circuits                                          |

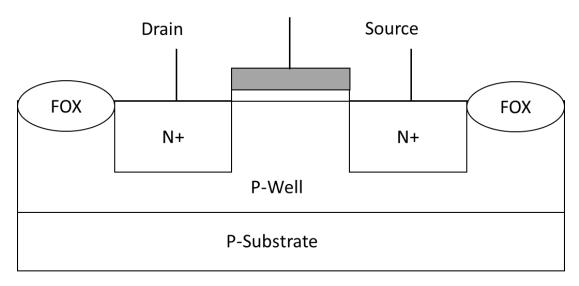

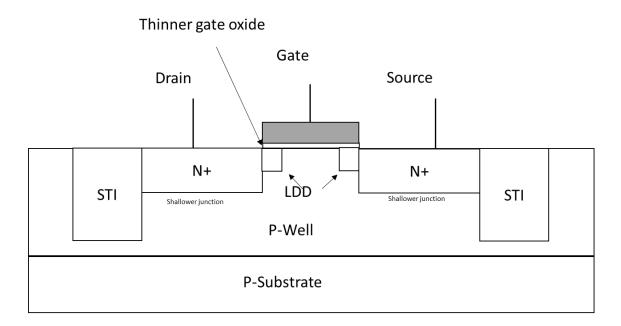

| Figure 2.1.2 (a) Traditional MOSFET device. (b) New technology MOSFET device 43           |

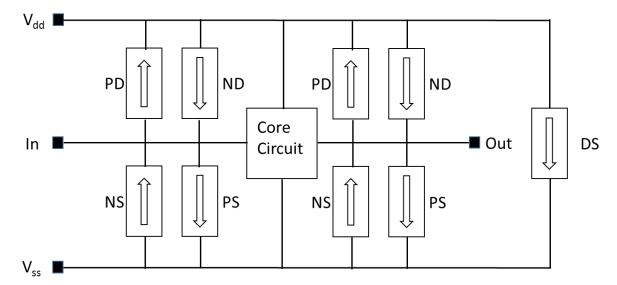

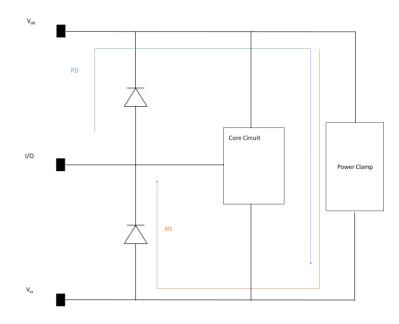

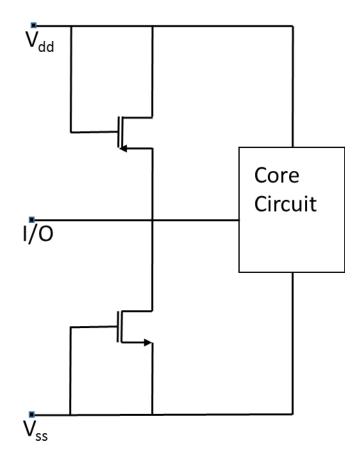

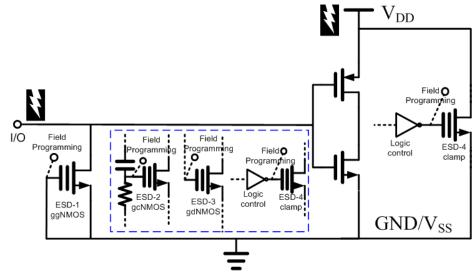

| Figure 2.1.3 Full-direction ESD protection scheme                                         |

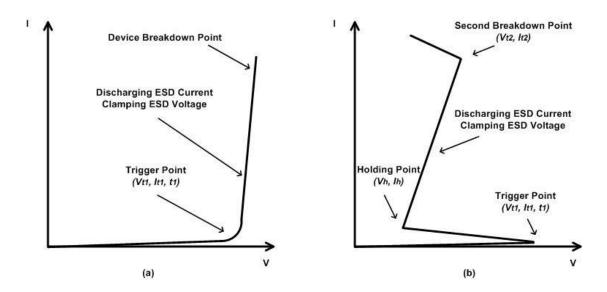

| Figure 2.1.4 (a) Simply turn-on I-V characteristic. (b) Snapback turn-on I-V              |

| characteristic                                                                            |

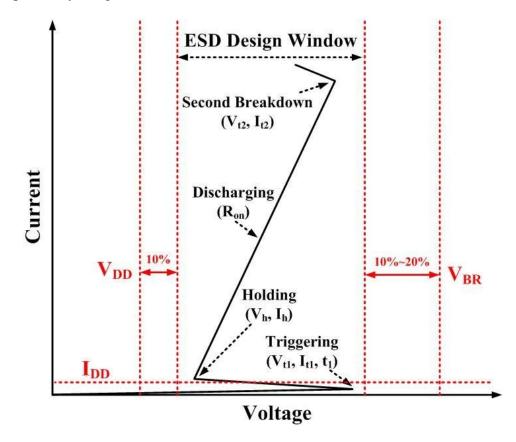

| Figure 2.1.5 ESD Design Window                                                            |

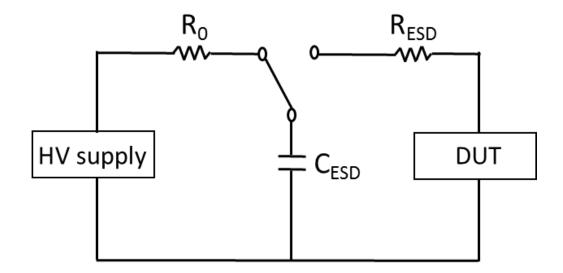

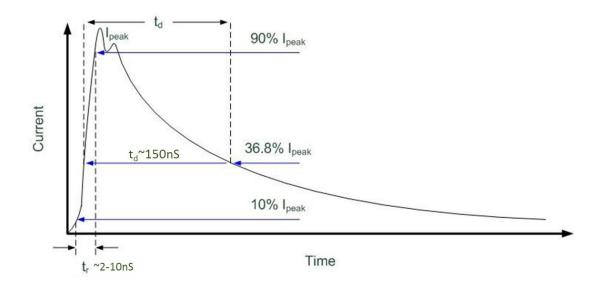

| Figure 2.1.6 HBM model equivalent circuit                                                 |

| Figure 2.1.7 A typical HBM ESD discharging waveforms shows a typical rising time          |

| (2~10nS) and duration time (150nS)                                                        |

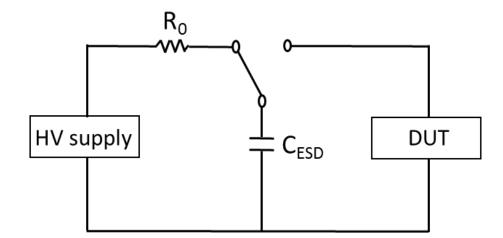

| Figure 2.1.8 MM model equivalent circuit                                                  |

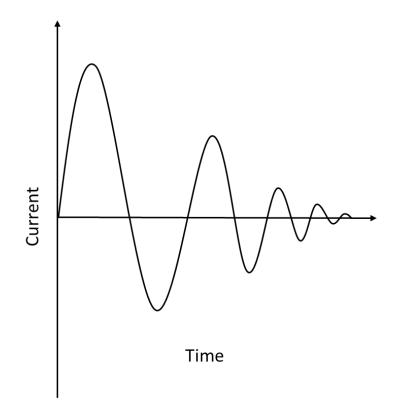

| Figure 2.1.9 A typical MM ESD discharging waveforms shows its oscillating properties.     |

|                                                                                           |

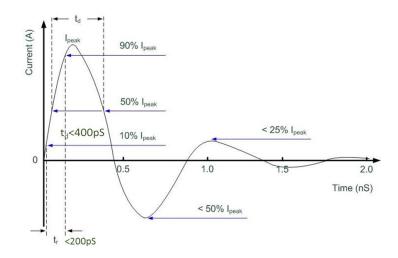

| Figure 2.1.10 A typical CDM ESD discharging waveforms under 3.5GHz bandwidth              |

| system                                                                                    |

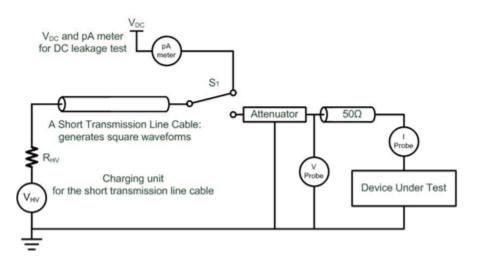

| Figure 2.1.11 TLP testing system scheme                                                   |

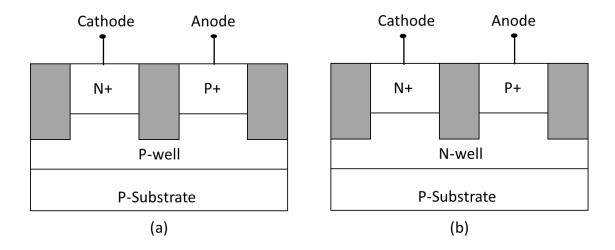

| Figure 2.1.12 (a) N-type diode. (b) P-type diode                                          |

| Figure 2.1.13 Diode ESD Protection Scheme                                                 |

| Figure 2.1.14 Diode String (N=2)                                                                                                        | 58 |

|-----------------------------------------------------------------------------------------------------------------------------------------|----|

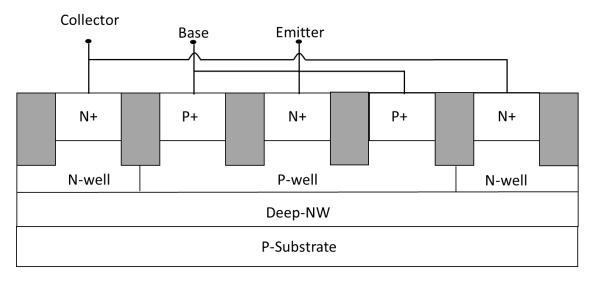

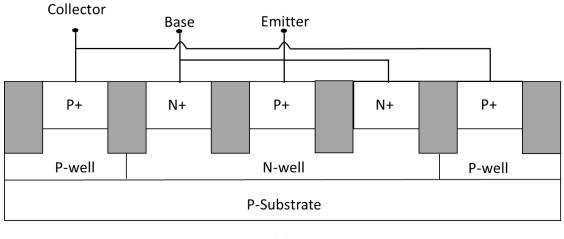

| Figure 2.1.15 (a) Typical vertical NPN BJT cross section. (b) Typical vertical PNP B.                                                   | JT |

| cross section                                                                                                                           | 59 |

| Figure 2.1.16 BJT ESD protection scheme                                                                                                 | 60 |

| Figure 2.1.17 (a) Cross section of a typical ggNMOS. (b) Equivalent circuit of ggNMO                                                    | S. |

|                                                                                                                                         | 62 |

| Figure 2.1.18 ggMOS ESD protection scheme                                                                                               | 63 |

| Figure 2.1.19 (a) Adding ballasting resistor to enhance uniformity. (b) A gate-coupl                                                    | ed |

| MOS ESD protection scheme                                                                                                               | 64 |

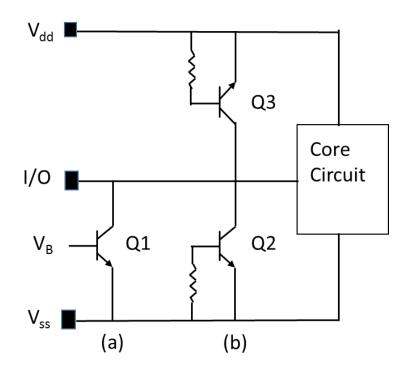

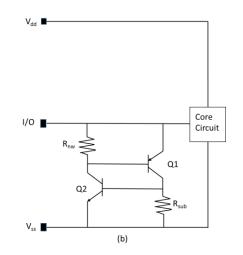

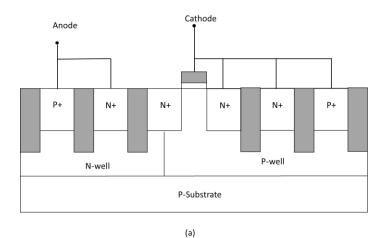

| Figure 2.1.21 (a) Cross section of LVSCR. (b) Equivalent circuit and ESD protection                                                     | on |

| scheme of LVSCR                                                                                                                         | 65 |

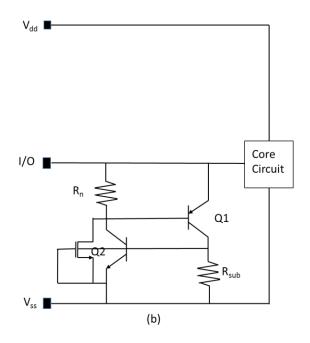

| Figure 2.1.22 Equivalent circuit of DTSCR (a) Forward-biasing $V_{BE}$ of Q2. (b) Forward-biasing $V_{BE}$ of Q2. (b) Forward-biasing V | d- |

| biasing $V_{BE}$ of Q1. (c) Forward-biasing $V_{BE}$ of Q1 and increase holding voltage at t                                            | he |

| same time                                                                                                                               | 68 |

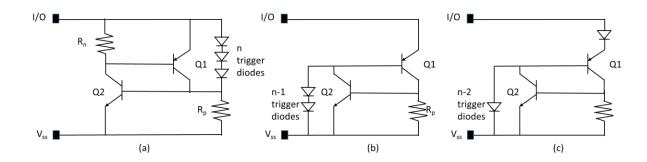

| Figure 2.2.1 Cross-section and energy diagram for the new NC-QD ESD protection                                                          | on |

| structure                                                                                                                               | 71 |

| Figure 2.2.2 Possible chip-level ESD protection schemes using the new NC-QD ES                                                          | SD |

| protection structure                                                                                                                    | 71 |

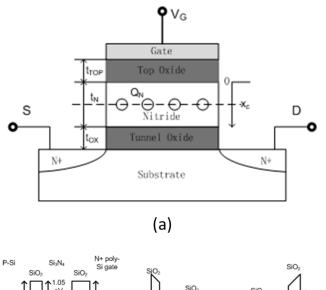

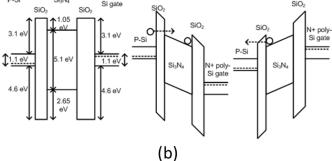

| Figure 2.3.3 Conceptual SONOS ESD protection. (a) Cross-section. (b) Bandg                                                              | ap |

| diagrams under fresh, programming and erasing conditions.                                                                               | 73 |

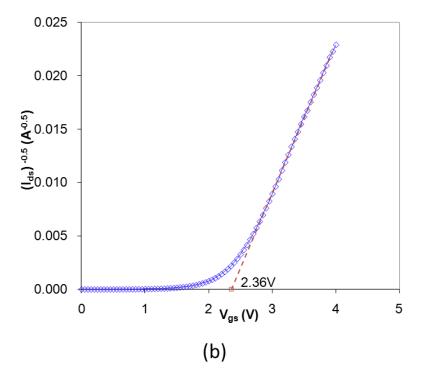

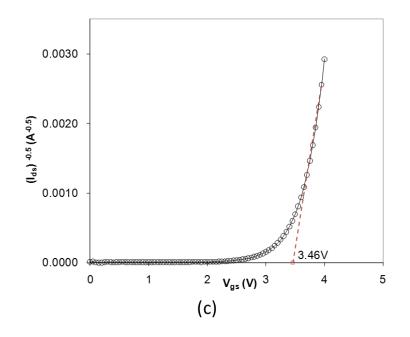

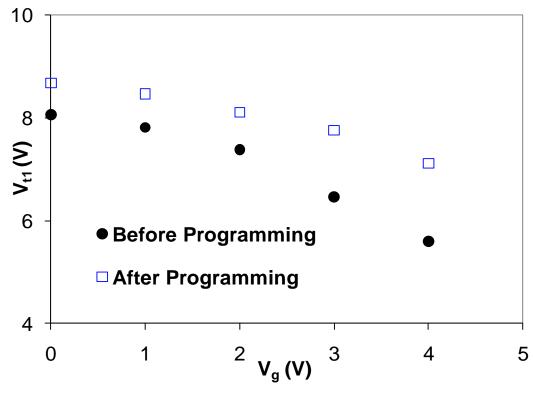

| Figure 2.2.4 Meausred DC I-V characteristics for NCQD ESD protection show the shift             |

|-------------------------------------------------------------------------------------------------|

| of threshold voltage by programming. (a) IDS~VDS before programming. (b) $\sqrt{\text{IDS}}$    |

| ~VGS before programming. (c) $\sqrt{IDS}$ ~VGS after programming                                |

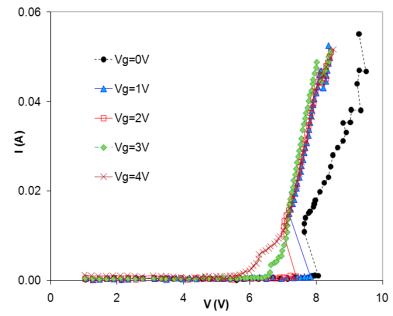

| Figure 2.2.5 Meausred ESD discharging I-V characteristics for the same sample by TLP            |

| before programming shows the desired ESD triggering variation, $\Delta Vt1$ , at different gate |

| biasing VG                                                                                      |

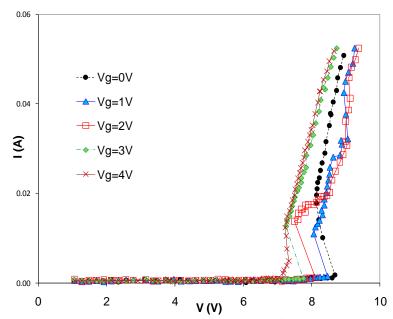

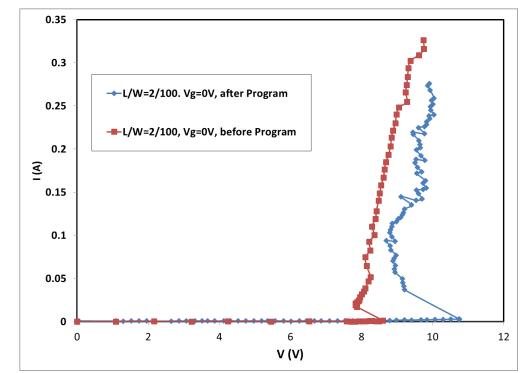

| Figure 2.2.6 Meausred ESD discharging I-V characteristics for the same sample by TLP            |

| after programming shows the desired ESD triggering variation, $\Delta Vt1$ , at different gate  |

| biasing VG                                                                                      |

| Figure 2.2.7 Meausred Vt1~ VG curves                                                            |

| Figure 2.2.8 Meausred I-V curves for a W/L=100µm/1µm NCQD ESD structure in                      |

| ggNMOS format before and after programming shows a $\Delta Vt1$ of $\sim 2V$                    |

| Figure 2.2.9 Meausred I-V curves for a W/L=1 $\mu$ m/1 $\mu$ m NCQD ESD structure by VF-TLP     |

| shows very fast ESD discharging response time of 100pS and very low leakage ~pA 80              |

| Figure 2.2.10 Meausred full transient I-V curves for a W/L=1 $\mu$ m/10 $\mu$ m NCQD ESD        |

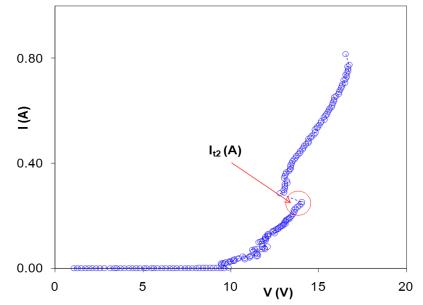

| structure by TLP shows its It2                                                                  |

| Figure 2.2.11 Meausred full transient I-V curves for a W/L=1 $\mu$ m/10 $\mu$ m NCQD ESD        |

| structure by VF-TLP shows its It2                                                               |

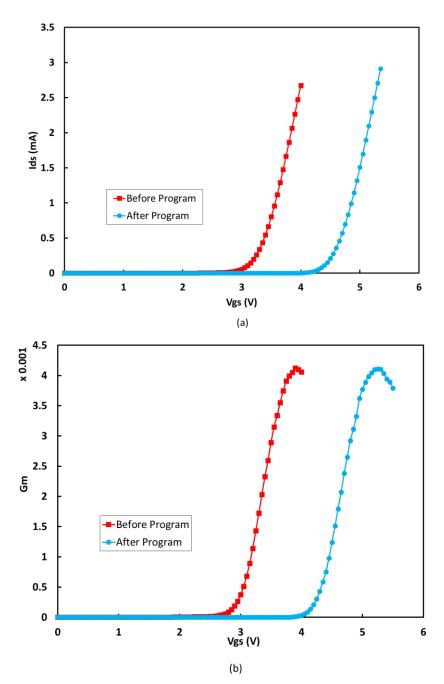

| Figure 2.2.12 Meausred (a) IDS~VGS before programming. (b) Gm~VGS for a sample                  |

| W/L=50 $\mu$ m/0.18 $\mu$ m SONOS ESD structure by DC testing show $\Delta$ Vth by programming  |

| (17V, 2ms programming pulse at gate)                                                            |

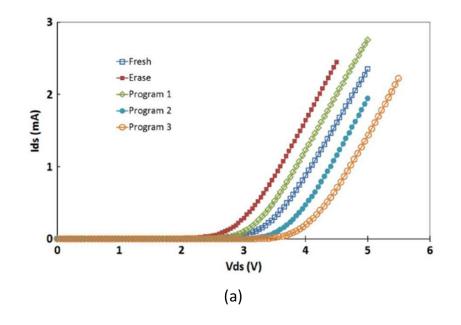

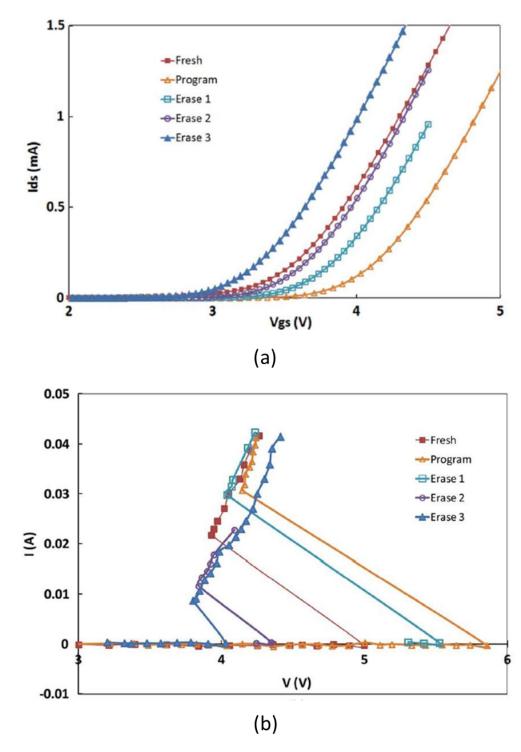

| Figure 2.2.13 Meausred I-V curves for a sample SONOS ESD structure, from fresh to                       |

|---------------------------------------------------------------------------------------------------------|

| one-step erase followed by multi-step programming, show $\Delta V$ th and ESD triggering $\Delta V$ th  |

| as designed. (a) DC testing. (b) TLP transient testing                                                  |

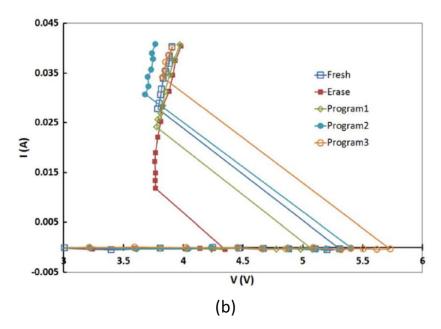

| Figure 2.2.14 Meausred I-V curves for a sample SONOS ESD structure, from fresh to                       |

| one-step program followed by multi-step erasing, show $\Delta V$ th and ESD triggering $\Delta V$ th as |

| designed. (a) DC testing. (b) TLP transient testing                                                     |

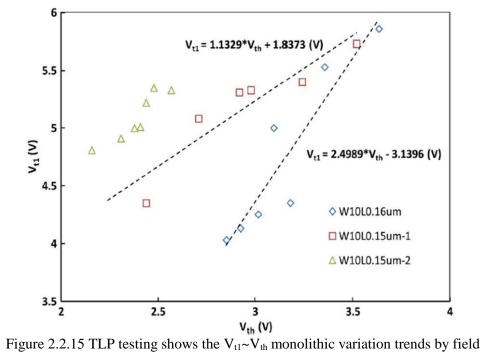

| Figure 2.2.15 TLP testing shows the Vt1~Vth monolithic variation trends by field                        |

| programming, depicted by a fitting model                                                                |

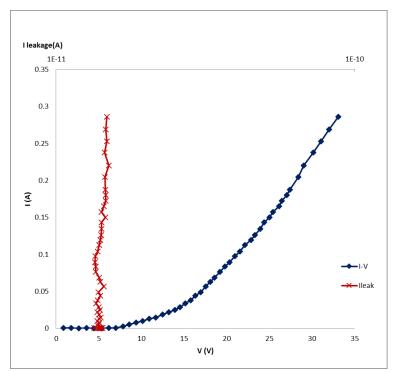

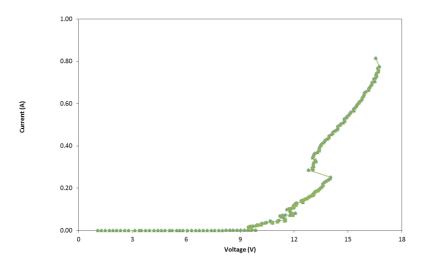

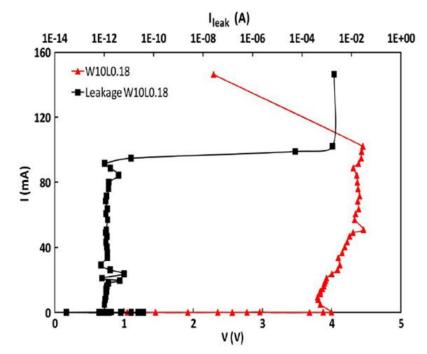

| Figure 2.2.16 Measured full ESD I-V curve for a sample SONOS ESD structure by TLP                       |

| shows the ESD It2 and ultralow leakage Ileak                                                            |

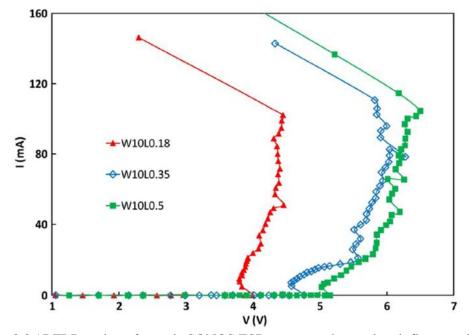

| Figure 2.2.17 TLP testing of sample SONOS ESD structure shows clear influence of the                    |

| channel length L on the ESD Vt1                                                                         |

| Figure 2.2.18 TLP testing of sample SONOS ESD structure shows clear influence of the                    |

| channel length L on the ESD Vt1                                                                         |

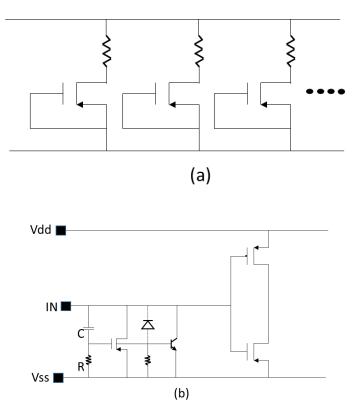

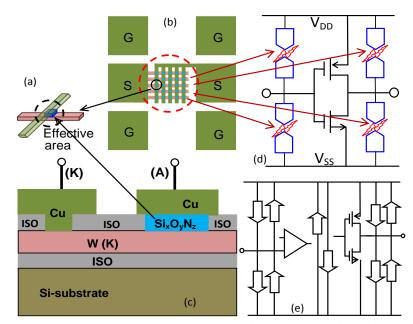

| Figure 2.2.19 Nano crossbar array ESD concept: (a) single-node device, (b) 5x5 array                    |

| device, (c) cross-section, (d) new on-chip ESD cirucit scheme, (e) ESD proteciton using                 |

| traditional single-polarity ESD devices. (ESD=symbols)                                                  |

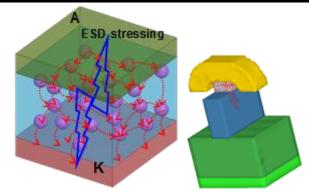

| Figure 2.2.20 Nano crossbar array ESD discharging effect by simulation (Right) and the                  |

| new dispersed local ESD tunneling model (Left)                                                          |

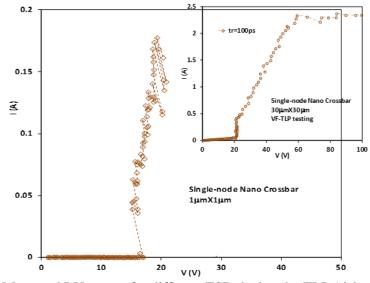

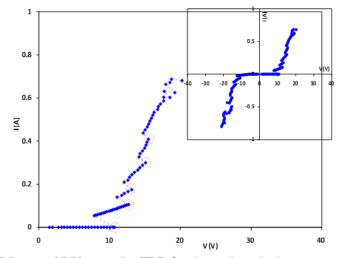

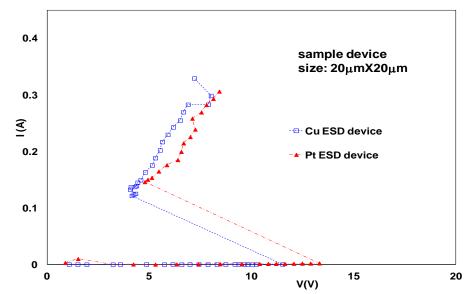

| Figure 2.2.21 Measured I-V curves for different ESD devices by TLP (rising time                         |

| tr~10nS, duration td~100nS) and VF-TLP (tr~100pS, td~1nS, Inset)                                        |

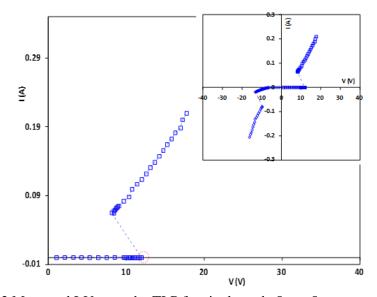

| Figure 2.2.22 Measured I-V curve by TLP for single-node $5\mu m \times 5\mu m$ nanocrossbar ESD      |

|------------------------------------------------------------------------------------------------------|

| devices. The inset shows its dual-directional ESD discharging curve                                  |

| Figure 2.2.23 Measured I-V curve by TLP for $5\mu m \times 5\mu m 5 \times 5$ nanocrossbar array ESD |

| devices. The inset shows its dual-directional ESD discharging curve                                  |

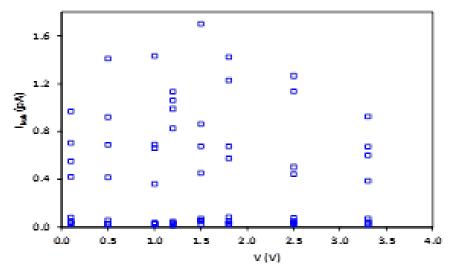

| Figure 2.2.24 Measured leakages for a large group of new ESD devices at voltage bias of              |

| 0.1-3.3V shows very low leakage current down to ~2pA                                                 |

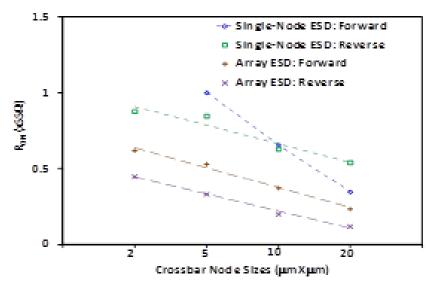

| Figure 2.2.25 Measured ESD RON for new ESD devices show that as total device area                    |

| increases, RON decreases monotonically, confirming the new dispersed local ESD                       |

| tunneling mechanism. Traditional phase memories show a fixed RON regardless of the                   |

| device size due to its fixed filament conduction model                                               |

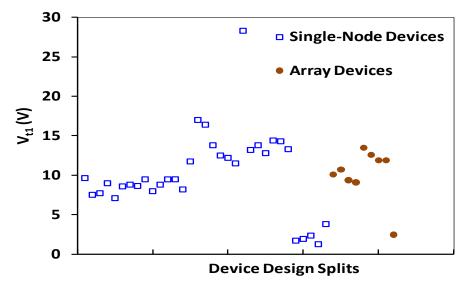

| Figure 2.2.26 Testing shows wide ESD $\Delta Vt1$ among fabricated prototype devices with            |

| different design splits (Table 3.4). Hence, efficient ESD programmability can be readily             |

| achieved by careful physical design matrix in future                                                 |

| Figure 2.2.27 Cu ESD device shows lower Vt1 and Vh than Pt device by TLP testing 97                  |

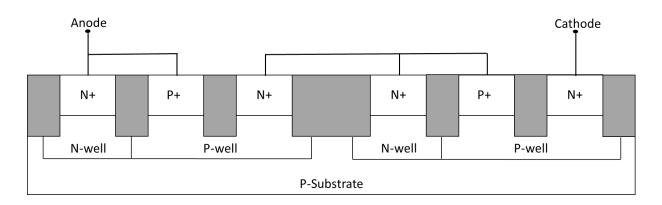

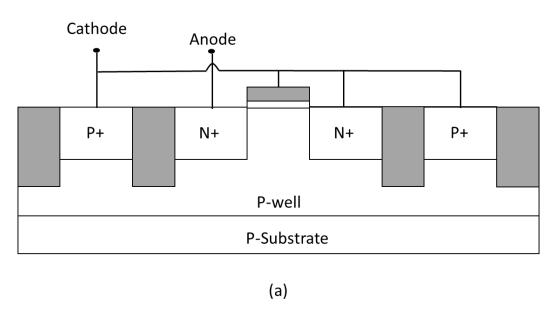

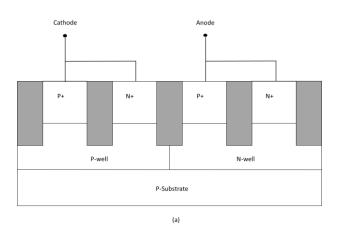

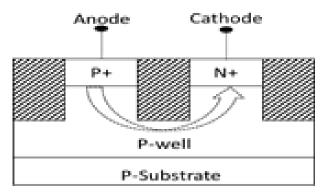

| Figure 2.3.1 Cross-section and ESD discharge path for an N+/P-well STI diode ESD                     |

| device. ESD current crowding at STI reduces ESD protection capability                                |

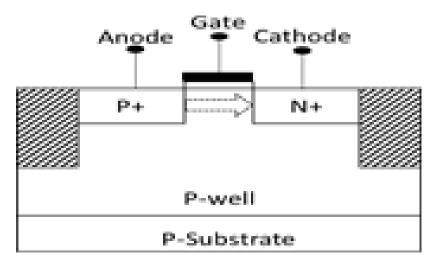

| Figure 2.3.2 Cross-section and ESD current discharging path for a poly-gated diode ESD               |

| protection structure                                                                                 |

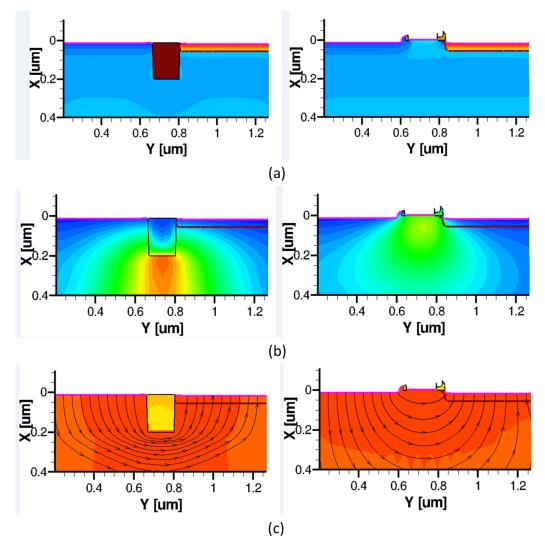

| Figure 2.3.3 Simulated (a) cross-section, (b) temperature contours and heating effect, and           |

| (c) ESD discharging current flows for STI core diode (left) and poly-gated diode (right)             |

| ESD protection structures under same ESD stressing                                                   |

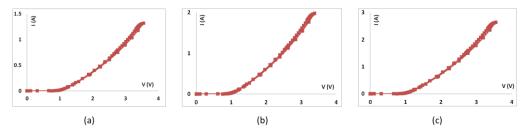

| Figure 2.3.4 Simulated transient ESD discharging I-V curves for sample STI core diode   |

|-----------------------------------------------------------------------------------------|

| ESD devices with different sizes: (a) 60µm, (b) 100µm and (c) 120µm 103                 |

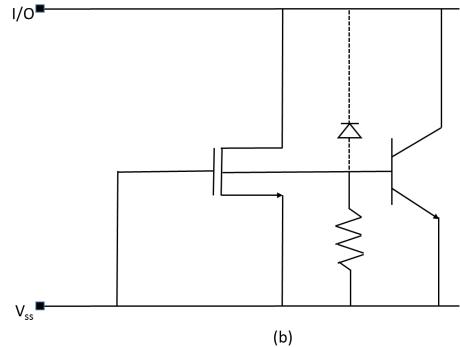

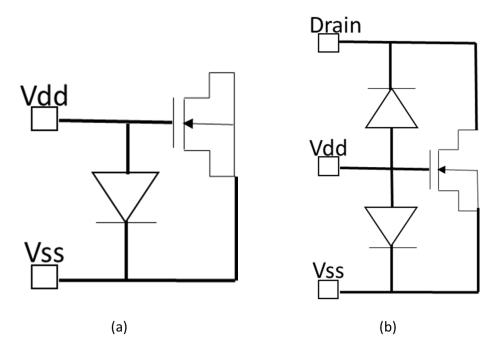

| Figure 2.3.5 Schematics for ESD dummy gate monitor circuits: (a) gate ESD testing       |

| monitor only, and (b) gate ESD monitor and MOFET I-V testing circuit 104                |

| Figure 2.3.6 Simulated ESD I-V curve for a dummy ESD gate monitor circuit block         |

| shows transient ESD discharging behavior                                                |

| Figure 2.3.7 Simulated ESD discharging voltage in time domain for a dummy ESD gate      |

| monitor circuit shows ESD clamping voltage with respect to MOSFET gate breakdown        |

| voltage in core and I/O process sections                                                |

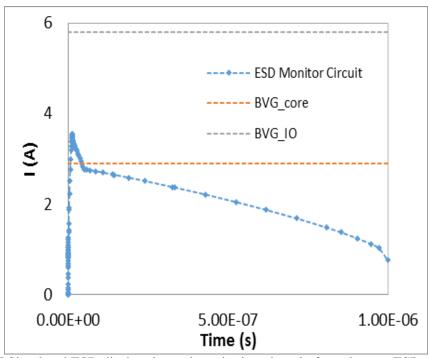

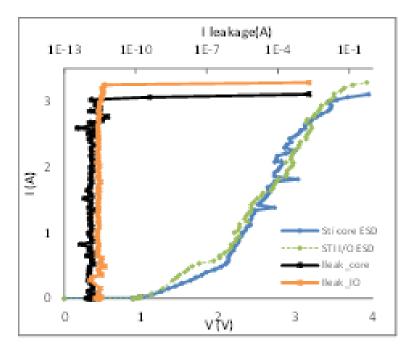

| Figure 2.3.8 Measured ESD discharging I-V curves by TLP testing for STI diode ESD       |

| devices (100µm finger width) designed in core and I/O process modules achieve It2>3A,   |

| translating into HBM ESD protection level of $> 4.5$ kV as predicted by ESD simulation. |

|                                                                                         |

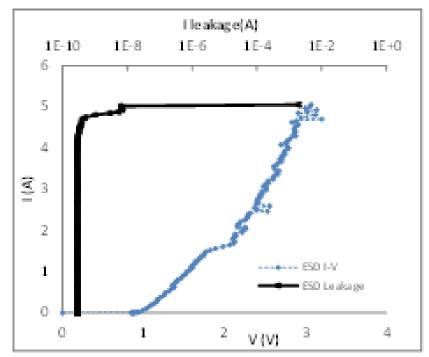

| Figure 2.3.9 Measured ESD I-V curves for a sample N+/P-well poly-gated diode of         |

| 120µm show desired ESD discharging behaviors                                            |

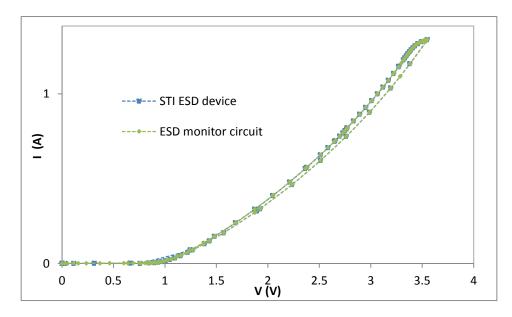

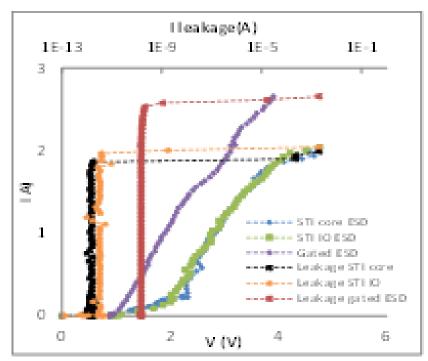

| Figure 2.3.10 Measured ESD I-V curves for sample STI core and I/O diodes and gated      |

| diode of 60µm reveal details and differences in ESD performance                         |

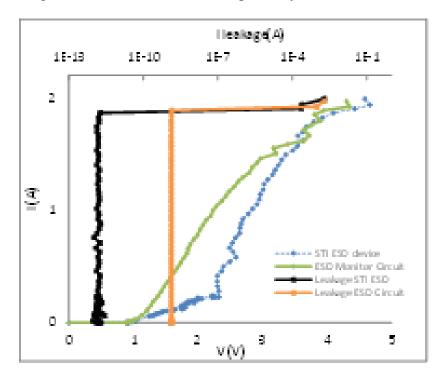

| Figure 2.3.11 Measured ESD discharging I-V curves for a sample STI core diode ESD       |

| devices of 60µm and its ESD gate monitor circuit confirms proper ESD protection at chip |

| level                                                                                   |

## List of Tables

| Table 2.2.1 Vt1 and Vh for sample NCQD ESD protection structures at different gate  |

|-------------------------------------------------------------------------------------|

| biasing VG by TLP                                                                   |

| Table 2.2.2 Erasing/Programming Results for a W10µm/L0.15µm SONOS-based ESD         |

| Protection Structure                                                                |

| Table 2.2.3 Programming/Erasing Results for a W10µm/L0.16µm SONOS-based ESD         |

| Protection Structure                                                                |

| Table 2.2.4 Nanocrossbar ESD structure design matrix.    92                         |

| Table 2.3.1 Comparison of measured ESD-critical parameters for sample STI and gated |

| diode ESD devices of different dimensions                                           |

#### Section 1 Soft Underlayers for Next Generation Magnetic Recording Media

#### **Chapter 1.1 Introduction to Hard Disk Drives (HDDs)**

Since the late 1950s IBM introduced random access method of accounting and control (RAMAC), hard disk drives (HDDs) have been used in computers. The first-generation HDDs were costly and bulky but advanced the random access feature for the main frame computers of that era. After improved over time, the HDDs entered the personal computer in the 1980s. Recently, HDDs are also being widely used in consumer electronics applications to store information, like iPods, video cameras, cell phones, game consoles etc. [1]. As the improvement of HDDs with larger capacity and smaller size over time, some analysts predict that more HDDs will be needed in the computers and consumer electronics market while the markets for other technologies such as flash memory and optical storage devices starts to grow.

Until recently, longitudinal recording technology is used to store information in the HDDs. In longitudinal recording technology, the magnetizations that lie longitudinally (parallel to the disk surface) are used for storing information. Alternative technologies such as perpendicular recording, in which magnetizations lie perpendicular to the disk surface, were proposed in the late 1970s to overcome some of the potential problems with longitudinal recording, especially the superparamagnetic limit faced by the longitudinal recording [2-4]. Efforts have been made to optimize the materials and introduce new techniques to produce better recording layers and soft underlayers (SULs) for the perpendicular recording media, which would provide comparable or superior performance

than the longitudinal recording media [5-9]. Significant improvements have also been made in the head design [10-11]. All these factors now make perpendicular recording more competitive.

#### 1.1.1 Overview of Longitudinal Magnetic Recording

Paulsen invented magnetic recording a century ago, which relies on two basic principles: (i) Strong magnetic field at the poles which produced by the magnets can be used for reading information. (ii) The polarity of the magnets itself can be changed by applying external field, which provides the possibility of writing information. Therefore, a magnetic recording device would need to have the following key components: a recording medium to store information, a write head to produce localized magnetic fields which used for writing information, and a read sensor to convert the magnetic field from the media to electrical (voltage) signals for reading information. And there are many other components to position the head, to interpret the voltages into bits, and so on.

In the first few generations of HDDs, and in many tape storage devices, such as VCRs, a particulate medium (which is essentially a mixture of magnetic particles in a binder) was used [1]. The medium was primarily iron (III) oxide, however, this particulate medium cannot have a high saturation magnetization since the saturation magnetization of the magnetic material will be diluted by the binder. In the early days, a high saturation (or remanent) magnetization was required from the recording media, since the signal will be proportional to remanent moment and thickness of the media and the heads were not sensitive enough to detect weak signal. Another problem was that the

coercivity could not be tailored easily to meet the high-density requirements. Therefore, thin film media were considered as alternative in the HDDs, for their high saturation/remanent magnetization, high coercivity and also smooth surfaces. Therefore, particulate media were phased out from HDDs in the 1980s. In this section, some of the requirements of longitudinal recording media and the ways they were achieved are discussed.

#### 1.1.1 Granular Media

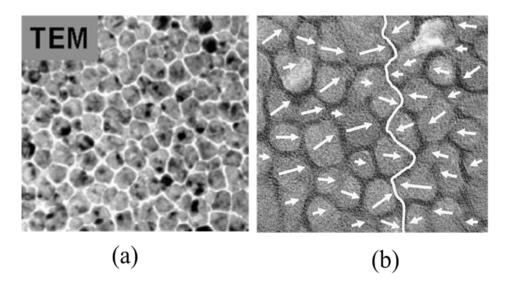

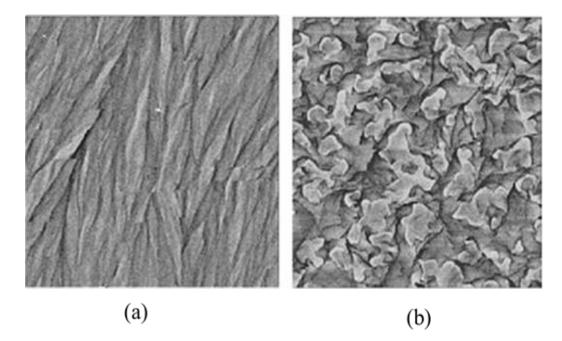

Thin film media are usually deposited by DC or RF magnetron sputtering onto glass or aluminum substrate disks. Current recording media have several functional layers to achieve desired performance. However, it is the magnetic layer that stores the information. And the magnetic layer produced by sputtering is a polycrystalline material. Therefore the grains of the recording medium would have random orientations with respect to the film plane and the track direction as well. Moreover, they would also be arranged in random positions and sizes and may have a random easy axis orientation. Because of the randomness of the grains used in storing the information, a group of grains are used to store information. The group of grains which acts as a larger, single magnet, is called a "bit". The bits are used to record binary code "0" and "1". Information could be stored by aligning the net magnetization of the grains in a bit in one direction. Depends on the quality of the media, the read/write head and the overall technology of the hard disk drive, the group grain can vary from as few as 20 grains to several hundred. Older generations of HDDs will use more grains per bit than new generations. The borders of these bits make up the "bit boundary", which is one of several factors that determine the signal-to-noise ratio (SNR). Figure 1.1.1(a) is the TEM image of granular magnetic media. Figure 1.1.1(b) illustrates the randomness of easy-axis orientations and the bit boundary.

Figure 1.1.1 (a) TEM image of a granular medium. (b) Illustration of grains, the randomness of easy-axis orientations and the bit boundary.

The signal-to-noise ratio (SNR) is approximately given by the expression

$$SNR = 10 \log(N), \tag{1}$$

where N is the number of grains in a bit. To some extent, the SNR at a particular linear density is an indicator of how reliable the bits could be read out at that linear density. Therefore, SNR is a key indicator of the recording performance of a recording medium.

Equation (1) indicates that increasing the number of grains would help increase the SNR. Therefore, one way to increase the SNR of the recording medium is to reduce the

grain size and grain size distribution, which can increase the number of grains in the bit area. However, simply apply more grains in the bit area without reducing the grain size would also increase SNR while at the same time reduce the areal density of the recording medium. Grain size reduction can be achieved by the use of seedlayers and /or underlayers with small grain size or from the magnetic layer itself [12-22].

#### 1.1.2 Orientation of Grains

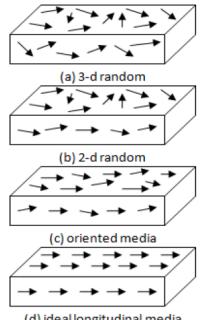

According to Equation (1), which assumes the SNR is proportional to the number of grains because the randomness involved in the grain orientation and grain size. In the case of longitudinal media, the magnetization of the grains should lie parallel to the track direction. However, when the thin film media is sputter-deposited, the randomness of grain size and magnetization orientation occurs in order to minimize the energy of the film. One way to minimize the randomness is to improve the number of grains that have an easy axis along the film plane. Several underlayers such as Cr, CrTi, CrV, CrMo, or combinations of these have been used to improve the c-axis orientation parallel to the film plane [12][23-29]. It has also been reported that the use of intermediate layers helps to improve the easy axis orientation by improving the lattice matching between the Cr underlayers and the CoCrPt based magnetic layers [30]. In addition to using an underlayer and an intermediate layer to improve the in-plane easy-axis orientation, another way to minimize the randomness is to increase the number of grains that have an easy axis orientation parallel to the track direction. Figure 1.1.2 illustrates the magnetization orientation for different media configuration. A recording medium in which the magnetic

moments are randomly oriented with respect to the plane and the track [Figure 1.1.2 (a)] would have the lowest SNR. This is because, in such a recording medium, the component of magnetization that lies parallel to the disk surface or the track direction is low. This will lead to a reduction in the signal and an increase in the noise. The SNR can be increased by maximizing the number of grains that are oriented parallel to the disk surface [Figure 1.1.2 (b)]. This is typically achieved by the use of underlayers such as Cr, as discussed previously. Further increase of SNR can be obtained by aligning the magnetization of the grains along the track direction [Figure 1.1.2 (c)]. This could be achieved by the texturing process, which leads to an increased orientation ratio. Figure 1.1.2 (d) illustrates the ideal configuration for obtaining very high SNRs, though it is not possible to achieve such orientations experimentally.

(d) ideal longitudinal media

Figure 1.1.1.2 The randomness of easy axis orientation: (a) three-dimensional (3D) random, (b) two-deminsional (2D) random, (c) oriented media, and (d) ideal orientation.

#### **1.1.3 Challenges of Longitudinal Magnetic Recording**

From the recording media perspective, the improvement of the recording media is always focused on controlling exchange coupling between the grains. Even if the magnetic grains are very small, having high exchange coupling enlarges the magnetic domains of the media, which in turn increases the smallest possible bit size, which then reduces the areal density of the film. Some of the initial research work on the reduction of exchange coupling between the grains relied on the surface morphology of the underlayers. A rough surface was obtained by depositing very thick underlayers, which led to a physical separation between the magnetic layer grains [31], thus reduce the exchange coupling between the grains of the recording layer. However, thick underlayers also led to a larger grain size in the recording layer. Therefore, better methods were needed to separate the magnetic layer grains from each other. By compositional segregation at high temperatures, exchange decoupling could be obtained [24]. It is possible to sputter a recording medium that has two regions with different properties. The core of the grain would have magnetic properties and the grain boundary would have nonmagnetic properties. Thus, the nonmagnetic grain boundary would reduce the exchange coupling.

In magnetic recording, the energy barrier that prevents the magnetization of a particle from flipping is proportional to anisotropy energy  $K_uV$ , where  $K_u$  is the anisotropy constant of the material and V is the volume of the grain. It is this anisotropy

energy that helps to store the bit and make HDD a nonvolatile storage device. If the particle has to switch its magnetization from one direction to another, energy has to be supplied to overcome the energy barrier. An applied external field, which alters the energy barrier, is usually required to switch the direction of magnetization. In magnetic recording, this external field is applied using the write head, which is an electromagnet with nanometer scale gaps.

In the previous section, it was discussed that the mean grain size and the grain coupling in longitudinal recording media need to be reduced to increase the areal density. However, the reduction of these two parameters leads to a reduction in the grain volume and, therefore, a reduction in the energy barrier for magnetization reversal, since the  $K_u$  is intrinsic property of the material and fixed. When the anisotropy energy  $K_uV$  gets lower, the thermal energy ( $k_BT$ ) starts to compete with the anisotropy energy and makes the magnetization thermally excited and reversed. This phenomenon, where the nano magnetic particles could flip their magnetization without any external field, is called superparamagnetism. Since a recording medium is composed of different size grains, some of the smaller grains would be more susceptible to thermal switching. And it has been reported that the data will be lost even if 5% of the magnetization reverses due to thermal excitations [32-33]. For a medium to be thermally stable, the above quantity  $K_uV$  should be substantially greater (>~40) than the thermal energy  $k_BT$ , and this is also the scale limit of the grain [34]. The HDD industry was no longer able to increase the areal density by simply scaling down, new methods and technologies should be considered.

The superparamagnetic limit is the physical limit of longitudinal recording technology that enhanced the current interest in perpendicular recording. However, the bottleneck for longitudinal recording technology is still based on the available write head materials to write information. It is still possible to make longitudinal recording media that can provide thermal stability at higher areal densities than the present densities. However, writing and reading information from such a medium remains a challenge.

#### 1.1.2 Overview of Perpendicular Magnetic Recording

Demagnetizing fields are experienced in any ferromagnetic or ferrimagnetic system and are expressed as

$$H_d = -NM, \tag{2}$$

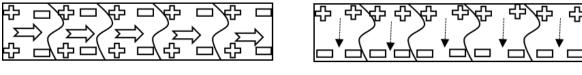

where N is the demagnetization tensor which depends on the shape and direction of the magnet and M is the magnetization vector. The rule of thumb is that the demagnetization field is stronger when the magnetic charges or the magnetic poles are nearer. In longitudinal recording, as the linear density increases, the distance between the magnetic charges or the magnetic poles decreases, as seen in Figure 1.1.3. Strong forces are experienced between neighbor tracks. This leads to an increased demagnetizing field.

Longitudinal

Figure 1.1.3 Illustration of magnetic charges and the associated demagnetizing fields for longitudinal and perpendicular recording.

However, in perpendicular recording technology, the demagnetization field would be reduced at high linear densities. Since they experience a much weaker force coming from the magnetic field of neighboring tracks.

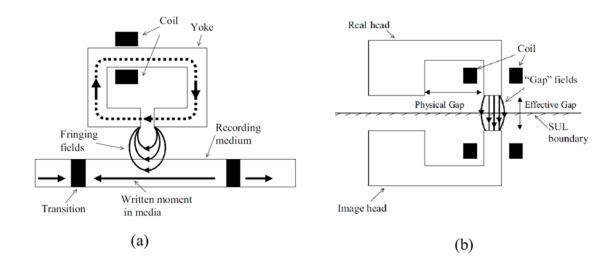

Although several configurations for perpendicular recording have been proposed, the invention of double-layered perpendicular recording medium (CoCr recording layer and NiFe as SUL) and the single-pole head design are crucial for the superiority of perpendicular recording over longitudinal recording. Together, these inventions provide superior writing performance on perpendicular recording than is possible in longitudinal recording. Figure 1.1.4 illustrates the writing process in longitudinal and perpendicular recording. In longitudinal recording, if the fringing field from the head is higher than that of the coercivity of the grain, the magnetization will be reversed and writing will be achieved. In the recording medium, the grains have different energy barriers because of the distribution in the size and anisotropy constant. Therefore, in order to reverse all the grains at smaller time scales encountered in hard disk recording, the field from the head is made to be two to three times the coercivity of the material. In longitudinal recording, the maximum longitudinal recording field generated by a ring head (RH), the fringing field  $(H_f)$  is approximately  $2\pi M_s$ , where  $M_s$  is the saturation magnetization for the material [35]. For comparison, in perpendicular recording, the maximum recording field generated by a single pole head (SPH), the gap field  $(H_g)$  is  $4\pi M_s$  [36-37]. Thus, in longitudinal recording, the weaker field is used to write the information. In perpendicular recording, the higher write field is achieved by the use of a soft underlayer and a single pole head, as illustrated in Figure 1.1.4 (b). Since SUL is highly permeable, it acts as a magnetic

10

mirror, which forms a closed loop for the magnetic flux of the pole head. It can be visualized that in perpendicular recording the media is virtually placed in the gaps of the poles and hence under higher writing fields. The direct consequence of higher writing field is the ability to write onto a higher anisotropy medium (higher  $K_u$ ). The use of higher anisotropy media materials allows higher areal densities without compromising thermal stability of the recording data.

Figure 1.1.4 Writing process in (a) longitudinal and (b) perpendicular recording. In perpendicular recording technology, the medium is virtually placed in the pole gaps between the head and the mirror image in SUL.

In spite of several advantages that the perpendicular recording had over the longitudinal recording technology, the perpendicular was not given a serious thought until lately. The areal density demonstrations on perpendicular recording media were lagging behind that of longitudinal recording. One reason was that a smaller grain size could be achieved in longitudinal recording then the possible grain size in perpendicular recording. Also, in the early 2000s, in order to obtain the desired grain boundary segregation, higher

compositions of Cr was studied in perpendicular recording. However, the presence of more Cr also led to a reduction in the anisotropy constant of the grains. In such case, some grains may be more sensitive to thermally assisted switching and become a source of dc noise. In addition, the soft underlayer issues were also not solved, which led to an inferior performance of perpendicular recording. Despite all these setbacks, perpendicular recording became the most likely candidate for the technology to be implemented in the next generation HDDs when an areal density of 340 Gbits/in.<sup>2</sup> was reported. For the past five years or so, significant progress were made in the perpendicular recording. The progress came from the recording layer and soft underlayers of the recording media, and also writing heads, made perpendicular recording technology more promising [5][9][38-41].

#### **1.1.3 Description of Various Layers and Their Functions**

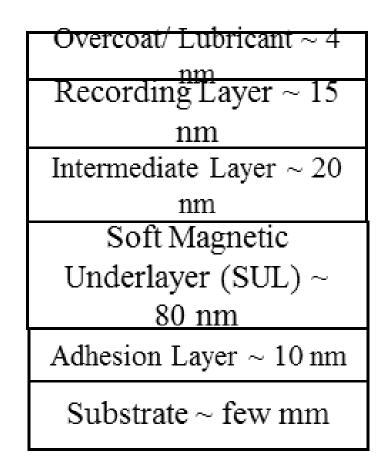

Figure 1.1.5 shows various functional layers, such as the soft underlayer, recording layer, etc., of a typical double-layered perpendicular recording medium. In the practical designs, there may be more than one layer involved for every function. The most advanced or exploratory designs may have a totally different structure than described. However, for the sake of simplicity, only a simple design is shown to illustrate the function of each layer.

The recording medium may be coated on an AlMg alloy precoated with a NiP layer or a glass substrate of a dimension suitable for its particular application. For example, an outer diameter of 3.5 in. or more disk substrates could be used in server and desktop HDDs. Outer diameter of 2.5 in. disk substrate can be used for laptops. HDDs with a diameter range of 1-2 inches are used for small electronic devices such as MP3 players, etc. Most of the layers in a hard disk medium are deposited by the sputtering process. Prior to the deposition of any layer, the substrates are cleaned to remove chemical and particle contaminants. Then, the substrate is first coated with an adhesion layer or an interface layer, made of Ta, Ti, or an alloy of these materials. This layer helps in improving the adhesion of SUL and all the other layers with the substrate. The next layer deposited is a soft magnetic underlayer. The soft magnetic underlayer helps in conducting the flux from the writing pole of the head to the trailing pole, as previously discussed. On top of the SUL, some intermediate layers may be deposited with or without seed layers. The intermediate layers aim at least two functions in the recording layer. One is to eliminate the exchange-coupling of the SUL and recording layer. If the SUL and the recording layers are coupled, the recording medium may show a larger noise during readback. Another function of the intermediate layer is to provide epitaxial growth conditions for the recording layer to obtain perpendicular orientation with respect to the film plane. Intermediate layers have also been served to decrease the grain size of the recording layer [42]. Usually, a seed layer is deposited below the intermediate layer to enhance a preferred growth. The recording layer is used to store information for long periods of time (about 10 years) and to produce the signal when reading back the information. The disk will then be coated with carbon overcoat layer and lubricants to prevent the corrosions of the recording layer. Typically, an amorphous carbon layer and a diamond-like carbon (DLC) layer are used. While both serve to prevent failures, the DLC layer also helps in the bonding of the lubricant layer to the disk. The lubricant layer is used to ensure a uniform fly-height of the recording head and to prevent wear and tear on the head, which can cause the head to crash onto the disk.

Figure 1.1.5 Different functional layers of perpendicular recording medium with approximate thickness (layers are not to scale).

#### 1.1.3.1 Soft Magnetic Underlayers

As discussed previously, the soft magnetic underlayer in the perpendicular recording media is helpful during the writing of information. It is the presence of a soft magnetic underlayer in the recording medium that provides a significant advantage for perpendicular recording technology. Higher writing fields can be achieved with a soft magnetic underlayer and a single-pole head, thus, materials with high  $K_u$  can be used as the recording media. Therefore, smaller grains can be used to store information in the recording medium. With smaller and stable grains, higher linear density could be achieved. Thus, soft magnetic underlayer is a significant part of perpendicular recording technology. The fact that the longitudinal media did not require a soft magnetic underlayer created a handful of new challenges in perpendicular recording, which are described below.

During the fabrication of a recording medium, all the layers except the lubricant are deposited by a sputtering process. The disk substrate (glass or Al-alloy) will pass from one sputtering chamber to another and finally leave the deposition system. During this process, each layer will be sputtered in a sputtering chamber that is isolated from the rest of the chambers. This helps to avoid contamination. The number of disks that can be produced by a system in 1 h throughput depends on the time that each disk spends in a particular chamber. The deposition of thicker layers needs longer time to sputter, which would reduce the throughput. It has to be noted that the thickness of SUL alone could equal the total thickness of longitudinal media, thus, the manufacturing efficiency is reduced. Another manufacturing problem that would arise because of thicker SULs is that higher deposition rates would be needed, which are usually achieved at higher powers. However, sputtering at higher power would cause spitting of particles, which would deteriorate the surface of the disk and make it unsuitable for the flying heads in a hard disk drive. Therefore, thicker layers are not desirable in the production. In order to avoid the above problems, thicker layers are usually deposited in two or three chambers to increase the throughput. This leads to an increase in the number of sputtering stations, which will lead to a significant investment. However, if the performance of perpendicular recording media is significantly higher, investment will out of the concern. This was one reason why the industry did not choose perpendicular recording technology for a long time, as the longitudinal recording media provided significant performance and cost advantages.

The fact that the SUL is too thick compared to the recording layer and is also made of materials with a larger magnetization than that of the recording layer also leads to the problem of noise from the SUL. As early as 1984, it has been reported that the presence of SUL, such as Permalloy, can increase the noise from the formation of domains [43]. Three different kinds of noises contributed by the SULs were reported: spike noise, medium noise, and low noise [44]. Spike noise arises due to the domain walls of the SUL. The medium noise, which arises because of the interaction between the SUL and the residual magnetization of the head, was weaker than the spike noise but larger than the low noise.

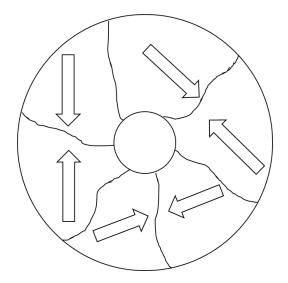

In the absence of a field, a soft underlayer may form domains, such as stripe domains or 180° domains, as these are ways to minimize the magnetostatic energy. However, the formation of such domain walls would also generate strong magnetic fields, which will cause strong noise during the reading process. A 180° domain wall with the magnetization along the track direction can be considered similar to a transition in longitudinal recording. In longitudinal recording, the signal produced by such a transition will be proportional to its  $M_r\delta$ . Therefore, if a thick SUL forms a 180° domain wall, the signal produced will be very high. Figure 1.1.6 illustrates such a situation. Therefore, a 180° domain wall of such a SUL will produce a signal (rather, it should be called noise, since SUL is not supposed to produce any signal during the reading) much stronger than that of longitudinal or perpendicular recording media. Therefore, the noise from the soft underlayer is a serious concern. If the domain walls formed in the SUL are fixed in one position, it would be possible to mark that position of the hard disk drive as a bad sector and still use perpendicular recording. However, the domains that cause the spike noise may move from one place to another [46]. Therefore, domain walls are a serious concern. Figure 1.1.7 shows MFM images of stripe domains formed in Permalloy thin films. Stripe domain periodicity is increased due to increasing film thickness. Even though the stripe domains are not as severe as the 180° domains, stripe domains also cause noise during the reading.

Figure 1.1.6. Illustration of 180° domain formation in SUL.

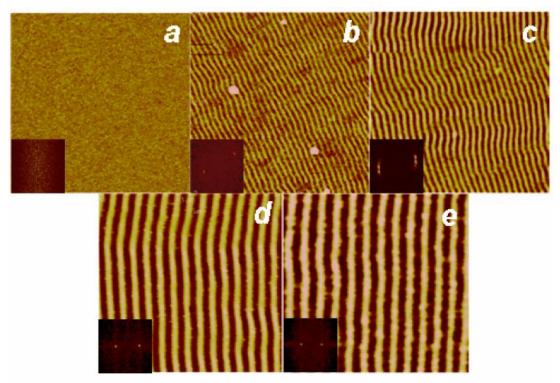

Figure 1.1.7  $5 \times 5 \ \mu m^2$  MFM images of Permalloy thin films representing the growth in stripe domain periodicity due to increasing film thickness: (a) lack of stripe domain structures, (b-e) increasing periodicity of stripe domains.

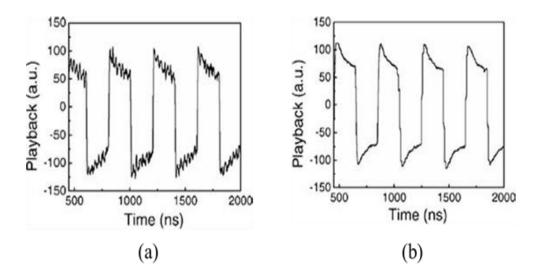

It has been reported that when the stripe domains were swept away by using external magnets (biasing) during the reading process, thus, no undesired stray field could be generated and the noise was much lower and the signal was higher. Figure 1.1.8 illustrates the spinstand-measured signal profiles along a track recorded into a perpendicular medium with and without external magnetic field.

Figure 1.1.8 Spinstand-measured signal profiles along a track recorded into a perpendicular medium with (a) a non-biased SUL and (b) a biased SUL.

One approach is to use new materials that could probably show fewer domains and hence a lower spike noise. Another approach is to do laminations of SUL material to minimize the domain formation. A third approach is to combine new materials, laminations, and/or processes. However, an easier alternative to reduce the noise of soft magnetic underlayers is to use antiparallel coupled soft underlayers (APC SUL) through a thin Ru layer. In this case, two or more soft magnetic underlayers could be made to couple to each other antiferromagnetically during the reading, and theoretically the remanances of each layer should cancel each other, as in Figure 1.1.9. However, during the writing process, the Zeeman energy would overcome the antiferromagnetic coupling energy [47]. Therefore, the two layers are aligned in the same direction and would produce a high field during writing. Such an antiferromagnetic coupling has been reported to reduce the noise of the SUL.

Figure 1.1.9 Magnetization of two layers of antiferromagnetically coupled SUL during the writing and reading (remanence).

Another problem with the use of a SUL is the difficulty in controlling its magnetic "softness." Some experiments indicate that the "softness" of a SUL strongly depends on its thickness and the bit pattern in the recording layer above it. Figure 1.1.10 illustrates how MFM image may change depending on the "softness" of SUL. Permalloy was used as the SUL material. Figure 1.1.10 (a) and (b) images correspond to adequately "soft" and strongly biased (or "hard") cases, respectively. The noticeable unidirectional orientation in Figure 1.1.10 (a) is due to the existence of an "easy axis" with an anisotropy field,  $H_k$ . Some effective "biasing" of SUL was predicted to take place in a thin layer of SUL close to the recording layer as the bit dimensions become smaller than the domain wall width

[48]. In the "hard" case, the SUL fails to screen off the demagnetized information in the recording layer or, in other words, loses its main purpose of being "soft." These measurements indicate that there is some limiting or "dead" thickness value, below which the SUL could not further adequately function.

Figure 1.1.10 MFM images of a SUL corresponding to (a) the relatively "soft" and (b) strongly biased ("hard") cases.

# 1.1.3.2 Intermediate Layers

When a magnetically soft underlayer and a hard layer are next to each other, their magnetic properties would change because of the exchange coupling interaction. Such an exchange interaction could reduce the coercivity of the recording layer and produce a larger noise during the readback. Thus, intermediate layers are inserted between the SUL and recording layer in perpendicular recording as an exchange breaking layer to reduce the noise. Thus, the optimization of the intermediated layer thickness together with the noise of the SUL are crucial to perpendicular recording.

Another function of intermediate layers is to induce a perpendicular hcp (002) orientation for the Co-alloy-based recording layer. In Co-alloy-based perpendicular recording media, the easy axis (*c* axis of the hcp crystal) needs to be deposited with a perpendicular orientation with respect to the substrate. In the current design of perpendicular recording media, amorphous materials such as CoTaZr or FeCoB are considered as the SUL because they could provide a lower noise. Moreover, the amorphous SULs also exhibit a very low average roughness (closer to that of the substrate) of about 0.15 nm. When a Co alloy is deposited directly on top of the *a*-SUL, the hcp (002) texture would not easily developed. Therefore, it is essential to grow intermediate layers that would induce a hcp (002) orientation on the Co-alloy-based recording layer. Recently, intermediate layer has also been loaded with an additional role of producing the right morphology to control the segregation of grains in the recording layer.

#### 1.1.3.3 Recording Layers

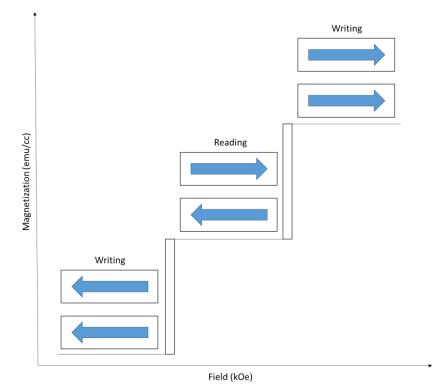

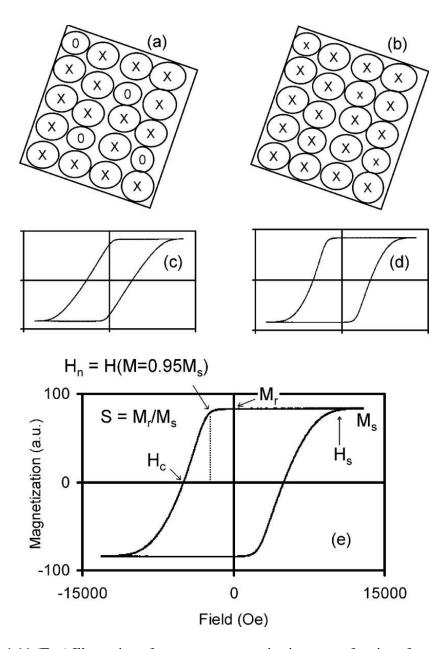

The material used for the recording layer of the perpendicular media has traditionally been a Co alloy. The CoCr alloy was the original media proposed in the late 1970s. Since then, modifications of Co alloys such as CoCrPt, CoCrTa, CoCrNb, CoCrPtNb, and CoCrPtB were used as the recording layer material [49-56]. One of the major problems of CoCr-alloy media materials was that the nucleation field (field required to switch 5% of the magnetization) of the recording layer was seen in the first quadrant of the hysteresis loop [57]. This implies that at zero fields magnetization of several grains has already reversed. Such grains with reversed magnetization would exhibit a high dc noise. Figure 1.1.11 is an illustration to show the significance of nucleation field. The grains are magnetized into the plane of the paper with an applied field. When the field is removed, all the grains are expected to maintain the magnetization if they are thermally stable and their anisotropy energy is higher than that of the demagnetizing energy.

However, if the anisotropy constant of the media is not high, some grains (smaller ones) would reverse, as in Figure 1.1.11 (a). However, if the anisotropy is high enough, all the grains would maintain their magnetization in the applied field direction, as in Figure 1.1.11 (b). This could be seen as hysteresis loops with nucleation fields in the first quadrant and second quadrant for media with low  $K_u$  and high  $K_u$ , respectively (Figure 1.1.11 (c) and 1.1.11 (d)). Therefore, media with high anisotropy are needed to obtain a negative nucleation field. In the earlier days, it was difficult to obtain such media as Cr was used as an additive element to obtain the exchange decoupling. As a side effect, the presence of Cr led to media with lower anisotropy energy.

Figure 1.1.11 (Top) Illustration of remanence magnetization state of grains of perpendicular media after it was saturated with a field into the plane. (a) Grains with a lower anisotropy constant show a reversal with remanent magnetization out of the plane showing instability. (b) Grains with a higher anisotropy constant show stable magnetization. (Middle) Illustration of hysteresis loops of the respective media that show (c) a positive  $H_n$  and (d) a negative  $H_n$  (bottom) hysteresis loop with relevant parameters.

Recently, oxide-based CoCrPt materials have received attention of researchers. In these media, CoCrPt is sputtered together with an oxide such as Si-oxide or Cr-oxide. This oxide element can be present in the target or can be formed in the film during the reactive sputtering of target in an oxygen atmosphere [53][40-41][58-61]. As the oxide and Co do not mix well, Co alloy grain is surrounded by an oxide based grain boundary. In order to form this grain boundary the amount of Cr needed in the target material is not high. About 5–10 at. % of Cr is sufficient, as compared to 14–17 at. % of Cr needed in the CoCrPt media without oxides. Moreover, out of the 5–10 at. % of Cr available in the target, some of the Cr would oxidize and go to the grain boundary as well. As a result, the grain could have a low Cr in its core and a high anisotropy constant. Such grains would be thermally stable, and squareness close to one could be achieved. The oxide based grain boundary is also effective in reducing the grain size and in reducing the intergranular exchange interaction. Therefore, the noise can be reduced and sharper transitions are possible. Another advantage of oxide-based CoCrPt materials is that the manufacturing process will be more or less similar to that of longitudinal recording media. And, more importantly, small grain size, low noise, and good thermal stability could all be achieved with oxide-based media.

In order to continue the use of CoCrPt-oxide media, it will be necessary to identify suitable oxide materials as the recording layers or other methods that would form a narrow grain boundary but effectively decouple the grains. The new oxide materials should also help in achieving narrower grains and a narrower grain size distribution. The future media would also have a higher anisotropy constant to overcome the thermal instability issues by reducing the Cr content or by increasing the Pt content. Reducing the grain size and distribution of the existing CoCrPt-oxide media using other methods is also possible.

### **Chapter 1.2 Magnetic Properties Optimization for Amorphous Soft Underlayers**

#### **1.2.1 Introduction**

The study of amorphous soft magnetic thin films has been receiving great attention recently since they are a key component in modern magnetic recording technologies. Applications involving amorphous soft magnetic thin films include high frequency magnetic recording heads, soft magnetic underlayers (SULs) in perpendicular magnetic recording, soft magnetic underlayers and interlayers that could be potentially used in multilevel three-dimensional magnetic technologies [62-63]. Nowadays, double-layer perpendicular media are routinely used for high-density magnetic recording media; therefore, finding a soft magnetic underlayer with optimal properties is crucial [64]. In order to optimize the performance of the magnetic writing heads, SULs with low coercivity and large value of  $B_{st}$  ( $B_{s}$  is the saturation magnetic flux density, t is the thickness of the SUL) are required [65]. Adequately high magnetic anisotropy field ( $H_{k}$ ) is also a necessary parameter of SULs to reduce the domain wall noise during the read back process [66].

In this paper, a study of amorphous CoTaZr and CoFeTaZr thin films for soft magnetic underlayers is presented. Iron (Fe) is added to the composition of CoTaZr to enhance both its magnetic and corrosion-resistance properties. Both type of SULs are

26

comparatively investigated. CoFeTaZr amorphous thin films are further analyzed due to their superior magnetic properties. Various sputtering conditions were used to fabricate CoFeTaZr amorphous thin films on glass, silicon and silicon oxide substrates. The importance of using pre-sputtering substrate Ar milling and the processing pressure dependence on the CoFeTaZr amorphous thin films are also studied. Furthermore, the effect of capping layers (Ta and Ru) and seed layers (Cu, Ta and Ru) on the magnetic properties of the CoFeTaZr amorphous thin films are examined.

### **1.2.2 Experiment**

CoTaZr, CoFeTaZr, Ta and Cu layers were all deposited via DC-magnetron sputtering in an AJA 1600 system. The Ru layers were deposited via RF-magnetron sputtering to improve the control of the sputtering rate. All samples were sputtered at a common base pressure of  $<2\times10^{-7}$  Torr. DC input power of 112.5 Watt for CoFeTaZr and CoTaZr SULs were used and the argon sputtering pressure was varied to achieve the desired sputtering rate. Ta capping layers and seedlayers were deposited under DC input power of 75 Watt and argon sputtering pressure of 10 mTorr with a sputtering rate of 0.831 Å/s. DC input power of 75 Watt, argon sputtering pressure of 5 mTorr, and a sputtering rate of 1.456 Å/s were used to fabricate the Cu seedlayers. Argon sputtering pressure of 5 mTorr was used for the Ru layers, with 60 Watt RF input power with a sputtering rate of 0.202 Å/s for the Ru capping layer and 22.5 Watt RF input power with a sputtering rate of 0.047 Å/s for the Ru seedlayer. Single crystal Si (100), silicon oxide and glass were used as the substrates for the thin films. The silicon oxide substrates were

made by growing a 200 nm oxide on the Si (100) substrates by chemical vapor deposition. Acetone and IPA were used to clean the substrates before loading them into the chamber of the sputtering system. Magnetic biasing was introduced in order to produce the easy-axis of magnetization.

The coercivity measurements were performed using Magneto Optical Kerr Effect (MOKE) microscopy with a field step of 0.1 Oe. Kerr rotation was used for easy-axis magnetization measurements and hard-axis magnetization measurements with Helmholtz coils.

The in-plane magnetic moment was measured using Vibrating Sample Magnetometry (VSM) system PPMS from Quantum Design, with the sensitivity of under  $10^{-6}$  emu for the average measurement time of 1 s. All the measurements were carried out at room temperature with a field step of 15 Oe.

Sputtering rate and roughness characterization were carried out via AFM Dimension 3100 system in tapping mode. In order to calculate the sputtering rate, materials were deposited on photolithography-featured substrates. The photoresist was then lifted off to obtain the thickness and thus the sputtering rate of the materials. NSC 15/Si<sub>3</sub>N<sub>4</sub>/NoAl probes from MikroMasch were used for sputtering rate characterization and FMR probes from Nano world were used for roughness measurements.

## **1.2.3 Results and Discussions**

#### **1.2.3.1** The Role of Ar Ion Milling on Substrate

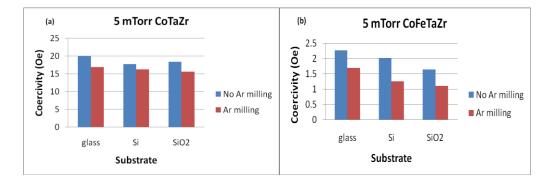

Amorphous CoTaZr and CoFeTaZr thin films were first prepared by sputtering under 5 mTorr Argon sputtering pressure and 112.5 Watt DC input power on glass, silicon and silicon oxide substrates. Films were prepared with and without the Ar presputtering milling before sputtering in order to examine its effects both on the CoTaZr and CoFeTaZr thin films. It was observed that samples with the Ar pre-sputtering milling showed superior magnetic properties, as shown in Figure 1.2.1. Roughness measurements were also carried out on the glass, silicon and silicon oxide substrates with and without Ar pre-sputtering milling, but did not show any significant difference, the roughness are all between 0.2-0.3 nm. Ar pre-sputtering milling helps to remove particles and contaminants on the substrate surfaces before sputtering, thus, making the surface of the substrates much cleaner and smoother for film growth. Since Ar milling produced improved results, Ar milling was used before sputtering for all samples in this study.

Figure 1.2.1 Ar ion milling effect on the magnetic properties of amorphous (a) CoTaZr and (b) CoFeTaZr thin films sputtered at 5 mTorr Ar processing pressure.

#### 1.2.3.2 Comparison Between CoTaZr and CoFeTaZr Amorphous Thin Films

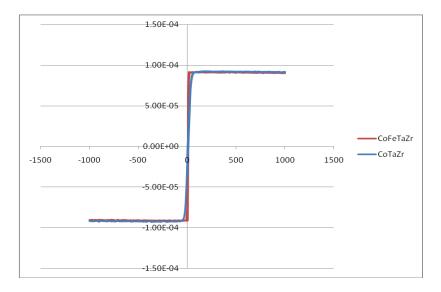

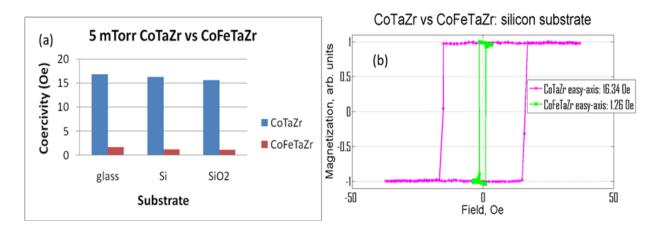

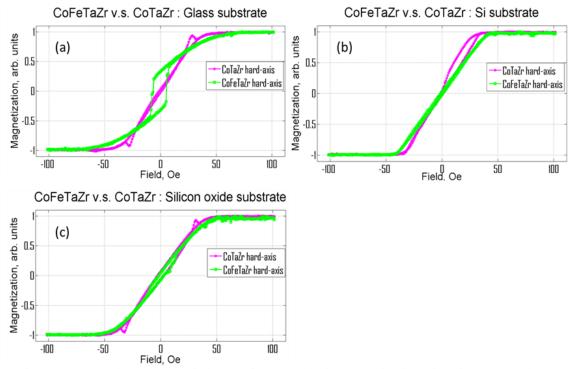

Recently, CoTaZr amorphous thin films have been intensively studied because of their importance as an SUL for perpendicular recording [67]. Considering the characteristics of SULs, CoTaZr amorphous thin film exhibits the best overall characteristics, like corrosion, thermal stability and abrasion resistance [68]. In this paper, the magnetic properties of CoTaZr and CoFeTaZr amorphous SULs were compared. They were all fabricated under the same sputtering conditions and thicknesses with Ar sputtering pressure of 5 mTorr and DC input power of 112.5 Watt. A comparison of the magnetic moment and coercivity of the CoFeTaZr and CoTaZr films on different substrates are shown in Figure 1.2.2, 1.2.3. The in-plane magnetic moment of CoFeTaZr and CoTaZr films are almost the same, and the magnetization of these two films are around 1150 emu/cm<sup>3</sup>. In perpendicular magnetic recording (PMR) media SUL is commonly used for providing the closed flux loop and thus increases recording field by approximately a factor of two from the write head due to the mirror effect [69]. However, due to magnetic domain walls in the SUL, SUL also increases the magnetic noise during the read back process. Hence, large uniaxial or unidirectional magnetic anisotropy field (H<sub>k</sub>) is essential for SUL to reduce domain wall noise and exhibits improved field gradient and writing performance simultaneously [66]. In this study, the uniaxial or unidirectional magnetic anisotropy field (Hk) of CoTaZr and CoFeTaZr thin film is around 60 Oe. The CoFeTaZr films produced over 10 times lower coercivity than the CoTaZr films. The in-plane hysteresis loops of the hard-axis magnetization direction on different substrates are presented in Figure 1.2.4. Adding Fe in the composition helps to reduce the coercivity while maintain the same magnetization.

Figure 1.2.2 Magnetic moment comparison between CoTaZr and CoFeTaZr amorphous soft magnetic underlayers.

Figure 1.2.3 (a) Coercivity comparison between CoTaZr and CoFeTaZr amorphous soft magnetic underlayers fabricated under same sputtering conditions with 5 mTorr Ar sputtering pressure. (b) In-plane hysteresis loops of the hard-axis magnetization direction on silicon substrates.

Figure 1.2.4 In-plane hysteresis loops of the hard-axis magnetization direction on (a) glass substrates, (b) silicon substrates, and (c) silicon oxide substrates.

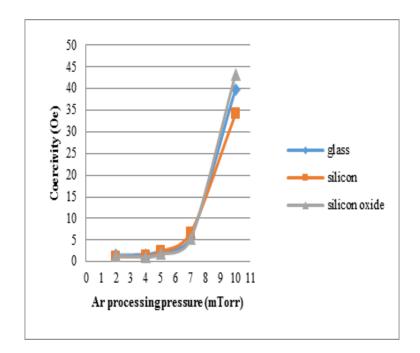

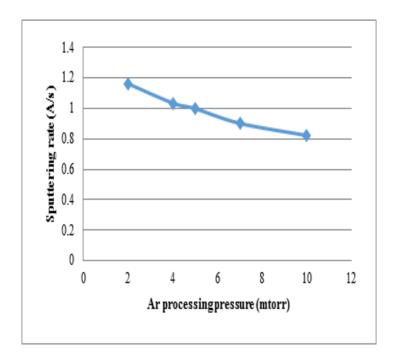

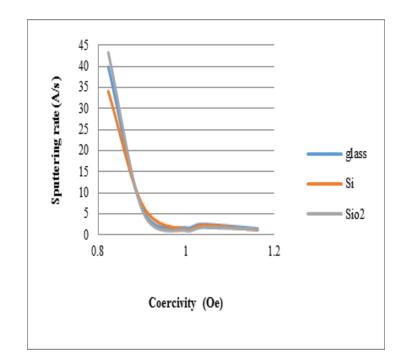

## 1.2.3.3 Pressure Dependence of CoFeTaZr Amorphous Thin Film

The Ar sputtering pressure of the CoFeTaZr films was varied from 2 to 10 mTorr. Higher sputter pressure resulted in higher coercivity, as seen in Figure 1.2.5. This is due to the samples sputtered at higher pressure having higher roughness [67]. Lower Ar sputtering pressure also resulted in a higher sputtering rate, as seen in Figure 1.2.6. And thus, higher sputtering rate resulted in lower coercivity, as seen in Figure 1.2.7. Since a lower sputtering rate is easier to control the thin film growth, 5 mTorr processing Ar pressure was chosen over 2 mTorr processing Ar pressure for future experiments.

Figure 1.2.5 CoFeTaZr amorphous thin film coercivity dependence vs. processing Ar pressure sputtered on various substrates.

Figure 1.2.6 Sputtering rate vs. processing Ar pressure.

Figure 1.2.7 Sputtering rate vs. coercivity dependence.

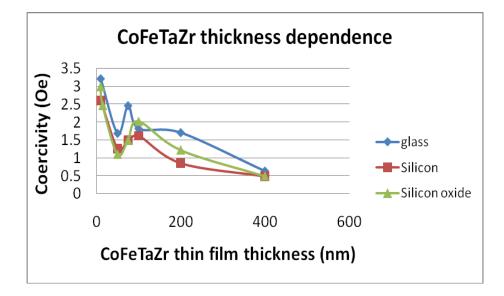

# 1.2.3.4 Thickness Dependence of CoFeTaZr Amorphous Thin Film

SULs are used for conducting flux from the recording head for double-layer perpendicular recording. The pole dimensions, the write pole moment and the moment of SUL will affect the thickness of CoFeTaZr SUL which can vary from 10 to hundreds of nanometers. However in this range, magnetic domains are observed [5][53][70-72]. Media noise will increase under a certain critical thickness due to these magnetic domains [8].

CoFeTaZr amorphous thin films were prepared under the same sputtering conditions (Ar sputtering pressure 5 mTorr, DC input power of 112.5 Watt) with varying thicknesses to measure the thickness effect on coercivity. The coercivity of the CoFeTaZr SULs decreased as the thickness increased, as seen in Figure 1.2.8 However, there was a sudden increase between 50 nm and 100 nm. The coercivity then decreased as the thickness increased from 100 nm to 400 nm.

Figure 1.2.8 Coercivity vs. thickness dependence of CoFeTaZr amorphous thin films sputtered on different substrates.

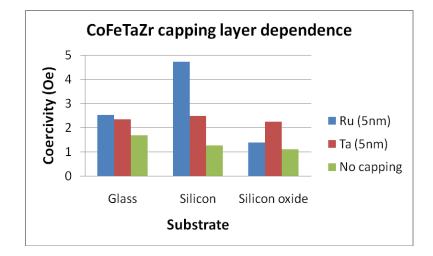

# 1.2.3.5 Capping Layer Dependence of CoFeTaZr Amorphous Thin Films

Capping layers are used to protect the SULs from oxidation but can also affect the magnetic properties of the SULs. CoFeTaZr samples with a 5 nm Ru capping layer, a 5 nm Ta capping layer and no capping layer were prepared to study the effects of the capping layer on the magnetic properties of the SULs. Samples without a capping layer showed lower coercivity, as seen in Figure 1.2.9. The Ta capping layer produced lower coercivity compared with the Ru capping layer. The increase in coercivity due to the capping layers may be caused by the capping layers inducing a perpendicular (out-of-

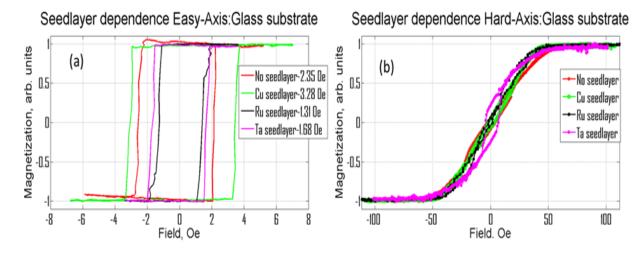

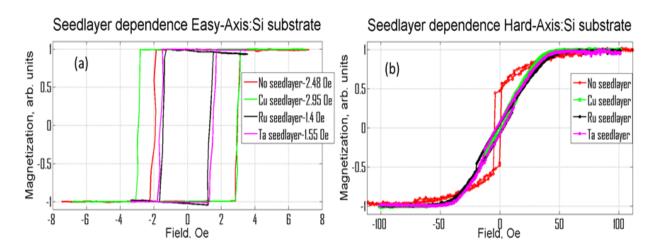

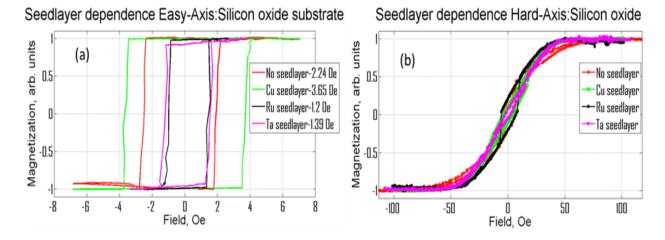

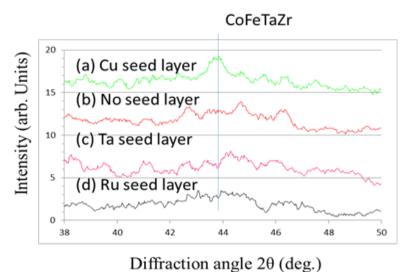

plane) component in the SULs [66]. The in-plane hysteresis loops of easy-axis magnetization and hard-axis magnetization on different substrates are also presented in Figure 1.2.10-1.2.12.