# UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Efficient Abstraction and Refinement for Word-level Model Checking

### Permalink

https://escholarship.org/uc/item/6jz4z4dn

#### **Author** Ho, Yen-Sheng

# **Publication Date** 2017

Peer reviewed|Thesis/dissertation

#### Efficient Abstraction and Refinement for Word-level Model Checking

By

Yen-Sheng Ho

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Robert K. Brayton, Chair Professor Sanjit A. Seshia Professor Alper Atamtürk

Fall 2017

# Efficient Abstraction and Refinement for Word-level Model Checking

Copyright 2017

by

Yen-Sheng Ho

#### Abstract

#### Efficient Abstraction and Refinement for Word-level Model Checking

by

Yen-Sheng Ho

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences University of California, Berkeley Professor Robert K. Brayton, Chair

Model Checking (MC) on a word-level circuit has important applications in the IC design industry, where MC is used to prove that a word-level circuit always satisfies a set of given properties. MC is challenging at the word level, when complex arithmetic operators like multipliers are involved. Abstraction and refinement are commonly used to address challenging MC problems. If an abstraction is proved, so is the original problem. Otherwise, spurious counterexamples are analyzed to refine abstractions. Although many abstraction refinement algorithms for word-level MC have been developed, few take full advantage of state-of-the-art bit-level MC algorithms, like Property Directed Reachability (PDR), which is considered the most efficient method for deriving unbounded proofs. Therefore, this thesis presents several techniques that enable efficient word-level MC by performing abstraction refinement at the word-level while verifying abstractions at the bit-level.

To compute good abstractions and refinements at the word-level, novel refinement strategies were proposed to take advantage of both structural and proof-based analysis. The proposed strategies are shown to achieve a good balance between the sizes of the abstractions and the number of refinement iterations needed for convergence.

To achieve efficient integration of abstraction refinement and bit-level MC algorithms, a bit-level algorithm, PDRA, was created, that minimally modifies the original PDR algorithm to perform on-the-fly abstraction refinement. Inspired by this, a word-level algorithm, PDR-WLA, was developed that efficiently integrates bit-level PDR implementations with word-level abstraction refinement. An important feature is the re-use of reachability information learned in previous refinement iterations.

Motivated by real industrial benchmarks characterized by having many related arithmetic operators, a word-level MC algorithm, UFAR, was proposed that uses uninterpreted functions (UF) constraints as a method of refinement. A UF constraint, between a pair of word-level operators, requires that if their inputs are equal then their outputs are equal. To enhance the applicability of UF constraints, a procedure for normalizing operators was devised. This allows UF constraints to be applied to a pair of same-type operators with different operator sizes and signedness. UFAR explicitly encodes UF constraints into word-level circuits. This allows any bit-level or word-level MC algorithm to be used, including both PDRA and PDR-WLA.

All these developments were implemented in a publically available model checking system, ABC. Experiments were done which show that UFAR successfully solves most cases in a large set of challenging benchmarks provided by an industrial collaborator.

To My Family.

# Contents

| Li                        | ist of | Figures                                                     | v   |

|---------------------------|--------|-------------------------------------------------------------|-----|

| $\mathbf{L}^{\mathrm{i}}$ | ist of | Tables                                                      | vii |

| A                         | cknov  | wledgments                                                  | ix  |

| 1                         | Intr   | oduction                                                    | 1   |

|                           | 1.1    | Word-level Circuits                                         | 2   |

|                           |        | 1.1.1 Registers                                             | 2   |

|                           |        | 1.1.2 Word-level Circuits as Directed Acyclic Graphs        | 3   |

|                           |        | 1.1.3 Bit-blasting                                          | 3   |

|                           |        | 1.1.4 Word-level Circuits as Finite State Machines          | 5   |

|                           | 1.2    | The Model Checking Problem                                  | 5   |

|                           | 1.3    | Algorithms for Model Checking Problems                      | 6   |

|                           | 1.4    | Counterexample-guided Abstraction Refinement                | 7   |

|                           | 1.5    | Challenges and Motivations                                  | 8   |

|                           | 1.6    | Contributions                                               | 9   |

|                           | 1.7    | Organization                                                | 10  |

| 2                         | Ref    | inement Strategies for Word-level Abstraction               | 11  |

|                           | 2.1    | Introduction                                                | 11  |

|                           | 2.2    | Preliminaries                                               | 12  |

|                           |        | 2.2.1 Word-level Localization Abstraction                   | 12  |

|                           |        | 2.2.2 Counterexamples                                       | 13  |

|                           |        | 2.2.3 Word-level CEGAR                                      | 15  |

|                           |        | 2.2.4 The Refinement Problem                                | 16  |

|                           |        | 2.2.5 Ternary Simulation and X-value Counterexamples (XCEX) | 17  |

|                           |        | 2.2.6 Assumption Interfaces in SAT Solvers                  | 18  |

|                           | 2.3    | Simulation-based Refinement (SBR)                           | 19  |

|                           | 2.4    | Proof-based Refinement (PBR)                                | 23  |

|                           |        | 2.4.1 Variants of Proof-based Refinement                    | 27  |

|                           | 2.5    | Maximum Fan-out Free Cone (MFFC) Refinement                 | 28  |

|   | 2.6 | Comparison of Refinement Strategies                        |

|---|-----|------------------------------------------------------------|

|   | 2.7 | Related Work                                               |

|   | 2.8 | Experimental Results                                       |

|   | 2.9 | Conclusion                                                 |

| 3 | Enh | ancing PDR with Localization Abstraction 35                |

|   | 3.1 | Introduction                                               |

|   | 3.2 | Background                                                 |

|   | 3.3 | Property Directed Reachability (PDR) 36                    |

|   |     | 3.3.1 The PDR Trace                                        |

|   |     | 3.3.2 Overview of PDR                                      |

|   | 3.4 | The Algorithm: PDRA                                        |

|   | 3.5 | Comparison with Previous Work                              |

|   | 3.6 | Experimental Results                                       |

|   | 3.7 | Conclusion                                                 |

| 4 | Pro | perty Directed Reachability with Word-Level Abstraction 50 |

|   | 4.1 | Introduction                                               |

|   | 4.2 | Preliminaries                                              |

|   |     | 4.2.1 The UMC problem                                      |

|   |     | 4.2.2 Property Directed Reachability                       |

|   |     | 4.2.3 Word-level Abstraction                               |

|   |     | 4.2.4 Simple CEGAR (S-CEGAR)                               |

|   | 4.3 | PDR with Word-Level Abstraction                            |

|   |     | 4.3.1 The Algorithm                                        |

|   |     | 4.3.2 Analysis of PDR-WLA                                  |

|   | 4.4 | Refinement                                                 |

|   | 4.5 | Related Work                                               |

|   |     | 4.5.1 Word-level Abstraction and Model Checking            |

|   |     | 4.5.2 PDR with Abstraction                                 |

|   | 4.6 | Experimental Results                                       |

|   | 4.7 | Conclusion                                                 |

| 5 | Uni | nterpreted Function Abstraction and Refinement 65          |

|   | 5.1 | Introduction                                               |

|   | 5.2 | Bit-Vectors and UF Constraints                             |

|   |     | 5.2.1 The MC Problem                                       |

|   |     | 5.2.2 Word-level Signals (Bit-Vectors)                     |

|   |     | 5.2.3 Basics of Word-level Operators                       |

|   |     | 5.2.4 Functions of Word-level Operators                    |

|   |     | 5.2.5 Generic Operators                                    |

|   |     | 5.2.6 Uninterpreted Function (UF) Constraints              |

|   |     |                                                            |

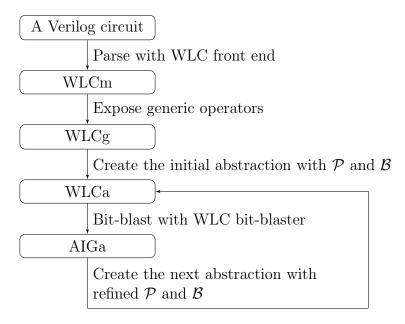

|    | 5.3   | UFAR                                          | 76  |

|----|-------|-----------------------------------------------|-----|

|    |       | 5.3.1 The Algorithm                           | 76  |

|    |       | 5.3.2 Exposing Generic Operators              | 78  |

|    |       | 5.3.3 Creating Abstractions                   | 79  |

|    |       | 5.3.4 Model Checking Using Concurrency        | 81  |

|    |       | 5.3.5 Refining UF Pairs                       | 84  |

|    |       | 5.3.6 Refining Black Operators                | 85  |

|    |       | 5.3.7 Analysis of UFAR                        | 88  |

|    | 5.4   | Improvement Techniques                        | 88  |

|    |       | 5.4.1 Minimizing Counterexamples              | 88  |

|    |       | 5.4.2 Performing Random Simulation            | 89  |

|    | 5.5   | The UFAR Framework                            | 91  |

|    |       | 5.5.1 Bit-blasting WLC with Verilog Semantics | 91  |

|    |       | 5.5.2 Creating Abstractions WLCa              | 92  |

|    | 5.6   | Related Work                                  | 92  |

|    | 5.7   | Experimental Results                          | 94  |

|    | 5.8   | Conclusion                                    | 101 |

| 6  | Con   | clusions                                      | 102 |

|    | 6.1   | Summary                                       | 102 |

|    | 6.2   | Future Work                                   | 103 |

| Bi | bliog | raphy                                         | 105 |

# List of Figures

| 1.1 | An example showing a word-level circuit with loops at flip-flops modeled as a directed acyclic graph (DAG).                                                                                                 | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.0 |                                                                                                                                                                                                             | 3  |

| 1.2 | An example showing a word-level circuit described in Verilog and its visualization as a DAG.                                                                                                                | 4  |

| 1.3 | A bit-level circuit bit-blasted from the word-level circuit in Figure 1.2. Symbol                                                                                                                           |    |

|     | $\wedge$ denotes a logic AND gate; dash arrows represent inverters                                                                                                                                          | 4  |

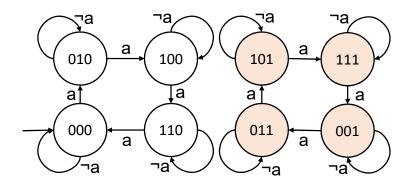

| 1.4 | The state transition graph of the circuit in Figure 1.2.                                                                                                                                                    | 5  |

| 2.1 | A combinational circuit illustrating word-level abstraction. $out \equiv 0$ , UNSAT,                                                                                                                        |    |

|     | since $2 \times x \equiv x + x$ , which forces <i>out</i> to be constant 0                                                                                                                                  | 14 |

| 2.2 | An example of refining the circuit in Figure 2.1b with $\Delta \mathcal{B} = \{n_4, n_5, n_8\}$ , a subset of the set of the current abstraction signals $\mathcal{B} = \{n_4, n_5, n_6, n_7, n_8, n_9\}$ . |    |

|     | The refined circuit is created from the original circuit using the updated set                                                                                                                              |    |

|     | $\mathcal{B} \setminus \Delta \mathcal{B} = \{n_6, n_7, n_9\},$ corresponding to PPIs = $\{c, d, f\}$ .                                                                                                     | 17 |

| 2.3 | An example showing a CEX can be minimized or generalized into an X-value                                                                                                                                    |    |

|     | CEX (XCEX). Symbol $\land$ denotes logic AND; dashed arrows represent logic NOT.                                                                                                                            | 18 |

| 2.4 | An example of refining the circuit in Figure 2.1b with $\Delta \mathcal{B} = \{n_8, n_9\}$ (PPIs                                                                                                            |    |

|     | $\{e,f\}$ ).                                                                                                                                                                                                | 21 |

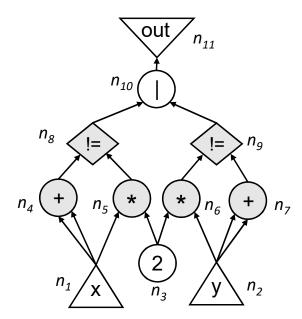

| 2.5 | A word-level abstraction example similar to the one in Figure 2.1; the node $n_{10}$                                                                                                                        |    |

|     | is changed to an OR gate. $out \equiv 0$ , UNSAT, since $2 \times x \equiv x + x$ , which forces                                                                                                            |    |

|     | out to be constant 0                                                                                                                                                                                        | 22 |

| 2.6 | An example of refining the circuit in Figure 2.5b with $\Delta \mathcal{B} = \{n_8\}$ (PPI e)                                                                                                               | 22 |

| 2.7 | A combinational circuit illustrating word-level abstraction. $out \equiv 0$ , UNSAT,                                                                                                                        |    |

|     | since $2 \times x \equiv x + x$ , which forces <i>out</i> to be constant 0                                                                                                                                  | 24 |

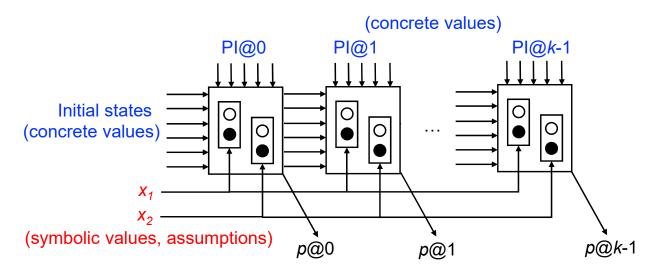

| 2.8 | An example of unrolling a circuit in PBR. $ITE$ operators (multiplexers) are introduced to select the concrete signals (white circles) and the abstracted ones                                              |    |

|     | (black circles). If all concrete signals are chosen, then the unrolling becomes the                                                                                                                         |    |

|     | same as the $k$ -unrolling of the original circuit, where the property holds under                                                                                                                          |    |

|     | the spurious CEX.                                                                                                                                                                                           | 25 |

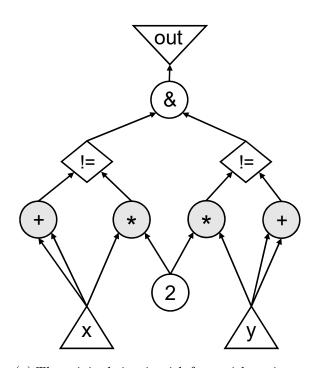

| 2.9                 | Example for proof-based refinement, where $x$ and $y$ are original PIs, $a-d$ are pseudo PIs, $s_1$ - $s_4$ are $sel$ PIs. This is created from the current abstraction shown in Figure 2.7b. If the assignments of $x$ and $y$ in $cex$ are plugged in, and assumptions are made that $s_1$ - $s_4$ are all 1, then <i>out</i> is constant-0 (UNSAT)                                                                               | 26       |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

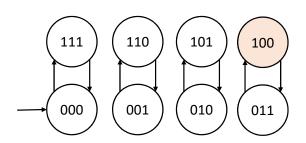

| $3.1 \\ 3.2$        | A simple finite state machine (FSM)                                                                                                                                                                                                                                                                                                                                                                                                 | 40<br>42 |

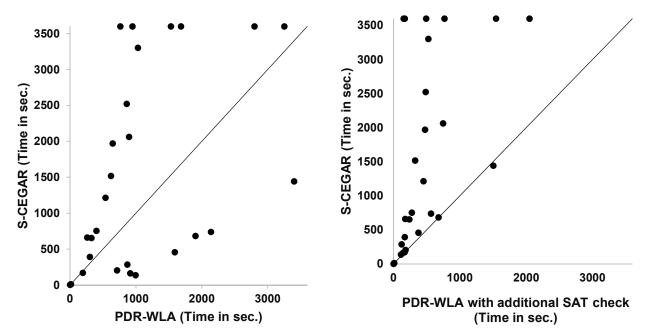

| 4.1<br>4.2          | A combinational circuit illustrating word-level abstraction. $out \equiv 0$ , UNSAT, since $2 \times x \equiv x + x$ , which forces $out$ to be constant 0 Comparison of PDR-WLA ( $\% pdra$ ) and S-CEGAR ( $\% abs$ ). This shows the effectiveness of re-using PDR traces. Note that PDR-WLA and S-CEGAR would be the same if no PDR traces can be re-used. Therefore, only 29 cases with non-zero re-used PDR traces are shown. | 55<br>62 |

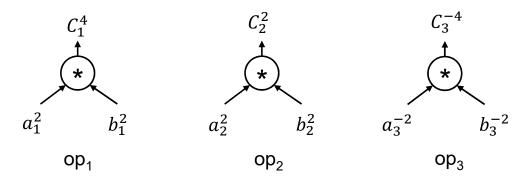

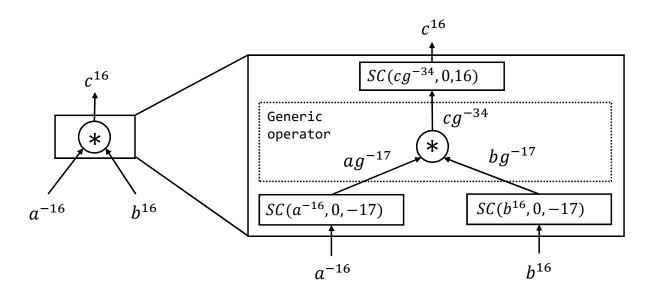

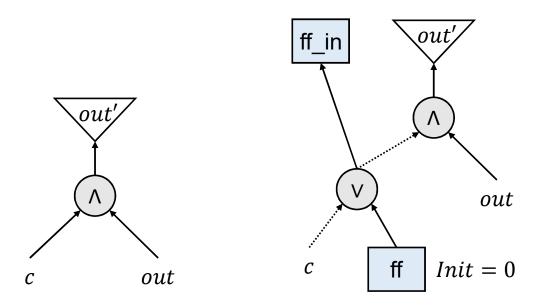

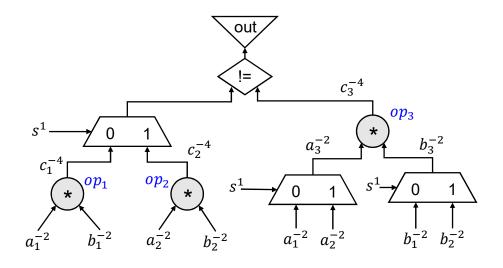

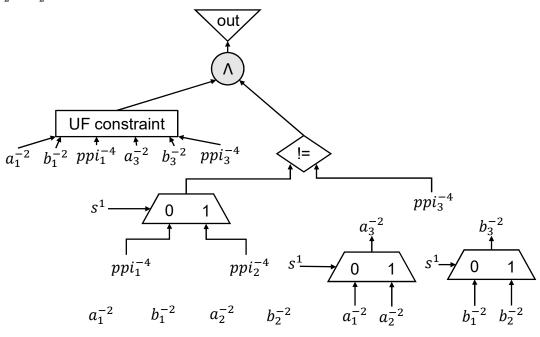

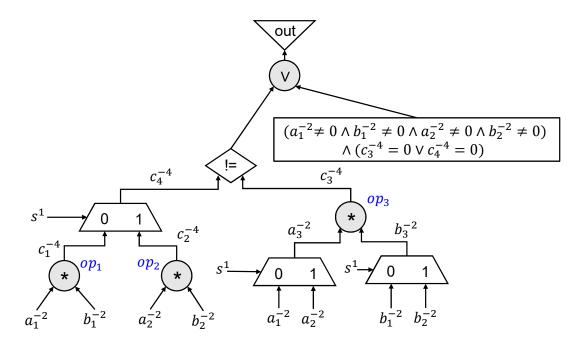

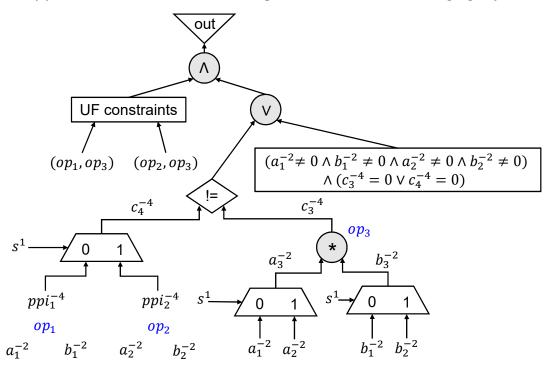

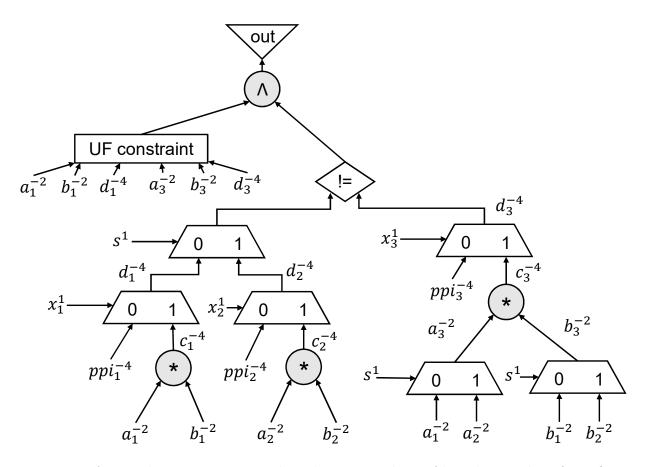

| $5.1 \\ 5.2 \\ 5.3$ | Three multipliers with different functions. $\dots$ An example showing how generic operators are modeled and exposed. $\dots$ An example showing how a UF constraint (signal $c$ ) is encoded as an invariant constraint in a circuit. Signal <i>out</i> is the original output where <i>out</i> = 1 means the property is violated. Signal <i>out'</i> is the new output with the UF constraint                                    | 69<br>74 |

|                     | encoded. Dashed arrows denote negations                                                                                                                                                                                                                                                                                                                                                                                             | 80       |

| 5.4                 | A combinational circuit illustrating word-level UF abstraction.                                                                                                                                                                                                                                                                                                                                                                     | 82       |

| $5.5 \\ 5.6$        | An example showing UF constraints are useful when applied to real multipliers.                                                                                                                                                                                                                                                                                                                                                      | 83       |

| 5.0                 | An auxiliary circuit created in the proposed proof-based procedure for refining<br>black operators. The original and the current abstraction circuits are shown in                                                                                                                                                                                                                                                                  |          |

|                     | Figure 5.4.                                                                                                                                                                                                                                                                                                                                                                                                                         | 87       |

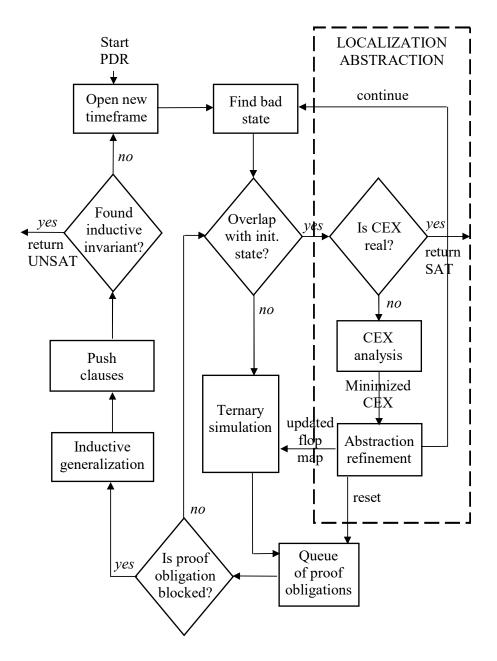

| 5.7                 | The flow of the UFAR framework                                                                                                                                                                                                                                                                                                                                                                                                      | 91       |

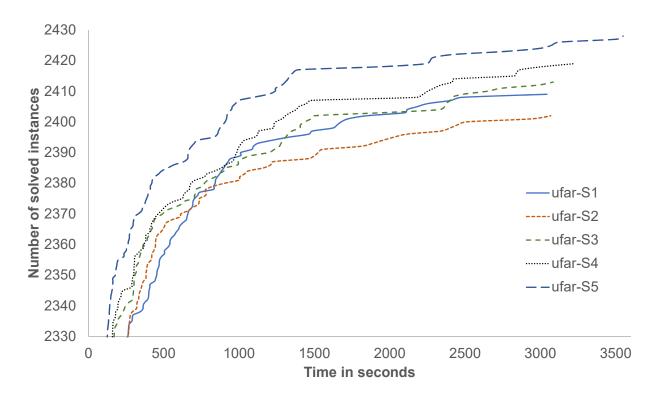

| 5.8                 | Comparison of five UFAR variants. The result of <b>super_prove</b> is not shown here because it only solves 2087 instances, well below the bottom scale of 2330                                                                                                                                                                                                                                                                     | 96       |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

# List of Tables

| 2.1                               | Detailed experimental results for the first 45 out of the 89 word-level test-cases<br>that can be solved by at least one of the six refinement strategies (the last 44 are<br>shown in the next table). $ S $ and $ B $ are sizes of the set of the initial targeted<br>signals ( $S$ ) and the set of signals to be abstracted away for each iteration ( $\mathcal{B}$ ) in<br>Algorithm 2.2.                                                                                                                                            | 31       |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <ul><li>2.2</li><li>2.3</li></ul> | Detailed experimental results for the last 44 out of 89 word-level test-cases that<br>can be solved by at least one of the six refinement strategies. $ S $ and $ B $ are sizes<br>of the set of the initial targeted signals ( $S$ ) and the set of signals to be abstracted<br>away for each iteration ( $\mathcal{B}$ ) in Algorithm 2.2.<br>Summary of Table 2.1 and Table 2.2 in terms of the number of test cases solved.                                                                                                           | 32<br>33 |

| 3.1                               | Comparing different flavors of PDR in terms of the number of solved cases and runtime on 77 industrial examples (implementations with abstraction, pdr -t, treb -abs, and pdr -nct, are compared against the baselines, pdr, treb, and pdr -nc).                                                                                                                                                                                                                                                                                          | 46       |

| 3.2                               | Comparing different flavors of PDR in terms of the frame count and the invariant size on 41 industrial examples (implementations with abstraction, pdr -t, treb -abs, and pdr -nct, are compared against the baselines, pdr, treb, and pdr -nc).                                                                                                                                                                                                                                                                                          | 48       |

| 4.1                               | Detailed experimental results for 20 unsatisfiable word-level test-cases. #HardSig-<br>nals is the number of hard signals (Definition 4.7). $ S $ and $ B $ are sizes of the set<br>of the initial targeted signals ( $S$ ) and the set of signals to be abstracted away for<br>each iteration ( $\mathcal{B}$ ) in Algorithm 4.3. #ReusedClauses is the number of clauses in<br>PDR traces re-used by PDR-WLA. The number is 0 if all refinements occur at<br>k = 0. The details of SBR, MFFC, PBR, and PBR-B can be found in Chapter 2. | 63       |

| 5.1<br>5.2                        | The standard integer functions (SIF) for Verilog operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71       |

|                                   | Blanks in CPU Time represent time-outs (1 hour).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 98       |

#### LIST OF TABLES

| cation set-<br>rs/bit-level |                                                                                       |

|-----------------------------|---------------------------------------------------------------------------------------|

| m rs/bit-level              |                                                                                       |

|                             |                                                                                       |

| white boxes                 |                                                                                       |

| e represent                 |                                                                                       |

|                             | 99                                                                                    |

| that can be                 |                                                                                       |

| f iterations                |                                                                                       |

| te boxes in                 |                                                                                       |

|                             | 100                                                                                   |

| ces remain                  |                                                                                       |

|                             | 101                                                                                   |

| e<br>t<br>f                 | chite boxes<br>e represent<br>that can be<br>f iterations<br>e boxes in<br>ces remain |

# Acknowledgments

I would like to express my deepest gratitude to my advisor, Professor Robert K. Brayton, for his endless patience of guiding me through my PhD years. Bob was always there and available. My favorite moments are those one-on-one meetings with Bob at his place. There were depressing times, but I gained energy and hope from Bob every time we met. Bob listened and understood my problems, giving his invaluable advice and warm encouragement. I always feel strongly supported by Bob. Without his support and guidance, I would not have accomplished this dissertation.

I would like to thank Dr. Alan Mishchenko for many stimulating discussions and critical feedback on my research. I was fortunate to have him as my unofficial co-advisor. I also learned a lot from his experience in developing ABC. Alan's enthusiasm for research and programming always inspired me to become a better researcher and programmer.

I would like to thank Professor Sanjit A. Seshia and Professor Alper Atamtürk for their constructive feedback on this dissertation. I would also like to thank Professor Edward A. Lee for serving on my qualifying examination committee. I would like to give special thanks to Professor Seshia for his guidance and mentoring during my first semester at Berkeley. I am grateful to Shirley Salanio for her help and support in graduate matters.

I would like to thank Pankaj Chauhan and Pritam Roy for mentoring me during my internships at Calypto. They had good influences in this thesis. I would also like to thank the whole SLEC team for making my internships at Calypto enjoyable and fulfilling.

I would like to thank Dr. Niklas Eén, Sayak Ray, Baruch Sterin, Jiang Long, and Yu-Yun Dai for many fruitful conversations and all the wonderful times we spent together in Bob's group. I am also thankful to Niklas for his mentoring in my early PhD years.

I would like to thank Wei Yang Tan, Antonio Iannopollo, Hokeun Kim, Tianshi Wang, Garvit Juniwal, Nishant Totla, Chung-Wei Lin, Pierluigi Nuzzo, Wenchao Li, Shromona Ghosh, and Baihong Jin for the intriguing conversations and all the functions in the DOP center. I would like to thank Semiconductor Research Corporation, National Science Foundation, National Security Agency, Altera, Atrenta, Cadence, Calypto, IBM, Intel, Mentor Graphics, Microsemi, Synopsys, and Verific for their financial supports and sponsorship.

Finally, I would like to thank my parents, my sister, and my brother for their unconditional love and strong support through all the years.

# Chapter 1

# Introduction

The development of integrated circuit (IC) design has been one of the main driving forces in technology. Bugs or errors in an IC can cause serious problems to a company or even human lives. Therefore, it is important to verify a circuit, checking if it is designed correctly according to its specifications. This process is called *verification*.

Verification can be either *simulation*-based or *formal*-based. In simulation-based techniques, an input vector is simulated on a circuit and the output results are checked against the specification. If the results are not consistent, then a bug is found. Otherwise, the circuit works properly under this input vector. However, as the complexity of an IC grows, it is impossible to simulate every possible input vector. If a simulation-based verification cannot cover all possible situations, then it cannot be concluded that a circuit is free of bugs. On the other hand, formal-based techniques automatically consider all possible inputs with the use of symbolic inputs and mathematical models of a circuit. This methodology is also known as *model checking* (MC), where a circuit is checked if a property holds under all possible situations. While MC is more powerful than simulation, it is less scalable on complicated designs. Improving the scalability of MC has been an active research area ever since its inception.

In the following sections, we introduce background material that is useful for understanding the problems, challenges, motivations, and contributions of this dissertation. Section 1.1 describes word-level circuits, which are the typical level of descriptions used for IC designs. These descriptions are the inputs to word-level model checking problems. Model checking word-level problems is the major focus of this thesis. The problem of model checking and state-of-the-art algorithms are presented in Section 1.2 and Section 1.3. Abstraction and refinement are discussed in Section 1.4. Challenges in word-level MC and motivations of this dissertation are given in Section 1.5. This chapter is then concluded in Section 1.6 by outlining the main contributions. The organization of this thesis in given Section 1.7.

# 1.1 Word-level Circuits

Practical circuits are usually specified at the *word level*, where bits are grouped as *words* or *bit-vectors*. A word-level circuit can be modeled at the *Register-Transfer Level (RTL)* in a hardware description language like *Verilog*.

**Definition 1.1.** A word-level signal, or bit-vector, of size m is a finite function whose domain is  $\{x | x \in \mathbb{N}, 0 \le x < m\}$  and the co-domain is  $\{0, 1\}$ . A word-level signal b with size mis denoted as  $b^m$ . For example, a word-level signal  $b^3$  can have  $b^3(0) = 1$ ,  $b^3(1) = 0$ , and  $b^3(2) = 1$ .

A word-level circuit is composed of two main parts, registers and combinational logic. Registers synchronize the behaviors of a circuit according to *clocks*. Registers are the only elements in a circuit that have memory, storing logic values computed in the previous clock cycle. The combinational logic in a circuit determines the output values at the current cycle as well as new register values for the next clock cycle.

#### 1.1.1 Registers

A word-level circuit is assumed to have a single clock and a single type of register: a D flip-flop. If a circuit has multiple clocks or different types of registers, it can be normalized to a single clock through a technique called *phase abstraction* [BK05]. With this normalization, a circuit has a single universal clock that ticks periodically, generating *cycles*. All registers are initialized with some given values, and are updated to new values at each clock cycle based on their inputs. In particular, every register is a D flip-flop that contains three components:

- 1. *The initial state*. This is the initial value for the register, which can be either a constant or a non-deterministic value.

- 2. The current state. This is the output of this register, which is the value available at the current cycle. It is also called *the flop output (FO)*.

- 3. The next state. This is the input of this register, which is a function of the inputs and the current states in this circuit. The register will be updated to this value at the beginning of the next cycle. It is also called *the flop input (FI)*.

For the rest of this thesis, we will use the terms *flip-flops* or simply *flops* to refer to registers in a circuit.

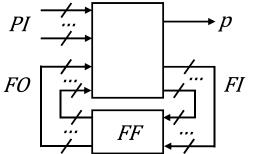

(a) A word-level circuit with feedback loops (cycles) at flip-flops (FF).

(b) The DAG transformed from the cyclic circuit in (a) with FFs modeled as flop outputs (FO) and flop inputs (FI).

Figure 1.1: An example showing a word-level circuit with loops at flip-flops modeled as a directed acyclic graph (DAG).

#### 1.1.2 Word-level Circuits as Directed Acyclic Graphs

A word-level circuit often contains feedback loops broken by flip-flops (FF), because next states are usually functions of current states. Given the simplified register model described in Section 1.1.1, a word-level circuit can be modeled as a directed acyclic graph (DAG) by breaking the feedback loops at the flip-flops, illustrated in Figure 1.1. At each clock cycle, the values of flop inputs (FI), or next states, and primary outputs (PO) are functions of flop outputs (FO), or current states, and primary inputs (PI). Internal nodes in a circuit are word-level operators such as such as  $\{+, -, *, /, \%, \ll, \gg, \ll, \$\}$  as well as the usual bit-level operators such as  $\{\neg, \land, \lor\}$ . A word-level operator takes input signals (operands) and produces a result in its output signal according to its functionality.

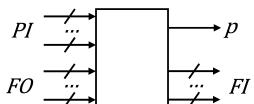

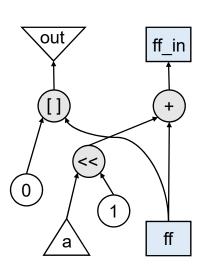

**Example 1.1.** Figure 1.2 shows an example of a word-level circuit described in Verilog and its visualization as a DAG. The nodes shown in Figure 1.2b are  $PIs = \{a\}$ ,  $POs = \{out\}$ ,  $FOs = \{ff\}$ ,  $FIs = \{ff\_in\}$ , constants  $\{0, 1\}$ , and word-level operators  $\{\ll, +, []\}$ .

#### 1.1.3 Bit-blasting

A word-level circuit can be *bit-blasted* into an equivalent bit-level circuit consisting of only logic gates such as  $\{\neg, \land, \lor\}$ . The process is called *bit-blasting*.

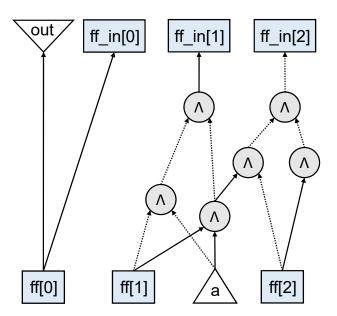

**Example 1.2.** Figure 1.3 shows a bit-level circuit bit-blasted from the word-level circuit shown in Figure 1.2. The bit-level circuit is an And-Invertor Graph (AIG) with AND gates  $(\wedge)$  and invertors (dashed arrows).

```

module main (a, clk, out);

input a;

input clk;

output out;

wire

[2:0] ff_in;

reg

[2:0] ff;

ff = 3'b000;

initial

assign ff_in = ff + (a << 1);</pre>

always @(posedge clk) begin

ff <= ff_in;</pre>

end

assign out

= ff[0];

endmodule

```

(a) The Verilog snippet of a word-level circuit.

(b) The DAG visualization of the circuit described in (a).

Figure 1.2: An example showing a word-level circuit described in Verilog and its visualization as a DAG.

Figure 1.3: A bit-level circuit bit-blasted from the word-level circuit in Figure 1.2. Symbol  $\land$  denotes a logic AND gate; dash arrows represent inverters.

Figure 1.4: The state transition graph of the circuit in Figure 1.2.

#### 1.1.4 Word-level Circuits as Finite State Machines

In a word-level circuit, the state space is finite because there are a finite number of finitesized flip-flops. Moreover, under the simplified register model, the behavior of a circuit at each cycle is well defined by its combinational logic. Therefore, a word-level circuit can be modeled also as a finite state machine (FSM).

**Definition 1.2.** An *FSM* is a tuple M = (I, O, S, Init, T) where I is the set of PIs, O is the set of POs, S is the set of FFs, *Init* is the set of initial states, and T is the set of (deterministic) transition relations where  $T \subseteq I \times S \times S$ . If  $(i, s, s') \in T$ , there exists a transition from s to s' under input i.

**Example 1.3.** The word-level circuit shown in Figure 1.2 can be modeled as an FSM. Its state transition graph is shown in Figure 1.4. The shaded states are the ones that make the PO out = 1.

## 1.2 The Model Checking Problem

The inputs to the model checking (MC) problem are an FSM, M, and a property specified in Linear Temporal Logic (LTL) [Pnu77]. The LTL property is assumed to be transformed into a *safety* property, p, through a technique for example proposed by Claessen et al. [CES13]. In terms of LTL, the MC problem is to check if the following formula holds.

$$M \models \mathbf{G}p.$$

If the above formula is true, then the model M satisfies the property p globally.

An MC algorithm should either report a *counterexample* (CEX) that falsifies the property or produce an *inductive invariant* proving that the property always holds.

**Definition 1.3.** A *counterexample (CEX)* is a trace consisting of a sequence of PI assignments driving the design from an initial state into a state falsifying the property.

**Definition 1.4.** An *inductive invariant* (Inv) proving a property P is a set of states that a) contains the initial states (Init), b) does not contain states falsifying the property, and c) contains all states 1-step reachable from the states contained in this invariant. Formally, it is a predicate function satisfying the properties below.

1.

$$Init(s) \implies Inv(s)$$

- 2.  $Inv(s) \wedge T(i, s, s') \implies Inv(s')$

- 3.  $Inv(s) \implies P(s)$

**Example 1.4.** For the circuit shown in Figure 1.2, if we let the PO represent the violation of the property, then the problem has a unique inductive invariant,  $Inv = \neg ff[0]$ , which proves the property. The invariant contains all four non-shaded states in Figure 1.4.

## **1.3** Algorithms for Model Checking Problems

Fundamental algorithms for model checking have been developed over the past few decades. Symbolic model checking with binary decision diagrams (BDD) was the first symbolic technique for MC problems [Bry92, BCM<sup>+</sup>92]. Later, Boolean satisfiability (SAT) solvers achieved major breakthroughs with conflict-driven clause learning [SS96] and two-literal watching [MMZ<sup>+</sup>01]. The first SAT-based model checking algorithm was bounded model checking (BMC) proposed by Biere et al. [BCCZ99]. *k*-induction was proposed to enhance BMC with unbounded proofs [SSS00]. Interpolation-based model checking was the first algorithm that explicitly computes over-approximations of reachable states to prove a property [McM03]. IC3 was proposed in 2011 [Bra11], later improved as Property Directed Reachability (PDR) [EMB11], has been considered the best performing algorithm in proving properties. In this dissertation, we focus on three algorithms that work best for word-level model checking: BMC, *k*-induction, and PDR.

Given an FSM M = (I, O, S, Init, T) and a property p, BMC and k-induction both require *unrolling* of a circuit up to a certain depth k and then checking the satisfiability of the propositional formulas below.

$$Init(s_0) \wedge \bigwedge_{t=0}^{k-1} T(i_t, s_t, s_{t+1}) \wedge \bigvee_{t=0}^k \neg p(s_t)$$

(1.1)

$$\bigwedge_{t=0}^{k} T(i_t, s_t, s_{t+1}) \wedge \bigwedge_{t=0}^{k} p(s_t) \wedge \neg p(s_{k+1}) \wedge \bigwedge_{0 \le i \le j \le k+1} s_i \ne s_j$$

(1.2)

BMC checks Formula (1.1): if it is satisfiable (SAT), then BMC finds a CEX that falsifies the property within k cycles. Otherwise, the formula is unsatisfiable (UNSAT), meaning there is no CEX within k cycles. BMC then either terminates with this bounded proof, or increases the depth k for the next check. k-induction checks an additional formula (1.2): if it is UNSAT, then it is proved that there exists no trace with the first k states satisfying the property and the k + 1-th state falsifying the property. If Formula (1.1) is also UNSAT, the property holds globally. Formula (1.1) and (1.2) can be viewed as the *base case* and *inductive step* in mathematical induction, respectively.

In contrast, PDR does not require unrolling of a circuit. Instead of checking a large and difficult formula like (1.1) or (1.2), PDR incrementally learns reachability information in a circuit using many small formulas like (1.3). More details of PDR will be presented in Chapter 3.

$$R_j(s) \wedge \neg c(s) \wedge T(i, s, s') \wedge c(s') \tag{1.3}$$

# 1.4 Counterexample-guided Abstraction Refinement (CEGAR)

In practice, directly solving a MC problem may not scale well due to the high complexity of the problem. *Abstraction* is often used to simplify the original problem. The idea is to create a new abstraction circuit such that if it can be proved that there is no CEX for the abstraction, then there is no CEX for the original circuit also. On the other hand, if a CEX is found in the abstraction, the CEX can be either *real* or *spurious* (Definition 1.5).

**Definition 1.5.** Given an original circuit M and an abstraction circuit A of M, a CEX of A is *real* if it can falsify the property on M. Otherwise, it is *spurious*.

A spurious CEX does not tell whether the property is proved or falsified in the original circuit. However, it provides information on how to *refine* the current abstraction to make the property more provable. An ideal refined abstraction is still an abstraction of the original model, but refutes the existence of the previous spurious CEX. The process of creating a new abstraction to block a spurious CEX is called *refinement*.

Counterexample-guided abstraction refinement (CEGAR) is a framework that combines the ideas of abstraction and refinement for MC problems [CGJ+00]. An overview of CEGAR is shown in Algorithm 1.1. CEGAR starts by creating an initial abstraction from the original

```

Algorithm 1.1 Counterexample-guided Abstraction Refinement (CEGAR)

Input: M

\triangleright M: the input circuit

Output: status \in { SAT, UNSAT }

1: A \leftarrow \text{CREATEABSTRACTION}(M)

2: while true do

cex \leftarrow MODELCHECKING(A)

3:

if cex \neq \emptyset then

4:

if ISREALCEX(M, cex) then

5:

return SAT

6:

else

7:

A \leftarrow \text{Refine}(M, A, \text{cex})

8:

else

\triangleright No CEX exists in M.

9:

return UNSAT

10:

```

circuit M (line 1). Next, an abstraction-refinement loop is entered (line 2) where each iteration begins by verifying the current abstraction with model checking (line 3). If an MC solver concludes that there is no CEX for the problem, then an inductive invariant (line 9) has been found. The property is proved, and CEGAR returns UNSAT (line 10). Otherwise, a CEX to the abstraction, *cex*, exists (line 4) and is then checked against the original circuit M to see if it is *real* (line 5). If yes, the property is falsified and CEGAR returns SAT (line 6); otherwise *cex* is analyzed to refine the current abstraction (line 8). A new abstraction is then created and a new iteration begins.

## 1.5 Challenges and Motivations

Many CEGAR-based algorithms for *word-level* MC have been proposed [AS04, JKSC05, BKO<sup>+</sup>07, ALS08, BBSO10, BBS11, LS14]. However, none take full advantage of recent developments at the bit level, whereas PDR has been improved constantly [HBS13, IG15, GR16]. For example, some word-level techniques rely on BMC and k-induction with satisfiability modulo theories (SMT) solvers [AS04, BKO<sup>+</sup>07, ALS08, BSST09, BBSO10, BBS11]. As discussed in Section 1.3, BMC and k-induction require unrolling of a circuit to a certain depth k. This becomes inefficient if deep unrolling is required to derive a unbounded proof. On the other hand, PDR does not require unrolling and has been shown to be more efficient in deriving unbounded proofs [Bra11]. In VCEGAR [JKSC05], abstractions are verified with BDD-based algorithms, which do not scale to large problems due to possible memory explosion. Lee and Sakallah developed a CEGAR-based algorithm based on their SMT-based PDR [LS14]. However this was not shown to be competitive with bit-level PDR algorithms.

Another way of solving word-level MC problems is to bit-blast a circuit and to solve

the resulting bit-level circuit with state-of-the-art bit-level model checkers like ABC [BM10]. However, direct bit-blasting loses word-level information, such as word boundaries and operator semantics that can be useful in solving a problem.

To address those challenges, this dissertation proposes a new CEGAR-based paradigm: performing abstraction refinement at the word level while proving bit-blasted abstractions with state-of-the-art bit-level MC algorithms. This paradigm offers two main benefits:

- 1. It takes full advantage of recent developments in bit-level MC algorithms. In particular, all the recent improvements in bit-level PDR algorithms as well as the winners in the Hardware Model Checking Competition [BvDH17] can be integrated directly under this paradigm.

- 2. It takes advantage of word-level information by performing abstraction and refinement at the word level. This greatly improves the approach of direct bit-blasting without sophisticated use of word-level information.

## **1.6** Contributions

In this dissertation, we propose several techniques that enable efficient abstraction and refinement for word-level MC problems. We focus on the proposed CEGAR-based paradigm of computing abstraction and refinement at the word-level and verifying abstractions at the bit-level.

The success of a CEGAR-based algorithm mainly relies on a) the quality of abstractions created in each iteration, and b) the number of iterations for the CEGAR flow to terminate. The key challenge is to have a good refinement procedure given a spurious CEX. Therefore we propose new word-level refinement strategies that take advantage of both structural and proof-based analysis [HCR<sup>+</sup>16, HMB17]. The proposed strategies achieve a good balance between the sizes of abstractions and the number of iterations, leading to an efficient CEGAR flow compared to previous methods.

With good refinement strategies, the next challenge is to integrate MC algorithms into the CEGAR flow in an efficient way. For example, a straightforward integration of PDR and CE-GAR is to use a fresh PDR engine to verify the current abstraction (line 3 in Algorithm 1.1), which is inefficient because reachability information learned in the current iteration would be lost in the next iteration. Therefore we first propose a bit-level algorithm, PDRA, which enhances PDR with an embedded localization abstraction [HMBE17]. In PDRA, we show that CEGAR can be built into the PDR algorithm with only slight modifications. The result is a PDR engine which is minimally modified to perform on-the-fly abstraction, where reach-

ability information is preserved across iterations. Inspired by this, we propose PDR-WLA, a word-level algorithm that efficiently integrates bit-level PDR with word-level abstraction and refinement [HMB17]. PDR-WLA re-uses reachability information learned in previous iterations explicitly to achieve an efficient integration.

The next challenge was a special class of word-level MC benchmarks, which was provided to us by industry. The benchmarks are characterized by containing hundreds of multipliers and adders where some of those operators may be related. For example, a pair of multipliers may have identical inputs only at certain clock cycles. Moreover, the related multipliers may have different sizes and signedness due to heavy synthesis and optimations done at the Verilog level. Given the above characteristics, simple localization abstraction does not work because localization cannot capture these relationships between multipliers. Therefore we propose UFAR, a word-level CEGAR-based framework, which takes advantage of the theory of uninterpreted functions (UF), by using UF constraints as a method of refinement [HCR<sup>+</sup>16]. A UF constraint, between a pair of multipliers, states that if their inputs are equal then their outputs must be equal. This is shown to be effective for a pair of *related* multipliers. However, a UF constraint is not necessarily valid between two multipliers with different sizes and/or signedness, even if they are related, because the two multipliers may implement different *functions*. Therefore in UFAR, we propose a way to *normalize* multipliers so that a UF constraint is applicable to any pair of multipliers in a design. The UFAR framework integrates all the proposed techniques presented in this thesis, leading to significant improvements in solving such challenging sets of industrial benchmarks.

### 1.7 Organization

This dissertation starts with new proposed refinement strategies in Chapter 2. The algorithm of PDRA, which enhances bit-level PDR with localization abstraction, is presented in Chapter 3. The algorithm of PDR-WLA, which efficiently integrates word-level abstraction with bit-level PDR, is discussed in Chapter 4. The framework of UFAR, which features using uninterpreted function constraints as a way of refinement, is presented in Chapter 5. This dissertation is concluded in Chapter 6.

# Chapter 2

# Refinement Strategies for Word-level Abstraction

This chapter presents novel refinement strategies that take advantage of both structural and proof-based analysis in order to compute good abstraction refinement at the word-level.

# 2.1 Introduction

Localization abstraction  $[WJK^+01]$  has been shown effective in simplifying the original problem for model checkers. Given a word-level circuit and a set of target signals (e.g., outputs of arithmetic operators), an abstraction is created by replacing the target signals with free (unconstrained) variables called *pseudo PIs* (PPIs).

While the abstraction scheme is straightforward, it is challenging to make it efficient in the CEGAR flow, shown in Algorithm 1.1. There are two main factors to be considered: a) the quality of the current abstraction in each iteration and b) the number of iterations taken for CEGAR to conclude the result. If we get an abstraction that is unnecessarily complex (one that is very close to the original circuit), then the model checker could get stuck at proving this instance (line 3 in Algorithm 1.1). Therefore, abstractions should be refined gradually so that complexities are built up over several iterations. However, the refinement should not be too incremental, meaning there should be only slight differences between the refinement and the current abstraction, otherwise it could lead to an unnecessarily large number of iterations for CEGAR to terminate. Thus, it is important to have good refinement strategies that strike a good balance between the two trade-offs (refinement too much vs. too little), leading to an efficient CEGAR-based algorithm. In this chapter, two novel refinement strategies are proposed that are able to solve more of the difficult cases than previous approaches, when evaluated on a set of 195 industrial Verilog benchmarks. The first strategy is called Proof-based Refinement (PBR). We propose a way to encode assumption variables into a circuit so that PBR can take advantage of assumption interfaces, which are available in modern SAT solvers. This provides a good and efficient way of estimating the minimum UNSAT subset (MUS) of assumptions. The second strategy is called the Maximum Fan-out Free Cone (MFFC) refinement. The idea is that using a simple structural analysis of a circuit (MFFC), unnecessary iterations can be avoided by refining additional relevant signals, which improves performances.

This chapter starts with background material in Section 2.2. An important previous approach, Simulation-based Refinement (SBR), is presented in Section 2.3. Our first proposed strategy, PBR, is given in Section 2.4. The refinement strategy of MFFC is presented in Section 2.5. Comparison of different refinement strategies is discussed with examples in Section 2.6. Related work is given in Section 2.7. Experimental results are discussed in Section 2.8. Conclusions are presented in Section 2.9.

## 2.2 Preliminaries

#### 2.2.1 Word-level Localization Abstraction

In localization abstraction  $[WJK^+01]$ , given a word-level circuit and a set of target signals (e.g., outputs of arithmetic operators), an abstraction is created by replacing the target signals with free variables called *pseudo PIs* (PPIs). Localization is not necessarily restricted to flip flops; *any* signal can be abstracted, similar to GLA  $[MEB^+13]$ . In this thesis, *RPIs* are used to denote the *real* PIs in the original circuit and *PPIs* are used for newly created PIs in localization abstraction.

Algorithm 2.1 presents the procedure of creating a localization abstraction  $(W_A)$  from the original circuit  $(W_M)$  and identifies a set of signals to be abstracted  $(\mathcal{B})$ . The procedure uses a signal map (U) that maps a signal in the original circuit  $(W_M)$  to a signal in the abstraction  $(W_A)$  (line 3). The procedure iterates through all the signals in  $W_M$  in a topological order (from [PIs, FOs] to [POs, FIs]) (line 4). For each signal v, if v is in the abstraction set  $(\mathcal{B})$ , then a new PI is created in the new abstraction  $(W_A)$ , and the created PI is mapped to v (line 6). Otherwise, a copy of v is created in  $W_A$ , and the copy is mapped to v (line 8). Then the inputs of U[v] in  $W_A$  are properly attached by iterating the inputs of v in  $W_M$  and using the signal map U (line 10). For example, if a signal v has inputs x and y in the original circuit  $(W_M)$ , then the inputs of its counterpart U[v] in the abstraction  $(W_A)$  need to be attached to the counterparts of x and y, which are U[x] and U[y]. Finally, the procedure

returns the newly created abstraction  $W_A$ .

```

Algorithm 2.1 Word-level Localization Abstraction

```

```

1: procedure CREATEABSTRACTION(W_M, \mathcal{B})

W_A \leftarrow \emptyset

2:

3:

U \leftarrow \emptyset

for v in TOPOLOGICALSORT(W_M) do

4:

if v \in \mathcal{B} then

5:

U[v] \leftarrow \text{CREATEPI}(W_A)

6:

else

7:

U[v] \leftarrow \text{COPYSIGNAL}(W_A, v)

8:

for x in GETINPUTS(v) do

9:

ATTACHINPUT(U[v], U[x])

10:

return W_A

11:

```

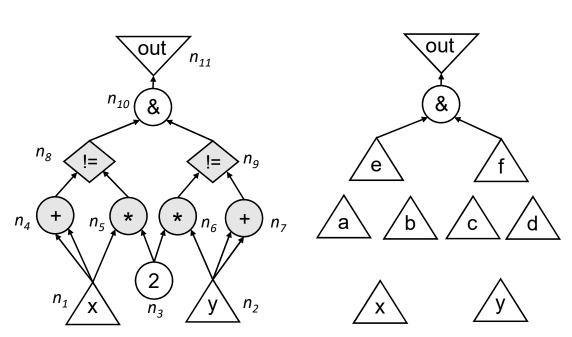

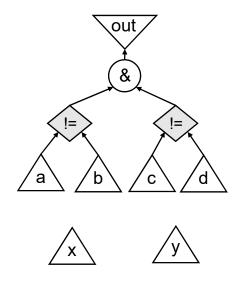

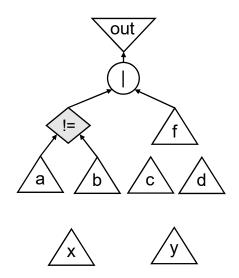

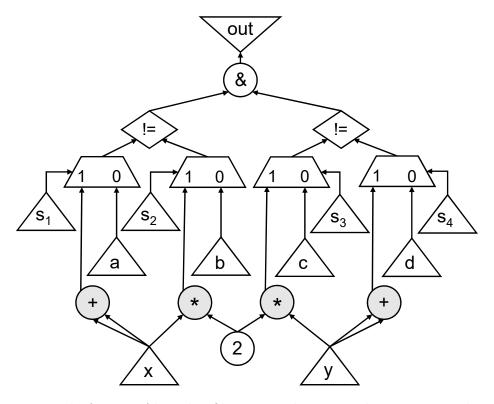

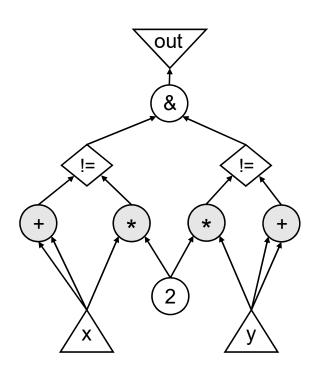

**Example 2.1.** Consider the circuits in Figure 2.1. The PO, *out*, in Figure 2.1a is constant-0, since both  $2 \times x \equiv x + x$  and  $2 \times y \equiv y + y$  are true. Figure 2.1b is the result of abstracting the original circuit with the set of abstraction signals  $\mathcal{B} = \{n_4, n_5, n_6, n_7, n_8, n_9\}$ . The 6 signals are replaced with 6 PPIs  $\{a, b, c, d, e, f\}$ . There are 8 PIs in the abstraction, including RPIs  $= \{x, y\}$  and PPIs  $= \{a, b, c, d, e, f\}$ . Note that while the example is combinational for illustration purposes, the abstraction scheme applies generally to circuits with FFs.

#### 2.2.2 Counterexamples

A counterexample (CEX) of length k is a sequence of concrete assignments of PIs (including RPIs and PPIs) that drive the input model from its initial states into a state falsifying the property. An example of a CEX trace is shown in (2.1), where  $s_j$  denotes the value of the *j*-th state and  $i_j$  denotes the PI assignment at the *j*-th cycle.

$$s_0 \xrightarrow{i_0} s_1 \xrightarrow{i_1} s_2 \xrightarrow{i_2} \dots \xrightarrow{i_{k-1}} s_k$$

(2.1)

A CEX cex can thus be described using PI values.

$$cex = (i_0, i_1, \dots, i_{k-1})$$

(2.2)

The assignment function of a CEX can then be defined below.

**Definition 2.1.** Given a CEX  $cex = (i_0, i_1, \ldots, i_{k-1})$ , the assignment function  $\beta$  maps PIs (i) and a time stamp (t) to a concrete assignment. Formally,

$$\beta(i,t) = i_t. \tag{2.3}$$

(a) The original circuit with four arithmetic operators  $\{n_4, n_5, n_6, n_7\}$ , where x and y are primary inputs, 2 is a constant, != is the complement of a comparator, & is a bit-wise AND, and *out* is the negation of the property.

(b) An abstraction created from the original circuit in (a) and the abstraction set  $\mathcal{B} = \{n_4, n_5, n_6, n_7, n_8, n_9\}$ . The 6 signals in  $\mathcal{B}$  are replaced with 6 pseudo primary inputs (PPI),  $\{a, b, c, d, e, f\}$ .

Figure 2.1: A combinational circuit illustrating word-level abstraction.  $out \equiv 0$ , UNSAT, since  $2 \times x \equiv x + x$ , which forces *out* to be constant 0.

Given a property p and an FSM M, an assignment function  $\beta$  of a length-k CEX to the pair (M, p) would make the formula (2.4) satisfiable (SAT), meaning that there exists a trace from  $s_0$  to  $s_k$  under PI assignments  $i_0$  to  $i_{k-1}$  such that some state  $s_t$  falsifies the property.

$$Init(s_0) \wedge \bigwedge_{t=0}^{k-1} T(i_t, s_t, s_{t+1}) \wedge \bigvee_{t=0}^k \neg p(s_t) \wedge \bigwedge_{t=0}^{k-1} (i_t = \beta(i, t))$$

(2.4)

Given a property p and two FSMs, M and A, where A is an abstraction of M, a *spurious* CEX and its assignment function  $\beta$  satisfy the following properties.

1. The formula below is SAT, meaning that the CEX falsifies the property in the abstraction A.

$$Init_{A}(s_{0}) \wedge \bigwedge_{t=0}^{k-1} T_{A}(i_{t}, s_{t}, s_{t+1}) \wedge \bigvee_{t=0}^{k} \neg p(s_{t}) \wedge \bigwedge_{t=0}^{k-1} (i_{t} = \beta(i, t))$$

(2.5)

2. The formula below is UNSAT, meaning that the CEX cannot falsify the property in the original model M. Note that the domain of  $\beta$  includes both RPIs and PPIs, so the PIs in M (RPIs) are correctly mapped to their corresponding concrete values in the CEX.

$$Init_{M}(s_{0}) \wedge \bigwedge_{t=0}^{k-1} T_{M}(i_{t}, s_{t}, s_{t+1}) \wedge \bigvee_{t=0}^{k} \neg p(s_{t}) \wedge \bigwedge_{t=0}^{k-1} (i_{t} = \beta(i, t))$$

(2.6)

#### 2.2.3 Word-level CEGAR

Algorithm 2.2 shows a word-level extension to Algorithm 1.1 (CEGAR). The algorithm starts by abstracting *all* signals in the set  $\mathcal{S}$  (e.g., outputs of all specified arithmetic operators). Next, an abstraction-refinement loop is entered where each iteration begins by creating a word-level abstraction based on the current set  $\mathcal{B}$ , the set of signals to be abstracted away. Procedure CREATEABSTRACTION is presented in Algorithm 2.1. The abstraction is then bit-blasted and solved by a bit-level MC solver (e.g., PDR). If the solver returns UNSAT, the property is proved. Otherwise a CEX to the abstraction, *cex*, exists and is then *simulated* on the original circuit ( $W_M$ ) to check if it is *real*. If yes, the property is falsified and *cex* is returned; otherwise *cex* is analyzed to derive a set of signals ( $\Delta \mathcal{B}$ ) that, if un-abstracted, can block *cex*. A new abstraction, with the set  $\Delta \mathcal{B}$  un-abstracted, is then created and a new iteration begins.

| Algorithm 2.2 Word                                 | lovol CECAB                                        |                                                                    |  |  |  |

|----------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|--|--|--|

|                                                    | TT7 1 11 1                                         |                                                                    |  |  |  |

| Input: $W_M$                                       |                                                    | $\triangleright W_M$ : the word-level input circuit                |  |  |  |

| Input: $\mathcal{S}$                               |                                                    | $\triangleright \mathcal{S}$ : the initial set of targeted signals |  |  |  |

| <b>Output:</b> status $\in$ { S                    | AT, UNSAT }                                        |                                                                    |  |  |  |

| 1: Iterations $\leftarrow 1$                       |                                                    |                                                                    |  |  |  |

| 2: $\mathcal{B} \leftarrow \mathcal{S}$            |                                                    | $\triangleright \mathcal{B}$ : the set of abstracted signals       |  |  |  |

| 3: while true do                                   |                                                    |                                                                    |  |  |  |

| 4: $W_A \leftarrow \text{CREATI}$                  | EABSTRACTION $(W_M, \mathcal{B})$                  |                                                                    |  |  |  |

| 5: $G_A \leftarrow \text{BitBla}$                  | $\operatorname{ST}(W_A)$                           |                                                                    |  |  |  |

| 6: $cex \leftarrow Model$                          | CHECKING $(G_A)$                                   |                                                                    |  |  |  |

| 7: <b>if</b> $cex \neq \emptyset$ <b>the</b>       | n                                                  |                                                                    |  |  |  |

| 8: <b>if</b> IsrealC                               | $\operatorname{CEX}(W_M, \operatorname{cex})$ then |                                                                    |  |  |  |

| 9: return                                          | SAT                                                |                                                                    |  |  |  |

| 10: else                                           |                                                    |                                                                    |  |  |  |

| 11: $\Delta \mathcal{B} \leftarrow \mathbf{I}$     | REFINE $(W_M, G_A, \mathcal{B}, \text{cex})$       |                                                                    |  |  |  |

| 12: $\mathcal{B} \leftarrow \mathcal{B} \setminus$ | $\Delta \mathcal{B}$                               |                                                                    |  |  |  |

| 13: Iteratio                                       | $ns \leftarrow Iterations + 1$                     |                                                                    |  |  |  |

| 14: <b>else</b>                                    |                                                    |                                                                    |  |  |  |

| 15: return UN                                      | SAT                                                |                                                                    |  |  |  |

#### 2.2.4 The Refinement Problem

Given a spurious CEX, *cex*, the goal of refinement is to identify a subset of signals  $\Delta \mathcal{B}$  in the current set of abstraction signals  $\mathcal{B}$ , such that if  $\Delta \mathcal{B}$  is removed from  $\mathcal{B}$ , then *cex* is *blocked* in the next iteration. We say that  $\Delta \mathcal{B}$  is *un-abstracted*. This procedure corresponds to lines 11 and 12 in Algorithm 2.2.

A spurious CEX with assignment function  $\beta$  is said to be *blocked* in the refined abstraction N if the formula below is UNSAT, meaning that the same CEX cannot falsify the property in N. In practice, the formula can be checked without SAT solving by simulating the CEX in N and checking that the output  $\neg p$  is constant-0 for the first k cycles.

$$Init_{N}(s_{0}) \wedge \bigwedge_{t=0}^{k-1} T_{N}(i_{t}, s_{t}, s_{t+1}) \wedge \bigvee_{t=0}^{k} \neg p(s_{t}) \wedge \bigwedge_{t=0}^{k-1} (i_{t} = \beta(i, t))$$

(2.7)

**Example 2.2.** Consider the abstraction circuit shown in Figure 2.1b. Suppose the spurious CEX to this abstraction is found with PI assignments

$$(x, y, a, b, c, d, e, f) = (0, 0, 0, 0, 0, 0, 1, 1)$$

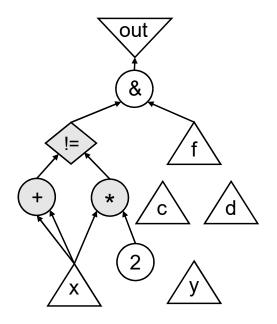

Suppose after some CEX analysis, a refined abstraction is created with PPIs =  $\{a, b, e\}$  being un-abstracted, as shown in Figure 2.2. The spurious CEX is blocked in the refined circuit

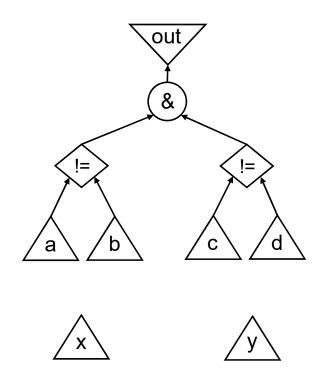

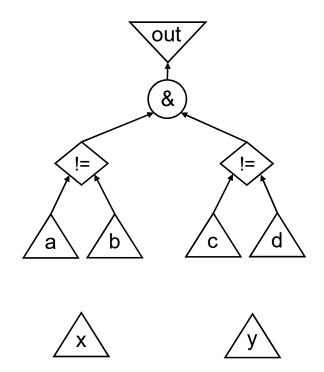

Figure 2.2: An example of refining the circuit in Figure 2.1b with  $\Delta \mathcal{B} = \{n_4, n_5, n_8\}$ , a subset of the set of the current abstraction signals  $\mathcal{B} = \{n_4, n_5, n_6, n_7, n_8, n_9\}$ . The refined circuit is created from the original circuit using the updated set  $\mathcal{B} \setminus \Delta \mathcal{B} = \{n_6, n_7, n_9\}$ , corresponding to PPIs =  $\{c, d, f\}$ .

because if we simulate the PI assignments below in the refined abstraction, the PO (out) value would be constant-0.

$$(x, y, c, d, f) = (0, 0, 0, 0, 1)$$

#### 2.2.5 Ternary Simulation and X-value Counterexamples (XCEX)

A CEX can be minimized or generalized in the sense that some PIs can be assigned X values (unknown logic values), but the resulting X-value CEX (XCEX) can still falsify the property using ternary simulation.

In ternary simulation, Boolean logic with binary values  $\{0, 1\}$  is extended to ternary logic with three values  $\{0, 1, X\}$ . The semantics of basic logic gates like AND ( $\land$ ) and NOT ( $\neg$ ) are given below.

|   | $\wedge P$   |   | A |   |  | Λ        | - 1           |

|---|--------------|---|---|---|--|----------|---------------|

|   | $A \wedge B$ | 0 | 1 | X |  | $\neg A$ |               |

|   | 0            | 0 | 0 | 0 |  | 1        | 1             |

| B | 1            | 0 | 1 | X |  |          | $\frac{0}{V}$ |

|   | X            | 0 | X | X |  | Λ        | Λ             |

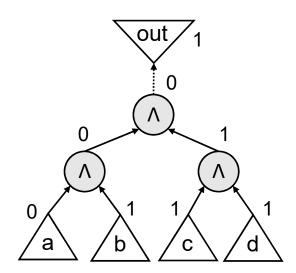

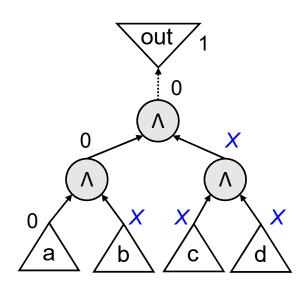

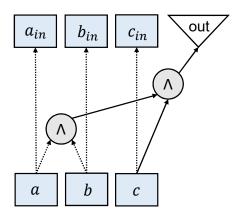

(a) The original CEX with concrete-value PI assignments (a, b, c, d) = (0, 1, 1, 1). The values of each gate derived using simulation are shown.

(b) An XCEX derived from the CEX in (a). PI assignments now contain X values with (a, b, c, d) = (0, X, X, X). The values of each gate derived using ternary simulation are shown. The XCEX still falsifies the property (making out = 1).

Figure 2.3: An example showing a CEX can be minimized or generalized into an X-value CEX (XCEX). Symbol  $\land$  denotes logic AND; dashed arrows represent logic NOT.

An XCEX is a generalized representation of a CEX because it represents a set of CEXes that can falsify the property. In later discussions, one of the refinement strategies is based on the idea of blocking a XCEX instead of a CEX, avoiding unnecessary CEGAR iterations.

**Example 2.3.** Figure 2.3 shows an example of how a CEX can be minimized into an XCEX. The original CEX has concrete values for the PIs (a, b, c, d) = (0, 1, 1, 1). Three of the PIs  $\{b, c, d\}$  can be assigned X values and the resulting XCEX (a, b, c, d) = (0, X, X, X) still falsifies the property using ternary simulation. The XCEX now represents a set of 8 CEXes, including the original CEX:

$\{(0, 0, 0, 0), (0, 0, 0, 1), (0, 0, 1, 0), (0, 0, 1, 1), (0, 1, 0, 0), (0, 1, 0, 1), (0, 1, 1, 0), (0, 1, 1, 1)\}.$

#### 2.2.6 Assumption Interfaces in SAT Solvers

Modern SAT solvers have assumption interfaces pioneered by Eén and Sörensson [ES03a, ES03b]. The interface is available through the following method.

$$SolveSAT(assumptions)$$

(2.8)

The assumptions are a set of unit clauses added to a SAT solver, which can be denoted as  $assumptions = a_0 \wedge a_1 \wedge \ldots \wedge a_{n-1}$ . The method (2.8) returns SAT if the SAT solver finds a satisfying assignment to the original problem under the given assumptions. Otherwise, the problem is UNSAT if the assumptions are given. The SAT solver would also return a subset of the assumptions  $\{a_0, a_1, \ldots, a_{n-1}\}$  that is sufficient to make the problem UNSAT. This capability of SAT solvers has been shown useful and effective in MC algorithms like abstraction and PDR [EMA10, EMB11], since it provides a cheap and efficient way of estimating the minimum UNSAT subset (MUS) of the given assumptions.

**Example 2.4.** Consider the SAT instance below.

$$P = (a \lor c) \land (\neg b \lor c) \land (\neg a \lor b \lor c)$$

$$(2.9)$$

If we call **SolveSAT** $(a \land \neg b \land \neg c)$ , the SAT solver would return UNSAT since

$$a \wedge \neg b \wedge \neg c \wedge P \tag{2.10}$$

is UNSAT. A possible subset of assumptions  $\{a, \neg b, \neg c\}$  that is sufficient for the UNSAT result is  $\{\neg c\}$ , since

$$\neg c \land P \tag{2.11}$$

is UNSAT. This means that we only need to assume  $\neg c$  to make Query (2.9) UNSAT.

### 2.3 Simulation-based Refinement (SBR)

A simple refinement strategy is to simulate the given sprious CEX cex on the original circuit  $(W_M)$  and compare the PPI values (in cex) with their counterparts in  $W_M$ . If the values of a signal s do not match, then s is a refinement *candidate*, i.e. a candidate for un-abstraction. If *all* such candidates are un-abstracted, the property must hold; thus *cex* is blocked. However, this approach often results in too many candidates being un-abstracted, and thus is not a good strategy.

**Example 2.5.** Consider the circuits shown in Figure 2.1. Suppose a spurious CEX to the abstraction (Fig. 2.1b) is given below.

$$(x, y, a, b, c, d, e, f) = (0, 0, 1, 2, 1, 2, 1, 1)$$

(Recall that 2 here is the constant 2). If the CEX is simulated on the original circuit (Fig. 2.1a), then the values of the counterparts of PPIs are

$$(n_4, n_5, n_6, n_7, n_8, n_9) = (0, 0, 0, 0, 0, 0).$$

In this case, all the values of PPIs do not match with their counterparts, so all PPIs are refinement candidates. Un-abstracting all PPIs  $\{a, b, c, d, e, f\}$  results in a refinement that can block the CEX, but it refines more PPIs than necessary. As we shall see later, an optimal refinement is to un-abstract PPIs  $\{a, b, e\}$ .

A more advanced way is to use a X-value CEX, discussed in Section 2.2.5 where some PIs are assigned to X (unknown logic value), while the XCEX still falsifies the property using ternary simulation.

An XCEX can be derived from a CEX in two ways:

- 1. For each PI value in the CEX, replace it with X, and then use ternary simulation to check if the resulting XCEX still falsifies the property. If so, then keep X for that PI. Otherwise, keep its original concrete value.

- 2. A more efficient way is to use *Priority-based Refinement* proposed by Mishchenko et al. [MEB<sup>+</sup>13]. The procedure traverses a circuit twice. The first traversal is from PIs to POs, assigning a priority for each node in a topological order. The second traversal goes from POs to PIs in a reverse topological order. Nodes traversed are based on their priorities and CEX values. Finally, a *justifying subset* (JS) of PPIs is returned. PPIs in the JS are the only PPIs that need to keep their concrete values. Other PPIs can be assigned X.

The concrete-value PPIs are also called *care-set* PPIs, since if their values are restricted to ones given in the CEX while other PPIs are assigned X, the property would still fail using ternary simulation. This provides a set of good candidates for refinement. If *all* PPIs in the care set are un-abstracted, then *cex* is very likely to be blocked. The refinement strategy of using *Priority-based Refinement* to identify a care set of PPIs to un-abstract, is called Simulation-based Refinement (SBR), because the resulting XCEX needs to falsify the property using ternary simulation.

SBR has the benefit of refining a more focused subset of PPIs than the one used in Example 2.5.

**Example 2.6.** Consider the same CEX and circuits shown in Example 2.5. The XCEX returned by Priority-based Refinement is

$$(x, y, a, b, c, d, e, f) = (X, X, X, X, X, X, 1, 1).$$

Therefore, the PPIs to un-abstract using SBR would be the care-set PPIs,  $\{e, f\}$ , instead of all PPIs as described in Example 2.5.

However, there are limitations in SBR. It is possible that each care-set PPI is fed by a tree, without overlaps with the trees of other care-set PPIs. Then, even if all the care-set

Figure 2.4: An example of refining the circuit in Figure 2.1b with  $\Delta \mathcal{B} = \{n_8, n_9\}$  (PPIs  $\{e, f\}$ ).

PPIs are un-abstracted, this will not provide enough constraints, and therefore the CEX is not blocked.

**Example 2.7.** Continuing Example 2.6, the refined circuit is shown in Figure 2.4. PPIs e and f are fed by trees that do not overlap. Their immediate inputs (a, b) and (c, d) are still PPIs, so the outputs of the refined e and f are still unconstrained. The CEX in Example 2.5 is not blocked in this refined circuit.

$$(x, y, a, b, c, d) = (0, 0, 1, 2, 1, 2)$$

**Example 2.8.** Consider the circuits shown in Figure 2.5. Suppose a spurious CEX to the abstraction (Fig. 2.5b) is given below.

$$(x, y, a, b, c, d, e, f) = (0, 0, 1, 2, 1, 2, 1, 1).$$

A minimized XCEX can be

$$(x, y, a, b, c, d, e, f) = (X, X, X, X, X, X, 1, X).$$

The only care-set signal is PPI e = 1, since it is sufficient to make out = 1 using ternary simulation. In this case, SBR un-abstracts PPI e and the refined abstraction is shown in Figure 2.6. Unfortunately, the same CEX is not blocked in this refinement, since the same PI assignments still falsify the property (f = 1 makes out = 1).

$$(x, y, a, b, c, d, f) = (0, 0, 1, 2, 1, 2, 1).$$

This shows another limitation of SBR.

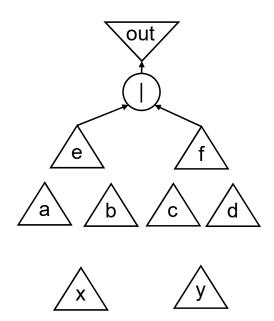

(a) The original circuit with four arithmetic operators  $\{n_4, n_5, n_6, n_7\}$ , where x and y are PIs, 2 is a constant, != is the complement of a comparator, | is a bit-wise OR, and *out* is the negation of the property.

(b) An abstraction created from the original circuit in (a) and the abstraction set  $\mathcal{B} = \{n_4, n_5, n_6, n_7, n_8, n_9\}$ . The 6 signals in  $\mathcal{B}$  are replaced with 6 pseudo primary inputs (PPI),  $\{a, b, c, d, e, f\}$ .