## UC San Diego UC San Diego Electronic Theses and Dissertations

### Title

Reshaping Deep Neural Networks for Efficient Hardware Inference

### Permalink

https://escholarship.org/uc/item/6m01b8sm

### **Author** Khodamoradi, Alireza

## Publication Date 2021

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SAN DIEGO

Reshaping Deep Neural Networks for Efficient Hardware Inference

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

### Computer Science (Computer Engineering)

by

### Alireza Khodamoradi

Committee in charge:

Professor Ryan C. Kastner, Chair Professor Gert Cauwenberghs Professor Sicun Gao Professor Steven Swanson Professor Jishen Zhao

Copyright Alireza Khodamoradi, 2021

All rights reserved.

The Dissertation of Alireza Khodamoradi is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2021

### DEDICATION

For my mother, Azar.

EPIGRAPH

Entities are not to be multiplied beyond necessity.

William of Ockham

| Dissertation Approval Page                                                                                                                                                                                                                                                                                                                                           | iii                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Dedication                                                                                                                                                                                                                                                                                                                                                           | iv                                                                 |

| Epigraph                                                                                                                                                                                                                                                                                                                                                             | v                                                                  |

| Table of Contents                                                                                                                                                                                                                                                                                                                                                    | vi                                                                 |

| List of Figures                                                                                                                                                                                                                                                                                                                                                      | viii                                                               |

| List of Tables                                                                                                                                                                                                                                                                                                                                                       | X                                                                  |

| Acknowledgements                                                                                                                                                                                                                                                                                                                                                     | xi                                                                 |

| Vita                                                                                                                                                                                                                                                                                                                                                                 | xii                                                                |

| Abstract of the Dissertation                                                                                                                                                                                                                                                                                                                                         | xiii                                                               |

| Chapter 1Introduction1.1Reshaping Spiking Neural Networks1.2Filtering Noise in Neuromorphic Vision Data1.3Reshaping Residual Neural Networks1.4Auto Tuning the Learning Rate                                                                                                                                                                                         | 1<br>3<br>4<br>5                                                   |

| Chapter 2Reshaping Spiking Neural Networks2.1Spiking Neural Network2.1.1LIF Model2.1.2Propagation Delays in Neuron2.1.3Custom SNN Implementations2.2Streaming Spiking Neural Networks (S2N2)2.2.1Input Buffer - Memory Utilization2.2.2Fixed-Per-Layer Propagation Delays2.3S2N2 for Automatic Modulation Classification2.4Image Classification on S2N22.5Conclusion | 6<br>8<br>10<br>12<br>12<br>14<br>14<br>15<br>17<br>22<br>31<br>34 |

| Chapter 3       Filtering Noise in SNN Input         3.1       Related Work         3.2       Proposed Spatiotemporal Filter         3.3       Noise Model         3.4       Filters' Error Analysis         3.4.1       Baseline BA Filter         3.4.2       Liu's BA Filter                                                                                      | 37<br>41<br>42<br>44<br>47<br>47<br>48                             |

### TABLE OF CONTENTS

| 3.5      |         | Normal Sub-Sampling Filter<br>Our Proposed Filter<br>Theoretical Comparison<br>Comparison Between Filters using Real Data<br>are Implementation | 50<br>50<br>52<br>53<br>54 |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3.6      | Conciu  | ision                                                                                                                                           | 56                         |

| Chapter  | 4 R     | eshaping Residual Neural Networks                                                                                                               | 59                         |

| 4.1      | Backgr  | ound                                                                                                                                            | 62                         |

|          | 4.1.1   | Importance of Skip Connections                                                                                                                  | 62                         |

|          | 4.1.2   | Accelerating ResNet Inference on Custom Platforms                                                                                               | 62                         |

|          | 4.1.3   | Removing Skip Connections                                                                                                                       | 64                         |

| 4.2      | SKIPT   | RIM                                                                                                                                             | 65                         |

|          | 4.2.1   | Skipper                                                                                                                                         | 65                         |

|          | 4.2.2   | Trimmer                                                                                                                                         | 67                         |

| 4.3      | Experi  | ments                                                                                                                                           | 69                         |

|          | 4.3.1   | Training Results                                                                                                                                | 70                         |

|          | 4.3.2   | Optimizing Short Skip Connections on FPGAs                                                                                                      | 71                         |

|          | 4.3.3   | Quantization                                                                                                                                    | 73                         |

| 4.4      |         | tions and Future Work                                                                                                                           | 74                         |

| 4.5      | Conclu  | sion                                                                                                                                            | 74                         |

| Chapter  | 5 A     | uto Tuning the Learning Rate                                                                                                                    | 77                         |

| 5.1      |         | exity of Learning Rate Tuning                                                                                                                   | 79                         |

| 5.2      |         | on Practices for Learning Rate Tuning                                                                                                           | 81                         |

|          | 5.2.1   | Second Order Information                                                                                                                        | 81                         |

|          | 5.2.2   | Adaptive Optimization Methods                                                                                                                   | 83                         |

|          | 5.2.3   | Schedulers                                                                                                                                      | 85                         |

|          | 5.2.4   | Methods with Line Search                                                                                                                        | 85                         |

| 5.3      | ASLR    |                                                                                                                                                 | 87                         |

| 5.4      | Results | 3                                                                                                                                               | 92                         |

| 5.5      | Conclu  | sions                                                                                                                                           | 97                         |

| Bibliogr | aphy    |                                                                                                                                                 | 100                        |

### LIST OF FIGURES

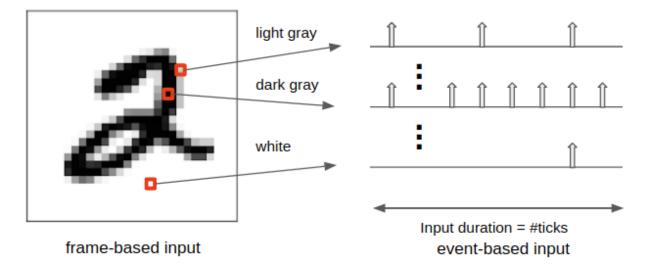

| Figure 2.1.  | Comparing frame-based and event-based inputs.                             | 10 |

|--------------|---------------------------------------------------------------------------|----|

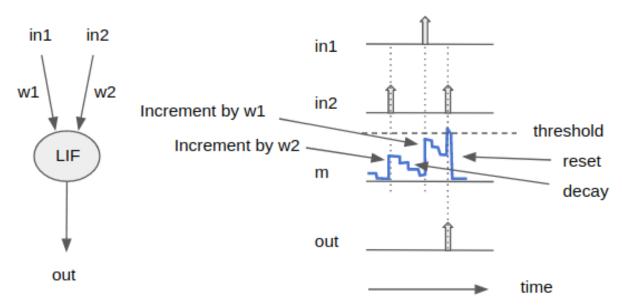

| Figure 2.2.  | LIF neuron with two inputs.                                               | 11 |

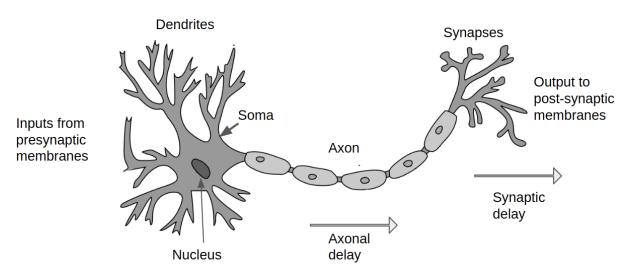

| Figure 2.3.  | Illustration of a biological neuron                                       | 12 |

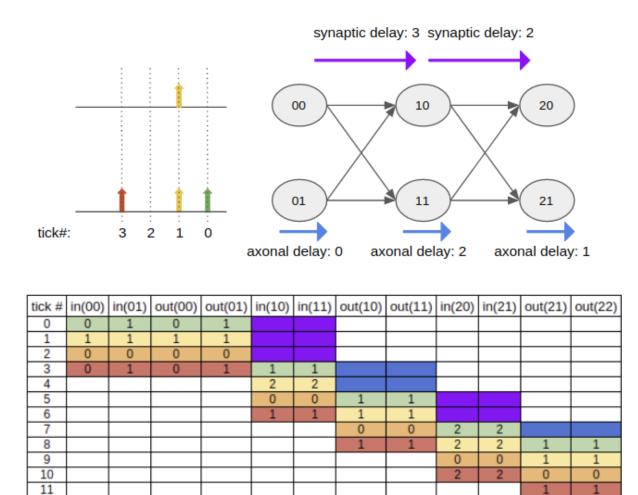

| Figure 2.4.  | A simple 3-layer network with fixed-per-layer axonal and synaptic delays. | 16 |

| Figure 2.5.  | Fixed-per-layer propagation delays                                        | 17 |

| Figure 2.6.  | FINN architecture                                                         | 19 |

| Figure 2.7.  | PE implementation in FINN and S2N2.                                       | 20 |

| Figure 2.8.  | Binary tensor for addressing spikes in an event-based input               | 22 |

| Figure 2.9.  | Examples of AM-DSB class from RadioML dataset.                            | 24 |

| Figure 2.10. | Applying quantization to the I/Q plane                                    | 25 |

| Figure 2.11. | S2N2_rf1 architecture                                                     | 26 |

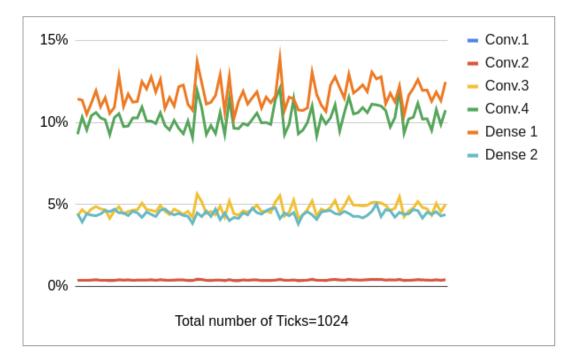

| Figure 2.12. | The ratio of spiking neurons in input to each layer of S2N2_rf1           | 27 |

| Figure 2.13. | S2N2_rf2 architecture                                                     | 28 |

| Figure 2.14. | The ratio of spiking neurons in input to each layer of S2N2_rf2           | 29 |

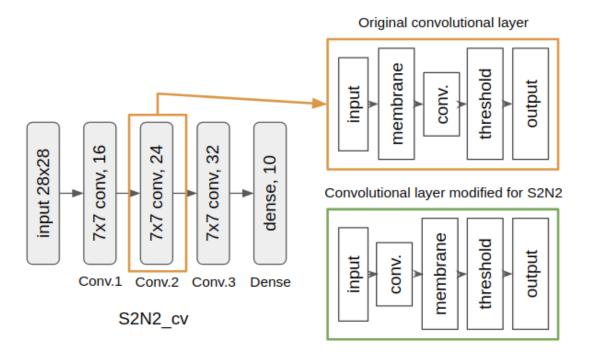

| Figure 2.15. | S2N2_cv structure                                                         | 32 |

| Figure 2.16. | The ratio of spiking neurons in input to each layer of S2N2_cv            | 33 |

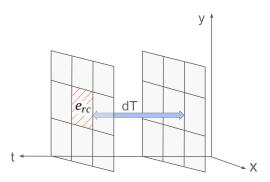

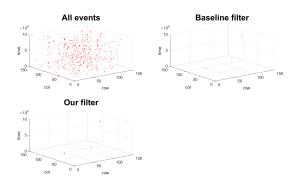

| Figure 3.1.  | Principal of spatiotemporal correlation filter.                           | 40 |

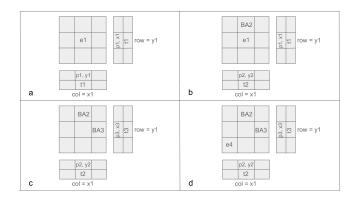

| Figure 3.2.  | Sub-sampling groups.                                                      | 42 |

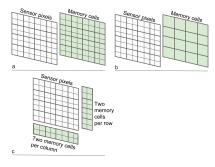

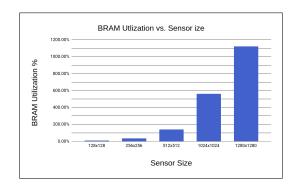

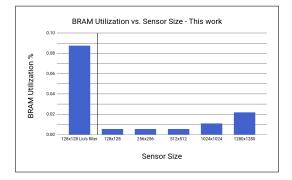

| Figure 3.3.  | Memory utilization for different spatiotemporal filter designs            | 43 |

| Figure 3.4.  | Memory utilization.                                                       | 43 |

| Figure 3.5.  | Experiment setup                                                          | 45 |

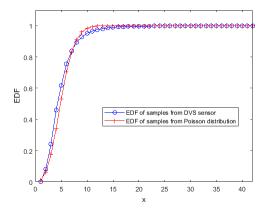

| Figure 3.6.  | Kolmogorov-Smirnov test results.                                          | 47 |

| Figure 3.7.  | Three pixel groups for a $S \times S$ sub-sampling group                  | 48 |

| Figure 3.8.  | Example of <i>false negative</i> error in our proposed filter                                                 | 52 |

|--------------|---------------------------------------------------------------------------------------------------------------|----|

| Figure 3.9.  | False positive error.                                                                                         | 52 |

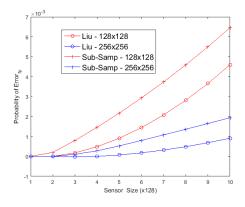

| Figure 3.10. | False negative error.                                                                                         | 53 |

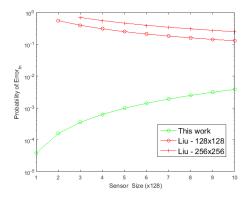

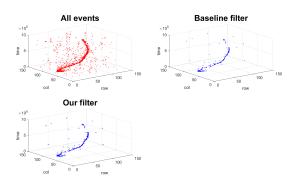

| Figure 3.11. | Comparison between our filter and baseline filter.                                                            | 54 |

| Figure 3.12. | Past event false negative noise                                                                               | 54 |

| Figure 3.13. | Memory utilization for baseline filter.                                                                       | 56 |

| Figure 3.14. | Memory utilization for proposed filter.                                                                       | 56 |

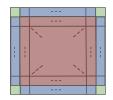

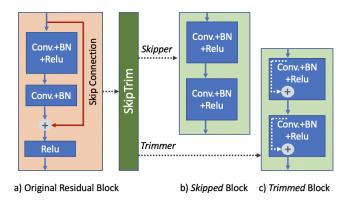

| Figure 4.1.  | SKIPTRIM overview                                                                                             | 60 |

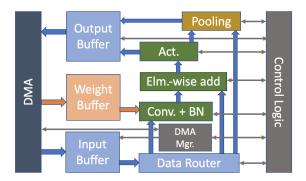

| Figure 4.2.  | Deep Learning Accelerator.                                                                                    | 63 |

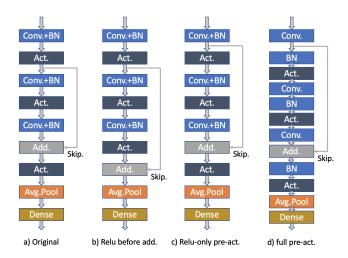

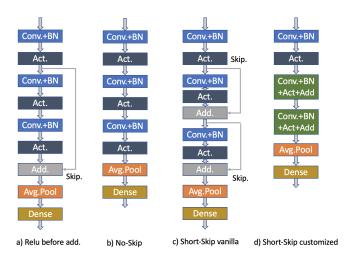

| Figure 4.3.  | Residual blocks                                                                                               | 68 |

| Figure 4.4.  | layers generated by hls4ml.                                                                                   | 72 |

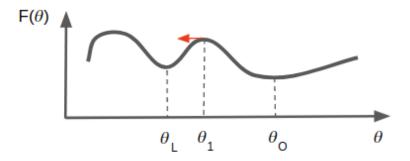

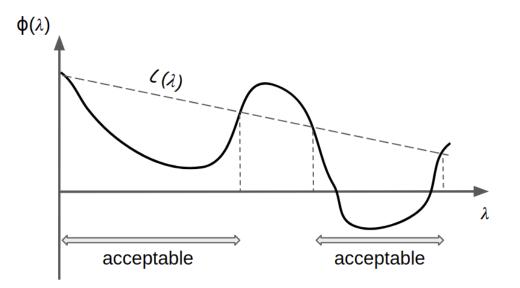

| Figure 5.1.  | A sketch of a loss surface with only one parameter                                                            | 80 |

| Figure 5.2.  | Armijo condition                                                                                              | 86 |

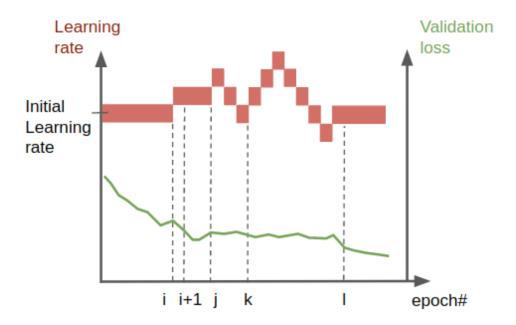

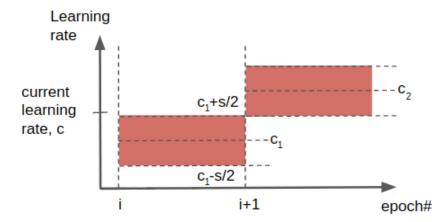

| Figure 5.3.  | Adjusting learning rate                                                                                       | 90 |

| Figure 5.4.  | Drawing learning rates from a uniform distribution                                                            | 91 |

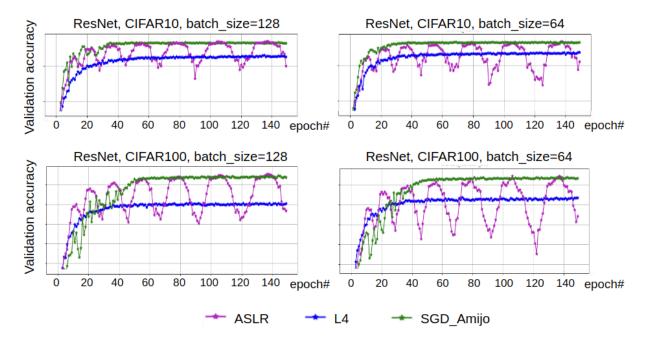

| Figure 5.5.  | Comparison between the validation accuracy evolution curve for ASLR and line search methods: L4 and SGD_Amijo | 94 |

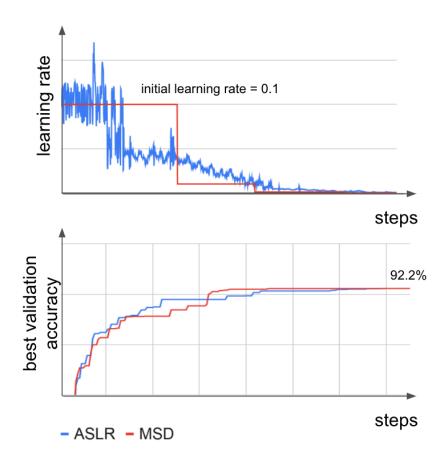

| Figure 5.6.  | Comparison between ASLR and multi-step-decay on ResNet20                                                      | 97 |

### LIST OF TABLES

| Table 2.1. | A comparison between S2N2 and previous works.                              | 14 |

|------------|----------------------------------------------------------------------------|----|

| Table 2.2. | Comparing validation accuracy and network size for S2N2_rf1                | 26 |

| Table 2.3. | Required memory for buffering input at each layer of S2N2_rf1              | 28 |

| Table 2.4. | Comparing validation accuracy and network size for S2N2_rf2                | 29 |

| Table 2.5. | Required memory for buffering input at each layer of S2N2_rf2              | 30 |

| Table 2.6. | Synthesis results for S2N2_rf1 and S2N2_rf2 network architectures          | 31 |

| Table 2.7. | Accuracy result of S2N2_cv on MNIST compared to similar SNNs               | 33 |

| Table 2.8. | Required memory for buffering input at each layer of S2N2_cv               | 34 |

| Table 2.9. | Synthesis results for S2N2_cv network architecture                         | 34 |

| Table 3.1. | Comparison between resource utilization                                    | 55 |

| Table 4.1. | CIFAR10 Top1 accuracy results on different ResNet configurations           | 70 |

| Table 4.2. | CIFAR100 Top1 accuracy results on different ResNet configurations          | 70 |

| Table 4.3. | SVHN Top1 accuracy results on different ResNet configurations              | 71 |

| Table 4.4. | RadioML.2018 top1 accuracy results on different ResBlock configurations    | 71 |

| Table 4.5. | Hardware utilization for networks in Figure 4.4                            | 71 |

| Table 4.6. | Synthesis results for fixed point precision designs on CIFAR10             | 73 |

| Table 5.1. | Comparing validation accuracy of ASLR with Line Search Methods on ResNet34 | 93 |

| Table 5.2. | Comparing average training time per epoch.                                 | 94 |

| Table 5.3. | Comparing validation accuracy of ASLR with schedulers on CIFAR10           | 95 |

| Table 5.4. | Comparing validation accuracy of ASLR with schedulers on ImageNet          | 96 |

#### ACKNOWLEDGEMENTS

I would like to acknowledge Professor Ryan Kastner for his support as the chair of my committee. I would also like to acknowledge Kristof Denolf, without whom my research would have no doubt taken longer.

Chapter 2, in full, is a reprint of the material as it appears in ACM/SIGDA International Symposium on Field-Programmable Gate Arrays 2021. Alireza Khodamoradi, Kristof Denolf, and Ryan Kastner. The dissertation author was the primary investigator and author of this paper.

Chapter 3, in full, is a reprint of the material as it appears in IEEE Transactions on Emerging Topics in Computing 2017. Alireza Khodamoradi and Ryan Kastner. The dissertation author was the primary investigator and author of this paper.

Chapter 4, in part is currently being prepared for submission for publication of the material. Alireza Khodamoradi, Olivia Weng, Nojan Sheybani, Kristof Denolf, Farinaz Koushanfar, and Ryan Kastner. The dissertation author was the primary investigator and author of this material.

Chapter 5, in full, is a reprint of the material as it appears in the International Joint Conference on Neural Networks 2021. Alireza Khodamoradi, Kristof Denolf, Kees Vissers, and Ryan Kastner. The dissertation author was the primary investigator and author of this paper.

#### VITA

- 2002 B.S. in Electrical Engineering, Azad University of Najafabad, Iran

- 2008 M.S. in Electrical Engineering, University of Kerman, Iran

- 2015 M.A.S in Wireless Embedded Systems, University of California San Diego

- 2021 Ph.D. in Computer Science (Computer Engineering), University of California San Diego

### PUBLICATIONS

Alireza Khodamoradi, Kristof Denolf, Ryan Kastner, "S2N2: A FPGA Accelerator for Streaming Spiking Neural Networks", *FPGA* 2021

Stephen Neuendorffer, Alireza Khodamoradi, Kristof Denolf, Abishek K. Jain, Samuel Bayliss, "The Evolution of Domain-Specific Computing for Deep Learning", *IEEE Circuits and Systems* 2021

Alireza Khodamoradi, Kristof Denolf, Ryan Kastner, Kees Vissers, "ASLR: an Adaptive Scheduler for Learning Rate", *IJCNN* 2021

Stephen Tridgell, David Boland, Philip H.W. Leong, Alireza Khodamoradi, Ryan Kastner, Siddhartha, "Real-time Automatic Modulation Classification using RFSoC", *RAW* 2020

Murad Qasaimeh, Kristof Denolf, Alireza Khodamoradi, Lisa Halder, Michaela Blott, Jack Lo, Kees Vissers, Joseph Zambreno, Phillip H.Jone, "Benchmarking Vision Kernels and Neural Network Inference Accelerators on Embedded Platforms", *JSA* 2019

Alireza Khodamoradi, Ryan Kastner, "O(N)-Space Spatiotemporal Filters for Reducing Noise in Neuromorphic Vision Sensors", *IEEE Transactions on Emerging Topics in Computing (TETC)*, 2017

Andrew Lanez, Sachin B. Sundramurthy, Alireza Khodamoradi, "RFNoC & Vivado HLS Challenge - Team Rabbit Ears: ATSC Receiver", *Proceedings of the 7th GNU Radio Conference* (*GRCon*), 2017

Alican Nalci, Alireza Khodamoradi, Ozgur Balkan, Fatta Nahab, Harinath Garudadri, "A computer vision based candidate for functional balance test", *Engineering in Medicine and Biology Society (EMBC)*, 2015

### ABSTRACT OF THE DISSERTATION

Reshaping Deep Neural Networks for Efficient Hardware Inference

by

Alireza Khodamoradi

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California San Diego, 2021

Professor Ryan C. Kastner, Chair

The latest Deep Learning (DL) methods for designing Deep Neural Networks (DNN) have significantly expanded our ability to train data processing systems. Coupled with exponential growth in available digital data, we have seen dramatic accuracy improvements in DNNs and widespread adoption of these models in different applications.

This increased demand has motivated innovations in DNN architecture design to deliver high-quality output. For example, advanced DL models can include irregular connections between their layers, have more parameters, and employ computationally complex neurons. Unfortunately, these new architectural additions often increase the implementation complexity of the DNNs on hardware, particularly when deploying DL models for inference in scale-out and power-limited systems.

Currently, to deploy a DNN on a custom platform, an abstract of the DL model is used to create a functionally identical realization. However, because altering this abstract changes the functionality of the DL model, hardware designers keep the model unchanged for a lossless implementation.

This thesis shows that a co-design approach can improve the hardware implementation of DL models. In a co-design approach, the designer reshapes the DNN architecture to better fit a target processing platform and preserves its accuracy by retraining the model.

We describe a custom accelerator for Spiking Neural Networks (SNN) with improved computational cost and memory utilization because of reshaping the layers and neurons of the model. We then apply these changes to the existing SNN models and show that they can maintain their accuracy after the reshaping and retraining. In addition, we introduce novel applications for SNNs based on the new architecture. We also present a stochastic noise filter for pre-processing SSN's input with improved accuracy and memory utilization. Furthermore, we explain a reshaping method for Residual Networks (ResNet) to reduce their memory footprint while preserving their accuracy.

This thesis also introduces a method for accelerating the co-design process. Reshaping DL models can increase the complexity of their training stage. We present an auto tuner for the learning rate (an essential parameter for training DNNs) that simplifies the manual tuning for this parameter and can accelerate the retraining of DL models.

## Chapter 1 Introduction

Deep Learning (DL) models are a subset of Artificial Neural Networks (ANN). These data processing systems learn how to process their inputs to produce desirable outputs similar to biological neural networks (e.g., mammal's brain). Recent advancements in DL methods have shown significant improvements in training these models and have revealed their capabilities in producing high-quality products in different industries, including self-driving cars, language translation, healthcare, virtual assistants, and many others.

Generally, a DNN includes several layers, and each layer extracts different levels of features from the input. For example, in a model designed for image classification, earlier layers extract edges or corners, and later layers pull the number of objects in the image or determine if the input is an image of a dog or a duck.

Usually, each layer passes its output forward to the next layer. However, neural networks can also include irregular connections to allow their layers to pass their output to non-adjacent layers. These irregular connections are essential for training specific models and applications. For example, in Residual Networks (ResNet) [38], skip connections increase the network accuracy and make it possible to train deeper models with more layers, or in UNets [93], crop-and-copy connections are vital for high-quality image segmentation.

In a DL model, a layer is a collection of neurons. Each neuron has input connections from presynaptic neurons and output connections to postsynaptic neurons. Furthermore, each

connection has a strength represented by a scalar, viz. weight. Finally, a non-linear function governs the relationship between the neuron's output and its input. This non-linear function (also known as the activation function) can be a simple Relu function or a complex Izhikevich model in a Spiking Neural Network (SNN).

The bulk of the computation power in the inference stage is spent on processing neurons' inputs, calculating their outputs, and data movement between the layers. The complexity of this computation depends on the connections between the layers, bit resolutions of the weights, and activation functions. For example, 16-bit fixed-point wights result in less expensive MAC operations than 32-bit float weights, or crop-and-copy connections in UNets increase the memory utilization and require more complex scheduling.

Modern deep learning models enjoy architectures with large numbers of parameters, increasing numbers of layers, and irregular connections between non-adjacent layers. Although these architectures provide higher accuracies for their models, they also increase the model's implementation complexity on hardware, particularly for scale-out and power-limited systems. Moreover, current trends in DL indicate that future DNNs will have architectures closer to their biological counterparts with further complex neuron models and more connections between non-adjacent layers. Therefore, realizing DL accelerators on resource-limited processing platforms will become an even more challenging task.

A tolerable solution is to take advantage of the DL methods for retuning models and reshape the model for improving its hardware implementation on a target device. Currently, to accelerate a DL model's inference on a custom platform, DL designers pass an abstract model to hardware designers to create a functionally identical and lossless realization of the model on the hardware. Any modifications in this abstract will change the model's behavior and output. Therefore, any implementation optimization that entails reshaping the DNN architecture requires additional steps in the training stage to reture the model to ensure the quality of its output.

This thesis shows that a co-design approach can lead to creating better models with lower computational costs. In a co-design approach, an existing model is reshaped to optimize its implementation on a target platform. Then, this modified model is retuned to ensure its output quality. Thus, the co-design process can include iterations of model reshaping and retuning until both output quality and hardware cost reach their desired targets.

The rest of this chapter presents the outline and motivations of the remaining chapters.

## **1.1 Reshaping Spiking Neural Networks**

SNNs are the next generation of Artificial Neural Networks (ANNs) that utilize an eventbased representation to perform more efficient computation. Most SNN implementations have a systolic array-based architecture assuming that high sparsity in spikes will significantly reduce computing in their designs. This chapter shows that this assumption does not hold for applications with signals of the large temporal dimension. We develop a streaming SNN (S2N2) architecture that can support fixed-per-layer axonal and synaptic delays for its network. Furthermore, we introduce a change in current SNN models to reshape their neuron's processing scheme for replacing MAC operation with ACC operations to optimize our accelerator's computational cost. We then show that current SNN models can preserve their accuracies after the retuning.

S2N2 is built upon FINN [9] and thus efficiently utilizes FPGA resources. By avoiding the tick-batching and replacing MAC operations with ACC operations, a stream of RF samples can efficiently be processed by this accelerator, improving the memory utilization by more than three orders of magnitude.

In addition, this chapter introduces novel SNN models for automatic modulation classification and shows how these radio frequency applications match our S2N2 computational model.

## **1.2** Filtering Noise in Neuromorphic Vision Data

Neuromorphic vision sensors are an emerging technology inspired by how the retina processing images. These sensors are a perfect match for SNNs to process their output.

A neuromorphic vision sensor only reports when a pixel value changes rather than continuously outputting the value every frame as is done in an "ordinary" Active Pixel Sensor (ASP). This move from a continuously sampled system to an asynchronous event-driven one effectively allows for faster sampling rates; it also fundamentally changes the sensor interface. In particular, these sensors are highly sensitive to noise, as any additional event reduces the bandwidth and thus effectively lowers the sampling rate.

This chapter introduces a novel spatiotemporal filter with O(N) memory complexity for reducing background activity noise in neuromorphic vision sensors. To design this filter, we study the noise characteristics in neuromorphic sensors and provide a novel filter with improved computational cost and more capabilities compared to previous works.

Our design consumes  $10 \times$  less memory and has  $100 \times$  reduction in error compared to previous designs. Our filter is also capable of recovering real events and can pass up to 180% more real events.

### **1.3 Reshaping Residual Neural Networks**

ResNets employ skip connections as identity shortcut connections between the input and output of each residual block to ease the training of deeper networks. These connections are valuable for training to deal with the vanishing gradient problem and overcoming the saturation issue in very deep networks. However, skip connections also increase the implementation complexity in hardware. In particular, they are more problematic for inference accelerators on resource-limited platforms.

The hardware architecture has two options to implement skip connections: 1) keep the residual block data in the block's input buffer while the residual block is being processed, preventing it from receiving new input and degrading the pipeline performance, or 2) buffer this input elsewhere, forcing higher utilization of on-chip/off-chip memories, requiring larger memory bandwidth, and additional control logic. This chapter introduces SKIPTRIM, a reshaping method for the ResNets. In this method, skip connections in smaller ResNets are entirely removed, then through a retuning technique, these reshaped networks can regain their accuracy.

For the larger ResNets with deeper architectures, we introduce a reshaping technique to reposition the skip connections for allowing a specific layer merge that can benefit the hardware implementation. We then show that our reshaped models can regain their accuracy after the retuning.

SKIPTRIM decreases the BRAM utilization by 20% by pruning the skip connections for smaller ResNets, and 16% by shortening them for larger ResNets on an FPGA with minimal to no loss in the model accuracy.

### **1.4** Auto Tuning the Learning Rate

Training a neural network is a complicated and time-consuming task that involves adjusting and testing different combinations of hyperparameters (the training parameters). After reshaping a DL model, hyperparameters may require readjustments which can create a bottleneck in the co-design process.

One essential hyperparameter for training DNNs is the learning rate, which balances the magnitude of changes at each training step. This hyperparameter has dependencies on both the model architecture and other training parameters such as the optimizer. For example, a reasonable learning rate value for a network can change by quantizing the network parameters.

This chapter introduces an Adaptive Scheduler for Learning Rate (ASLR) that significantly lowers the tuning effort since it only has a single hyperparameter. ASLR produces competitive results compared to the state-of-the-art for both hand-optimized learning rate schedulers and line search methods while requiring significantly less tuning effort. Furthermore, our algorithm's computational cost is trivial and can be used to train various network topologies included quantized networks.

# Chapter 2 Reshaping Spiking Neural Networks

Artificial Neural Networks have shown remarkable success in large-scale image and video recognition [113, 117], speech recognition [11, 36], radio signal classification [95], and many other application domains [46, 63]. Spiking Neural Networks (SNNs) use an event-based model that better mimics biological neurons [33, 77] with the goal of providing high prediction accuracy while using minimal energy [118]. Recent advancements in SNN architecture design and training methods show promise in matching the accuracy of non-spiking ANNs [3, 8, 29, 115] and the potential to out-perform a similar-sized non-spiking ANN [17]. However, much work remains until we fully uncover the potentials of SNNs [118].

A conventional neuron model assumes every input requires calculation and performs N operations, e.g., multiplying and accumulating N input values with N weights (and an optional bias - see Equation 2.1). A typical convolutional layer in a modern feedforward neural network includes many neurons with an equal number of inputs (fan-in). This architecture creates patterns suitable for massively parallel implementations. Frameworks such as FINN [9], fpgaConvNet [132], and Eyeriss [12] provide efficient implementations of this architecture on FPGAs.

Conversely, event-based neural networks reduce wasted computation by only processing received events. For example when an event-based neuron with fan-in=N receives M < N events, calculating the input only requires M operations (Equation 2.2). This assumes a certain amount of sparsity and requires dynamic handling of events. This sparsity creates a run-time dependency

based on the input data and induces unpredictable and potentially irregular memory accesses. Therefore exploiting parallelism in SNN is more challenging than CNNs, DNNs, and other more traditional neural networks.

Previous works such as IBM TrueNorth [3], Intel Loihi [19], SpiNNaker [96], and BlueHive [87] have shown that processing SNN events can be efficiently implemented in custom hardware for both training and inference. Neurogrid [8] uses a mixed analog-digital approach for simulating large-scale spiking models and Minitaur [90] and SpinalFlow [89] describe inference accelerators for SNNs. Event processing is either done by encoding and storing events in a buffer to be processed in a systolic fashion (tick-batching) [3, 19, 89, 90] or a spike-routing mechanism is used to prevent deadlocks [8, 87, 96].

In this work, we introduce a streaming accelerator for spiking neural networks, S2N2. Our design efficiently supports both axonal and synaptic delays for feedforward networks with interlayer connections. We show that because of the spikes' binary nature, a binary tensor can be used for addressing the input events of a layer. We describe the condition when addressing events with a binary tensor, and no tick-batching (streaming) can provide a better memory utilization compared to encoding events and tick-batching. We show that this condition depends on the input's sparsity (more detail in Section 2.2.3) and holds, for example, applications, in particular for Radio Frequency (RF) applications.

We use the FINN framework [130] as our baseline and extend it with new functions for supporting our event-based processing of SNNs. Our proposed changes can maintain the high throughput of FINN and provide an efficient streaming implementation for SNNs by benefiting from FINN's optimized utilization footprint.

We also propose novel example applications for SNNs in the RF domain that can benefit from S2N2's streaming architecture. By looking at RF samples as events in In-phase and Quadrature (I/Q) plane, RF samples can be turned into highly sparse events as input to a SNN. RF inputs available in RF datasets [94,95] have a large temporal dimension, and a SNN designed for classifying these inputs can efficiently be implemented in S2N2. In addition, our design is tested by using some of the published applications for SNNs in the image classification domain [53, 115]. In order to adopt these previously published spiking networks to S2N2, we propose new architectural changes in these networks and show that modified networks can maintain their accuracy after re-training with new hyperparameters.

Our contributions can be summarized as following:

- We introduce a new streaming architecture, S2N2, for accelerating SNNs on FPGA platforms.

- We describe how to reduce the memory utilization for inputs with a large temporal dimension.

- We propose novel applications for SNNs in the RF domain that can benefit from our streaming architecture.

- We release our code as open-sourced to enhance accessibility and aid in future comparisons of our work <sup>1</sup>.

The remainder of the paper is organized as follows. In Section 2.1, we introduce SNNs in more depth and review the previous work on SNN FPGA implementations. S2N2 is described in detail in Section 2.2 and we demonstrate its advantages and implementation results for RF applications in Section 2.3. Additionally, Section 2.4 applies the S2N2 architecture to previously published SNNs for image classifications. We conclude our work in section 2.5.

## 2.1 Spiking Neural Network

Spiking neural networks are the third generation of ANNs developed to process information more similar to biological neural networks [77, 118]. In these networks, neurons propagate information by using spikes. The information is coded into the rate and time-of-arrival of the spikes.

<sup>&</sup>lt;sup>1</sup>github.com/arkhodamoradi/s2n2

Figure 2.1 shows an example comparison between a frame-based input and an eventbased input with rate-coded spikes. In general, input to each layer in a non-spiking neural network is a tensor of values (a multi-channel matrix). In contrast, in a SNN, inputs to each layer are events that have temporal and spatial positions. The temporal dimension of the input in SNNs consists of several "*ticks*". A tick is the minimum unit of time in a SNN that a neuron evaluates its input, updates its potential, and, depending on its model parameters, may generate a spike in its output.

For a more clear comparison, we look at the operations required for evaluating inputs in non-spiking and spiking neurons. Input to a non-spiking neuron is calculated as follows:

$$I = \sum_{i=0}^{N} w_i x_i \tag{2.1}$$

Here,  $x_i$  are the input values and  $w_i$  are their associated weights and bias is not shown. While input to a spiking neuron at tick=*t* is calculated as following:

$$I_t = \sum_{i \in S_t} w_i \tag{2.2}$$

Here,  $S_t$  is the set of inputs to the neuron that have a spike at tick=*t*, and  $w_i$  are the weights associated with those inputs.

With sparsity in input spikes, Equation 2.2 requires fewer and simpler accumulation operations compared to the fixed number of MAC operations required in Equation 2.1. However, Equation 2.1 is more suitable for applying techniques such as loop-unrolling for exploiting parallelism. In addition, Equation 2.2 requires memory to store S to keep track of input spikes. Later in this work, we provide solutions to efficiently implement Equation 2.2 on custom hardware.

In a conventional ANN, an activation function of a neuron defines the output of that neuron given an input. In SNNs, neuron's output and evaluation of neuron potential are governed by *neuron's model*.

**Figure 2.1.** A frame-based input (on the left) is a matrix of numbers. An event-based input (on the right) includes trains of spikes. In this example, the number of trains is equal to the number of pixels in the frame. The duration of the spike trains is equal to the number of ticks. At each tick, up to one spike can exist in each train.

Neuron models used in SNNs are biologically plausible models that are computationally more powerful units compared to activation functions used in non-spiking networks [33]. These models are capable of extracting the temporal information embedded in their input and perform more complex tasks [77].

Although more complex mathematical models such as Izhikevich [50] and Hodgkin–Huxley [44] can accurately model a biological neuron's behavior, current training methods for SNNs are not geared to train these complex models [118]. For now, simpler models such as Integrate and Fire (IF) and Leaky Integrate and Fire (LIF) are more prevalent in current SNN applications. In this work, we use a LIF model with one internal parameter.

### 2.1.1 LIF Model

Leaky Integrate and Fire (LIF) model is a neuron model widely used in SNN applications [53,64,97,115,143]. LIF model memorizes its past inputs by adding every input to its membrane potential and uses a leak (decay) parameter to forget them. This leak parameter is reflecting the diffusion of ions that occurs through the membrane when some equilibrium is not reached in the

cell:

**Figure 2.2.** LIF neuron with two inputs. An incoming spike increases the membrane voltage by the weight associated with its connection. A decay parameter decreases the membrane potential, and if this voltage passes a threshold, it resets to a preset value, and the neuron generates a spike at its output.

$$m_t = (1 - \operatorname{out}_{t-1}) * d * m_{t-1} + I_t \quad , \quad 0 < d < 1$$

(2.3)

$$\operatorname{out}_{t} = \begin{cases} 1, & \text{if } m_{t} > T \\ 0, & \text{ow} \end{cases}$$

$$(2.4)$$

Here,  $d \in (0, 1)$  is the decaying leak parameter, T is the threshold,  $m_t$  is the membrane voltage at tick=t, and  $I_t$  is the input from Equation 2.2. The term  $(1 - \text{out}_{t-1})$  in Equation 2.3 is the reset mechanism that sets the membrane voltage to zero if neuron fires a spike in its output. This mechanism is illustrated in Figure 2.2.

1

Generally, training LIF neurons is done by treating the threshold (T) and decay (d) as non-trainable hyperparameters.

### 2.1.2 **Propagation Delays in Neuron**

As shown in Figure 2.3, a biological neuron has different components. Simply, nerve impulses are received by dendrites and processed by the nucleus. Impulses generated by the neuron travel through the axon and are distributed through synapses.

This process has two propagation delays: 1) *Axonal delay* that is the time required for an action potential to travel from soma to synapses through the axon. 2) *Synaptic delay* that is the time interval required for a neurotransmitter to be released from a presynaptic membrane distribute across the synaptic cleft and received by the post-synaptic membrane.

Supporting these propagation delays in implementation can increase the complexity of the design. Hence, only a few previous works support these delays (more detail in the next section).

**Figure 2.3.** Illustration of a biological neuron. Dendrites receive inputs from presynaptic membranes to soma. The nucleus reacts to the received signals and may produce an action potential, which then has to go through the axon and distribute to post-synaptic membranes through Synapses.

### 2.1.3 Custom SNN Implementations

Analog [70,71,124], digital [3,13,19,87,89,90,96,126], and mixed-analog-digital [8,88] accelerators for SNNs have been described in the literature.

Analog realizations [70, 71, 124] are based on memristive technology [122] and have to deal with latency, density, and variability issues related to this technology [2]. In an other work [88], in addition to a memristive-based analog module, a digital module is used to route events and update receptive neurons. Neurogrid [8] does not use memristive technology in its analog module and increases parallelism by using a digital router for its events. In this work, we introduce a digital implementation for SNNs, and therefore we do not compare our work with analog realizations.

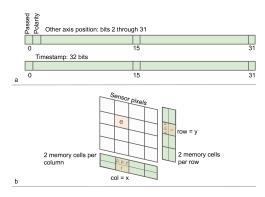

Large scale custom chip implementations such as Intel Loihi [19] with 4,096 on-chip cores and 1,024 neural units per core, SpiNNaker supercomputer [96] with 57,600 chips and 1,036,800 processors each capable of simulating 1,000 neurons, and IBM TrueNorth [3] with 4,096 cores and supporting one million neurons are designed with synaptic delay support. These implementations are designed to support a mesh of neurons with no particular topology. This is done by using advanced routers and schedulers. For example, Loihi uses six bits for the synaptic delay and two independent physical routing networks for core-to-core multicast. And events in SpiNNaker are coded to AER [78] packets (including timestamp, position, polarity, and debugging bits) and are source coded, meaning that the destination of each neuron has to be stored for routing the packets. TrueNorth has its own packet coding scheme, including the address of the core, axon index, tick number, and debugging flags. It buffers the events and uses a scheduler for processing events at specified ticks for supporting the synaptic delay.

Previous FPGA implementations of SNNs took a similar approach. BlueHive [87] is a 4-FPGA system and supports 64k Izhikevich [50] neurons per FPGA. BlueHive uses a routing system for events and 16 FIFOs for queuing events for 16 different synaptic delays with 1 millisecond granularity. Minitaur [90] encodes its events into five bytes, four bytes for timestamp and one byte for layer index. It supports a fixed axonal delay by buffering its events. In some other implementations routing and queuing is done without supporting synaptic or axonal delays [13, 32, 89, 126]. Because of queuing, parallelism in these works is done when an event is processed. Each event has a number of destinations, and upon processing an event, all of

| Architecture    | Technology  | Purpose                 | Supported Topology                        | ted Topology Supported Propagation Delay Required Complexity for |                                           |

|-----------------|-------------|-------------------------|-------------------------------------------|------------------------------------------------------------------|-------------------------------------------|

| Loihi [19]      | custom chip | training and simulation | general mesh synaptic two separate physic |                                                                  | two separate physical routers             |

| SpiNNaker [96]  | custom chip | simulation              | general mesh synaptic AER packets+re      |                                                                  | AER packets+router                        |

| TrueNorth [3]   | custom chip | simulation              | general mesh synaptic per-chip sc         |                                                                  | per-chip scheduler                        |

| BlueHive [87]   | FPGA        | simulation              | general mesh                              | general mesh synaptic 16 FIFOs with                              |                                           |

| Minitaur [90]   | FPGA        | accelerator             | general mesh                              | fixed axonal                                                     | tick-batching and sorting                 |

| SpinalFlow [89] | FPGA        | accelerator             | feedforward                               | none                                                             | tick-batching (without supporting delays) |

| [126]           | FPGA        | accelerator             | small and dense                           | none                                                             | N/A                                       |

| [13]            | FPGA        | accelerator             | feedforward                               | none                                                             | tick-batching (without supporting delays) |

| [32]            | FPGA        | accelerator             | feedforward                               | none                                                             | tick-batching (without supporting delays) |

| [52]            | FPGA        | accelerator             | feedforward                               | none tick-batching (without supporting                           |                                           |

| S2N2            | FPGA        | accelerator             | feedforward                               | synaptic+axonal streaming                                        |                                           |

|                 |             |                         |                                           |                                                                  |                                           |

**Table 2.1.** A comparison between S2N2 and previous works.

its destinations (membrane potentials) are incremented by their associated weights in parallel. Routers and schedulers are used to prevent deadlocks and data hazards while processing events from different queues with the same destinations. A comparison is provided at Table 2.1.

In the next section, we argue that by considering the network topology, for a feedforward network with interlayer connections, fixed-per-layer axonal and synaptic delays can be supported without extra FIFOs, schedulers, and separate routing networks.

## 2.2 Streaming Spiking Neural Networks (S2N2)

To explain the streaming architecture of S2N2, we first look into the coding scheme used for storing events in input buffers. And explain the condition when a binary tensor can utilize less memory. We then explain how feedforward SNNs with interlayer connections can support fixed-per-layer synaptic and axonal delays without requiring schedulers and separate routing systems.

### 2.2.1 Input Buffer - Memory Utilization

As shown in Figure 2.1, a spiking input has a temporal duration with a total number of ticks (time units). In tick-batching, all the events for the entire duration of input are buffered and processed in a systolic implementation [89].

Let's look at the input events in a layer of a feedforward network. Assuming *S* being the total number of inputs to the layer, and *T* the total duration of the input, to encode events, we need  $\log_2 S$  bits for addressing the position and  $\log_2 T$  bits for addressing the tick number of each event. Assuming sparsity in the incoming events, the layer can receive up to p \* ST events when  $p = 1-sparsity\_ratio$  and  $p \in (0,1)$ . Therefore we need a buffer of size:

buffer size in bits =

$$pST \log_2 ST$$

(2.5)

On the other hand, we can use a binary tensor to address the input events, ones for when there is an event, and zeros otherwise. In this case, we need ST-bits to store addresses in a binary tensor. Buffering encoded events requires less memory compared to a binary tensor if:

$$p\log_2 ST < 1 \tag{2.6}$$

This can be a tight condition on input's sparsity. E.g., for a layer with an input tensor of size  $64 \times 16 \times 16$  with a total duration of 16 ticks, only for  $p < \frac{1}{18} = 5.5\%$  or 94.5% sparsity for input, buffering encoded events uses less memory compared to a binary tensor of size  $2^{18}$  bits. In this example, as soon as the input's sparsity drops below 94.5%, Equation 2.6 is not satisfied, and the binary tensor requires less memory. In Sections 2.3 and 2.4, we show that Equation 2.6 can not be satisfied for our applications.

### 2.2.2 Fixed-Per-Layer Propagation Delays

As mentioned before, synaptic delays are realized in a limited number of previous work. Custom chips [3, 19, 96] queue their events and use complex routing and scheduling systems to process events at the correct tick with an appropriate delay. In FPGA implementations, multiple FIFOs are used to support synaptic delays with large granularity (1 millisecond) [87]. These implementations support different topologies of spiking networks. And [90] supports feedforward networks with fixed axonal delays by buffering and sorting its encoded events.

**Figure 2.4.** Top: A simple 3-layer network with fixed-per-layer axonal and synaptic delays. Inputs to each layer are binary vectors, and "1"s are for spikes. Input to a neuron is the sum of all inputs, and all weights are equal to one. Bottom: the flow of the input through the network. E.g., network input at tick=1 (color-coded) is received by both neurons in the first layer. With no axonal delay, they each produce one spike at their outputs at the same tick. The second layer receives this input (same color code) with a synaptic delay (3 ticks). At tick=4, both inputs to each neuron in the second layer have spikes. Hence their inputs are equal to 2.

Feedforward SNNs with interlayer connections have a specific topology that can be exploited for supporting fixed-per-layer synaptic and axonal delays with a reduced implementation cost. As shown in [133], temporal coding is still possible with fixed propagation delays. Figure 2.4 shows a simple 3-layer network with fixed-per-layer axonal and synaptic delays, meaning that all neurons in one layer have the same axonal delay and the same synaptic delay. For the sake of simplicity, neurons in this network spike if they receive an input larger than zero, and all weights are equal to one. Input to each neuron is the sum of all inputs.

The bottom part of Figure 2.4 shows how spikes spread through the network under axonal and synaptic delay conditions. Input to each layer is a binary vector, and spikes are represented by "1"s. Weights are equal to one, and input to a neuron is the sum of weights for connections with a spike. E.g. at tick=4, both inputs to neuron 10 have spikes and in(10) = 2. Previous works with propagation delay support [3, 19, 87, 90, 96] support this with different complexities (see Table 2.1).

| tick # | in(00) | in(01) | out(00) | out(01) | in(10) | in(11) | out(10) | out(11) | in(20) | in(21) | out(21) | out(22) |

|--------|--------|--------|---------|---------|--------|--------|---------|---------|--------|--------|---------|---------|

| 0      | 0      | 1      | 0       | 1       | 1      | 1      | 1       | 1       | 2      | 2      | 1       | 1       |

| 1      | 1      | 1      | 1       | 1       | 2      | 2      | 1       | 1       | 2      | 2      | 1       | 1       |

| 2      | 0      | 0      | 0       | 0       | 0      | 0      | 0       | 0       | 0      | 0      | 0       | 0       |

| 3      | 0      | 1      | 0       | 1       | 1      | 1      | 1       | 1       | 2      | 2      | 1       | 1       |

| 4      |        |        |         |         |        |        |         |         |        |        |         |         |

| 5      |        |        |         |         |        |        |         |         |        |        |         |         |

| 6      |        |        |         |         |        |        |         |         |        |        |         |         |

| 7      |        |        |         |         |        |        |         |         |        |        |         |         |

| 8      |        |        |         |         |        |        |         |         |        |        |         |         |

| 9      |        |        |         |         |        |        |         |         |        |        |         |         |

| 10     |        |        |         |         |        |        |         |         |        |        |         |         |

| 11     |        |        |         |         |        |        |         |         |        |        |         |         |

**Figure 2.5.** With fixed-per-layer propagation delays in the example network shown in Figure 2.4, we can process inputs and outputs of all layers assuming no delay and push all the delays to the end. Then an accumulated delay (shown in purple and blue) can be added to the network output.

However, because of the network topology, we can process all the layers, assuming no propagation delay, and push all the delays to the end. Then a total delay equal to all accumulated delays can be applied to the network's output as shown in Figure 2.5.

This practice can be applied to any structured feedforward network with only interlayer connections. In this case, we can support both synaptic and axonal delays without schedulers, extra FIFOs, and sorting mechanisms used in previous works.

### 2.2.3 Architecture

The streaming architecture of S2N2 is designed based on the FINN framework [130]. In the following, we first describe FINN's approach to implementing non-spiking and conventional

neural networks. We then describe our design to support the LIF model in FINN.

**FINN framework:** The original FINN paper [130] introduced a framework for building fast and flexible FPGA accelerators using a flexible heterogeneous streaming architecture. Exploiting a set of optimizations, FINN enables efficient mapping of binarized neural networks to hardware and supports fully connected, convolutional, and pooling layers. The second version of FINN described in [9], provides support for non-binary networks.

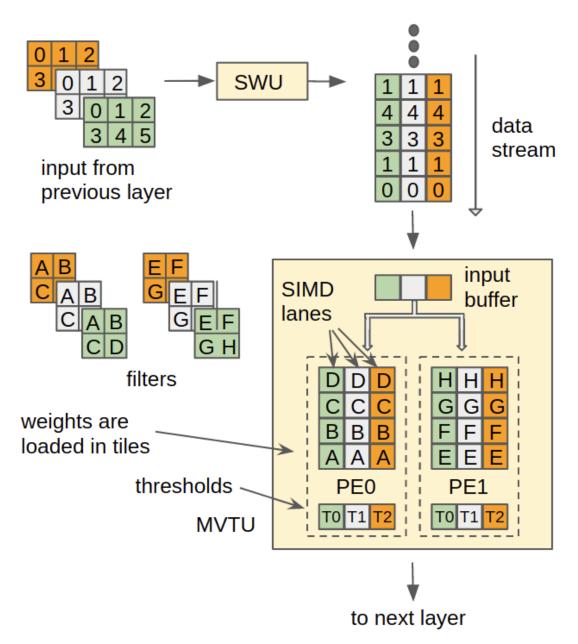

In the FINN architecture, a Sliding Window Unit (SWU) prepares the input by applying interleaving and implementing the image-to-column (im2col) algorithm. The output stream of a SWU feeds a Matrix Vector Threshold Unit (MVTU), which is the computational core for FINN's accelerator designs. This core is used in the implementations of both fully connected and convolution layers.

As shown in Figure 2.6, a MVTU has several Processing Elements (PE) that can generate output channels in parallel. Each PE has a number of SIMD lanes. If  $P_{\text{FINN}}$  be the number of PEs and  $S_{\text{FINN}}$  be the number of SIMD lanes, A  $P_{\text{FINN}}$ -high,  $S_{\text{FINN}}$ -wide tile matrix is processed at a time, inputs are mapped to different SIMD lanes and outputs are calculated in parallel by PEs. To accommodate this process, weights are also loaded from memory in tiles, and each PE takes a sub-tile of the weights to process its output.

All PE units have access to the input buffer inside the MVTU. The width of this buffer in bits is equal to the number of SIMD lanes multiplied by the activation bit width. For simplicity, only one row of this buffer is shown in Figure 2.6. The total number of rows in this buffer is equal to the ratio of (*kernel width*  $\times$  *kernel height*  $\times$  *#input channels*)/#SIMD lanes. Which makes the input buffer size equal to (*kernel width*  $\times$  *kernel height*  $\times$  *#input channels*) for 1-bit activation.

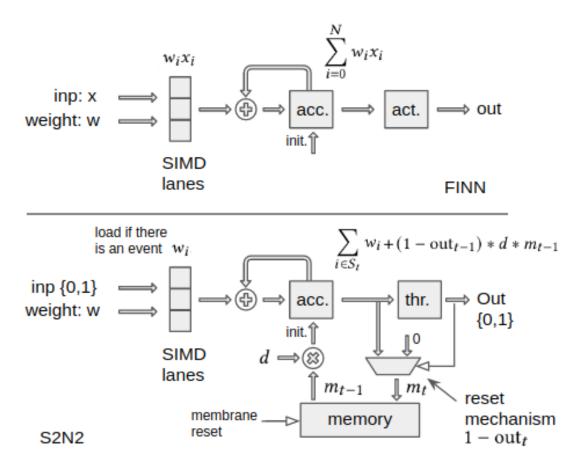

The process flow of one PE is shown in (Figure 2.7.upper). The accumulator is initialized to a preset value (usually zero), then input and PE's sub-tile of weights are loaded into SIMD lanes. SIMD lanes execute Equation 2.1 and accumulate the results in the accumulator. After processing all the inputs for the current output, the accumulator value is passed through the

**Figure 2.6.** FINN [130] architecture. SWU interleaves the input by applying the image-tocolumn algorithm and feeds MVTU. Each PE inside MVTU processes one output channel and has a number of SIMD lanes that read from input channels and multiply the input by kernel weights in parallel.

activation for generating the output.

**Implementing the LIF Model:** S2N2's contribution to the FINN platform is by providing support for the LIF model in FINN's computational core, MVTU. In the following, we describe our design in detail and explain how to utilize FINN's architecture for initializing

**Figure 2.7.** Upper: PE implementation in FINN [130]. Lower: PE architecture to support SNN in FINN.

membrane potentials for each input. In the next section, we describe a possible optimization for decaying membrane potentials without a multiplication operation to maintain FINN's high throughput.

As mentioned in Section 2.2.1, if the condition in Equation 2.6 is not met, using a binary tensor for addressing events has a lower memory utilization than encoding events. In Sections 2.3 and 2.4, we show that this condition does not hold for example applications. Therefore, we use the input as is (a binary tensor) for addressing events. In addition, because FINN is not a systolic implementation, and the input is processed in a streaming architecture, the size of the input buffer used in the MVTU can be smaller than the input [130]. E.g., for an input of size  $I_W \times I_H \times I_{Ch}$  with a kernel size of  $K_W \times K_H$ , and 1-bit activation, the buffer size is equal to

$K_{\rm W} \times K_{\rm H} \times I_{\rm Ch}$ .

To support SNNs with the LIF model (Figure 2.7.lower), we initialize the accumulator by the previous membrane voltage stored in the on-chip memory, multiplied by the decay value, *d*. The SIMD lanes are programmed to use the input as the address of events and only load weights if there is a spike in that input position. This is exactly executing Equation 2.2. After executing all the operations required by Equation 2.2, the value stored in the accumulator is equal to Equation 2.3. This value can then be passed to a comparator to execute Equation 2.4. The result of this comparator is our output spike and is also used as the input to a selector for implementing the reset mechanism  $(1 - out_t)$  and storing the correct membrane voltage back to the memory.

The MVTU in a FINN implementation has a control signal defining the number of runs per input. We use this signal to indicate the last tick for an input. This signal can be used to reset membrane potentials to zero if required.

In FINN, the MVTU is used for implementing both convolutional and fully connected layers. Similarly, with our proposed additions and modifications to the MVTU, both convolutional and fully connected layers for SNNs can be implemented with the MVTU shown in Figure 2.7.lower.

The pooling unit (PU) described in FINN [130] is a binary max-pooling layer. We chose to use binary tensors for addressing our spikes. Therefore we use the PU as is.

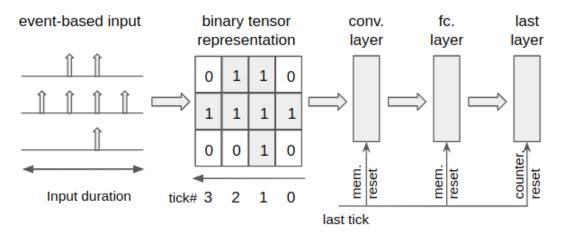

As illustrated in Figure 2.8, an event-based input has a temporal dimension that is divided into a number of ticks. To produce the classification output, the last layer in a SNN has one counter per label. Each counter keeps track of all the spikes received for that label. At the last tick for an input, the value of these counters can be fed to a function for determining the classification result (e.g., SoftMax). These counters are reset to zero at the last tick of each input.

As we explained earlier in this section, fixed-per-layer propagation delays in feedforward SNNs with only interlayer connections can be added as an accumulated delay to the output. Therefore, our proposed design can be used to implement such networks with fixed-per-layer

**Figure 2.8.** Binary tensor for addressing spikes in an event-based input. The last tick is used as a reset signal to reset membrane potentials (mem. reset) and counters at the last layer (counter reset).

axonal and synaptic delays. This design has no scheduler, and we do not queue encoded events. This gives us a number of advantages. 1) We can expand the parallelism of our design by processing events in parallel vs. sequential process in previous work. 2) By using a binary representation for addressing instead of addressing events by their position and tick number, we do not require a separate router. 3) we can support fixed-per-layer axonal and synaptic delays without a scheduler. 4) Addressing events with a binary tensor reduces our memory utilization when the condition in Equation 2.6 is not met.

# 2.3 S2N2 for Automatic Modulation Classification

Deep learning for Radio Frequency (RF) applications is a relatively new field. In particular, using SNNs for RF applications is barely touched in the literature. One of the RF applications suitable for ANNs is Automatic Modulation Classification (AMC). This important method can be used in radio fault detection, opportunistic mesh networking, dynamic spectrum access, and numerous regulatory and defense applications. Previous works have shown that ANNs can effectively perform modulation classification with high accuracy [73, 83, 94, 95].

This section introduces two new network architectures for AMC that are based on S2N2.

The novelty of these architectures is that the input is fed to the network as a stream of events in the In-phase/Quadrature (I/Q) plane. To our knowledge, these are the only neural networks that consume a stream of RF samples as an event-based input. In the following, we describe the datasets used for training and explain our networks' architecture.

**Datasets:** We use two RF datasets to train our networks. *RadioML.2016* [94] is a collection of 11 different modulations (8PSK, AM-DSB, AM-SSB, BPSK, CPFSK, GFSK, PAM4, QAM16, QAM64, QPSK, and WBFM). Each class has samples recorded at 20 different Signal to Noise Ratio (SNR) levels (from -20dB to 18dB in increments of 2dB). Each pair {modulation, SNR} has 728 training examples, and Each training example is a time-series of 128 In-phase Quadrature (I/Q) sample pairs.

*RadioML.2018* [95] is a collection of 24 different modulations (OOK, 4ASK, 8ASK, BPSK, QPSK, 8PSK, 16PSK, 32PSK, 16APSK, 32APSK, 64APSK, 128APSK, 16QAM, 32QAM, 64QAM, 128QAM, 256QAM, AM-SSBWC, AM-SSB-SC, AM-DSB-WC, AM-DSB-SC, FM, GMSK, and OQPSK). Each modulation class has samples recorded at 26 different SNR levels (from -20dB to 30dB in increments of 2dB). Each pair {modulation, SNR} has 4096 training examples and Each training example is a time-series of 1024 I/Q sample pairs. Both datasets are publicly available <sup>2</sup>.

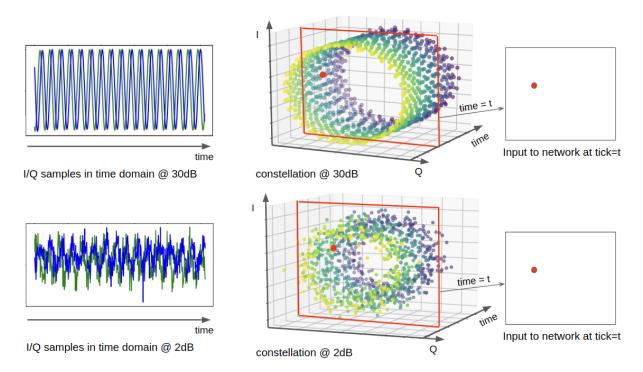

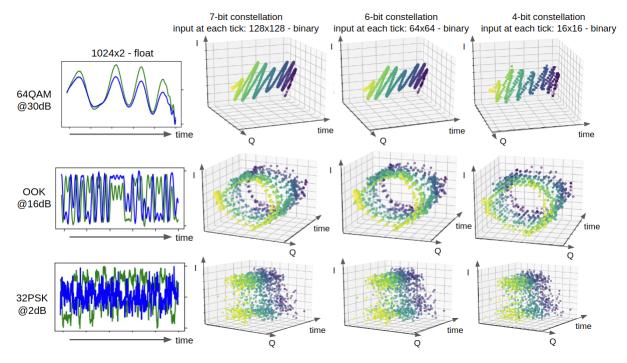

Two time-series examples from RadioML.2018 are shown in Figure 2.9.left. These examples are 1024 I/Q sample pairs. In all of the previous work, inputs are tensors with same shape as these examples. E.g., for RadioML.2016, inputs are  $2 \times 128$  float tensors, and in RadioML.2018, inputs are  $2 \times 1024$  float tensors.

S2N2 is not a systolic implementation. Meaning, we can feed the network with a stream of events. Therefore, in our networks, we use the constellation of signals (shown in Figure 2.9.middle), and at each tick, we feed the network with one sample (Figure 2.9.right). Therefore our input is a stream of binary tensors.

To our knowledge feeding RF samples as events to a neural network has never been done

<sup>&</sup>lt;sup>2</sup>https://www.deepsig.ai/datasets

**Figure 2.9.** Examples of AM-DSB class from RadioML dataset [95]. On the left, two examples of AM-DSB I/Q samples are shown at 30dB and 2dB SNR at top and bottom, respectively. The middle illustrates the constellations of the same examples. On the right, input to the network at time (tick)=*t* is shown. Input to our networks are samples as events in I/Q plane.

before. The only work on using SNNs for AMC is a preliminary investigation done by NASA [57] that implements a two-layer SNN in MATLAB for classifying three noise-free modulations (BPSK, QPSK, and 8PSK). In NASA's work, inputs are 8-bit images of constellations.

Feeding a neural network with RF samples as events come with two benefits. 1) Although we and all the previous works use recorded data, in a real-world setup, our network can consume RF samples one-by-one in a stream. Other works have to buffer samples (e.g., 128 or 1024 samples) before taking them as input. 2) We can aggressively quantize the I/Q plane; therefore the input size (in bits) can get smaller. The following explains the I/Q plane quantization.

Examples in RadioML.2016 and RadioML.2018 are 128 and 1024 pairs of float numbers, respectively. We construct the I/Q plane by quantizing the pair using a uniform quantizer. This will reduce our input size. Figure 2.10 illustrates three examples from RadioML.2018: OOK, 64QAM, and 32PSK classes at 30db, 16dB, and 2dB SNR, respectively. To the right of these

**Figure 2.10.** Applying quantization to the I/Q plane. Original examples from RadioML.2018 [95] dataset are 1024 pairs of float numbers (left). In-phase and Quadrature values can be quantized for a smaller input tensor (first three columns from the right). At each tick, we feed one slice of the quantized constellation tensor to the network. The figure shows that the constellation shape is recognizable while I/Q plane is aggressively quantized.

examples, their constellations with quantized in-phase and quadrature values are shown. As it is shown, the shapes of the constellations are recognizable even at the lowest bit resolution. We used the 4-bit quantized constellations to train our networks.

## **Network Architecture for RadioML.2016**

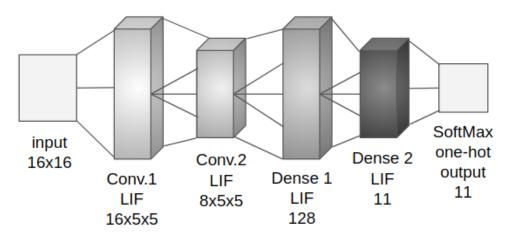

This network is a four layer architecture similar to the network described in [94] with different number of kernels and LIF model for activation (Figure 2.11).

Inputs to each layer are binary tensors. We used 90% of the dataset for training and 10% for validation. For training, we used the method described in [108] as our baseline and changed the loss function to *smooth L1 loss*, and adjusted the hyperparameters. Throughout this chapter, we refer to this network as  $S2N2\_rf1$ .

We achieved 91.7% Top-1 and 100% Top-5 validation accuracy using all SNR levels in

Figure 2.11. S2N2\_rf1 architecture.

Table 2.2. Comparing validation accuracy and network size for S2N2\_rf1.

| Network  | Input           | Conv.1 | Conv.2 | Dense 1 | Dense 2 | Accuracy |

|----------|-----------------|--------|--------|---------|---------|----------|

| [94]     | 128x2<br>32-bit | 64x1x3 | 16x2x3 | 128     | 11      | 87.4%    |

| S2N2_rf1 | 16x16<br>binary | 16x5x5 | 8x5x5  | 128     | 11      | 91.7%    |

our training. A comparison between S2N2\_rf1's size and accuracy with the previous work on RadioML.2016 is provided in Table 2.2.

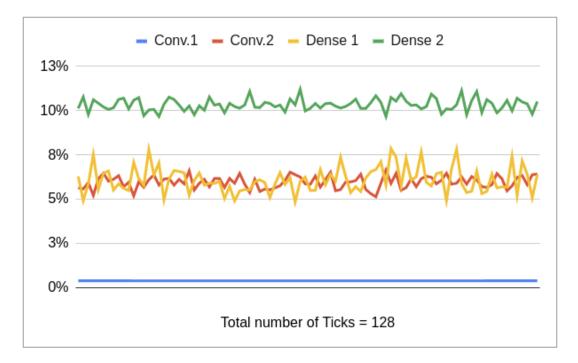

Figure 2.12 illustrates the spike ratio in the input of each layer for S2N2\_rf1. The first convolution layer (Conv.1) receives one event at each tick; this means that the spike ratio for this layer with an input of size  $16 \times 16$  is  $\frac{1}{16 \times 16} = 0.0039$ .

As mentioned in Sections 2.1.3 and 2.2.1, previous works have used tick-batching and buffered encoded events. This means that for a total number of ticks=128, and input size of  $16 \times 16$  at spike ration of 0.39%, according to Equation 2.5, tick-batching requires 1,917 bits to queue the input events. Because S2N2 is based on the streaming architecture of FINN [130], and only a portion of the input is buffered for processing. The size of this buffer used in MVTU is

**Figure 2.12.** The ratio of spiking neurons in input to each layer of S2N2\_rf1. Ratios are collected during classifying one input (128 ticks) with trained weights.

equal to *kernel size*  $\times$  *#input channels*=25 bits for Conv.1 layer. In Table 2.3, we provide the same comparison for all the layers of this network. These results show that, on average, memory utilization for input buffers in S2N2\_rf1 is improved by over three orders of magnitude.

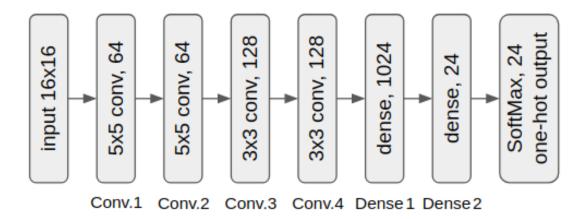

#### **Network Architecture for RadioML.2018**

As mentioned in our introduction, training methods for spiking neural networks are not as mature as other ANNs. In particular, current training methods are evaluated on smaller networks, and simple datasets [32] and perform poorly when used for training very deep architectures [53, 115] and evaluated on more complex datasets [112]. Therefore we could not train a deep spiking network similar to the non-spiking networks used in previous works (VGG10 and Resnet33) [95, 129]. Instead, we chose a smaller network with only eight layers. We refer to this network as  $S2N2_rf2$ .

S2N2\_rf2 architecture is shown in Figure 2.13. We used the same training script like the one we used for training S2N2\_rf1 as the baseline. We then adjusted the script for the dataset

| Layer   | #Ticks | Input Size | Maximum<br>Spike Ratio | Buffer Size<br>Tick-Batching | Buffer Size<br>S2N2_rf1 | Improvement |

|---------|--------|------------|------------------------|------------------------------|-------------------------|-------------|

| Conv.1  | 128    | 16×16      | 0.39%                  | 1,917 bits                   | 25 bits                 | ×77         |

| Conv.2  | 128    | 16×16×16   | 7%                     | 697,304 bits                 | 400 bits                | ×1,744      |

| Dense 1 | 128    | 8×12×12    | 8%                     | 212,337 bits                 | 128 bits                | ×1,658      |

| Dense 2 | 128    | 128        | 12%                    | 27,526 bits                  | 11 bits                 | ×2,502      |

**Table 2.3.** Required memory for buffering input at each layer of S2N2\_rf1 is compared with tick-batching (Equation 2.5).

Figure 2.13. S2N2\_rf2 architecture.

and its increased number of labels.

This network can achieve 68.5% Top-1 and 95% Top-5 validation accuracy on 24 classes in RadioML.2018 dataset. Table 2.4 compares our accuracy with two related non-spiking networks.

Although that S2N2\_rf2 does not have a high accuracy compared to deeper and nonspiking networks, it is included in this work to provide a comparison between S2N2 architecture and tick-batching with regards to memory utilization. In particular, when larger RF inputs are used.

Figure 2.14 shows spike rations at the input of each layer of S2N2\_rf2. These ratios are similar to the ratios in S2N2\_rf1 (Figure 2.12). We expect that with future improvements in

| Network     | Input           | #Layers | Accuracy |

|-------------|-----------------|---------|----------|

| ResNet [95] | 1024x2 (32-bit) | 33      | 95.5%    |

| VGG [95]    | 1024x2 (32-bit) | 10      | 88.0%    |

| S2N2_rf2    | 16x16 (binary)  | 6       | 68.5%    |

Table 2.4. Comparing validation accuracy and network size for S2N2\_rf2.

training methods for deeper SNNs, similar spike ratios with no significant reductions will hold for a spiking network with a higher accuracy.

We use these ratios to show the efficiency of S2N2 for reducing the input buffer size at each layer. Even if our assumption does not hold, and in the future networks with lower spike ratios provide a higher accuracy, S2N2 is still more efficient at the minimum possible spike ratio; only one spike at layer's input (first row in Tables 2.3 and 2.5).

**Figure 2.14.** The ratio of spiking neurons in input to each layer of S2N2\_rf2. Ratios are collected during classifying one input (1024 ticks) with trained weights.

Table 2.5 illustrates a comparison between input buffer sizes required for S2N2 and tick-batching. Equation 2.5 is used to calculate the buffer size for tick-batching. It is clear that for inputs with large temporal dimension, using a streaming architecture significantly reduces the memory utilization.

**Table 2.5.** Required memory for buffering input at each layer of S2N2\_rf2 is compared with tick-batching (Equation 2.5).

| Layer   | #Ticks | Input Size | Maximum<br>Spike Ratio | Buffer Size<br>Tick-Batching | Buffer Size<br>S2N2_rf2 | Improvement |

|---------|--------|------------|------------------------|------------------------------|-------------------------|-------------|

| Conv.1  | 1024   | 16×16      | 0.39%                  | 18,403 bits                  | 25 bits                 | ×737        |

| Conv.2  | 1024   | 16×16×64   | 0.5%                   | 2,013,266 bits               | 1,600 bits              | ×1,258      |