## **UC Berkeley**

### **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Switching Schemes for Hybrid Switched-Capacitor DC-DC Power Converters

### **Permalink**

https://escholarship.org/uc/item/6m99v3vp

#### **Author**

Blackwell, Margaret Elizabeth

#### **Publication Date**

2023

Peer reviewed|Thesis/dissertation

### Switching Schemes for Hybrid Switched-Capacitor DC-DC Power Converters

Ву

Margaret Elizabeth Blackwell

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Robert C. N. Pilawa-Podgurski, Chair Assistant Professor Jessica Boles Professor Ali Niknejad Assistant Professor Andrew Stillwell

Fall 2023

## Switching Schemes for Hybrid Switched-Capacitor DC-DC Power Converters

Copyright 2023 by Margaret Elizabeth Blackwell

#### Abstract

Switching Schemes for Hybrid Switched-Capacitor DC-DC Power Converters

by

#### Margaret Elizabeth Blackwell

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Associate Professor Robert C. N. Pilawa-Podgurski, Chair

Power converter topologies are continually evolving and improving especially as new applications such as space exploration mature, and new power architectures emerge. One such evolutionary branch of power converters is hybrid switched-capacitor (SC) converters which leverage capacitors as highly energy-dense components, high figure-of-merit switching devices, and small magnetics to realize high-performance power electronics. To fully exploit the benefits of this relatively new class of power converters requires investigation into control schemes. Whether using conventional switching control strategies or developing novel arrangements, this work explores the theoretical and practical intricacies of applying various switching schemes to hybrid SC converters.

Due to the reliance on capacitors for energy processing, SC converters typically suffer from charge-sharing losses when capacitors are charged/discharged into other capacitors or sources. However, adding a small inductance to the circuit and incorporating clever switching patterns can reduce or eliminate these losses. Furthermore, with an increase in the number of switching devices over traditional converters, losses associated with those switches may also increase. This work examines soft-switching techniques and how application to hybrid SC converters differs from previous works.

Finally, a hybrid SC converter is designed and tested for low-voltage automotive powertrain applications. In an industry that has strict regulations, this work seeks to demonstrate these new topologies can meet the required specifications and can do so with high performance as well. Switching techniques for mitigation of electromagnetic interference are evaluated against regulated limits and against efficiency performance.

Theory, analysis, and experimental results are expounded upon for several switching control strategies of hybrid SC converters addressing challenges of high-efficiency, low-noise, and high-density for applications to data center power delivery, space technology, and automotive powertrains.

### $To\ Devin$

for your incessant love and support

# Contents

| $\mathbf{C}$ | onter              | nts                                                      | ii          |

|--------------|--------------------|----------------------------------------------------------|-------------|

| Li           | st of              | Figures                                                  | iv          |

| Li           | st of              | Tables                                                   | ix          |

| 1            | Intr<br>1.1<br>1.2 | Introduction                                             | 1<br>1<br>2 |

| 2            | Dic                | kson Converter Variations                                | 5           |

|              | 2.1                | Topology Evolution                                       | 5           |

|              | 2.2                | Chapter Summary                                          | 7           |

| 3            | Fun                | damentals of Hybrid Switched-Capacitor Converters        | 9           |

|              | 3.1                | Modeling of Power Converters                             | 9           |

|              | 3.2                | Advantages of Hybrid Switched-Capacitor Converters       | 10          |

|              | 3.3                | General Analysis of Hybrid Switched-Capacitor Converters | 14          |

|              | 3.4                | Framework Definition                                     | 16          |

|              | 3.5                | Phase Timings                                            | 24          |

|              | 3.6                | Chapter Summary                                          | 28          |

| 4            | Spli               | t-Phase Switching                                        | 29          |

|              | 4.1                | Introduction                                             | 29          |

|              | 4.2                | Resonant Split-Phase Switching                           | 31          |

|              | 4.3                | Above Resonant Split-Phase Switching                     | 46          |

|              | 4.4                | Chapter Summary                                          | 48          |

| 5            | Soft               | t-Switching Techniques                                   | <b>50</b>   |

|              | 5.1                | Introduction                                             | 50          |

|              | 5.2                | Zero-Current Switching                                   | 51          |

|              | 5.3                | Zero-Voltage Switching                                   | 52          |

|              | 5.4                | Non-linear C. Considerations                             | 50          |

|    | 5.5                   | Experimental Results                                           | 62  |

|----|-----------------------|----------------------------------------------------------------|-----|

|    | 5.6                   | Chapter Summary                                                | 70  |

| 6  | A F                   | Hybrid Switched-Capacitor Converter for Automotive Powertrains | 72  |

|    | 6.1                   | Background and Motivation                                      | 72  |

|    | 6.2                   | Interleaved-Input, Single-Inductor Dickson Converter           | 74  |

|    | 6.3                   | EMI Mitigation Techniques                                      | 80  |

|    | 6.4                   | Experimental Prototype                                         | 86  |

|    | 6.5                   | Chapter Summary                                                |     |

|    | 0.0                   |                                                                | 100 |

| 7  | Los                   | s Analysis of Hybrid Switched-Capacitor Converters             | 102 |

|    | 7.1                   | Switching Devices                                              | 102 |

|    | 7.2                   | Current and Voltage Analysis                                   | 105 |

|    | 7.3                   | Capacitors                                                     | 112 |

|    | 7.4                   | Printed Circuit Board                                          | 112 |

|    | 7.5                   | Magnetics                                                      |     |

|    | 7.6                   | Chapter Summary                                                | 115 |

| _  | $\boldsymbol{\alpha}$ |                                                                | 110 |

| 8  | Cor                   | nclusion                                                       | 116 |

|    | 8.1                   | Future Work                                                    | 116 |

|    | 8.2                   | Conclusion                                                     | 117 |

| Bi | bliog                 | graphy                                                         | 119 |

# List of Figures

| 1.1        | Control domains discussed in this thesis                                                                                                                                                                                                                    | 3  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1        | Schematic drawing of a Cockcroft-Walton voltage multiplier circuit                                                                                                                                                                                          | 5  |

| 2.2        | Schematic drawing of a Dickson charge-pump circuit                                                                                                                                                                                                          | 6  |

| 2.3        | Schematic drawing of a pure SC Dickson converter                                                                                                                                                                                                            | 6  |

| 2.4        | Schematic drawing of a hybrid stacked-ladder converter                                                                                                                                                                                                      | 7  |

| 2.5        | Schematic drawing of a hybrid Dickson converter                                                                                                                                                                                                             | 7  |

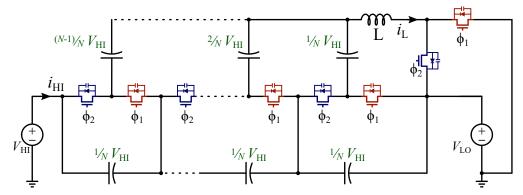

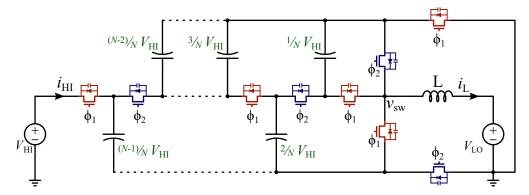

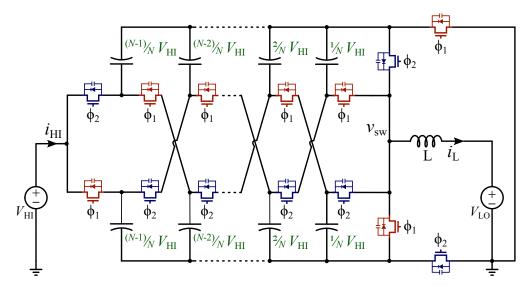

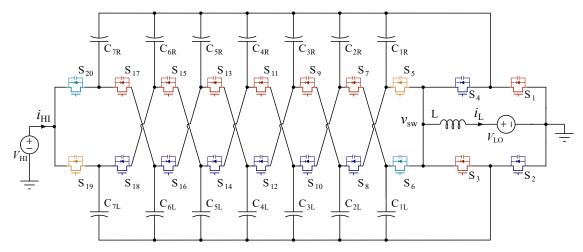

| 2.6        | Schematic drawing of an interleaved-input hybrid Dickson converter                                                                                                                                                                                          | 8  |

| 3.1        | Schematic drawings of a step-down and a step-up power converter with consistent                                                                                                                                                                             |    |

|            | analysis presented in the following chapters                                                                                                                                                                                                                | 10 |

| 3.2<br>3.3 | Example switched-inductor converter schematic drawing                                                                                                                                                                                                       | 10 |

|            | of capacitor $C_1$                                                                                                                                                                                                                                          | 11 |

| 3.4        | Effective output resistance versus frequency of an exemplary pure, resonant, and                                                                                                                                                                            |    |

|            | multi-mode hybrid SC converter [1] in the slow-switching limit frequency range.                                                                                                                                                                             | 11 |

| 3.5        | Schematic drawings of capacitor charging circuits                                                                                                                                                                                                           | 13 |

| 3.6        | Example capacitor charging waveforms corresponding to the circuits in Fig. 3.5.                                                                                                                                                                             | 13 |

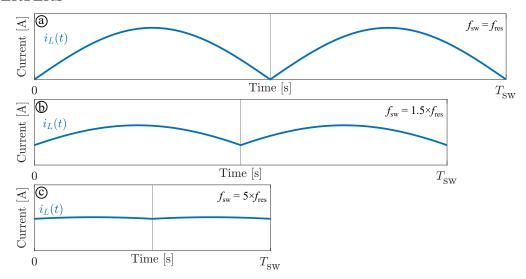

| 3.7        | Example inductor current waveforms for a hybrid SC converter operating at resonant frequency (a), slightly above resonant frequency (b) and much higher than                                                                                                |    |

|            | resonance (c)                                                                                                                                                                                                                                               | 14 |

| 3.8        | Four common $N:1$ ReSC converters with "inductor-at-the-output": (a) series-parallel, (b) flying capacitor multilevel (FCML), (c) Dickson (odd $N$ ), and (d) Fibonacci. Here $N$ refers to the conversion ratio and $N_{\rm C}$ refers to the total number |    |

|            | of capacitors.                                                                                                                                                                                                                                              | 17 |

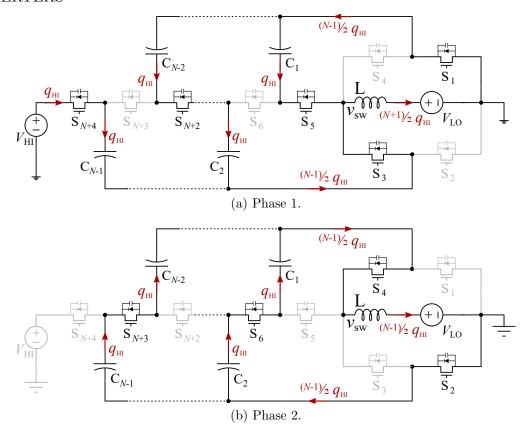

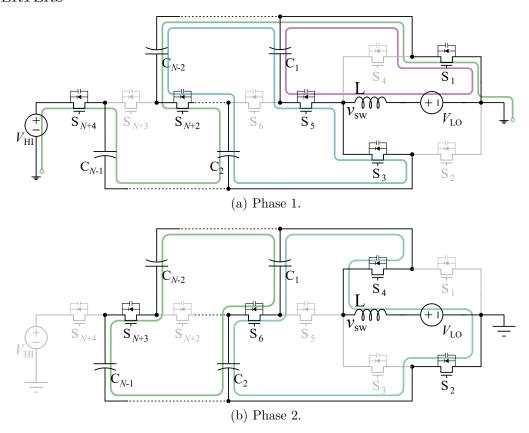

| 3.9        | Charge flow in a two-phase $N:1$ odd- $N$ Dickson converter                                                                                                                                                                                                 | 20 |

| 3.10       | KVL loops in an $N:1$ odd- $N$ Dickson converter                                                                                                                                                                                                            | 22 |

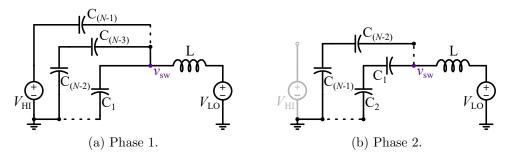

| 3.11       | Per-phase equivalent circuits for a two-phase $N:1$ odd- $N$ Dickson converter                                                                                                                                                                              | 23 |

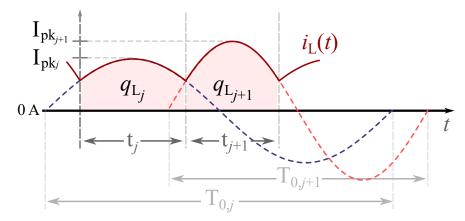

| 3.12       | Two adjacent phases of the inductor current waveform, $i_L(t)$ , operating above resonance. Each phase constitutes a symmetrically centered sinusoidal segment with angular frequency governed by $(3.25)$                                                  | 26 |

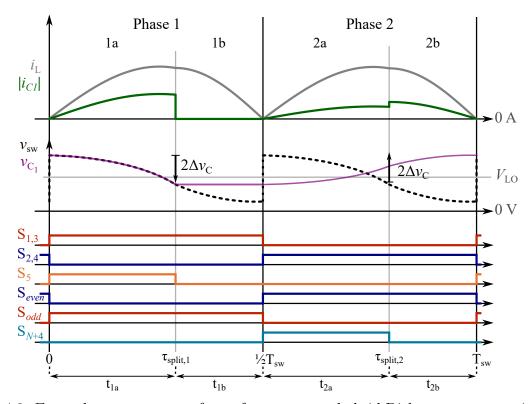

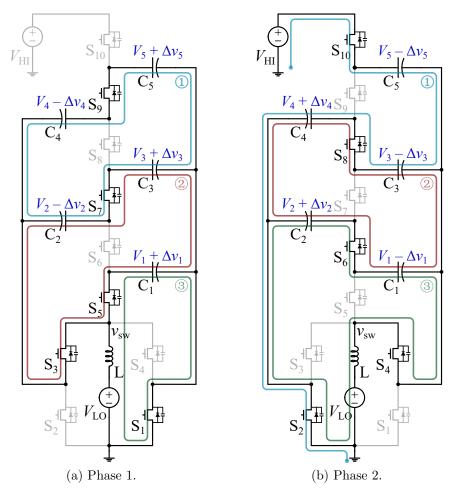

| 4.1        | Schematic drawing of a hyrbid switched-capacitor Dickson converter                                                                                                                                                                                          | 29 |

| 4.2        | Example converter waveforms for a resonant even- $N$ hybrid Dickson converter with two-phase operation. Capacitors $C_1$ and $C_{N-1}$ are hard-charged, resulting                          |            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.0        | in discontinuous capacitor voltages and high current pulses at phase transitions.                                                                                                           | 30         |

| 4.3        | Example converter waveforms for a resonant hybrid Dickson converter with split-<br>phase operation. Capacitors $C_1$ and $C_{N-1}$ are soft-charged, resulting in continu-                  |            |

|            | ous capacitor voltages and currents at phase transitions                                                                                                                                    | 31         |

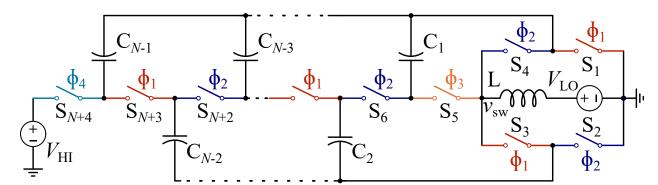

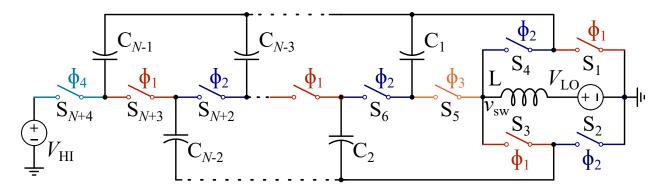

| 4.4        | Schematic drawing of an even-N Dickson converter with switches labeled with their respective control phases. Switches $S_1$ - $S_4$ are referred to as 'bridge' switches,                   |            |

|            | $S_5$ , $S_{N+4}$ as 'split-phase' switches, and $S_6$ - $S_{N+3}$ as 'string' switches                                                                                                     | 32         |

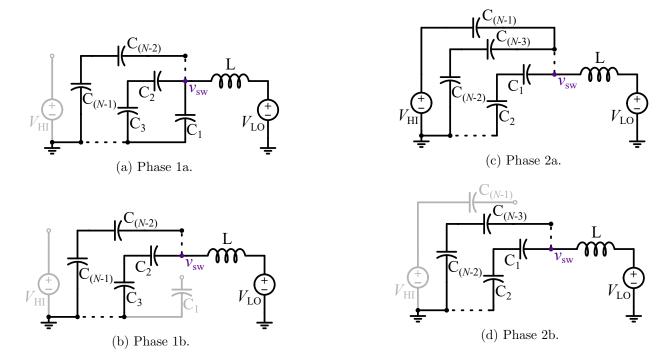

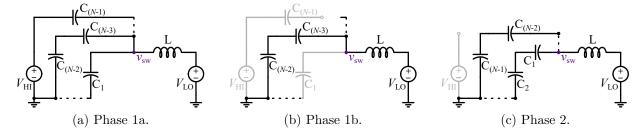

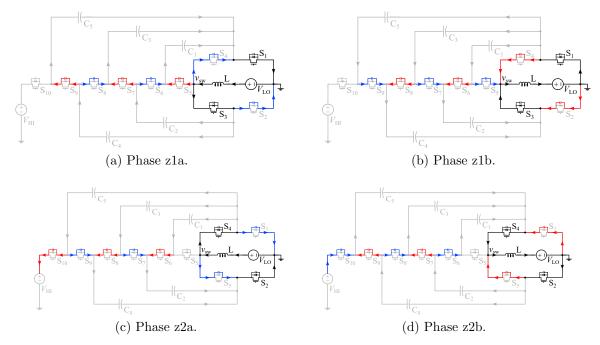

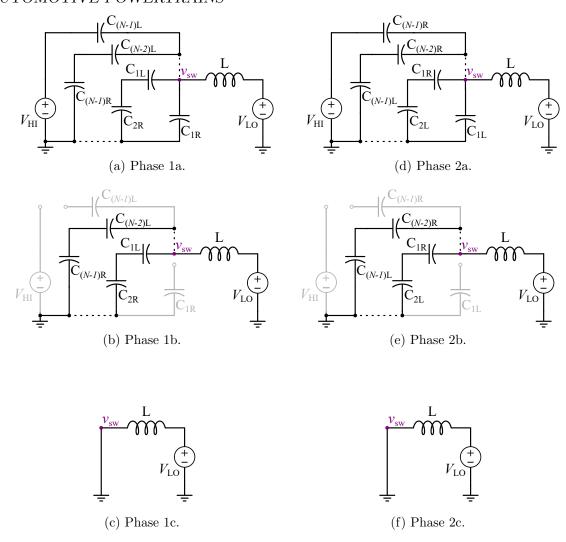

| 4.5        | Equivalent circuits for each sub-phase of an N-to-1 Dickson converter (even N), with split-phase switching as ordered a-d: Phase $1a \rightarrow Phase 1b \rightarrow Phase 2a \rightarrow$ |            |

|            | Phase 2b                                                                                                                                                                                    | 33         |

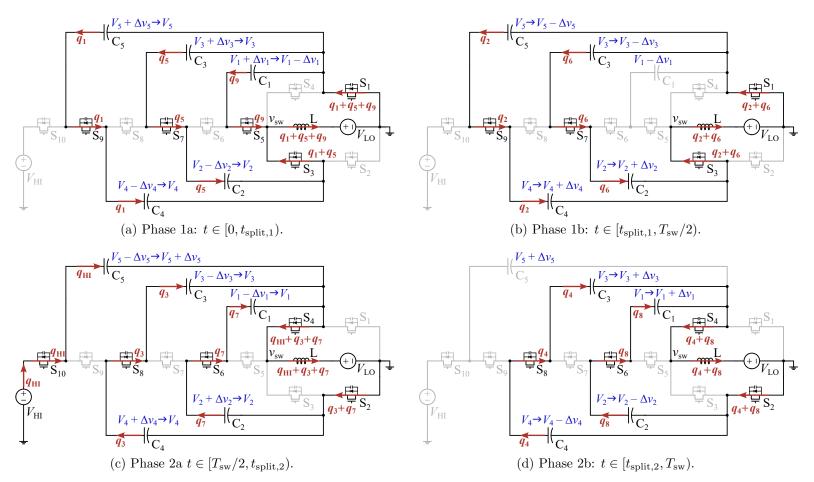

| 4.6        | Charge flow during each sub-phase of a 6:1 split-phase hybrid Dickson converter with capacitor voltages labeled for the start of Phases 1a and 1b, at the split-phase                       |            |

|            | transition, and for the end of Phases 1b and 2b                                                                                                                                             | 35         |

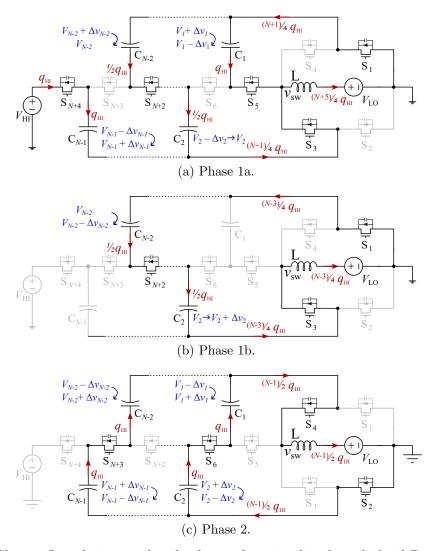

| 4.7        | Illustrated KVL loops with capacitor voltages labeled for the beginning of each                                                                                                             |            |

|            | phase. These KVL relationships are used to determine the mid-range capacitor voltages which satisfy soft-charging conditions                                                                | 38         |

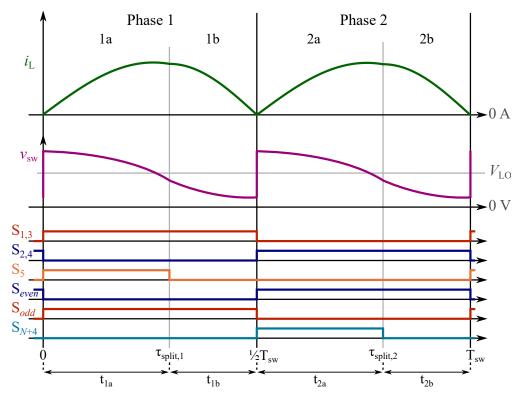

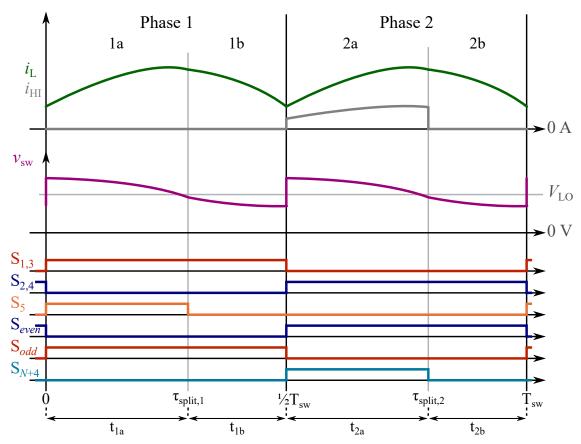

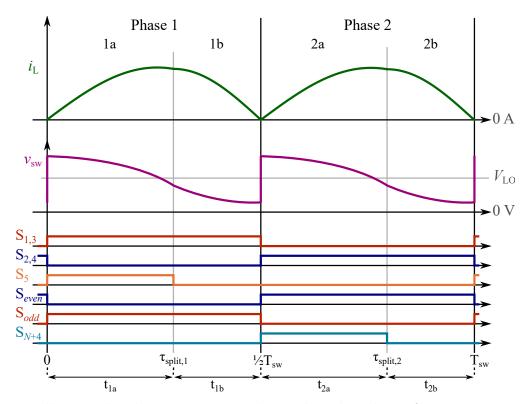

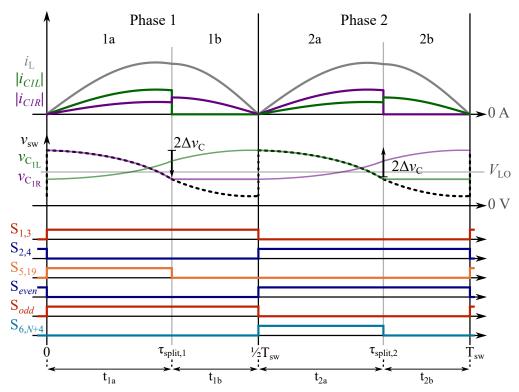

| 4.8        | Illustrated inductor current and switch-node voltage for an even-N resonant Dick-                                                                                                           | <b>J</b> C |

| 1.0        | son with split-phase control                                                                                                                                                                | 40         |

| 4.9        | Schematic drawing of an odd- $N$ Dickson converter with switches labeled with                                                                                                               |            |

|            | their respective control phases. Switches $S_1$ - $S_4$ are referred to as 'bridge' switches, $S_5$ , $S_{N+4}$ as 'split-phase' switches, and $S_6$ - $S_{N+3}$ as 'string' switches       | 42         |

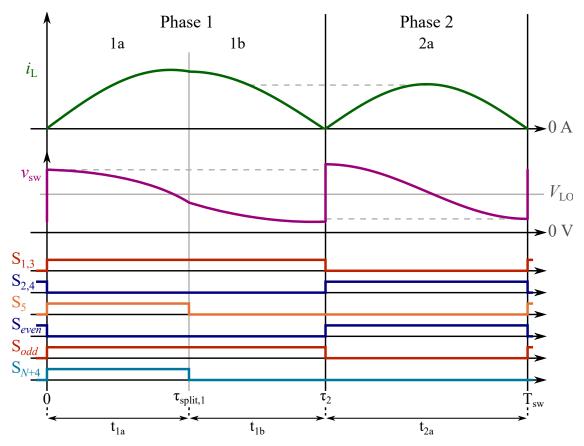

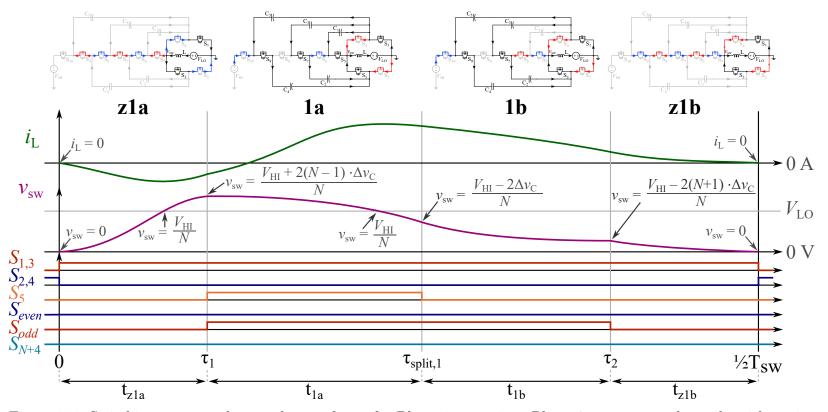

| 4.10       | Illustrated waveforms for the resonant split-phase odd- $N$ Dickson converter, show-                                                                                                        |            |

| / 11       | ing only Phase 1 requiring split-phase operation                                                                                                                                            | 43         |

| 4.11       | with split-phase switching as ordered a-c: Phase $1a \rightarrow Phase 1b \rightarrow Phase 2$                                                                                              | 43         |

| 4.12       | Charge flow during each sub-phase of a 5:1 split-phase hybrid Dickson converter                                                                                                             |            |

|            | with capacitor voltages labeled for the start of Phases 1a and 1b, at the split-phase                                                                                                       |            |

|            | transition, and for the end of Phases 1b and 2                                                                                                                                              | 44         |

| 4.13       | Illustrated waveforms for the split-phase even- $N$ Dickson converter, operating at a switching frequency above resonance                                                                   | 46         |

| 5.1        | Schematic drawing of an even- $N$ Dickson converter with switches labeled with                                                                                                              |            |

|            | their respective control phases. Switches $S_1$ - $S_4$ are referred to as 'bridge' switches,                                                                                               |            |

|            | $S_5$ , $S_{N+4}$ as 'split-phase' switches, and $S_6$ - $S_{N+3}$ as 'string' switches                                                                                                     | 51         |

| 5.2        | Illustrated inductor current and switch-node voltage for an even- $N$ resonant Dick-                                                                                                        | <b>-</b> c |

| <b>E</b> 0 | son with split-phase control                                                                                                                                                                | 52         |

| 5.3        | Circuit configurations for ZVS sub-periods showing which $C_{oss}$ capacitances are charging (blue) and discharging (red)                                                                   | 53         |

| 5.4        | Illustrative gate signals, inductor current, and switch-node voltage for a 6:1 res-                                                                                                         | Je         |

| J. I       | onant Dickson with split-phase control and ZVS                                                                                                                                              | 54         |

| 6.6  | analogously with equivalent inductor current and switch-node voltage waveforms.                                                                                | 57 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.6  | Switching states and example waveforms for Phase 2 operation                                                                                                   | 58 |

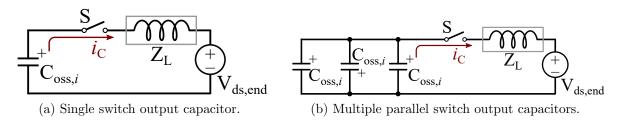

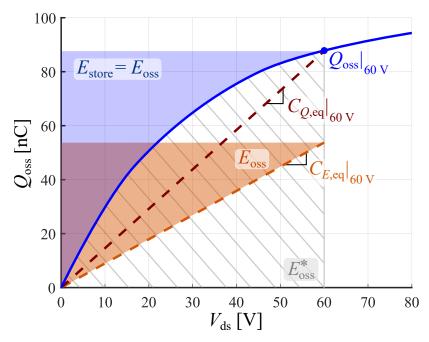

| 5.7  | Equivalent circuit diagram for switch $C_{\text{oss}}$ capacitor discharging                                                                                   | 60 |

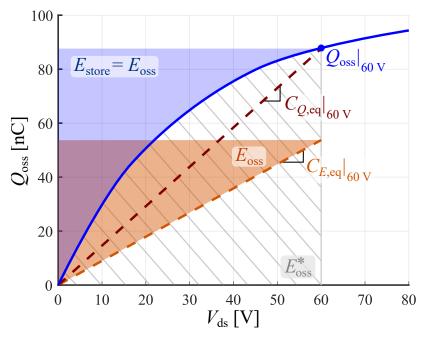

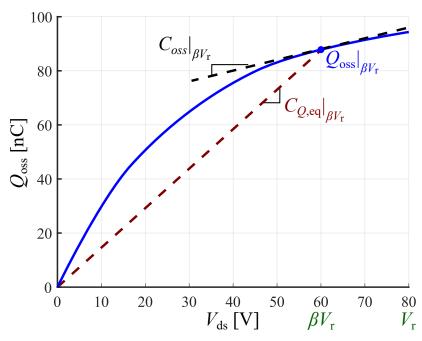

| 5.8  | Stored charge in the switch output capacitance and as a function of the blocking                                                                               |    |

|      | voltage for an example switch device. Shaded areas corresponding to stored                                                                                     |    |

|      | energy, co-energy; as well as linearized capacitances (charge-equivalent $(C_{Q,eq})$                                                                          |    |

|      | and energy-equivalent $(C_{E,eq})$ are notated                                                                                                                 | 62 |

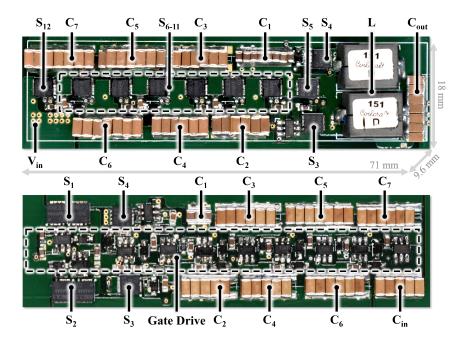

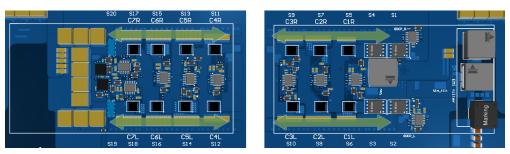

| 5.9  | Annotated photograph of an 8-to-1 48 V-input hybrid Dickson converter, mea-                                                                                    |    |

|      | suring $71 \mathrm{mm} \times 18 \mathrm{mm} \times 9.6 \mathrm{mm}$                                                                                           | 63 |

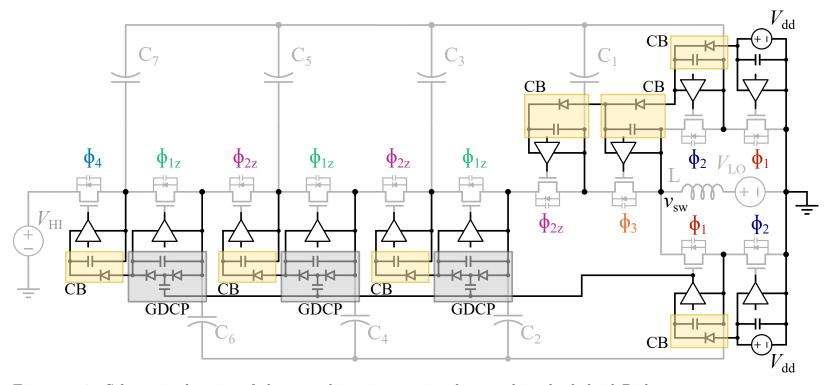

| 5.10 |                                                                                                                                                                |    |

|      | converter prototype combining Cascaded Bootstraps (yellow boxes) with Gate-                                                                                    |    |

|      | Driven Charge Pumps (grey boxes)                                                                                                                               | 64 |

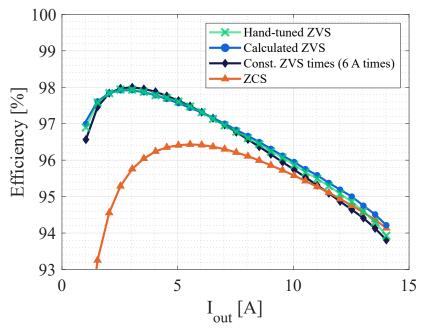

| 5.11 |                                                                                                                                                                |    |

|      | an unregulated 48 V-to-6 V hybrid Dickson converter. ZVS operation has higher                                                                                  |    |

|      | efficiency than ZVS operation a lighter load, but as conduction losses begin to                                                                                |    |

|      | dominate with increased load, ZVS operation exhibits lower efficiency                                                                                          | 66 |

| 5.12 |                                                                                                                                                                |    |

|      | put current.                                                                                                                                                   | 67 |

| 5.13 | Measured inductor current waveforms for ZCS and ZVS operation highlighting                                                                                     |    |

|      | the increased peak-to-peak ripple and increased rms of the ZVS case                                                                                            | 67 |

| 5.14 | Experimental waveforms illustrating switch drain-source and gate-source voltages                                                                               |    |

|      | demonstrating the discharging of switch output capacitance to near 0 V before                                                                                  | 00 |

| F 1F | switch turn-on.                                                                                                                                                | 68 |

| 5.15 | Measured inductor current and switch-node voltage waveforms for ZCS and ZVS                                                                                    | co |

| T 16 | Operation                                                                                                                                                      | 69 |

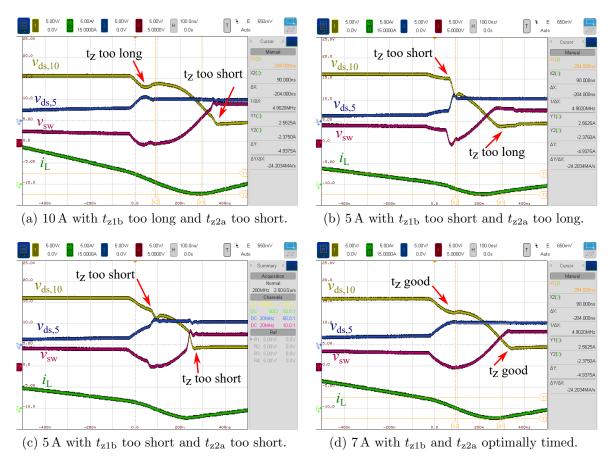

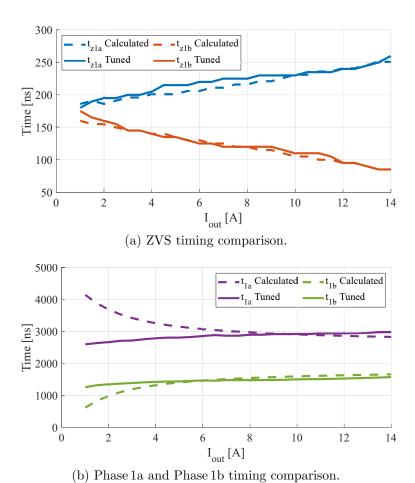

| 5.10 | Drain-source voltage measurements for switches $S_{10}$ and $S_5$ exhibiting sub-optimal ZVS phase timings and optimal phase timings for various load currents | 69 |

| 5 17 | Timing comparison of hand-tuned values to calculated time durations of the 8-                                                                                  | 09 |

| 5.17 | to-1 hybrid Dickson converter                                                                                                                                  | 71 |

|      | to-1 hybrid Dickson converter                                                                                                                                  | 11 |

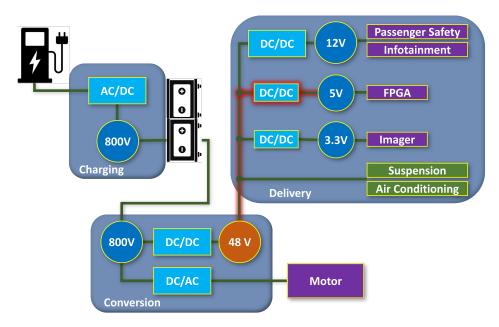

| 6.1  | Block diagram of a 48 V bus architecture for electric vehicles highlighting the                                                                                |    |

|      | power conversion stage which is the focus of this chapter                                                                                                      | 73 |

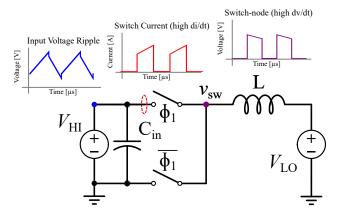

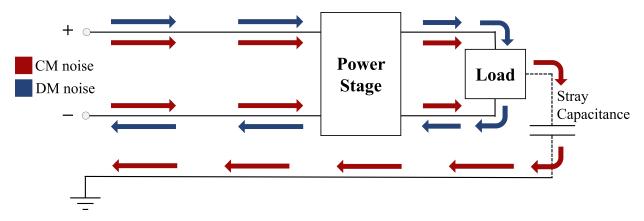

| 6.2  | Diagram illustrating sources of conducted EMI in a buck converter                                                                                              | 74 |

| 6.3  | Schematic drawing of an 8-to-1 interleaved-input Dickson-variant hybrid switched-                                                                              |    |

|      | capacitor converter                                                                                                                                            | 75 |

| 6.4  | Equivalent circuits for each sub-phase of a regulating 8-to-1 Dickson converter,                                                                               |    |

|      | with split-phase switching and regulating sequence as ordered a-f: Phase 1a $\rightarrow$                                                                      |    |

| 0.5  | Phase $1b \rightarrow Phase 1c \rightarrow Phase 2a \rightarrow Phase 2b \rightarrow Phase 2c$                                                                 | 76 |

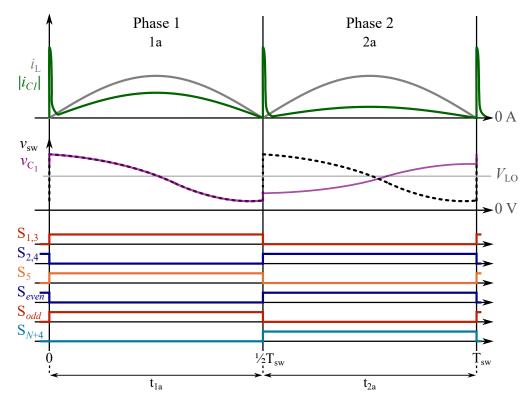

| 6.5  | Switching scheme and exemplar converter waveforms for split-phase switching of                                                                                 |    |

|      | the interleaved-input hybrid Dickson converter operating at the resonant switch-                                                                               |    |

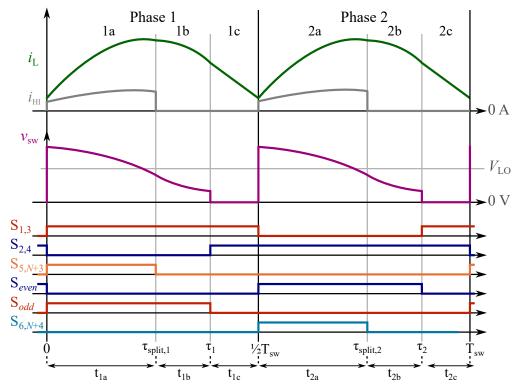

|      | ing frequency.                                                                                                                                                 | 77 |

| 6.6  | Switching scheme and exemplar converter waveforms for output voltage regula-<br>tion of the interleaved-input hybrid Dickson converter operating at a switching        |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | frequency faster than resonance                                                                                                                                        | 80  |

| 6.7  | Common Mode and Differential Mode noise paths through the system                                                                                                       | 82  |

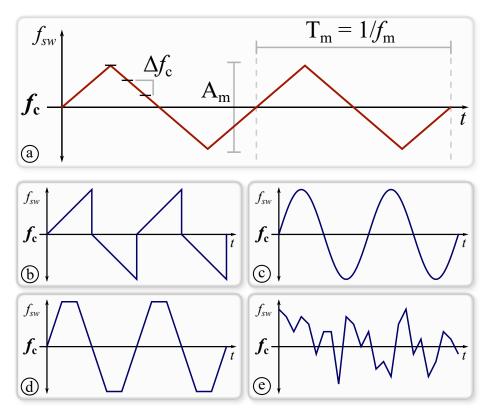

| 6.8  | Modulated switching frequency over time and key parameters for various SSFM schemes: a) triangular, b) right-triangular, c) sinusoidal, d) trapezoidal, and e)         |     |

|      | pseudo-random                                                                                                                                                          | 83  |

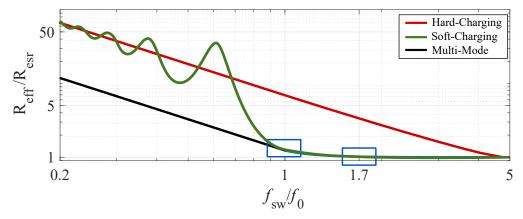

| 6.9  | Effective output resistance versus frequency of an exemplary pure, resonant, and                                                                                       |     |

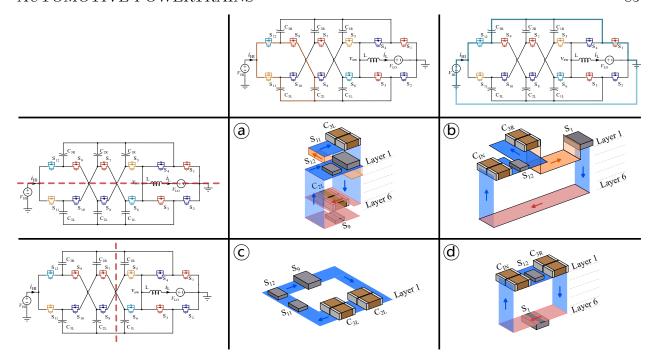

| 6.10 | Commutation loop comparison for different layout configurations of the HISID                                                                                           |     |

|      | converter.                                                                                                                                                             | 85  |

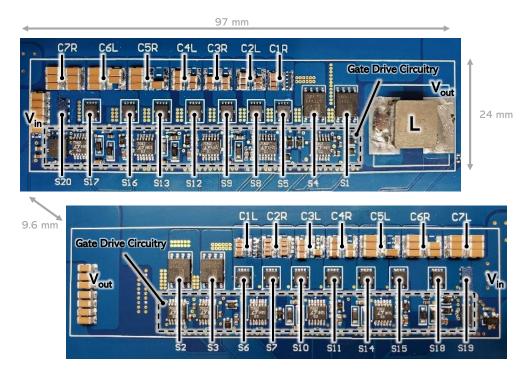

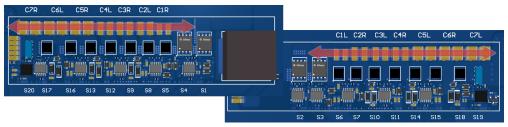

| 6.11 | Image of prototype board with key components labeled                                                                                                                   | 86  |

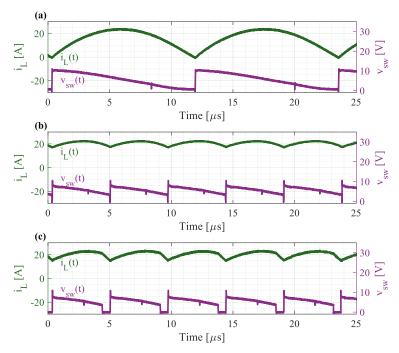

|      | (a) Resonant, (b) above resonant, and (c) regulating inductor current, $i_L$ , and switch-node voltage, $v_{sw}$ , measured waveforms for the 8-to-1 discrete hardware |     |

|      | prototype                                                                                                                                                              | 88  |

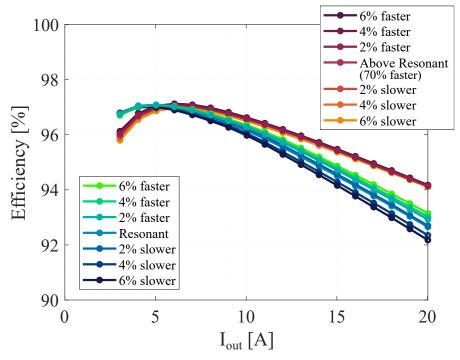

| 6.13 | Static efficiency plots for frequency bands near resonant and above-resonance                                                                                          |     |

|      | operation at 48 V input and un-regulated 6 V output                                                                                                                    | 89  |

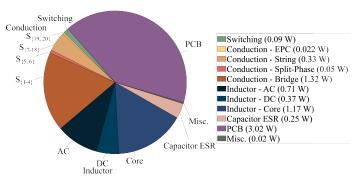

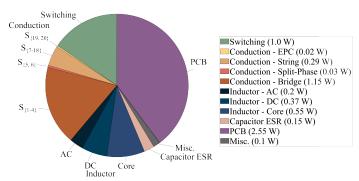

| 6.14 | Power loss breakdown for hardware prototype for at and above resonance operation.                                                                                      | 90  |

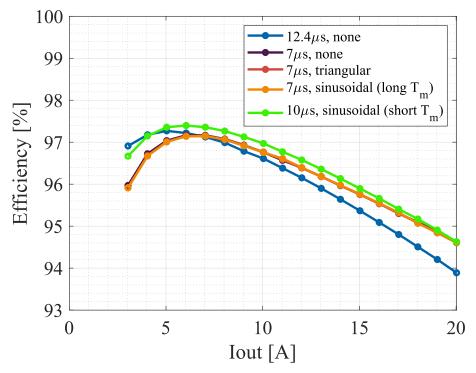

|      | Efficiency plots for 48 V input, resonant and above-resonance operation with and                                                                                       |     |

|      | without SSFM                                                                                                                                                           | 92  |

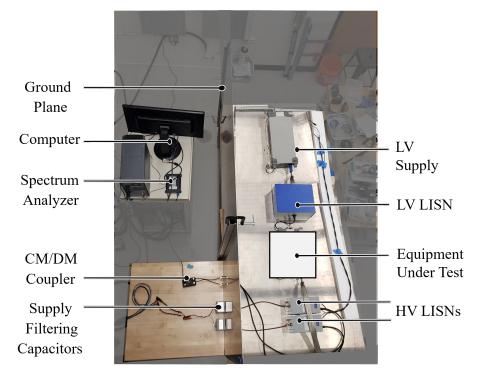

| 6.16 | In-lab pre-compliance conducted EMI measurement setup                                                                                                                  | 94  |

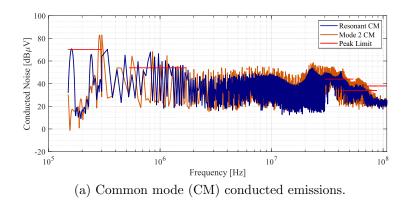

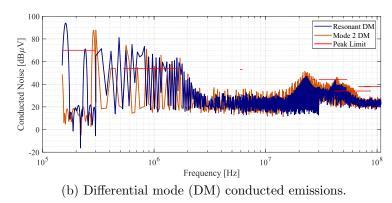

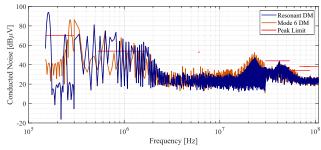

| 6.17 | Conducted emissions for 81 kHz (blue) and 143 kHz (green) with no SSFM, Modes 1 and 2, respectively, at an input voltage of 48 V, an (unregulated) output voltage      |     |

|      | of 6 V, and a load current of 20 A                                                                                                                                     | 95  |

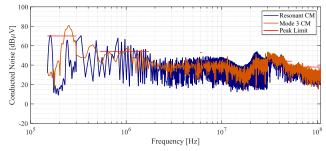

| 6.18 | Conducted emissions for 81 kHz (blue) with no SSFM and 143 kHz (green) with                                                                                            |     |

|      | triangle SSFM, Modes 1 and 3, respectively, at an input voltage of 48 V, an                                                                                            |     |

|      | (unregulated) output voltage of 6 V, and a load current of 20 A                                                                                                        | 96  |

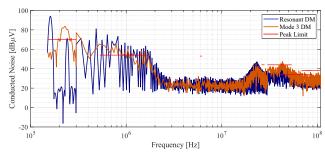

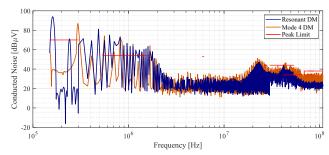

| 6.19 | Conducted emissions for 81 kHz (blue) with no SSFM and 143 kHz (green) with                                                                                            |     |

|      | sinusoidal SSFM, Modes 1 and 4, respectively, at 48 V in, and a 20 A load                                                                                              | 97  |

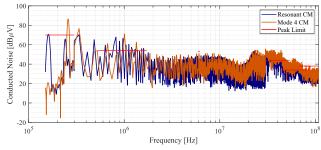

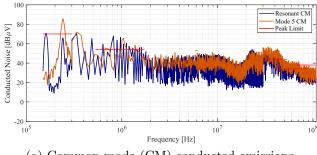

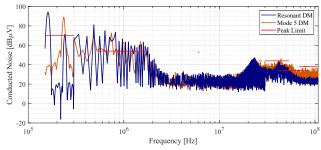

| 6.20 | Conducted emissions for 81 kHz (blue) with no SSFM and 143 kHz (green) with                                                                                            |     |

|      | sinusoidal SSFM, Modes 1 and 5, respectively, at 48 V in, and a 20 A load                                                                                              | 98  |

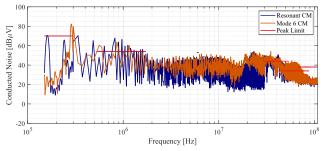

| 6.21 | Conducted emissions for 81 kHz (blue) with no SSFM and 143 kHz (green) with                                                                                            |     |

|      | right triangle SSFM, Modes 1 and 6, respectively, at $48~\mathrm{V}$ in, and a $20~\mathrm{A}$ load                                                                    | 99  |

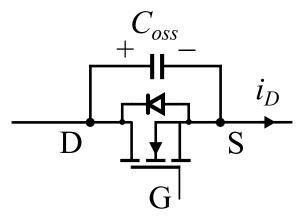

| 7.1  | Circuit diagram of an N-channel MOSFET with parasitic output capacitance,                                                                                              |     |

|      | obb, v                                                                                                                                                                 | 102 |

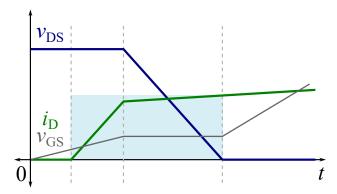

| 7.2  | Example switch gate-source voltage, drain-source voltage and drain-source current during a turn-on transition. Overlap losses are shown by the highlighted             |     |

|      |                                                                                                                                                                        | 104 |

|      | 11                                                                                                                                                                     | _   |

| 7.3 | Stored charge in the switch output capacitance as a function of the blocking                             |     |

|-----|----------------------------------------------------------------------------------------------------------|-----|

|     | voltage for an example switch device. Shaded areas corresponding to stored                               |     |

|     | energy, co-energy; as well as linearized capacitances (charge-equivalent $(C_{Q,eq})$                    |     |

|     | and energy-equivalent $(C_{E,eq})$ are notated                                                           | 109 |

| 7.4 | Stored charge in the switch output capacitance as a function of the blocking                             |     |

|     | voltage for an example switch device rated at $V_r$ . The output capacitance at the                      |     |

|     | operating voltage, $\beta V_{\rm r}$ , and the linearized charge-equivalent capacitance $(C_{Q,\rm eq})$ |     |

|     | are notated                                                                                              | 111 |

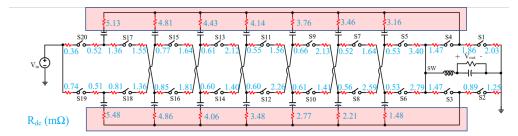

| 7.5 | Layout diagrams for a laterally symmetric HISID converter, highlighting high                             |     |

|     | impedance paths                                                                                          | 113 |

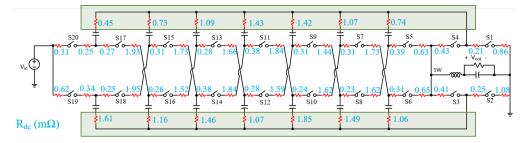

| 7.6 | Layout diagrams for a vertically symmetric HISID converter, highlighting reduced                         |     |

|     | impedance paths                                                                                          | 114 |

# List of Tables

| 3.1 | Definition of Characteristic Terms                                                                                       | 18<br>19 |

|-----|--------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1 | Time-Domain Circuit Dynamics Expressions - Phase $1/2$ even- $N$ hybrid Dickson Converter                                | 47       |

| 4.2 | Time-Domain Circuit Dynamics Expressions - Phase 1 and 2 odd- $N$ hybrid Dickson Converter                               | 48       |

| 4.3 | Comparison of phase durations for the split-phase hybrid Dickson topology between large ripple and small ripple analysis | 49       |

| 5.1 | Time-Domain Circuit Dynamics Expressions - Phase 1                                                                       | 55       |

| 5.2 | Converter Operating Parameters                                                                                           | 62       |

| 5.3 | Component Listing of the Hardware Prototype                                                                              | 65       |

| 6.1 | Survey of 48 V power converters                                                                                          | 74       |

| 6.2 | Time-Domain Circuit Dynamics Expressions - Phase 1 of even- $N$ regulating hy-                                           |          |

|     | brid converter                                                                                                           | 79       |

| 6.3 | Conducted Noise Limits for CISPR 25, Class 5 EMI Standards [2]                                                           | 81       |

| 6.4 | Component Listing of the Hardware Prototype                                                                              | 87       |

| 6.5 | Converter Operating Parameters                                                                                           | 87       |

| 6.6 | Definition of Converter Modes of Operation                                                                               | 91       |

| 6.7 | CM and DM Noise Peaks for Various Modes of Operation                                                                     | 100      |

| 7.1 | Two-Phase Odd- $N$ Dickson Maximum Switch Voltage Stress                                                                 | 108      |

| A.1 | Maximum Switch Voltage Stress (even- $N \ge 6$ )                                                                         | 135      |

| A.2 | Maximum Switch Voltage Stress (split-phase odd- $N$ Dickson)                                                             | 135      |

| A.3 | Switch Voltages for a ZVS Split-Phase Even- $N$ Dickson Converter                                                        | 136      |

### Acknowledgments

Firstly, I want to thank my research adviser, Prof. Robert Pilawa-Podgurski. His confidence in me and in my potential has been much needed encouragement over the past several years. Thank you for taking the time to be involved with my research, as well as caring about my life outside of the lab. I am very grateful for the research group he continues to grow; not only is our group made up of impressive minds, but also such fun and welcoming personalities that I am lucky enough to call friends and colleagues.

I don't believe I would be at this point without so many wonderful influences in my life. Particularly, going back to eighth grade and my math teacher, Jacque Solomon. Ms. Solomon went out of her way to challenge me, prepare me, and give me a leg up for what would eventually become a career involving lots and lots of math.

I also want to thank Dr. Prasad Enjeti at Texas A&M University for providing me with the opportunity to jump into power electronics research as an undergraduate student, and for being a proponent of my success even after graduation.

I want to thank my Dissertation Committee: Prof. Jessica Boles, Prof. Ali Niknejad, and Prof. Andrew Stillwell. I especially want to thank Andrew; without him, I would not have made it to the end of this Ph.D. I could not have asked for a better guide and mentor during my first few years of graduate school. Thank you for not only encouraging me and having confidence in my abilities, but letting me know that when I needed to hear it.

As I mentioned, the Pilawa Research Group is such an extraordinary group of individuals. I want to thank each member with whom I have had the pleasure of working and navigating research: Yicheng Zhu, Rod Bayliss III, Ting Ge, Rahul Iyer, Elisa Krause, Ivan Petric, Nate Pallo, Zichao Ye, Sophia Chou, Enver Candan, Logan Horowitz, Haifah Sambo, Zitao Liao, Yong-Long (Max) Syu, Pourya Assem, Wen-Cheun (Joseph) Liu, Nagesh Patle, Tahmid Mahbub, Nathan Biesterfeld, Jiarui Zou, Ben Liao, Marrin Nerenberg, Will Vavrik, Anya Shah, Mads Graungaard Taul, Nicole Stokowski, Amanda Jackson, Joseph Schaadt, Raya Mahony, Chris Barth, Yixuan Wu, Evan Sandoval, Yizhe Zhang, and Pei Han Ng. In addition to helping answer questions, discussing ideas, as well as helping in the lab, they have continually supported my success and have been sincere friends to me.

A special thank you to our 'Mathmania' crew: Rose Abramson, Nathan Brooks, Sam Coday, and Nathan Ellis. Doing hours of math together, while maybe not the most efficient, was definitely the most fun way to tackle power converter analysis.

I am very grateful to be in a cohort with Sam Coday, Kelly Fernandez, and Rose Abramson. Thank you for struggling with me and for helping me throughout grad school; I would not be here without your encouragement, friendship, and wisdom. I'm glad that I got to share a lab room with Kelly; it made debugging much more fun as we devolved into talking about random topics. I want to thank Sam and Rose for being such amazing friends from my first semester (at UIUC with Sam and at Berkeley with Rose). Thank you for being proponents of my success and also being such wonderful people to hangout with at and away from work. I am so proud and inspired by Sam and everything she accomplished in grad school and now will accomplish as a professor; and I am very much indebted to Rose for all

the miscellaneous help she has given me throughout the years and I can't wait to see where that knowledge takes her. I also want to thank Finn Giardine for being the best distraction. I'm so glad that your desk was near mine so we could chat about anything from actual research to random animal facts and everything in between.

My partner in crime: Sahana Krishnan. Thank you for tolerating me and being such an amazing friend. I am so lucky that you joined our group and got stuck working with me. As I always say, it's a wonder we ever got anything done together, but I wouldn't change anything. You helped me learn, grow in confidence, and got me out of the house sometimes! I can't wait to see all that you accomplish in the future and I'll be here to cheer you on like you have for me.

Finally, I want to thank my friends and family, who provide motivation and encouragement. Thank you Greg for being Greg. Thank you Dan, Dorina, and Drew for championing me throughout grad school and for letting me keep Devin. I want to especially thank Mom, Matthew, Tim, Andrew, Sabrina, and Cathy for loving me and not forgetting me even though I am several states away. Thank you for being proud of me; it is what keeps me continuing on in my studies and career. Thank you for always being there for me through everything. Also, I also want to thank Joseph, Sally, and Eliza for loving Devin and me even though we can only visit occasionally and for being so excited about anything and everything that we've been doing out in California.

Last, but certainly not least, I want to send a parking lot's worth of thanks to Devin. Thank you for your constant and never-ending support and dedication. Thank you for cooking for me so I can work late into the night trying to finish up this degree and for helping me with anything and everything programming/computer related even if you don't actually have any experience with it. Thank you for loving me with your whole heart and for always being there for me. You know I would be lost without you, so I am eternally grateful that I have found a partner in you. Since you claimed you'll read this dissertation, there's one chapter for each year so far and I can't wait to write even more with you.

## Chapter 1

## Introduction

### 1.1 Introduction

With the diversification of the power grid, including new forms of energy production (e.g., renewable energy sources) and advanced loads (e.g., electric vehicles and power-demanding data centers), advancements in power electronics are urgent. Estimates show that by 2030, almost 80% of electricity could flow through power electronics [3], either on the side of power generation or consumption. Data centers used almost 2% of all electricity in the United States in 2014 [4] and the demand is continually increasing with further developments in machine learning, data processing, and digital commerce/communication, especially as teleconferencing fully integrated into the workday. Moreover, aviation accounted for almost 2% of global emissions [5] and is expected to triple by 2050 [6]. With increased adoption of hybrid electric aircraft and electric drivetrain, forecasts expect that electricity will account for almost 45% of total transportation consumption in 2050 [5]. In additional to transportation within our atmosphere, space operations – lunar micro-grids, extraterrestrial robotics, and satellites – have also been expanding.

The feasibility of the transition to more electric transportation and of keeping up with the demand for data centers and space exploration requires small (volume or mass), reliable, and efficient power converters. One potential solution to these challenges is to utilize new circuit topologies that can allow for reduced component sizing and reduced specific component losses, such as those associated with magnetic components or switching devices. However, conventional switching strategies may not apply to these new circuit topologies or new switching schemes may need to be implemented to achieve further performance benefits over conventional solutions.

Recently hybrid switched-capacitor (hybrid SC) converters have demonstrated improvements over more conventional topologies due to their use of capacitors as the primary energy transfer elements [7–12]. Hybrid SC converters leverage the superior energy density of capacitors over magnetics [13] to achieve the high power density and efficiency needed in applications such as data center power delivery [14–18] and electric transportation [19–23].

Moreover, to mitigate the hard-charging capacitor losses present in pure switched capacitor (SC) converters, some small inductance is introduced to enable soft-charging of the flying capacitors [24, 25].

Due to their multi-level nature, hybrid SC converters can have lower switch blocking voltages and lower dv/dt at the switch nodes, allowing for the use of lower-voltage-rated, higher figure-of-merit (FOM) switches and smaller magnetic components [25]. However, though these topologies can use lower-voltage-rated switches, they often have a larger number of switching elements and, therefore, more switching instances, which may be hard-switched transitions, emphasizing the need for soft-switching techniques. Moreover, for harsh environments such as automotive or space applications, not only are component rating more constrictive, but additional converter characteristics – such as electromagnetic interference – are regulated, potentially requiring additional components or new switching schemes.

## 1.2 Organization of Thesis

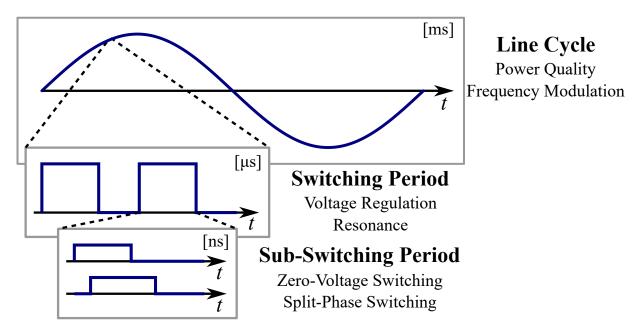

This thesis explores the implementation of varied control techniques in three domains (Fig. 1.1):

- Line cycle (ms scale)

- Switching period (µs scale)

- Sub-switching period (ns scale)

Heavy emphasis is placed on analytically describing circuit operation at sub-switching periods, specifically for split-phase and zero-voltage switching.

The remainder of this thesis is organized as follows:

Chapter 2 discusses the history and circuit topology evolution of a specific family of (hybrid) switched-capacitor (SC) converters — Dickson-based converters. The merits of Dickson-based power converters as a test-bed for exploring various switching schemes are discussed. Among resonant SC converters, the Dickson converter has some of the lowest switch stress making it a good choice for applications which require more stringent component ratings and for applications that require more complicated switching strategies that might impose additional stress on the switching devices.

To understand the various switching strategies which can further improve the performance of hybrid SC converters, first an analytical framework is presented in Chapter 3. A general method for analyzing ReSC converters based on peak energy requirements serves as a basis for investigating strategies to overcome challenges presented by hybrid SC topologies as well as to demonstrate hybrid SC converters for use in specialized applications. These switching and modulation tactics are discussed in detail in the following chapters.

The use of capacitors as primary energy storage elements in power converters does not come without additional challenges, one of which being capacitor charge-sharing losses. Using switches to connect/disconnect capacitors in various configurations can incur additional losses and generate EMI if there are large capacitor voltage differentials. Chapter 4 discusses

Figure 1.1: Control domains discussed in this thesis.

the theory behind a technique called split-phase switching in which additional switching states are introduced within a switching period to ensure that there are no voltage 'jumps' across any capacitors. Inserting these phases effectively, however, requires inspection of circuit operation and of timing analysis. Moreover, this timing analysis becomes more complicated when additional features are desired in the power converter, such as soft-switching, above-resonant operation, or frequency modulation.

Not only do some hybrid SC converters benefit from implementing split-phase switching, but additionally, techniques such as soft-switching can also improve performance by reducing losses associated with switching devices. Re-configuring a network of capacitors often requires many switching devices. While those devices may be exposed to lower voltage and current stress, they also require more switching transitions than conventional topologies. The nuances that make achieving a specific method of soft-switching — zero-voltage switching (ZVS) — more complicated for hybrid SC converters than conventional topologies are explained in Chapter 5. Additionally, experimental results of a hybrid Dickson converter achieving ZVS on every switch are shown, highlighting the efficiency benefits and validating the presented theoretical work.

Though hybrid SC converters are relatively new in terms of widespread industry/commercial adoption, there have been many demonstrations and validation of the feasibility for their use in data center applications, as one of the highest energy-consuming industries. However, other applications (e.g., automotive or space) which could benefit from the unique characteristics of hybrid SC converters have not yet caught up to data center power delivery, in part due to more constrictive design and testing requirements. Chapter 6 presents theoretical and experimental results of a hybrid SC converter, also a Dickson-derivative topology, designed

specifically for low-voltage automotive powertrain applications requiring voltage regulation. This chapter highlights the inherent benefits hybrid SC converters have for automotive environments, but also investigates areas which have yet to be answered, such as how the EMI noise profile of a hybrid SC converter with many additional switching actions looks compared to the industry-regulated limits. Different switching frequency regimes are compared for efficiency and EMI performance. Furthermore, a conventional frequency modulation strategy is applied this new hybrid SC topology demonstrating EMI reductions without efficiency penalties.

To complete the argument of how hybrid SC converters can and should be used in more application areas, Chapter 7 also briefly discusses the sources of loss in the converter and how hybrid SC topologies can have lower losses compared to conventional solutions.

Finally, this dissertation is closed out in Chapter 8 with a review of this work's contributions to power electronics as well as inviting thought into extensions of the work presented here.

## Chapter 2

## **Dickson Converter Variations**

This chapter explores the evolution of a family of pure switched-capacitor converters and hybrid switched-capacitor converters based on the Dickson charge-pump. Both conventional topologies and new topologies are discussed here as an introduction to the specific analyses presented in the following chapters.

## 2.1 Topology Evolution

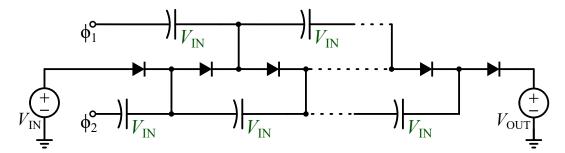

Historically, a Cockcroft-Walton voltage multiplier circuit [26] was used in discrete converters to step up low voltages to much higher voltages. The combination of switching devices and capacitors(2.1) used as intermediate voltage 'steps' are the building blocks of any switched-capacitor converter. Each capacitor blocks a fraction of the high-side voltage and therefore each diode also is only subjected to a portion of the high-side voltage – allowing for low-voltage rated parts.

In [27], a charge-pump circuit was proposed for high step-up converters as an improvement over the Cockcroft-Walton multiplier. The Dickson charge-pump, named for the proposer, is shown in Fig. 2.2 and instead of having series-connected capacitors as in the Cockcroft-Walton multiplier, the Dickson charge-pump capacitors are connected in parallel among the diodes. This adjustment in capacitor arrangement allows for easier chip-integration. Fur-

Figure 2.1: Schematic drawing of a Cockcroft-Walton voltage multiplier circuit.

Figure 2.2: Schematic drawing of a Dickson charge-pump circuit.

Figure 2.3: Schematic drawing of a pure SC Dickson converter.

thermore, the charge-pump acts similarly to a bootstrapping method, but with the capacitors connected to one of two complementary clock signals to alternately charge the capacitors and discharge them into the load. Despite the capacitors of the Dickson charge-pump needing to block higher voltages than those in the Cockcroft-Walton multiplier, the Dickson charge-pump typically has better performance especially as the conversion ratio increases [27], in part due to the requirement of lower capacitance values.

For step-down applications, the diodes can be replaced with active switching devices as shown in Fig. 2.3. Using two-quandrant devices, such as MOSFETs or GaNFETs, allows power flow from the high-side port to the low-sides port, which is prevented when diodes are used as the switching devices.

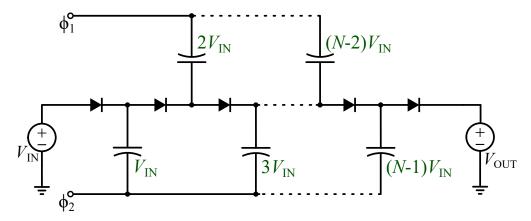

As will be described in Chapter 3, one drawback of pure switched-capacitor converters, such as the Cockcroft-Walton multiplier and Dickson charge-pump is the presence of capacitor hard-charging. To mitigate these hard-charging capacitor losses, some small inductance is introduced to enable soft-charging of the flying capacitors [24,25], forming hybrid switched-capacitor converters. Fig. 2.4 and Fig. 2.5 show hybrid versions of the Cockcroft-Walton multiplier and Dickson charge-pump, respectively. Here, a singular inductance is used to

Figure 2.4: Schematic drawing of a hybrid stacked-ladder converter.

Figure 2.5: Schematic drawing of a hybrid Dickson converter.

facilitate capacitor soft-charging, however, distributed inductors may also be used in other hybrid variations [10, 28, 29] in this family of converters.

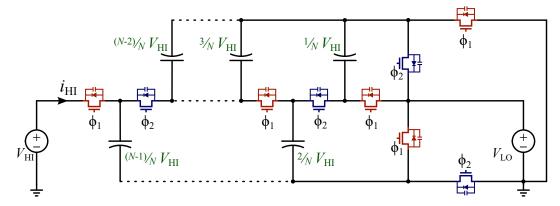

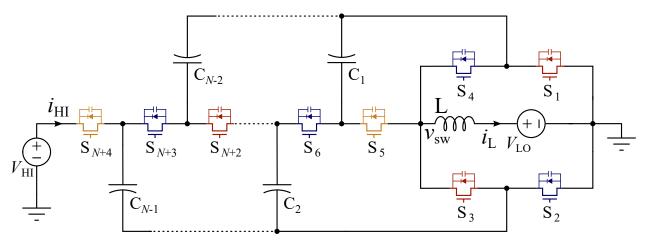

Furthermore, interleaving hybrid SC converters have shown strong performance metrics [11,18,22,30] due in part to the reduction of inductor current ripple. Specifically, [11,22, 30] are derived from Dickson/Cockcroft-Walton circuits with some redundant components eliminated.

As detailed in [12,31–34], the Dickson converter exhibits minimal total switch stress – defined as the sum across all switching elements of the peak blocking voltage times the rms current through each switch – among hybrid SC converters, making it a practical choice for applications where switching losses are significant and where soft-switching is imperative. The hybrid Dickson converter and the interleaved-input hybrid Dickson converter are used to demonstrate various switching techniques of hybrid SC converters in the following chapters.

## 2.2 Chapter Summary

This chapter describes the evolution of the Dickson-style hybrid SC converters and introduces two topologies which serve as the basis for the switching analysis and techniques described

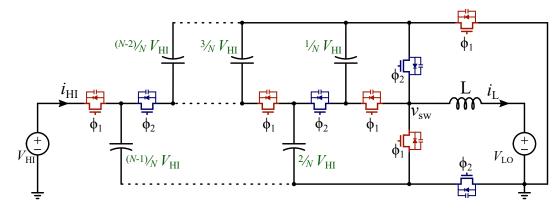

Figure 2.6: Schematic drawing of an interleaved-input hybrid Dickson converter.

in the remainder of this dissertation.

## Chapter 3

# Fundamentals of Hybrid Switched-Capacitor Converters

Fundamentals are the building blocks of fun.

Mikhail Baryshnikov

This chapter highlights the advantages of hybrid switched-capacitor (hybrid SC) converters over conventional pure switched-capacitor (SC) power converters. Then an analytical framework for comparing hybrid SC converters is presented, which will also form the basis of the analysis presented in the following chapters for various switching strategies.

### 3.1 Modeling of Power Converters

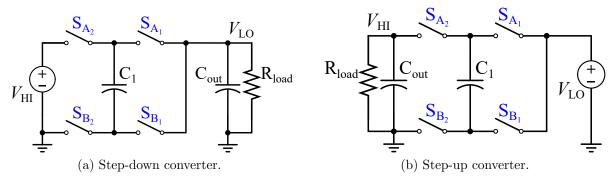

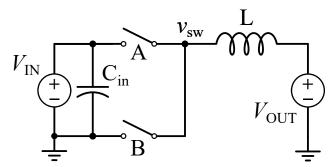

Please note that here and in the remainder of this dissertation, because the presented analysis is (mostly) consistent for both step-up and step-down operation of these power converters (Fig. 3.1), only step-down topologies will be discussed for simplicity. Remarks will be pointed out where step-up operation differs from step-down operation. Furthermore, for simplicity since the analysis here does not account for impacts of terminal capacitance on resonance and converter operation, we model both the high-side and low-side ports as ideal voltage sources, exemplified in the schematic of the conventional Buck converter in Fig. 3.2.

Figure 3.1: Schematic drawings of a step-down and a step-up power converter with consistent analysis presented in the following chapters.

Figure 3.2: Example switched-inductor converter schematic drawing.

## 3.2 Advantages of Hybrid Switched-Capacitor Converters

Capacitor-based topologies gained traction in both high-conversion-ratio dc-dc and multilevel inverter applications due to various benefits over conventional switched-inductor topologies, such as the Buck converter [35–38]. Moreover, recently, advantages in performance and size (volume and/or mass) of introducing a small inductance into capacitor-based topologies have also been demonstrated [12, 39, 40].

### Switched-Inductor and Switched-Capacitor Converters

Compared to conventional switched-inductor topologies, pure switched-capacitor (SC) converters (circuits made of only switches and capacitors) can potentially have higher power densities (i.e., smaller volume/mass for the same processed power) due to the reliance on capacitors as the primary energy storage and processing element, rather than on magnetic elements, such as an inductor, which tend to have lower energy densities [13]. Furthermore, the elimination of the inductor enables easier monolithic integration for low power applications [35–37]. Extending SC converters to high power and high voltage applications

Figure 3.3: Circuit schematic of a 2-to-1 hybrid SC converter with inductor L for soft-charging of capacitor  $C_1$ .

does present a few challenges; namely efficiency, voltage regulation, and electromagnetic interference (EMI).

### Hybrid Switched-Capacitor Converters

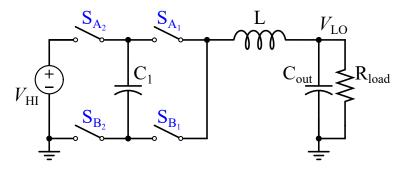

To allay the drawbacks of pure SC converters, a small (compared to conventional switched-inductor topologies) inductance can be inserted into the capacitor charging paths [24, 25, 39–41], creating a 'hybrid' converter which uses both capacitors and inductors for power processing, but still utilizes the capacitors as the primary energy element. An example 2-to-1 'hybrid' converter is illustrated in Fig. 3.3. These hybrid switched-capacitor (hybrid SC) converters can be operated in a resonant-manner to improve efficiency by reducing switching losses, or in a manner similar to that of pulse-width-modulated (PWM) converters to allow for voltage regulation and to reduce conduction losses (from reduced rms currents).

Furthermore, the added inductance helps mitigate the slow-switching limit (SSL) impedance (Fig. 3.4) [32,42] and associated pulse inrush currents in pure switched capacitor (SC) converters by enabling 'soft-charging' of the flying capacitors [24,25,41].

Figure 3.4: Effective output resistance versus frequency of an exemplary pure, resonant, and multi-mode hybrid SC converter [1] in the slow-switching limit frequency range.

### Capacitor Soft-charging

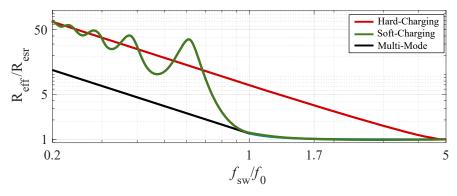

The power loss (or output-impedance) in the SSL regime is the result of charging/discharging the capacitors with either a constant voltage source or another capacitor, as illustrated in Fig. 3.5a. This capacitor charge-sharing loss contributes to both lower efficiencies but also to increased EMI, which is a significant concern in several applications such as space and automotive (Chapter 6).

Each switching state of a pure SC converter can be reduced to Fig. 3.5a (or the scenario with one capacitor replaced by a dc voltage source) [1,43]. For the sake of demonstrating the merits of 'soft-charging', capacitor  $C_1$  is assumed to start fully charged  $(V_{1,init} = V_1)$  and  $C_2$  fully discharged  $(V_{2,init} = 0)$ ; and  $C_1$  and  $C_2$  are assumed to be equal in capacitance.

When the switch closes, because the capacitor voltage cannot change instantaneously, the difference in the initial capacitor voltages is imposed across the series resistor (which may be a combination of switch on-state resistance, trace resistance, and capacitor equivalent series resistance). This voltage differential across a resistive element results in a large instantaneous current through the capacitors, Fig. 3.6, thus producing a noisy transition and termed 'hard-charging'.

The power loss associated with full charge redistribution for the RC circuit in Fig. 3.5a is related to the difference is initial energy,  $E_{\text{init}}$ , and ending energy,  $E_{\text{fin}}$ , in the system:

$$P_{\text{loss}} = f_{\text{sw}}(E_{\text{init}} - E_{\text{fin}}) = f_{\text{sw}} \left[ \left( \frac{1}{2} C_1 V_{1,init}^2 + \frac{1}{2} C_2 V_{2,init}^2 \right) - \left( \frac{1}{2} C_1 V_{1,fin}^2 + \frac{1}{2} C_2 V_{2,fin}^2 \right) \right]$$

(3.1)

$$\rightarrow P_{\rm loss,RC} = \left(\frac{1}{4}C_1V_1^2\right)f_{\rm sw} \tag{3.2}$$

This equation is valid only if the on-time duration of the switch is much larger than the time-constant of the circuit, i.e. in the SSL region of operation. Moreover, the capacitor charge-sharing loss does not depend on the value of the series resistance, but rather on the initial difference in voltage across each capacitor. In typical power converter operation, the initial capacitor voltages are dependent on loading conditions, switching frequency, and the capacitance. As load or power are increased, the charge sharing losses can increase proportionally to the *square* of the voltage differential, therefore, limiting the range of allowable voltage ripple based on efficiency [43].

If a current-limiter is placed in series with the capacitors, e.g., Fig. 3.5b, the capacitors charge/discharge linearly, limiting the power loss and generate noise. Furthermore, if instead of a dc current source, an inductor is placed in series with the charging capacitor, a similar benefit is seen. The inductor, which resists instantaneous changes in current charges the capacitor in a resonant manner Fig. 3.5c and Fig. 3.6, again avoiding current spikes. This method of capacitor charging was first termed 'soft-charging' in [24] because the capacitor voltages 'softly' reach equilibrium, without any high dv/dt or di/dt transitions.

Moreover, when soft-charged, capacitor voltage ripple may be greatly increased without incurring large SSL losses. This allows for more effective energy density utilization of the

Figure 3.5: Schematic drawings of capacitor charging circuits.

Figure 3.6: Example capacitor charging waveforms corresponding to the circuits in Fig. 3.5.

capacitors which perform most of the voltage conversion [44], while the added magnetics are subjected to reduced volt-seconds. Recent demonstrations [7–12] have considered these benefits and illustrate reductions in overall hybrid SC converter volume as compared with more traditional architectures (e.g. buck/boost).

In addition, it has been shown that resonant converters (those with inductors in series with each capacitor) and soft-charging SC converters (wherein there might only be one lumped inductance) are closely related and it is possible to use similar techniques to analyze and synthesize both types of converters [12,25,34].

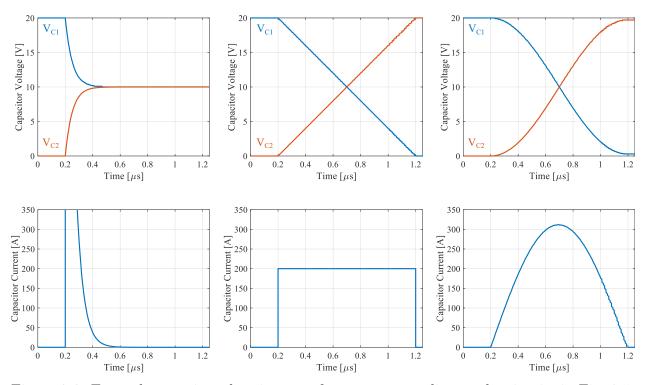

Figure 3.7: Example inductor current waveforms for a hybrid SC converter operating at resonant frequency (a), slightly above resonant frequency (b) and much higher than resonance (c).

### Operation Regimes

Hybrid switched-capacitor converters are often operated at the resonant frequency, which depends on the relationship between the effective capacitance and inductance in the conduction path. Because these topologies are made up of different configurations of L-C tanks, when the converter is operated at that resonant point, the inductor current (Fig. 3.7a) is sinusoidal in shape and returns to 0 A at the end of each switching period. Furthermore, some hybrid SC topologies can be operated above resonance (i.e., switching faster than the resonance point). Here, the inductor current does not fully resonate to 0 A, but the shape is still quasi-sinusoidal (Fig. 3.7b-c). Several use-cases and trade-offs for these different operating regimes are discussed in the remainder of this thesis, including impacts on losses, as well as on noise generation.

## 3.3 General Analysis of Hybrid Switched-Capacitor Converters

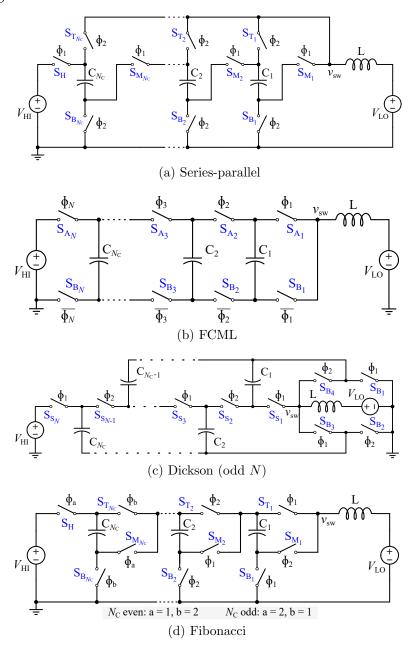

Resonant switched capacitor (ReSC) power converters (e.g., Fig. 3.8) are a relatively new class of converter topology. Prior literature has presented analytical methods to calculate both the minimum achievable passive component volume and output impedance for these types of converter; however, these analyses are often limited to ReSC converters operating exactly at resonance (e.g., [12,45]). While this operating point facilitates zero current switching (ZCS) for reduced switching loss, other work in [1,46–52] has established that operating some ReSC converters above resonance can significantly improve overall converter efficiency

through a reduction in rms currents and associated conduction losses, despite increases in relative switching loss. Although above resonance operation has been demonstrated in practice, a characteristic analysis has been lacking. The framework presented in [12] is not applicable, while a provision (parameter  $\beta$ ) in [32] characterizing the ratio of rms to dc inductor current allows the analysis to be extended to above-resonance operation without being explicitly derived.

This work therefore contributes a generalized analytical technique enabling complete characterization of ReSC operation while operating both at and above resonance. No small-ripple approximations are made, resulting in an accurate large-signal solution accounting for both voltage and current ripple on capacitors and inductors, respectively. In addition, the presented analysis is simplified with respect to [12] (which required instantaneous power integrals to be evaluated) and only requires the use of inherent topology characteristics, such as the number of components and phases, and standard charge flow vectors, similar to those described by the analytical method for pure SC converters presented in [42].

While the methodology presented here can be extended and applied to any ReSC converter topology, this work restricts its application to a subset of ReSC converters capable of operating effectively above resonance. Specifically, this work considers fixed-ratio (N:1) ReSC converter topologies with a single inductor placed in series with the low-side port, as is the case for several common example topologies depicted in Fig. 3.8. Termed "direct" in [32,53], "inductor-at-the-output" in [54], and here as "inductor-at-the-low-side-port" (to accommodate step-up 1:N variants), these structures are capable of operating both at or significantly above their nominal resonant switching frequency. When operated above resonance, the inductor enters a forward continuous conduction mode where the converter exhibits a lower sensitivity to component or timing mismatch, in addition to the aforementioned reduction in rms current.

In contrast, LC-tank type ReSC structures (e.g. [10,55–59]), termed "indirect" in [53], are constrained to at- or near- resonant operation since they either incur excessive circulating currents when operated above resonance, or hard-charging losses when operated below resonance without the introduction of discontinuous conduction states or dynamic off-time modulation [58, 60, 61].

Consequently, tank-based topologies have a susceptibility to component and timing mismatch and require either active auto-tuning control [62,63], or accurate component tolerance and stability with aging, temperature, and bias — disqualifying Class II multi-layer ceramic capacitors (MLCCs) [64] and soft-saturating magnetics.

Conversely, the switches within tank topologies generally experience favorable constant blocking voltages that are independent of load since voltage ripple is hidden within LC-tank elements [48,59] — serving to simplify design. Both "direct" and "indirect" topology variations exhibit theoretically identical total passive component volume when operated at resonance, irrespective of inductor count, when inductance is distributed accordingly [12]. However, unless a common core can be used in indirect multi-inductor designs, the magnetics of direct single inductor ReSC designs scale more favorably [65], lending further preference to direct variants. Moreover, the LC tanks within indirect topologies require bi-directional

inductor current, necessitating a  $2\times$  increase in flux density ripple,  $\Delta B$ , as compared to the uni-polar current observed in equivalent direct converters, where much of the spectral power is concentrated at dc, having implications for magnetic losses [66,67].

Following this reasoning, the subset of ReSC converters evaluated in this work (single inductor "direct" topologies) are simultaneously highly attractive and challenging to fully analyze.

Analytical expressions for peak ratings are derived for both the capacitor voltages and inductor current, aiding the practicing engineer in component selection. These expressions also permit a derivation of the minimum passive component volume, both at- and arbitrarily above- resonance. The general expressions derived herein collapse into the results presented in [12] when constrained to resonant operation, further validating this general approach. In addition, this framework is used to improve the fidelity of calculated switch stress metrics. Prior switch stress computations typically use simplified voltage and current calculations to characterize the switches, such as neglecting the effects of capacitor voltage ripple on switch voltage [12, 42, 51, 68] or neglecting the effects of inductor current ripple on switch current [12, 42].

Here we calculate the precise peak switch voltages and rms currents and demonstrate that prior simplifying assumptions can lead to significant under-sizing of switches for high-ripple designs. Moreover, while minimized passive component volume is emphasized, the presented framework assists with global optimization efforts (e.g., [69]) by providing the large-signal values and waveforms needed for accurate loss estimation.

Table 3.1 summarizes, categorizes, and highlights the limitations of several analytical approaches to SC and ReSC analysis presented in the literature. For example when assessing passive volume, [12] addresses both capacitor voltage ripple,  $\Delta v_{\rm C}$ , and inductor current ripple,  $\Delta i_L$ , for both direct and indirect topologies, strictly at resonance. However, the impact of ripple on switch stress is not considered.

### 3.4 Framework Definition

The proposed framework stems from conventional vectorized descriptions of switched capacitor converters in [25, 32, 42, 71] and is derived from fundamental charge-balance and zero volt-second principles. In addition, we assume periodic steady-state operation, with dynamic response beyond the scope of this work. Ideal circuit elements are also assumed, with no ohmic losses or parasitic effects. This assumption is valid for moderate- to heavy-load operation and where ohmic losses have minimal impact on the large-signal dynamics of a converter designed for high efficiency (e.g.  $\eta \geq 95\%$ ). Phase durations are chosen so each phase begins and ends with the same inductor current, implying zero inductor volt-seconds within each phase. This constraint is justified in [34]. Lastly, input and output bypass capacitance is assumed large with respect to the flying capacitors, thus the input and output sources can be considered ideal as is done in many existing models and analyses [9,25,32,42,48,72]. Finite input/output bypass capacitors may be included as part of a comprehensive analysis that

Figure 3.8: Four common N:1 ReSC converters with "inductor-at-the-output": (a) series-parallel, (b) flying capacitor multilevel (FCML), (c) Dickson (odd N), and (d) Fibonacci. Here N refers to the conversion ratio and  $N_{\rm C}$  refers to the total number of capacitors.

facilitates port voltage ripple constraints [73, 74], however, this adds significant analytical complexity and is omitted here for conciseness. This framework applies not only to two-phase ReSC, but also to multi-phase/multi-resonant converters—more than two phases in a switching period—such as the flying capacitor multi-level (FCML) converter in Fig. 3.8b.

|                       | Work            | Type     | Above     | Analyzes Ripple                                      |                               | Calculates |

|-----------------------|-----------------|----------|-----------|------------------------------------------------------|-------------------------------|------------|

|                       | .,,             | -J P *   | Resonance | Passives                                             | Switches                      | Loss       |

| SC                    | Seeman [42]     | _        | _         | $\Delta v_{ m C}$                                    | None                          | Yes        |

| Pure SC               | McRae [70]      | -        | -         | $\Delta v_{ m out}$                                  | $\Delta v_{ m out}$           | Yes        |

|                       | Pasternak [32]  | Direct   | Yes       | $\Delta i_L{}^*$                                     | $\Delta i_L$                  | Yes        |

| •                     | He [58]         | Indirect | _         | $\Delta v_{\rm C},  \Delta v_{\rm out},  \Delta i_L$ | None                          | Yes        |

| $\operatorname{ReSC}$ | McLaughlin [45] | Both     | No        | $\Delta i_L^*$                                       | $\Delta i_L$                  | Yes        |

|                       | Ye [12]         | Both     | No        | $\Delta v_{\rm C},\Delta i_L$                        | None                          | No         |

|                       | This Work       | Direct   | Yes       | $\Delta v_{\rm C},\Delta i_L$                        | $\Delta v_{\rm C},\Delta i_L$ | No         |

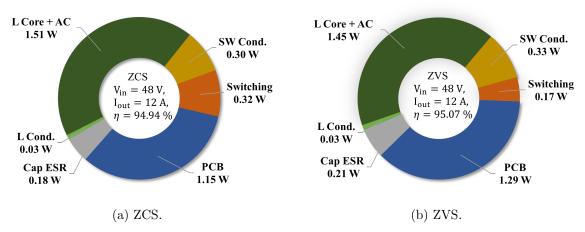

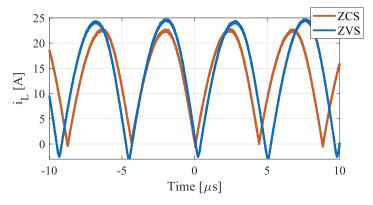

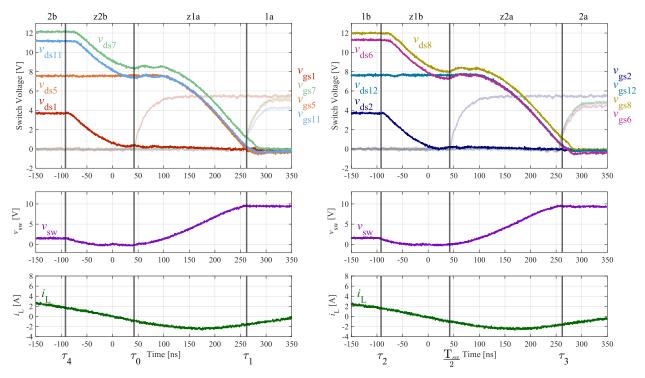

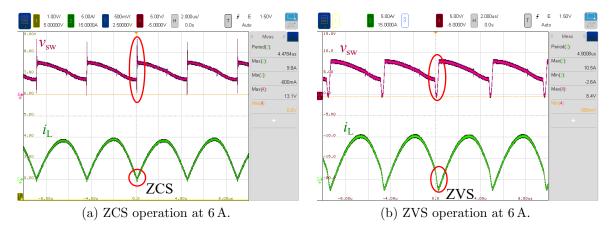

Table 3.1: Survey of Analytical Methods for Switched-Capacitor Converters