## Lawrence Berkeley National Laboratory

**LBL Publications**

## Title

A Sixteen Channel Peak Sensing ADC for Singles Spectra in the FERA Format

## Permalink

https://escholarship.org/uc/item/6qq2v893

## **Authors**

Maier, M.R. Ludewigt, B.A. Rossington, C.S. <u>et al.</u>

Publication Date

1995-10-01

# ERNEST ORLANDO LAWRENCE Berkeley National Laboratory

# A Sixteen Channel Peak Sensing ADC for Singles Spectra in the FERA Format

M.R. Maier, B.A. Ludewigt, C.S. Rossington, H. Yaver, and J.J. Zaninovich **Engineering Division**

#### DISCLAIMER

This document was prepared as an account of work sponsored by the United States Government. While this document is believed to contain correct information, neither the United States Government nor any agency thereof, nor the Regents of the University of California, nor any of their employees, makes any warranty, express or implied, or assumes any legal responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by its trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or the Regents of the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof or the Regents of the University of California.

## A Sixteen Channel Peak Sensing ADC for Singles Spectra in the FERA Format

M.R. Maier, B.A. Ludewigt, C.S. Rossington, H. Yaver, and J.J. Zaninovich

Engineering Division Ernest Orlando Lawrence Berkeley Laboratory University of California Berkeley, California 94720

October 1995

This work was supported by the Laboratory Directed Research and Development Program of Ernest Orlando Lawrence Berkeley National Laboratory under the U.S. Department of Energy, Contract No. DE-ACO3-76SF00098, and a grant from NIH, RR10748.

### A Sixteen Channel Peak Sensing ADC for Singles Spectra in the FERA Format

M. R. Maier, B. Ludewigt, C. Rossington, H. Yaver and J. Zaninovich

Engineering Division, Lawrence Berkeley Laboratory University of California, Berkeley, California 94720

#### ABSTRACT

To read out multi-element small X-ray detectors for X-ray fluorescence applications with synchrotron radiation one needs the capability to record multiple singles spectra for each detector element at high rates. We have developed a sixteen channel 11 bit peak sensing ADC in a CAMAC module. We use the FERA readout bus to place the data into a commercially available histogramming module developed to generate multiple histograms from FERA ADCs. The sixteen channels digitize shaped pulses from the detectors without external gating. The digitizing time is 8 µsec, the peak acquisition time is  $\geq 2 \mu sec$ . The module contains a LIFO to permit block transfers in order to minimize dead times associated with the readout. There is a common-CAMAC controlled analog threshold for noise suppression and a 16 bit mask to enable or disable individual ADCs. Differential non linearity is less than +8% / -4%. A  $\gamma$ -ray spectrum collected using this ADC is presented.

#### I. INTRODUCTION

At LBL a 64 element linear silicon detector is used to record spectra in a dispersive spectrometer for X-ray fluorescence work with synchrotron radiation. In this application one wants to accumulate amplitude histograms (spectra) for each of the elements at rates as high as possible. Each detector element signal is processed in a standard spectroscopy chain: a charge sensitive preamplifier followed by a shaping amplifier and an ADC. 16 preamplifiers and shapers have been placed in an analog integrated circuit (IC). This leaves the task of building peak sensing ADCs to digitize the signals. Commercially available multi-channel ADCs are not designed to digitize asynchronous signals from their inputs, they require a gating signal which triggers all channels at the same time. Since the signals from our detector are random we have to provide one ADC per input with the proper "self trigger".

#### II. ELECTRONICS

We have chosen a 16 bit sampling ADC IC (Burr Brown ADS 7805) using only the most significant 11 bits. We combined it with a peak detector and placed this circuit on 16 small daughter boards with a size of 53x39mm<sup>2</sup>. These boards are then plugged into a CAMAC mother board which holds the logic for control, setup, and readout. Because of the high rate requirements we have chosen the FERA readout [1].

Commercial histograming memories for this standard are available in CAMAC which are designed to accumulate histograms from FERA bus data. These histograms can be read through CAMAC. We provide also a LIFO on the motherboard for intermediate storage. This allows the transfer of the data to the histogramming memory in 16 word blocks minimizing the dead time associated with reading out of the data. Within the processing time of one ADC (10  $\mu$ sec) 100 digitized data words can be read neglecting the overhead associated with block transfer. Therefore, with this arrangement six of these modules (each producing 16 words or 96 total in 10  $\mu$ sec) can be connected to one histogramming memory of the proper size (>96 times 2k = 192k words) without slowing down the data collection since the reading takes 96 times 100 nsec or 9.6  $\mu$ sec.

#### III. DESIGN

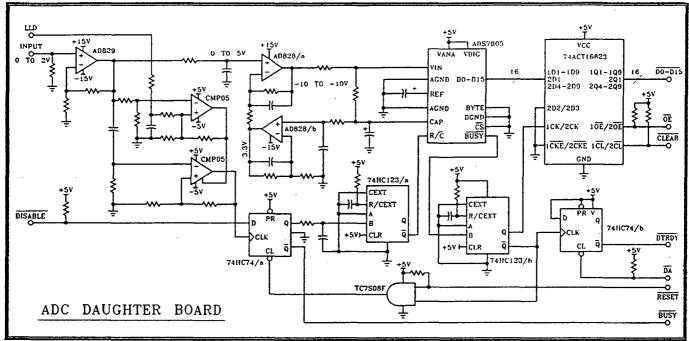

The schematic of a daughter board is given in fig 1. The input signal is amplified by a factor of 2.5 and limited to a range of 0 to 5V in the first stage. This is followed by a peak detector similar to the one proposed in ref.[2]. In this method the signal is fed through a RC integrator to the ADC and a RC differentiator to a zero cross comparator. The output of the RC integrator is amplified by a factor of 4 and level shifted so that the signal falls within the input range of the ADS 7508 i.e. -10V to +10V. The zero cross discriminator output changes state at the peak of the integrated pulse going to the ADC. The signal there triggers a BUSY flipflop which starts the ADC IC. At the end of the ADC-busy signal the ADC data are transferred into an output register and a DATA-READY signal is set. At this time the ADC can start another conversion cycle, therefore the BUSY flipflop is cleared. The logic on the motherboard then has to read the output register before the next signal has been digitized.

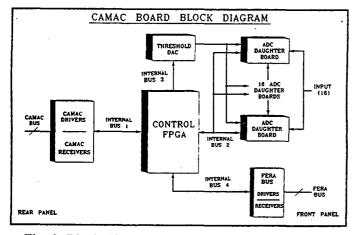

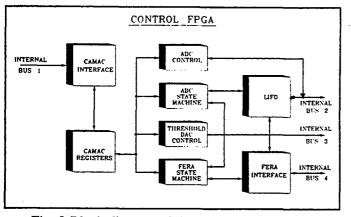

The block diagram of the CAMAC board design is shown in fig.2. The 16 ADC daughterboards are connected to the field programmable gate array (FPGA) that controls the digitizing, the control, and the readout by a bus that carries the data and separate lines for the control signals. The connection to the CAMAC and FERA busses is achieved with the appropriate line driver ICs. There is also a DAC which controls the trigger threshold for the ADCs. The schematic of the control FPGA is shown in fig.3. which shows the different state machines that accomplish the different functions. Details of the logic will be published in a separate paper.

1

Fig. 1. ADC Daughter Board Schematic

Fig. 2. Block Diagram of the CAMAC module design

Fig. 3 Block diagram of the control FPGA design

#### **IV. RESULTS**

Tests with early daughter board prototypes have shown the following results: Peak acquisition time is  $1.5 \ \mu sec$ , digitizing time is  $8 \ \mu sec$ .

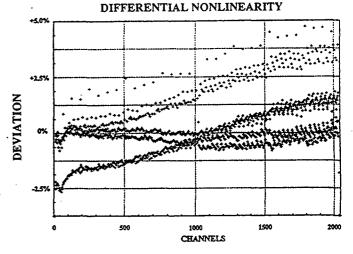

At a peaking time of the input signal of 2 µsec the boards trigger at <0.3% of full scale in the prototype version. Differential non linearity is +8% / -4%. We show a test of the differential nonlinearity using a ramp pulser. 0% corresponds to 1.6 million counts per channel in fig. 4.

Fig. 4.Plot of the differential nonlinearity of a prototype ADC daughter board obtained with a ramp pulser. 0% corresponds to 1.6 million counts per channel. The integral nonlinearity of the pulser contributed to the slope of the curve.

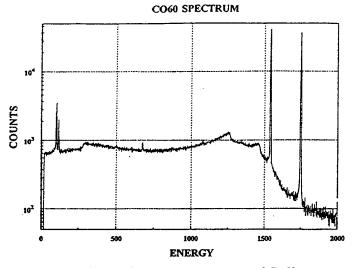

In fig. 5 we show a spectrum of a Co60 source taken with a 75% Germanium detector. The resolution at the 1333 keV line is about 2.7 keV FWHM.

Fig. 5 Germanium detector spectrum of Co60

The experimenters have requested recently that the ADC be able to digitize pulses with shorter peaking times. This requires the use of a separate sample and hold I.C. We have designed a version of this "improved" circuit. Preliminary tests of a breadboard version of this variant show that it can digitize pulses with 250 nsec peaking time. In that design we have also included a base line restorer [3].

#### V. CONCLUSION

In summary, we have built a module which allows the accumulation of multiple singles spectra at high speed. This is a function which is needed, but is not yet commercially available, for new multi-element detectors used in X-ray applications at the new high intensity synchrotron radiation facilities. This is achieved using commercial hardware and software wherever possible. Results from an initial  $\gamma$ -ray spectrum show resolutions comparable to commercial spectroscopy ADCs.

#### VI.ACKNOWLEDGMENTS

This work was supported by the Lawrence Berkeley Laboratory's Engineering Division of the U.S.. Department of Energy under Contract No. DE-AC03-76SF00098.

Reference to a company or product name does not imply approval or recommendation of the product by the University of California or the U.S. Department of Energy to the exclusion of others that may be suitable.

#### **VII. REFERENCES**

- [1] FERA is a Trademark registered by LeCroy, see Manual of the LeCroy 4300 Module

- [2] G. P. Westphal, NIM. 115 (1974) 509

- [3] L. B. Robinson, Rev. Sci. Instr. 32 (1961) 1057

Grnest Orlando Lawrence Berkeley National Laboratory One Gyglotron Road # Berkeley, Gaufornia 94720

Prepared for the U.S. Department of Duergy under Contract No. DB-ACOB-765100093