# **UC Santa Barbara**

# **UC Santa Barbara Electronic Theses and Dissertations**

### **Title**

III-V  $In_{x}Ga_1{-x}As / InP MOS-HEMTs$  for 100-340GHz Communications Systems

#### **Permalink**

https://escholarship.org/uc/item/6st812pb

#### **Author**

Markman, Brian David

# **Publication Date**

2020

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA

#### Santa Barbara

# III-V In<sub>x</sub>Ga<sub>1-x</sub>As / InP MOS-HEMTs for 100-340GHz

# **Communications Systems**

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

**Electrical and Computer Engineering**

by

Brian David Markman

# Committee in charge:

Professor Mark J. W. Rodwell, Chair

Professor Umesh K. Mishra

Professor Jonathan Klamkin

Professor Jim Buckwalter

September 2020

| The dissertation of Brian David Markman is approved. |

|------------------------------------------------------|

| Professor Umesh K. Mishra                            |

| Professor Jonathan Klamkin                           |

| Professor Jim Buckwalter                             |

|                                                      |

Professor Mark J. W. Rodwell, Committee Chair

August 2020

III-V  $In_xGa_{1\text{-}x}As\ /\ InP\ MOS\text{-}HEMTs$  for 100-340GHz Communications Systems

Copyright © 2020

by

Brian David Markman

#### ACKNOWLEDGEMENTS

I cannot begin to express my gratitude to all the people who have helped me in my journey here at UCSB. I certainly would like to thank my advisor, Professor Mark Rodwell, for his support and guidance. Mark's enthusiasm and knowledge for semiconductor physics, devices, and fabrication is unmatched. His knowledge of circuits and electronic systems, despite never fully rubbing off on me, gave me the confidence to know that the devices we make will be impactful for circuit designers and consumers. I would also like to thank my committee members: Professor Umesh Mishra, Professor Jonathan Klamkin, and Professor Jim Buckwalter for the time, effort, patience, and insight into my work.

Before I began my Ph.D., in the summer of 2014, I worked as an intern with Prateek Choudhary and Rob Mauer and fell in love with III-V semiconductors and Santa Barbara. I owe them both a tremendous thank you for setting me on the path that I am now following. I would like to thank the NNIN program specifically and people like Wendy Ibsen who work very hard to give undergraduates research experience. Without REU programs, I likely never would have gone to graduate school and am extremely thankful for the experience. Beyond that, I am especially thankful to have had the opportunity to return the favor and set other undergraduate students on their own research course. I have been a mentor every summer of my graduate experience and would like to thank all Rodwell Group interns for helping me learn by teaching.

I owe a *TREMENDOUS* debt of gratitude to Brian Thibeault, Bill Mitchell, and Tom Reynolds for helping me learn semiconductor processing. While most graduate students benefit from institutional knowledge passed down by senior group members, I unfortunately

had to learn from scratch, often by nagging the Nanofab staff. Brian, Bill, and Tom took the time to teach me how to design and execute experiments and then went even further and helped me analyze data, draw conclusions, and determine future direction based on those results. Without their help, none of this work would have been possible. Finally, I would like to thank all the cleanroom staff: Demis John, Aidan Hopkins, Biljana Stamenic, Don Freeborn, Brian Lingg, Tony Bosch, Lee Sawyer, Ning Cao, Mike Silva, Mike Day, Luis Zuzunaga, and Tino Sy. At some point I broke one of your tools or complained that somebody else had. Thank you all for being so approachable and helpful. I firmly believe that the excellence of the UCSB Nanofab begins and ends with the people who operate it.

In addition to the staff, I would also like to thank all the people that work in the cleanroom. Everybody has been extremely friendly and helpful. Thankfully, I rarely had to develop entirely new processes because somebody in the cleanroom already had and was happy to share data and insight. Without such a wonderful community of users, I cannot imagine having achieved anything during my Ph.D. Specifically I would like to thank Atiquzzaman, Matt Jacob-Mitos, Paula Hue, Sean Demura, Alfredo Torres, Alex Spott, Yahya Mohtashami, and Brian Romanczyk – thank you all for tolerating my questions with a smile and helping pass the time during resist bakes and pump downs. Beyond the cleanroom, I would like to thank the Rodwell group members: Rob Mauer, Hsin-Ying Tseng, Yihao Fang, Ahmed Sayed, Utku Soylu, Ali Farid, Logan Whitaker, Arda Simsek, and Hai Yu. I am immensely grateful for the many conversations ranging from beer drinking to circuit design. Thank you all for poking holes in my crazy ideas and helping me understand what circuit designers want from their transistors. I must thank Aranya Goswami and Simoné Tommaso Šuran Brunelli for all their hard work and contribution to my research. We struggled together to get CELO working and

then struggled some more to tease any information out of it. When I transitioned onto the HEMT process, I was fortunate that the team loosely stayed together. Without Simoné's enthusiasm to grow structures that all epi-vendors scoffed at or Aranya's incredible talent on the TEM, this thesis would end after the introduction. Thank you both for being fantastic coworkers and friends.

In my personal life, there are far too many people for me to properly express my gratitude. Thank you to the Storke Ranch crew, the M. Special College Night crew, the UCSB Cycling team, Shoop Squad, the Cavs, the Royals, the Atomic Bombs, the Endless Summer crew, and so many more. Thank you all for making my time in Santa Barbara, especially my time away from work, fun and memorable.

Finally, I would like to thank my family for their unconditional love and support. Regardless of what I wanted to do throughout life, my parents would always respond with a smile and, "Do it. How can we help?" I owe much of my success and happiness to the lessons they taught me and the passion that they both expressed for their profession. I absolutely cannot even begin to express my gratitude for their unconditional love and support. Last, I would like to thank my girlfriend, Monica. Your love and support have gotten me through countless long days and stressful months. Without your big smile, loud laugh, and adventurous spirit, I could never have made it here. Thank you all for being a part of my life and supporting me in my efforts to make super-tiny, super-low power and super-tiny, super-fast switches.

### VITA OF BRIAN DAVID MARKMAN AUGUST 2020

#### **PERSONAL**

| May 1993 | Born in Dresher, Pennsylvania, USA | ١. |

|----------|------------------------------------|----|

|          |                                    |    |

#### **EDUCATION**

| 2020 | Ph.D. in Electrical and Computer Engineering, University of |

|------|-------------------------------------------------------------|

|      | California, Santa Barbara.                                  |

| 2016 | M.S. in Electrical and Computer Engineering, University of  |

|      | California, Santa Barbara.                                  |

| 2015 | B.S. in Materials Science & Engineering, Pennsylvania State |

|      | University, Schreyer Honors College                         |

#### **PUBLICATIONS**

- [1] **Brian Markman**, Simone Tommaso Šuran Brunelli, Matthew Guidry, and Mark Rodwell. " $L_g = 40$ nm Composite Channel MOS-HEMT Exhibiting  $f_{\tau} = 420$  GHz,  $f_{max} = 562$  GHz," Manuscript Submitted for Publication in IEEE IEDM 2020.

- [2] Aranya Goswami, Simone Tommaso Šuran Brunelli, **Brian Markman**, Aidan Taylor, Hsin-Ying Tseng, Kunal Mukherjee, Mark Rodwell, Jonathan Klamkin, Chris Palmstrøm. "Controlling facets and defects of InP nanostructures in confined epitaxial lateral overgrowth," Manuscript Submitted for Publication in Physical Review Materials 2020.

- [3] **Brian Markman**, Simone Tommaso Šuran Brunelli, Aranya Goswami, Matthew Guidry, and Mark Rodwell. " $In_{0.53}Ga_{0.47}As$  / InAs Composite Channel MOS-HEMT Exhibiting 511 GHz  $f_{\tau}$  and 256 GHz  $f_{max}$ ," IEEE Journal of Electron Devices, 2020.

- [4] Aranya Goswami, Simone Tommaso Šuran Brunelli, **Brian Markman**, Dan Pennachio, Hsin-Ying Tseng, Sukgeun Choi, Aidan Taylor, Jonathan Klamkin, Mark Rodwell, and Chris Palmstrom. "Effects of growth parameters on faceting and defects in confined epitaxial lateral overgrowth," Bulletin of the American Physical Society, vol. 65, no. 1, 2020.

- [5] Simone Tommaso Šuran Brunelli, Aranya Goswami, **Brian Markman**, Hsin-Ying Tseng, Mark Rodwell, Chris Palmstrøm, and Jonathan Klamkin. "Horizontal Heterojunction Integration via Template Assisted Selective Epitaxy," Crystal Growth & Design, vol. 19, no. 12, pp. 7030-7035, 2019

- [6] Jonathan P Sculley, **Brian Markman**, Utku Soylu, Yihao Fang, Miguel E Urteaga, Andy D Carter, Mark JW Rodwell, and Paul D Yoder. "*Monte Carlo Investigation of Traveling Accumulation Layers in InP Heterojunction Bipolar Transistor Power Amplifiers*," 2019 IEEE BiCMOS and Compound semiconductor Integrated Circuits and Technology Symposium (BCICTS), Nashville, TN, USA, pp. 1-4, 2019.

- [7] Joon Sue Lee, Sukgeun Choi, Mihir Pendharkar, Daniel J Pennachio, **Brian** Markman, Michael Seas, Sebastian Koelling, Marcel A Verheijen, Lucas Casparis, Karl D Petersson, Ivana Petkovic, Vanessa Schaller, Mark JW Rodwell, Charles M

- Marcus, Peter Krogstrup, Leo P Kouwenhoven, Erik PAM Bakkers, and Chris J Palmstrøm. "Selective-area chemical beam epitaxy of in-plane InAs one-dimensional channels grown on InP (001), InP (111) B, and InP (011) surfaces," Physical Review Materials 3, 084606, 2019.

- [8] **Brian Markman**\*, Simone Tommaso Šuran Brunelli\*, Aranya Goswami, Hsin-Ying Tseng, Sukgeun Choi, Chris Palmstrøm, Mark Rodwell, and Jonathan Klamkin. "Selective and confined epitaxial growth development for novel nano-scale electronic and photonic device structures," Journal of Applied Physics 126, 015703, 2019.

- [9] Jonathan P Sculley, Yihao Fang, **Brian Markman**, Miguel Urteaga, Andrew Carter, Mark Rodwell, and Douglas Yoder. "First Principles Study of Collector Transit Time Modulation in Double Heterojunction Bipolar Transistors," 2019 IEEE Device Research Conference, Ann Arbor, MI, USA, pp. 105-106, 2019.

- [10] Miguel Urteaga, Andrew Carter, Yihao Fang, **Brian Markman**, Mark Rodwell, Jonathan Sculley, and Douglas Yoder. "Development of a High Power Density Millimeter-Wave InP HBT Technology," 2019.

- [11] Mark Rodwell, Yihao Fang, Johann Rode, Jun Wu, **Brian Markman**, Simone Tommaso Šuran Brunelli, Jonathan Klamkin, and Miguel Urteaga. "100-340GHz Systems: Transistors and Applications," 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, pp. 14.3.1-14.3.4, 2018.

- [12] Jun Wu, Yihao Fang, **Brian Markman**, Hsin-Ying Tseng, and Mark JW Rodwell. " $L_g = 30 \text{ nm InAs Channel MOSFETs Exhibiting } f_{max} = 410 \text{ GHz and } f_t = 357 \text{ GHz}$ ," IEEE Electron Device Letters, vol. 39, no. 4, pp. 472-475, April 2018.

- [13] Mattia Cattelan, **Brian Markman**, Giacomo Lucchini, Pranab Kumar Das, Ivana Vobornik, Joshua Alexander Robinson, Stefano Agnoli, and Gaetano Granozzi. "*New strategy for the growth of complex heterostructures based on different 2D materials*," Chemistry of Materials, vol. 27, no. 11, pp. 4105-4113, 2015.

- [14] Hua Qian, **Brian Markman**, and Noel C. Giebink. "Vector vortex beam emission from organic semiconductor microlasers," Applied Physics Letters, 103, 161110, 2013.

- [15] **Brian Markman**, Rohit Ranade, and Noel C. Giebink. "Nonimaging optics in luminescent solar concentration," Optics Express, vol. 20, pp. A622-A629, 2012.

#### ABSTRACT

III-V In<sub>x</sub>Ga<sub>1-x</sub>As / InP MOS-HEMTs for 100-340GHz Communications Systems

by

#### Brian David Markman

This work summarizes the efforts made to extend the current gain cutoff frequency of InP based FET technologies beyond 1 THz. Incorporation of a metal-oxide-semiconductor field effect transistor (MOSFET) at the intrinsic Gate Insulator-Channel interface of a standard high electron mobility transistor (HEMT) has enabled increased  $g_{m,i}$  by increasing the gate insulator capacitance density for a given gate current leakage density. Reduction of  $R_{S,TLM}$  from 110  $\Omega^{\bullet}\mu m$  to 75  $\Omega^{\bullet}\mu m$  and  $R_{on}(0)$  from 160  $\Omega^{\bullet}\mu m$  to 120  $\Omega^{\bullet}\mu m$  was achieved by removing/thinning the wide bandgap modulation doped link regions beneath the highly doped contact layers. Process repeatability was improved by developing a gate metal first process and  $D_{it}$  was improved by inclusion of a post-metal H<sub>2</sub> anneal. In<sub>x</sub>Ga<sub>1-x</sub>As / InAs composite quantum wells clad with both InP and In<sub>x</sub>Al<sub>1-x</sub>As were developed for high charge density and low sheet resistance to minimize source resistance.

With these improvements a  $L_g = 8$  nm,  $t_{ch} = 6.5$  nm transistor with  $f_{\tau} = 511$  GHz,  $f_{\text{max}} = 283$  GHz, a  $L_g = 18$  nm,  $t_{ch} = 2.5$  nm transistors with  $f_{\tau} = 350$  GHz,  $f_{\text{max}} = 400$  GHz, a  $f_{\text{max}} = 400$  nm,  $f_{\text{max}} = 400$  nm,  $f_{\text{max}} = 420$  GHz,  $f_{\text{max}} = 592$  GHz were demonstrated. Power gain was sometimes limited by  $f_{\text{max}} = 420$  GHz,  $f_{\text{max}} = 592$  GHz were filling.

Based on these results and those reported in [1-3], a theory on the effects of channel thickness on quantum well ballistic devices was proposed. Simply, thin quantum wells have large Eigen-state energies limiting the amount of available  $(E_F - E_I)$  beyond threshold.

Because a quantum well device's maximum conductance occurs when  $E_F$  is equal to or nearly equal to the conduction band minimum of the barrier material, current in thin channel devices is limited not by effective mass effects (i.e. density of states or injection velocity) but by band-offset limitations.

# **TABLE OF CONTENTS**

| 1. | Intro | oduction                                         | 1  |

|----|-------|--------------------------------------------------|----|

|    | Refe  | erences                                          | 6  |

| 2. | FET   | Theory and Design                                | 9  |

|    | A.    | Principle of Operation                           | 9  |

|    | B.    | Subthreshold Slope & Interface Defects           | 13 |

|    | C.    | Short-Channel Effects                            | 15 |

|    | D.    | Gate-Channel Capacitance                         | 17 |

|    | E.    | Ideal Ballistic MOSFET Theory                    | 18 |

|    | F.    | Channel Quantum Well                             | 23 |

|    | G.    | Increasing $f_{\tau}$ and $f_{max}$              | 30 |

|    | Н.    | Equivalent Circuit Model                         | 33 |

|    | E. S  | Summary                                          | 38 |

|    | Refe  | erences                                          | 39 |

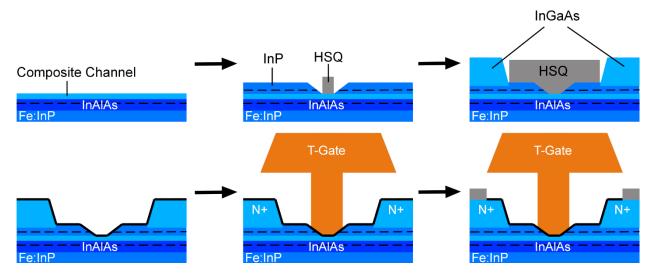

| 3. | Fab   | rication Process                                 | 45 |

|    | A.    | Overview                                         | 45 |

|    | В.    | Alignment Marks                                  | 46 |

|    | C.    | Dummy Gate 1 + Link Regrowth                     | 48 |

|    | D.    | Dummy Gate 2 + Link Etch + Source-Drain Regrowth | 50 |

|    | E.    | Mesa Isolation                                   | 55 |

|    | F.    | High-K Dielectric                                | 56 |

|    | G.    | T-Gate Formation                                 | 58 |

|    | Н.    | Source-Drain Via                                 | 64 |

|    | I.   | Pad Metal                        | 66 |

|----|------|----------------------------------|----|

|    | Refe | rences                           | 67 |

| 4. | Gene | ration 1                         | 72 |

|    | A.   | Device Structure and Fabrication | 72 |

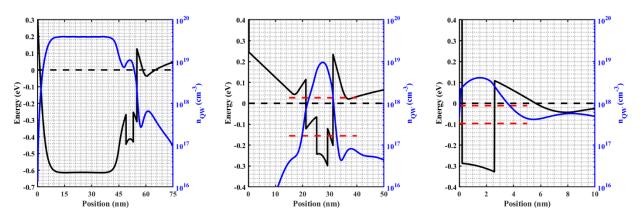

|    | B.   | Band Diagrams                    | 76 |

|    | C.   | DC Results                       | 77 |

|    | D.   | RF Results.                      | 82 |

|    | E.   | 8nm Equivalent Circuit Model     | 88 |

|    | F.   | Summary                          | 92 |

|    | Refe | rences                           | 93 |

| 5. | Gene | ration 2                         | 95 |

|    | A.   | Device Structure and Fabrication | 95 |

|    | B.   | Band Diagrams                    | 99 |

|    | C.   | DC Results                       | 00 |

|    | D.   | RF Results10                     | 05 |

|    | E.   | Equivalent Circuit Model1        | 10 |

|    | Refe | rences1                          | 13 |

| 6. | Gene | eration 31                       | 15 |

|    | A.   | Device Structure and Fabrication | 15 |

|    | B.   | Band Diagrams                    | 18 |

|    | C.   | DC Results1                      | 19 |

|    | D.   | RF Results                       | 22 |

|    | E.   | Equivalent Circuit Model12       | 27 |

|    | References 1                                 | 29  |

|----|----------------------------------------------|-----|

| 7. | Confined Epitaxial Lateral Overgrowth (CELO) | 31  |

|    | A. Motivation1                               | 31  |

|    | B. Fabrication Process                       | 34  |

|    | 1. Seed Layer                                | .37 |

|    | 2. Sacrificial Layer1                        | .42 |

|    | 3. Source Layer1                             | 45  |

|    | C. Template Effects on Growth                | 47  |

|    | D. Conclusions1                              | .55 |

|    | References1                                  | 57  |

| 8. | Conclusions1                                 | 63  |

|    | A. Summary1                                  | 63  |

|    | B. Future Work                               | 66  |

|    | C. References                                | 69  |

|    | Appendix 2 – Generation 2 Process            | .75 |

|    | Appendix 3 – Generation 3 Process            | 78  |

|    | Appendix 4 – TASE/CELO Process A             | .82 |

|    | Appendix 5 – TASE/CELO Process R             | .84 |

# **LIST OF FIGURES**

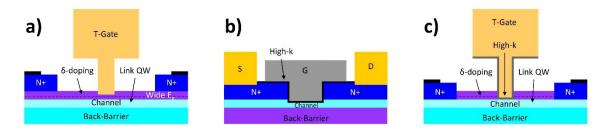

| Figure 1.1 Cross-sectional illustration of a standard a) InP-based HEMT b) III-V DC                                                |

|------------------------------------------------------------------------------------------------------------------------------------|

| optimized MOSFET c) proposed InP-based MOS-HEMT                                                                                    |

| Figure 2.1 a) cross-sectional illustration of long channel MOSFET operating at $V_{DS} = V_{GS}$ –                                 |

| $V_{TH}$ b) top-down view of a typical MOSFET                                                                                      |

| Figure 2.2 Ideal long $L_g$ MOSFET a) output characteristics b) transfer characteristics at large                                  |

| $V_{DS}$ (saturation region)                                                                                                       |

| Figure 2.3 a) unified model of interface states and associated Schottky barriers of GaAs, InP,                                     |

| and GaSb. Reprinted with permission from [9]. © 1980 AIP Publishing LLC b) Energy                                                  |

| level of interface states of GaAs, InP, and GaSb. Reprinted with permission from [9].                                              |

| © 1980 AIP Publishing LLC c) Fermi level pinning energy levels relative to valence                                                 |

| band maximum for In <sub>x</sub> Ga <sub>1-x</sub> As as a function of Indium content. Reprinted with                              |

| permission from [10]. © Copyright 2013 IEEE                                                                                        |

| Figure 2.4 illustration of a) the gate-channel series capacitance b) $C_{QW}$ and c) $C_{DOS}$                                     |

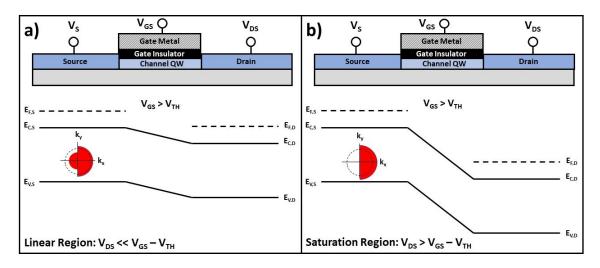

| Figure 2.5 Band diagrams of ballistic FET a) low $V_{DS}$ b) high $V_{DS}$                                                         |

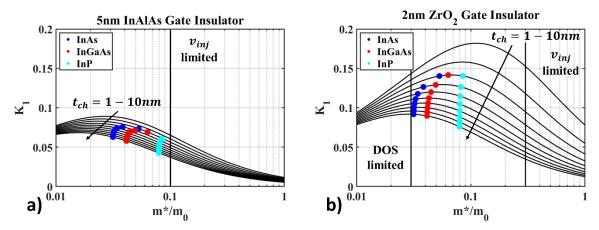

| Figure 2.6 Normalized drive current as a function of channel effective mass for a) 5 nm                                            |

| In <sub>0.52</sub> Al <sub>0.48</sub> As gate insulator b) 2 nm ZrO <sub>2</sub> gate insulator                                    |

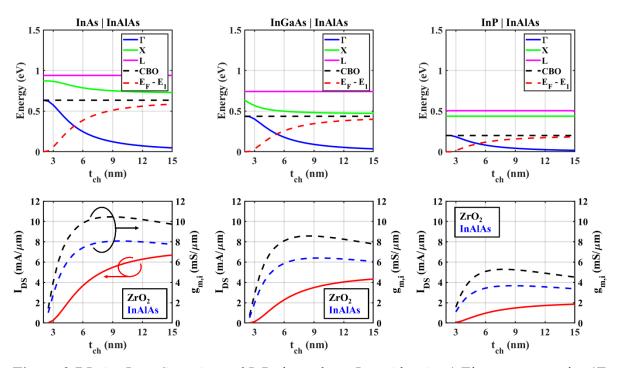

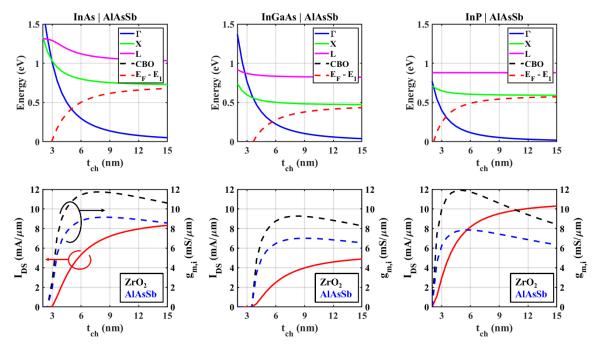

| Figure 2.7 InAs, $In_{0.53}Ga_{0.47}As$ , and $InP$ channels on $In_{0.52}Al_{0.48}As$ a) Eigenstate energies ( $\Gamma$ ,         |

| $L, X)$ b) Peak ballistic $I_{DS}$ and $g_{m,i}$ using 0.5 nm $Al_xO_yN_z$ / 1.5 nm $ZrO_2$ high-k gate                            |

| dielectric and 5.0 nm $In_{0.52}Al_{0.48}As$ gate dielectric, note $I_{DS}$ is independent of gate                                 |

| insulator                                                                                                                          |

| Figure 2.8 InAs, In $_{0.53}$ Ga $_{0.47}$ As, and InP channels on AlAs $_{0.56}$ Sb $_{0.44}$ a) Eigenstate energies ( $\Gamma$ , |

| $L, X)$ b) Peak ballistic $I_{DS}$ and $g_{m,i}$ using 0.5 nm $Al_xO_yN_z$ / 1.5 nm $ZrO_2$ high-k gate                            |

| dielectric and 5.0 nm AlAs <sub>0.56</sub> Sb <sub>0.44</sub> gate dielectric, note $I_{DS}$ is independent of gate                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| insulator                                                                                                                                               |

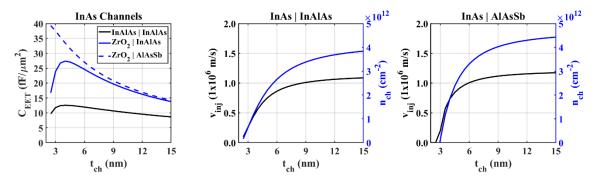

| Figure 2.9 (left) CEET for InAs channels for HEMT, FET with In <sub>0.52</sub> Al <sub>0.48</sub> As back-barrier,                                      |

| and FET with AlAs <sub>0.56</sub> Sb <sub>0.44</sub> back-barrier and peak $n_{ch}$ and $v_{inj}$ for InAs channel devices                              |

| with (middle) In <sub>0.52</sub> Al <sub>0.48</sub> As back-barrier and (right) AlAs <sub>0.56</sub> Sb <sub>0.44</sub> back-barrier 29                 |

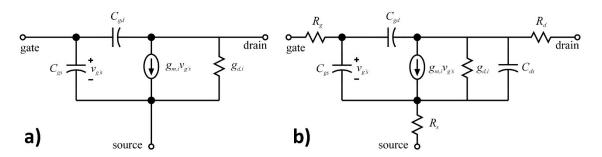

| Figure 2.10 Common source FET equivalent circuit a) simple b) moderate complexity 33                                                                    |

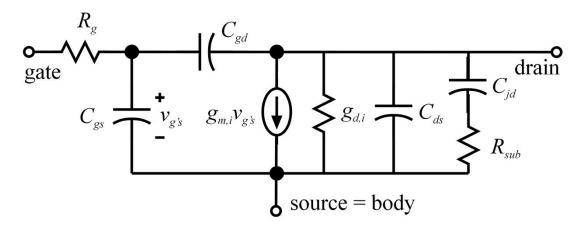

| Figure 2.11 Equivalent circuit used to derive Y-parameters reported in [38]                                                                             |

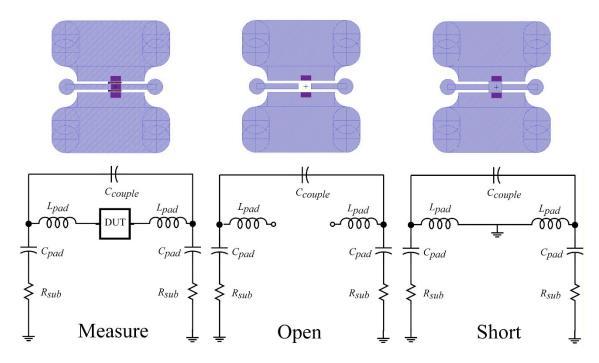

| Figure 2.12 Mask layout and equivalent circuit used for de-embedding                                                                                    |

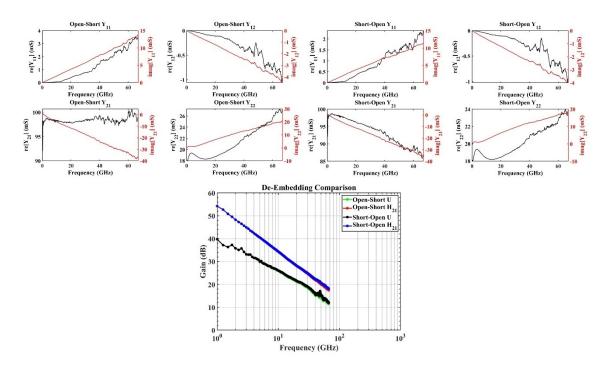

| Figure 2.13 De-embedded Y-parameters by open-short and short-open and their FOMs 38                                                                     |

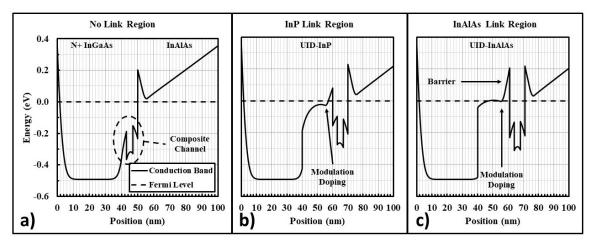

| Figure 3.1 Band diagrams beneath $N+$ In <sub>0.53</sub> Ga <sub>0.47</sub> As source-drains in HEMT structures for a)                                  |

| link region removed b) modulation doped InP link c) modulation doped In <sub>0.52</sub> Al <sub>0.48</sub> As                                           |

| link                                                                                                                                                    |

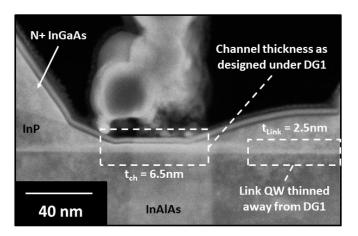

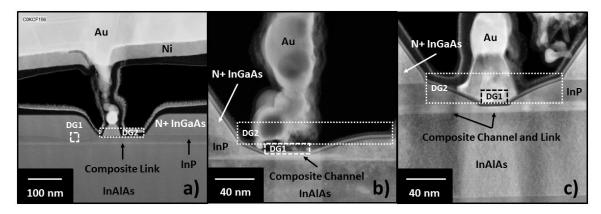

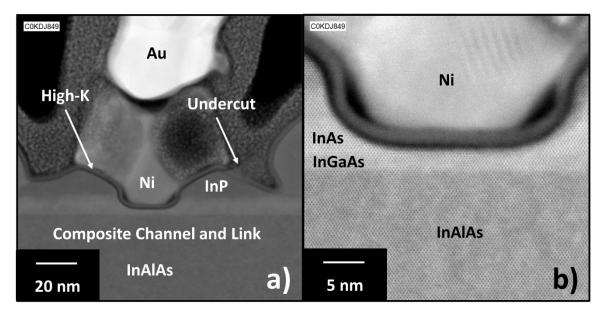

| Figure 3.2 Cross-section TEM of completed device Ch2-L1G2SD3 showing link region                                                                        |

| thinning due to overdevelopment of dummy gate 1 HSQ (90s NaOH:NaCl:H2O                                                                                  |

| 2g:8g:200mL + 120s AZ300-MIF) where InGaAs / InAs composite channel etched in                                                                           |

| dilute base chemistry                                                                                                                                   |

| Figure 3.3 Cross-sectional TEM images demonstrating the reliability of aligning dummy gate                                                              |

| 2 to dummy gate 1 using a) different beam current and scan locations b) different beam                                                                  |

| current and same scan location c) same beam current and same location                                                                                   |

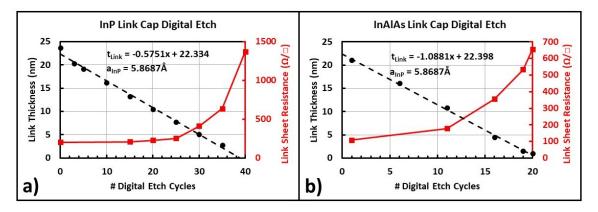

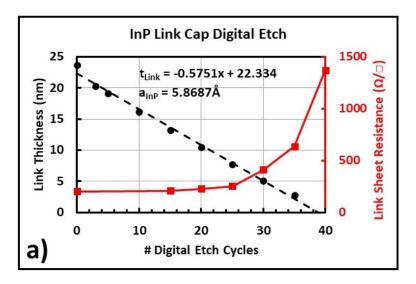

| Figure 3.4 Fitted digital etch rate and link region sheet resistance dependence on link cap                                                             |

| thickness for a) InP link (3 nm UID-InP spacer, 2 nm 1x10 <sup>19</sup> cm <sup>-3</sup> InP modulation                                                 |

| doping, 20 nm UID-InP cap) b) InAlAs link (3 nm UID-In <sub>0.52</sub> Al <sub>0.48</sub> As spacer, 3 nm                                               |

| 1x10 <sup>19</sup> cm <sup>-3</sup> In <sub>0.52</sub> Al <sub>0.48</sub> As modulation doping, 15 nm UID-In <sub>0.52</sub> Al <sub>0.48</sub> As cap) |

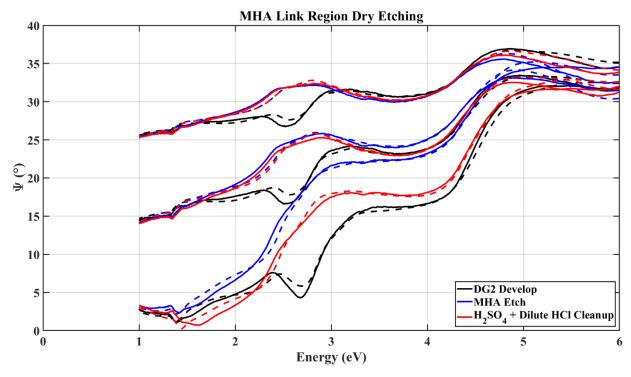

| Figure 3.5 Ellipsometry of MHA dry etch of In <sub>0.52</sub> Al <sub>0.48</sub> As link region where solid lines are |

|-----------------------------------------------------------------------------------------------------------------------|

| measured and dashed lines are modeled                                                                                 |

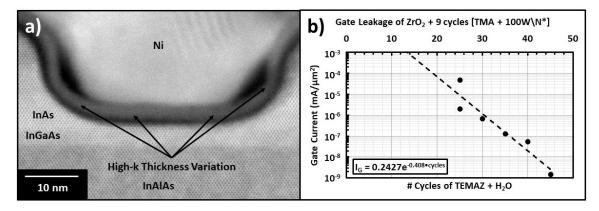

| Figure 3.6 a) cross-sectional TEM image showing thickness variation across the length of the                          |

| channel b) Gate leakage current as a function TEMAZ + H <sub>2</sub> O cycles as extracted from                       |

| long gate length devices with $(V_{DS} - V_{GS}) = 0.7 \text{ V}.$                                                    |

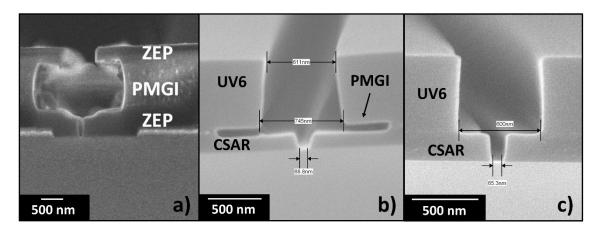

| Figure 3.7 T-Gate resists stacks commonly used a) Trilayer ZEP / PMGI stack used in [26] b                            |

| Trilayer, single exposure CSAR / PMGI / UV6 stack used at UCSB, PMGI thickness                                        |

| can be modified to facilitate easier liftoff c) Bilayer, double exposure CSAR / UV6                                   |

| stack used at UCSB                                                                                                    |

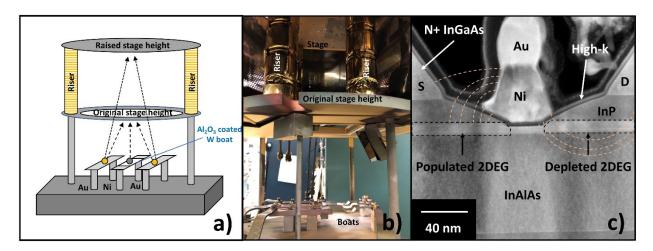

| Figure 3.8 T-Gate process considerations a) illustration of UCSB thermal evaporator set up                            |

| and modification for T-Gate evaporation b) picture of thermal evaporator set up c                                     |

| Resulting T-Gate footprint and illustration of electric field lines that cause $C_{GS}$ and                           |

| $C_{GD}$                                                                                                              |

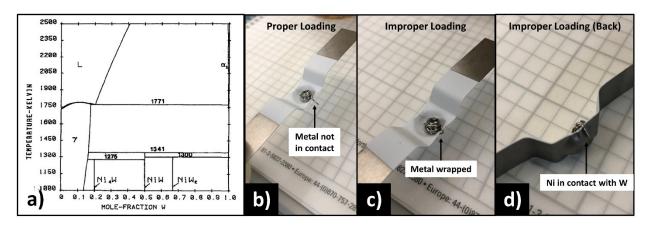

| Figure 3.9 a) Ni-W binary phase diagram reproduced from [28] b) proper loading of Ni ir                               |

| aluminum coated, tungsten boat for gate thermal evaporation c) improper loading o                                     |

| Ni d) contact region of Ni-W when improperly loaded                                                                   |

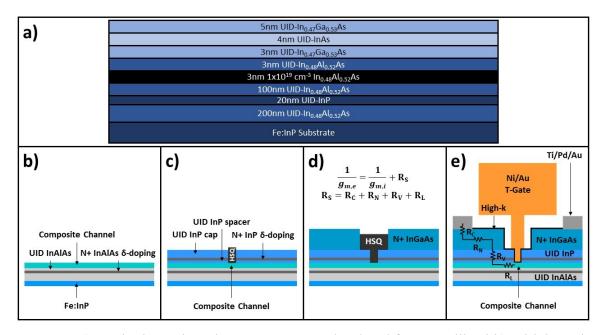

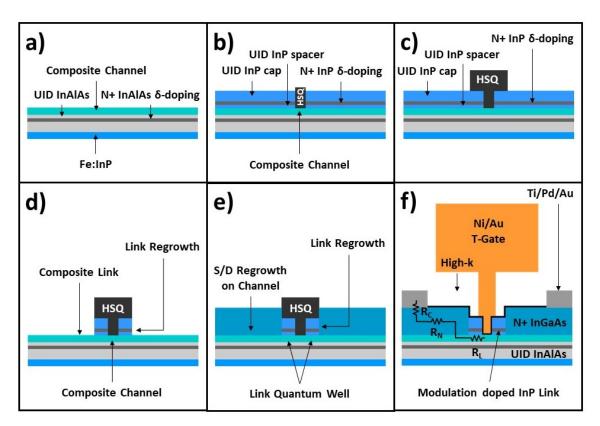

| Figure 4.1 a) Beginning epi stack, MBE grown and ordered from IntelliEpi b) Initial starting                          |

| surface c) First dummy gate and link regrowth d) Second dummy gate and source                                         |

| drain regrowth e) Final structure after T-Gate metallization and source-drain contac                                  |

| formation72                                                                                                           |

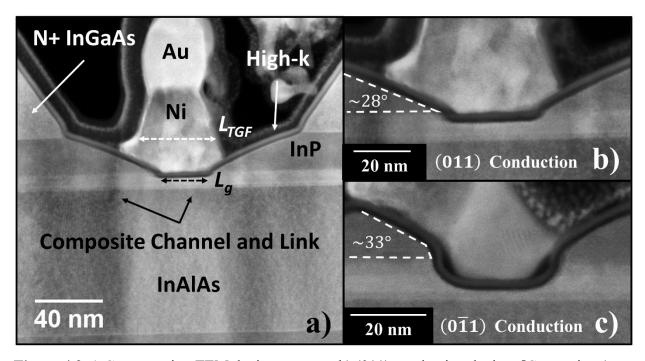

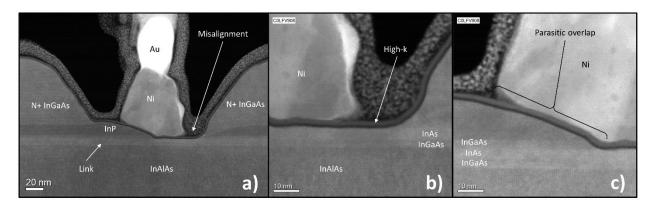

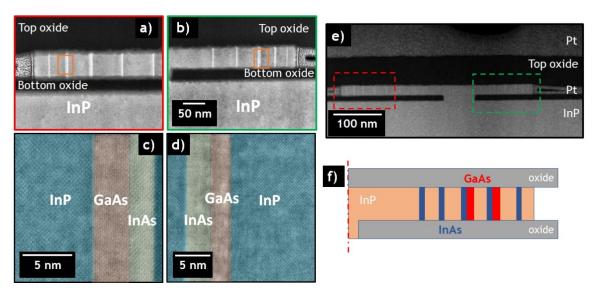

| Figure 4.2 a) Cross-section TEM device structure b) (011) conduction devices [Generation 1                            |

| device shown] and c) 011 conduction devices [Generation 2 device shown] 75                                            |

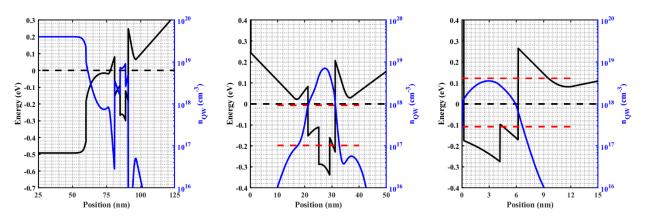

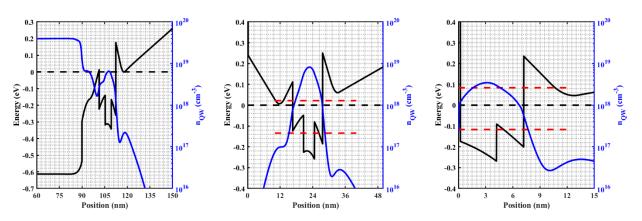

| Figure 4.3. Band diagrams for Generation 1 devices                                                                    |

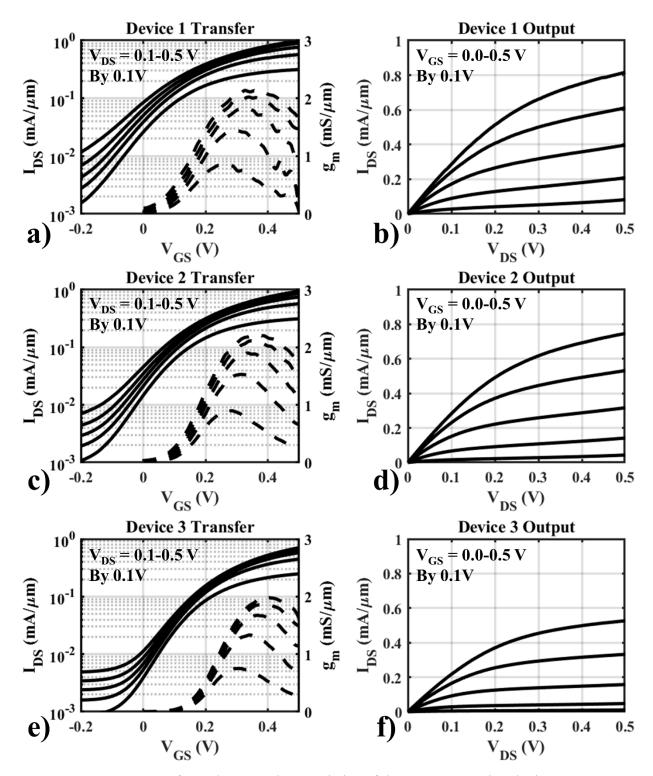

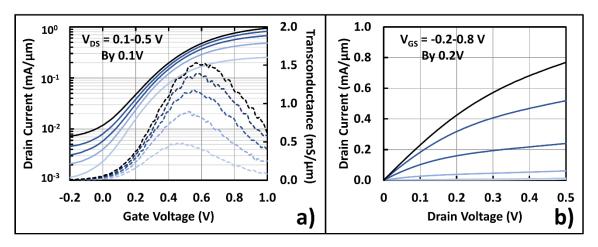

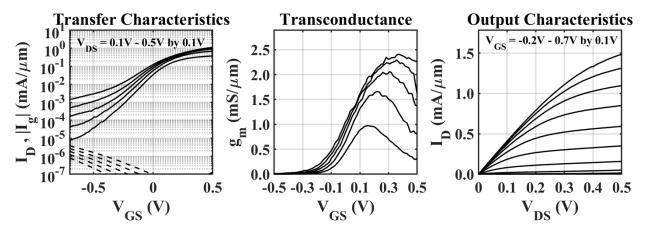

| Figure 4.4 Transfer and output characteristics of three representative devices                                                 |

|--------------------------------------------------------------------------------------------------------------------------------|

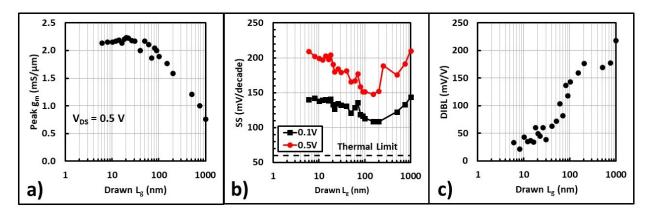

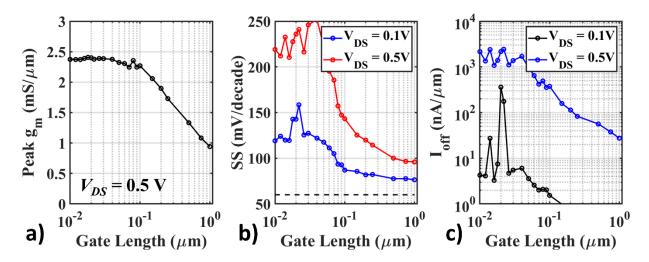

| Figure 4.5 DC lot characterization of Generation 1 devices a) Peak transconductance b) SS at                                   |

| $V_{DS} = 0.1 \text{ V and } 0.5 \text{ V c}) \text{ DIBL}$                                                                    |

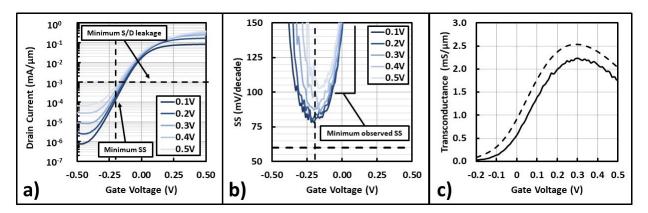

| Figure 4.6 $L_g$ = 150 nm device from device run Ch5-L3G3SD3 illustrating where minimum                                        |

| SS occurs and why it is not observed for Generation 1 devices a) transfer characteristics                                      |

| b) SS as a function of $V_{GS}$ c) DC and 1 GHz $g_{m,e}$ for drawn $L_g = 22$ nm Generation 1                                 |

| device at $V_{DS} = 0.5 \text{ V}$                                                                                             |

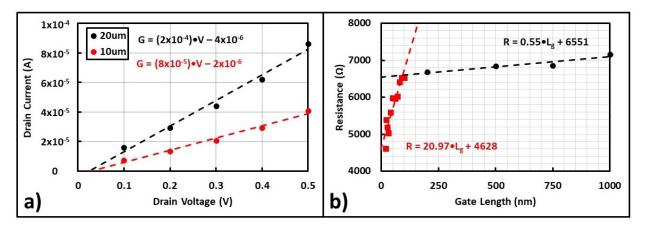

| Figure 4.7 a) Extraction of etch stop conductance for $L_g = 1$ µm devices at $W_g = 20$ µm and                                |

| $W_g = 10 \ \mu \text{m b}$ ) $R_{off} \text{ vs } L_g \text{ for } W_g = 20 \ \mu \text{m}$                                   |

| Figure 4.8 Extracted resistances a) N+ InGaAs and Link Quantum Well TLMs b) On-                                                |

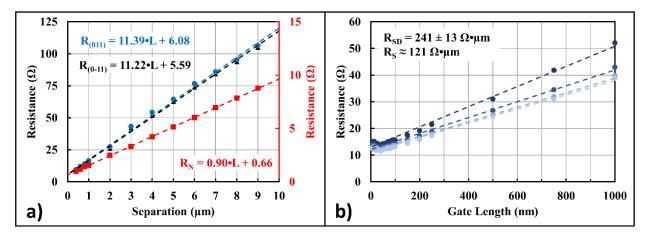

| resistance measurements at various $(V_{GS} - V_{TH})$                                                                         |

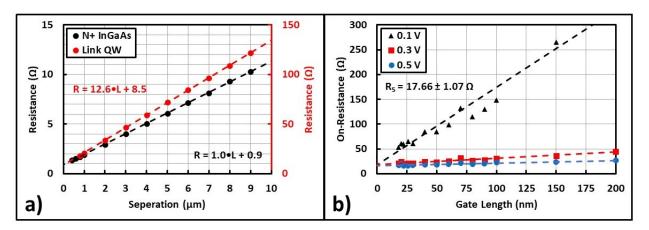

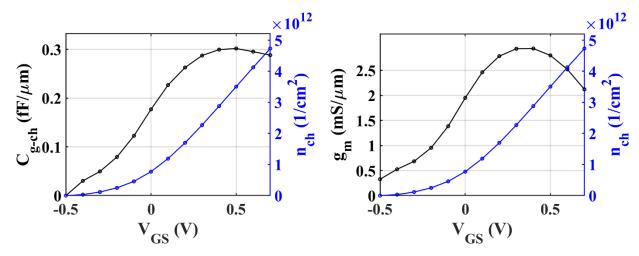

| Figure 4.9 $L_g$ = 8 nm 011 conduction device, S-parameter extracted a) CV-characteristics b)                                  |

| $n_{ch}$ , $g_{m,e}$ vs. $V_{GS}$ at $V_{DS} = 0.7$ V                                                                          |

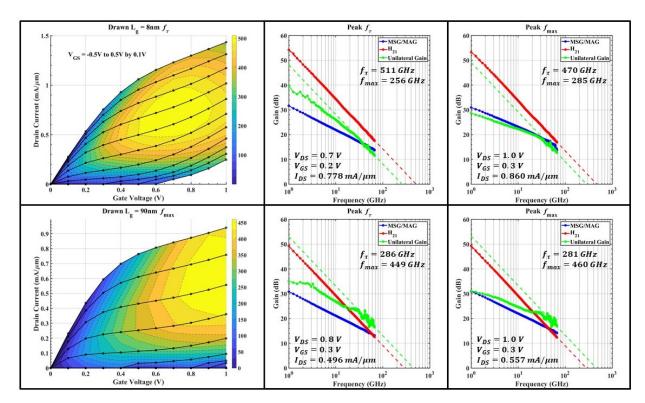

| Figure 4.10 (top) $L_g = 8$ nm 011 oriented device (left) $f_{\tau}$ contour plot (middle) FOM fitting at                      |

| peak $f_{\tau}$ (right) FOM fitting at peak $f_{\text{max}}$ (bottom) $L_g = 90 \text{ nm}$ (011) oriented device (left)       |

| $f_{\tau}$ contour plot (middle) FOM fitting at peak $f_{\tau}$ (right) FOM fitting at peak $f_{\text{max}}$ 84                |

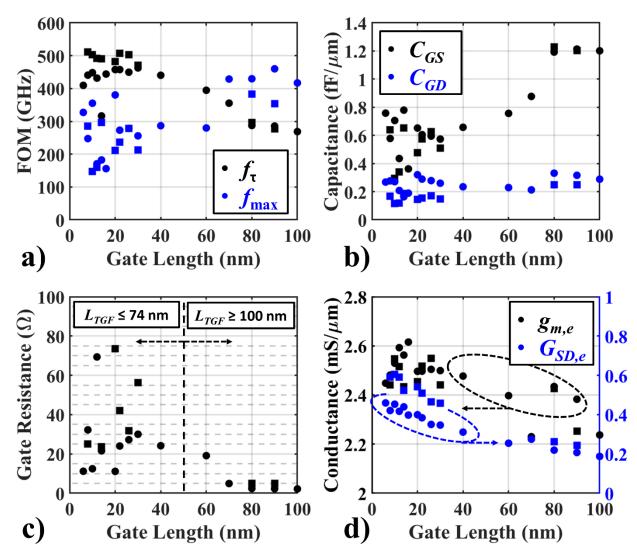

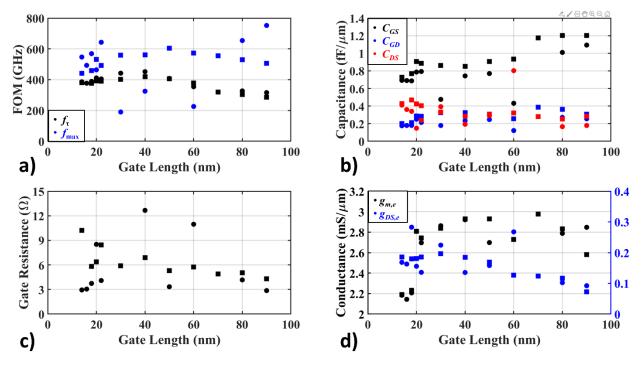

| Figure 4.11 Extracted equivalent circuit parameters at peak $f_{\tau}$ bias where circles are (011)                            |

| conduction and triangles are (0-11) conduction a) $f_{\tau}$ , $f_{\text{max}}$ b) $C_{GS}$ and $C_{GD}$ c) $R_G$ d) $g_{m,e}$ |

| and <i>G<sub>DS,e</sub></i> 85                                                                                                 |

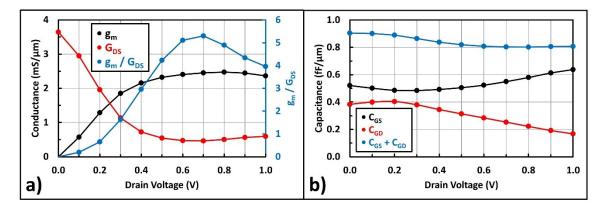

| Figure 4.12 Extracted equivalent circuit parameters from Y-parameter fitting drawn $L_g = 8$                                   |

| nm, $W_{mesa} = 20 \mu m$ , 2 finger device oriented in 011 under peak $f_{\tau}$ bias of $V_{DS} = 0.7$ and                   |

| $V_{GS} = 0.2 \text{ V a}$ ) $g_{m,e}$ and $G_{DS,e}$ b) $C_{GS}$ and $C_{GD}$                                                 |

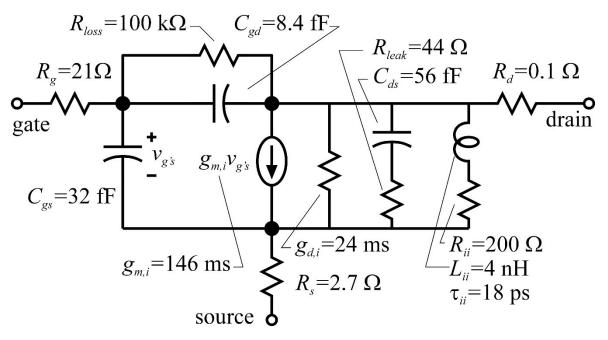

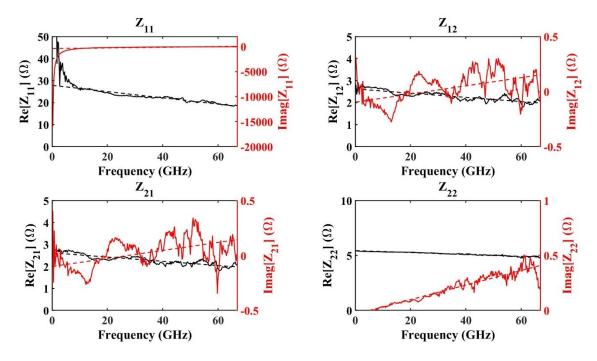

| Figure 4.13 Equivalent circuit model of drawn $L_g = 8$ nm, $W_{mesa} = 20$ µm, 2 finger device        |

|--------------------------------------------------------------------------------------------------------|

| oriented in 011 under peak $f_{\tau}$ bias of $V_{DS} = 0.7$ and $V_{GS} = 0.2$ V                      |

| Figure 4.14 Measured and fit Z-parameters drawn $L_g = 8$ nm, $W_{mesa} = 20$ µm, 2 finger device      |

| oriented in 011 under peak $f_{\tau}$ bias of $V_{DS} = 0.7$ and $V_{GS} = 0.2$ V shown with automatic |

| fitting89                                                                                              |

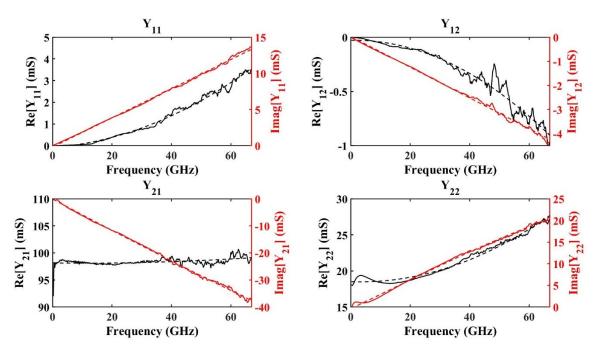

| Figure 4.15 Measured and fit Y-parameters for drawn $L_g = 8$ nm, $W_{mesa} = 20$ µm, 2 finger         |

| device oriented in 011 under peak $f_{\tau}$ bias of $V_{DS} = 0.7$ and $V_{GS} = 0.2$ V shown with    |

| automatic fitting91                                                                                    |

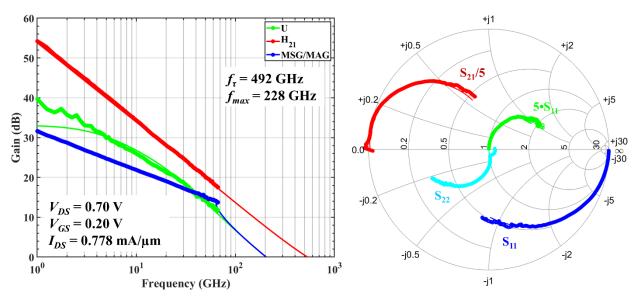

| Figure 4.16 Measured and modeled S-parameters and high-frequency FOMs for $L_g = 8$ nm                 |

| 011 device biased for peak $f_{\tau}$                                                                  |

| Figure 4.17 Simulated high-frequency FOMs for Generation 1 $L_g = 8$ nm device with $R_G = 7$          |

| $\Omega$ , $C_{GD} = 0.2$ fF/um, and $G_{DS} = 0.2$ mS/um                                              |

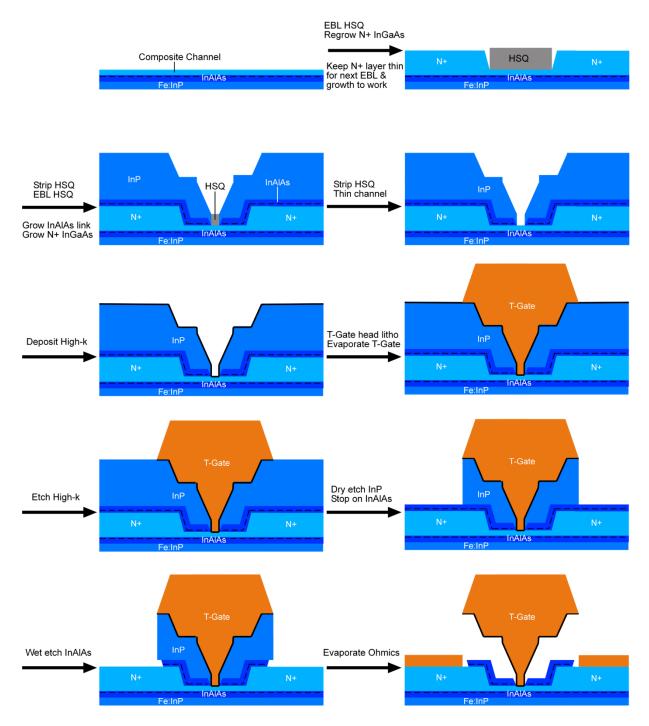

| Figure 5.1 a) Initial starting surface b) First dummy gate and link regrowth c) Second dummy           |

| gate d) Link region wet etch e) source-drain regrowth on channel f) Final structure                    |

| after T-Gate metallization and source-drain contact formation                                          |

| Figure 5.2 Digital etch rate and link sheet resistance for InP link, Generation 2 devices 97           |

| Figure 5.3 Cross-sectional TEM of $L_g = 18$ nm device a) intrinsic device b) gated region 98          |

| Figure 5.4 Band diagrams of the (left) source-drain regions and (right) link quantum well              |

| plotted on (top) log-scale to show parallel 2DEGs and (bottom) linear scale to show                    |

| wave-function distribution                                                                             |

| Figure 5.5 Drawn $L_g = 18$ nm (011) oriented device a) transfer and b) output characteristics         |

|                                                                                                        |

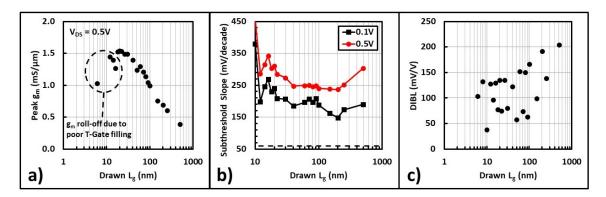

| Figure 5.6 DC lot characterization of Generation 2 devices a) Peak transconductance b)                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| subthreshold slope at $V_{DS} = 0.1 \text{ V}$ and $0.5 \text{ V}$ c) DIBL                                                                                                        |

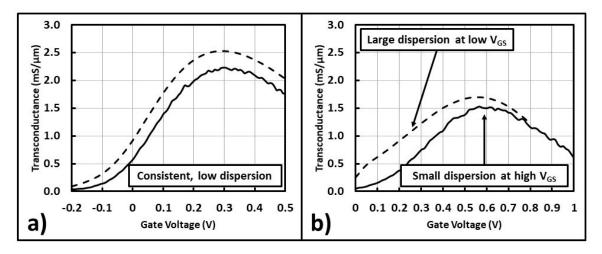

| Figure 5.7 DC and 1 GHz $g_{m,e}$ for a) Generation 1 $t_{ch}$ = 6.5 nm with high-k / InAs interface                                                                              |

| and b) Generation 2 $t_{ch}$ = 2.5 nm with high-k / In <sub>0.53</sub> Ga <sub>0.47</sub> As interface                                                                            |

| Figure 5.8 Extracted resistances a) N+ $In_{0.53}Ga_{0.47}As$ and Link Quantum Well TLMs, where                                                                                   |

| "Horizontal" refers to (011) conduction and "Vertical" is 011 conduction b) On-                                                                                                   |

| resistance measurements at various $(V_{GS} - V_{TH})$                                                                                                                            |

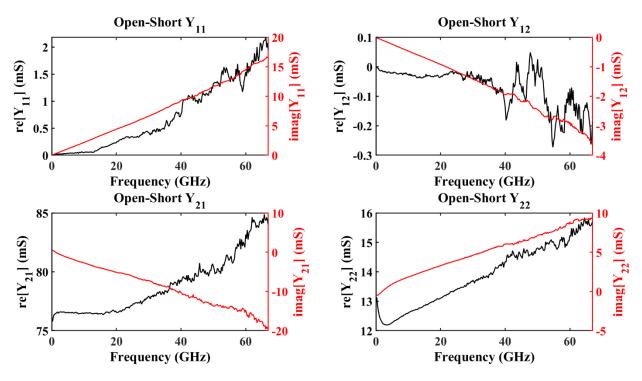

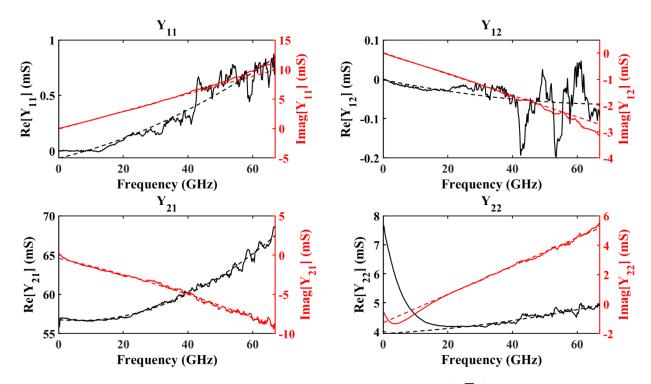

| Figure 5.9 Open-Short de-embedded Y-parameters for $L_g = 12$ nm device                                                                                                           |

| Figure 5.10 Short-Open de-embedded Y-parameters for $L_g = 12$ nm device                                                                                                          |

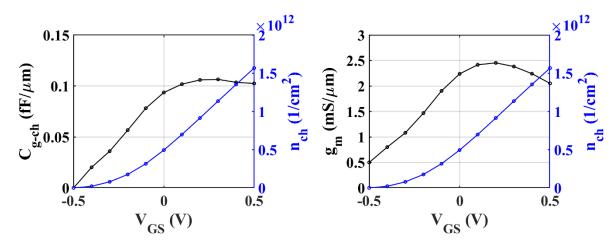

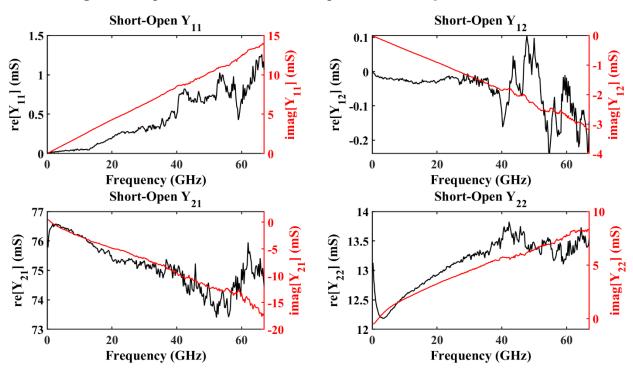

| Figure 5.11 $L_g = 12$ nm 011 S-parameter extracted a) CV characteristics b) $g_{m,e}$ and $n_{ch}$ at $V_{DS}$                                                                   |

| = 0.7 V                                                                                                                                                                           |

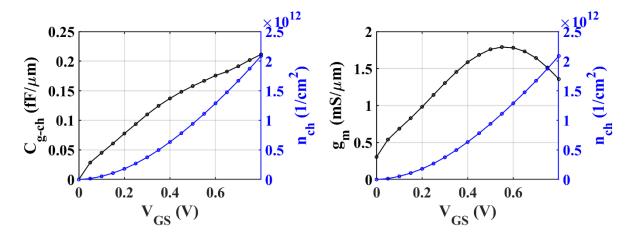

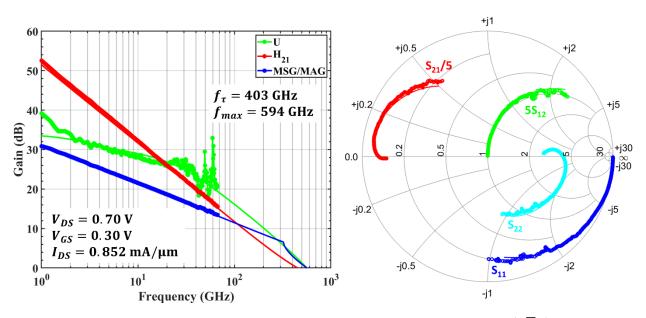

| Figure 5.12 Extracted FOMs and common source small signal equivalent circuit parameters                                                                                           |

| for Generation 2 devices                                                                                                                                                          |

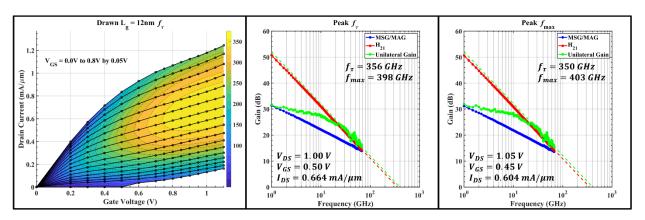

| Figure 5.13 $L_g = 12$ nm 011 conduction device (left) $f_{\tau}$ contour plot (middle) FOM fitting at                                                                            |

| peak $f_{\tau}$ (right) FOM fitting at peak $f_{max}$ (bottom)                                                                                                                    |

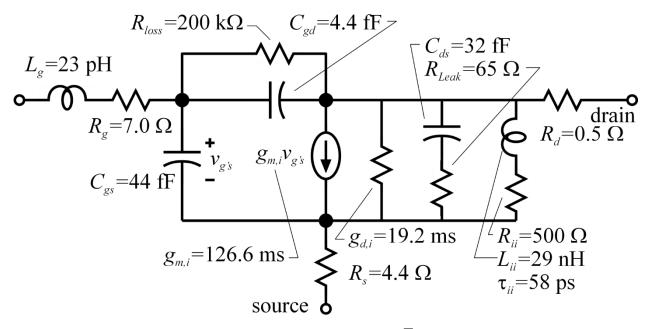

| Figure 5.14 Small signal equivalent circuit of $L_g = 12$ nm 011 conduction device at $V_{DS} = 1.00$                                                                             |

| V, $V_{GS} = 0.50$ , $I_{DS} = 0.664$ mA/ $\mu$ m                                                                                                                                 |

|                                                                                                                                                                                   |

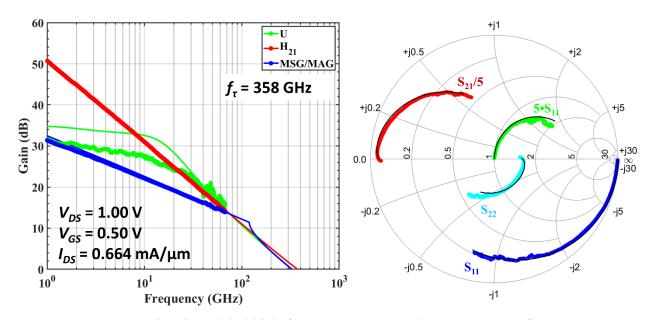

| Figure 5.15 Measured and modeled high frequency FOMs and S-parameters of $L_g = 12$ nm                                                                                            |

| Figure 5.15 Measured and modeled high frequency FOMs and S-parameters of $L_g = 12$ nm 011 conduction device at $V_{DS} = 1.00$ V, $V_{GS} = 0.50$ , $I_{DS} = 0.664$ mA/ $\mu$ m |

|                                                                                                                                                                                   |

| 011 conduction device at $V_{DS} = 1.00 \text{ V}$ , $V_{GS} = 0.50$ , $I_{DS} = 0.664 \text{ mA/}\mu\text{m}$                                                                    |

| 011 conduction device at $V_{DS} = 1.00 \text{ V}$ , $V_{GS} = 0.50$ , $I_{DS} = 0.664 \text{ mA/}\mu\text{m}$                                                                    |

| Figure 6.4 Drawn $L_g$ = 18 nm, (011) conduction device a) transfer and b) output                              |

|----------------------------------------------------------------------------------------------------------------|

| characteristics                                                                                                |

| Figure 6.5 DC figures of merit for Generation 3 devices a) Peak $g_m$ b) SS at $V_{DS} = 0.1$ V and            |

| 0.5 V c) DIBL                                                                                                  |

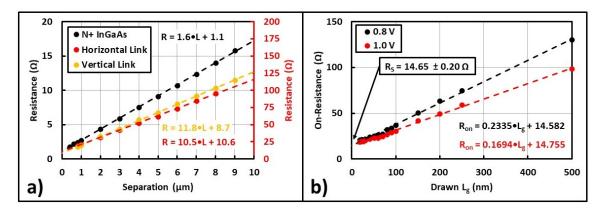

| Figure 6.6 Generation 3 source-resistance extraction a) on wafer TLMs b) $R_{ON}$ extrapolation                |

| at $V_{GS} = 0.4$ to 0.7 V                                                                                     |

| Figure 6.7 Open-Short de-embedded Y-parameters of $L_g = 30$ nm 011 conduction device                          |

| shown with automated fitting used to determine SSEC parameters                                                 |

| Figure 6.8 $L_g$ = 40 nm 011 S-parameter extracted a) CV characteristics b) $g_{m,e}$ and $n_{ch}$ at $V_{DS}$ |

| = 0.7 V                                                                                                        |

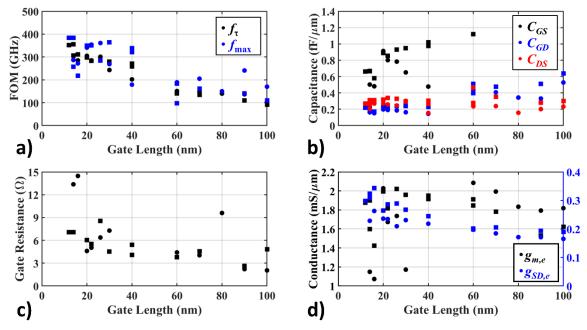

| Figure 6.9 RF FOM and SSEC extraction of Generation 3 devices a) high frequency FOMs b)                        |

| $C_{GS}$ , $C_{GD}$ , and $C_{DS}$ c) $R_G$ d) $g_{m,e}$ and $g_{ds,e}$                                        |

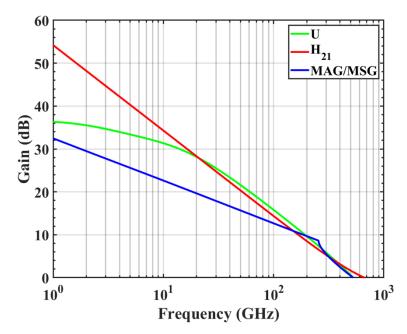

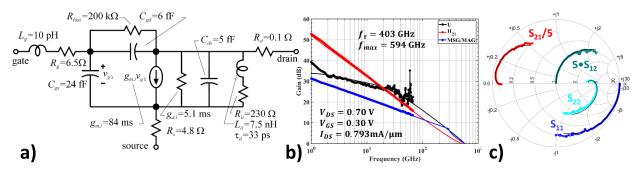

| Figure 6.10 a) Small signal equivalent circuit b) measured / modeled FOMs c) and measured                      |

| / modeled S-parameters of $L_g$ = 40 nm 011 conduction device at $V_{DS}$ = 0.70 V, $V_{GS}$ =                 |

| $0.30, I_{DS} = 0.793 \text{ mA/}\mu\text{m}.$                                                                 |

| Figure 6.11 Measured and modeled U, $H_{21}$ , and MAG/MSG for $L_g = 40$ nm 011 device 128                    |

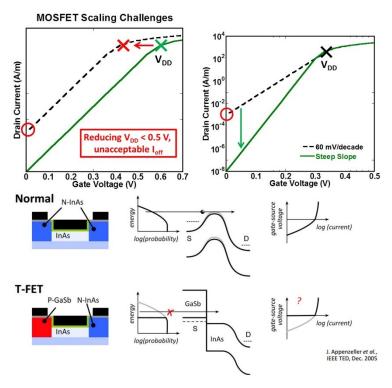

| Figure 7.1 a) Transfer characteristics of MOSFET b) motivation for steep-slope device c)                       |

| illustration of the mechanisms responsible for sub-threshold behavior                                          |

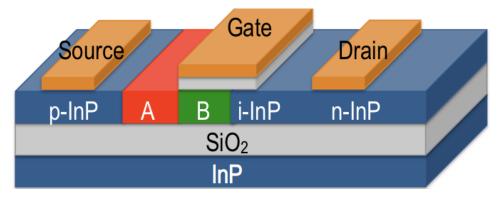

| Figure 7.2 Simplified 3HJ-TFET fabricated using laterally grown material by CELO 133                           |

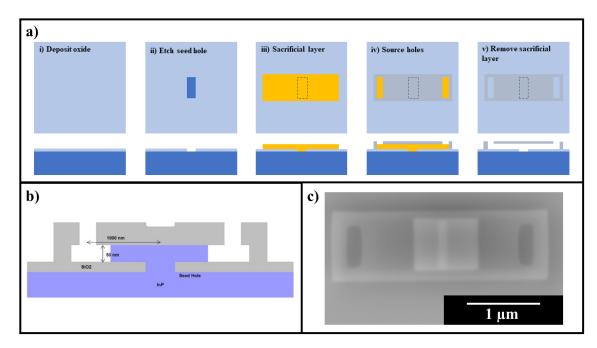

| Figure 7.3 a) cross-sectional and top-down view of CELO template fabrication b) illustration                   |

| of template cross-section after growth c) top-down SEM of CELO structure with                                  |

|                                                                                                                |

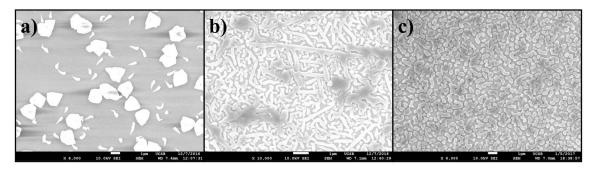

| Figure 7 | 7.4 MOCVD SAG trials on un-patterned SiO <sub>x</sub> deposited by a) PECVD b) ALD c)                             |

|----------|-------------------------------------------------------------------------------------------------------------------|

| S        | putter                                                                                                            |

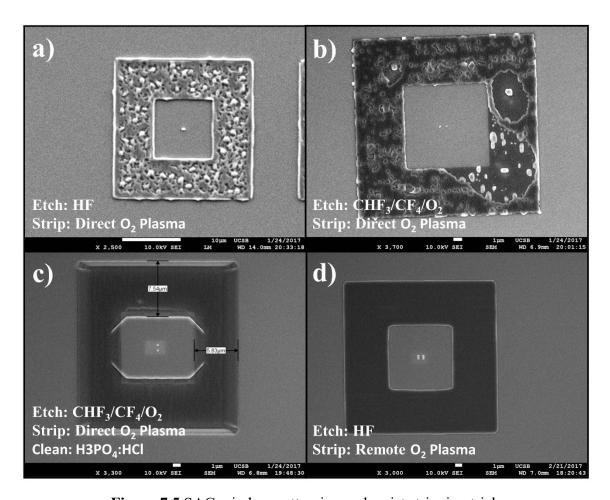

| Figure 7 | .5 SAG window patterning and resist stripping trials                                                              |

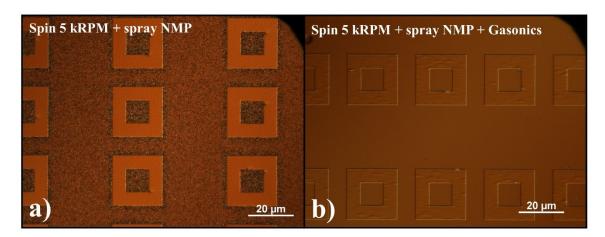

| Figure 7 | .6 SAG growth on substrates with various surface preparation                                                      |

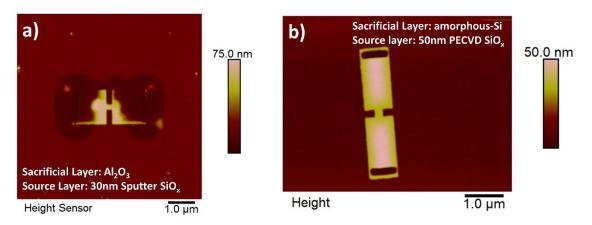

| Figure 7 | .7 Fabricated CELO structures after sacrificial layer removal a) Al <sub>2</sub> O <sub>3</sub> sacrificial layer |

| b        | o) amorphous-Si sacrificial layer                                                                                 |

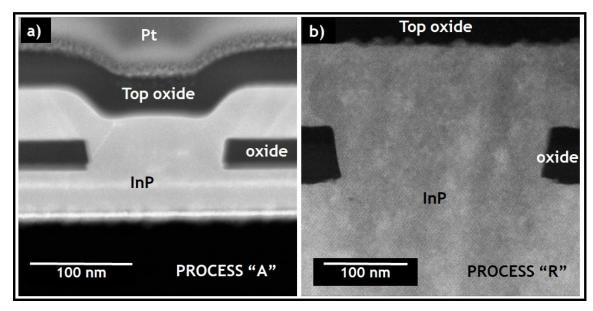

| Figure 7 | .8 cross-sectional TEM of CELO cavities fabricated with a) a-Si sacrificial layer and                             |

| P        | PECVD SiO <sub>x</sub> source layer b) resist sacrificial layer and HSQ source layer. Reprinted                   |

| (        | adapted) with permission from [12]. Copyright (2019) American Chemical Society.                                   |

|          |                                                                                                                   |

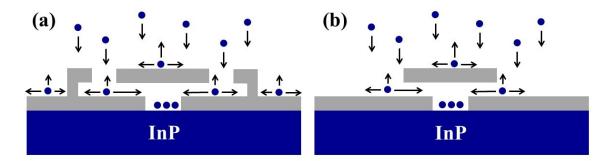

| Figure 7 | .9 Illustration of adatom motion during growth for CELO structures fabricated using                               |

| a        | a) a-Si sacrificial layer and PECVD SiO <sub>x</sub> source layer b) resist sacrificial layer and                 |

| ŀ        | HSQ source layer                                                                                                  |

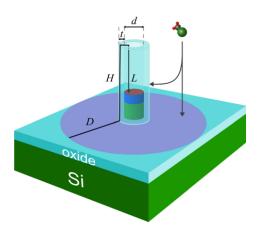

| Figure 7 | 7.10 Illustration of TASE nanowire structure used in [14]. Reprinted from [14], with                              |

| t]       | he permission of AIP Publishing                                                                                   |

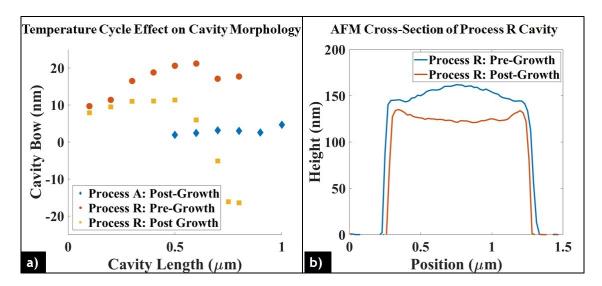

| Figure 7 | 7.11 Cavity bowing of a) type A and R templates before and after growth b) cross-                                 |

| S        | sectional profile for type R template as measured by AFM. Reprinted (adapted) with                                |

| р        | permission from [12]. Copyright (2019) American Chemical Society                                                  |

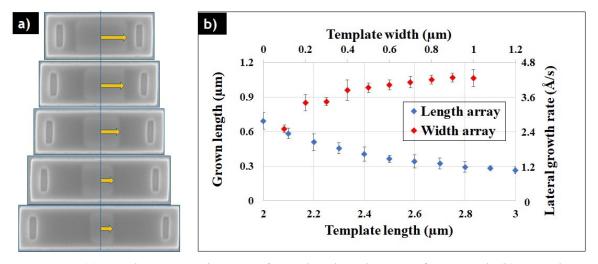

| Figure 7 | 7.12 (a) top-down SEM images of template length array after growth (b) growth-rate                                |

| a        | as a function of template length ( $w = 0.35 \mu m$ , $t = 50 nm$ ) and width (L = 1.0 $\mu m$ , $t =$            |

| 5        | 50 nm). Reprinted (adapted) with permission from [12]. Copyright (2019) American                                  |

| (        | Chemical Society                                                                                                  |

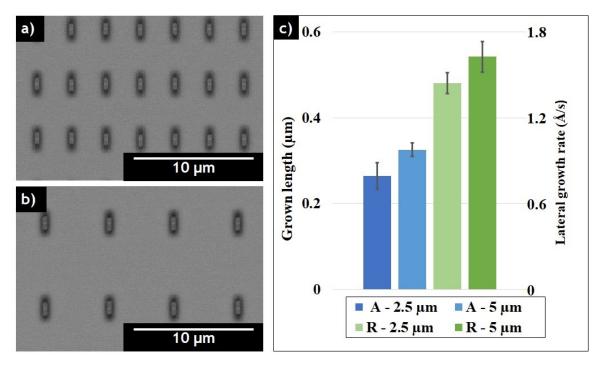

| Figure 7.13 top-down SEM of multiple structures with a) 2.5 $\mu$ m edge-to-edge spacing b) 5.0 |

|-------------------------------------------------------------------------------------------------|

| μm edge-to-edge spacing c) average growth length and rate as function of edge-to-               |

| edge spacing for type A and R templates. Reprinted (adapted) with permission from               |

| [12]. Copyright (2019) American Chemical Society                                                |

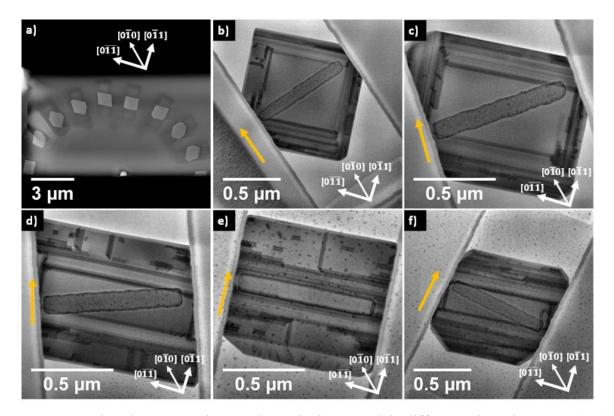

| Figure 7.14 Plan view TEM micrographs analyzing growth in different orientations on a (100)     |

| InP substrate. (a) shows the HAADF-STEM of the entire lamella with a flower pattern             |

| of CELO templates starting from the one oriented along [110] and with separations of            |

| 22.5° between consecutive templates. (b)-(f) BF-STEM of individual templates                    |

| oriented in different directions on the wafer. The nature and density of defects change         |

| as the orientations of the templates vary from [011] to [011]. The yellow arrows point          |

| to the direction the templates are oriented. Reprinted with permission from Aranya              |

| Goswami, paper submission [39].                                                                 |

| Figure 7.15 Cross-sectional TEM of 3HJ in type R template. Reprinted (adapted) with             |

| permission from [13]. Copyright (2019) American Chemical Society                                |

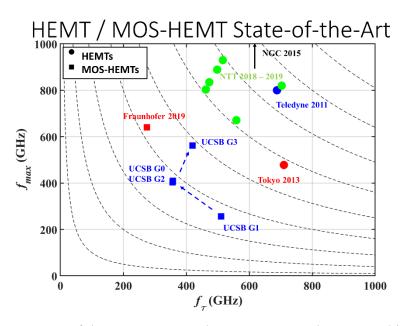

| Figure 8.1 State of the art HEMTs and MOS-HEMTs also reported in Table 8-1 163                  |

| Figure 8.2 Proposed double regrowth with regrowth reversal and self-align T-Gate to gate-       |

| recess process                                                                                  |

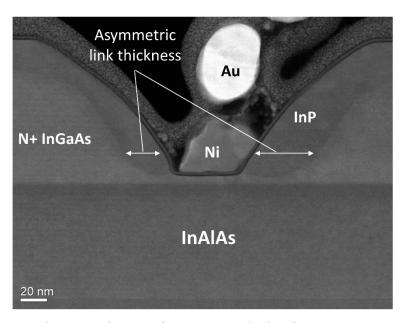

| Figure 8.3 Cross-section TEM image of $L_g = 40$ nm device from process run Ch4-L1G2SD4         |

| – an initial attempt at regrowth reversal using a non-self-aligned T-Gate                       |

| Figure 8.4 Proposed regrown extrinsic base, buried oxide HRT leveraging TASE 169                |

# 1. Introduction

Demand for high data rate communication systems has exploded in the last decade. Higher frequency systems enable access to higher data rates, currently unallocated bands, and wide bandwidth. As industry begins to introduce 5G technologies at 25-100 GHz, research must aim to facilitate >100 GHz communication systems. For amplifiers to exhibit low noise figure and high-power efficiency, their cutoff frequencies ( $f_{\tau}$  and  $f_{\text{max}}$ ) must be ~10x the operating frequency due to the 20 dB/decade gain roll off at high frequencies [1]. Because FETs exhibit lower parasitic resistance ( $R_S + R_G$ ) •  $g_m$  than bipolar transistors  $R_{bb}$  •  $g_m$ , they can realize smaller charging times (RC) and larger current gain cut-off frequencies ( $f_{\tau}$ ) which is useful for low-noise applications. Amplification at f > 600 GHz has been widely demonstrated using both HEMTs and HBTs [2]–[5]. Further improvement in cutoff frequencies is required to realize power efficient amplification for frequencies more than 100 GHz.

Despite the highly scaled dimensions of Si devices,  $f_{\tau}$  and  $f_{\text{max}}$  are limited to ~500 GHz due to large end capacitances intrinsic to very-large-scale integration (VLSI) devices [6]. InP-based HEMTs are widely used in RF applications because of their low parasitic capacitances and high transconductance ( $g_m$ ). State-of-the-art (SOA) high frequency HEMTs generally use an In<sub>x</sub>Ga<sub>1-x</sub>As/InAs composite channels that have smaller  $m^*$  than Si and thus large injection velocity ( $v_{inj}$ ). However, they are limited by large gate leakage current ( $I_G$ ) density, low gate insulator capacitance ( $C_{ins}$ ), and large source resistance ( $R_s$ ). Gate leakage current density determines the minimum thickness ( $t_{ins} = 5$  nm) of the In<sub>0.52</sub>Al<sub>0.48</sub>As gate insulator which also limits the intrinsic transconductance ( $g_{m,i}$ ) [7], [8]. The extrinsic transconductance is limited by large  $R_s$  associated with conduction across the widegap modulation doped "Link" layer.

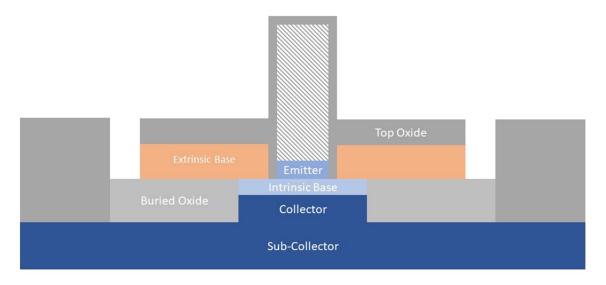

Figure 1.1a illustrates a typical HEMT cross-section. The channel region is controlled by the gate capacitor where the gate insulator is a wide bandgap semiconductor. The epitaxially smooth interface between the gate insulator and channel reduces scattering and enables extremely high  $g_m$ . To enable low parasitic gate-source ( $C_{GS}$ ) and gate-drain capacitances ( $C_{GD}$ ), the source and drain electrodes are located far from the gate (50 - 200 nm). To get electrons from the source to the channel, a conductive quantum well is used. The quantum well is comprised of modulation doped wide bandgap semiconductor barriers and a narrow bandgap, high mobility channel.

**Figure 1.1** Cross-sectional illustration of a standard a) InP-based HEMT b) III-V DC optimized MOSFET c) proposed InP-based MOS-HEMT

InP based high-electron mobility transistors (HEMTs) have been widely reported exhibiting  $f_{\tau}$  in excess of 400 GHz [7]–[12]. Recent devices report  $f_{\tau} > 600$  GHz and  $f_{\text{max}} > 800$  GHz using high-indium content, 8-10 nm thick channels [3], [13]. Chang *et al.* reported record  $f_{\tau} = 710$  GHz using a 5 nm thick In<sub>0.70</sub>Ga<sub>0.30</sub>As channel [14]. Pushing the cutoff frequencies beyond 1 THz requires increased  $g_{m,i}$  and reduced  $R_{S}$ .

To further scale  $g_{m,i}$  the gate insulator must be thinned. Due to the small conduction band offset (CBO) of metal /  $In_{0.52}Al_{0.48}As$  /  $In_xGa_{1-x}As$ , thermionic and tunneling currents are large. The larger CBO of an oxide truncates the thermionic emission and reduces the tunneling current at a given thickness, enabling further scaling of  $t_{ins}$  thus facilitating larger  $g_{m,i}$ .

Despite the attractive transport properties of III-V materials, III-V metal-oxide-semiconductor-field-effect-transistor (MOSFET) technology was elusive for many years due to large interface trap densities ( $D_{tt}$ ) at the semiconductor-oxide interface. Major recent advancements in oxide deposition facilitated an abundance of research in III-V MOS. Lee *et al.* reported  $g_{m,e} = 3.0$  mS/ $\mu$ m using a 6 nm pseudomorphic-InAs channel [15]. Huang *et al.* reported on improved drain conductance and reduced source-drain leakage using AlAs<sub>0.56</sub>Sb<sub>0.44</sub> back-barriers [16] and also demonstrated  $g_{m,e} > 2.0$  mS/ $\mu$ m for ultra-thin-body (UTB) devices [17]. Lin *et al.* reported the effect of channel thickness on  $g_{m,i}$  as well as record  $g_{m,e} = 3.45$  mS/ $\mu$ m [18], [19]. Regrowth processes were common among the MOS community, enabling a bottom-up process rather than the top-down processes often used for HEMTs. Despite the extraordinary DC results, most III-V MOSFET research targeted VLSI applications, imposing certain design constraints:

- 1. Device footprint requires small gate-source and gate-drain spacing resulting in larger parasitic  $C_{GS}$  and  $C_{GD}$

- 2. Low supply voltage limits the gate overdrive and degree of channel inversion

- 3. Intrinsic transistor designed to maximize  $I_{on}/I_{off}$  at set  $I_{off}$  requires spacers and/or barriers as well as a doped back-barrier. The former increases  $R_S$  and the latter introduces parasitic body capacitance

Additionally, because the intrinsic device is of primary interest, III-V MOSFET work aimed to simplify the extrinsic device. **Figure 1.1b** illustrates a typical III-V MOSFET cross-section optimized for VLSI. As a result, the above reported devices have large gate footprints and doped back-barriers, resulting in additional parasitic capacitances, making them unsuitable for high-frequency operation.

Our proposed device combines the MOSFET with the HEMT, illustrated in **Figure 1.1c**. The gated region is a MOSFET and contains a high-k gate dielectric with a pseudomorphic-InAs channel enabling increased  $C_{g-ch}$  and  $g_{m,i}$ . The access regions and extrinsic device are a HEMT. The source-drain is pulled 50 nm away from the gate and connected by a conductive quantum well while a T-Gate is used rather than an I-gate. To minimize  $R_S$ , a regrowth process, similar to that in [15]–[17], is proposed to place the source-drain directly on the channel. The RF performance of MOS-HEMTs is increased by:

- 1. Reducing intrinsic transit delays by reducing  $L_g$  and increasing  $g_{m,i}$

- 2. Reducing RC charging delays by adding Gate-Source ( $L_{GS}$ ) and Gate-Drain ( $L_{GD}$ ) recesses in order to reduce both  $C_{GS,f}$  and  $C_{GD,f}$

- 3. Reducing RC charging delays by increasing  $I_{DS}$  and  $g_{m,e}$  by reducing  $R_S$ .

Successful scaling requires lithographic resolution of the gate to be < 25 nm while the Gate-Contact alignment must be better than 20 nm. Further scaling challenges include aligning, resolving, and filling high-aspect ratio (<50 nm wide 200 nm tall) T-Gates. Alignment of the T-Gate to the Gate-Recess must be better than 20 nm and occurs late in the process after the 0-layer alignment marks have experienced significant processing. This thesis describes the design and fabrication of  $In_xGa_{1-x}As$  / InP MOS-HEMTs and is organized as follows:

Chapter 2 describes the basic operation of long and short gate-length MOSFETs and explores the effects of channel eigenstates in ultra-thin body (UTB) devices. Chapter 3 explains the regrowth fabrication process of MOS-HEMTs later described and discusses in detail process considerations and tradeoffs. Chapter 4 discusses the first Generation of regrown MOS-HEMTs which exhibited peak  $f_{\tau} = 511$  GHz for a drawn  $L_g = 8$  nm device.

Increased  $f_{\tau}$  compared to [20] was achieved by including an In<sub>0.52</sub>Al<sub>0.48</sub>As back-barrier, scaling the source-drain metal spacing, and decreasing resistance through the wide band-gap modulation doped region. Short gate length devices exhibited small power-gain cut-off frequencies  $(f_{\text{max}})$  due to excessively large gate resistance  $(R_G)$  which is attributed to poor T-Gate stem filling. Chapter 5 discusses second Generation devices which exhibited peak  $f_{\tau}$  = 356 GHz for a drawn  $L_g = 12$  nm device. The decrease in current-gain-cutoff-frequency is attributed to the ultra-thin channel ( $t_{ch} = 2.5$  nm) which limits the intrinsic transconductance. Moderately reduced  $R_S$  was achieved by digital etching through the modulation doped InP layer immediately prior to re-growing the N+ In<sub>0.53</sub>Ga<sub>0.47</sub>As source-drain regions. End resistance ( $R_{end}$ ) associated with charge imaging on the link semiconductor surface rather than in the quantum well due to the isotropic etch profile limited the benefit of link removal. Chapter 6 discuss third Generation devices which exhibited peak  $f_{\tau}$  = 420 GHz for a drawn  $L_g$ = 40 nm and peak  $f_{\text{max}}$  = 604 GHz for a drawn  $L_g$  = 50 nm device. Increased channel thickness, decreased  $t_{ins}$ , and reduced  $R_S$  compared to Generation 1 enabled extremely high  $g_{m,e} = 2.9$ mS/ $\mu$ m. The current gain cutoff frequency was limited by large  $C_{GS} > 0.85$  fF/ $\mu$ m and  $C_{GD} >$ 0.25 fF/ $\mu$ m. Improved gate resistance compared to Generation 1 enabled balanced ( $f_{\tau}$ ,  $f_{max}$ ). Generation 3 devices exhibited  $I_{off} \approx 10 \text{ nA/}\mu\text{m}$ ,  $I_g < 10 \text{ nA/}\mu\text{m}$ , and  $g_m / g_{ds} > 12$  demonstrating the significant improvements in leakage and electrostatics realizable with a MOS-HEMT. Chapter 7 introduces a confined selective regrowth technique – template assisted selective epitaxy (TASE) – and explores process considerations for template fabrication as well as the template effects on growth. Finally, Chapter 8 aims to summarize the work and propose future device generations for the MOS-HEMT and possible device applications for TASE.

### References

- [1] M. J. W. Rodwell *et al.*, "100-340 GHz Systems: Transistors and Applications," *Tech. Dig. Int. Electron Devices Meet. IEDM*, vol. 2018-Decem, pp. 14.3.1-14.3.4, 2019, doi: 10.1109/IEDM.2018.8614537.

- [2] K. M. K. H. Leong *et al.*, "850 GHz Receiver and Transmitter Front-Ends Using InP HEMT," *IEEE Trans. Terahertz Sci. Technol.*, vol. 7, no. 4, pp. 466–475, 2017, doi: 10.1109/TTHZ.2017.2710632.

- [3] X. Mei *et al.*, "First Demonstration of Amplification at 1 THz Using 25-nm InP High Electron Mobility Transistor Process," *IEEE Electron Device Lett.*, vol. 36, no. 4, pp. 327–329, 2015, doi: 10.1109/LED.2015.2407193.

- [4] J. Hacker, M. Urteaga, M. Seo, A. Skalare, and R. Lin, "InP HBT amplifier MMICs operating to 0.67 THz," *IEEE MTT-S Int. Microw. Symp. Dig.*, pp. 1–3, 2013, doi: 10.1109/MWSYM.2013.6697518.

- [5] A. Tessmann, A. Leuther, H. Massler, and M. Seelmann-Eggebert, "A high gain 600 GHz amplifier TMIC using 35 nm metamorphic HEMT technology," *Tech. Dig. IEEE Compd. Semicond. Integr. Circuit Symp. CSIC*, pp. 1–4, 2012, doi: 10.1109/CSICS.2012.6340102.

- [6] G. Foundaries, "22nm FD-SOI Technology," 2020. https://www.globalfoundries.com/solutions.

- [7] K. Shinohara *et al.*, "547-GHz ft In<sub>0.7</sub>Ga<sub>0.3</sub>As-In<sub>0.52</sub>Al<sub>0.48</sub>As HEMTs with reduced source and drain resistance," *IEEE Electron Device Lett.*, vol. 25, no. 5, pp. 241–243, 2004, doi: 10.1109/LED.2004.826543.

- [8] Y. Yamashita, A. Endoh, K. Shinohara, K. Hikosaka, and T. Matsui, "Pseudomorphic

- In<sub>0.52</sub>Al<sub>0.48</sub>As / In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs," *IEEE Electron Device Lett.*, vol. 23, no. 10, pp. 573–575, 2002, doi: 10.1109/LED.2002.802667.

- [9] K. Shinohara *et al.*, "Ultrahigh-speed pseudomorphic InGaAs/InAlAs HEMTs with 400-GHz cutoff frequency," *IEEE Electron Device Lett.*, vol. 22, no. 11, pp. 507–509, 2001, doi: 10.1109/55.962645.

- [10] D. Y. Yun *et al.*, "Impact of the source-to-drain spacing on the DC and RF characteristics of InGaAs/InAlAs high-electron mobility transistors," *IEEE Electron Device Lett.*, vol. 39, no. 12, pp. 1844–1847, 2018, doi: 10.1109/LED.2018.2876709.

- [11] T. Takahashi *et al.*, "Enhancement of fmax to 910 GHz by adopting asymmetric gate recess and double-side-doped structure in 75-nm-gate InAlAs/InGaAs HEMTs," *IEEE Trans. Electron Devices*, vol. 64, no. 1, pp. 89–95, 2017, doi: 10.1109/TED.2016.2624899.

- [12] T. Takahashi *et al.*, "Maximum frequency of oscillation of 1.3 THz obtained by using an extended drain-side recess structure in 75-nm-gate InAlAs/InGaAs high-electron-mobility transistors," *Appl. Phys. Express*, vol. 10, no. 2, 2017, doi: 10.7567/APEX.10.024102.

- [13] H. B. Jo *et al.*, " $L_g = 25$  nm InGaAs/InAlAs high-electron mobility transistors with both  $f_T$  and  $f_{max}$  in excess of 700 GHz," *Appl. Phys. Express*, vol. 12, no. 5, 2019, doi: 10.7567/1882-0786/ab1943.

- [14] E. Y. Chang, C. I. Kuo, H. T. Hsu, C. Y. Chiang, and Y. Miyamoto, "InAs thin-channel high-electron-mobility transistors with very high current-gain cutoff frequency for emerging submillimeter-wave applications," *Appl. Phys. Express*, vol. 6, no. 3, pp. 1–4, 2013, doi: 10.7567/APEX.6.034001.

- [15] S. Lee *et al.*, "Highly scalable raised source/drain InAs quantum well MOSFETs exhibiting  $I_{ON} = 482 \, \mu\text{A}/\mu\text{m}$  at  $I_{OFF} = 100 \, \text{nA}/\mu\text{m}$  and  $V_{DD} = 0.5 \, \text{V}$ ," *IEEE Electron Device Lett.*, vol. 35, no. 6, pp. 621–623, 2014, doi: 10.1109/LED.2014.2317146.

- [16] C. Y. Huang *et al.*, "Reduction of leakage current in In<sub>0.53</sub>Ga<sub>0.47</sub>As channel metal-oxide-semiconductor field-effect-transistors using AlAs<sub>0.56</sub>Sb<sub>0.44</sub> confinement layers," *Appl. Phys. Lett.*, vol. 103, no. 20, pp. 0–4, 2013, doi: 10.1063/1.4831683.

- [17] C. Y. Huang *et al.*, "12 nm-gate-length ultrathin-body InGaAs/InAs MOSFETs with 8.3•10<sup>5</sup> I<sub>ON</sub>/I<sub>OFF</sub>," *Device Res. Conf. Conf. Dig. DRC*, vol. 2015-Augus, p. 260, 2015, doi: 10.1109/DRC.2015.7175669.

- [18] J. Lin, D. A. Antoniadis, and J. A. Del Alamo, "Impact of Intrinsic Channel Scaling on InGaAs Quantum-Well MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 11, pp. 3470–3476, 2015, doi: 10.1109/TED.2015.2444835.

- [19] J. Lin, X. Cai, Y. Wu, D. A. Antoniadis, and J. A. Del Alamo, "Record maximum transconductance of 3.45 mS/μm for III-V FETs," *IEEE Electron Device Lett.*, vol. 37, no. 4, pp. 381–384, 2016, doi: 10.1109/LED.2016.2529653.

- [20] J. Wu, Y. Fang, B. Markman, H. Y. Tseng, and M. J. W. Rodwell, " $L_g$ =30 nm InAs Channel MOSFETs Exhibiting  $f_{max}$ =410 GHz and  $f_i$ =357 GHz," *IEEE Electron Device Lett.*, vol. 39, no. 4, pp. 472–475, 2018, doi: 10.1109/LED.2018.2803786.

# 2. FET Theory and Design

In this chapter, ideal MOSFET theory and practical design considerations will be discussed. Ballistic FET theory for quantum well devices will be derived, and quantum mechanical effects in the channel included to provide further guidance for future high frequency FET/HEMT channel design. High frequency figure of merits and the common-source small-signal-equivalent-circuit (SSEC) are introduced. Radio frequency (RF) measurement, pad de-embedding, and SSEC extraction are also discussed. Multiple device parameters used throughout the rest of this thesis are defined and discussed in this chapter.

# A. Principle of Operation

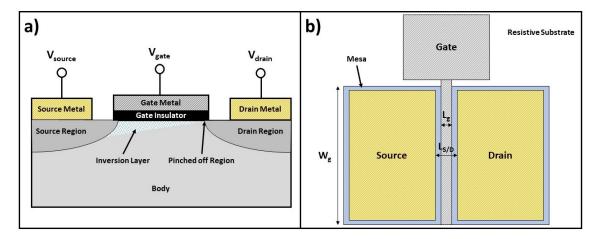

A MOSFET is a four-terminal device: gate, source, drain and body [1]. Usually the body is tied to the source and will be assumed to be grounded. A MOSFET, as all FETs and HEMTs, operates based on the field effect; charges on the controlling terminal (gate) induce opposite charges elsewhere in the device. In the case of a MOSFET, charge on the gate induces charge in the channel which is supplied by the source and drain. **Figure 2.1** illustrates a standard MOSFET cross-section as well as a top-down layout. A MOSFET has three regions of operation: thermionic emission (subthreshold), resistive (linear), and current source (saturation). The basic operation of a MOSFET can be understood by considering a long gate length device (i.e.  $L_g \gg \lambda_n$  where  $\lambda_n$  is the electron mean-free-path). Many textbooks detail MOSFET operation in the long-gate length limit [2]–[4].

**Figure 2.1** a) cross-sectional illustration of long channel MOSFET operating at  $V_{DS} = V_{GS} - V_{TH}$  b) top-down view of a typical MOSFET

In the long gate length limit, transistors are simple to describe. A n-channel transistor drain current can be written:

$$I_{DS} = q \cdot n_{ch} \cdot v_n \tag{2.1.1}$$

where q is the elementary charge,  $n_{ch}$  is the channel charge density, and  $v_n$  is the electron velocity. In the linear region, the transistor is simply a resistor where:

$$n_{ch} = C_{GS}(V_{GS} - V_{TH}) (2.1.2)$$

Where  $C_{GS}$  is the intrinsic gate-source capacitance and  $V_{TH}$  is the threshold voltage.  $C_{GS}$  describes the capacitive coupling of the gate-metal to the surface potential of the semiconductor and is described in more detail in **Section D**. The threshold voltage can be thought of as the voltage required to make the channel conductive. For long gate length, thick oxide devices,  $C_{GS} \approx C_{ox}$ . If the gate length  $(L_g)$  is much longer than the electron mean-free-path, implying many scattering events occur within the channel, electron mobility  $(\mu_n)$  can be used to describe the velocity:

$$v_n = \mu \mathcal{E} = \mu \frac{V_{DS}}{L_q} \tag{2.1.3}$$

where  $\mathcal{E}$  is the lateral electric field and  $V_{DS}$  is the drain-source voltage. The electron mobility describes the dependence of electron velocity on electric field inside the semiconductor, in the direction of current flow. The channel potential is therefore lower at the drain edge than at the source edge. Combining equations (2.1.1) - (2.1.3) and integrating the channel potential from source-to-drain, we get the familiar expression:

$$\frac{I_{DS,lin}}{W_g} = \left(\frac{q\mu C_{ox}}{L_g}\right) \cdot \left[ (V_{GS} - V_{TH}) \cdot V_{DS} - \frac{{V_{DS}}^2}{2} \right]$$

(2.1.4)

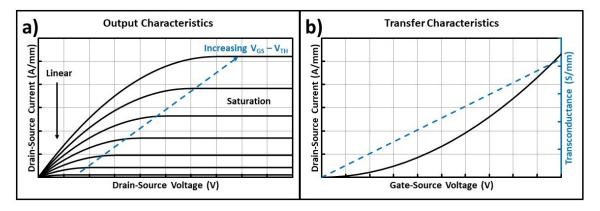

Simply put – in the linear region, a MOSFET is a resistor where the lateral field, from source-to-drain is modulated by applying  $V_{DS}$ . The resistance of the channel is modulated by increasing or decreasing the channel charge density which is done by modulating ( $V_{GS} - V_{TH}$ ). Figure 2.2 illustrates an ideal long gate length, MOSFET transfer and output characteristics.

Figure 2.2 Ideal long  $L_g$  MOSFET a) output characteristics b) transfer characteristics at large  $V_{DS}$  (saturation region)

If a large  $V_{DS}$  is applied, the drain side depletion region will begin to encroach on the channel. When the channel-surface potential at the drain edge of the gate is reduced below  $V_{TH}$ , the channel is "pinched off", illustrated in **Figure 2.1**. Beyond this point, all additional applied  $V_{DS}$  drops across the drain-side depletion region. Applying more drain voltage does not result in more current beyond this point as the lateral electric field, beneath the channel,

is saturated. This is called the saturation regime – where the transistor behaves as a current source – and occurs when  $V_{DS} \ge (V_{GS} - V_{TH})$ . Equation (2.1.4) then becomes:

$$\frac{I_{DS,sat}}{W_g} = \left(\frac{q\mu C_{ox}}{L_g}\right) \cdot \frac{(V_{GS} - V_{TH})^2}{2} \tag{2.1.5}$$

Transconductance is a metric analogous to gain and describes how well a voltage on the gate modulates the conductivity of the overall device:

$$g_m \equiv \frac{dI_D}{dV_{GS}} \tag{2.1.6}$$

Using equation (2.1.5) and (2.1.6):

$$g_m = \left(\frac{q\mu C_{ox}}{L_a}\right) \cdot (V_{GS} - V_{TH}) \tag{2.1.7}$$

Transconductance is linear when the transistor is operating in saturation mode and increases without bound. The transfer characteristics and transconductance of an ideal, long  $L_g$  MOSFET are illustrated in **Figure 2.2b**.

The final regime of interest for MOSFETs is the thermionic region, often referred to as subthreshold. Below threshold, the Fermi level ( $E_F$ ) is far below the channel conduction band minimum and the channel charge density is dominated by thermal physics. When  $E_F \ll E_C$  the carrier concentration can be described using Boltzmann statistics:

$$n_{ch} = N_C \exp\left(\frac{-(E_C - E_F)}{k_B T}\right) \tag{2.1.8}$$

Where  $k_B$  is the Boltzmann constant, T is the device junction temperature, and  $N_C$  is the conduction band effective density of states. In this regime, the current is controlled by the rapidly changing channel charge density. Relating the channel surface Fermi-level position to the gate-voltage, using  $(E_C - E_F) = q \cdot (V_{GS} - V_{TH})$ , we can write:

$$\frac{I_{DS}}{W_g} = I_0 \exp\left(\frac{q(V_{GS} - V_{TH})}{mk_B T}\right) \tag{2.1.9}$$

where  $I_0$  is the "dark current" and m describes the degree of gate capacitive coupling to the channel's surface potential. Any capacitor in parallel with the gate-oxide and source will result in m > 1.

#### B. Subthreshold Slope & Interface Defects

Subthreshold slope (SS) is a figure-of-merit (FOM) commonly used to characterize the thermionic region of operation and describe the off-state performance of a MOSFET:

$$SS \equiv \left[ \frac{d(\log_{10} I_D)}{dV_{GS}} \right]^{-1} \tag{2.2.1}$$

Subthreshold slope is usually reported in mV/decade and represents the amount of gate voltage required to modulate the drain current by an order of magnitude. If a significant density of defects ( $D_{it}$ ) exists at the gate-insulator / semiconductor interface, some  $V_{GS}$  will be required to fill / empty these states and SS will increase. Historically it has been difficult to form defect free dielectrics on III-V surfaces [5], [6]. Defects often sit at the oxide / semiconductor interface and manifest themselves as a parallel capacitance ( $C_{it}$ ) that screens the semiconductor surface potential from the gate potential. Including  $C_{it}$ , SS becomes [3]:

$$SS = ln(10) \left(\frac{k_B T}{q}\right) \left(\frac{C_{ox} + C_{it}}{C_{ox}}\right)$$

(2.2.2)

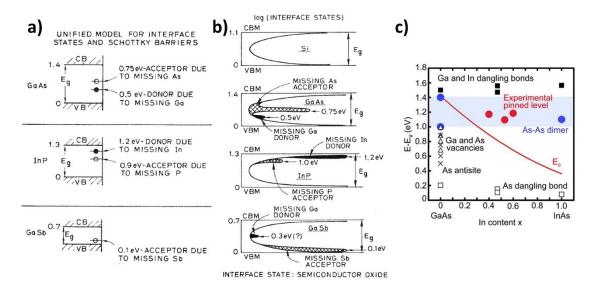

Defects at the semiconductor / dielectric interface can be of many different forms: dangling bonds, vacancies, anti-sites, and native oxides [6]. Significant  $D_{it}$  can result in Fermi-level pinning which prevents carrier modulation. From [7] and [8], the Fermi level of GaAs is surface pinned for  $D_{it} \approx 10^{12} - 10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup>. Concentrations below this allow carrier modulation but limit the channel conductivity and degrade transistor performance. Defects

can exist in the channel material's bandgap ( $E_g$ ), valence band ( $E_V$ ), or conduction band ( $E_C$ ). Defects that are filled or emptied over the  $V_{GS}$  range of interest will affect the performance of the transistor. Spicer *et al.* demonstrated the energy levels of donors and acceptors due to missing atoms and proposed the levels of interfacial states for InP, GaAs, and GaSb [9] – shown in **Figure 2.3**. The energy level of Fermi-level pinning has been calculated for In<sub>x</sub>Ga<sub>1-x</sub>As [10] and is also shown in **Figure 2.3**. Recent results of III-V MOSFETs on InAs [11], InGaAs [12], and InP [13] suggest that the defect energy levels that exist inside the semiconductor bandgap are likely more detrimental to SS than defects deep in the conduction band.

**Figure 2.3** a) unified model of interface states and associated Schottky barriers of GaAs, InP, and GaSb. Reprinted with permission from [9]. © 1980 AIP Publishing LLC b) Energy level of interface states of GaAs, InP, and GaSb. Reprinted with permission from [9]. © 1980 AIP Publishing LLC c) Fermi level pinning energy levels relative to valence band maximum for In<sub>x</sub>Ga<sub>1-x</sub>As as a function of Indium content. Reprinted with permission from [10]. © Copyright 2013 IEEE

Formation of an oxide can remove Fermi level pinning on Si; III-V oxides move or modify the Fermi-level pinning [14]. Additionally, the mechanism for oxide formation on III-V is different than on silicon. Oxygen moves through the oxide to form  $SiO_2$  at the Si-oxide interface where III-V atoms move outward to form oxides [15], leaving behind interface defects. Finally, wet chemical treatment can also cause the formation of surface oxides, requiring careful attention be paid to surface preparation prior to high-k formation on III-Vs. In summary, surface and bulk chemistry of the channel material need to be carefully chosen and understood to form a low  $D_{ii}$  high-k gate dielectric on III-V semiconductors. Surface preparation, treatment, channel material, and choice of high-k gate dielectrics are discussed in detail in [6], [16]–[18].

### C. Short-Channel Effects

MOSFETs are two-dimensional devices and thus require 2D electrostatics to be properly described. So far the device has been treated in one-dimension, ignoring the effect of the drain voltage on the channel surface potential. At long gate lengths, only the drain-edge of the channel potential is affected by the drain voltage. As the gate-length is reduced, proportionally more of the channel is coupled to the drain. At extremely short-gate lengths, the gate losses control of the channel potential and the drain dictates device performance.

If the gate length is short compared to the drain-side depletion width, the drain will also modulate the channel surface potential. This encroachment of the drain depletion width into the channel lowers the surface potential which effectively decreases  $V_{TH}$ . This effect is referred to as drain-induced-barrier-lowering (DIBL) and is the root of most short channel effects:

$$DIBL \equiv \frac{V_{TH,sat} - V_{TH,lin}}{V_{DS,sat} - V_{DS,lin}}$$

(2.3.1)

DIBL is related to the drain-source capacitance ( $C_{DS}$ ) and causes threshold voltage rolloff, increase in subthreshold slope, and output conductance modulation. At long gate lengths,  $C_{DS}$  /  $C_{ox}$  is small so short channel effects are small. As the gate length decreases,  $C_{DS}$  /  $C_{ox}$  increases because  $C_{ox}$  decreases and the drain begins to modulate the channel surface potential.

Subthreshold slope increases because the drain-channel modulation prevents ideal gate-channel modulation. Output conductance modulation occurs because of the encroachment of the drain-side depletion width into the gated region. Beyond pinch-off, additional  $V_{DS}$  further depletes the drain-side, lowering the source-channel barrier under the gate. This effectively shortens the gate-length. If the depleted region is a significant portion of the nominal gatelength, the output conductance increases.

To improve short-channel effects, a MOSFET must be designed so that the gate has stronger capacitive coupling than the drain. Brews *et al.* derived empirical formulas for inversion mode FETs and provided guidance regarding the aspect ratios where devices would begin to suffer from short-channel effects [19]. Planar inversion mode FETs generally have better electrostatic coupling when the substrate doping is high, creating a more tightly confined inversion layer. However, this technique creates another capacitive term which can further reduce SS and increase RC charging times. Consequently, other confinement techniques are desired. Confinement of channel carriers can be achieved by using heterobarriers (common to HEMTs) or oxides (common to SOI or III-V on insulator) as the channel back-barrier. A commonly used parameter to characterize the 2D electrostatics in a MOSFET is the natural length ( $\lambda$ ):

$$\lambda = \sqrt{\frac{\varepsilon_{ch}}{N\varepsilon_{ins}} t_{ins} t_{ch}}$$

(2.3.2)

where N is the number of gate fingers,  $\varepsilon_{ch}$ ,  $\varepsilon_{ins}$  is the dielectric permittivity of the channel and gate-insulator respectively, and  $t_{ins}$ ,  $t_{ch}$  are the thicknesses of the gate-insulator and

channel respectively. The natural length describes the ratio of the electrostatic strength of the gate and drain and depends on the structure of the device. A smaller natural length implies better gate control. Double-gates, finFETs, and gate-all-around structures have smaller  $\lambda$  than a planar FET. Generally, a transistor should be designed so  $\lambda > 5$  to mitigate short-channel effects. Because III-V materials have large dielectric permittivity ( $\varepsilon_{ch}$ ), a III-V channel of a given geometry will have worse electrostatics than a Si device.

### D. Gate-Channel Capacitance

Gate control of the channel is the foundation of MOSFET operation. In previous sections,  $C_{GS} = C_{GS,i} = C_{g\text{-}ch}$  was used to describe the capacitive coupling of the gate potential to the channel charge density. A larger gate-channel capacitance results in more charge for the same applied gate-voltage.

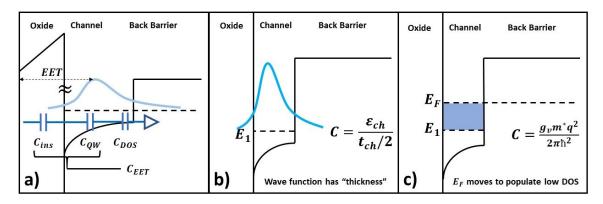

**Figure 2.4** illustration of a) the gate-channel series capacitance b)  $C_{QW}$  and c)  $C_{DOS}$

The total Gate-Channel capacitance ( $C_{GS,i}$ ) in a highly scaled quantum well device is series combination of 3 capacitors, illustrated in **Figure 2.4**.

$$C_{GS,i}^{-1} = C_{ins}^{-1} + C_{OW}^{-1} + C_{DOS}^{-1}$$

(2.4.1)

Where  $C_{ins}$  is that gate insulator capacitance,  $C_{QW}$  is the wave-function capacitance (referred to as the quantum well capacitance in this thesis), and  $C_{DOS}$  is the density of states

capacitance. The gate insulator capacitance is the most discussed and is simply the parallel plate capacitance that a MOSFET is usually designed around.  $C_{QW}$  arises due to the spatial separation of the channel electron wave-function from the insulator / semiconductor interface:

$$C_{QW} \approx \frac{\varepsilon_{ch}}{t_{ch}/2} \tag{2.4.2}$$

$C_{DOS}$  occurs because the channel Fermi-level must move to provide charge. Because the density of states is low for low effective mass materials, the resulting capacitance is small:

$$C_{DOS} = \frac{d(qN_S)}{d\left(\frac{E_F - E_1}{q}\right)} = \frac{g_v \frac{q^2 m^{*2}}{\pi \hbar^2}}{1 + \exp\left(-\frac{E_F - E_1}{k_B T}\right)}$$

(2.4.3)

where  $g_v$  is the electronic band degeneracy. In the highly degenerate limit (i.e. when the channel is strongly inverted):

$$\lim_{(E_F - E_1) \to \infty} \exp\left(-\frac{E_F - E_1}{k_B T}\right) = 0$$

Then:

$$C_{DOS} = g_v \frac{q^2 m^{*2}}{\pi \hbar^2} \tag{2.4.4}$$

Because series capacitors result in an overall smaller capacitance,  $C_{GS,i}$  in highly scaled III-V devices are limited by  $C_{DOS}$ . Because the electrostatic gate control vs. drain control is important for both VLSI (SS and DIBL) and RF devices  $(g_m/g_{ds})$ , the electrostatic terms can be grouped:

$$C_{EET}^{-1} = C_{ins}^{-1} + C_{QW}^{-1} (2.4.5)$$

#### E. Ideal Ballistic MOSFET Theory