### **UC Riverside**

#### **UC Riverside Electronic Theses and Dissertations**

#### **Title**

Design-for-Reliability on Thermal Management and ESD Protection of Integrated Circuits

#### **Permalink**

https://escholarship.org/uc/item/6tm0c72g

#### **Author**

Li, Cheng

#### **Publication Date**

2021

## **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at https://creativecommons.org/licenses/by/4.0/

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA RIVERSIDE

# Design-for-Reliability on Thermal Management and ESD Protection of Integrated Circuits

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Cheng Li

March 2022

Dissertation Committee:

Dr. Albert Wang, Chairperson

Dr. Ming Liu Dr. Sheldon Tan

| The Dis | ssertation of Cheng Li is approved: |                       |

|---------|-------------------------------------|-----------------------|

|         |                                     |                       |

|         |                                     |                       |

|         |                                     |                       |

|         |                                     |                       |

|         |                                     |                       |

|         |                                     |                       |

|         |                                     | Committee Chairperson |

University of California, Riverside

#### **ACKNOWLEDGEMENTS**

I would like to take this opportunity to sincerely express my gratitude to my research advisor, Dr. Albert Wang, heartfeltly, during my Ph.D. studies at the University of California, Riverside (UCR), for continuous support, encouragement, supervision, and academic mentorship. His conscientious spirit towards work and rich experience in life illuminate me a lot and formulate my own way of critical thinking and time arrangement skills, especially communication skills. I have been inspired by his motivation, broader knowledge, and affluent ideas through my research periods and I hope to absorb them to guide my future work career and thrive in my rest life. It's been a great fortune for me to have him as my advisor.

I would like to thank the Department of Electrical and Computer Engineering at the University of California, Riverside, especially the members of my dissertation committee, Dr. Ming Liu and Dr. Sheldon Tan, for their supports of my dissertation research.

I would thank all my laboratory mates with whom I have conducted researches together, including Dr. Fei Lu, Dr. Chen Qi, Dr. Chenkun Wang, Dr. Feilong Zhang, Mr. Mengfu Di, and Ms. Zijin Pan. Through discussion on the research work and help from life, we make a unified group which is beneficial to my study. Also, I want to thank my senior laboratory mates Dr. Zongyu Dong and Dr. Bo Qin, their professional guidance on my work and concerns for my life.

I appreciate the opportunity to do the design internship on Fairchild-Onsemi and thanks to Dr. Bin Zhao and Mr. Burl Fermandes. Also, I want to express my gratitude to the group of the School of Integrated Circuits, Tsinghua University for my research support

such as Dr. Huaqiang Wu, Dr. Junxu, Dr. Rongren Liang, Dr. Weijun Cheng, Mr. Tao Zhong, and Ms. Li Zong.

Last but not least, I would like to express my deepest gratitude to my lovely parents Mr. Jinchuan Li and Ms. Li Liang, also my passionately devoted fiancée Ms. Shuai Xu. Thanks for their generous and endless love to me. They are always with me when I go through tough situations and provide encouragement and support to me.

#### ABSTRACT OF THE DISSERTATION

Design-for-Reliability on Thermal Management and ESD Protection of Integrated Circuits

by

#### Cheng Li

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, March 2022 Dr. Albert Wang, Chairperson

Transistor self-heating is a grand challenge in modern integrated circuit (IC) chip designs. Chip-scale thermal management is required to ensure IC design reliability. As IC technologies rapidly advance into few-nm nodes, while performance, complexity and size of chips continue to increase, heat dissipation becomes a technical bottleneck to advanced chips. For example, data servers and mobile electronics increasingly rely on high clock frequency, multiple-core CPU and GPU, which are extremely power-hungry and are heavy heat generators. However, portable devices, such as smartphones, have little room to accommodate traditional heat dissipation means. Further, advanced IC technologies, such as silicon-on-insulator (SOI) and FINFET, are inherently in thermal conduction, hence, making transistor self-heating even severer at the chip level. In addition, advanced 3D packaging makes it much harder to dissipate heat from IC dies. Together, advanced high-performance, complex chips made in advanced IC technologies are essentially big heat generators, unfortunately, poor thermal conduction makes IC chips increasingly suffering

vi

from heat-induced performance degradation and reliability problems. Existing on-chip thermal sensors used to monitor temperature typically use thermocouple, thermistor and PN diode devices, which are placed on a chip in a coplanar manor, i.e., laterally side-byside, with the circuit blocks to be monitored. There are several major technical disadvantages of making accurate full-chip thermal management impractical using the existing thermal-sensing techniques. First, a thermal sensor is laterally far away from a transistor to be monitored, making it impossible to accurately detect any real hot spots, which are often at the corners of a conduction channel of a transistor. Second, these thermal sensors are bulky, hence, impossible to construct a very large thermal sensor network on a chip to realize full-chip thermal mapping. Consequently, existing on-chip thermal sensing may only achieve circuit block level thermal-sensing resolution, which makes practical thermal management impractical. In order to fundamentally address the transistor selfheating problem and enable effective full-chip thermal management, novel thermal sensing techniques are needed to accurately detect the transient hot spots at the single transistor level, which hence requires transistor-level thermal sensing resolution. Further, to enable accurate run-time full-chip thermal management, a large on-chip thermal sensor mash network is required to achieve transistor-level thermal sensing resolution, which in turn, make full-chip thermal management practical. In this dissertation, I proposed and prototyped a novel under-FET thermal sensor device structure, which utilizes a vertical PN junction. This PN junction thermal sensor is made inside a through-silicon via (TSV) type vertical hole, which is placed directly under a MOSFET, hence being able to detect the transient hot spot in a MOSFET channel. Since the TSV-like under -FET thermal sensor

does not take any extra "lateral" Si die area and is placed right underneath the heating source, i.e., the MOSFET channel, it allows constructing a large thermal sensor mash network on a chip to realize transistor-level thermal sensing resolution without taking extra IC die area. Using the new under-FET thermal sensing technique, a machine-learning (ML) algorithm is proposed to enable run-time full-chip thermal management, which can fundamentally resolve the transistor self-heating-induced chip performance degradation and thermal reliability problems.

Electrostatic discharge (ESD) protection is another major IC reliability challenge, particularly for complex chips implemented in advanced IC technologies. For the past six decades, substantial R&D efforts have been devoted to developing various on-chip ESD protection solutions. Yet, as IC technologies continue to shrink, while IC performance and complexity continuously increase, on-chip ESD protection for advanced ICs becomes extremely challenging. In general, any ESD protection structures inevitably induce the ESD-design overhead problem, including parasitic capacitance, noises and leakages, as well as ESD device size and layout problem. The semiconductor industry urgently needs novel on-chip ESD protection solutions to overcome the ESD-design overhead problems. In this desertion, I proposed and demonstrated three novel on-chip ESD protection structures aiming to address the ESD-design overhead problem. The first new ESD protection structure proposed is a vertical TSV-like diode, which is a truly vertical PNdiode ESD protection device residing inside a TSV-like vertical hole under a bonding pad. Unlike any traditional PN diode ESD protection devices, which always require lateral discussion elements for electrical interconnections, the new TSV-like ESD diode can conduct ESD pulses and ESD-induced heat vertically, hence, significantly improving ESD protection while minimizing Si die area consumed by large ESD protection structures. The second new ESD protection structure is a cell-based Sudoku-type diode-trigger silicon-controlled rectifier (DTSCR) low-triggering ESD protection sub-circuit structure. The third novel ESD protection structure is a single-crystalline graphene-based nano-electromechanical system (gNEMS) ESD protection switch device. This gNEMS ESD protection structure is novel in that it is a mechanical switch made in the back-end-of-line (BEOL) in CMOS, which can be turned on/off extremely fast to provide both human body models (HBM) and charged device model (CDM) ESD protection. Both theoretical and experimental studies were conducted to validate the three novel ESD protection structures

Chapter 1 introduces the transistor self-heating problem, which is the root cause of the thermal reliability problem of modern IC chips. Chapter 2 discusses the new TSV-type under-FET thermal sensor device and the ML-based full-chip thermal management method. Chapter 3 gives an induction of ESD protection fundamentals and graphene material background. Chapter 4 presents the novel vertical TSV-like ESD protection diode structure of the TCAD mixed-mode ESD protection design calibration flow. Chapter 5 discusses the new Sudoku-type ESD protection array and theoretical design analysis. Chapter 6 discusses the novel single-crystallin graphene-based gNEMS ESD switch structure. Chapter 7 summarizes my Ph.D. research achievements.

# **Contents**

| Chapter 1 | Introduction to heat dissipation and thermal management     | 1  |

|-----------|-------------------------------------------------------------|----|

| 1.1 H     | leat dissipation background                                 |    |

| 1.1.1     | Heat dissipation system for different sizes of applications |    |

| 1.1.2     | Heat generation with the chip development                   |    |

| 1.1.3     | CMOS Technology influence on the heat dissipation           |    |

| 1.2 T     | hermal management background                                |    |

| 1.2.1     | Temperature monitor necessity                               |    |

| 1.2.2     | Thermal sensors category                                    |    |

| 1.2.3     | Run-time thermal management flow                            | 9  |

| Chapter 2 | Under-FET thermal management for design reliability         | 11 |

| 2.1 T     | he motivation of Under-FET thermal management               | 11 |

| 2.1.1     |                                                             |    |

| 2.1.2     | •                                                           |    |

| 2.2 Iı    | n-hole diode thermal sensor fabrication                     | 14 |

| 2.2.1     | The deep silicon etching procedure                          |    |

| 2.2.2     | PN junction formation                                       |    |

| 2.3 II    | n-hole diode characterization                               | 21 |

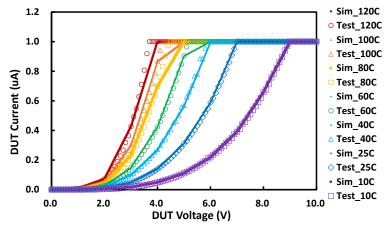

| 2.3.1     | Thermal property validated by TCAD simulation               | 21 |

| 2.3.2     | Thermal property validated by I-V-T testing                 | 23 |

|           | un-time thermal monitoring system                           |    |

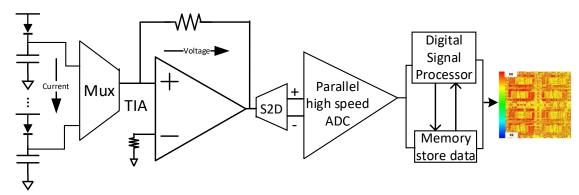

| 2.4.1     | Thermal management topology                                 |    |

| 2.4.2     | Exemplar thermal monitoring blocks for thermal management   |    |

| 2.4.3     | Exemplar victim modules and machine learning strategy       | 32 |

| Chapter 3 | Introduction to the ESD protection and graphene             | 30 |

| 3.1 E     | SD protection background                                    | 36 |

| 3.1.1     | ESD characterization and standard models                    | 36 |

| 3.1.2     | ESD testing methods and design window                       | 39 |

| 3.1.3     | ESD common structures and protection strategy               |    |

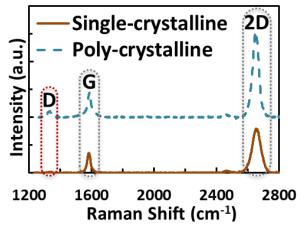

| 3.2 C     | Fraphene material background                                | 44 |

| 3.2.1     | Graphene advantageous properties                            |    |

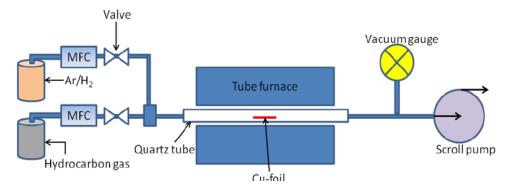

| 3.2.2     | Graphene material synthesis                                 | 45 |

| Chapter 4 | TSV-based ESD protection and TCAD flow for calibration      | 47 |

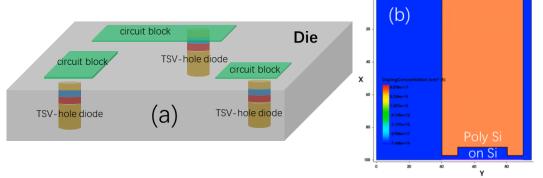

| 4.1 V     | Vertical TSV-like diode ESD protection design               | 47 |

| 4.1.1     | Vertical TSV-like diode for distribution ESD protection     |    |

| 4.1.2     | TCAD comprehensive simulation on vertical TSV-like diode    |    |

| 4.1.3     | TLP validation on vertical TSV-like diode                   |    |

|           | CAD Mixed-mode ESD flow for Calibration                     |    |

| 4.2.1     | TCAD ESD simulation flow overview                           |    |

| 4.2.2     | TCAD ESD calibration methodology                            |    |

| 4.2.3     | TCAD ESD calibration results                                | 57 |

| Chanter 5 | 3D TCAD ESD simulation and sudoku DTSCR design              | 65 |

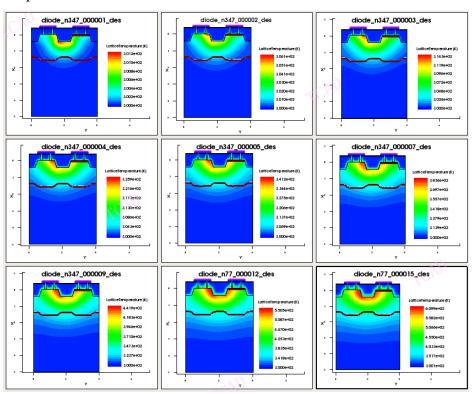

| 5.1 2D vs 3D TCAD ESD simulation                                           | 65  |

|----------------------------------------------------------------------------|-----|

| 5.1.1 Diode structure simulated by the TCAD for 2D and 3D                  | 65  |

| 5.1.2 Mesh density influence on the TCAD simulation                        |     |

| 5.1.3 I-V-T behaviors on the TCAD ESD simulation                           |     |

| 5.1.4 ESD thermal map and design guidelines                                |     |

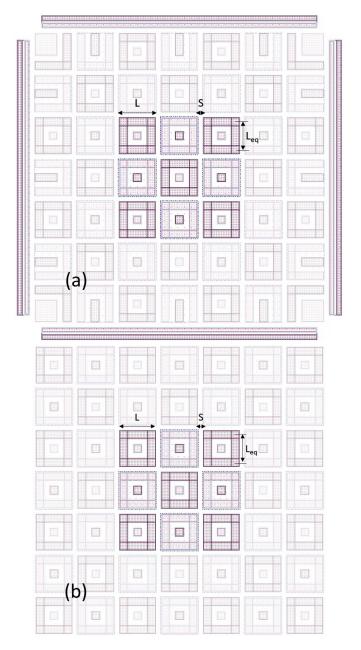

| 5.2 Overview of sudoku and finger structures for both SCR and DTSCR        | 76  |

| 5.2.1 Conventional finger-type SCR and DTSCR structure                     | 76  |

| 5.2.2 Sudoku-type SCR and DTSCR core structure                             | 79  |

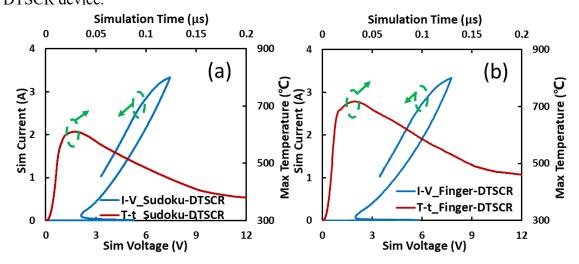

| 5.3 3D TCAD transient HBM ESD simulation analysis                          |     |

| 5.3.1 HBM simulation comparison of sudoku array and finger SCR             |     |

| 5.3.2 HBM simulation comparison of sudoku array and finger DTSCR           |     |

| 5.4 3D TCAD transient CDM ESD simulation analysis                          |     |

| 5.4.1 CDM simulation comparison of sudoku array and finger SCR             | 9۱  |

| 5.4.2 CDM simulation comparison of sudoku array and finger DTSCR           |     |

| 5.5.1 TLP measurement and analysis                                         |     |

| 5.5.2 VFTLP measurement and analysis                                       |     |

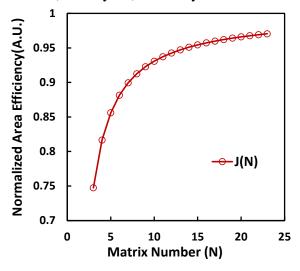

| 5.6 Sudoku ESD array design scalability                                    |     |

| ·                                                                          |     |

| Chapter 6 Graphene MEMS ESD switch design and evaluation                   |     |

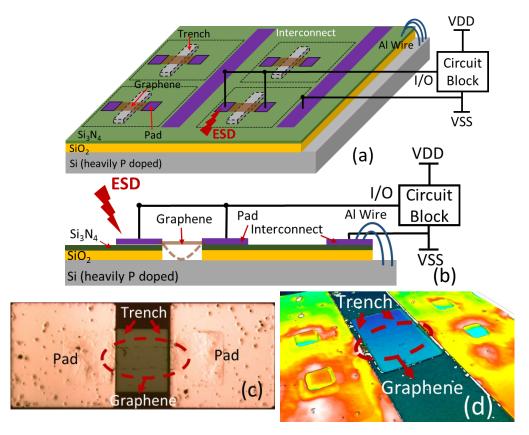

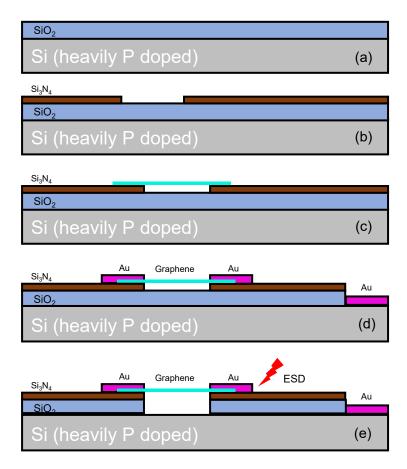

| 6.1 Single crystalline gNEMS ESD switch structure                          |     |

| 6.1.1 Overview of the gNEMS ESD switch function                            |     |

| 6.1.2 The fabrication process of the gNEMS ESD switch                      |     |

| 6.2 gNEMS ESD switch behaviors on poly and single crystalline graphene     |     |

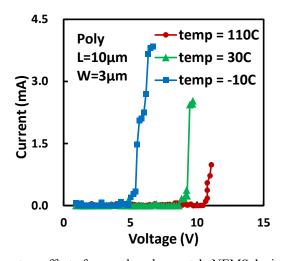

| 6.2.1 Temperature influence on poly crystalline gNEMS                      |     |

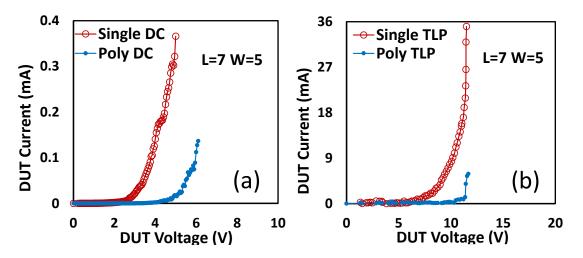

| 6.2.2 Performance comparison between poly and single crystalline graphene  |     |

| 6.2.3 Comprehensive ESD measurement on single crystalline gNEMS            |     |

| 6.3 gNEMS switch reliability evaluation on ESD performance                 |     |

| 6.4.1 Rise time condition under TLP and VFTLP measurement                  |     |

| 6.4.2 Pulse duration condition under TLP and VFTLP measurement             |     |

| 6.5 The influence of graphene ribbon dimension on gNEMS                    |     |

| 6.5.1 gNEMS dimension effect on triggering voltage                         |     |

| 6.5.2 gNEMS dimension effect on current handleability                      |     |

| 6.6 Quality control on the single crystalline gNEMS                        |     |

| 6.6.1 Single crystalline gNEMS being robust                                |     |

| 6.6.2 Single crystalline gNEMS failure analysis                            |     |

| 6.7 Transient gNEMS behaviors via TLP testing                              | 124 |

| 6.8 gNEMS triggering mechanism by FEM simulation                           | 120 |

| 6.8.1 gNEMS transient movement analysis on triggering                      |     |

| 6.8.2 TLP voltage step influence on the gNEMS triggering by FEM simulation | 129 |

| 6.9 Pulse condition and graphene dimension impact analysis                 | 130 |

| 6.9.1 Pulse condition influence on gNEMS switch by FEM simulation          |     |

| 6.9.2 Graphene dimension influence on gNEMS switch by FEM simulation       |     |

| 6.10 The shape of graphene membrane impact analysis                        |     |

| Chapter 7 Conclusion                                                       | 142 |

| Ribliography                                                               | 146 |

## **List of Figures**

| Figure 1.1 Different heat dissipation system for different applications                                | 1        |

|--------------------------------------------------------------------------------------------------------|----------|

| Figure 1.2 The historical trend and CPU scaling development                                            | 3        |

| Figure 1.3 The illustration for the multitasks running and high-quality of vision during the game.     | 4        |

| Figure 1.4 Comparison of heat flow between the plenary CMOS and FinFET                                 |          |

| Figure 1.5 Comparison of heat flow between the plenary CMOS and SOI                                    | 6        |

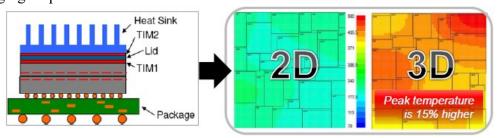

| Figure 1.6 Illustration of the 3D packaging chip impact on the temperature                             | 6        |

| Figure 1.7 Illustration of thermal sensors on the chip                                                 | 7        |

| Figure 1.8 The Seebeck effect residing in the thermocouple.                                            | 9        |

| Figure 2.1 Illustration of the block level thermal sensors floorplan on the chip                       | 2        |

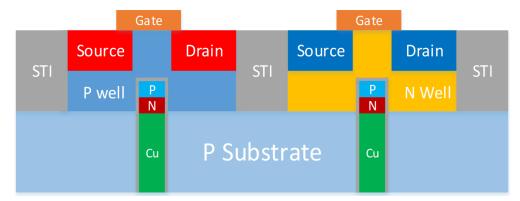

| Figure 2.2 Illustration of the new in-hole diode thermal sensor concept in CMOS where the              |          |

| sensor is embedded in a deep hole in the Si substrate under individual MOSFET for transistor-          |          |

| level sensing resolution                                                                               | 4        |

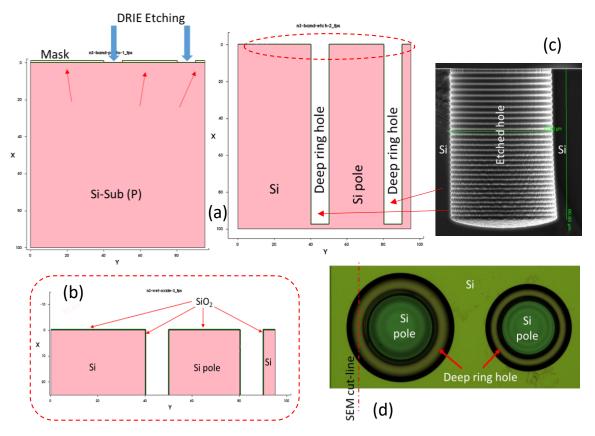

| Figure 2.3 (a) Si substrate covered by a mask for DRIE etching to create a deep ring hole, (b) a       |          |

| zoom-in view for the deep ring hole etched by DRIE, covered by the required SiO <sub>2</sub> isolation |          |

| layer, (c) SEM X-section view of the etched side wall of the deep ring hole, and (d) a top view of     | •        |

| in-hole diodes by optical microscope1                                                                  | 6        |

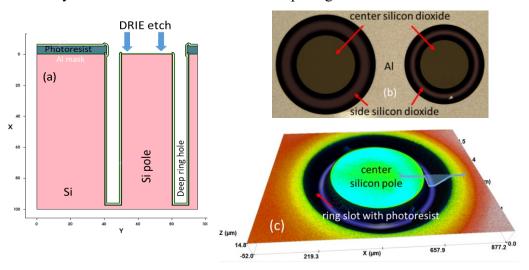

| Figure 2.4 (a) TCAD simulation shows the deep hole using a hard Al-mask to protect the top             |          |

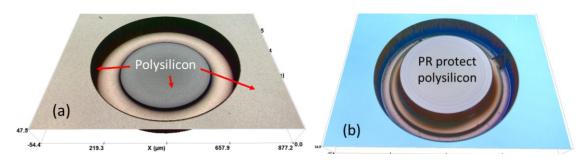

| edges of the hole, (b) confocal microscope 3D image of ring structure with photoresist covering        |          |

| the SiO <sub>2</sub> side wall (c) using Al as the hard mask to protect the corner from being etched1  |          |

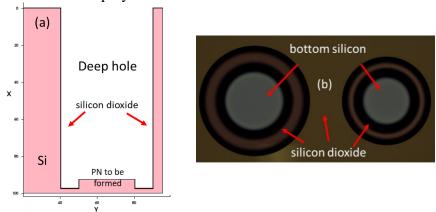

| Figure 2.5 (a) using thick PR to define the deep hole pattern for etching by TCAD simulation (b)       |          |

| after DRIE etching, the center bottom silicon is exposed without SiO <sub>2</sub> covering             |          |

| Figure 2.6 (a) image for polysilicon deposition around the bottom, side wall and the top plane, (b     |          |

| negative photoresist protects the polysilicon above center bottom pole silicon from being etched.      |          |

| 1                                                                                                      |          |

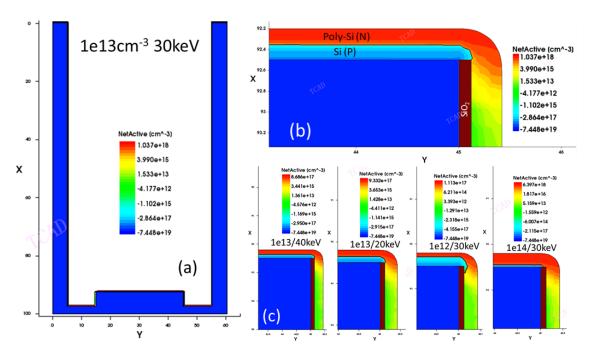

| Figure 2.7 TCAD process simulation was used to optimize the deep DRIE etching process: (a) the         |          |

| high-aspect-ratioed deep shaft to be formed, (b) a poly-Si/Si PN diode to be formed at the bottom      |          |

| and (c) different doping recipes to optimize the PN junctions                                          | J        |

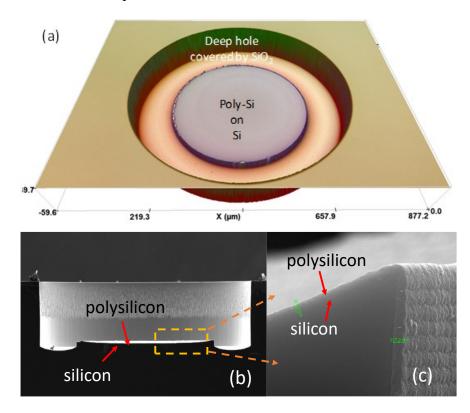

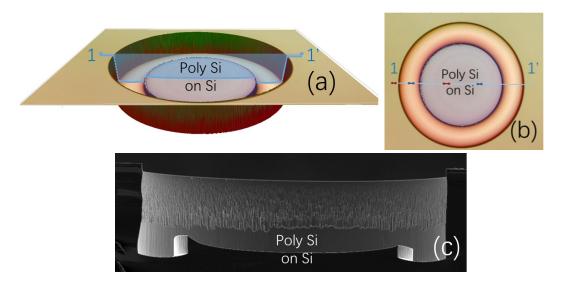

| Figure 2.8 Images for the poly-Si/Si PN diode sensor formed at the bottom of the deep shaft            |          |

| under a MOSFET in the Si substrate: (a) a 3D image by confocal microscope, (b) a cross-section         |          |

| view of the PN junction by SEM, and (c) zoom-in of the poly-Si/Si junction corresponding to the        |          |

| yellow box region in (b)                                                                               |          |

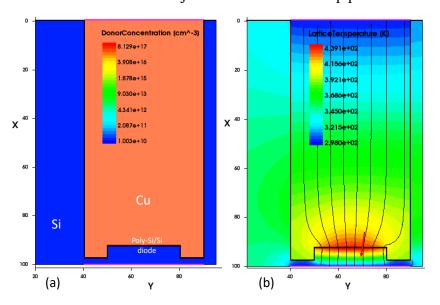

| Figure 2.9 TCAD simulation shows (a) the vertical poly-Si/Si PN diode at the bottom of the deep        |          |

| shaft, and (b) the I-V curves of the diode sensor.                                                     | 2        |

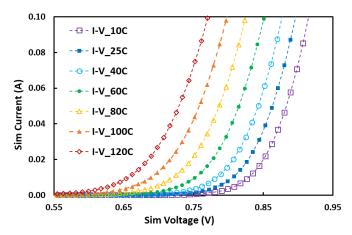

| Figure 2.10 TCAD simulation shows desired I-V-T behaviors for the new in-hole diode thermal            | _        |

| sensor across a wide temperature range.                                                                |          |

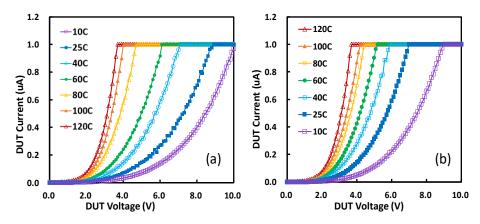

| Figure 2.11 Measured I-V-T curves for a sample in-hole diode sensor with a diameter of 250μm:          |          |

| (a) I-V curves with ascending temperature sweeping, and (b) I-V curves with descending                 | <u>-</u> |

| temperature sweeping                                                                                   |          |

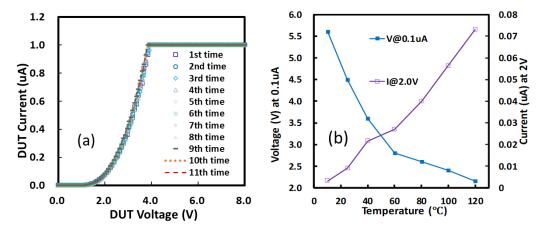

| Figure 2.12 (a) Measurement shows that a sample in-hole diode sensor with a diameter of 400 µm         | Ĺ        |

| is stable after repeated DC sweeping tests, (b) Measured V-T and I-T curves show monotonous            | 1        |

| trend against temperature that is required for a diode thermal sensor.                                 | +        |

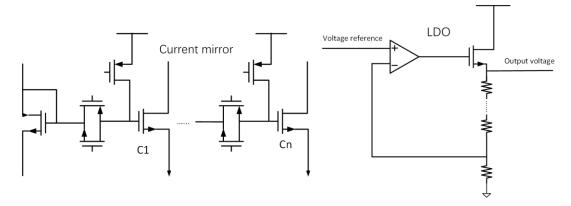

| Figure 2.13 Schematic of LDO adjusting the bias voltage and current mirror scaling the driving         | _        |

| current                                                                                                | J        |

| network                                                                                                | 7        |

| Figure 2.15 Brief schematic of the temperature sensing and feedback control circuits with in-hole diode    |

|------------------------------------------------------------------------------------------------------------|

| Figure 2.16 In-hole sensor behavior model developed using the test data is validated by Spectre simulation |

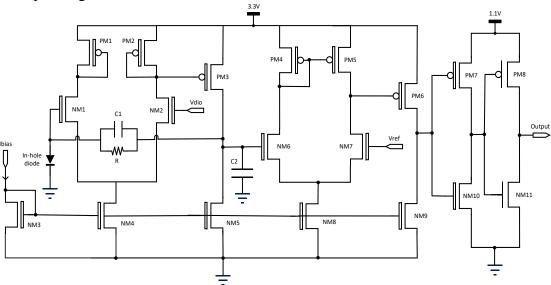

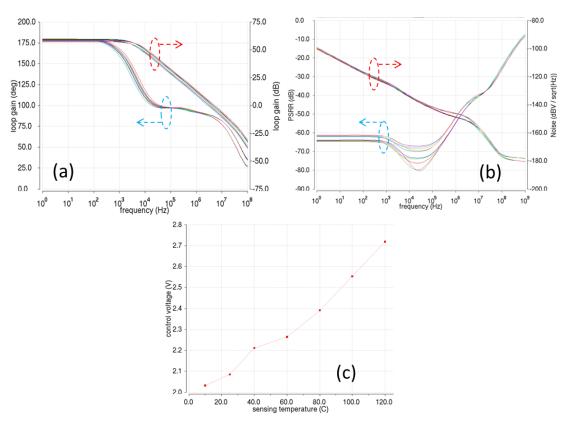

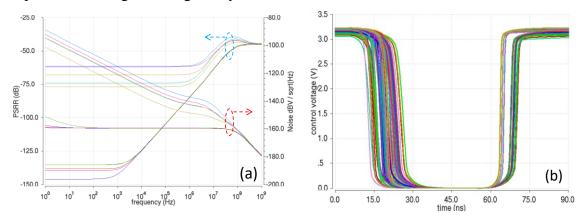

| Figure 2.17 Post simulation for TIA shows: (a) good stability across the frequency from 1Hz to             |

|                                                                                                            |

| 100MHz over all corners, (b) low PSRR and noises across frequency from 1Hz to 1GHz over all                |

| corners (-40°C to-125°C), and (c) desired monotonous temperature sensing and voltage                       |

| controlling for thermal management                                                                         |

| Figure 2.18 Post simulation for comparator block shows: (a) low PSRR and noises from 1Hz to                |

| 1GHz over all corners across -40°C and 125°C temperature range, and (b) required flipping                  |

| output control signals (-40°C and 125°C) driven by the in-hole sensing data for PA operation               |

| scaling against self-heating.                                                                              |

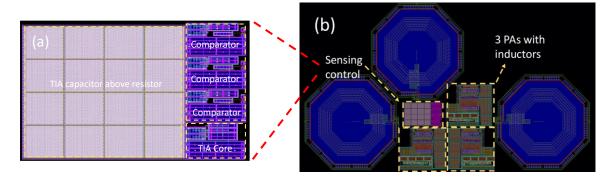

| Figure 2.19 (a) Sensing control layout of monitoring circuit layout including TIA and 3                    |

| comparators zoomed in view from PA module layout (b) Layout for the PA module with                         |

| embedded under-FET in-hole thermal sensors designed in 40nm CMOS                                           |

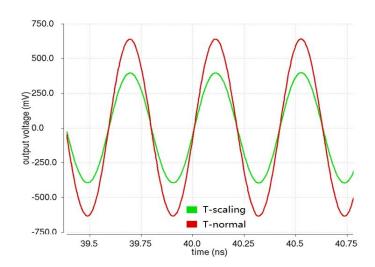

| Figure 2.20 Simulation for the PA module confirms the thermal management function through                  |

| temperature-based PA performance scaling controlled by varying voltage biasing tuned by the                |

| under-PA in-hole temperature sensors, hence mitigating thermal impacts in real time. T-normal:             |

| PA operation under normal temperature; T-scaling: PA operation scaled down triggered by                    |

| overheating sensed                                                                                         |

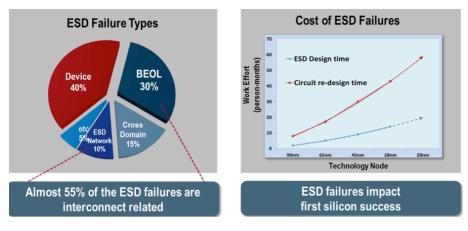

| Figure 3.1 ESD failure statics and ESD design time cFigure 3.2ost                                          |

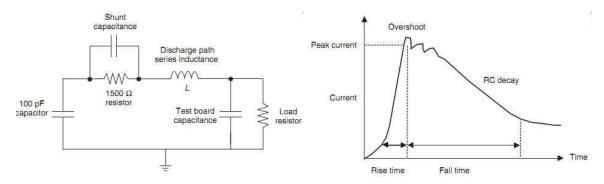

| Figure 3.3 MM equivalent circuit model with parasitic and pulse waveform                                   |

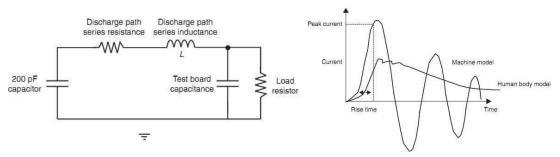

| Figure 3.4 CDM equivalent circuit model with parasitic and pulse waveform                                  |

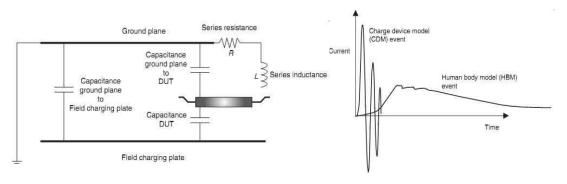

| Figure 3.5 (a) TLP/VFTLP time domain reflectometry configuration (b) comparison between                    |

| TLP and VFTLP waveform (c) TDR results for current and voltage                                             |

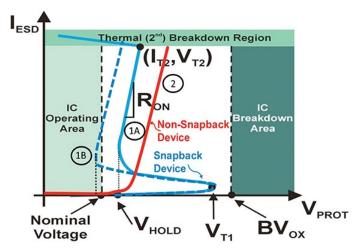

| Figure 3.6 ESD design window                                                                               |

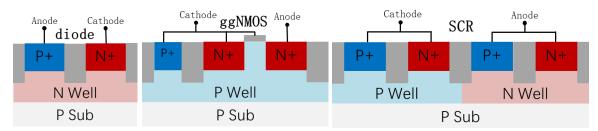

| Figure 3.7 ESD cross-section structure of diode, ggNMOS and SCR                                            |

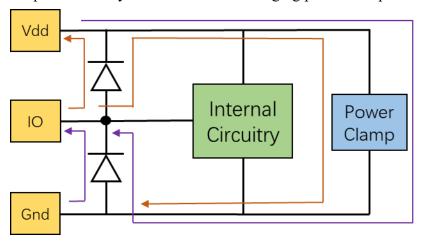

| Figure 3.8 Double diode ESD network and discharging current path                                           |

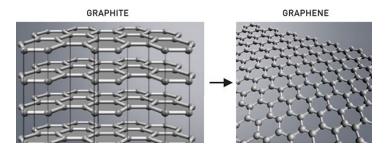

| Figure 3.9 A sketch of graphite and graphene lattice structures                                            |

| Figure 3.10 A sketch diagram of the graphene synthesis facility and needed sources                         |

| Figure 4.1 Concept of the new in-TSV ESD diode for distributed ESD protection (a) and its X-               |

| sectional view by TCAD (b)                                                                                 |

| Figure 4.2 Images for prototype in-TSV poly-Si/Si PN diode ESD protection device fabricated                |

| inside a 100µm deep TSV hole: (a) a 3D image by confocal microscope, (b) a X-section view                  |

| along 1-1' cutline of the PN diode by SEM, and (c) a top view of in-hole ESD diodes by optical             |

| microscope along 1-1' cutline                                                                              |

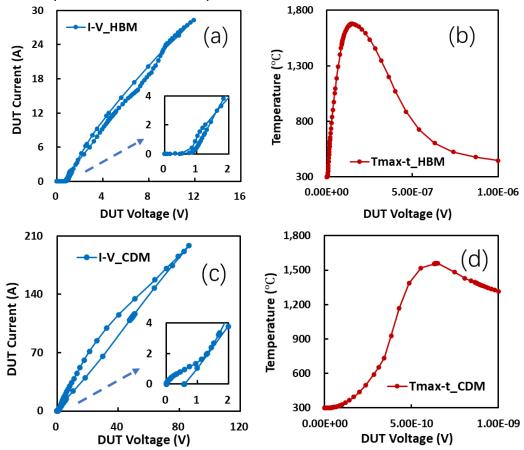

| Figure 4.3 TCAD transient ESD simulation on vertical TSV-like diode: (a) I-V curve zapped by               |

| HBM waveform, (b) T <sub>max</sub> -t curve zapped by HBM waveform, (c) I-V curve zapped by CDM            |

| waveform, (d) T <sub>max</sub> -t curve zapped CDM waveform                                                |

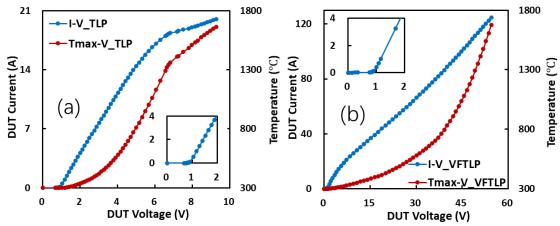

| Figure 4.4 TCAD transient ESD simulation on TSV-like hole diode: (a) I-V and T-V curves for                |

| TLP waveform, (b) I-V and T-V curves for VFTLP waveform                                                    |

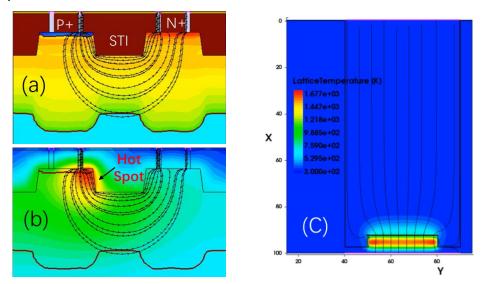

| Figure 4.5 TCAD transient ESD simulation reveals: (a) the ESD discharge current flowlines are              |

| curved around the STI plug, causing (b) severe local overheating at the STI corner, i.e., a hot spot       |

| for a traditional planar STI ESD diode, (c) the vertical evenly distributed ESD discharge current          |

| flowlines and uniform thermal map under HBM zapping for a sample TSV-like ESD diode 51                     |

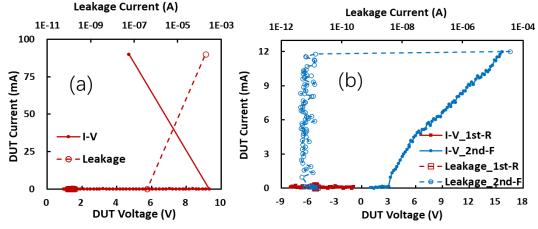

| Figure 4.6 TLP testing on TSV-like diode: (a) reverse TLP zapping shows the current blocking               |

| until broken-down, (b) first reverse zapping and second forward zapping shows the TSV-like                 |

| diode function                                                                                             |

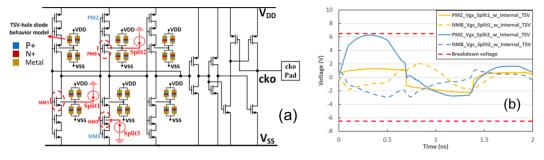

| Figure 4.8 (a) A 3-stage oscillator with TSV-based internally distributed CDM ESD network, (b)                                |

|-------------------------------------------------------------------------------------------------------------------------------|

| transient voltage analysis for V <sub>GS</sub> of PM2 and NM8 using TSV-based can pass 350V CDM                               |

| zapping                                                                                                                       |

| Figure 4.7 TLP-measured transient ESD discharge I-V curves for prototype TSV-like ESD diodes                                  |

| confirm the ESD protection function and low ESD-induced leakage                                                               |

| Figure 4.9 TCAD simulation process flow.                                                                                      |

| Figure 4.10 Main physical models related to TLP calibration                                                                   |

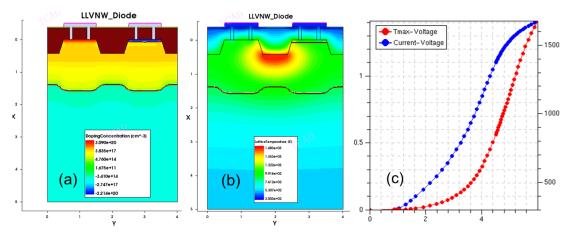

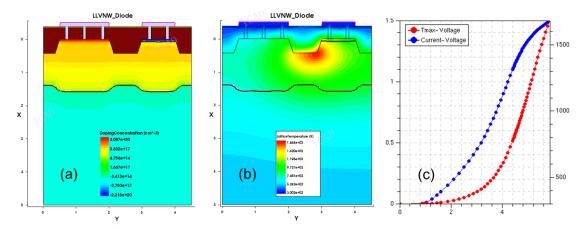

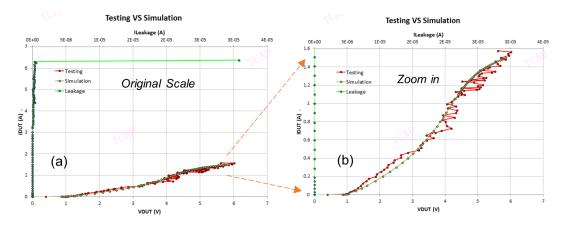

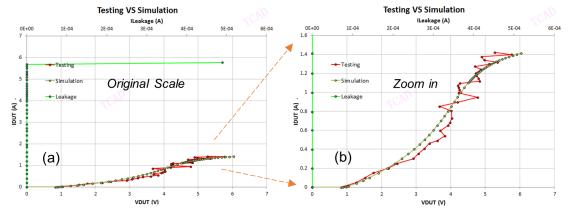

| Figure 4.11 TCAD ESD simulation of LLVNW diode (NL=PL=SL=1) under TLP zapping: (a)                                            |

| cross-section of TCAD simulated structure, (b) heat distribution map showing the hotspot                                      |

| location, (c) I-V and T <sub>max</sub> -V curve until the silicon melting temperature                                         |

| Figure 4.12 TCAD ESD simulation of LLVNW diode (NL=1.5 PL=SL=1) under TLP zapping:                                            |

| (a) cross-section of TCAD simulated structure, (b) heat distribution map showing the hotspot                                  |

| location, (c) I-V and Tmax-V curve until the silicon melting temperature                                                      |

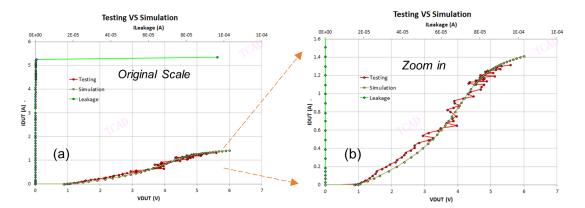

| Figure 4.13 Comparison of LLVNW diode (NL=PL=SL=1) under TLP zapping between the                                              |

| testing data and simulation data shows a good matching mainly on the $V_{t1},R_{on}$ and $I_{t2},\ldots 60$                   |

| Figure 4.14 Comparison of LLVNW diode (NL=1.5, PL=SL=1) under TLP zapping between the                                         |

| testing data and simulation data shows a good matching mainly on the V <sub>t1</sub> , R <sub>on</sub> and I <sub>t2</sub> 61 |

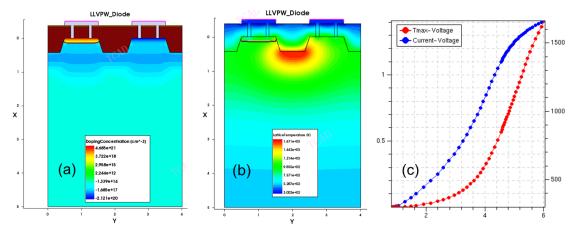

| Figure 4.15 TCAD ESD simulation of LLVPW diode (NL=PL=SL=1) under TLP zapping: (a)                                            |

| cross-section of TCAD simulated structure, (b) heat distribution map showing the hotspot                                      |

| location, (c) I-V and T <sub>max</sub> -V curve until the silicon melting temperature61                                       |

| Figure 4.16 Comparison of LLVPW diode (NL=PL=SL=1) under TLP zapping between the                                              |

| testing data and simulation data shows a good matching mainly on the V <sub>t1</sub> , R <sub>on</sub> and I <sub>t2</sub> 62 |

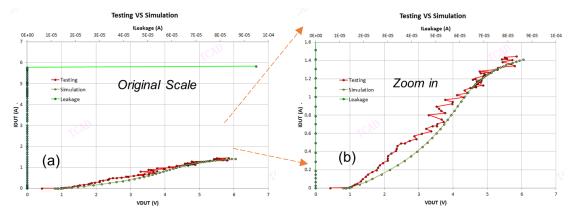

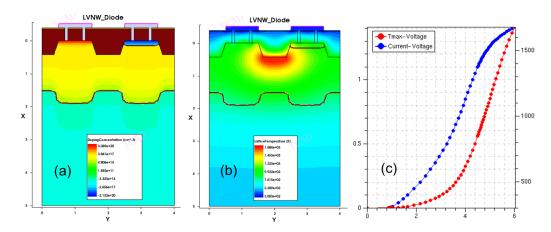

| Figure 4.17 TCAD ESD simulation of LVNW diode (NL=PL=SL=1) under TLP zapping: (a)                                             |

| cross-section of TCAD simulated structure, (b) heat distribution map showing the hotspot                                      |

| location, (c) I-V and T <sub>max</sub> -V curve until the silicon melting temperature63                                       |

| Figure 4.18 Comparison of LLVPW diode (NL=PL=SL=1) under TLP zapping between the                                              |

| testing data and simulation data shows a good matching mainly on the V <sub>t1</sub> , R <sub>on</sub> and I <sub>t2</sub> 63 |

| Figure 4.19 A set of hotspots distributed diagrams on the time domain under the TCAD HBM                                      |

| simulation showing the hotspot movement                                                                                       |

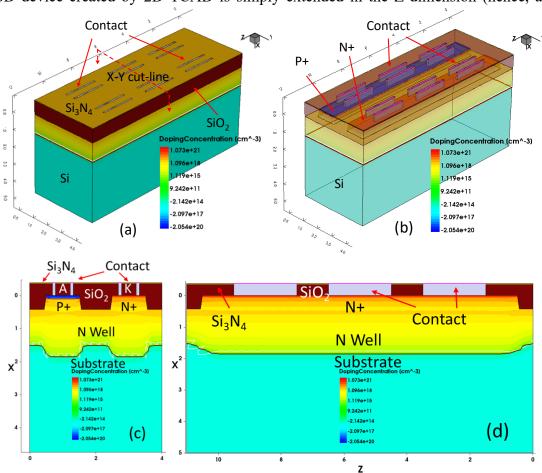

| Figure 5.1 A 3D ESD diode generated by true 3D TCAD process simulation that contains 12                                       |

| evenly distributed ESD metal contact lines per ESD Design Rules. (a) 3D ESD diode created, (b)                                |

| 3D ESD diode view in transparent mode, (c) a cross-section view of the 3D ESD diode along the                                 |

| X-Y cut-line, (d) a cross-section view of the 3D ESD diode along the X-Z cut-line67                                           |

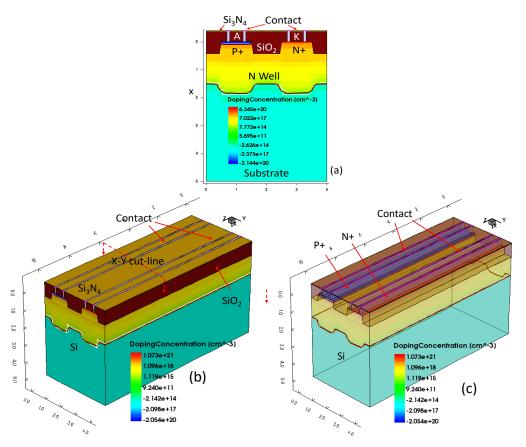

| Figure 5.2 The same ESD diode structures created by (a) 2D TCAD (equivalent to Fig. 1c), and                                  |

| (b) psedo-3D TCAD with (c) being its transparent view                                                                         |

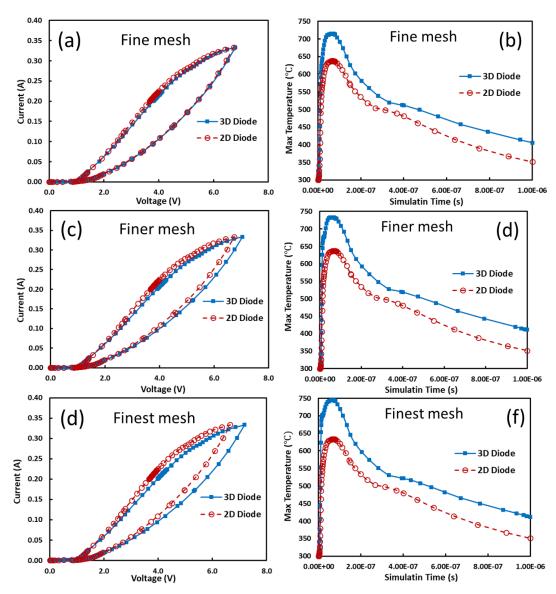

| Figure 5.3 Transient ESD I-V-T curve comparison by TCAD ESD simulation for the 2D and 3D                                      |

| ESD diodes with varying mesh densities: (a) I-V curves for Fine mesh, (b) T <sub>max</sub> -t curves for Fine                 |

| mesh (c) I-V curves for Finer mesh, (d) T <sub>max</sub> -t curves for Finer mesh and (e) I-V curves for Finest               |

| mesh, and (f) T <sub>max</sub> -t curves for Finest mesh                                                                      |

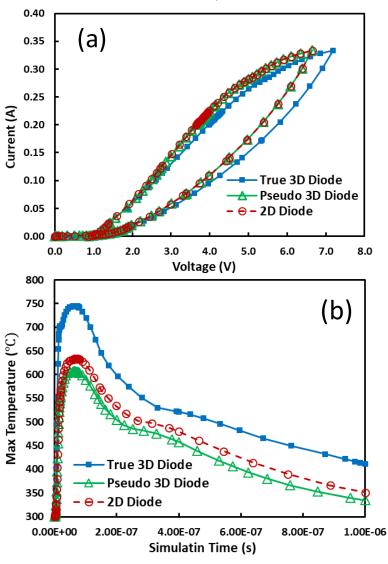

| Figure 5.4 Transient ESD I-V-T comparison for 2D, pseudo 3D and true 3D ESD diodes: (a) I-V                                   |

| curves, and (b) $T_{\text{max}}$ -t curves.                                                                                   |

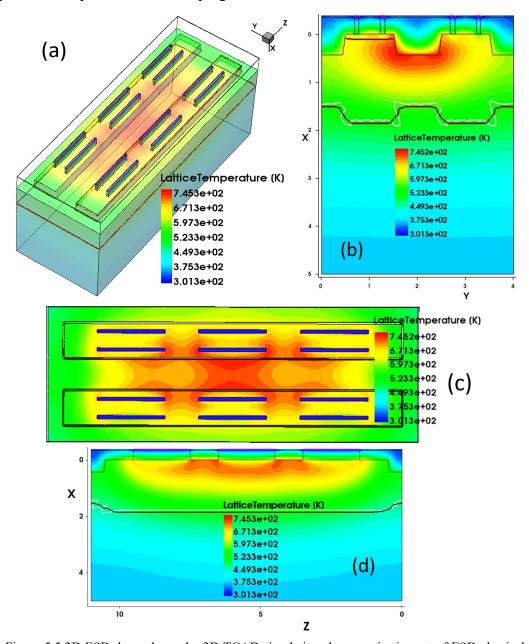

| Figure 5.5 3D ESD thermal map by 3D TCAD simulation shows major impact of ESD physical                                        |

| layout design: (a) 3D transparent view, (b) X-Y cross-section view, (c) top view (Y-Z cross-                                  |

| section), and (d) X-Z cross-section view.                                                                                     |

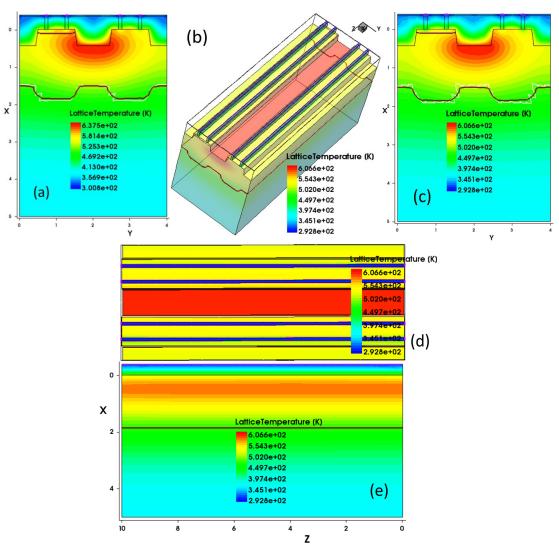

| Figure 5.6 ESD thermal map for the ESD diode by 2D/2.5D TCAD ESD simulation: (a) 2D ESD                                       |

| diode thermal map, (b) pseudo 3D view of the 2.5D ESD diode, (c) X-Y cross-section view of                                    |

| the 2.5D ESD diode, (d) Y-Z cross-section view of 2.5D ESD diode thermal map, and (e) X-Z                                     |

|                                                                                                                               |

| cross-section view of 2.5D ESD diode thermal map                                                                              |

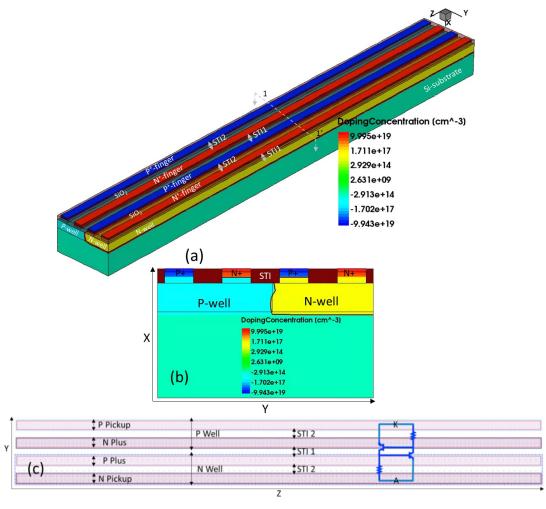

| Figure 5.7 A conventional Finger-SCR ESD core array by 3D TCAD where SCR ESD devices                   |

|--------------------------------------------------------------------------------------------------------|

| are formed across the cell boundaries: (a) 3D view, (b) cross-section view on X-Y plane along the      |

| 1-1' cutline, and (c) actual Y-Z plane layout view with equivalent circuit                             |

| Figure 5.8 A conventional Finger-DTSCR ESD core array by 3D TCAD where SCR ESD devices                 |

| are formed across the cell boundaries: (a) 3D view, (b) cross-section view on X-Y plane along the      |

| 1-1' cutline, and (c) actual Y-Z plane layout view with equivalent circuit                             |

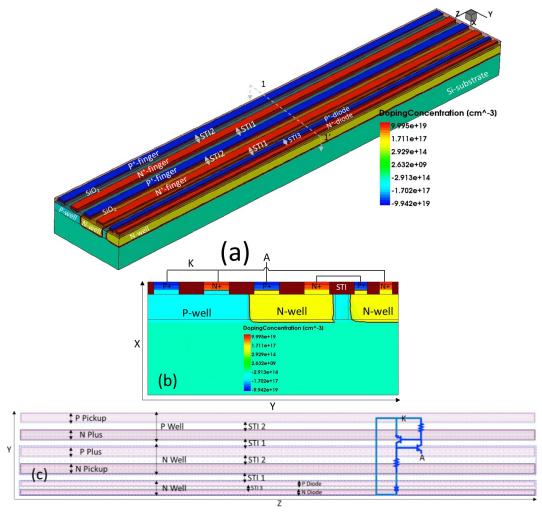

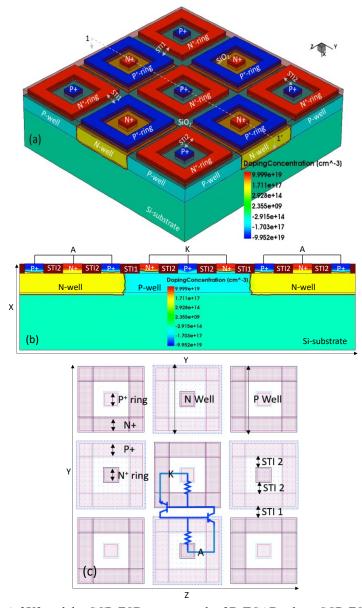

| Figure 5.9 A 3X3 sudoku SCR ESD core array by 3D TCAD where SCR ESD devices are formed                 |

| across the cell boundaries: (a) 3D view, (b) cross-section view on X-Y plane along the 1-1'            |

| cutline, and (c) actual Y-Z plane layout view with equivalent circuit                                  |

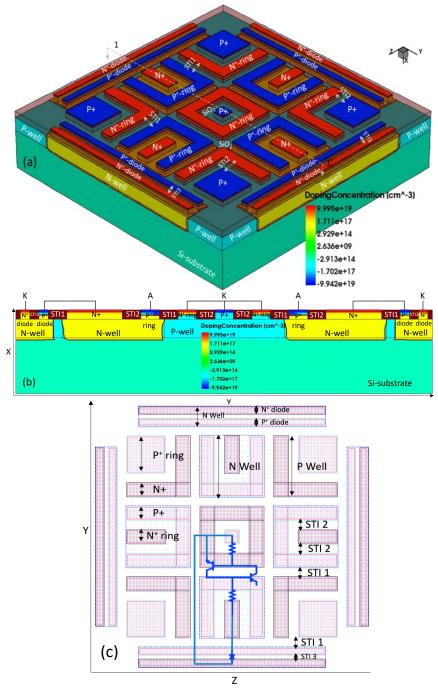

| Figure 5.10 A 3X3 sudoku DTSCR ESD array by 3D TCAD where DTSCR ESD devices are                        |

| formed across the cell boundaries: (a) 3D view, (b) cross-section view on X-Y plane along the 1-       |

| 1' cutline, and (c) actual Y-Z plane layout view with equivalent circuit                               |

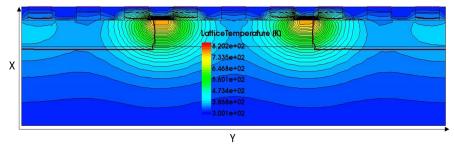

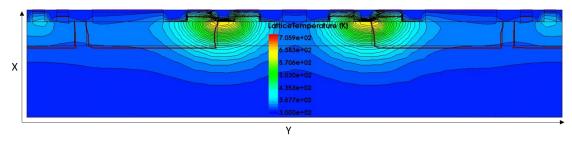

| Figure 5.11 Cross-section view of transient ESD heating for the 3X3 Sudoku-SCR ESD array               |

| under 5kV HBM ESD stressing reveals transient ESD discharging behaviors                                |

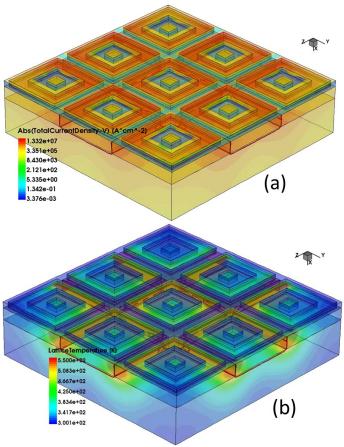

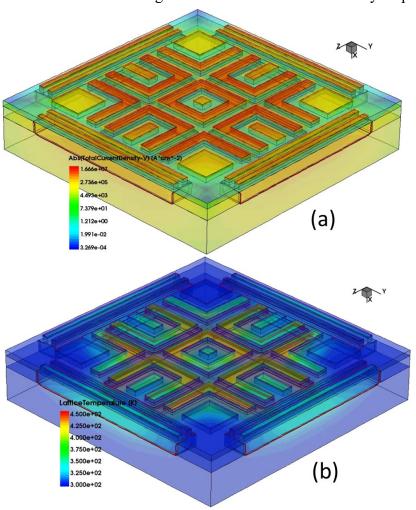

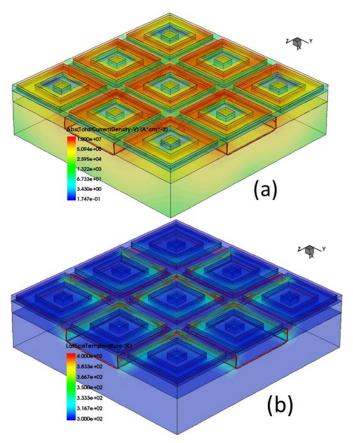

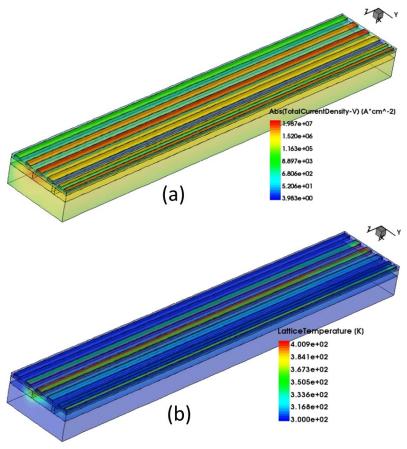

| Figure 5.12 3D ESD TCAD simulation under 5kV HBM stressing for 3X3 sudoku SCR ESD core                 |

| array: (a) 3D ESD discharging I-density map, and (b) 3D lattice temperature T-map84                    |

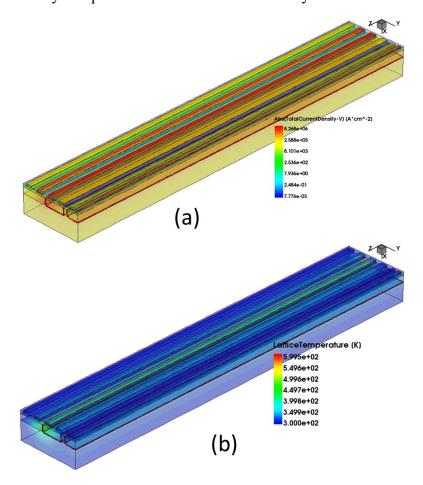

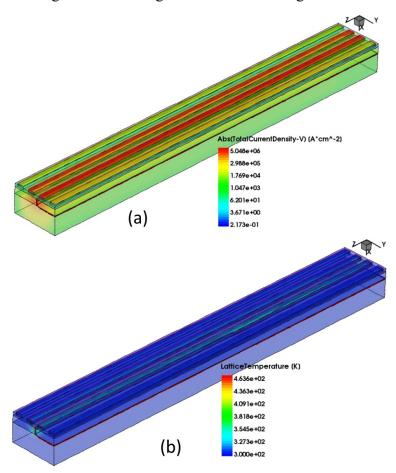

| Figure 5.13 3D ESD TCAD simulation under 5kV HBM stressing for finger SCR ESD device:                  |

| (a) 3D ESD discharging I-density map, and (b) 3D lattice temperature T-map                             |

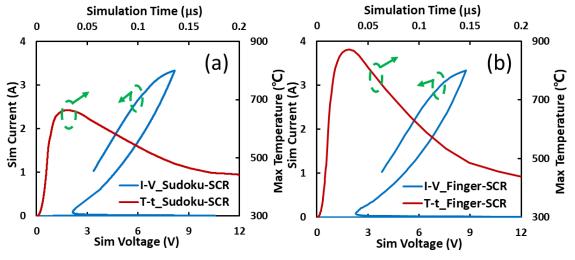

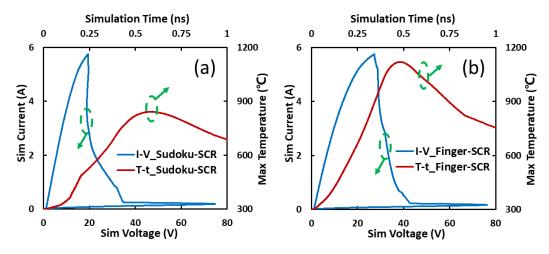

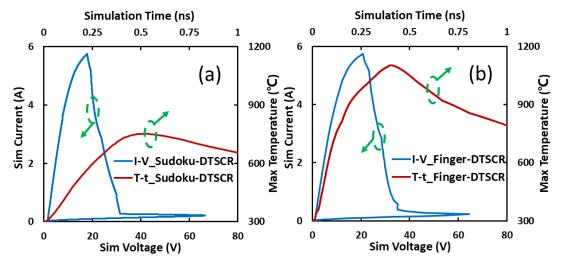

| Figure 5.14 HBM-simulated I-V and T <sub>max</sub> -t curves based on transient 3D TCAD ESD simulation |

| for (a) 3X3 sudoku SCR ESD core array structure, and (b) finger SCR ESD core device                    |

| Figure 5.15 Cross-section view of transient ESD heating for the 3X3 sudoku DTSCR ESD array             |

| under 5kV HBM ESD stressing reveals transient ESD discharging behaviors                                |

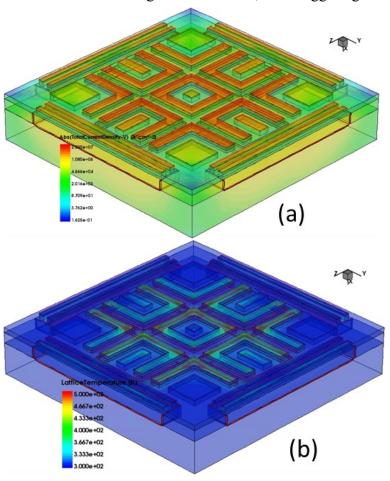

| Figure 5.16 3D ESD TCAD simulation under 5kV HBM stressing for 3X3 sudoku DTSCR ESD                    |

| core array: (a) 3D ESD discharging I-density map, and (b) 3D lattice temperature T-map 88              |

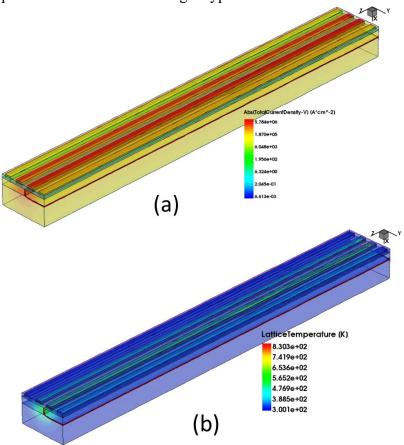

| Figure 5.17 3D ESD TCAD simulation under 5kV HBM stressing for finger DTSCR ESD device:                |

| (a) 3D ESD discharging I-density map, and (b) 3D lattice temperature T-map                             |

| Figure 5.18 HBM simulated I-V and T <sub>max</sub> -t curves based on transient 3D TCAD ESD simulation |

| for (a) 3X3 sudoku DTSCR ESD core array structure, and (b) finger DTSCR ESD core device. 90            |

| Figure 5.19 3D ESD TCAD simulation under 500V CDM stressing for 3X3 sudoku SCR ESD                     |

| core array: (a) 3D ESD discharging I-density map, and (b) 3D lattice temperature T-map91               |

| Figure 5.20 3D ESD TCAD simulation under 500V CDM stressing for finger SCR ESD device:                 |

| (a) 3D ESD discharging I-density map, and (b) 3D lattice temperature T-map92                           |

| Figure 5.21 CDM simulated I-V and T <sub>max</sub> -t curves based on transient 3D TCAD ESD simulation |

| for (a) 3X3 sudoku SCR ESD core array structure, and (b) finger SCR ESD core device93                  |

| Figure 5.22 3D ESD TCAD simulation under 500V CDM stressing for 3X3 sudoku DTSCR ESD                   |

| core array: (a) 3D ESD discharging I-density map, and (b) 3D lattice temperature T-map 94              |

| Figure 5.23 3D ESD TCAD simulation under 500V CDM stressing for finger DTSCR ESD                       |

| device: (a) 3D ESD discharging I-density map, and (b) 3D lattice temperature T-map95                   |

| Figure 5.24 CDM simulated I-V and T <sub>max</sub> -t curves based on transient 3D TCAD ESD simulation |

| for (a) 3X3 sudoku DTSCR ESD core array structure, and (b) finger DTSCR ESD core device. 96            |

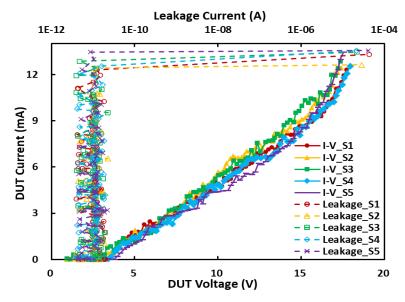

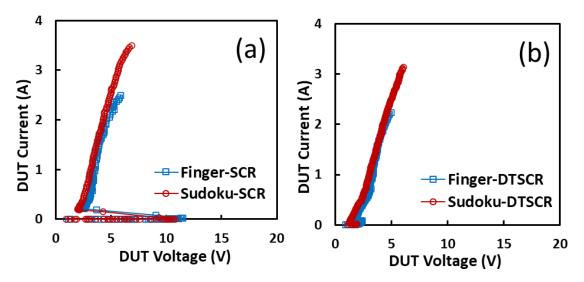

| Figure 5.25 Comparison of TLP measured ESD discharging I-V curves for: (a) sudoku SCR ESD              |

| array and its finger SCR device counterpart, (b) sudoku DTSCR ESD array and its finger DTSCR           |

| device counterpart                                                                                     |

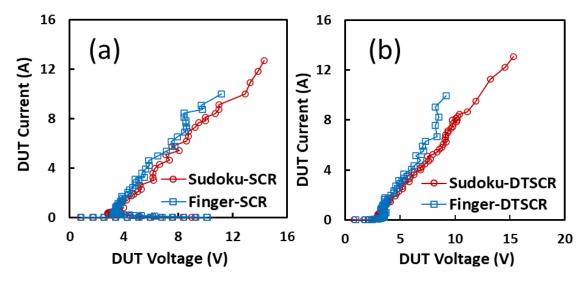

| Figure 5.26 Comparison of VFTLP measured ESD discharging I-V curves for: (a) sudoku SCR                |

| ESD array and finger SCR device counterpart, (b) sudoku DTSCR ESD array and finger DTSCR               |

| device counterpart 98                                                                                  |

| Figure 5.27 Illustration of <i>NxN</i> scalable array containing the 3x3 device fabricated in a 22nm FDSOI CMOS technology for (a) sudoku DTSCR ESD array structure, and (b) sudoku SCR ESD                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| array structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| top view, and (b) a cross-section view, (c) a 2D top view of optical microscope, and (d) a 3D confocal view showing the vertical trench                                                                                                                                                                                                                                                                                                                                                |

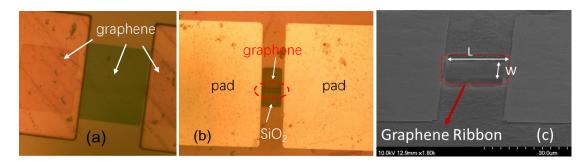

| Figure 6.4 Optical top views of graphene ESD devices fabricated: (a) post oxygen RIE showing the patterned graphene ribbon, (b) after e-beam pad deposition, and (c) SEM image shows single-crystal graphene gNEMS ESD switch fabricated. With dimension defined as L = length and W = width.                                                                                                                                                                                          |

| Figure 6.5 Temperature effect of a sample poly-crystal gNEMS device by TLP testing                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 6.8 Repeating stressing tests for different single-crystal gNEMS devices of varying sizes confirm that the gNEMS structures are extremely stable: (a) 11-times repeating DC sweeping stress test, (b) 110-times repeating TLP zapping, and (c) 110-times repeating VFTLP zapping test                                                                                                                                                                                           |

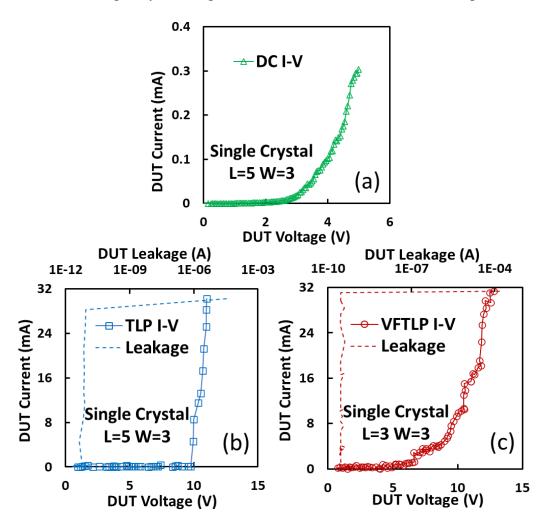

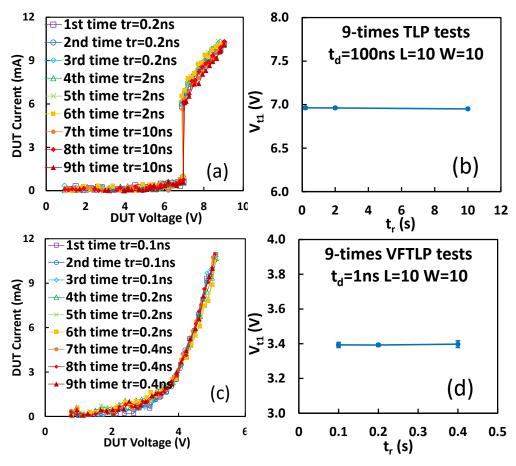

| Figure 6.9 Evaluation of possible $t_r$ effect on different single-crystal gNEMS devices by 9-times repeating TLP and VFTLP ESD zapping tests: (a) 9-times repeating TLP zapping with fixed $t_d\sim 100$ ns and varying $t_r\sim 0.2/2/10$ ns, (b) TLP $V_{t1}\sim t_r$ statistics, (c) 9-times repeating VFTLP zapping with fixed $t_d\sim 1$ ns and varying $t_r\sim 100/200/400$ ps, and (d) TLP $V_{t1}\sim t_r$ statistics. Tight error bars in (b/d) indicate testing stability |

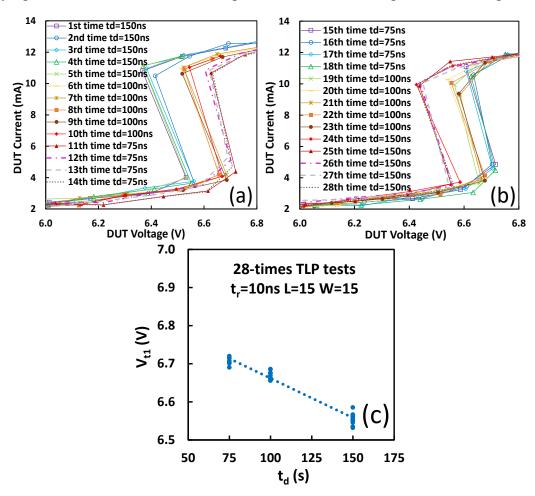

| Figure 6.10 Evaluation of possible $t_d$ effect on different single-crystal gNEMS devices by repeating TLP ESD zapping test routines: (a) 28-times repeating TLP zapping with fixed $t_r \sim 10$ ns and decreasing $t_d \sim 150/100/75$ ns routine, (b) 28-times repeating TLP zapping with fixed $t_r \sim 10$ ns and increasing $t_d \sim 75/100/150$ ns routine, (c) TLP $V_{t1} \sim t_d$ statistics                                                                             |

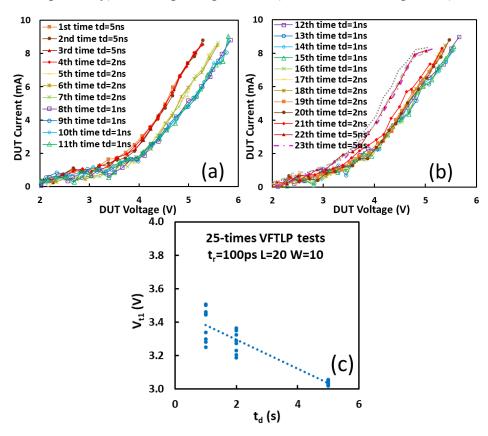

| repeating VFTLP ESD zapping test routines: (a) 25-times repeating VFTLP zapping with fixed $t_r$ ~100ps and decreasing $t_d$ ~5/2/1ns routine, (b) 25-times repeating VFTLP zapping with fixed $t_r$ ~100ps and increasing $t_d$ ~1/2/5ns routine, and (c) VFTLP $V_{t1}$ ~ $t_d$ statistics                                                                                                                                                                                           |

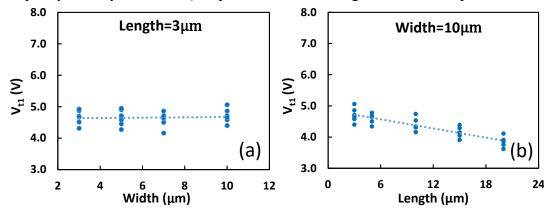

| Figure 6.13 Statistics for possible graphene dimension impacts on ESD $V_{tl}$ under VFTLP stressing: (a) $V_{tl}$ ~W for a fixed L is almost flat, and (b) $V_{tl}$ ~L for a given W shows a monotonous trend                                                                                                                                                                                                                                                                         |

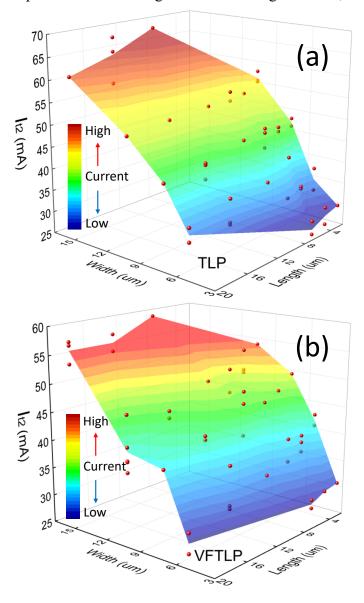

| Figure 6.14 Statistics for measured ESD I <sub>12</sub> capability of different gNEMS of varying dimensions        |

|--------------------------------------------------------------------------------------------------------------------|

| under TLP and VFTLP stressing: (a) by TLP zapping, and (b) under VFTLP stressing                                   |

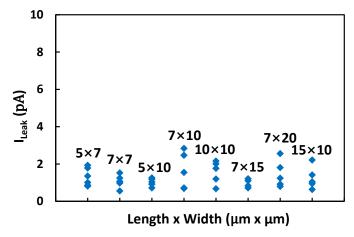

| Figure 6.15 Statistics show that the measured leakage currents I <sub>leak</sub> for different gNEMS devices       |

| of varying dimensions under TLP stressing are extremely low                                                        |

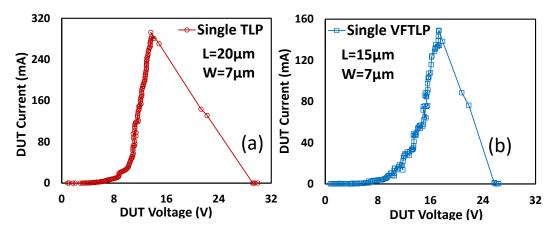

| Figure 6.16 Measurements of sample single-crystal gNEMS devices set the record for ESD                             |

| protection robustness, i.e., I <sub>12</sub> : (a) TLP zapping, and (b) VFTLP stressing                            |

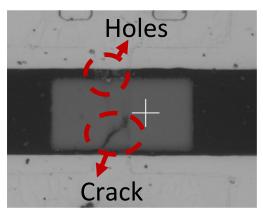

| Figure 6.17 Two ESD failure signatures were observed for single-crystal gNEMS device: a hole                       |

| in the graphene (Upper) and a crack across the graphene ribbon (Lower)                                             |

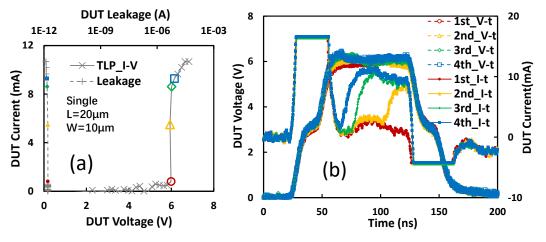

| Figure 6.18 Sample gNEMS ESD discharging behaviors by TLP testing reveals dynamic gNEMS                            |

| triggering and discharging characteristics: (a) instantaneous ESD discharging I-V curve, and (b)                   |

| transient DUT V-t and I-t waveforms corresponding to the gNEMS triggering threshold (red) and                      |

| full ESD conduction with increased TLP pulse heights (from yellow to green to blue)                                |

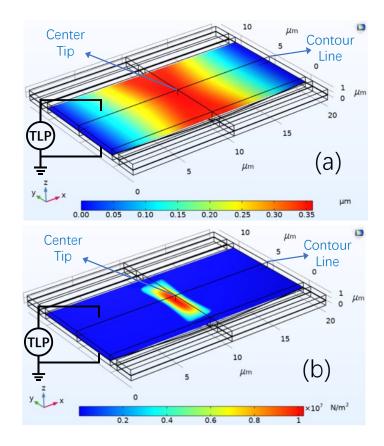

| Figure 6.19 3D transient FEM simulation of gNEMS during TLP ESD stressing: (a) displacement                        |

| of suspended graphene film (physical displacement in Z-axis with zero displacement at z=0 and                      |

| "touching" when z=-350nm), and (b) contact force upon the graphene ribbon induced by the net                       |

| pulling force when the graphene membrane touches the bottom Si (gNEMS = on)                                        |

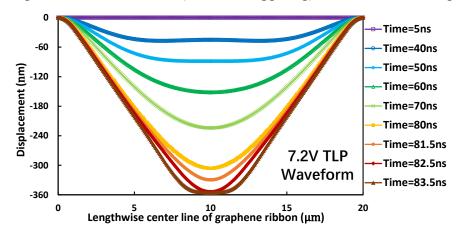

| Figure 6.20 Simulated graphene ribbon vertical displacement in the time domain. As the time                        |

| flow, graphene ribbon bends more and more until touching the bottom                                                |

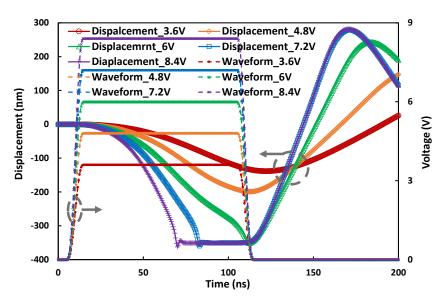

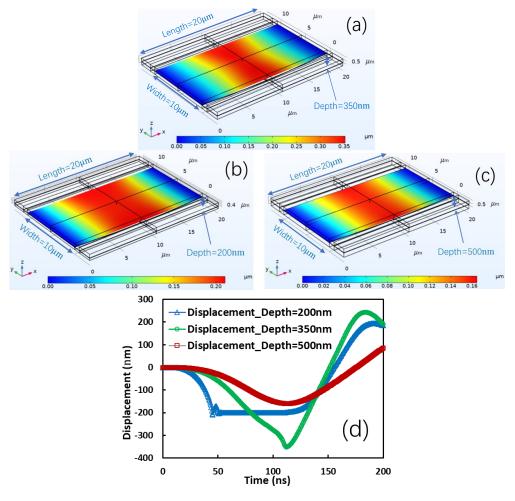

| Figure 6.21 Transient ESD triggering behaviors for a sample gNEMS (d=350nm, L=20µm,                                |

| W=10µm), stressed by a TLP pulse train of varying pulse heights (3.6V, 4.8V, 6V, 7.2V & 8.4V)                      |

| with a step of $\Delta V = 1.2V$ , show the ESD triggering threshold at $V_{t1} \sim 6V$                           |

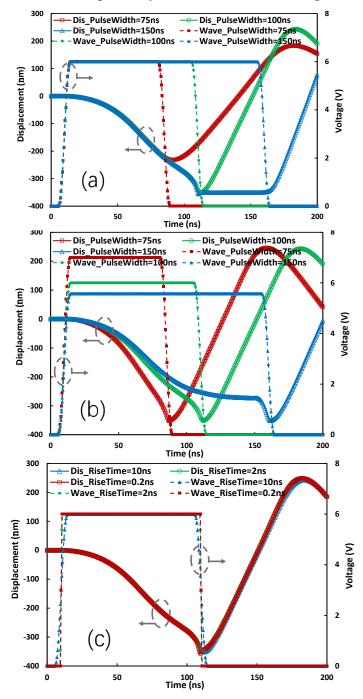

| Figure 6.22 Transient ESD response under TLP stressing: (a) varying t <sub>d</sub> of 75ns, 100ns and 150ns        |

| at fixed pulse height (6V) and rise time ( $t_r = 10$ ns), (b) varying $t_d$ of 75ns, 100ns and 150ns and          |

| TLP pulse height at fixed $t_r = 10$ ns, leading to different ESD $V_{t1}$ of 7V, 6V and 5.6V, and (c)             |

| varying $t_r$ of 0.2ns, 2ns and 10ns at fixed pulse height (6V) and $t_d = 100$ ns showing no change in            |

| ESD triggering                                                                                                     |

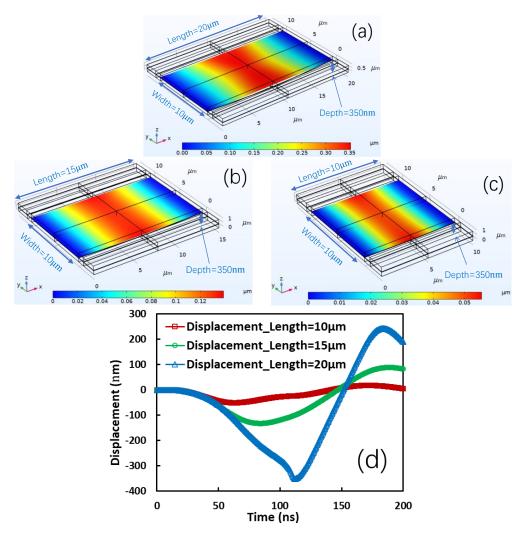

| changing graphene displacements: (a) $L = 20\mu m$ , $W = 10\mu m$ , $d = 350nm$ (base device), (b) $L =$          |

| 15 $\mu$ m, W = 10 $\mu$ m, d = 350nm, (c) L = 10 $\mu$ m, W = 10 $\mu$ m, and (d) transient ESD                   |

| triggering behaviors by graphene ribbon length effect.                                                             |

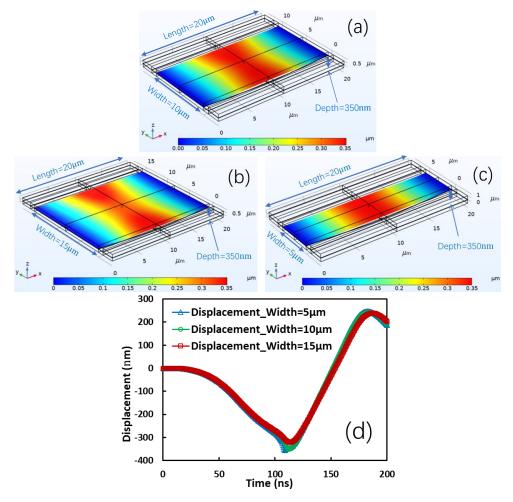

| Figure 6.24 gNEMS device splits of different dimensions stressed by TLP pulse of 6V show                           |

| changing graphene displacements: (a) $L = 20\mu m$ , $W = 10\mu m$ , $d = 350nm$ (base device), (b) $L =$          |

| $20\mu m$ , W = 15 $\mu m$ , d = 350nm, (c) L = 20 $\mu m$ , W = 5 $\mu m$ , d = 350nm, and (d) transient ESD      |

| triggering behaviors by graphene ribbon width effect                                                               |

| Figure 6.25 gNEMS device splits of different dimensions stressed by TLP pulse of 6V show                           |

| changing graphene displacements: (a) $L = 20\mu m$ , $W = 10\mu m$ , $d = 350nm$ (base device), (b) $L =$          |

| $20\mu m$ , W = $10\mu m$ , d = $220nm$ , (c) L = $20\mu m$ , W = $10\mu m$ , d = $5000nm$ , and (d) transient ESD |

| triggering behaviors by graphene ribbon depth effect.                                                              |

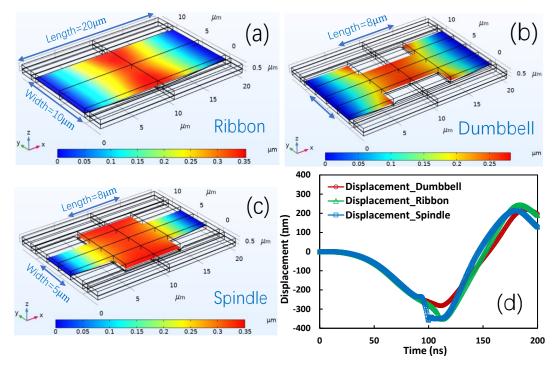

| Figure 6.26 gNEMS devices (L =20 $\mu$ m, W = 10 $\mu$ m, d = 350nm) with different shapes of                      |

| graphene membranes experience different net pulling force under TLP stressing: (a) baseline                        |

| rectangular graphene ribbon, (b) dumbbell-shaped with the center part of 8µm long and 5µm                          |

| wide, (c) spindle-shaped with the pulling arms being 6μm long and 5μm wide, and (d) transient                      |

| response zapped by TLP pulses of ~6V                                                                               |

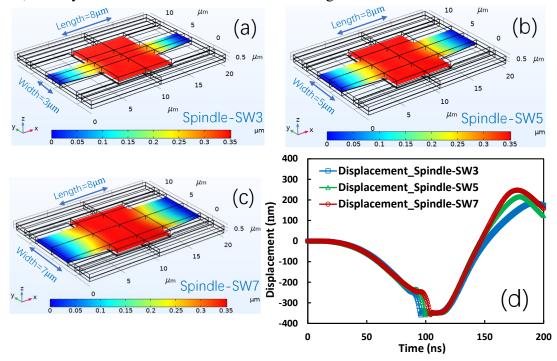

| Figure 6.27 Spindle-shaped gNEMS devices (L =8μm, W = 10μm, d = 350nm) with different                              |

| pulling arms under TLP stressing: (a) Spindle-SW3 of 3μm wide arms, (b) Spindle-SW5 of 5μm                         |

| wide arms, (c) Spindle-SW7 of 7μm wide arms, and (d) transient displacement of gNEMS splits                        |

| stressed by TI Phulse of a 6V                                                                                      |

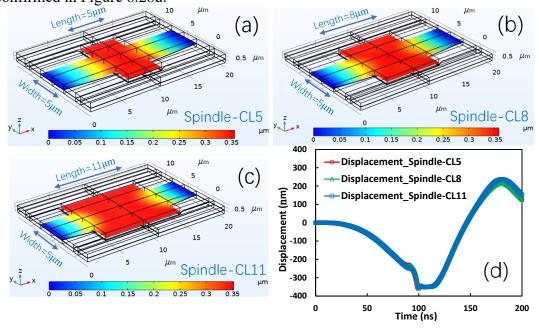

| Figure 6.28 Spindle-shaped gNEMS devices (W = $10\mu m$ , d = $350nm$ ) with varying length of              |

|-------------------------------------------------------------------------------------------------------------|

| $5\mu$ m, $8\mu$ m and $11\mu$ m under TLP zapping: (a) Spindle-CL5 of L = $5\mu$ m, (b) Spindle-CL8 of L = |

| 8 $\mu$ m, (c) Spindle-CL11 of L = 11 $\mu$ m, and (d) transient response stressed by TLP pulses of ~6V.    |

|                                                                                                             |

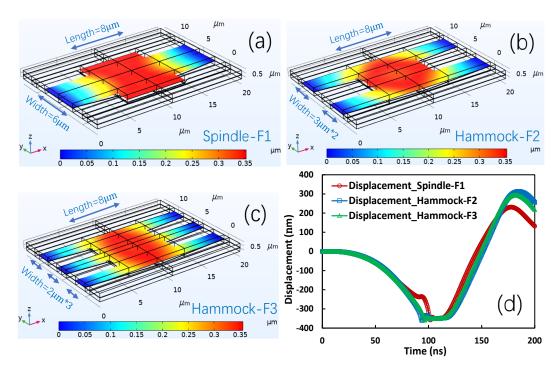

| Figure 6.29 Comparing spindle and hammock shaped gNEMS devices (L =8μm, W = 10μm, d =                       |

| 350nm) under TLP zapping: (a) Spindle-F1 featuring arm width of 6µm, (b) Hammock-F2 having                  |

| two pulling arms of 3µm wide each, (c) Hammock-F3 having three pulling arms of 2µm wide                     |

| each, and (d) transient response of gNEMS splits stressed by TLP pulse of ~6V                               |

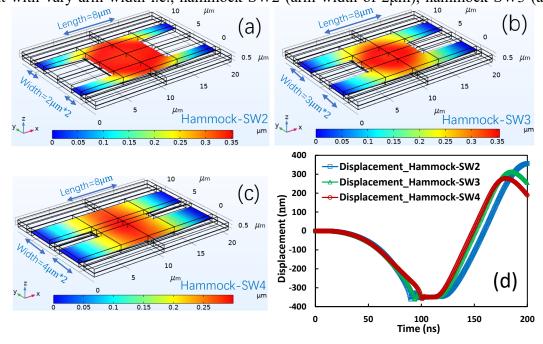

| Figure 6.30 Influence of pulling arm locations on elastic restoring forces of gNEMS devices (L =            |

| $8\mu m$ , W = $10\mu m$ , d = $350nm$ ) under TLP stressing: (a) hammock-SW2 having two arms of $2\mu m$   |

| wide each, (b) hammock-SW3 featuring two arms of 3µm wide each, (c) hammock-SW4 having                      |

| two arms of 4µm wide each, and (d) transient response of gNEMS splits stressed by TLP pulse of              |

| ~6V                                                                                                         |

#### Chapter 1 Introduction to heat dissipation and thermal management

#### 1.1 Heat dissipation background

#### 1.1.1 Heat dissipation system for different sizes of applications

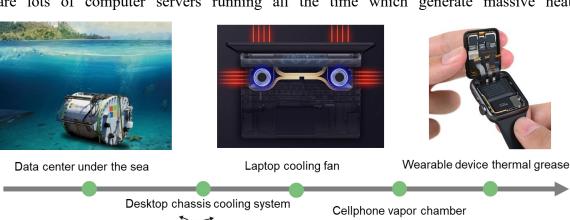

Considering the computer heat dissipation, we can find that there are different methods to release the heat generated from the chip to its surroundings. The only unchanged thing is that as long as any chip starts to run, it will generate heat. Therefore, under the situation that we do not change the amount of the heat generation, we need to develop the methods for heat dissipation, which dynamically balance the generated heat and dissipated heat. Seen from figure 1.1, the different application covers from the largest data center to the smallest wearable device like a smart watch. For the data center, there are lots of computer servers running all the time which generate massive heat

Figure 1.1 Different heat dissipation system for different applications

simultaneously. Now the best method nowadays is to place the data center under the sea to utilize the natural and abundant sea water to flow around the data center to take away plentiful heat. For the size scaling to the desktop, the main heat dissipation tool is the chassis cooling system. Normally, many fans are placed above the massive heat generation source like the computer processing unit (CPU), graphic processing unit (GPU), and power unit. The heat generated by these modules is delivered by their fans to the whole chassis then via the fans installed on the surface of the chassis to form a good air flow channel to exhale the hot air and inhale the environment cold air. For some severely loaded desktop system, they even use the water-cooling system which use the higher heat capacity fluid to take the heat more efficiently than air. Then the next scaled device is the laptop which can only use one or two small sizes of cooling fans plus the conductive copper tube. Compared with the desktop which directly installed the cooling fan above the heat generation source combining the heat sink to increase the heat conductivity, the laptop can only use the copper tube to pass the heat to the small cooling fan to indirectly dissipate the heat due to the limited volume of the laptop, which inevitable eliminate the efficiency of heat dissipation. Then moving to the smaller volume device, cellphone, which can only have the vapor chamber similar to the copper tube but without the cooling fan. After the heat passes through the vapor chamber to transfer the heat from the chip to another location of the cellphone in order to average the temperature. The last device is a wearable device like a smart watch, which has almost no heat dissipation solution but for the little effective thermal grease. Of course, there is no tool to facilitate heat dissipation and we have only counted on less heat generation. The law reveals the phenomenon that with the volume of the device decreasing, there are fewer methods for heat dissipation. Since today's devices are continuing to scale, the heat dissipation is more and more useless and we should pay more attention to temperature monitoring and controlling.

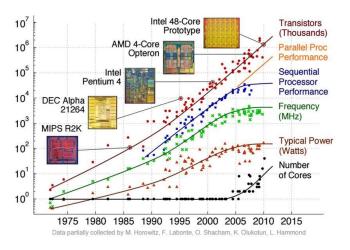

#### 1.1.2 Heat generation with the chip development

After the first integrated circuits were developed, the Moore law always guides the IC development like scale down and the transistor density doubles a while year. As seen from figure 1.2, the transistor density arises from 102 orders to 106 orders within these 30 years from the 1980s to the 2010s. A high density of transistors will definitely make the space between each transistor is limited which is unbeneficial for heat dissipation. Of course, more numbers of transistors mean more probability of heat generation source. Not only to add the number of transistors, but the modern CPU also boosts the clock frequency of the transistor in order to increase its computing ability in turn of adding the heat generation. Also, considering today's needs, the chip integrates more and more functions including fast charging, 5G communication, and individual GPU modules, which are all the main

Figure 1.2 The historical trend and CPU scaling development

heat generation sources. Not only from the hardware requirements but also the software submits the high requirement for the CPU and GPU computing ability. Today work typically needs to operate much software simultaneously and interact within them, which needs the heavy load of CPU supporting for the multitasks running. Besides, better and better vision quality needs the complexity of the high GPU computing abilities. These requirements are shown in figure 1.3 also will cause high-power consumption during running, which in turn will generate lots of heat. It is noted that these requirements normally happen in laptops and cellphones which have limited tools for heat dissipation. Therefore, it will intensify the temperature issue.

Figure 1.3 The illustration for the multitasks running and high-quality of vision during the game.

#### 1.1.3 CMOS Technology influence on the heat dissipation

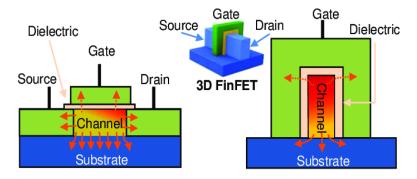

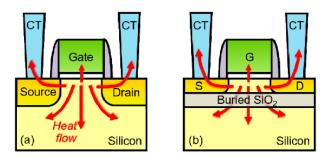

With the technology node development, the complementary MOSFET (CMOS) structure has developed with both the front end of the line (FEOL) and the back end of the line (BEOL). For the FEOL, the structure has changed a lot from the plenary CMOS to the 3D structure of FinFET and even the gate all around (GAA). As shown in figure 1.4, we can find the difference between the plenary CMOS structure and the FinFET structure. For the plenary CMOS structure, the core heat source, the channel, is adjacent with the

substrate, the source, and the drain with a large area connected which is beneficial for the heat conduction from the channel to the surrounding part for the heat dissipation. However, for the FinFET, since the channel arches up with the three-side covered by the gate oxide compared with the channel of the plenary CMOS with one top side covered, has only one bottom side connecting to the substrate for the heat conduction. Also, FinFET is an advanced technology node with a very short length resulting in the small er area connected to the substrate, which is a huge obstacle for heat dissipation [1].

Figure 1.4 Comparison of heat flow between the plenary CMOS and FinFET.

Another structure different from the plenary CMOS is the silicon on the insulator (SOI) structures mainly for the radio-frequency (RF) application to decrease the noise coupling seen in figure 1.5. SOI structure has one layer of buried silicon dioxide underneath the active layer called the BOX. Since SiO<sub>2</sub> has bad thermal conduction, the heat accumulation inside the channel cannot flow past the substrate. Therefore, the heat has to accumulate among the channel, source, and drain parts so as to increase the temperature. Nowadays, many circuits design uses these two technologies to have the main drawback of self-heating. In the meanwhile, BEOL has more and more stacks for the advanced technology node. Because each metal layer has the insulation layer as the isolation mainly comprising of the SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> which are both poor thermal conductors, the heat can also transfer via the

BEOL to the surrounding environment, in turn of adding the difficulties for the heat dissipation.

Figure 1.5 Comparison of heat flow between the plenary CMOS and SOI.

The next issue is the packaging technology after the die fabrication. Previously, the packaging is 2D. However, in order to satisfy the scaling down the law, the industry begins to use the 2.5 and 3D packaging which makes many dies stacked together to save the plenary area for the chip. Therefore, for one chip packaging, there are maybe many dies stacked vertically which mean more heat generation source accumulate inside a small volume. Therefore, there are less effective air flow or heat sink for the 3D packaging chip and its temperature easily increase during the chip running [2]. Figure 1.6 shows the illustration for the 3D stacked chip packaging and we can find that the dies far away from the heat sink normally suffers more self-heating issue. According to the right figure example, the peak temperature of the 3D packaging chip is 15% higher than the 2D packaging chip.

Figure 1.6 Illustration of the 3D packaging chip impact on the temperature

#### 1.2 Thermal management background

#### 1.2.1 Temperature monitor necessity

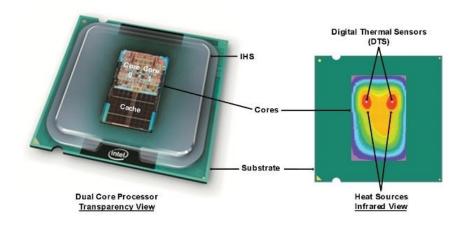

Since the easy heat generation and hard heat dissipation become a hot potato with the chip development, it is necessary to develop a method to monitor the chip temperature in order to keep it at an acceptable level. Normally the circuit performance will dramatically degrade with the increasing temperature. Even in some cases, the function will be impaired. Because of the intrinsic MOSFET properties, with the increasing temperature, the designed goals of the circuits cannot be fulfilled. Besides, even not on that high temperature, the relatively high temperature will still create many potential problems like largely decreasing the lifetime of the circuits and may even burning down some MOSFETs. In this situation, we must control the temperature of the die to guarantee its good performance and function. Therefore, the important or large scaled circuits like the CPU will have several thermal sensors monitoring the chip temperature based on several hot spots like figure 1.7 [3].

Figure 1.7 Illustration of thermal sensors on the chip

#### 1.2.2 Thermal sensors category

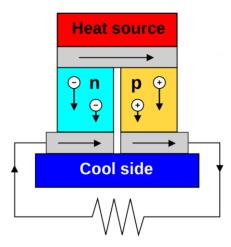

A thermal sensor on-chip normally has several types like thermocouple, thermistor, and PN junction. The thermocouple is an electrical device consisting of two different conductive materials forming the electrical junctions at different temperatures due to the Seebeck effect. The Seebeck effect is the electromotive force that develops across two points of an electrically conducting material when there is a temperature difference between them. Figure 1.8 shows the mechanism of the thermocouple circuit utilizing the Seebeck effect. Thermocouple utilizes this effect to detect one end of the temperature with the aid of the other end in the reference temperature environment via the self-induced voltage changing. The temperature changes responses quickly and it can get a wide temperature range. However, thermocouple normally is not sensitive to minor temperature changing and it always needs the reference temperature atmosphere where hardly coexists with the testing atmosphere within the same environment of the small chip. The thermistor is a type of resistor whose resistance is sensitive to the atmosphere temperature. It has better sensitivity compared with the thermocouple and easy structure just a resistor and its testing range is relatively wide. Nevertheless, thermistors are usually composed of ceramic or polymer material which is not compatible with CMOS fabrication. Also, the worst thing is that the thermistor has very bad linearity because of its self-heating which makes it hardly construct an equation to accurately describe the relationship between the temperature and resistance [4]. The PN junction is the only potential candidate that has good sensitivity, is CMOS fabrication compatible, and has a relatively simple structure. Also, it has good linearity to enable us to build the relationship between temperature and the current or voltage. Though the PN junction has a limited temperature range, the range is enough for IC temperature changing. Also, not a relatively fast response on temperature change is not a big issue for temperature monitoring on IC because the thermal map does not need to refresh at that high speed. In total, the PN junction of the thermal sensor is suitable for IC temperature monitoring [5] [6].

Figure 1.8 The Seebeck effect residing in the thermocouple.

#### 1.2.3 Run-time thermal management flow

For the full thermal management flow, there are five key procedures. The first is the fabricate the under-FET thermal sensor and locate it close to the target transistor. The second step is using the PN junction thermal-electrical property to sense the temperature change and convert it to the current change according to equation 1.

$$I = I_0(e^{\frac{qV}{nkT}} - 1) \tag{1}$$

In this equation, the  $I_0$  represents the saturation current, q is the charge, V is the voltage, n is the ideal factor (ideal diode is 1 and the non-ideal diode is normally  $2\sim3$ ), k is the Boltzmann factor and the T is the temperature. After getting the current signal, using the analog and digital circuits output the regulated data. Then combined the software to convert

the acquired data to the real-time thermal map. Finally, using the feedback control circuits to decrease the power consumption of the over-heated transistor to maintain the system stability. In terms of the controlling methods, we can decrease the clock frequency, decrease the power supply via regulating the LDO for voltage or current mirror for current, and so on [7] [8].

# Chapter 2 Under-FET thermal management for design reliabilityThe motivation of Under-FET thermal management

#### 2.1.1 The conventional thermal monitor system

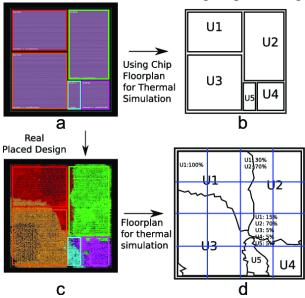

Thermal management is a grand challenge and reliable issue for the ICs stated as previously and due to the more severe inherent self-heating along with the more advanced technology process, thermal management is a necessity for a modern chip. However, the existing on-chip thermal sensing has many limitations. The reported thermal sensors including the thermocouple, thermistor, diode, BJT as well as CMOS circuits block like the bandgap or oscillator circuitry are all based on the block level [9] [10] [11]. Therefore, they cannot support this ultimate full-chip thermal management goal because of several technical problems. First, existing sensors are co-planar in nature which means that they are laterally placed next to or near the IC cores. Thus, the side-by-side proximity sensing cannot achieve the accurate temperature data of the target transistor because sensors are located too far away from the heating source to identify the hot spot like the drain or channel of the victim MOSFET. Second, the existing on-chip thermal is too large compared with the target MOSFET and many thermal sensors are not compatible with the CMOS process. Third, in order to get a full-chip thermal mapping with fine spatial resolution, we need a large in-die sensing mesh network that is not compatible with the existing co-planar sensors. Since these sensors are equivalent to the core circuit in size, they might take the unbearable area overhead on a chip. Facing the practical thermal management, these coplanar sensors are practically either under-functional that fails to detect overheating or too conservative that often leads to an overreaction in controlling IC operations, such as setting

too much headroom for a power transistor in power chips. As seen in figure 2.1, the chip is divided into five blocks which are named from u1 to U5. Each block will have one thermal sensor which is responsible to monitor the temperature of the whole block [12] [13] [14]. However, for the real heat running test, the heat will flow to the surrounding areas and the temperature of its self-block will be influenced by the neighboring blocks which makes the monitored temperature according to the pre-divided blocks useless. Therefore, the full chip with the fine spatial resolution is an urgent need.

#### 2.1.2 The conventional thermal monitor system

Ideally, precision on-chip thermal sensors will be embedded in a die to realize full-chip temperature mapping that allows dynamically controlling IC operations, hence realizing full-chip thermal management at circuit block or transistor level. This general on-chip thermal sensing and management methodology requires a chip-scale thermal sensing network, comprising thermal sensors, readout and signal processing circuitry, and global

Figure 2.1 Illustration of the block level thermal sensors floorplan on the chip

thermal control circuitry, to achieve real-time thermal sensing with high spatial resolution, ideally down to transistor level. As such, an over-heated transistor may be tuned to cool down temporarily by reducing biasing and/or clock speed, per the thermal mapping and feedback controlling, to ensure lifetime and performance. Instead of using the on-existing thermal sensors on a block level, the high-resolution thermal map generation requires large numbers of the thermal sensors to get enough specific temperature data, close to the real heat source like the drain or channel of the target MOSFET, and not taking the design area. Figure 2.2 depicts the conceptual under-FET thermal sensor implemented by the in-hole diode [15]. The diode consists of the vertical PN junction inside the TSV-like deep shaft located in the substrate close to the MOSFET channel. The deep shaft is a high-aspectratioed hole created from the backside of a Si substrate analogous to a non-through-silicon TSV hole. Careful design will be excised to maintain a safety margin between the channel bottom and the sensor hole in order to avoid any adverse impact on MOSFET performance. This novelty structure has several advantages: First, since the in-hole diode is embedded in the substrate underneath the transistor, it will not consume any extra area, which is suitable to be placed in a large number to form the thermal mesh network covering the whole chip. Second, since the sensor is placed right underneath the channel of MOSFET to sense the self-heating, it can precisely identify the self-heating source and ensure high sensing accuracy due to the extremely close to the hot spot of the victim device. Third, the thermal sensor can be readily made upon the industry CMOS process. Fourth, the diode sensor can be naturally interconnected to the readout and control circuitry on the die to realize full-chip thermal mapping and management.

#### 2.2 In-hole diode thermal sensor fabrication

The fabrication procedure starts with a 4-inch heavily doped P-type Si wafer (a resistivity < 0.0015Ω•cm via Boron doped). Ideally, a standard TSV-like process module would be used to fabricate the new in-hole diode sensors, i.e., to etch a high-aspect-ratioed TSV hole that will stop at the bottom of the active Si layer under N-/P-wells that host a MOSFET, followed by a PN diode sensor formed in the deep hole. Unfortunately, due to the lack of advanced TSV etching tool in our cleanroom facility, we have to develop an alternative process flow to fabricate the in-hole diode sensor on this work for demonstration, which can be readily modified and integrated into standard CMOS processes in the future. In the meanwhile, 2D TCAD simulation was used to optimize and guide the design and fabrication of in-hole diodes, critical to selecting the process recipes, in this work. Since this in-hole diode structure is high symmetric or centroid to the center line like a cylinder, the 3D TCAD simulation is not much improved compared to the 2D. What's more, 3D TCAD simulation is computing hungry and here the 2D TCAD is just a guideline for the fabrication instead of the accurate simulation.

Figure 2.2 Illustration of the new in-hole diode thermal sensor concept in CMOS where the sensor is embedded in a deep hole in the Si substrate under individual MOSFET for transistor-level sensing resolution.

#### 2.2.1 The deep silicon etching procedure

Because of the limitation in our cleanroom, if a deep TSV-like shaft would be created, we would not be able to etch off the SiO<sub>2</sub> layer at the bottom without etching off the SiO<sub>2</sub> layer on the side wall. Otherwise, we cannot form the in-hole PN diode. While, if the SiO2 on the side wall is etched off, it would cause the metal contact problem. To address this problem, we developed a deep ring hole approach as depicted in figure 2.3. Figure 2.3a shows a mask used to define the deep ring hole pattern and AZ4620 photoresistor (PR) is used for deep reactive ion etching (DRIE) protection. Figure 2.3b shows a zoom-in view for the etched deep ring hole by Bosch DRIE etcher. The etched deep ring hole is around 90μm to 100μm, similar to a typical TSV hole. A SiO<sub>2</sub> layer is grown via thermal oxidation to cover the inner side wall of the ring hole to isolate the in-hole diode from the surrounding Si as depicted in Figure 2.3b. Figure 2.3d gives a top view of the device area by optical microscope showing the deep ring hole and the in-hole diode area. In this figure, we can see the deep ring around the center silicon pole. Figure 2.3c is the SEM cross-section view of the side wall of the etched deep ring hole following the cut-line shown in Figure 2.3d, where the unique etching pattern on the side wall came from the Bosch DRIE processes of alternatively using SF<sub>6</sub> plasm bottom etching and C<sub>4</sub>F<sub>8</sub> plasma side protection flow. A group of in-hole devices with different dimensions were designed with the outer ring diameters being 400µm, 600µm, 800µm, and 1000µm, and the inner ring diameters of 250μm, 400μm, 500μm, and 600μm, respectively. The etched deep ring hole has a width of 75µm to 200µm corresponding to the different dimensions like the diameters.

The next step is to create a TSV-like deep hole to host the in-hole PN diode. Since a thin SiO<sub>2</sub> layer was grown to cover all surfaces of the etched deep ring hole structure, grown in an oxidation furnace, we need to etch the SiO<sub>2</sub> above the center silicon pole to open the window for the followed long-time high-power DRIE follows to form the desired deep hole to host the in-hole PN diode. Because of the previous ring structure, the SiO<sub>2</sub> etching will be easy due to its location not being on the bottom of the TSV shaft. Since the

Figure 2.3 (a) Si substrate covered by a mask for DRIE etching to create a deep ring hole, (b) a zoom-in view for the deep ring hole etched by DRIE, covered by the required SiO<sub>2</sub> isolation layer, (c) SEM X-section view of the etched side wall of the deep ring hole, and (d) a top view of in-hole diodes by optical microscope.

top edge of the silicon sidewall is vertical, the photoresist is hardly hung along with the etch to provide enough thickness in order to protect the SiO<sub>2</sub> from etching off during the

long-time high power DRIE. Therefore, during this step, a combined PR/Al layer stack is used where the patterned Al layer serves as a hard mask to keep the shape of the top edge of the deep shaft because it has very high etching selective during the DRIE. Figure 2.4a is the TCAD simulation that shows the deep ring structure is patterned by the PR/Al mask. The cyan stands for aluminum and the light-yellow stands for the photoresist.

Figure 2.4b shows the optical image with the Al hard mask covering the outside of the deep ring hole including the corner with the center-left open for DRIE etching. A very thick PR (positive photoresist AZ4601) layer, filling the deep ring hole, serves to protect the SiO<sub>2</sub> layer that covers the inner wall surface of the deep hole during DRIE etching, which is fairly difficult to handle because of requiring careful craftsman's work for PR

Figure 2.4 (a) TCAD simulation shows the deep hole using a hard Al-mask to protect the top edges of the hole, (b) confocal microscope 3D image of ring structure with photoresist covering the SiO<sub>2</sub> side wall (c) using Al as the hard mask to protect the corner from being etched.

baking, exposure and developing to the ensure the fine patterns. A mask is used to define the opening of the deep shaft area, which will be etched to the bottom by DRIE etching to form the required high-aspect-ratioed deep shaft shown in figure 2.4c. Then the mask will

be etched to the bottom by first the normally SiO<sub>2</sub> above the silicon pole etching followed by DRIE etching to form the required high-aspect-ratioed deep shaft as shown in figure 2.5a. After the etching is finished, we will strip the photoresist and then wet etch off the aluminum hard mask to show the bottom silicon exposed and with the side wall still covered by the SiO<sub>2</sub> insulator. Figure 2.5b shows the whole image after the second DRIE etching where the center part looks gray, which is the silicon opening not covered by SiO<sub>2</sub>. To this step, we can get the desired TSV structure with half P part of the PN junction exposed at the bottom of the deep shaft.

#### 2.2.2 PN junction formation