## **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

System Architecture and Signal Processing Techniques for Massive Multi-user Antenna Arrays

#### **Permalink**

https://escholarship.org/uc/item/6x176573

#### **Author**

Puglielli, Antonio

#### **Publication Date**

2017

Peer reviewed|Thesis/dissertation

## System Architecture and Signal Processing Techniques for Massive Multi-user Antenna Arrays

by

Antonio Puglielli

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Elad Alon Professor David Aldous

Fall 2017

# System Architecture and Signal Processing Techniques for Massive Multi-user Antenna Arrays

Copyright 2017 by Antonio Puglielli

#### Abstract

System Architecture and Signal Processing Techniques for Massive Multi-user Antenna Arrays

by

#### Antonio Puglielli

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

Future advancements in wireless communication standards will rely on two inter-related technologies. First, to address the saturation of traditional cellular spectrum in the < 6 GHz bands, new and much-higher frequency mm-wave spectrum will be utilized. The mm-wave bands at 24, 28, 39, 60, and 72 GHz, among others, have tens of gigahertz of available and unused spectrum. Second, because modern coding and modulation techniques make near-optimal use of time and frequency resources, the spatial dimension of wireless channels must be exploited to send data streams in a spatially selective manner only to the desired users.

From an engineering perspective, both of these technology trends rely on the design of antenna arrays — spatial selectivity is achieved by having a large number of radios while mm-wave operation needs directional transmissions to overcome the propagation loss. Designing large antenna arrays — on the order of 64-256 or larger number of radios — represents a huge departure from traditional radios used in wireless networks which have at most 4 independent radiators and transceiver chains.

This thesis explores system architecture, signal processing, and hardware design techniques which are suitable for massive antenna arrays which form many spatial beams simultaneously. First, beamforming is identified as the preferred spatial processing technique for the large array regime, and a beamforming-aware array architecture is proposed which is modular, scalable, and distributed. The core element of the proposed array architecture is a common module which integrates multiple transceivers, analog and digital signal processing, and interconnect. Additionally, a time-domain beamforming algorithm is proposed for channels with strong multipath components.

Next, synchronization architectures and algorithms are proposed for both carrier and baseband synchronization in massive antenna arrays. It is shown that uncorrelated phase noise between different transceivers causes decoherence between the front ends. Accordingly, a synchronization strategy consisting of co-optimized carrier recovery loops and distributed phase-locked loops (PLLs) is proposed to manage the total phase noise impact in antenna arrays. For baseband synchronization, a hierarchical timing alignment strategy is proposed

which uses a background calibration loop to compensate for front-end and sampling skews while using distributed data timing recovery to compensate for true time delay effects in large arrays.

Finally, hardware implementations of these system- and signal-processing-level ideas are demonstrated. The first prototype consists of a system-on-chip for low-frequency massive MIMO. The proposed SoC integrates multiple full digital radios with on-chip DSP and serial links. The second prototype demonstrates the first massive, multi-user phased array operating at 72GHz. A 128-element phased array is implemented using off-the-shelf components which can form 16 simultaneous beams over 250MHz bandwidth, for an aggregate capacity of 20 Gbps.

Dedication

Per Nonno Tonino

# Contents

| C              | Contents         |                                                                 | ii           |  |

|----------------|------------------|-----------------------------------------------------------------|--------------|--|

| $\mathbf{Li}$  | st of            | Figures                                                         | $\mathbf{v}$ |  |

| List of Tables |                  | ix                                                              |              |  |

| 1              | Intr             | roduction                                                       | 1            |  |

|                | 1.1              | Motivation: Large Arrays are Needed to Extend Network Capacity  | 1            |  |

|                |                  | 1.1.1 Spatial Processing                                        | 2            |  |

|                |                  | 1.1.2 Moving to higher frequencies                              | 4            |  |

|                | 1.2              | Prior work in array design                                      | 5            |  |

|                | 1.3              | Thesis scope and outline                                        | 6            |  |

| 2              | Array Processing |                                                                 |              |  |

|                | 2.1              | Phased Arrays                                                   | 8            |  |

|                | 2.2              | Spatial Processing for Communications                           | 11           |  |

|                |                  | 2.2.1 Channel Matrices and Channel Estimation                   | 11           |  |

|                |                  | 2.2.2 Single-user and Multi-user MIMO                           | 12           |  |

|                |                  | 2.2.3 Linear Beamforming                                        | 13           |  |

|                |                  | 2.2.4 Maximum Likelihood Detection, Sphere Decoding, and K-Best | 17           |  |

|                |                  | 2.2.5 Successive Interference Cancellation                      | 18           |  |

|                |                  | 2.2.6 Dirty Paper Coding                                        | 19           |  |

|                | 2.3              | Linear Beamformers for Wideband Channels                        | 19           |  |

|                |                  | 2.3.1 Frequency-Flat Beamforming                                | 20           |  |

|                |                  | 2.3.2 Frequency-Domain Beamforming                              | 21           |  |

|                | 2.4              | Case Study on Wideband Beamforming Performance                  | 22           |  |

|                | 2.5              | Summary                                                         | 26           |  |

| 3              | Arr              | ay Architecture for the Massive Regime                          | 27           |  |

|                | 3.1              | Spatial Processing for the Large Array Regime                   | 28           |  |

|                |                  | 3.1.1 Computational Complexity                                  | 28           |  |

|                |                  | 3.1.2 Performance Comparison of Linear and Nonlinear schemes    | 28           |  |

|   |     | 3.1.3 Performance Comparison of Linear Beamformers              | 30 |

|---|-----|-----------------------------------------------------------------|----|

|   | 3.2 | A Scalable Beamforming-Aware Array Architecture                 | 32 |

|   |     | 3.2.1 State of the Art                                          | 32 |

|   |     | 3.2.2 Large Arrays Must Use Distributed Processing              | 35 |

|   |     | 3.2.3 The Interconnect Must be Digital                          | 37 |

|   |     | 3.2.4 The Array should be Composed of Common Modules            | 38 |

|   | 3.3 | Fully Distributed Signal Processing with Two-Stage Beamforming  | 40 |

|   | 3.4 | FIR Filter-Bank Beamforming                                     | 43 |

|   |     | 3.4.1 Review of FIR Equalizers for SISO Channels                | 44 |

|   |     | 3.4.2 Design of Time-Domain Beamformers                         | 46 |

|   |     | 3.4.3 MIMO FIR Beamformer in the Large Array Regime             | 48 |

|   |     | 3.4.4 Equivalence of FIR and FDE Beamformers                    | 51 |

|   |     | 3.4.5 Computational Complexity of FIR and FDE Beamformers       | 53 |

|   |     | 3.4.6 Mixed Time- and Frequency-Domain Algorithm                | 54 |

|   |     | 3.4.7 Summary                                                   | 55 |

| 4 | Car | rier Generation and Synchronization                             | 56 |

| _ | 4.1 | LO Distribution Architectures                                   | 57 |

|   |     | 4.1.1 LO Subsystem Components                                   | 58 |

|   |     | 4.1.2 Comparison of LO Distribution Architectures               | 59 |

|   | 4.2 | Phase Noise Filtering Loops                                     | 62 |

|   |     | 4.2.1 Phase-locked Loops                                        | 62 |

|   |     | 4.2.2 Channel Estimation                                        | 64 |

|   |     | 4.2.3 Carrier Recovery                                          | 64 |

|   | 4.3 | System Model for Carrier Generation in Large Arrays             | 65 |

|   |     | 4.3.1 OFDM System Model                                         | 65 |

|   |     | 4.3.2 Single-carrier System Model                               | 68 |

|   | 4.4 | Phase Noise in Single-User Arrays                               | 70 |

|   |     | 4.4.1 Signal Energy Loss from Uncorrelated Phase Noise          | 71 |

|   |     | 4.4.2 Gain and Phase Fluctuations from Uncorrelated Phase Noise | 71 |

|   |     | 4.4.3 SINR for SIMO Arrays with Phase Noise                     | 73 |

|   | 4.5 | Phase Noise in Multi-User Arrays                                | 75 |

|   |     | 4.5.1 SINR for Multi-User Arrays with Phase Noise               | 77 |

|   |     | 4.5.2 PLL Sharing in Multi-User Arrays                          | 79 |

|   |     | 4.5.3 Full-System Simulations                                   | 79 |

|   | 4.6 | Summary: LO Generation Approach for Large Arrays                | 79 |

| 5 | Hie | rarchical Baseband Synchronization                              | 81 |

| _ | 5.1 | Background: Synchronization Requirements and Architecture       | 81 |

|   | J.1 | 5.1.1 Synchronization Architecture                              | 83 |

|   | 5.2 | Distributed ADC de-skew in a Modular Digital Array              | 85 |

|   |     | U V                                                             |    |

|   | 5.3<br>5.4<br>5.5         | 5.2.1 Joint Golay Channel and Timing Estimator                                                                                                                                                                                                    | 86<br>88<br>90<br>90<br>93<br>93                                                 |

|---|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 6 | Sys                       | tem-on-Chip for $< 6 \mathrm{GHz}$ Massive MIMO                                                                                                                                                                                                   | 97                                                                               |

|   | 6.1                       | Overview                                                                                                                                                                                                                                          | 97                                                                               |

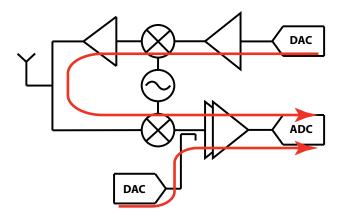

|   | 6.2                       | RX and TX filters                                                                                                                                                                                                                                 | 99                                                                               |

|   | 6.3                       | TX Quantization Noise Averaging                                                                                                                                                                                                                   | 100                                                                              |

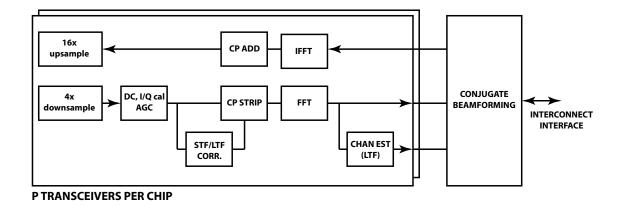

|   | 6.4                       | DSP Path                                                                                                                                                                                                                                          | 102                                                                              |

|   |                           | 6.4.1 ADC and DAC Timing                                                                                                                                                                                                                          | 104                                                                              |

|   |                           | 6.4.2 Reciprocity Calibration                                                                                                                                                                                                                     | 104                                                                              |

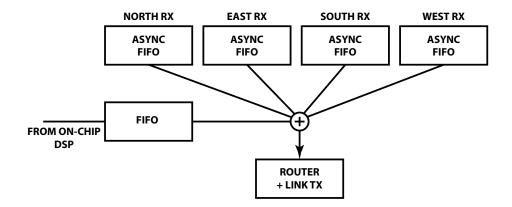

|   |                           | 6.4.3 Link Router                                                                                                                                                                                                                                 | 105                                                                              |

|   | 6.5                       | Test Chip                                                                                                                                                                                                                                         | 107                                                                              |

| 7 | Des                       | sign of a Massive MIMO Array at E-Band                                                                                                                                                                                                            | 108                                                                              |

|   | 7.1                       | System Overview                                                                                                                                                                                                                                   |                                                                                  |

|   |                           |                                                                                                                                                                                                                                                   | 108                                                                              |

|   |                           | 7.1.1 Link Budget                                                                                                                                                                                                                                 | 108<br>109                                                                       |

|   | 7.2                       | 7.1.1 Link Budget                                                                                                                                                                                                                                 |                                                                                  |

|   | 7.2                       | $\sim$                                                                                                                                                                                                                                            | 109                                                                              |

|   | 7.2                       | Hardware Implementation                                                                                                                                                                                                                           | 109<br>110                                                                       |

|   | 7.2<br>7.3                | Hardware Implementation                                                                                                                                                                                                                           | 109<br>110<br>110<br>111<br>111                                                  |

|   |                           | Hardware Implementation 7.2.1 Modular Architecture 7.2.2 Testbed design Signal Processing Chain 7.3.1 DSP Chain Overview                                                                                                                          | 109<br>110<br>110<br>111<br>111<br>111                                           |

|   |                           | Hardware Implementation 7.2.1 Modular Architecture 7.2.2 Testbed design Signal Processing Chain 7.3.1 DSP Chain Overview 7.3.2 Frame Structure                                                                                                    | 109<br>110<br>110<br>111<br>111<br>111<br>115                                    |

|   | 7.3                       | Hardware Implementation 7.2.1 Modular Architecture 7.2.2 Testbed design Signal Processing Chain 7.3.1 DSP Chain Overview 7.3.2 Frame Structure 7.3.3 Two-stage Beamforming: ZF at Low SNR                                                         | 109<br>110<br>110<br>111<br>111<br>111<br>115<br>116                             |

|   |                           | Hardware Implementation 7.2.1 Modular Architecture 7.2.2 Testbed design Signal Processing Chain 7.3.1 DSP Chain Overview 7.3.2 Frame Structure                                                                                                    | 109<br>110<br>110<br>111<br>111<br>111<br>115                                    |

| 8 | 7.3<br>7.4                | Hardware Implementation 7.2.1 Modular Architecture 7.2.2 Testbed design Signal Processing Chain 7.3.1 DSP Chain Overview 7.3.2 Frame Structure 7.3.3 Two-stage Beamforming: ZF at Low SNR Results and Measurements                                | 109<br>110<br>110<br>111<br>111<br>111<br>115<br>116<br>117                      |

| 8 | 7.3<br>7.4                | Hardware Implementation 7.2.1 Modular Architecture 7.2.2 Testbed design Signal Processing Chain 7.3.1 DSP Chain Overview 7.3.2 Frame Structure 7.3.3 Two-stage Beamforming: ZF at Low SNR                                                         | 109<br>110<br>110<br>111<br>111<br>111<br>115<br>116                             |

| 8 | 7.3 7.4 Con               | Hardware Implementation 7.2.1 Modular Architecture 7.2.2 Testbed design Signal Processing Chain 7.3.1 DSP Chain Overview 7.3.2 Frame Structure 7.3.3 Two-stage Beamforming: ZF at Low SNR Results and Measurements                                | 109<br>110<br>111<br>111<br>111<br>115<br>116<br>117                             |

|   | 7.4<br>Cor.<br>8.1<br>8.2 | Hardware Implementation 7.2.1 Modular Architecture 7.2.2 Testbed design Signal Processing Chain 7.3.1 DSP Chain Overview 7.3.2 Frame Structure 7.3.3 Two-stage Beamforming: ZF at Low SNR Results and Measurements  aclusion Thesis Contributions | 109<br>110<br>110<br>111<br>111<br>111<br>115<br>116<br>117<br><b>120</b><br>120 |

# List of Figures

| 2.1  | Phased array principle of operation, and example beampattern                                                                                          | 9   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | True time delay effects in phased arrays                                                                                                              | 10  |

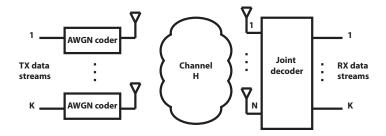

| 2.3  | SU or MU MIMO scenario with only RX CSI. All spatial processing must be                                                                               |     |

|      | performed at the receiver                                                                                                                             | 13  |

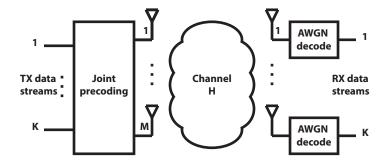

| 2.4  | Downlink MU-MIMO, where all spatial processing must be performed at the base-station                                                                  | 13  |

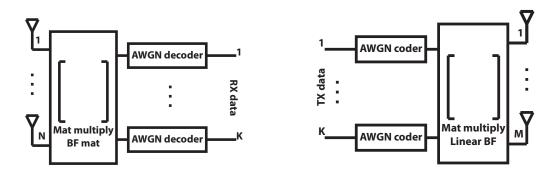

| 2.5  | Linear beamforming at RX (left) and TX (right)                                                                                                        | 14  |

| 2.6  | Comparison of conjugate, zero-forcing, and MMSE beampatterns for an 8-element                                                                         |     |

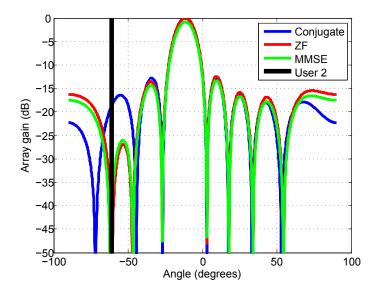

|      | array serving 2 users                                                                                                                                 | 17  |

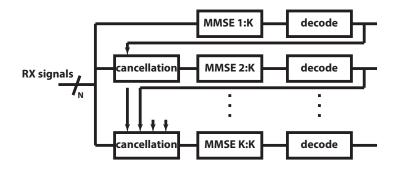

| 2.7  | MMSE successive interference cancellation (SIC) receiver                                                                                              | 18  |

| 2.8  | True time delay (left) and multipath (right) channels, showing how time and                                                                           |     |

|      | space are inextricably linked                                                                                                                         | 19  |

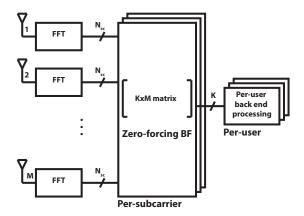

| 2.9  | Block diagram of a receiver using full frequency-domain beamforming — a differ-                                                                       |     |

|      | ent $M \times K$ beamforming matrix is used for each subcarrier                                                                                       | 22  |

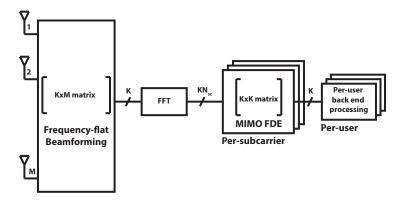

| 2.10 | Block diagram of a receiver using frequency-flat beamforming with a MIMO FDE                                                                          |     |

|      | — a single $M \times K$ beamforming matrix is applied in the time domain followed                                                                     |     |

|      | by a $K \times K$ MIMO FDE                                                                                                                            | 23  |

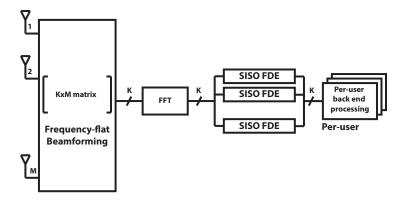

| 2.11 | Block diagram of a receiver using frequency-flat beamforming with only per-user                                                                       | 0.0 |

|      | SISO equalization.                                                                                                                                    | 23  |

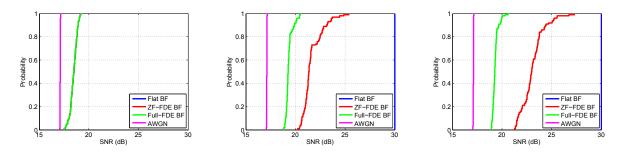

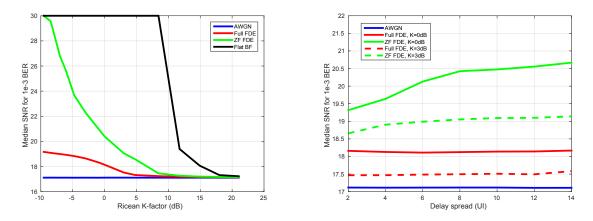

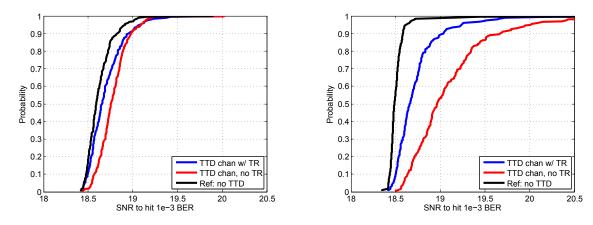

| 2.12 | CDF of SNR required to achieve $10^{-3}$ BER in WLAN channel models A-C, with $M=128$ and $K=16$ , using Full-FDE, ZF-FDE, and Flat-BF receivers. (a) |     |

|      | Channel model A (line of sight). (b) Channel model B (small office). (c) Channel                                                                      |     |

|      | model C (medium office).                                                                                                                              | 24  |

| 2.13 | Median SNR required to obtain 1e-3 BER with $M=128$ and $K=16$ . (a) Ricean                                                                           |     |

|      | K-factor is swept while delay spread is constant at 6. (b) Delay spread is swept                                                                      |     |

|      | for K-factor of 0dB or 3dB.                                                                                                                           | 24  |

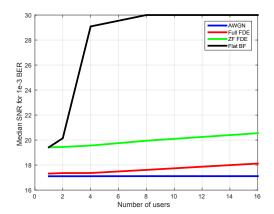

| 2.14 | Median SNR required to obtain 1e-3 BER with 0dB K-factor and delay spread                                                                             |     |

|      | of 18. (a) Varying number of users, with $M = 128$ . (b) Varying number of array                                                                      |     |

|      | antennas, with $K=2$                                                                                                                                  | 25  |

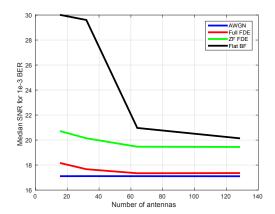

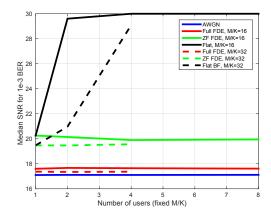

| 2.15 | Median SNR required to obtain 1e-3 BER with $M/K$ fixed at 8 and varying                                                                              |     |

|      | number of users.                                                                                                                                      | 26  |

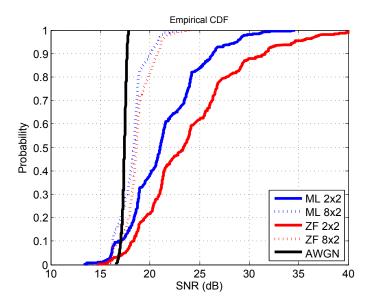

| 3.1         | Cumulative density function of SNR required to achieve 1e-3 bit error rate (BER) in 2 different MIMO Rayleigh channels with ML and zero-forcing detection | 29 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

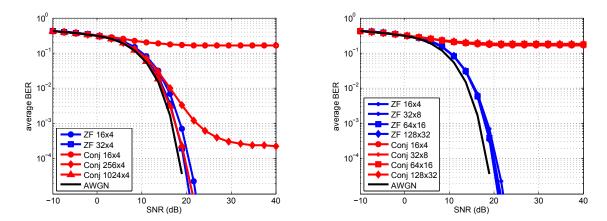

| 3.2         | Average BER vs SNR for ZF and conjugate beamforming in a Rayleigh channel.                                                                                | 20 |

| J. <b>_</b> | (a) $K=4$ , with varying array size. (b). Varying number of users with $M/K=4$ .                                                                          | 31 |

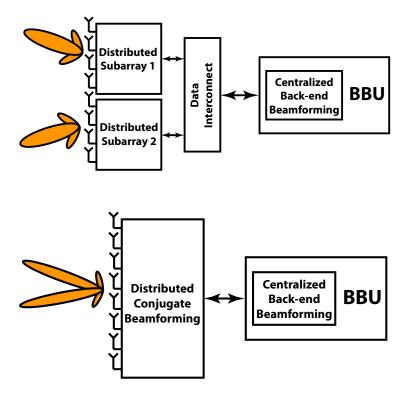

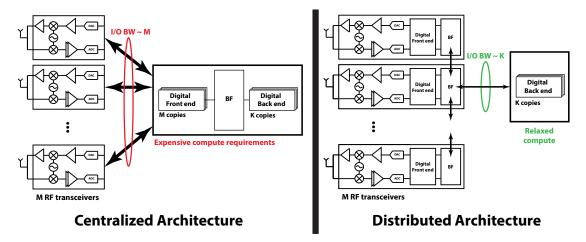

| 3.3         | Partially (top) and full (bottom) connected array architectures                                                                                           | 34 |

| 3.4         | Comparison of centralized and distributed processing architectures for massive                                                                            |    |

|             | MIMO arrays                                                                                                                                               | 35 |

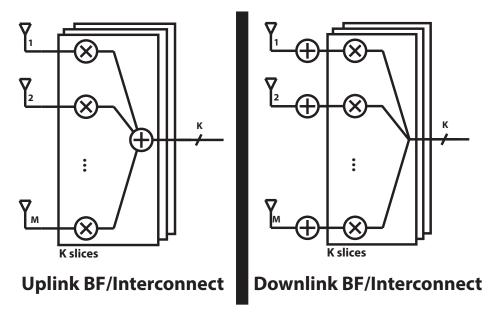

| 3.5         | Implementation of distributed beamforming and data interconnect for uplink and                                                                            |    |

|             | downlink.                                                                                                                                                 | 37 |

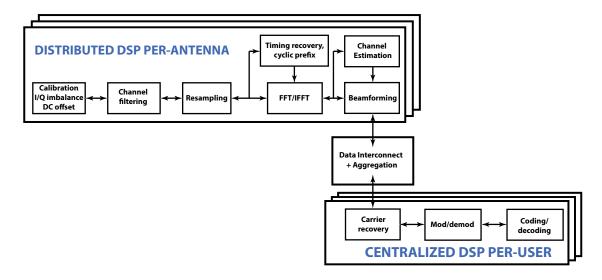

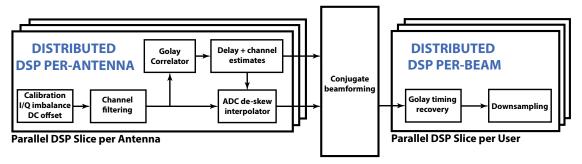

| 3.6         | Distributed datapath for an OFDM based communication system — per-antenna                                                                                 |    |

|             | functions are local to the transceiver while per-user functions are centralized                                                                           | 38 |

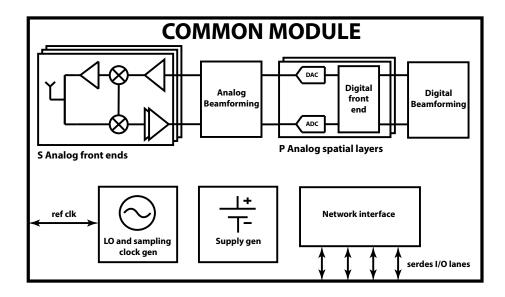

| 3.7         | Block diagram of a generic common module for a massive MIMO array, including                                                                              |    |

|             | signal path and shared support functions                                                                                                                  | 39 |

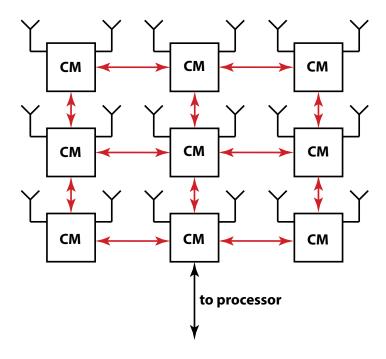

| 3.8         | Modular and scalable implementation of a massive MIMO array using common                                                                                  |    |

|             | modules                                                                                                                                                   | 40 |

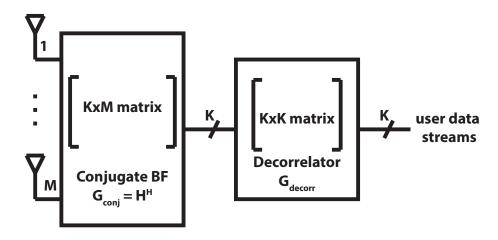

| 3.9         | Conceptual mapping of any beamformer (including conjugate, ZF, or MMSE)                                                                                   |    |

|             | into a two-stage structure — beamforming + decorrelation — for both transmit                                                                              |    |

|             | and receive directions                                                                                                                                    | 42 |

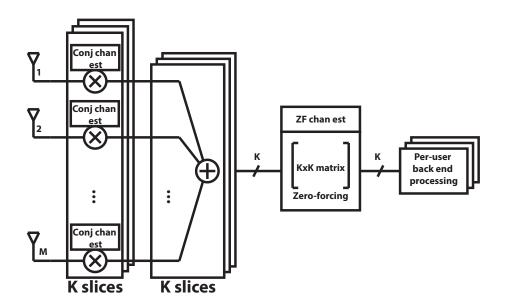

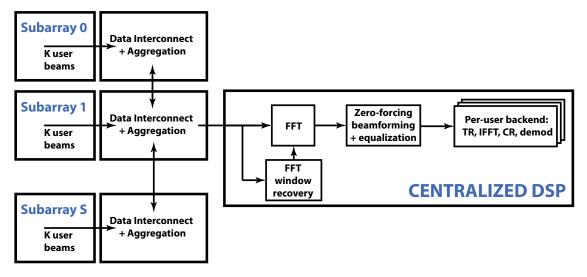

| 3.10        | Implementation of two-stage receive-side beamforming, for a frequency-domain                                                                              |    |

|             | beamformer, with distributed conjugate estimation/beamforming and centralized                                                                             |    |

|             | zero-forcing                                                                                                                                              | 42 |

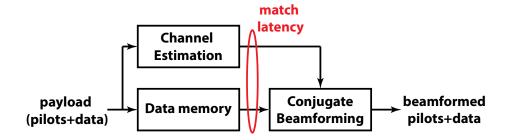

| 3.11        | Pilot beamforming algorithm. Incoming data payload is delayed to match the                                                                                |    |

|             | latency of the channel estimation block so that both pilots and data may be                                                                               |    |

|             | conjugate beamformed                                                                                                                                      | 43 |

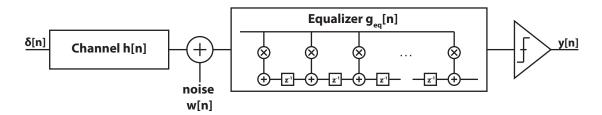

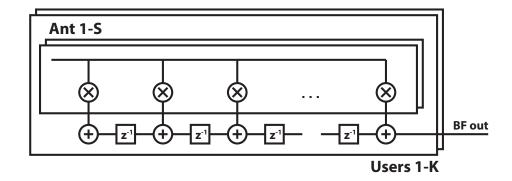

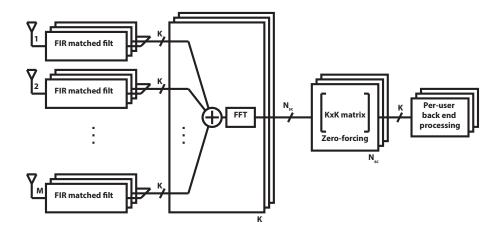

| 3.12        | SISO FIR equalizer design scenario                                                                                                                        | 45 |

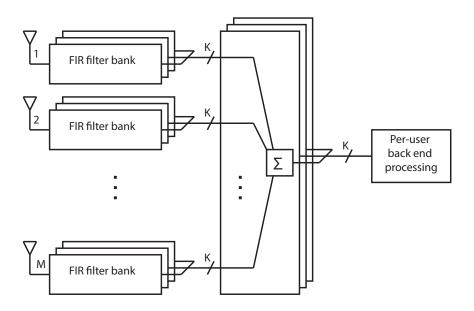

| 3.13        | Block diagram of a receiver using the proposed time-domain beamforming and                                                                                |    |

|             | equalization — each receiver is equipped with a bank of $K$ FIR filters                                                                                   | 48 |

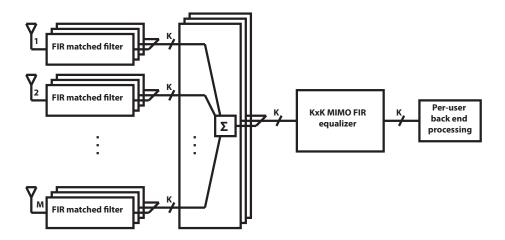

| 3.14        | Two-stage FIR beamforming: bank of matched filters at each antenna followed by                                                                            |    |

|             | summation network and a $K \times K$ matrix FIR zero-forcing beamformer/equalizer.                                                                        | 51 |

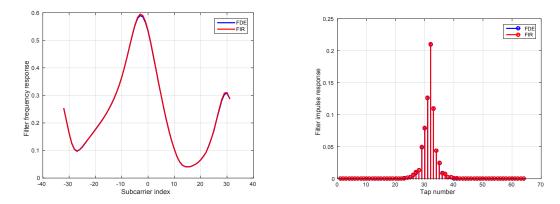

| 3.15        | ( ) 1 0 1                                                                                                                                                 |    |

|             | C. (b) Impulse response of FIR and FDE beamformers in a WLAN channel model                                                                                |    |

|             | C                                                                                                                                                         | 52 |

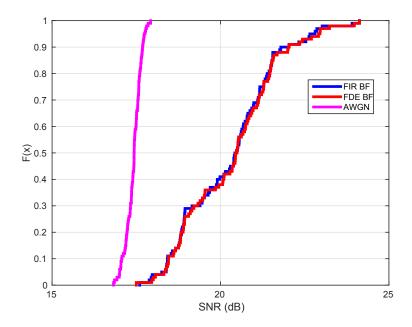

| 3.16        | CDF of SNR required to achieve a $10^{-3}$ BER in a WLAN channel model C                                                                                  |    |

|             | environment, with $M=16$ and $K=2$ , comparing FIR and FDE schemes                                                                                        | 52 |

| 3.17        | Optimal FIR-beamforming structure for implementation on a subarray basis when                                                                             |    |

|             | K < S                                                                                                                                                     | 53 |

| 3.18        |                                                                                                                                                           |    |

|             | process one OFDM symbol $(N = N_{sc})$                                                                                                                    | 54 |

| 3.19        |                                                                                                                                                           |    |

|             | ing: a matched filter bank per receiver followed by a ZF or MMSE FDE on a                                                                                 |    |

|             | per-subcarrier basis                                                                                                                                      | 54 |

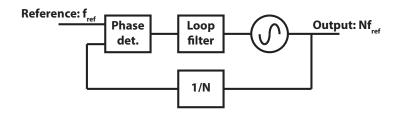

| 4.1         | Block diagram of standard PLL                                                                                                                                         | 57 |

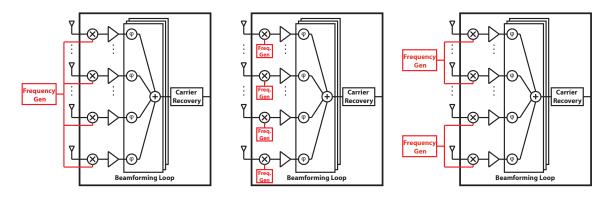

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2         | Three main LO distribution architectures. (a) Central carrier generation (CCG),                                                                                       |    |

|             | (b) Local carrier generation (LCG), (c) Generalized carrier generation (GCG)                                                                                          | 59 |

| 4.3         | LO subsystem power consumption versus PLL hierarchy. (a) 5GHz array. b)                                                                                               |    |

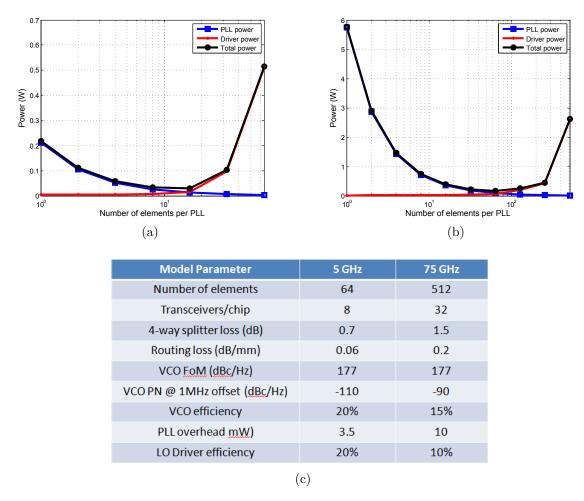

|             | 75GHz array. (c) Model parameters                                                                                                                                     | 61 |

| 4.4         | (a) PLL reference and VCO noise transfer functions. (b) Phase noise PSDs at                                                                                           |    |

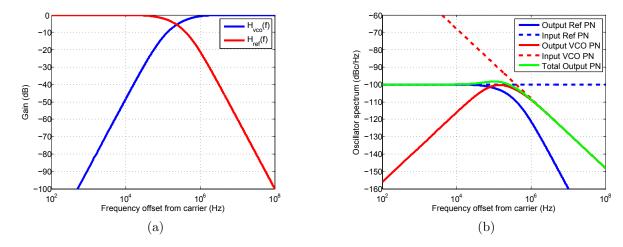

|             | the input and output of the PLL                                                                                                                                       | 63 |

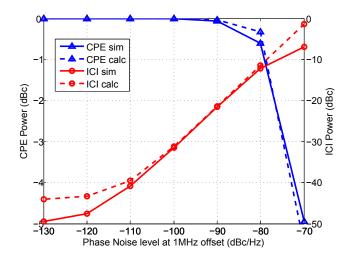

| 4.5         | Simulated and predicted results of ICI and CPE power based on the model in $(4.11)$ and $(4.12)$ , for a PLL with 200kHz bandwidth and $B_{sc}$ of 624kHz             | 67 |

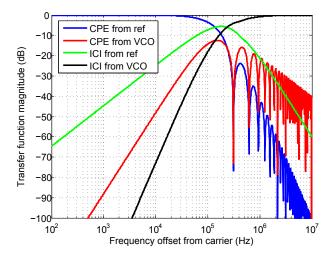

| 4.6         | Cascaded transfer function of reference and VCO phase noise to the CPE and ICI, with $B_{PLL} = 200kHz$ and $B_{sc} = 312kHz$ . These results validate the conclusion |    |

|             | that reference noise dominates the CPE while VCO noise dominates the ICI                                                                                              | C  |

| 1 7         | generation.                                                                                                                                                           | 67 |

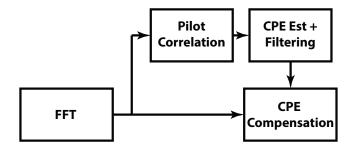

| 4.7         | Feedforward pilot-based carrier recovery for OFDM modulation                                                                                                          | 68 |

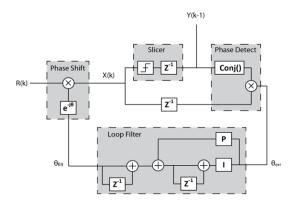

| 4.8         | Block diagram of decision-directed carrier recovery loop                                                                                                              | 69 |

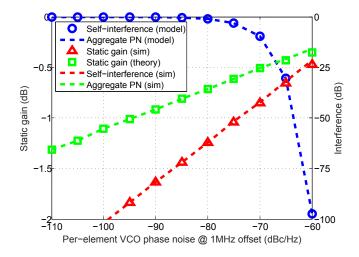

| 4.9         | Characterization of error mechanisms from uncorrelated VCO phase noise in a 16-element array                                                                          | 72 |

| <i>1</i> 10 | SINR versus PLL bandwidth for a 2.5GHz 64-element MIMO-OFDM array with                                                                                                | 12 |

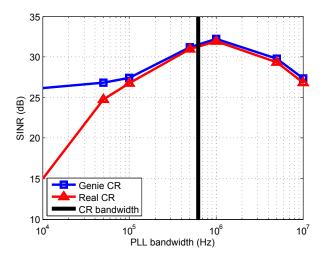

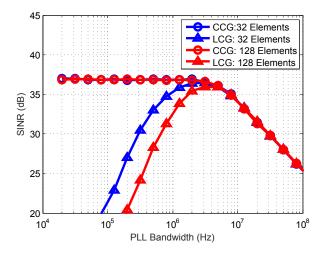

| 4.10        | $B_{sc}$ of 624kHz and effective phase noise of -100dBc/Hz at 1MHz offset                                                                                             | 75 |

| <i>1</i> 11 | $B_{sc}$ of 024kHz and elective phase hoise of -100dBc/Hz at IMHz obset SINR versus PLL bandwidth for a 75GHz single-carrier massive MIMO array                       | 10 |

| 4.11        | with CR bandwidth of 10MHz, reference noise at -140dBc/Hz and VCO effective                                                                                           |    |

|             | phase noise of -90dBc/Hz at 1MHz offset.                                                                                                                              | 75 |

| 4.12        | Simulated and predicted SINR for synchronous array with various levels of phase                                                                                       | 10 |

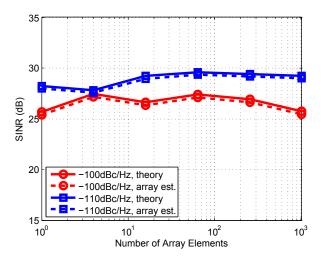

| <b>-</b>    | noise. $B_{PLL} = 500kHz$ , $B_{sc} = 312kHz$ , and $N_{sc} = 64$                                                                                                     | 76 |

| 4.13        | Simulated SINR with multi-user, synchronous array. $B_{PLL} = 500kHz$ , $B_{sc} =$                                                                                    |    |

|             | $624kHz$ , and $N_{sc} = 64$                                                                                                                                          | 78 |

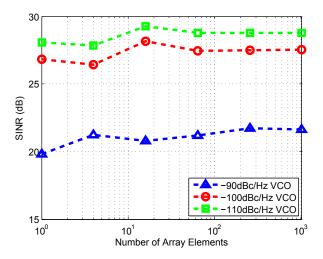

| 4.14        | Average SINR vs number of users for 128-element array with CCG or LCG                                                                                                 |    |

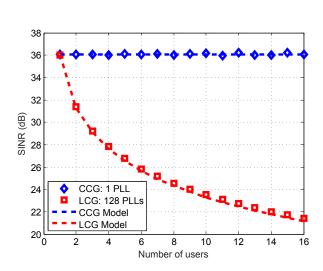

|             | scheme. Carrier recovery bandwidth is 10 MHz and PLL bandwidth is 5 MHz                                                                                               | 78 |

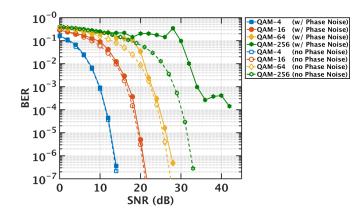

| 4.15        | Sum BER for 16 users versus thermal SNR with and without phase noise, for                                                                                             |    |

|             | various constellation orders. The carrier recovery bandwidth is optimized for                                                                                         |    |

|             | each thermal SNR level. The phase noise limited SINR is 36dB                                                                                                          | 80 |

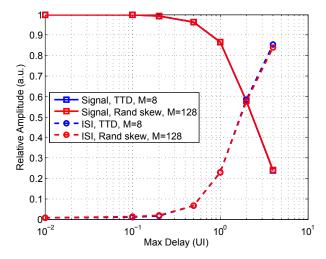

| 5.1         | Total signal energy loss and ISI energy as a function of worst-case timing offset.                                                                                    | 82 |

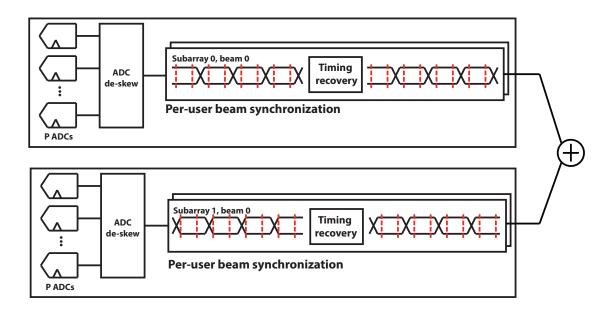

| 5.1         | Hierarchical baseband synchronization strategy                                                                                                                        | 84 |

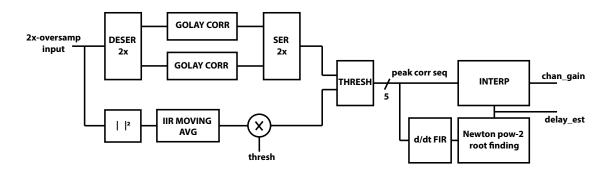

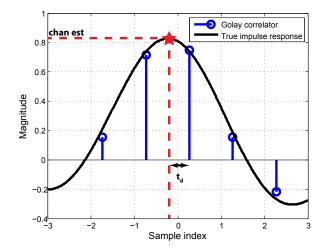

| 5.3         | Joint Golay channel and delay estimator for 2x oversampled input                                                                                                      | 87 |

| 5.4         | Estimated channel impulse response from polyphase Golay correlator                                                                                                    | 87 |

| 5.5         | Detection, delay estimation, and channel estimation accuracy achieved by the                                                                                          | 01 |

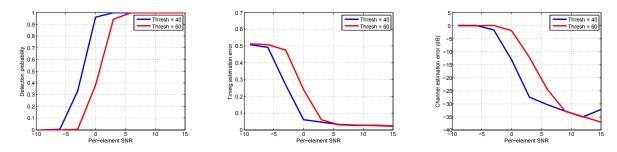

| 5.5         | proposed Golay channel/delay estimator                                                                                                                                | 89 |

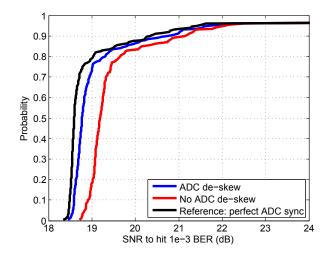

| 5.6         | ADC de-skew performance in a 16-element subarray serving 4 users                                                                                                      | 89 |

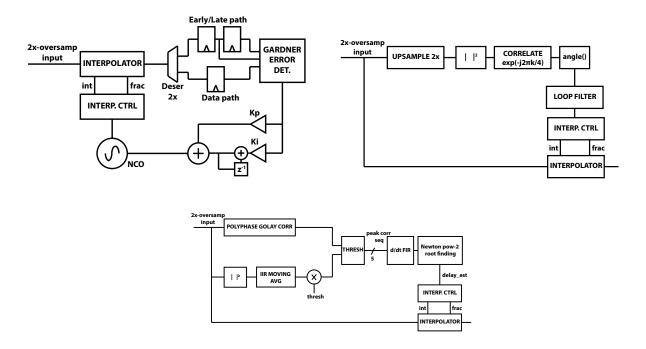

| 5.7         | Three timing recovery algorithms: NDA feedback loop with Garder detector,                                                                                             | 00 |

|             | O&M feedforward spectral estimator, and Golay pilot-aided estimator                                                                                                   | 91 |

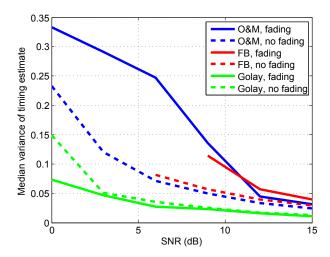

| 5.8  | Comparison of feedback, O&M feedforward, and Golay timing recovery performance versus thermal SNR                                                   | 92           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 5.9  | True-time delay compensation using distributed Golay-aided timing recovery at each subarray for 200MHz and 2GHz channel bandwidths at 75GHz carrier | 93           |

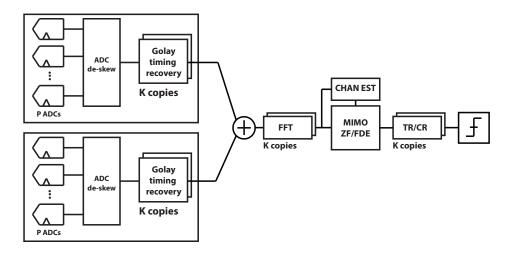

| 5.10 | Overall array DSP chain including subarrays and central processor                                                                                   | 93           |

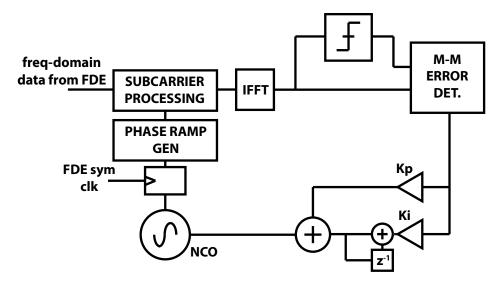

| 5.11 | Time-frequency timing recovery loop using Mueller-Muller detector                                                                                   | 95           |

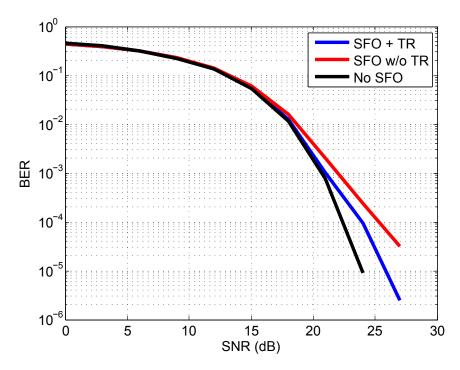

|      | Performance of time-frequency timing recovery algorithm with 20ppm offset SFO.                                                                      | 96           |

| 6.1  | Block diagram of $< 6$ GHz massive MIMO SoC                                                                                                         | 98           |

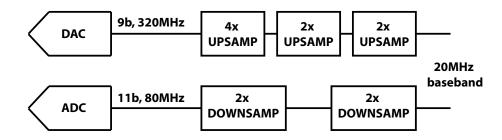

| 6.2  | Analog interface including ADC/DAC and resampling filter hierarchy                                                                                  | 99           |

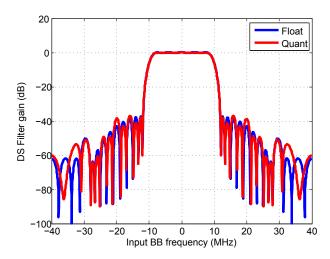

| 6.3  | Receiver downsampling filter transfer function                                                                                                      | 100          |

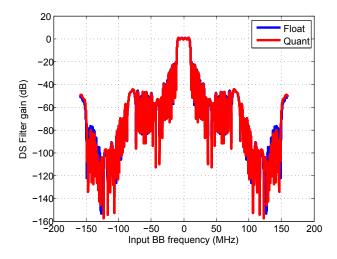

| 6.4  | Transmitter upsampling filter transfer function                                                                                                     | 100          |

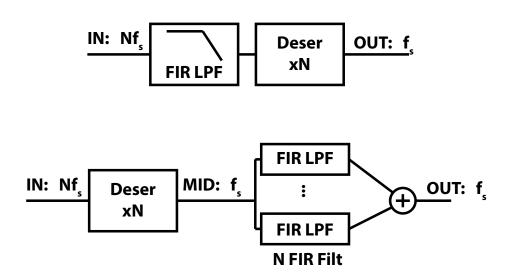

| 6.5  | Standard downsampling filter (top) and polyphase implementation (bottom),                                                                           |              |

|      | which reduces the clock rate for the entire design                                                                                                  | 101          |

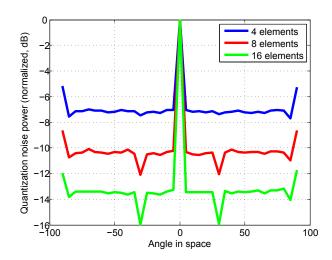

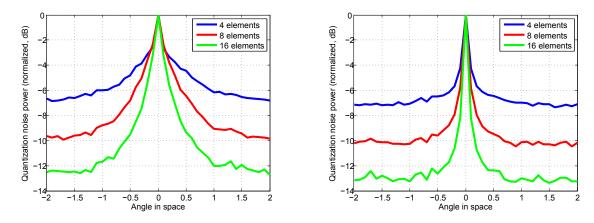

| 6.6  | Quantization noise versus line of sight angle for various array sizes                                                                               | 101          |

| 6.7  | Quantization noise in a near-broadside line-of-sight array, for a 5-bit and 7-bit DAC.                                                              | 102          |

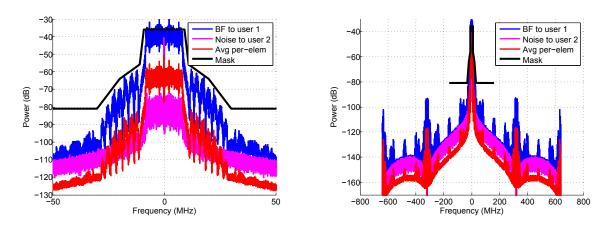

| 6.8  | Output spectrum of a 16-element array with two users in a 802.11n mask                                                                              | 103          |

| 6.9  | DSP path for massive MIMO SoC using 802.11n                                                                                                         | 103          |

| 6.10 | Per-element reciprocity calibration scheme consisting of measurement TX and                                                                         |              |

|      | loopback                                                                                                                                            | 105          |

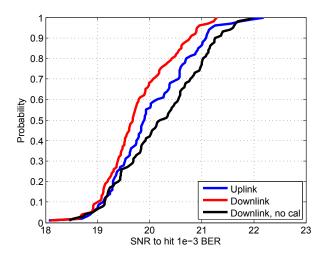

|      | Downlink performance with and without reciprocity calibration Link router for receive (uplink) direction — the incoming data is synchronized,       | 106          |

| G 12 | summed with the delayed output from the local DSP, and forwarded                                                                                    | $106 \\ 107$ |

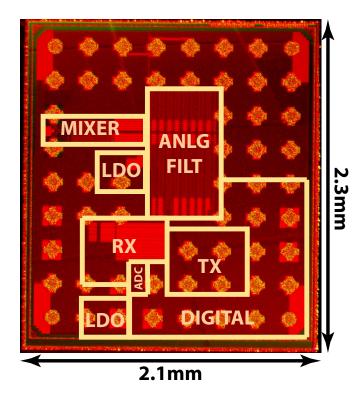

| 0.13 | Die piloto for test cirp                                                                                                                            | 107          |

| 7.1  | Link budgets for actual system uplink, along with hypothetical extensions to                                                                        |              |

|      | wider channels, longer range, and downlink scenarios                                                                                                | 109          |

| 7.2  | Modular array architecture for a massive mm-wave MIMO array                                                                                         | 110          |

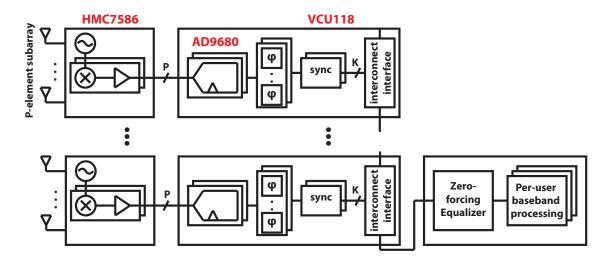

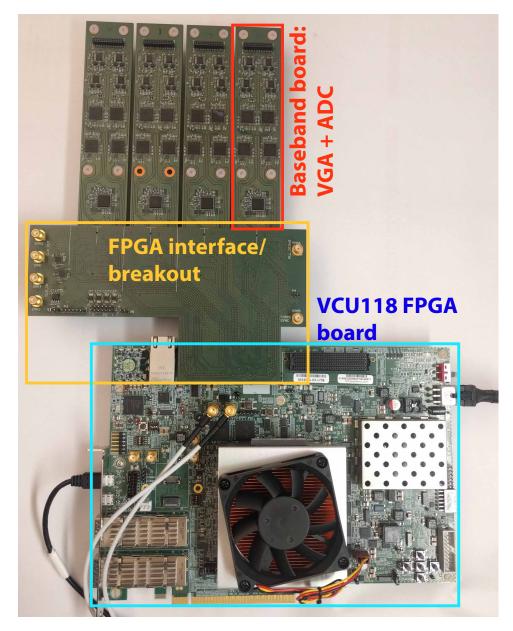

| 7.3  | Baseband path for a single 16-element subarray                                                                                                      | 112          |

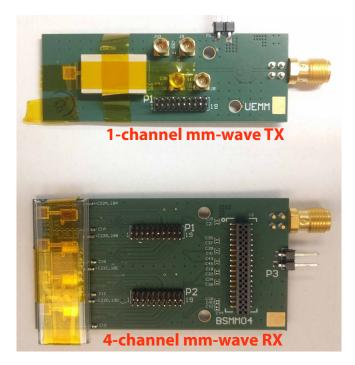

| 7.4  | RX and TX mm-wave front-end boards including on-board aperture-coupled                                                                              | 110          |

| 7 5  | patch antenna.                                                                                                                                      | 113          |

| 7.5  | User equipment for testing, including FPGA, DAC, clocking, power generation, and LO path                                                            | 114          |

| 7.6  | Signal processing chain for mm-wave massive MIMO link                                                                                               | 115          |

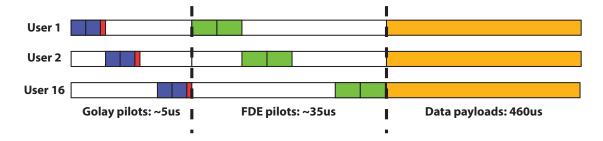

| 7.7  | Frame structure for mm-wave multi-user MIMO link                                                                                                    | 116          |

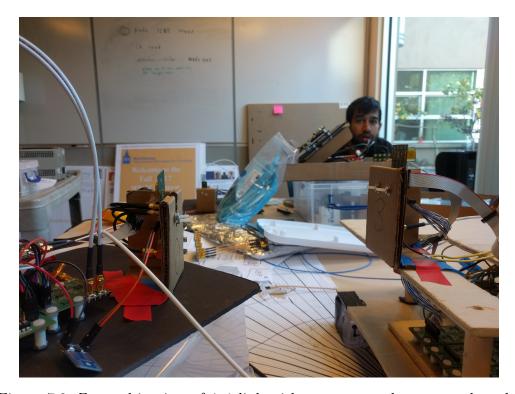

| 7.8  | Lab setup for 4x1 SIMO testing                                                                                                                      | 117          |

| 7.9  | Zoomed-in view of 4x1 link with antennas and mm-wave boards                                                                                         | 118          |

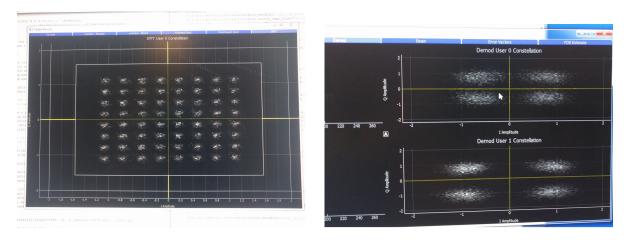

| 7.10 |                                                                                                                                                     |              |

|      | MIMO link                                                                                                                                           | 119          |

## List of Tables

### Acknowledgments

It is hard to communicate the depth of emotion and experience behind the acknowledgement section of a PhD dissertation. I find that as I have progressed in grad school, I keep finding more depth of meaning and perspective in the acknowledgement sections of theses I read. I think the acknowledgement section is the most significant and interesting part of a PhD dissertation, conveying the immensity of the task accomplished and offering a snapshot into the bizarre and unusual world of graduate school.

I would like to start by thanking my advisors, Bora Nikolic and Elad Alon. You guys were definitely the right advisors for me, both individually and together. Bora — I have learned so much from your big-picture thinking and broad grasp of the context of our work and our industry. Many times I have dismissed your predictions or advice and later realized that you were right all along. I also really appreciate your focus on big, ambitious, complex systems. When I started working for you, you asked me to look into "beamforming" — who would have known that that would launch a five year endeavor touching analog and digital circuits, signal processing, wireless communications, and so much more. I could not imagine working on any narrower scope. Elad — your deep understanding of all technical topics and lightning-fast intellectual reflexes have kept me on my toes through many a discussion with you. You always ask the right questions and slowly I have been (still) learning both how to give the right answers and more importantly, how to ask those questions myself. Your guidance has helped me find the gaps in my understanding and explanations, and pushed me to not settle for good enough but rather strive for perfection, even when I did it kicking and screaming.

I also owe a debt of gratitude to Tom Courtade and Ali Niknejad, who despite not being my advisors were always willing to take the time to discuss ideas, give me feedback, and point me in the right direction. I also want to thank Paul Wright for serving on my quals committee (with Tom) and David Aldous for serving on my dissertation committee. Finally, thanks to Rikky Muller, for your advice and discussions on life after grad school and for hiring me as a TA.

A huge part of this dissertation was done in collaboration with Ozzy LaCaille. Ozzy, you have been my friend, mentor, and inspiration throughout grad school, not to mention travel companion, fellow monkey trainer, and (worryingly) doppelganger. I have worked with you for over three years straight but I am still dumbfounded by your unbounded passion for the work you do, your herculean work ethic, and your deep insights. You'll make a tremendous professor someday soon.

The best part of grad school by far is the friends you make. Sameet — I couldn't imagine grad school without you. I have enjoyed all our time together, from late-night juice taste tests to heated arguments to constant startup ideas. Luke — you are an incredibly loyal friend and a truly strange person. Your passion for the things you care about is really inspiring.

Emily and Keertana - who are always somehow mentioned in the same sentence - thank you for your companionship, for throwing crazy parties and fun picnics, for cheering me up when I am depressed, for long pointless debates (Emily) and always being ready to get lunch (Keertana). John, thank you for being my friend outside of work: skipper, backpacking buddy, DIY guru. You have way too many hobbies for me to hope to emulate. Bonjern and Nathan, thanks for thousands of lunches at up to 10 different places, and ensuing inane discussions. Krishna, thanks for always taking the time to chat when we bump into each other in the kitchen. Lorenzo and Matteo, thank you for strengthening my tie with the motherland.

I want to thank many others at BWRC for your friendship and technical discussions: Marko for commiserating about project management and system design; Ben and Stevo for serving as my digital tapeout consultants; Paul and Chris Yarp for discussing comm systems; Kosta, Amy, Eric, Zhongkai, and Pengpeng for long ewallpaper tapeout hours; as well as Pavan, Katerina, Matthew, Nandish, Sidney, and Andrew. Thanks also to all the other members of the ComIC group — Amanda, Angie, Brian, Charles, Jaehwa, Luis, Matt, Milos, Mira, Nick, Pi-Feng, Rachel, Sharon, and Vladimir — and the EEIS group — Ali, Jaeduk, Kristel, Nick, and Seobin.

The staff at BWRC secretly keep the place from turning into lord of the flies, so a deep thank you to Candy and Yessica for always being cheerful and getting the engineers to have fun, James for always going above and beyond, Fred for keeping the lab running, and the rest of the team: Amber, Brian, Bira, Erin, Leslie, Melissa, Olivia, and Sarah.

I have a deep gratitude to Greg Wright and Ajith Amerasekara for your mentorship and friendship. Greg, you are a bottomless fount of wireless knowledge, business trends, and random and hilarious stories. Thanks for all your guidance and advice, coffees and beers drunk, and for hosting me at Bell Labs many years ago. Ajith, thank you for your mentorship on career paths, industry trends, and always seeing the bigger picture. You spent countless hours helping us learn how to think about business and how to understand the context of our research, and then had the gall to treat us to dinner. I have really enjoyed your friendship.

Thank you to industry partners and internship mentors — Farhana Sheikh, Chris Hull, Chintan Thakkar, and Bryan Casper of Intel and Brucek Khailany, Rangha Venkatesan, and Bill Dally of Nvidia — for technical discussion, feedback, and guidance as well as great intern experiences.

Friends outside BWRC have helped me stay slightly in touch with the world. Arjun, thanks for countless nights of video games, grad school horror stories, junk food and unreasonably large pancakes, and excessive drinking of CENSORED. Abi, we've been brothers for ages so I guess you had to at least half-heartedly pretend to care about my research. Rachel, your enthusiasm and optimism is infectious. Maggie, thanks for the constant reminder that I could have been a software engineer. Susan, thanks for your encouragement and for teaching us to backpack.

Almost finally, thanks to my parents, little brothers, and grandparents. Dad, you've been preparing me for this since I was a tiny kid reading your papers and grants. Mom, your life's passion has been your kids and at least two of them turned out fine. Ale and Lorenzo, you look up to me even when it's not reasonable. Since I've been away you have grown into men and I see a lot of myself in you guys. Nonno Enzo and Nonna Maria Teresa, thanks for always caring about what I work on even though I can't explain it to you, least of all

in Italian. Finally, Nonno Tonino — you are stubborn as a mule and frequently a pain in the ass, but I guess that's where my dad and I get that from. Without you we wouldn't be where we are today, and we are all more similar than you'd think.

Finally finally: I cannot express my gratitude to my girlfriend Jiwon. You dealt with me for three years from across the country and subjected yourself to another year and a half up close and personal. Sometimes I try to imagine what grad school would have been like without you by my side — I simply draw a blank. You believed in me when I didn't believe in myself, kept me going when I didn't want to, made me smile when I needed it, and stood out as a constant bright spot in my life. It hasn't always been smooth sailing but I could not have done it without you. Trust me, I'm a doctor.

## Chapter 1

## Introduction

## 1.1 Motivation: Large Arrays are Needed to Extend Network Capacity

Recent years have witnessed a dramatic increase in network traffic [1], as rapidly proliferating mobile devices drive increased consumption of media-rich services such as mobile video. Current projections anticipate that mobile traffic will grow seven-fold in the five years from 2016-2021. By 2021 it is anticipated that almost two-thirds of global IP traffic will originate over a wireless connection, with 20% coming over a cellular network.

Mobile data consumption both drives and results from advances in communications technologies, which have made it possible to deliver up to hundreds of megabits per second over wireless connections using standards such as 802.11 wireless LAN (WLAN) [2] or LTE [3]. On the back of this capability, the smartphone has become the fastest growing consumer electronic device in human history [4]. The spread of smartphones ensures that everyone in the world has a high-bandwidth device in their back pocket and demands to use it on the go for activities such as mobile gaming, video streaming, and live broadcasts. Today video accounts for almost 75% of all consumer IP traffic; this will increase to 82% by 2021. It is further expected that new device classes, such as augmented reality (AR) or virtual reality (VR) glasses, along with new applications such as connected vehicles and robots, will drive even more traffic growth in the next five years [5]. In fact, AR/VR traffic is expected to grow 20-fold in the next five years.

Even as smartphone traffic consumption has been growing with compound annual growth rate (CAGR) in excess of 50% [1], the capabilities of wireless communication techniques have approached their theoretical limits. Since Shannon proposed his theory of information and communication in 1948 [6], innovations such as low-density parity check (LDPC) codes [7] and orthogonal frequency-division multiplexing (OFDM) modulation [8, 9] have brought the spectral efficiency of wireless standards close to the theoretical Shannon bound. 802.11 and LTE today are within a fraction of a dB away from the Shannon limit [10], meaning that these standards make near-optimal use of time and frequency resources.

Though this is a great achievement, it means that there are no simple solutions to address existing and emerging traffic demands. Previous generations of cellular networks increased datarates in one of two ways. First, wider channels were used (from 200kHz in 2G GSM to 5MHz in 3G WCDMA and 20MHz in 4G LTE to 60 or even 100MHz using carrier aggregation). Second, the infrastructure deployments have been dramatically densified [11]. Today both of those techniques are running into roadblocks. Existing spectrum bands below 6GHz are nearly all allocated. This spectrum scarcity is such that the small remaining chunks of spectrum are auctioned for tens of billions of dollars [12], which is almost an order of magnitude higher than the capital cost of the network equipment itself [13]. In parallel, network densification has run into a cost and complexity bottleneck. Ubiquitous infrastructure deployments are not economically feasible given the high cost of infrastructure equipment today as well as the cost and time of acquiring backhaul connections and zoning/siting permits. Additionally, densification results in interference-limited networks where the achievable performance is limited by the large number of base-stations in close proximity [11]. Mitigating this requires coordination and management of radio resources to deal with interference between densely-deployed and irregularly-spaced base-stations.

Based on this discussion, we can identify three key requirements for next-generation cellular networks. First, physical-layer technologies must make more efficient use of existing spectrum. Second, future base stations must be equipped with techniques to manage and mitigate interference in dense deployments. Finally, infrastructure solutions must be as cheap as possible so that they may be ubiquitously deployed.

It will fall on the fifth generation (5G) of mobile networks to begin addressing some of these challenges. The wireless industry expects that 5G standards will introduce new techniques which can increase the capacity of wireless networks [14] and support emerging data-hungry applications and device classes. Addressing today's challenges and tomorrow's needs will require significant innovation at all layers of the network hierarchy. At the PHY layer, the only available solutions are to move to new high-frequency spectrum, where wide channel bandwidths are available, and to introduce complex spatial processing which is able to spatially filter network interference. Both of these capabilities are implemented using large antenna arrays, meaning that cost- and power-efficient array design is the cornerstone technology upon which future network generations will be built.

## 1.1.1 Spatial Processing

Spatial processing was the focus of extensive research and development in the 1990s [15–19]. This effort led to the invention of space-time codes [20–22] and finally the discovery of the multi-channel capacity formula [23, 24]. In essence, it was discovered that space presents an additional degree of freedom on top of time and frequency which wireless communications systems can exploit. More specifically, if a wireless link is equipped with multiple antennas at both the transmitter and receiver and if the propagation environment is sufficiently rich, then the capacity of this channel scales linearly with the minimum of the number of trans-

mit or receive antennas. This technique is called multiple-input, multiple-output (MIMO) communications.

MIMO techniques present an engineering approach to network capacity. Rather than being limited by the frequency allocation, more capacity can be added to a network simply by deploying more antennas and transceivers. Recognizing the potential of this approach, demonstration systems were quickly built [25, 26] and wireless standards adopted MIMO techniques. Single-user (SU) MIMO was the first technique proposed, where multiple spatial streams are sent to a single user which is equipped with multiple transmit/receive antennas [25, 27]. In practice, real propagation environments can only support limited number of streams to an SU-MIMO device. Multi-user (MU) MIMO is an extention of the MIMO technique where multiple spatial streams are sent to a number of spatially distinct users [28]. The MU channel is significantly more decorrelated since the user devices are fundamentally spatially separated. As such, MU-MIMO can reuse spectrum to communicate simultaneously with many users in the same frequency band, by exploiting those users' separation in space.

MIMO techniques employ spatial processing to manage in-network interference. A related concern is external interference sources which degrade the link quality and performance. These interferers may come from adjacent cells in a cellular network, different operators which occupy separate frequency bands, communication systems on different standards, or even non-communication devices such as radars and microwaves. In the absence of any knowledge about these interferers, spatial filtering is the only known technique which can address the problem of general interferers. Spatial filtering is a form of spatial processing which filters out signals using their spatial characteristics or direction of arrival [29]. A spatial filter could identify external interferers by their spatial signature and reject them.

In summary, spatial processing provides two key benefits. First, spatial multiplexing can be used to send multiple data streams simultaneously over the same frequency band, providing a multiplicative capacity gain. Second, spatial filtering can be used to reject arbitrary interference in the environment. These capabilities make aggressive spatial processing an attractive candidate for 5G networks. One could envision deploying infrastructure nodes equipped with a large number of antennas, serving dozens of simultaneous users in the same band while rejecting interference from nearby cell sites.

In fact, this vision has strong theoretical backing. In 2010, Marzetta proposed the concept of "massive MIMO", where a base station with a large number of elements serves a much smaller number of users using MU-MIMO [30]. Marzetta's theoretical results show that as the number of base-station antennas grows large, simple spatial signal processing techniques can eliminate both intra- and inter-cell interference. Intra-cell interference is explicitly managed by the cell itself using its spatial resolution. Inter-cell interference disappears because, in the limit of very large number of antennas, all links use vanishingly thin pencil beams so the probability of crossing beams goes to zero. In other words, the massive MIMO paradigm — deploying large antenna arrays — provides a scalable approach to simultaneously increase network capacity (by a large factor!) and mitigate network-level interference.

Massive MIMO will be exploited to enhance the value of traditional < 6GHz cellular bands. Today, high-order MIMO is being introduced into the latest versions of the LTE

standards [31–33] and infrastructure vendors are commercializing systems using 32-96 antennas [34–36], which provide up to 3-5x capacity improvements over existing 4G networks. However a key limitation of < 6GHz massive MIMO is the physical size and weight of the antenna array. Because the antenna size is related to the wavelength, antenna arrays at < 6GHz are very bulky — up to 3m on a side with a weight up to 40kg. The weight is mostly contributed by power supplies and cooling structures, so addressing power consumption via optimized electronics may help mitigate that. However, the physical antenna size is constrainted by the available site size on standard masts. Unless base-station sites are substantially modified to support huge antenna sizes, it will be impossible to go beyond 96 or certainly 128 antennas in < 6GHz systems, which means that we must look elsewhere for further network enhancements.

### 1.1.2 Moving to higher frequencies

At the same time, to address the congestion in exisiting low-frequency network deployments, regulatory bodies around the world are opening up higher-frequency mm-wave spectrum, including at 24, 28, 39, 60, and 72 GHz [37, 38]. These mm-wave bands provide much higher bandwidths than existing spectrum which can be used to dramatically increase network capacity. Moreover, the much smaller wavelength at mm-wave frequencies provides the opportunity to deploy arrays with thousands of elements in a very small form factor.

Traditionally, the challenge of operating at high frequencies is the higher propagation loss. This has either limited mm-wave links to short distances, or required the use of large mechanically-steered dish antennas with very high directivity. Recent measurement campaigns in both 28 and 72 GHz bands reveal that with modern technologies, communcation over a range around 200-500m is feasible [39–42]. The proposed systems use phased arrays to synthesize a directional transmission/reception which compensates for the propagation loss. Accordingly, a numer of groups have shown 16- or 32-element arrays with a single-beam range of 100-300m [43–46].

These capabilities will underpin the first deployments of mm-wave spectrum for fixed-access to the home, deploying commercial services at high frequency for the first time [47]. Wireless fixed access services exploit the wide mm-wave channel bandwidths to deliver fiber-quality gigabit home or business internet without the costly and time-consuming fiber deployments.

Looking forward, the true promise of mm-wave lies in deploying a ubiquitous fixed + mobile access network which provides gigabit internet on-the-go, everywhere. 1000-element mm-wave arrays can be realized in a form factor comparable to a WiFi router today. These tiny infrastructure nodes can be deployed anywhere — on lamp-posts, buildings, and bus shelters — providing a super-dense wireless coverage. The huge number of antennas provide super-directional pencil beams which can overcome shadowing, glass or concrete obstructions, and outdoor-to-indoor operation. Spatial processing algorithms exploit the 1000 antennas to serve dozens of clients simultaneously, anywhere from homes to smartphones to vehicles,

while cancelling interference arising from the dense deployments. All of this is complemented by network intelligence which coordinates services across a wide geographic range.

In order to achieve this vision, it is necessary to develop techniques for implementing 1000-element arrays in a cost- and power-efficient manner. The technologies underlying today's 16- or 32-element, single-beam arrays will not scale to the envisioned scenario. As such, developing scalable array design techniques will be a critical step toward tomorrow's glorious wireless future.

## 1.2 Prior work in array design

In light of the above discussion, it is unsurprising that the design and implementation of antenna arrays is a focus of research effort in academia and industry.

Low-order SU- and MU-MIMO have been introduced in wireless standards over the past decade, including 802.11n/ac and LTE [2, 3]. The recent WLAN standard, 802.11ac, can support up to 8 spatial streams to a single device or 4 simultaneous users through downlink-only MU-MIMO. The forthcoming 802.11ax standard will additionally introduce uplink MU-MIMO capabilities. LTE Advanced supports similar levels of spatial multiplexing.

Today's cellular MIMO radios in the handset are implemented using an integrated RF transceiver chip along with per-antenna front-end electronics (filters, switches, and power amplifiers) and a baseband processor [48]. WLAN radios are more integrated — it is common for radio and baseband processing to be integrated on the same die, and the number of external components is smaller [49]. In contrast, due to their more stringent specifications, LTE base-stations use a larger number of front-end components, particularly power amplifiers (PAs) and their associated predistortion capabilities [50]. Additionally, celllular base-stations frequently separate the radio and baseband processing into physically distinct boxes with an electrical or optical interconnect between them. Finally, while baseband processors in handsets (for both LTE and WiFi) are implemented on dedicated chips, base-stations primarly use more generic hardware, realized as an application-specific integrated circuit (ASIC) which integrates digital signal processor (DSP) cores, CPUs, and some custom accelerators.

Several university and industry research groups have built massive MIMO testbeds in the < 6GHz bands, using 64-128 antennas to serve up to 20 simultaneous users [51–59]. These testbeds have shown successful over-the-air measurements and validated many of the theoretical predictions. However, from a hardware design perspective, they reveal the limitations of scaling up existing radio design paradigms from 8 to 128 antennas. Almost all of these testbeds adopt a fully centralized architecture, where all processing, synchronization, and calibration is performed globally on a set of powerful processors. The radios and front-ends are not that challenging from this perspective — cost and power can be managed by tailoring the radio design to the system specifications. Instead the bulk of the cost, power, and complexity of these testbeds arise from the data aggregation and array processing. Commercial systems entering the market today [35, 36] can brute-force this complexity by using

complex baseband ASICs with custom accelerators for array tasks. However, architectural innovations toward more distributed operation could significantly reduce the power and cost of this solution.

At mm-wave frequencies, over the past decade a number of research groups have shown 16- or 32-element arrays monolithically integrated on a single die [43, 44, 46, 60–65]. Because of the small wavelength and small circuit area, it is possible to fit up to 32 elements (or even more!) on a single chip. These arrays use analog beamforming techniques to form a single transmit/receive beam. These demonstrations were enabled by innovations surrounding the beamforming circuits and the LO distribution to all the front-end elements.

There is no clear way to scale today's 32-element mm-wave arrays to hundreds or even 1000 elements. In particular, such large arrays would necessarily be implemented using a number of front-end subarrays which are fused to form the overall array. These subarray chips have to be interconnected with appropriate data aggregation, synchronization, and signal processing techniques. Moreover, the capability to form dozens of simultaneous beams does not exist in today's mm-wave array solutions.

In summary, the main difference between conventional multi-antenna technology and its 5G counterpart is that future antenna arrays will require massive hardware duplication. As such, the radios, signal processing, etc fundamentally cannot all be implemented on the same chip. Existing array design techniques break down in this regime; the cost, complexity, and power of global synchronization, data aggregation, and processing tasks makes the resulting systems impractical to build and deploy.

## 1.3 Thesis scope and outline

Motivated by this background, this thesis considers system-level techniques to manage the cost and design complexity of very large arrays. The key role of an array can be thought of as taking a large number of antennas/front-ends and "making them play well together". Accordingly, the main objective of this thesis is to develop techniques for efficiently and cheaply interconnecting the radio front ends in order to form an antenna array with very large spatial aperture.

In keeping with the discussion above, the main areas of focus are data aggregation, signal processing, and synchronization. Chapter 2 provides a brief overview of existing spatial signal processing techniques and presents simulation results showing how these techniques perfom in real channel models. Building off of this background, Chapter 3 proposes a distributed array architecture designed around the spatial signal processing task. Additionally, Chapter 3 presents innovative signal processing techniques which may be used in some array implementations.

Chapters 4 and 5 then move on the synchronization tasks. Chapter 4 analyzes the carrier synchronization across the array and presents innovations and design guidelines into the carrier generation architecture as well as the specifications for circuit components within

this subsystem. Chapter 5 studies the baseband synchronization of the array and proposes techniques to accomplish this in a distributed fashion.

Finally, Chapters 6 and 7 describe hardware implementations of these ideas. Chapter 6 presents a highly-integrated system-on-a-chip in 65nm CMOS operating < 6 GHz, while Chapter 7 describes a 72GHz MU-MIMO array implemented using off-the-shelf radios, data converters, and FPGAs.

## Chapter 2

## **Array Processing**

Antenna arrays have been used for decades for their ability to resolve the spatial characteristics of the environment. For example, radars can precisely track multiple targets in space while filtering out the impact of ground reflections or other clutter. Similarly, spatially selective communication systems can send multiple data streams in the same frequency channel by exploiting different propagation paths through the environment.

The input (output) of a transmit (receive) antenna array system is one or more signals of interest along with each signal's desired spatial pattern. The key components of the array are the actual antennas themselves (and any front-end electronics as required by the application) along with a signal processing engine that converts between the signals of interest and the transmit or receive signals at each antenna. For example in a phased-array radar, a large network of phase shifters is used to transmit or receive in a specific direction.

There are a large number of spatial signal processing algorithms, ranging from phase shifts in phased arrays to maximum likelihood detection in communication systems. This chapter briefly overviews existing spatial processing techniques and concludes with a performance study that compares the performance of various algorithms in real channels.

## 2.1 Phased Arrays

Phased arrays were initially used in World War II [66] but received sustained attention starting in the late 1950s and early 1960s [67] as the next-generation of military radars [68]. Radars require the use of directional radiation to precisely localize targets in space. Early radars used directional antennas, such as parabolic dishes, which were mechanically steered to find and track their targets [69]. However, mechanically steered antennas suffer from slow steering, inability to track multiple targets, and mechanical stress and failures. This motivated the search for more flexible and reliable radar systems.

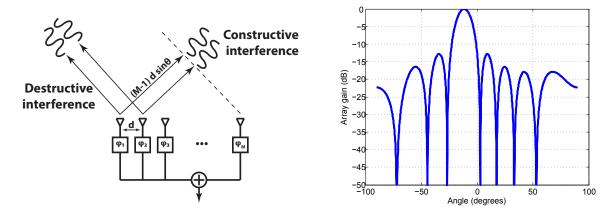

An antenna array is a virtual directional antenna which is electronically steerable. As shown in Figure 2.1(a), phased arrays operate by applying a per-element phase shift to each antenna's signal. The phase shift is a function of the desired look direction, and ensures that

Figure 2.1: Phased array principle of operation, and example beampattern.

signals in that direction add constructively, while signals from all other directions add destructively. In this way, the look direction of the array can be steered simply by changing the phase shifts, which requires no mechanical components and can occur on the time constant of the phase shifter setting. Additionally, multiple beams can be formed simultaneously by implementing parallel phase shifter networks, one for each desired beam. This operation is referred to as "beamforming".

An example of an array's spatial response is shown in Figure 2.1(b), showing the spatial processing gain as a function of direction arrival or departure. This "array pattern" is described in terms of three key parameters. The look direction refers to the direction in which the array is pointed. The main lobe width measures the angular width of the array response in that direction. Finally, the sidelobe level describes the array gain at angles other than the look direction of the array.

The array pattern can be expressed as a function of the beamforming coefficients:

$$G(\theta, \phi) = \sum_{i=0}^{M-1} w_i e^{j\mathbf{k}\cdot\mathbf{d}_i}$$

(2.1)

where k is the wave-vector of the desired look direction and  $d_i$  is the position of a given element in the array. For a planar 2D array this simplifies to:

$$G(\theta, \phi) = \sum_{i=0}^{M-1} w_i e^{jk(x_i \sin \theta \cos \phi + y_i \sin \theta \sin \phi)}$$

(2.2)

where  $\theta$  and  $\phi$  are the azimuth and elevation angles of arrival relative to the array's normal vector. To point in direction  $(\theta, \phi)$ , the phase at position  $(x_i, y_i)$  should be  $-k(x_i \sin \theta \cos \phi + y_i \sin \theta \sin \phi)$ .

This equation describes a discrete Fourier transform (DFT) of the beamforming coefficients, where the original variable is position d and the transform variable is wave-vector k.

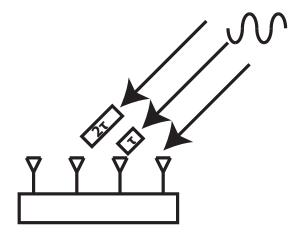

Figure 2.2: True time delay effects in phased arrays.

This gives two key insights. First, if  $|w_i| = 1$  (a pure phase shift), then the array pattern is a shifted sinc function (defined as  $\sin(x)/x$ ). Second, the sidelobes and null positions can be controlled by applying non-uniform amplitudes to  $w_i$ . For example, standard DFT windows such as Kaiser or Hamming [70] could be applied to achieve a certain array pattern.