# **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Multi-Mode Sub-Nyquist Rate D/A Converter for TV Band Cognitive Radio

#### **Permalink**

https://escholarship.org/uc/item/6z89d8vg

#### **Author**

Chen, Yuan-Shih

## **Publication Date**

2012

Peer reviewed|Thesis/dissertation

## Multi-Mode Sub-Nyquist Rate D/A Converter for TV Band Cognitive Radio

By

## Yuan-Shih Chen

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division of the University of California, Berkeley

Committee in charge:

Professor Jan M. Rabaey, Chair

Professor Elad Alon

Professor Paul K. Wright

Fall 2012

# Multi-Mode Sub-Nyquist Rate $\mathrm{D/A}$ Converter for TV Band Cognitive Radio

Copyright © 2012 by Yuan-Shih Chen

#### Abstract

Multi-Mode Sub-Nyquist Rate D/A Converter for TV Band Cognitive Radio

by

#### Yuan-Shih Chen

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Jan M. Rabaey, Chair

Advances in high-speed DAC implemented in deeply scaled-CMOS processes open up the possibility of direct IF and RF waveform synthesis in a next-generation digitized transmitter architecture. A state of the art CMOS current-steering DAC is capable of providing wide bandwidth and high dynamic range for direct RF waveform generation. This enables the mostly-digital implementation of a direct waveform synthesis transmitter for TV band cognitive radio. RF waveforms with various modulation schemes can be synthesized in the digital domain and directly converted by a high-speed DAC. The transmission characteristics can be dynamically adapted to time-varying spectral environment. This transmitter architecture brings the benefits of reconfigurability and frequency agility. However, conventional waveform synthesis requires a >2GS/s DAC to fulfill the Nyquist requirement for covering the whole TV band ( $54 \sim 862$ MHz). Nevertheless, an alternative method is to convert the signals at a sampling rate below the Nyquist requirement and extract the image spectrum in higher Nyquist zones by bandpass filters.

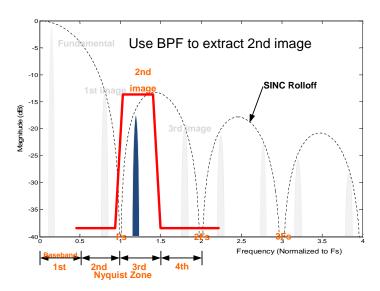

This work demonstrates a proof-of-concept design of sub-Nyquist rate conversion and wideband direct synthesis using image spectrum. By utilizing the proposed multi-mode reconstruction, the DAC can shape the spectral envelope for enhancing the image spectrum located in the target channels. The desired transmission waveforms can be extracted from the second or third Nyquist zone by a bandpass filter. A circuit prototype demonstrating the proposed concept has been designed, fabricated, and measured in a general-purpose 65nm CMOS process.

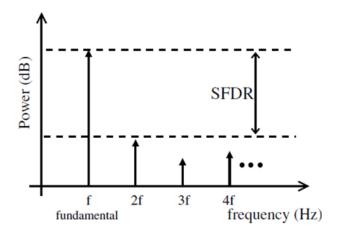

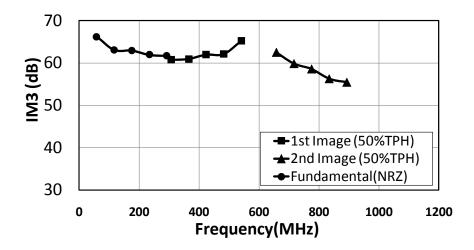

This work presents the implementation of a 600MS/s 10-bit multi-mode sub-Nyquist rate DAC that enables wideband direct waveform synthesis for TV band cognitive radio transmitters. Measurement results show SFDR >55dB across the first three Nyquist zones

and a low power consumption of 30mW. The IM3 is < -60dBc in the first and second Nyquist zones and < -55dBc in the third Nyquist zone.

To my parents, my wife, and my son

# Contents

| Li | st of | Figures                                                           | iv  |

|----|-------|-------------------------------------------------------------------|-----|

| Li | st of | Tables                                                            | vii |

| 1  | Intr  | roduction                                                         | 1   |

|    | 1.1   | TV Band Cognitive Radio - "WiFi on Steroids"                      | 2   |

|    | 1.2   | Related Work                                                      | 5   |

|    | 1.3   | Thesis Organization                                               | 8   |

| 2  | Mos   | stly Digital Transmitter for TV Band Cognitive Radio              | 9   |

|    | 2.1   | White Spaces in TV Bands                                          | 10  |

|    | 2.2   | TV Band Cognitive Radio Standards                                 | 16  |

|    |       | 2.2.1 IEEE 802.22                                                 | 16  |

|    |       | 2.2.2 ECMA-392                                                    | 17  |

|    |       | 2.2.3 IEEE 802.11af - "White-Fi"                                  | 19  |

|    | 2.3   | Direct Waveform Synthesis Transmitter for TV band Cognitive Radio | 21  |

|    |       | 2.3.1 Transmitter Architecture                                    | 22  |

|    | 2.4   | Design Challenges on Digital/Analog Boundary                      | 26  |

| 3  | Mu    | lti-Mode Sub-Nyquist Rate Digital-to-Analog Conversion            | 30  |

|    | 3.1   | Analog Signal Reconstruction                                      | 30  |

|    |       | 3.1.1 Non-Return-to-Zero                                          | 30  |

|    |       | 3.1.2 Return-to-Zero                                              | 33  |

|    | 3.2   | Proposed Two-Phase Holding                                        | 35  |

|    | 3.3   | Variable Duty-Cycled Two-Phase Holding                            | 36  |

|    | 3.4   | Multi-mode Sub-Nyquist Rate Conversion                            | 40  |

|    | 3.5   | Implementation Considerations and Issues                          | 40  |

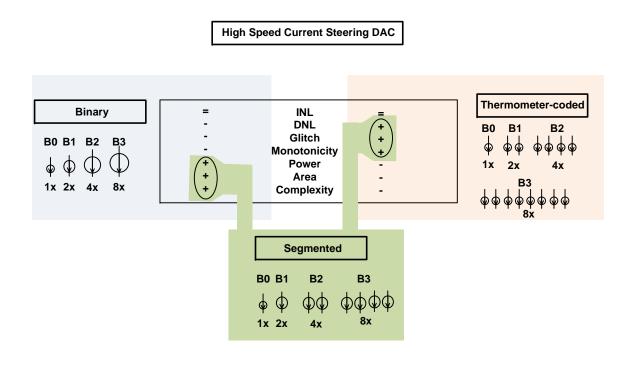

|    |       | 3.5.1  | DAC Architecture                                  | 41 |

|----|-------|--------|---------------------------------------------------|----|

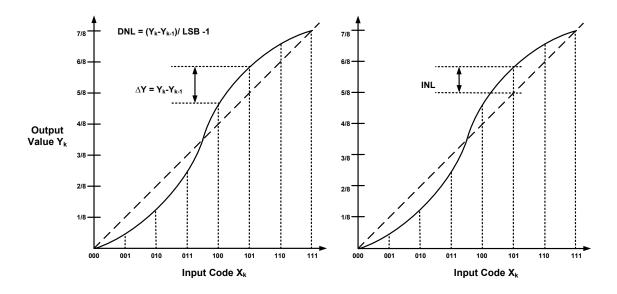

|    |       | 3.5.2  | Static Linearity                                  | 42 |

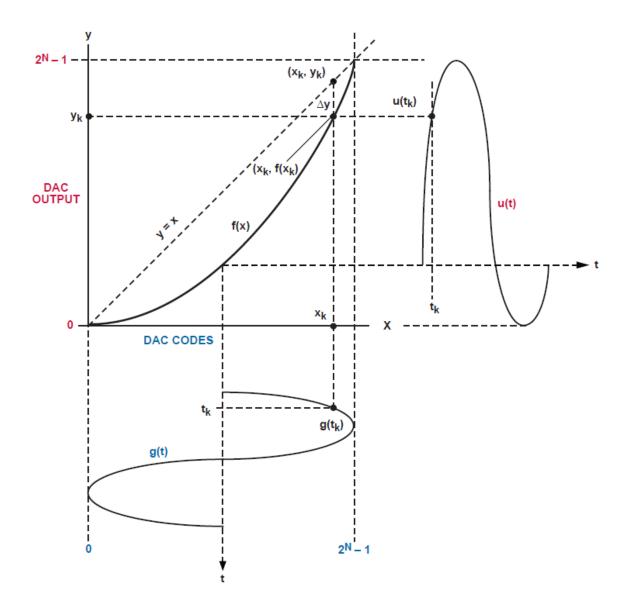

|    |       | 3.5.3  | Distortion                                        | 44 |

|    |       | 3.5.4  | Timing Accuracy                                   | 48 |

|    |       | 3.5.5  | Speed and Settling Time                           | 50 |

|    |       | 3.5.6  | Power                                             | 50 |

|    |       | 3.5.7  | Summary of Specifications                         | 51 |

| 4  | Exp   | erime  | ntal Prototype                                    | 53 |

|    | 4.1   | Circui | t Design                                          | 53 |

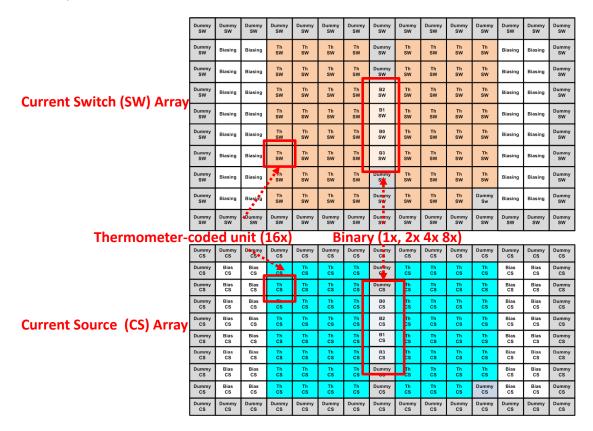

|    |       | 4.1.1  | DAC Architecture and Segmentation                 | 53 |

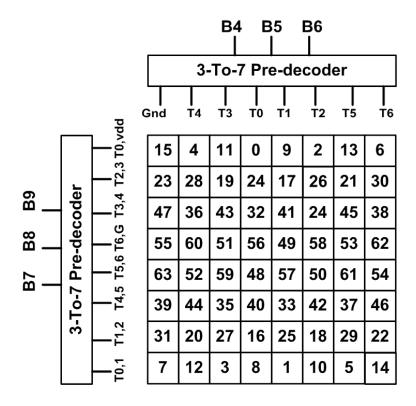

|    |       | 4.1.2  | Sizing and Matching of Current Source Array       | 54 |

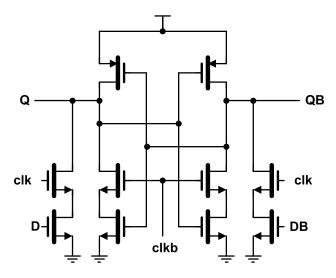

|    |       | 4.1.3  | Switch Cells                                      | 58 |

|    |       | 4.1.4  | High-Speed Thermometer Decoder and Latches        | 58 |

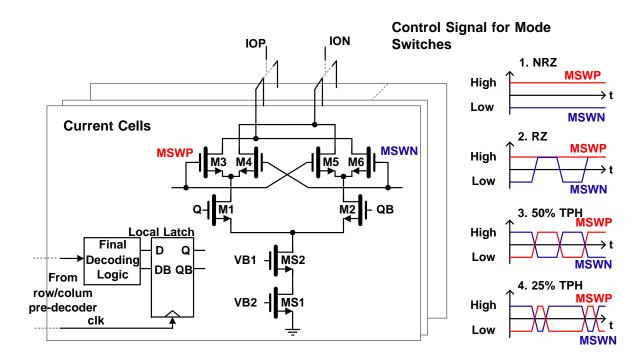

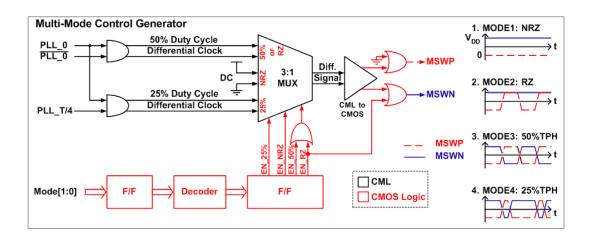

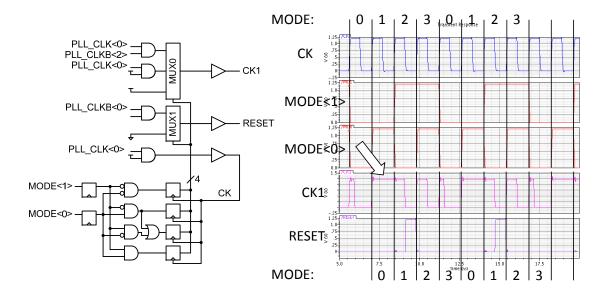

|    |       | 4.1.5  | Multi-Mode Control and Variable Duty-Cycled Clock | 61 |

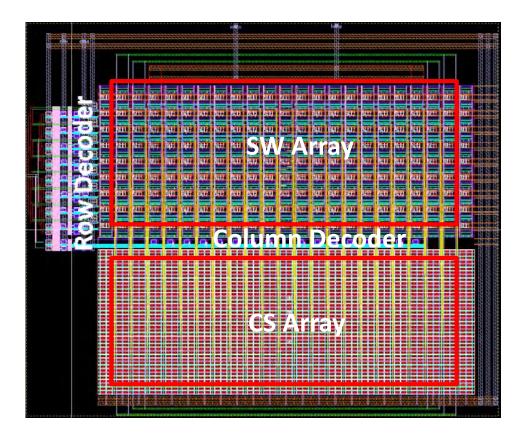

|    |       | 4.1.6  | Floorplan and Layout                              | 61 |

|    |       | 4.1.7  | Peripheral and Bias Circuitry                     | 65 |

|    | 4.2   | Test-C | Chip Prototype                                    | 66 |

|    | 4.3   | Measu  | rement Results                                    | 67 |

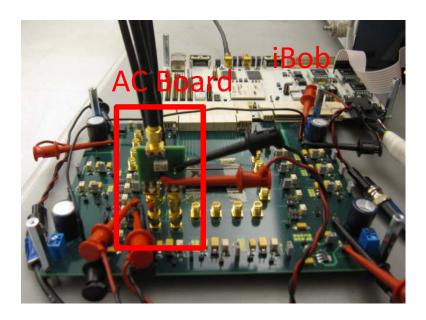

|    |       | 4.3.1  | Measurement Setup                                 | 67 |

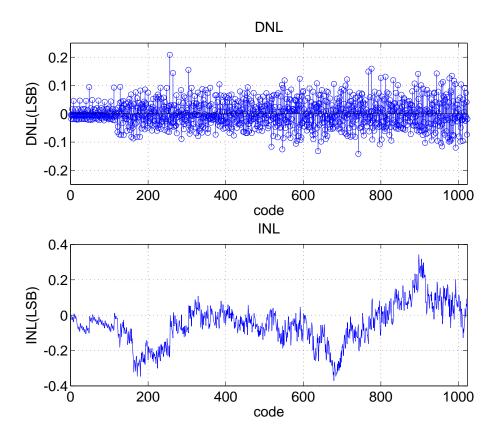

|    |       | 4.3.2  | DC Linearity Measurements                         | 69 |

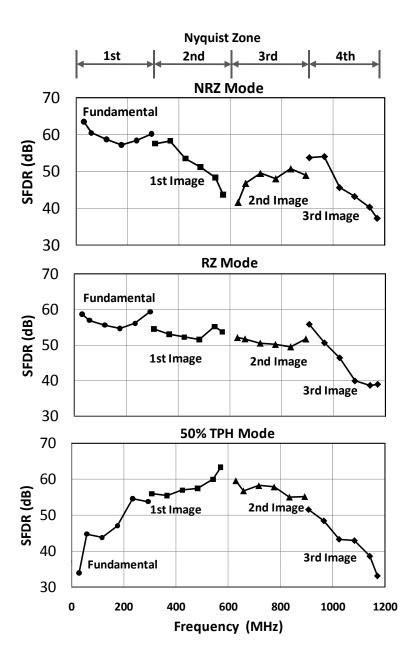

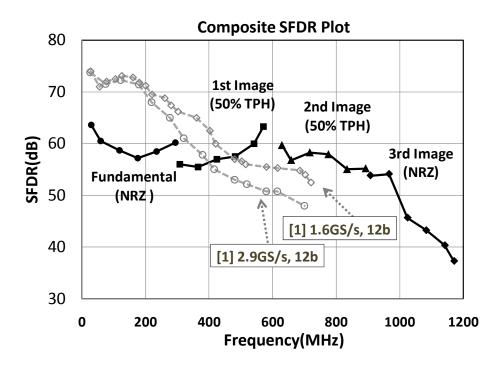

|    |       | 4.3.3  | AC Linearity Measurements                         | 70 |

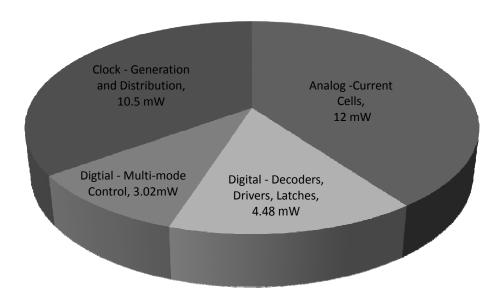

|    |       | 4.3.4  | Power Consumption                                 | 76 |

|    |       | 4.3.5  | Comparative Analysis                              | 77 |

| 5  | Con   | clusio | n                                                 | 82 |

|    | 5.1   | Summ   | nary                                              | 82 |

|    | 5.2   | Sugges | stions for Future Work                            | 83 |

| Bi | bliog | graphy |                                                   | 85 |

| A  | App   | oendix | A: TV Band White Spaces                           | 91 |

# List of Figures

| 1.1  | Spectrum utilization of 30MHz $\sim$ 3GHz in a 24-hour period   | 1  |

|------|-----------------------------------------------------------------|----|

| 1.2  | TV band white spaces                                            | 3  |

| 1.3  | Heterogeneous coexistence of TV band radios                     | 5  |

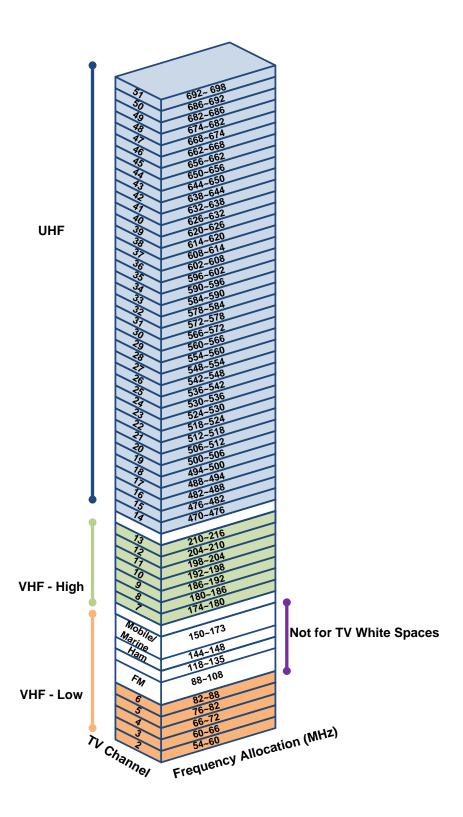

| 2.1  | Overview of TV Channels in US                                   | 11 |

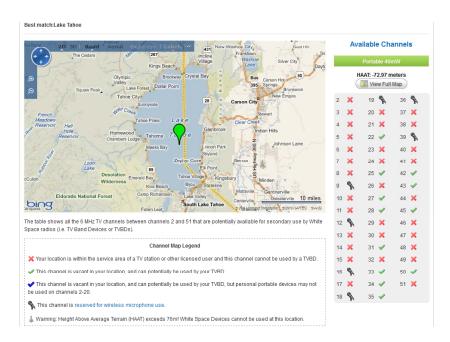

| 2.2  | Available TV White Spaces for Portable Devices in Lake Tahoe    | 13 |

| 2.3  | Available TV White Spaces for Fixed Devices in Lake Tahoe       | 14 |

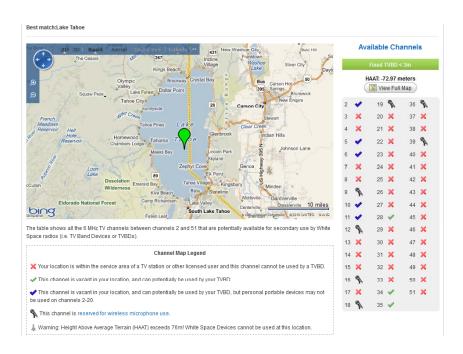

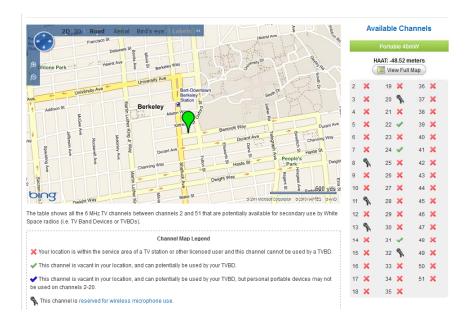

| 2.4  | Available TV White Spaces for Portable Devices in Berkeley      | 14 |

| 2.5  | Overview of EMCA 392                                            | 18 |

| 2.6  | Example Applications of EMCA 392                                | 19 |

| 2.7  | TV white Spaces Usage in 802.11af                               | 20 |

| 2.8  | Conventional transmitter architecture                           | 22 |

| 2.9  | Synergy of software-defined radio and cognitive radio           | 23 |

| 2.10 | SDR-type transmitter architecture                               | 24 |

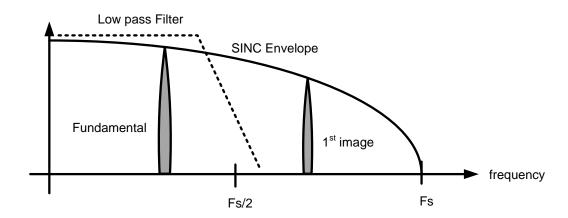

| 2.11 | Nyquist rate synthesis using the fundamental spectrum           | 26 |

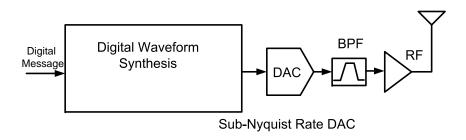

| 2.12 | Sub-Nyquist rate DWS transmitter architecture                   | 27 |

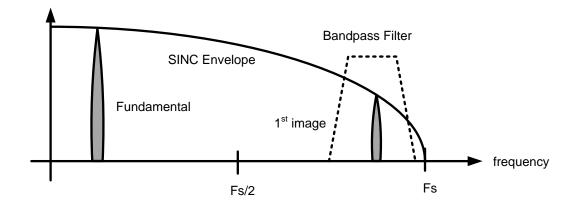

| 2.13 | Utilize the image spectrum                                      | 28 |

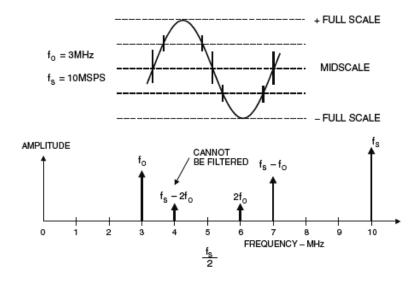

| 2.14 | Sub-Nyquist rate digital-to-analog conversion                   | 29 |

| 3.1  | The time domain operation on the boundary of digital and analog | 31 |

| 3.2  | The frequency domain response of NRZ reconstruction             | 32 |

| 3.3  | The time domain operation of NRZ and RZ                         | 33 |

| 3.4  | NRZ and RZ with various duty cycles                             | 34 |

| 3.5  | The time domain operation of TPH                                | 35 |

| 3.6  | Two phase holding with 50% duty cycle                           | 36 |

| 3.7  | Two phase holding with 25% duty cycle                           | 37 |

| 3.8  | Two phase holding with period variation                         | 38 |

| 3.9  | Two phase holding with duty cycle variation                                | 39 |

|------|----------------------------------------------------------------------------|----|

| 3.10 | Summary of multi-mode reconstruction                                       | 41 |

| 3.11 | Binary, Thermometer-coded, and Segmented DAC                               | 42 |

| 3.12 | DNL and INL                                                                | 43 |

| 3.13 | Spurious free dynamic range                                                | 45 |

| 3.14 | Distortion caused by the non-ideal transfer function curve                 | 46 |

| 3.15 | code dependent glitches and harmonic spurs                                 | 47 |

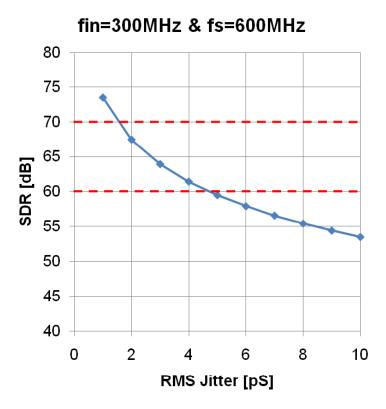

| 3.16 | SDR versus RMS jitter                                                      | 49 |

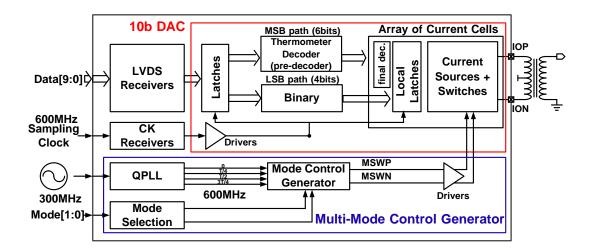

| 4.1  | The block diagram                                                          | 54 |

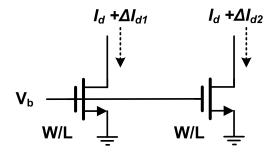

| 4.2  | Mismatch between two MOS current sources                                   | 56 |

| 4.3  | Schematics of current cells with mode control signals                      | 57 |

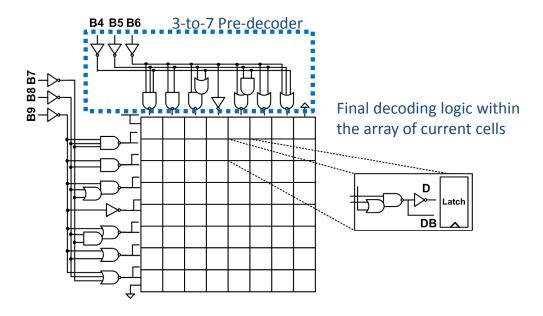

| 4.4  | Binary-to-thermometer code decoder                                         | 59 |

| 4.5  | The schematic of the latch inside switch cells                             | 60 |

| 4.6  | Scrambled mapping of the unary array                                       | 61 |

| 4.7  | The circuitry of clock and multi-mode control signal generation            | 62 |

| 4.8  | Transition of modes                                                        | 62 |

| 4.9  | DAC floorplan                                                              | 63 |

| 4.10 | 2D common centroid floorplan                                               | 64 |

| 4.11 | DAC core layout                                                            | 65 |

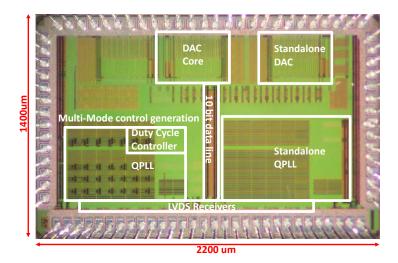

| 4.12 | Chip microphotograph                                                       | 67 |

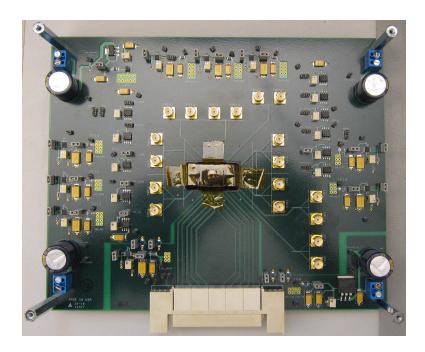

| 4.13 | Prototype printed circuit board                                            | 68 |

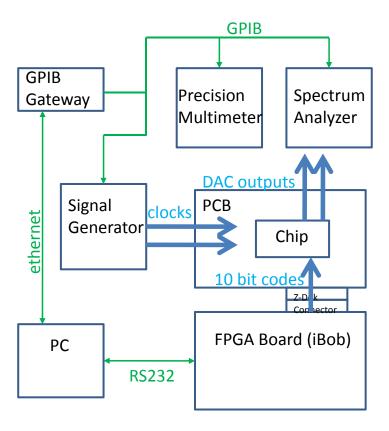

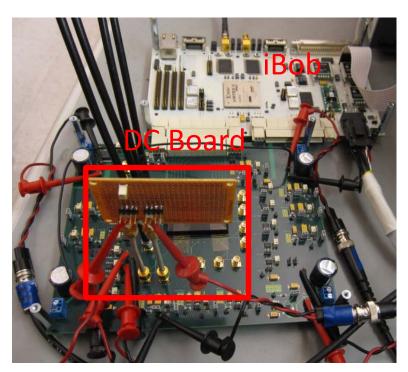

| 4.14 | Measurement setup                                                          | 69 |

| 4.15 | DC linearity measurement setup                                             | 70 |

| 4.16 | Measured DNL and INL plots                                                 | 71 |

| 4.17 | AC linearity measurement setup                                             | 72 |

| 4.18 | Measured SFDR curves: NRZ, RZ, and 50%TPH mode                             | 74 |

| 4.19 | Output spectrum of the 1st image at 590MHz in 50%TPH mode, sampling at     |    |

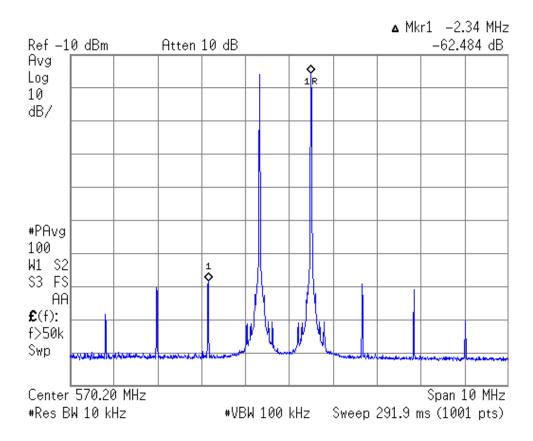

|      | 600MS/s                                                                    | 75 |

| 4.20 | Composite SFDR plot (NRZ + $50\%$ TPH)                                     | 75 |

| 4.21 | Measured IM3 versus signal frequency: NRZ + TPH mode                       | 76 |

| 4.22 | Output spectrum of two-tone IMD centered at 570MHz in 50%TPH mode, 600MS/s | 77 |

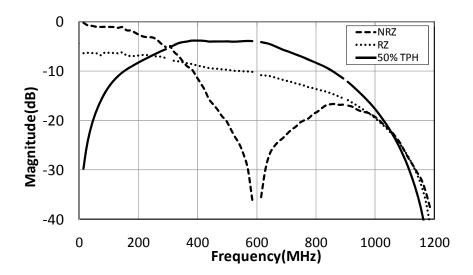

| 4.23 | Measured amplitude response                                                | 78 |

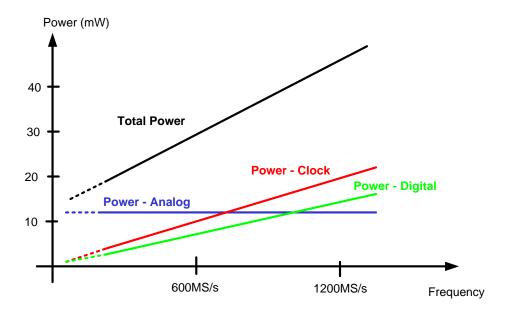

|      | Power consumption breakdown                                                | 78 |

|      |                                    | vi |

|------|------------------------------------|----|

| 4.25 | Power consumption versus frequency | 81 |

| 5.1  | The evolution of cognitive radios  | 84 |

| A.1  | US TV channels                     | 91 |

# List of Tables

| 2.1 | Overview of the FCC rules for TV white spaces              | 12 |

|-----|------------------------------------------------------------|----|

| 3.1 | Summary of design specifications                           | 52 |

| 4.1 | Performance summary of the multi-mode sub-Nyquist rate DAC | 79 |

| 4.2 | Comparison of published CMOS current-steering DACs         | 79 |

## Acknowledgments

It has been a great experience for me to study at the University of California, Berkeley. The knowledge and experience gained at Berkeley are going to benefit me along my career path.

First and foremost, my sincere gratitude goes to my advisor, Professor Jan M. Rabaey for his guidance, and support during my stay at Berkeley. I benefited tremendously from his vision and a broad spectrum of creative ideas from systems to circuits. I also want to thank Professor Alon, Professor Ramchadram, and Professor Wright for being in my qualifying examination committee and for their comments and feedbacks. I would like to thank Professors Rabaey, Alon, and Wright for reading my dissertation.

I am indebted to Mike Shuo-Wei Chen for his mentoring of signal processing and mixed-signal circuit designs. He provided me with intuition in analog/mixed-signal circuits and shared many thoughts on school and life. In addition, I would like to thank Nam-Seog Kim for designing the clock generation circuits for my chip, Bill Tsang for discussion of data converter designs, Wei-Hung Chen for comments in my design review, and Mark Wagner for assisting the FPGA board setup. Also, I would like to thank Jun-Chau Chien, Renaldi Winoto, Lingkai Kong, and Debopriyo Chowdury, who always stayed with me when I struggled with the challenges during my chip design and measurement. The constructive discussion with them always brought me to the light of hope to resolve the obstacles and move to next steps.

Sincere thanks also go to faculty, and sponsors of the Berkeley Wireless Research Center (BWRC), funding support from the National Science Foundation Infrastructure Grant No. 0403427, wafer fabrication donation of STMicroelectronics, and the support of the Gigascale Systems Research Center, one of the five research centers funded under the Focus Center Research Program, a Semiconductor Research Corporation program.

I was based in BWRC for the most part of my Ph.D. career. It is really a privilege to be associated with the center. Special thanks to Gary Kelson, Deirdre McAuliffe-Bauer, Tom Boot, Brenda Farrell, Pierce Chua, Ellen Lenzi, Brian Richards, Fred Burghardt, Sue Mellers, Chang Chun, Dan Burke, Kevin Zimmerman, Brad Krebs, and other staff members for making BWRC such a pleasant place to work.

I would like to express my appreciation to all colleagues at the BWRC and EECS Department for their help and support. I learned so much from them during my stay at Berkeley. Especially, I would like to thank students from Professor Rabaey's research group for their help and friendship, Enyi Lin, Yuen-Hui Chee, Louis Alarcon, Simone Gambini, Chris Baker, Jesse Richmond, Micheal Mark, David Chen, Tsung-Te Liu, Nam-seog Kim, Rikky Muller, Wenting Zhou, Wen Li, William Biederman, and Dan Yeager. They all made my life at

Berkeley easier and happier. Furthermore, my appreciation also goes beyond the group boundary - thanks to Wei-Hung Chen, Zhengya Zhang, Zheng Guo, Bill Tsang, Renaldi Winoto, Jun-Chau Chien, Seng Oon Toh, Ji-Hoon Park, Lingkai Kong, Chintan Tekkar, Debopriyo Chowdury, Cristian Marcu, Xuening Sun, Yury Markovsky, and Liang-Teck Pang. Without them, my study would not be as successful. I will like to thank all my friends for their supports.

Finally, I would like to thank my parents for the support in the long journey of perusing a Ph.D degree at Berkeley. I would also like to thank my wife, Wan-Yu, for her support, encouragement, and patience in the past few years, especially in tough moments of my study. She is the main support in my life with endless love.

# Chapter 1

# Introduction

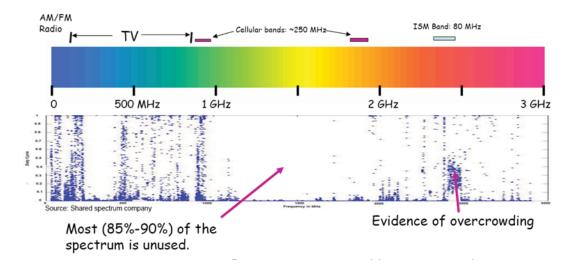

As the demand for high data-rate wireless and wide-range coverage of communications services increases rapidly, technologies to improve the flexibility and efficiency of spectrum utilization are becoming more significant. According to the spectrum measurement study conducted by Shared Spectrum Inc., the measurement results in Figure 1.1 show the spectrum utilization from 30MHz to 3GHz in 24 hours. The spectrum usage experiences vast temporal and geographic variations ranging from 15% to 85%. It shows the evidences of low utilization in most of the spectrum and overcrowded situations in certain frequency bands.

Figure 1.1: Spectrum utilization of 30MHz  $\sim$  3GHz in a 24-hour period

Cognitive Radio (CR) technology has been proposed as a way of improving spectrum utilization efficiency. A cognitive radio system senses the spectral environment over a wide frequency range and exploits the spectrum occupancy information to provide wireless links. It opportunistically uses the unoccupied spectrum segments while preserving the rights of privileged primary licensed users [1].

To communicate efficiently without interfering with licensed or unlicensed users, the cognitive radio network adapts its transmission and reception parameters dynamically. The seamless connectivity in a time-varying spectral environment is ensured by the reconfigurability and frequency agility of the cognitive radio terminals. Low power consumption is also required to save battery life on the mobile devices.

The current cognitive radio research directions are steered toward consumer-oriented scenarios so as to enable seamless adaptation of dynamic spectrum access to multiple networks in TV band white spaces. The future directions may include opportunity-discovery mechanisms minimizing network overhead (e.g., coordination between spectrum sensors) to promote flexible network topologies with less control, spectrum-aware network architectures and frequency-agile transceivers designed to accommodate popular customer applications such as video streaming, and spectrum-trading mechanisms to enable elastic spectrum reuse for various cognitive radio applications.

## 1.1 TV Band Cognitive Radio - "WiFi on Steroids"

Regulatory efforts are currently ongoing in many countries to open up secondary access to TV band white spaces, under the prerequisite of no harmful interference produced to primary users. The regulatory agencies include Federal Communications Commission (FCC) regulations in the USA, Office of Communications (OFCOM) in the UK, and the Electronic Communications Committee (ECC) in Europe. According to the FCC's National Broadband Plan in 2010 [2], the FCC should make 500 megahertz newly available for broadband use within the next 10 years, of which 300 megahertz between 225 MHz and 3.7 GHz should be made newly available for mobile use within five years. The FCC initiates a rule making proceeding to reallocate 120 MHz from the broadcast television bands and expand opportunities for innovative spectrum access models. The license-exempt use of TV band white spaces is very promising as a key component in the National Broadband Plan. It becomes a big driving force of the research on cognitive radio technologies.

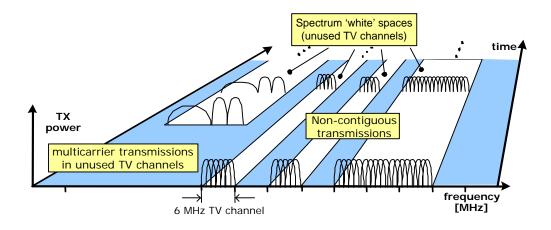

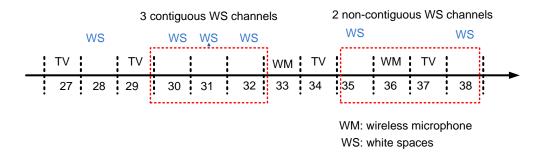

As shown in Figure 1.2, white space is the name given to the vacant unused spectrum

between television channels. In the TV band, the airwaves have the potential to carry wireless data at speeds and distances that overtake the existing WiFi systems. This "Super WiFi" in those TV white spaces has a range of several miles, rather than the length of a football field, and it is capable of traveling through obstructions like trees or walls. Therefore, the TV white space has earned the nickname "WiFi 2.0" or "WiFi on Steroids". With a range of several miles as well as speeds close to cable modem broadband, we can easily see how the TV white spaces could open up a whole new realm of wireless technologies and fundamentally change how and where wireless communications are used.

Figure 1.2: TV band white spaces

Regarding the current progress on TV white spaces, the FCC has worked with the concerned parties and come up with a plan that ensures that devices using the TV band white spaces will not interfere with adjacent broadcasts. The FCC has mapped TV channels and major wireless microphone usage (such as the Broadway theater district in New York City, or major sports arenas), and will require that wireless devices using the white spaces be configured to avoid the frequencies in use in a given area. Devices could be built to be location-aware, and automatically configure themselves based on information in the database.

A number of transitional steps will be necessary to allow for the gradual introduction of unlicensed devices on unused broadcast frequencies. The first step would allow unlicensed devices to operate on the guard bands and unassigned channels in the bands associated with TV channels 52-69. Since these channels have been designated for relocation early in the DTV transition, and since there are very few allocated stations, a significant amount of spectrum would be available for immediate sharing. As the band is vacated by current

licensed users, unlicensed devices would then be granted the full frequency range for dedicated unlicensed use while remaining cognizant of and avoiding interference to the public safety operations in the Upper 700 MHz band. Finally, as the DTV transition enters its final stages, former analog guard bands in the range of channels 2-51 (excluding Channel 37, reserved for radio astronomy), could be made available for unlicensed use.

As cognitive radios and TV band white spaces continue to draw more and more attention, they become an essential part of the emerging wireless communications standards and systems recently. The prospects of TV white space regulations have triggered development of new wireless standards, including IEEE 802.22, ECMA-392, and IEEE 802.11af. These various schemes proposed thus far have been reviewed and compared to identify which of them to use for real-life cognitive radio applications.

For wide-area broadband applications, IEEE 802.22 is a standard for Wireless Regional Area Network (WRAN) using white spaces in the TV broadcasting band (54MHz ~ 862MHz) [3] [4]. This standard aims at using cognitive radio technologies to allow sharing of geographically unused TV broadcast spectrum, on a non-interfering basis, to bring broadband access to hard-to-reach, low population density rural areas. On the other hand, the FCC's allowance of personal/portable devices in TV white spaces also introduces other two standards: IEEE 802.11af [5] and ECMA-392 [6]. Those two standard are for portable or personal devices with low transmit power of 40mW or 100mW, operating within a smaller coverage.

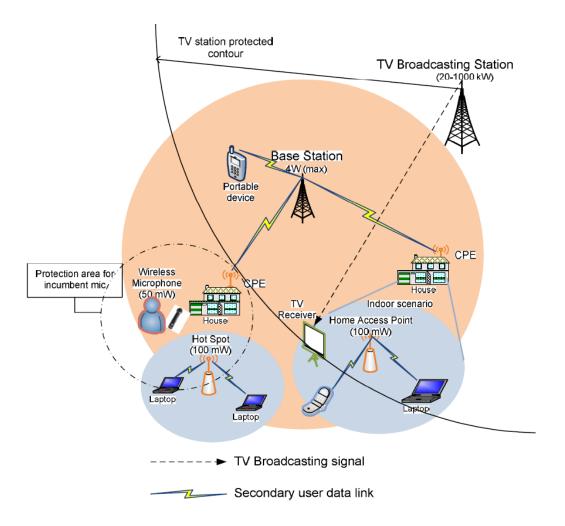

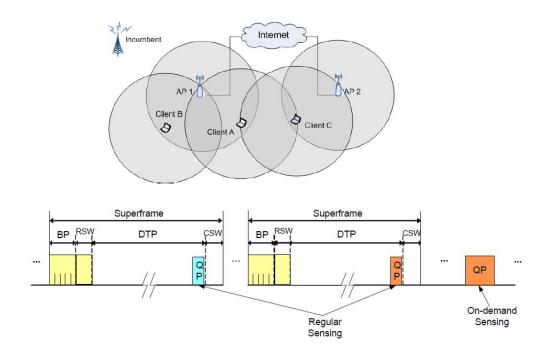

As new standards and compatible products are developed, we can envision scenarios where multiple cognitive radio networks in TV band white spaces will likely overlap with each other creating the needs for coexistence mechanisms. A generic heterogeneous scenario is illustrated in Figure 1.3, where multi-radio devices take advantage of the TV band white spaces to achieve higher capacity and/or wide transmission ranges. In one typical case, a fixed wide area broadband network (e.g. IEEE 802.22) could provide wireless backhaul to homes, which use Wi-Fi (e.g. IEEE 802.11af) or ECMA-392 for in-home coverage. Alternately, IEEE 802.11af or ECMA-392 devices could form a neighborhood mesh network.

This is a new paradigm for wireless communications based on harnessing unused spectrum. Those spectrum agile radios enable new applications, such as wireless internet, remote patient monitoring, and public safety.

Figure 1.3: Heterogeneous coexistence of TV band radios

## 1.2 Related Work

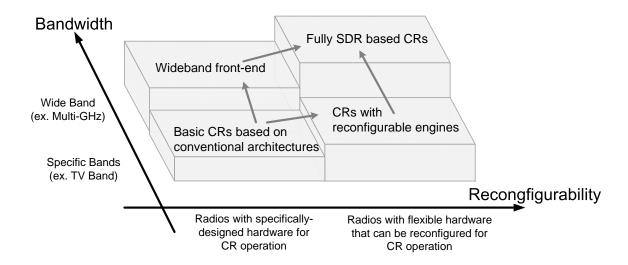

The idea of cognitive radio was first presented officially in 1999 by Joseph Mitola III in his pioneering work [7]. The research of cognitive radios has been rapidly developed in the past decade [8]. Cognitive radio was initially thought of as a software-defined radio extension. Cognitive radio has the potential of reshaping the way of utilizing spectrum resources. This led to the FCC's initiation of a new spectrum policy in 2000 [9]. Many research efforts span from radio and reconfigurable hardware to communications theory as well as the networking layer. Through the continuing efforts of spectrum regulators and the research community, the TV white spaces are going to be opened for license-exempt uses

of cognitive radio applications. The TV band white spaces are expected to mitigate the anticipated spectrum shortage problem. The regulatory policies, industrial activities, and standardization will soon be developed.

The history of TV band radios can be traced back to the late 1920's. Since the TV broadcast services had been widespread in the past decades, various analog/digital TV broadcast standards and systems exist throughout the world today. The conventional TV broadcasts is a one-way transmission from the high power TV transmission towers to TV tuner. The design of high-power TV transmitters and high sensitivity tuners has been well exploited and engineered [10] [11] [12].

With the advances of circuits and technologies, classical analog TV "can tuners" have been replaced by much more integrated IC solutions. The low power and low cost CMOS tuners can be directly integrated onto the main board with reduced numbers of discrete components. To support the terrestrial broadcast TV in UHF/VHF band, tuners need to address issues, such as the interference rejection at integer multiples of the wanted signal as well as the in-band image rejection. Typical techniques include using external RF tracking filters with limited bandwidth that track the signal carrier, or the conventional up-down conversion super-heterodyne architecture. To achieve the wide tuning range and wide bandwidth, tunable analog/RF blocks are intensively used in the front-end of the conventional architecture.

There are many published examples of integrated TV band receivers. In [13], the competitive, low-cost solutions in CMOS technology presents the implementation of a tuner in 65nm CMOS process, supporting all most popular mobile TV standards, such as DVB-T/H, DAB based T-DMB, and ISDB-T. The extensive use of digital calibration hardware to improve the tuner performance and achieve a high degree of programmability required in multi-standard operation. In [14], a silicon tuner has been designed for the reception of analog or digital TV signals from a cable or a terrestrial network. It exhibits 5 dB NF over the 42-870 MHz frequency range and integrates a self-calibrated LC tracking filter. This allows 55 dB video SNR under fully loaded spectrum conditions. However, those examples are mainly focusing on the design of the TV band receiver. The transmitter designs in TV band radios have not been shifted from high-power TV tower to an integrated low-power and small form factor design.

This work explores practical TV band cognitive radio transmitter from system-level design to circuit implementation of critical blocks. The proposed direct waveform synthesis architecture is mostly-digital and frequency-agile. There are notable examples of reconfigurable, or software-defined transmitters [15]. Broadband, reprogrammable, and highly-

integrated implementation as well as novel techniques can be found in the literature [16–18]. The focus here is on the TV band frequency range where the spectrum white spaces are permitted for unlicensed use. Digital signal processing offers a degree of flexibility that is perhaps unmatched by analog circuits. This drives us to push the Digital/Analog boundary toward the front-end. Nevertheless, this trend implies that demand of high-speed wide bandwidth D/A converter to fulfil the system requirements.

To overcome the bottleneck of D/A conversion and the challenges of Nyquist rate synthesis, many signal reconstruction techniques have been proposed for enabling wideband signal synthesis. Past work presented Return-to-Zero (RZ) to flatten the SINC envelope and extend the possible operation region to higher Nyquist zones [19–21]. By using RZ reconstruction, the SINC roll-off in the DAC output is flattened while null frequencies are pushed to higher. This extends the usable region of signal synthesis from the first Nyquist zone to the second or the third Nyquist zone. Also, partial-order-hold (POA) technique for wide bandwidth operation had been proposed in [22]. The POH-DAC architecture is archived by a zero-order-hold DAC followed by a windowed-integration-based filter. It has the ability of broadband image reduction between 1.5 and two times the sampling frequency while also providing a flat-group delay. Interleaving two such POH-DACs results in a DAC with an excellent output signal reconstruction whereby the broadband sampling images below two times the sampling frequency in the output signal spectrum are strongly reduced.

In the research community of RF circuits, people tried to push the D/A interface closer to the RF front-end, which contributes the idea of RF-DAC. In [23] an IQ-modulator constructed using direct digital-to-RF converters for wide-band multi-radio applications achieves better than -43dBc of LO-leakage and -47dBc of image rejection. This idea has been demonstrated in 0.13um standard CMOS process. Another similar idea can be found in [24]. A low-distortion wide-band CMOS direct digital RF amplitude modulator uses a 10-bit linear interpolation current-steering DAC and a Gilbert-cell-based mixer to generate an amplitude modulated RF signal directly. In [25], a RF-DAC in 65nm CMOS is presented. The RF-DAC combines DAC and mixer functionality in a single building block. It is the basis for a direct-digital vector modulator used in reconfigurable broadband multi-standard transmitters for mobile communications. In [26], a 17b RF DAC is applied a fully digital multi-mode polar transmitter in 3G Mode.

In this work, a multi-mode sub-Nyquist rate conversion technique is proposed to achieve the goal of wide bandwidth waveform generation. The reconstruction mode can be dynamically reconfigured to achieve the best spectrum envelope for utilizing the image spectrum. A circuit prototype demonstrating the proposed concepts has been designed, fabricated and measured. The prototype chip is able to maintain good SFDR across multiple Nyquist zones. This enables the direct waveform synthesis for the cognitive radio transmitters.

## 1.3 Thesis Organization

Chapter 2 begins by presenting an in-depth overview of cognitive radios for TV band white spaces, and reviewing the standards for TV band cognitive radios. After that, the system-level work is the main focus, which includes the transmitter architectures and direct waveform synthesis using sub-Nyquist rate conversion.

In Chapter 3, the concept and analysis of sub-Nyquist rate conversion are discussed. The multi-mode reconstruction technique has been proposed to overcome the wide bandwidth and high dynamic range requirements for direct waveform synthesis. The multi-mode sub-Nyquist rate DAC operation has been proposed to be a versatile solution for spectrum agile radio applications.

In Chapter 4, the circuit implementation and measurement results are presented. The sub-Nyquist rate DAC chip was fabricated in 65nm CMOS technology by ST Microelectronics. The chip is measured to be fully functional and characterized in static and dynamic performances. The performance and power measurements are presented in the end.

Finally, the conclusions and future work are summarized in Chapter 5.

# Chapter 2

# Mostly Digital Transmitter for TV Band Cognitive Radio

The growth in demand for wireless voice and data communications has driven recent research to develop highly-integrated next-generation radio transceivers. To reduce costs and power consumption, much effort has gone into implementing these transceivers in standard CMOS technology. Advances in high-speed DACs, implemented in deeply-scaled CMOS processes, open up the possibility of direct IF and RF waveform synthesis in a digitized transmitter architecture. The state of the art CMOS current-steering DAC is capable of providing wide bandwidth and high dynamic range for direct RF waveform generation [27]. The conventional waveform synthesis requires a DAC running at > 2GS/s to fulfill the Nyquist requirement for covering the TV band (54  $\sim$  862MHz). Nevertheless, an alternative method is to convert the signals at a sampling rate below the Nyquist requirement and extract the image spectrum in higher Nyquist zones by bandpass filters [19,20].

In this chapter, the direct waveform synthesis transmitter is proposed for TV band cognitive radio applications. The reconfigurable digital waveform synthesizer and multi-mode sub-Nyquist rate D/A conversion are the two key components in this mostly-digital transmitter.

## 2.1 White Spaces in TV Bands

TV band white spaces refer to the vacant channels allocated to a broadcasting service but not used locally. On Feb. 13, 2009, Congress initiated the American Recovery and Reinvestment Act of 2009. As part of this initiative, the Federal Communications Commission (FCC) developed a National Broadband Plan. This plan sets its primary goal to ensure every American has access to broadband capability. It also promotes other objectives, including a detailed strategy to maximize broadband usage and affordability. The FCC has several tools available to help reach these goals: regulatory authority in spectrum policy and spectrum allocation (both licensed and unlicensed). The importance of spectrum is further underscored by the fact that an entire chapter of the Commission's National Broadband Plan is devoted to spectrum usage and policy. The FCC has also highlighted the availability and use of TV White Spaces as a key component of the National Broadband Plan. As mentioned in section 5.12 in the plan, the FCC should move expeditiously to conclude the TV white spaces proceeding.

The TV broadcast band in the United States has evolved through a number of changes over time, primarily due to the FCC's desire to make more VHF and UHF bandwidth available for wireless two-way communications. To achieve this, the FCC adopted rules to allow unlicensed radio transmitters to operate in the broadcast TV spectrum at locations where that spectrum is not being used by licensed services - this unused TV spectrum is often termed "TV White Space". TV White Spaces are unused TV broadcast channels, made more available through the transition from analog to digital TV. The current TV channels and frequency allocation in the US is shown in Figure 2.1. The FCC has not dictated specific modulation or protocol requirements for TV Band Devices (TVBDs), allowing TV White Space to employ a wide range of devices and applications on an unlicensed basis, similar to Wi-Fi. The FCC has also ensured incumbent TV band users (TV broadcasters, public safety, registered microphone users, etc) have priority over TV White Space Device operation. To make certain incumbent users are protected, TV White Space devices must communicate with an Internet geographic database to obtain a current list of available White Space channels. Available channels may vary, depending on TVBD device type and location.

Figure 2.1: Overview of TV Channels in US

| Device types/<br>Capability |         | Allowed TV<br>Channels                  | Max<br>EIRP | Incumbent protection requirements                  | Allowed on<br>Adjacent<br>Channels |

|-----------------------------|---------|-----------------------------------------|-------------|----------------------------------------------------|------------------------------------|

| Fixe                        | ed      | Ch 2 – 51<br>(except Ch 3, 4<br>and 37) | 4 W         | Geolocation /<br>Database                          | No                                 |

| Personal/                   | Mode I  | Ch 21 – 51<br>(except Ch 37)            | 100 mW      | Enabling signal<br>from Mode II or<br>Fixed Device | Yes<br>(< 40mW EIRP)               |

| Portable                    | Mode II |                                         | 100 mW      | Geolocation /<br>Database                          | Yes<br>(<40 mW EIRP)               |

Table 2.1: Overview of the FCC rules for TV white spaces

The current FCC rules for TV band channels are listed in Table 2.1. the devices are divided into two categories: fixed and personal/portable. Fixed devices can transmit up to 4 W EIRP (equivalent isotropically radiated power) with a power spectral density (PSD) of 16.7 mW/100 kHz, and they must have geolocation capability and a means to retrieve a list of available channels from an authorized database. The fixed devices are restricted of operating in adjacent channels of active TV broadcasting channels. Fixed devices may operate in channels 2 to 51, excluding channels 3, 4, and 37.

Personal/portable devices are allowed a maximum EIRP of 100 mW (with PSD of 1.67 mW/100 kHz) on channels non-adjacent to TV broadcast services and 40 mW (with PSD of 0.7 mW/100 kHz) on channels adjacent to an active TV broadcasting channel. Personal/portable devices are classified into two modes: Mode I and Mode II. Similar to fixed devices, Mode II devices must possess geolocation and database access in order to obtain a list of available channels. On the contrary, Mode I devices are not required to have geolocation and database access, but they must obtain a list of available channels from a fixed or Mode II device. Personal/portable devices are only allowed in channels 21 to 51 (excluding channel 37). The main expectation is that fixed devices will most likely be used in rural areas, whereas portable devices may be highly used in metropolitan areas. The idea behind this channel allocation is to avoid the risk of interference with primary services, especially in high density population areas.

The available white spaces varies according to where you locate and what type of devices that you want to operate. The company, Sprectrum Bridge Inc, provides a centralized location-based database for visuallize the available white spaces. For non-highly populated areas, like Lake Tahoe, we can see the available white spaces for operating portable TV band devices from Figure 2.2. If we want to operate higher power, fixed TV band device, the number of available white space decreases as shown in from Figure 2.3. If we move our target location to the city area, like Berkeley, we can see the available white spaces from Figure 2.4.

Figure 2.2: Available TV White Spaces for Portable Devices in Lake Tahoe

Figure 2.3: Available TV White Spaces for Fixed Devices in Lake Tahoe

Figure 2.4: Available TV White Spaces for Portable Devices in Berkeley

For most of the U.S. land mass and population, there are significant amounts of TV White Space bandwidth available that can be used for a wide variety of applications. There is sufficient bandwidth available for Fixed Device (4W devices) use, which is needed to deliver wireless broadband to many communities in the country. In the majority of the country, there also appears to be sufficient white spaces available for portable/mobile applications, such as Wireless LAN - useful for augmenting 3G/4G services. A generous amount of bandwidth has been reserved for wireless microphone use. TV White Space is clearly an essential and significant element in the National Broadband Plan. Both the spectrum itself, as well as the database-driven spectrum allocation, make it a model for more efficiently deploying spectrum resources for a wide range of innovative applications.

- Whole home application: Television white spaces will enable wireless distribution of high-quality and high definition television for whole home, vastly improving the DTV experiences. The new standard will provide reliable and robust coverage anywhere in a home, while consuming much lower power. Robust delivery of high definition video inside home and across multiple walls.

- Community internet access application: Television white spaces will provide more widely available and cost effective access to the internet in underserved markets. The superior propagation characteristics provide much greater coverage range than existing unlicensed technologies. Robust coverage inside buildings and across campuses for wireless data applications such as wireless VoIP and mobile unified communications. Enhanced range for municipality, community and rural internet access without sufficient line of coverage.

- Smart services and other applications: Enhanced coverage for smart service and remote machine-to-machine and RFID deployments such as smart grid, smart metering, transportation, industrial automation, supply chain automation, asset tracking and environmental monitoring. New interactive applications for TV broadcasters, such as weather and news updates, upcoming program previews, interactive advertisements and games and web access. Most importantly, TVWS can provide enhanced range, robustness and quality for emergency-response and public service communication networks.

The TV White Spaces bring a new paradigm to wireless networking. By using a centralized database architecture for allocating spectrum, the FCC has taken the first step towards policies and technologies that embrace a dynamic and highly efficient approach to increase spectrum availability and utilization for other licensed and unlicensed spectrum bands.

## 2.2 TV Band Cognitive Radio Standards

TV band cognitive radio is fundamentally different from the conventional TV broadcasts. TV broadcasts are one-way radio transmission, where the signals are transmitted from the high power TV towers to the tuners inside the televisions. For decades of technology development, the high-power TV broadcast towers and high sensitivity TV tuners have been explored and designed to reach the best performance.

The TV band cognitive radio aims at two-way communications. The transmitter design used in the high power TV towers is inadequate and obsolete to be the target solution for cognitive radio transmitters, because of the limited power budget for cognitive radio applications. Compared to conventional TV broadcast services, the low-power and small form factor TV band transceivers are the main area for further exploration and research. The TV band white spaces have motivated several standardization efforts, such as IEEE 802.22, IEEE 802.11af, and ECMA 392 for furthering cognitive networking. The introduction and highlights of the selected standards are presented in the following sections.

#### 2.2.1 IEEE 802.22

On 27 July 2011, IEEE published the IEEE 802.22 standard for opportunistic use of the available TV white spaces [4]. IEEE 802.22 systems provide broadband access to wide regional areas around the world and bring reliable and secure high-speed communications to under-served and un-served communities. This new standard for Wireless Regional Area Networks (WRANs) takes advantage of the favorable transmission characteristics of the VHF and UHF TV bands to provide broadband wireless access over a large area up to 100 km from the transmitter. Each WRAN will deliver up to 22 Mbps per channel without interfering with reception of existing TV broadcast stations, using the white spaces between the occupied TV channels. This technology is especially useful for serving less densely populated areas, such as rural areas, and developing countries where most vacant TV channels can be found. IEEE 802.22 incorporates advanced cognitive radio capabilities including dynamic spectrum access, incumbent database access, accurate geolocation techniques, spectrum sensing, regulatory domain dependent policies, spectrum etiquette, and coexistence for optimal use of

the available spectrum. It also defines the air interface of WRAN. The airwaves in TV bands have superior propagation characteristics that can increase coverage and the ability to penetrate buildings at low power levels. This is the leading factor that helps IEEE 802.22 to provide better broadband service for far-out users. IEEE 802.22 focuses on wireless broadband access in rural and remote areas as its coverage area is much greater than other wireless broadband technologies, such as WiMAX and Wi-Fi.

IEEE 802.22 WRAN system consists of Base Stations (BS), fixed Consumer Premise Equipments (CPEs), and also personal/portable devices which can operate in the TV band white spaces. The fixed devices would have geographical location capability with embedded GPS device so that they can communicate with a centralized database to identify other transmitters in the area operating in the same TV band. In addition, there are other measures suggested by the FCC and IEEE to avoid interference, such as: dynamic spectrum sensing and dynamic power control. The personal/portable devices transmit lower power and shorter coverage for mobile applications.

The PHY layer needs to provide excellent in performance as well as simple in implementation. To avoid interferences, the PHY layer must be able to adapt to different conditions and also needs to be flexible to jump from channel to channel without errors in transmission or losing CPEs. This flexibility is also required to enable dynamical adjustment of the bandwidth, modulation and coding schemes. OFDMA is the modulation scheme for transmission in both up and down links. With OFDMA, it will be possible to achieve this fast adaptation needed for the BS's and CPEs. By using just one TV channel (6 MHz/channel in US; in some other countries 7 or 8 MHz/channel), the approximate maximum bit rate is 19 Mbit/s with the coverage of a 30 km distance. To allow the system to have higher performance, Channel bonding is one of the suggested features for dealing with the insufficient bandwidth which can combine up to 3 TV channels for the transceivers. Also, IEEE 802.22 defines 12 combinations of three modulations (QPSK, 16-QAM, 64-QAM) and four coding rates (1/2, 2/3, 3/4, 5/6) for data communications that can be flexibly chosen among to achieve various trade-offs of data rate and robustness, depending on channel and interference conditions.

## 2.2.2 ECMA-392

ECMA International started developing a high-speed wireless networking standard for utilizing the TV band white spaces, based on the contribution from Cognitive Networking Alliance (CogNeA). The ECMA-392 standard employs cognitive radio technology to avoid interference with licensed services and other incumbent users in compliance with the FCC

regulatory rules. It aims at multimedia distribution and internet access for low-power personal/portable cognitive devices in TV white spaces [6]. It specifies medium access control (MAC) sub-layer and physical (PHY) layer for operation in TV White Spaces. It also specifies a number of incumbent protection mechanisms which may be used to meet regulatory requirements.

Figure 2.5: Overview of EMCA 392

The specification targets a flexible system that uses one or multiple vacant TV channels to provide the wireless communications, for example, in home distribution of audio and video, wireless internet access, etc. The various aspects of the PHY specifications are highlighted below. This PHY operates in the VHF/UHF TV broadcasting frequencies, subject to regulation. The extremes of the international regulations range of TV broadcast band is from 47 MHz to 910 MHz. Similar to IEEE 802.22, the channel bandwidth is equivalent to that of one TV broadcast channel, i.e., 6 MHz in US and 7 MHz, or 8 MHz in other countries. The channel bandwidth and channel numbering is dependent on the geographic location where the device is intended for operation. This PHY aims for personal/portable devices operating in TV white spaces with 100mW of transmit power. A high efficient MAC layer is also defined in this standard. To support world-wide spectrum regulation, a toolbox approach is adopted, while the FFT-based pilot sensing algorithms is mainly used as the

Figure 2.6: Example Applications of EMCA 392

spectrum sensing and estimation technique.

#### 2.2.3 IEEE 802.11af - "White-Fi"

The IEEE 802.11af Task Group aims to make a transition from the existing Wi-Fi to a Wi-Fi-like protocol operating over the TV white spaces. The white spaces are made up of unused TV channels, which vary from location to location and from time to time. It has been set up to work on the 802.11 MAC and PHY layers to meet the legal requirements for channel access and coexistence in the TV white spaces [28]. The nickname, "White-Fi", is a term being used to describe the use of a Wi-Fi technology within the unused TV white spaces. It is believed that the White-Fi system offers sufficient advantages to invest the efforts on research and kick-start the development. The IEEE 802.11af standardization effort expects to fully standardized TV white spaces on the timeline of 2013.

The spectrum opportunity of TV white spaces consists of fragments of different numbers of available TV channels. This implies variable channel bandwidth can be utilized for wireless communications. The 802.11af plans to support the usage of multiple available channels in TV white spaces. The first type is to use multiple contiguous channels: 1, 2, 3, 4, (optional 8, 16) channels. The second type is to use multiple non-contiguous available channels: within 4 consecutive channels.

Many benefits can be gained from using TV white spaces in IEEE 802.11af system. First, since the TV white spaces locate at frequencies below 1 GHz, the 802.11af system is capable

Figure 2.7: TV white Spaces Usage in 802.11af

of propagating for greater distances than current Wi-Fi systems. In contrast, the Wi-Fi signals operating in the ISM bands are easily absorbed, even in the lowest band of 2.4 GHz. Second, TV white spaces are that additional unused frequencies which can be accessed. However, to achieve the data throughput rates similar to that Wi-Fi uses on 2.4 and 5 GHz, the IEEE 802.11af system will be necessary to aggregate several TV channels to provide the high bandwidth. The synergy of propagation characteristics and additional bandwidth makes IEEE 802.11af an extension of Wi-Fi services in TV white spaces.

When using the IEEE 802.11af in TV white spaces, the overall system must not cause any undesired interference to the primary users such as existing television transmissions and wireless microphones. Using cognitive radio technology, the IEEE 802.11af system detects transmissions and moves to alternative channels. Also, similar to IEEE802.22, geographic sensing is another method proposed to minimize the harmful interference. To have a geographic database with the knowledge of available channels is another way of allowing the system to avoid interferences with used channels.

IEEE 802.11af devices, known as TV Band Devices(TVBDs), will come in two flavors: Fixed TVBDs and Personal/Portable TVBDs. Fixed TVBDs must operate from a known, fixed location, have a maximum 4 W EIRP, maximum 30m antenna height and must be able to determine and report their actual location (within 50m) to an authorized database to retrieve a list of available channels. Fixed TVBDs will be used for establishing long-range links and getting broadband out to unserved and underserved rural locations. They also can operate in any available channels, except reserved channels. Portable/Personal TVBDs are further divided into two categories, Mode I and Mode II. Mode II devices are like Fixed TVBDs in that they have internal geo-location capability and access to a TV

channel database. Mode I devices can not determine their location or check in with a TV channel database, but instead must get their channel list from a Fixed or Mode II TVBD. Portable/Personal TVBDs can use only channels 21 - 51, again, with the exception of reserved channels. For a single channel, a maximum link rate of 23.74 Mbps, or about half the maximum 54 Mbps link rate of 802.11g. Based on the past experience with the difference between PHY link rate and actual throughput, we can reasonably to assume a maximum throughput of a single White-Fi channel at around 10 - 12 Mbps.

Work has being started on the IEEE 802.11af standard for "White-Fi" applications in TV white spaces. In January 2012, "Super Wi-Fi" launched in New Hanover County, North Carolina. It is essentially Wi-Fi re-using the in-between spaces of TV channels below 700MHz and above 50MHz. Spectrum Bridge, a venture funded start-up (2007), and the county of New Hanover County in North Carolina and deploying on white space capable radio channels using 802.11 Wi-Fi as the Physical Layer protocol. Spectrum Bridge provides the channel list and other services while the radios are from Google, Microsoft, Cisco and KTS Wireless. New Hanover County is using their Wi-Fi network to surveil on a subdivision and collect telemetry from their water infrastructure although it appears they will provide citizen Wi-Fi at outdoor locations such as Hugh MacRae Park. In testing white spaces, the ranges can cover up to 1.5 miles on a point-to-point application of the spectrum including signal propagation through vegetation and buildings. With these newly approved radios and appropriate antennas, wireless service can reach far beyond traditional boundaries. By utilizing more favorable unutilized TV spectrum bands than the ISM, the "White-Fi" would be able to support resource-intensive multimedia services more easily than the current Wi-Fi.

# 2.3 Direct Waveform Synthesis Transmitter for TV band Cognitive Radio

Many transceiver architectures are feasible for TV band applications, such as conventional superheterodyne transceivers, direct conversion transceivers, and software-defined radio transceivers. A conventional RF transmitter performs modulation, up-conversion, and power amplification. To accommodate various standards and requirements of TV band cognitive radios, frequency-agility and reconfigurability are two essential requirements in selecting transceiver architecture, since the multiple TV band cognitive radio standards and devices are going to operate on the vacant TV band white spaces with stringent requirements on

spurious emission. A highly-reconfigurable radio is needed as a versatile and low-cost solution.

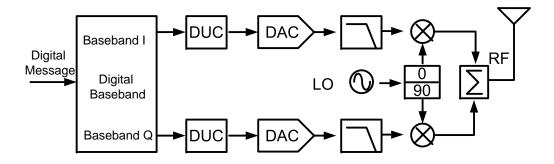

#### 2.3.1 Transmitter Architecture

A conventional direct conversion transmitter block diagram is shown in Figure 2.8. The digital baseband circuitry generates two digital signals (I/Q), the in-phase and the quadrature phase bitstreams. These digital bitstreams are first digitally up-converted and interpolated to match the rate of DAC, and then converted to an analog signal by the following DAC. Next, these two analog signals are then filtered to remove spikes and other spurious non-idealities, mixed up to the RF frequency, and sent off to the front-end power amplifier for transmission. The disadvantage of this transmitter architecture is that the up-conversion mixer and the frequency synthesizer in the analog/RF front-end have to achieve a wide tuning range and fast adaptation, if we need to cover a wide frequency range and hop around agilely. The analog/RF front-end will face stringent design challenges and consume a lot of power to meet the requirements.

Figure 2.8: Conventional transmitter architecture

As we mentioned before, CR is a dynamically reconfigurable radio that adapts its operating parameters to the surrounding environment. By looking at this architecture closely, if the speed of the DAC can be increased substantially, the specifications for the filter stage and analog front-end would be relaxed. Therefore, the DAC can be moved toward the antenna, since part of the functions of the analog/RF front-end can be moved to the digital domain with DSP enhancements and compensation for analog impairments. As the advances of CMOS technology scaling, digital processing may be used to assist in removing or relaxing

the constraints on analog blocks, thus allowing a reduction of power consumption in the radio system. This leads to an transmitter architecture with flexibility and reconfigurability of digital processing, which is introduced in the next section.

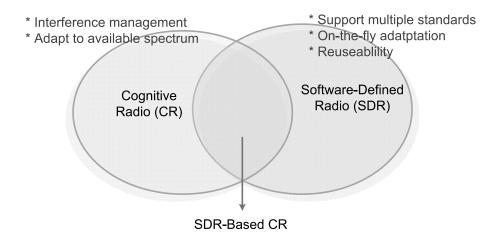

In contrast to the traditional radio architecture, an alternative approach is to adopt mostly-digital implementation by moving the digital logics as close to the antenna as possible. Therefore, direct synthesis of digital waveforms and high-speed RF waveform conversion has drawn a lot of interests among researchers and engineers. This leads to the software-defined radio transmitter architecture for cognitive radio applications. As illustrated in Figure 2.9, the synergy of SDR and cognitive radio brings lots of benefits, including on-the-fly switching to multiple networks, reusability of components, and reconfigurability after manufacture.

Figure 2.9: Synergy of software-defined radio and cognitive radio

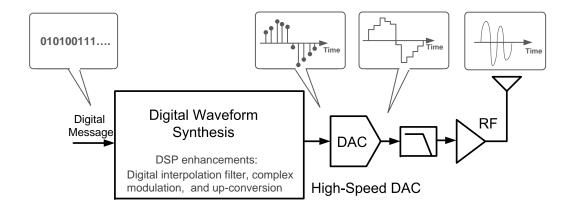

In this work, the proposed architecture is based on the concepts of a direct conversion SDR style transmitter rather than a conventional superheterodyne architecture. The proposed transmitter is a direct waveform synthesis (DWS) transmitter, as illustrated in Figure 2.10. Under this mostly-digital transmitter architecture, the wideband IF/RF waveform is directly synthesized without the analog up-conversion stage (e.g. the mixer and the frequency synthesizer).

Waveform synthesis has been studied extensively in signal processing and communication communities [29–31]. A well-synthesized waveform, meaning one with good auto- and cross-correlation properties, can reduce computational burden at the receiver and in the meantime improve performance. This DWS transmitter architecture is mostly-digital, which can take

Figure 2.10: SDR-type transmitter architecture

advantage of the rapid performance increase due to the scaling of CMOS technology. All the complex modulation schemes and waveform generation are fully implemented in a generic digital processing unit or reconfigurable fabric (e.g. FPGA).

To hop around any available TV white spaces, the DWS transmitter achieves the best dynamic adaptation by directly synthesizing the waveform for transmission. With a full control of the waveform in the digital domain, the transmitter can quickly switch to various modulation schemes and transmitter parameters. The waveform is synthesized in the digital domain without using conventional heterodyne type or direct-conversion transmitter architectures.

The baseband waveform synthesizer produces the discrete sampled waveform in the digital domain. It supports complex I/Q modulation schemes and digital up-conversion. The digital interpolation filter adjusts the sample rate to match the sample rate between the baseband waveform generator and the DAC. The pulse-shaping filter, which is often the last baseband operation in the transmitter chain, is required to meet the specification of spectral mask and adjacent channel leakage power ratio(ACLR). It can also be integrated into the interpolating filter. It increases the sampling rate at the output of the filter and shapes the digital samples. This increase in sample rate is desirable as it allows a wider filter transition band, reducing the required number of coefficients in the digital filter. Then the synthesized discrete waveform samples are directly converted into a continuous-time analog waveform by a high-speed DAC with the sampling rate  $f_{DAC}$ . Also the higher sample rate also relaxes the requirements of the post-DAC reconstruction filter. Then the analog waveform is fed into the analog front-end module.

In TV band cognitive radio, one or more types of digital modulation schemes may be used depending on the requirements of the target data rate, channel conditions, spectral usage around the neighborhood. Digital modulation schemes differ greatly in performance and complexity. While simple linear PSK modulation schemes such as QPSK and  $\pi/4$  QPSK offer the best trade-off between power and bandwidth requirements. Other more complex nonlinear modulations, such as GMSK provide high spectral efficiency with the desirable constant envelope behavior for low data rate wireless systems. The high-data rate transmission leads to the inclusion of schemes such as 8-PSK, M-ary QAM, and OFDM. Given the reconfigurability, the baseband can adapt from one standard to another. Also, the dynamic reconfiguration technology in FPGA permits the run-time adaptation of baseband hardware without interrupt he connectivity. This capability enables the run-time reconfiguration of transceiver baseband, modulation schemes, and waveform synthesis engine, etc.

The interpolation filters and complex numerically controlled oscillator (NCO) functions for digital mixer can be easily and efficiently implemented in the digital platforms, such as reconfigurable fabric or digital signal processors. Efficient implementation of OFDM modulation and demodulation is also possible on the reconfigurable fabric, since the inverse fast Fourier transform (IFFT) and fast Fourier transform (FFT) algorithms exhibit a high degree of parallelism. Also the digital up and down conversion chains, pulse shape filtering, CDMA bit level processing, Transmit Crest Factor Reduction, Turbo, Viterbi, and Reed Solomon decoding are all good condidates to benifit from the processing power and programmability in the digital domain.

By moving more functional blocks into the digital domain, we can benefit from CMOS scaling. However, for wideband applications, the primary challenge with this architecture is a drastic increase in the difficulty of digital-to-analog conversion. The transmit D/A converter operating nearly at the RF frequency must have high dynamic range and high precision to keep the output signals within the transmit spectral mask. This mostly-digital architecture without an up-conversion stage is essentially carrier-less, communicating at the baseband by sending out the digital synthesized waveforms. It takes the full advantage of the digital approach in waveform conditioning and adapts in a very short time. The nature of this radio lends itself to a digital implementation and promises power reduction through lower supply voltages and scaled geometries, as well as a more efficient and straight-forward transmitter design.

The advantages of the DWS transmitter are highlighted as follows:

• Digital combination of signals from multiple channels

- Software programmable or reconfigurable

- Full control of modulation schemes

## 2.4 Design Challenges on Digital/Analog Boundary

The bottleneck of this SDR-type transmitter is the digital-to-analog conversion stage. The wide bandwidth and high dynamic range requirements result in extreme stringent design specifications. In particular, the DAC speed and resolution become of utmost importance. To fulfill the Nyquist rate requirement, the sampling rate at DAC should be at least two times of the highest frequency component in the target synthesized signal frequency (Figure 2.11). Nyquist synthesis of the wider bandwidth requires the DAC clocking above GHz which may consume enormous amounts of power relative to our low power target. Additionally, the high-speed DAC may place severe limitations on jitter requirements. The power consumed in the wideband front-end stage as well as the necessary sensitivity and gain requirements for those blocks are also important. Finally, the area and power burden coming from digital signal processing and demodulation blocks must be considered.

Figure 2.11: Nyquist rate synthesis using the fundamental spectrum

High sampling rate and high linearity are the two critical requirements in D/A conversion for this architecture. For example, in TV band CR applications, the DAC sampling rate must be above 1.6GS/s for synthesizing a 800MHz signal. If the filter stage is considered, the DAC sampling rate will need to be increased even higher to relax the specifications for realistic

filter design. Nyquist rate synthesis imposes strict design requirements in DAC sampling rate and system complexity. Also, the DAC needs to have  $10 \sim 12$  bit resolution in order to support the modulation schemes in IEEE 802.22 or other standards.

To fulfill the Nyquist rate requirement, the sampling rate at DAC should be at least two times of the highest frequency component of the target synthesized signal frequency. A 10-bit DAC with 1.6GS/s with high SFDR (e.g. >60dB) is very challenging, even with state-of-the-art CMOS technology especially in low power applications. High-speed and high-linearity requirements result in high power consumption, high implementation cost and system complexity. This implies that the critical challenge is on the boundary of digital and analog. Our main objective is to investigate the technique of the digital-to-analog conversion for reducing the complexity of the signal processing blocks in the digital front-end.

In order to overcome the design specifications of Nyquist rate synthesis, a sub-Nyquist rate DWS transmitter is proposed as shown in Figure 2.12. It is similar to the conventional SDR-type transmitter but the synthesized digital waveform is directly converted by a high speed multi-mode sub-Nyquist rate DAC followed by a tunable band-pass filter.

Figure 2.12: Sub-Nyquist rate DWS transmitter architecture

The conceptual frequency domain response is shown in Figure 2.13. Instead of using the fundamental spectrum, the first image can be extracted by a bandpass filter for transmission, therefore, eliminating an up-conversion stage.

In this mostly digital transmitter, we propose to clock the DAC below the Nyquist rate and utilize the image spectrum. With the reduced sampling rate, it helps the transmitter avoid the complex high-speed DAC design and high power consumption. Figure 2.14 shows the concept of sub-Nyquist rate conversion and the utilization of image spectrum. Intuitively, this is the reciprocal of the sub-sampling receiver. The technique of sub-sampling is now moved to the digital-to-analog conversion stage at the transmitter side. In order to synthesize

Figure 2.13: Utilize the image spectrum

the signal for transmission in higher Nyquist zones, the sampling rate of the DAC and the fundamental spectrum need to be configured carefully based on the frequency plan.

Due to the nature of non-return-to-zero (NRZ) reconstruction in the DAC output, the SINC roll-off attenuate the image spectrum located in higher Nyquist zones. Also, the null frequencies at the multiples of the sample frequency create the dead zones which prohibit direct wideband synthesis across Nyquist zones. To overcome the attenuation and null frequencies of the SINC envelope, special techniques have to be used in the reconstruction stage.

The prior art of direct waveform generation using the harmonics/image spectrum can be found in [19, 20]. Both of these two examples use the same technique, return-to-zero, which effectively flattens the SINC envelope and moves null frequencies to the higher regions.

In the next chapter, we will review and analyze the NRZ and RZ techniques in the prior art as well as the proposed two-phase holding (TPH) reconstruction, which enables the multi-mode sub-Nyquist rate front end.

Figure 2.14: Sub-Nyquist rate digital-to-analog conversion

# Chapter 3

# Multi-Mode Sub-Nyquist Rate Digital-to-Analog Conversion

The previous chapter introduces the concept of direct waveform synthesis transmitter for TV band cognitive radio applications. Regarding the critical D/A conversion stage, the evolution of high-speed DACs in RF communication systems is driven by cost, power and performance. The state of the art DAC from Broadcom [27] demonstrates the possibility of implementing high-speed DACs above 2GS/s with high resolutions and high dynamic ranges. Other DACs [32–36] also show the good dynamic linearity performance over a wide output frequency range. Those advances and development, open the door to the direct generation of high bandwidth multi-carrier signals in communication systems. In this chapter, the signal reconstruction methods will first be reviewed. Then the proposed multi-mode sub-Nyquist rate conversion is introduced and discussed.

# 3.1 Analog Signal Reconstruction

#### 3.1.1 Non-Return-to-Zero

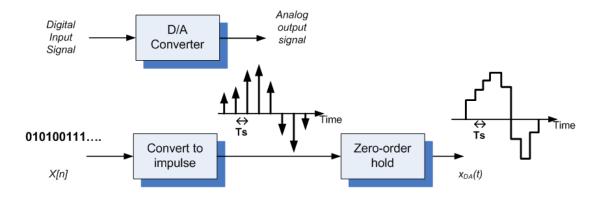

In the time domain, the DAC takes the discrete samples and converts them into electrical signals, either current or voltage. Then the DAC reconstructs the continuous-time signal by holding the electrical value until the end of this sample period. The operation can be written

as the discrete samples, x[n], convolving with the DAC output holding reconstruction pulse,  $h_0(t)$ :

$$I_{DAC}(t) = \sum_{n=-\infty}^{\infty} X[n]h_0(t - nT_S)$$

(3.1)

where Ts is the DAC sample period. Figure 3.1 illustrates the operation of D/A conversion.

Figure 3.1: The time domain operation on the boundary of digital and analog

The Fourier transform of the reconstructed output  $I_{DAC}(t)$  is

$$I_{DAC}(j2\pi f) = X(e^{j2\pi fT_s}) \cdot H_0(j2\pi f)$$

(3.2)

and

$$X(e^{j2\pi fT_s}) = \frac{1}{T_s} \left( \sum_{n=-\infty}^{\infty} X_a(j(2\pi f - \frac{2\pi n}{T_s})) \right)$$

(3.3)

$H_0(j2\pi f)$  is the frequency response of the reconstruction pulse. If Zero-Order-Hold (ZOH), also known as Non-Return-To-Zero (NRZ), is chosen, the response of  $H_0(j2\pi f)$  is easily shown to be  $H_{NRZ}(j2\pi f)$ .

$$H_{NRZ}(j2\pi f) = \frac{2sin(\pi f T_s)}{2\pi f} e^{-j2\pi f T_s/2} = SINC(f \times T_s)e^{-j2\pi f T_s/2}$$

(3.4)

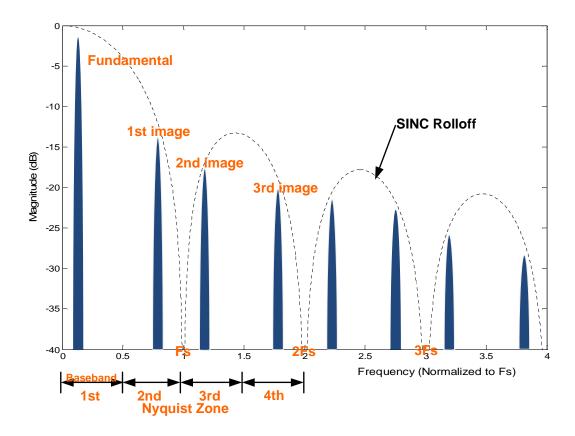

The spectral characteristic is shown in Figure 3.2 where the terms annotated here are defined in [37]. The DAC output reconstructed by NRZ has the SINC envelope in the frequency domain. Mathematically, the spectral characteristic of DAC outputs without

Figure 3.2: The frequency domain response of NRZ reconstruction

quantization noise is the SINC function multiplying the continuous-time baseband spectrum located around the multiples of Fs.

$$I_{DAC}(j2\pi f) = \frac{1}{T_s} \left( \sum_{n=-\infty}^{\infty} X_a(j(2\pi f - \frac{2\pi n}{T_s})) \right) H_{NRZ}(j2\pi f)$$

(3.5)

As mentioned in the previous chapter, the SINC roll-off should be taken into account if sub-Nyquist rate conversion and the image spectrum are used for direct waveform generation. In the following section, we will review the return-to-zero technique for its applications in wideband synthesis.

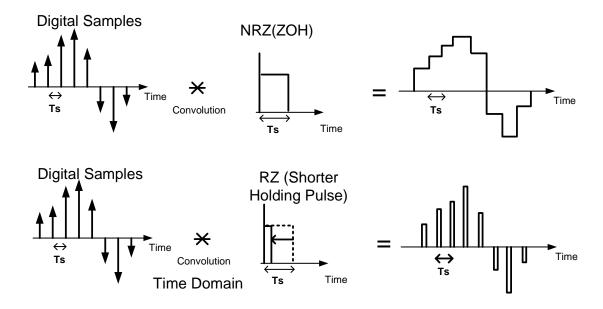

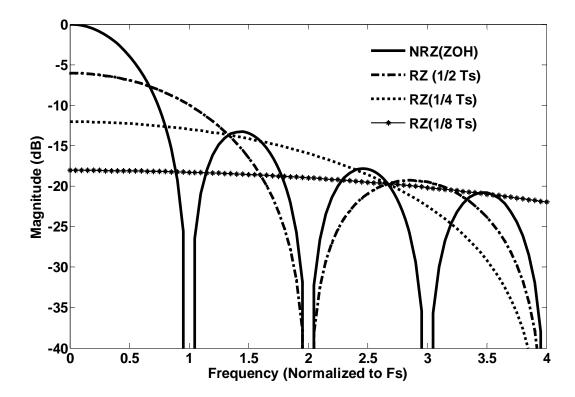

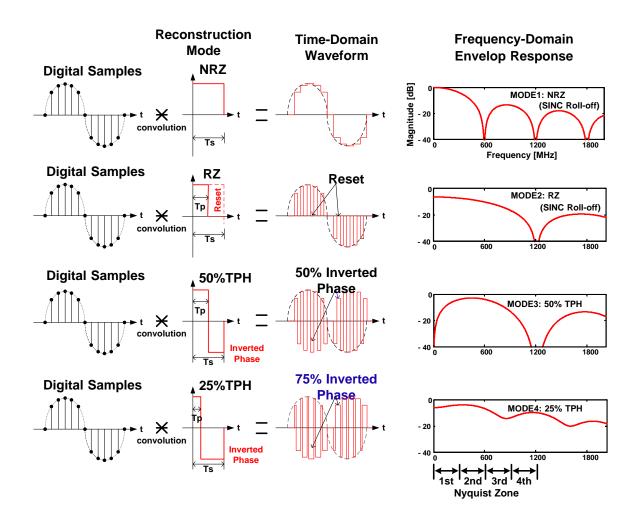

#### 3.1.2 Return-to-Zero

To flatten the SINC roll-off, one of the possible solutions is to reduce the holding period of the DAC output. This leads to the well-known Return-to-Zero (RZ) techniques in signal reconstruction at the DAC's outputs [19,20]. Figure 3.3 shows the time domain operation of RZ. The output is reset every other half clock cycle. The output is similar to the conventional NRZ DAC, except that the output pulses only have half the width and the first null frequency is pushed at 2 Fs.

Figure 3.3: The time domain operation of NRZ and RZ

For a shorter holding pulse, the frequency response of the holding pulse  $H_{RZ}(j2\pi f)$  is easily shown to be:

$$H_{RZ}(j2\pi f) = \frac{T_p}{T_s} SINC(f \times T_s) e^{-j2\pi f T_p/2}$$

(3.6)

where  $T_p$  is the holding pulse width and  $T_p/T_s$  is the magnitude scaling factor.

By reducing the width of the holding pulse,  $T_p$ , the null frequencies are moved to higher frequencies. For example, if the holding pulse is reduced to 1/4 of the original period, the null frequencies are pushed to the frequency four times higher. Figure 3.4 shows the effect of holding pulses with different duty cycles. The SINC roll-off is flattened due to the null frequency being pushed to higher frequencies. However, the magnitude of the fundamental

Figure 3.4: NRZ and RZ with various duty cycles

spectrum and its images is attenuated because the shorter holding pulse contributes less signal energy. RZ flattens the response and delivers more power around the second and third Nyquist zones. But the attenuated signal strength significantly impacts the performance of the transmitter. The reconstruction process of NRZ or RZ can be viewed as a filter function for shaping the spectrum envelope. NRZ and RZ are two common types of reconstruction processes due to the simplicity of hardware implementation.

RZ technique is used for direct wideband signal generation. In [19], a 1.2 GS/s DAC demonstrated direct waveform generation for four 5MHz WCDMA signal in 900MHz by using the first image spectrum. In [20], the same technique is applied to demonstrate the RZ technique for multiple Nyquist zone operation.

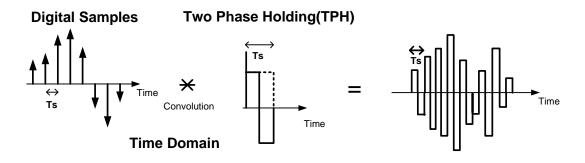

## 3.2 Proposed Two-Phase Holding

After discussing the NRZ and RZ techniques in the previous section, the two-phase holding (TPH) reconstruction is proposed to shape the spectrum envelope more aggressively in this work. As illustrated in Figure 3.5, the sample period is divided into two phases. In the first phase, the DAC takes the digital sample and holds for  $T_p$ . In the second phase, the DAC produces the inverted version of the digital sample in the output for  $T_s - T_p$ .

Figure 3.5: The time domain operation of TPH

The frequency response of two-phase holding (TPH) can be expressed as the following equation:

$$H_{TPH}(j2\pi f) = \frac{T_p}{T_s} sinc(f \times T_s) e^{-j2\pi f T_p/2} + \frac{T_s - T_p}{T_s} sinc(f \times (T_s - T_p)) e^{-j2\pi f (T_s + T_p)/2}$$

(3.7)

As shown in this example, the output holding pulse has two phases and each phase is half of the clock period. The output alternates between the original and inverted samples. Because the inverted phase provides signal energy into the analog output waveform instead of resetting in the second phase, the magnitude of the output image spectrum is enhanced. The TPH operation can be viewed as the superposition of one RZ operation and the other time-shifted and inverted RZ operation.

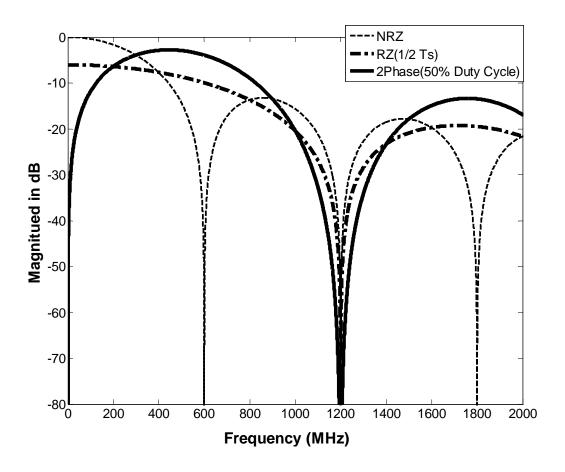

Intuitively, the frequency response of this two-phase operation is a high-pass response by nature since the DC is zero. The spectrum envelope is shifted to higher frequencies. Especially, the signal is enhanced significantly around the sampling frequency Fs. More signal energy is directed to have higher signal gain around the second and third Nyquist zones in comparison with NRZ or RZ operation. By manipulating the sampling rate and the holding pulse period, the spectrum envelope can be configured to achieve a better flat

response with minimum attenuation over the target bands. Figure 3.6 shows the envelopes of TPH reconstruction. As we can see that TPH mode creates a better response covering  $400 \mathrm{MHz} \sim 800 \mathrm{MHz}$  than that of NRZ or RZ mode. This frequency range is where the major TV white spaces locate.

Figure 3.6: Two phase holding with 50% duty cycle

# 3.3 Variable Duty-Cycled Two-Phase Holding

We can further control the duty cycle of two phases so that the spectrum envelope is shaped to enhance different Nyquist zones. Figure 3.7 shows an example of the 25% duty cycle with two-phase operation. This operation provides more energy in high-frequency band in the fourth and the fifth Nyquist zones, around 1000 to 1400 MHz. Without 25% TPH,

this region is highly attenuated in NRZ and RZ and 50% TPH modes due to the location of null frequencies.

It is possible to utilize higher order image spectrum for direct waveform synthesis since the spectrum envelope is shaped into a wider range in the 25% duty cycle TPH mode. This operation provides an opportunity in using even high order harmonics/image spectrum like the fourth or the fifth Nyquist zone.

Figure 3.7: Two phase holding with 25% duty cycle

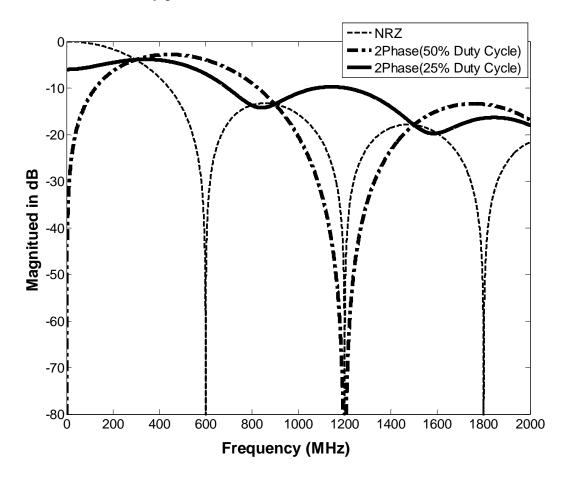

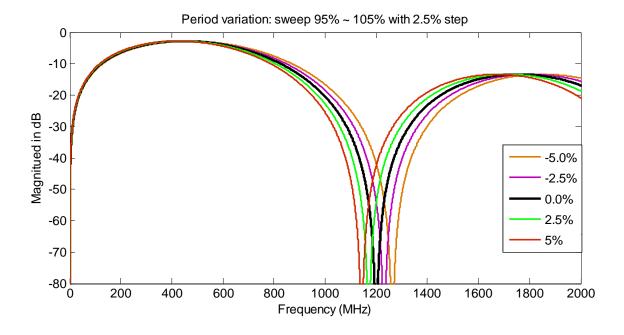

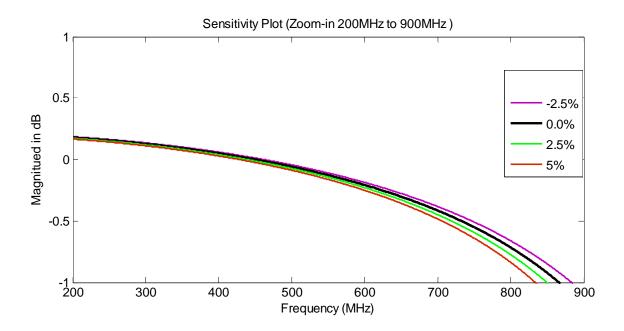

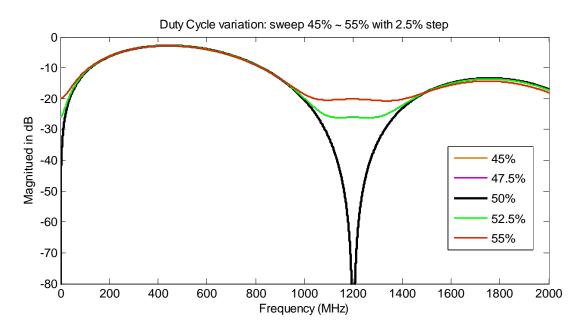

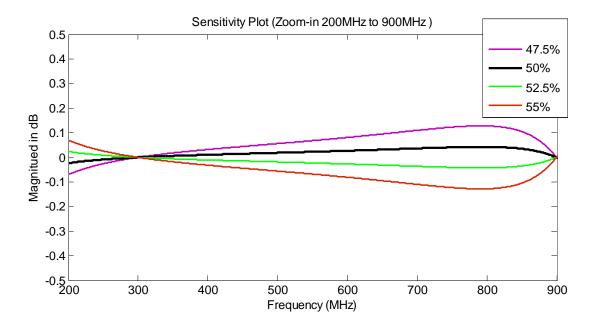

The sensitivity of the duty cycle variation and sampling period variation is analyzed by the system-level simulation in Matlab. The effect of the sampling period variation,  $\pm 5\%$ , is shown in Figure 3.8. Clearly, the variation of the sampling period effectively moves the location of the nulls around the multiple of the sampling frequency. Also the magnitude response has less than 0.3 dB deviation from the nominal response from 200MHz to 900MHz.

The effect of the duty cycle variation,  $\pm 5\%$ , is shown in Figure 3.9. If the duty cycle of the

Figure 3.8: Two phase holding with period variation

two phase is not ideal 50%, the original and inverted samples won't be able to canceled out perfectly. So the envelope does not have the deep notches around the multiple of the sampling

frequency. Also the magnitude response deviates less than  $0.15~\mathrm{dB}$  from the nominal response from  $200\mathrm{MHz}$  to  $900\mathrm{MHz}$ .

Figure 3.9: Two phase holding with duty cycle variation

# 3.4 Multi-mode Sub-Nyquist Rate Conversion