# **UC Irvine**

# **UC Irvine Electronic Theses and Dissertations**

# **Title**

Holey Silicon and Through Silicon Vias for Thermal Management of Next-Generation Electronic Systems

# **Permalink**

https://escholarship.org/uc/item/72v118tn

#### **Author**

Ren, Zongqing

# **Publication Date**

2021

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

Holey Silicon and Through Silicon Vias for Thermal Management of Next-Generation Electronic Systems

# **DISSERTATION**

submitted in partial satisfaction of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

in Mechanical and Aerospace Engineering

by

Zongqing Ren

Dissertation Committee: Associate Professor Jaeho Lee, Chair Professor Yun Wang Professor Nader Bagherzadeh

# **DEDICATION**

To

my parents, family

in recognition of their love and support

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                      | Page |

|----------------------------------------------------------------------------------------------------------------------|------|

| LIST OF TABLES                                                                                                       | vii  |

| LIST OF TABLES                                                                                                       | VII  |

| ACKNOWLEDGMENTS                                                                                                      | ix   |

| VITA                                                                                                                 | X    |

| ABSTRACT OF THE DISSERTATION                                                                                         | xii  |

| CHAPTER 1: INTRODUCTION                                                                                              | 1    |

| 1.1 Thermal Management Challenges for Advanced Electronics                                                           | 1    |

| 1.2 Thermoelectric Cooling Devices                                                                                   | 4    |

| 1.2.1 Introduction to the thermoelectric effect                                                                      | 4    |

| 1.2.2 Thermoelectric cooling devices for hot spot management                                                         | 5    |

| 1.3 Silicon-based Thermoelectric Materials                                                                           | 12   |

| 1.3.1 Size effect in silicon                                                                                         | 12   |

| 1.3.2 Thermoelectric properties of holey silicon                                                                     | 13   |

| 1.4 Outline of Doctoral Research                                                                                     | 18   |

| CHAPTER 2: Thermal Conductivity Anisotropic in Holey Silicon Nanostructures and Its Impact on Thermoelectric Cooling | 20   |

| 2.1 Introduction                                                                                                     | 21   |

| 2.2 Analytical and Numerical Modeling Methods                                                                        | 22   |

| 2.2.1 Cross-plane and in-plane thermal transport in holey silicon                                                    | 22   |

| 2.2.2 Numerical simulations of the on-chip cooling system                                                            | 25   |

| 2.3 Results and Discussion                                                                                           | 27   |

| 2.3.1 Thermal and electrical properties of holey silicon                                                             | 27   |

| 2.3.2 Effects of micro-cooler size and substrate thickness                                                           | 30   |

| 2.3.3 Effects of thermal conductivity anisotropy                                                                     | 31   |

| 2.3.4 Effects of lateral substrate size                                                                              | 32   |

| 2.4 Conclusions                                                                                                      | 34   |

| CHAPTER 3: TSV-integrated Thermoelectric Cooling by Holey Silicon for Hot Spot Thermal Management                    | 35   |

| 3.1 Introduction                                                                                                     | 36   |

| 3.2 Analytical Models for Cross-plane and In-plane Thermal Transport in Au-filled Holey Silicon                                | 37 |

|--------------------------------------------------------------------------------------------------------------------------------|----|

| 3.3 Finite-element Simulations of TEC Systems                                                                                  | 40 |

| 3.4 Results and Discussion                                                                                                     | 43 |

| 3.4.1 Thermal and electrical properties of holey silicon and Au-filled holey silicon                                           | 43 |

| 3.4.2 Effects of TSV on the TEC designs for on-state and off-state conditions                                                  | 46 |

| 3.4.3 Effects of the substrate on the TSV-inserted TEC designs for on-state and off-state conditions                           | 49 |

| 3.5 Conclusions                                                                                                                | 50 |

| CHAPTER 4: Transient Cooling and Heating Effects in Holey Silicon-based Thermoelectric Devices for Hot Spot Thermal Management | 52 |

| 4.1 Introduction                                                                                                               | 52 |

| 4.2 Simulation of Holey Silicon-based Thermoelectric Cooler for On-chip Hot Spots                                              | 55 |

| 4.2.1 Numerical modeling of transient thermoelectric cooling                                                                   | 55 |

| 4.2.2 Thermoelectric properties of holey silicon                                                                               | 58 |

| 4.3 Results and Discussion                                                                                                     | 60 |

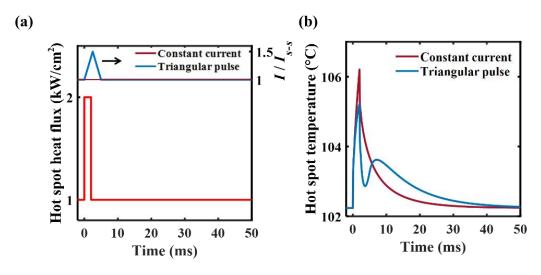

| 4.3.1 Effects of the Thomson coefficient                                                                                       | 62 |

| 4.3.2 Effects of current pulse shapes and consecutive pulses                                                                   | 64 |

| 4.3.3 Effects of current pulse amplitudes and durations                                                                        | 68 |

| 4.3.4 Effects of phase change materials                                                                                        | 71 |

| 4.4 Conclusions                                                                                                                | 75 |

| CHAPTER 5: Experimental Demonstration of Holey Silicon-based Thermoelectric Coolers                                            | 76 |

| 5.1 Introduction                                                                                                               | 76 |

| 5.2 Holey Silicon-based thermoelectric cooler Development                                                                      | 78 |

| 5.2.1 Design of the holey silicon-based thermoelectric cooler                                                                  | 78 |

| 5.2.2 Fabrication recipes of the holey silicon-based thermoelectric cooler                                                     | 79 |

| 5.3 Measurement of the Holey Silicon-based thermoelectric cooler                                                               | 81 |

| 5.4 Results and Discussion                                                                                                     | 83 |

| 5.4.1 Characterization of the fabricated holey silicon                                                                         | 83 |

| 5.4.2 Steady-state performance of the holey silicon-based thermoelectric cooler                                                | 84 |

| 5.4.3 Transient performance of the holey silicon-based thermoelectric cooler                                                   | 87 |

| 5.5 Conclusions                                                                                                                | 90 |

| CHAPTER 6: Thermal TSV Optimization and Hierarchical Floorplanning for 3D Integrated Circuits                                  | 91 |

| 6.1 Introduction                                                                  | 91  |

|-----------------------------------------------------------------------------------|-----|

| 6.2 System-level Simulation and Power Consumption for the 3D Nehalem              | 94  |

| 6.3 Thermal Characterization and Modeling for the 3-D Nehalem and TSVs            | 97  |

| 6.3.1 Thermal modeling of the 3-D Nehalem                                         | 97  |

| 6.3.2 Analytical models for the TSV unit cell                                     | 100 |

| 6.4 TTSV Placement Optimization and Hierarchical Floorplanning for the 3D Nehalem | 102 |

| 6.4.1 Optimization flow                                                           | 103 |

| 6.4.2 Problem formation for floorplan optimization                                | 105 |

| 6.4.3 Simulated annealing-based optimization algorithm                            | 107 |

| 6.4.4 Multilevel core arrangement for the 3D Nehalem                              | 110 |

| 6.5 Results and Discussion                                                        | 113 |

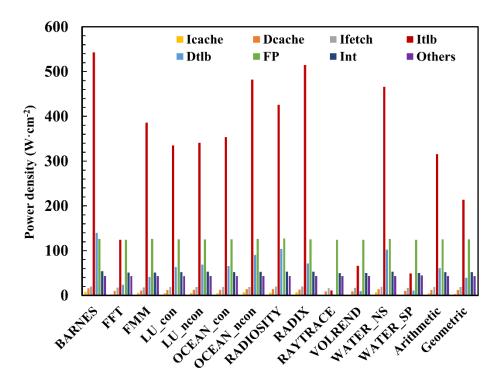

| 6.5.1 Power density of the 3D Nehalem running Splash-2 benchmarks                 | 114 |

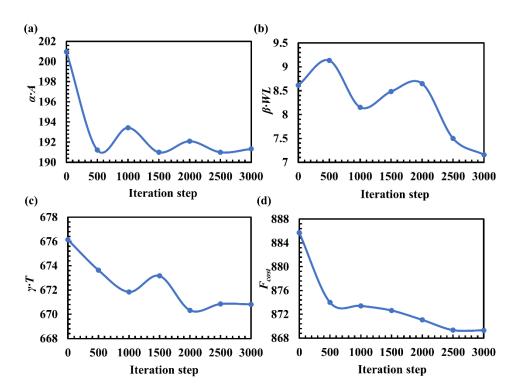

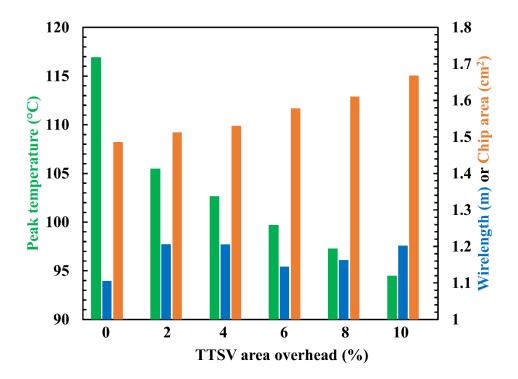

| 6.5.2 Trade-off in area, wirelength, and peak temperature                         | 115 |

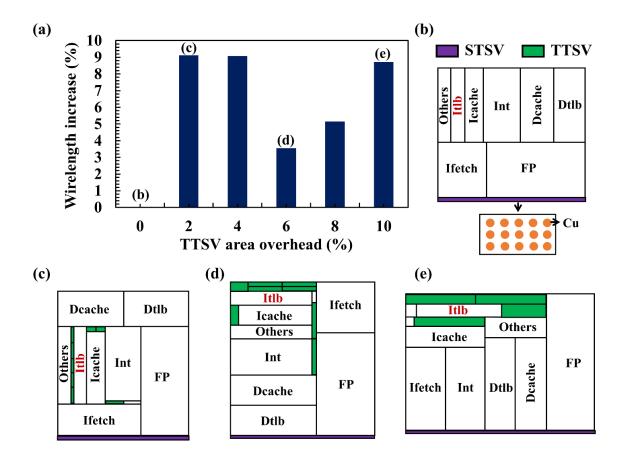

| 6.5.3 Impact of TTSVs on wirelength of the 3D Nehalem                             | 116 |

| 6.5.4 Impact of TTSVs on the peak temperature of the 3D Nehalem                   | 118 |

| 6.6 Conclusions                                                                   | 123 |

| CHAPTER 7 Conclusions and Suggestions                                             | 124 |

| 7.1 Summary                                                                       | 124 |

| 7.2 Suggestions for Future Works                                                  | 126 |

| 7.2.1 Holey silicon-based thermoelectric cooler for dynamic hot spots             | 127 |

| 7.2.2 Experimental demonstration of holey silicon-based TEC for hot spot cooling  | 128 |

| 7.2.3 Signal-ground TSV pair optimization                                         | 129 |

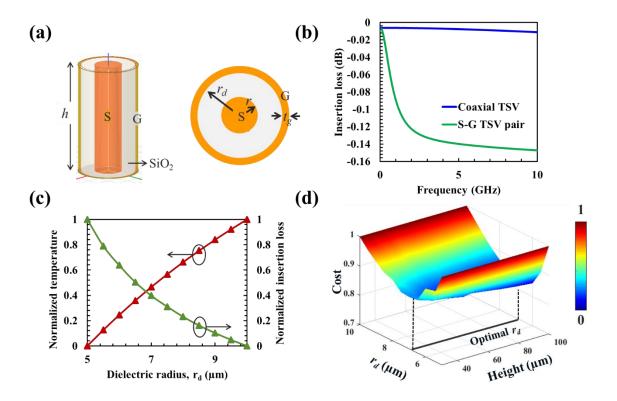

| 7.2.4 Coaxial TSV optimization                                                    | 131 |

| References                                                                        | 133 |

| Appendix A: Microfabrication Recipes of Holey Silicon-based TECs                  | 147 |

# LIST OF FIGURES

|             |                                                                                                                                                 | Page |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

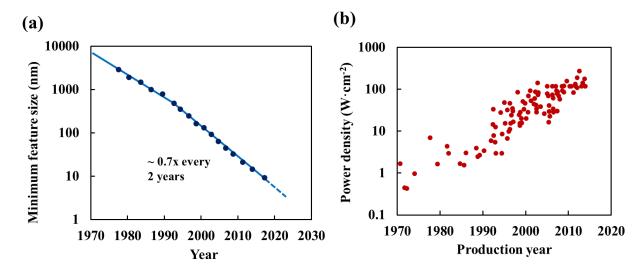

| Figure 1.1  | The scaling trends of the minimum feature size of transistors and power densities of commercial processors                                      | 2    |

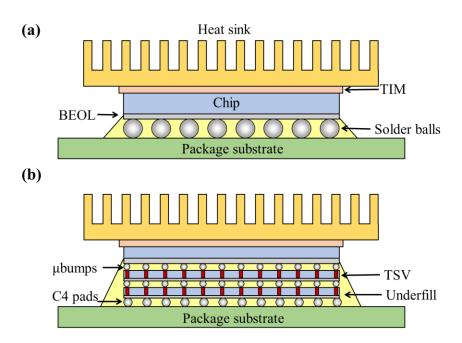

| Figure 1.2  | The package structure of 2D and 3D ICs                                                                                                          | 3    |

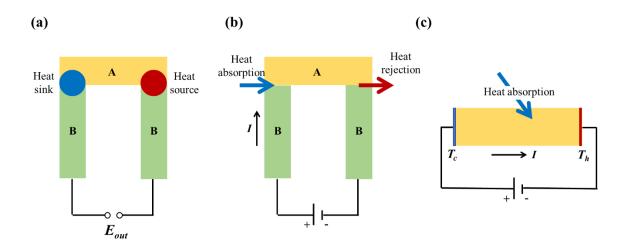

| Figure 1.3  | Schematics of the Seebeck, Peltier, and Thomson effects                                                                                         | 5    |

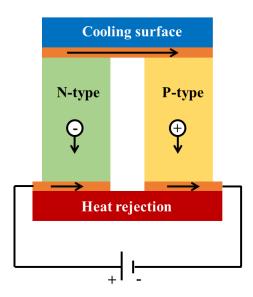

| Figure 1.4  | The basic schematic of a TEC with n- and p-type legs                                                                                            | 6    |

| Figure 1.5  | Schematics of the micro-contact TEC                                                                                                             | 7    |

| Figure 1.6  | Schematics of the SiGeC/Si-, superlattice-, and SiGe-based TECs                                                                                 | 9    |

| Figure 1.7  | SEM image of the Si-based micro-cooler and its application for hot spot cooling                                                                 | 10   |

| Figure 1.8  | Photograph of the Si-based micro-cooler and IR images for the on and off states                                                                 | 11   |

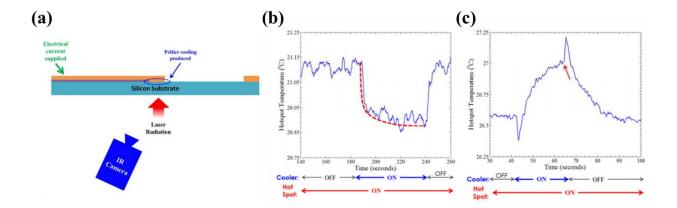

| Figure 1.9  | Schematic of the test setup of Si-based micro-cooler and the time-<br>dependent hot spot temperature                                            | 12   |

| Figure 1.10 | SEM image and thermoelectric properties of 23 nm neck size holey Si                                                                             | 15   |

| Figure 1.11 | Holey Si cross-plane SEM and thermal conductivity data                                                                                          | 16   |

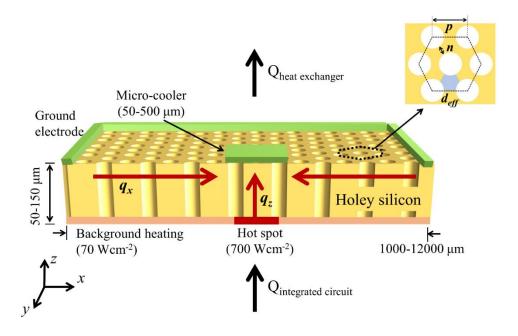

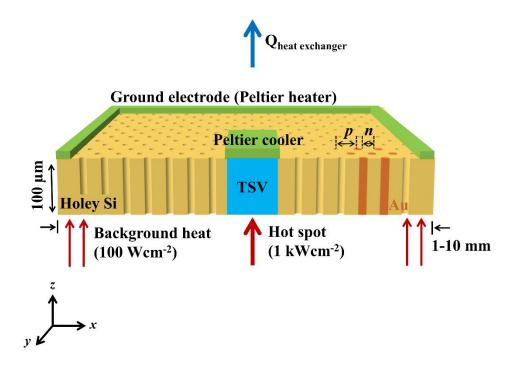

| Figure 2.1  | Schematic of holey Si-based TEC for hot spot cooling                                                                                            | 27   |

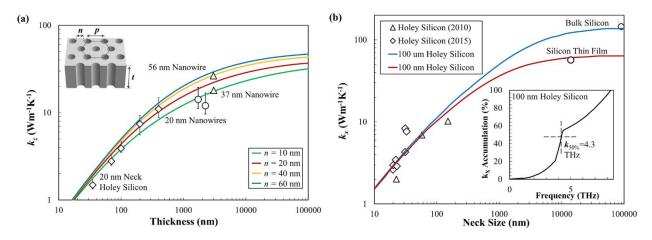

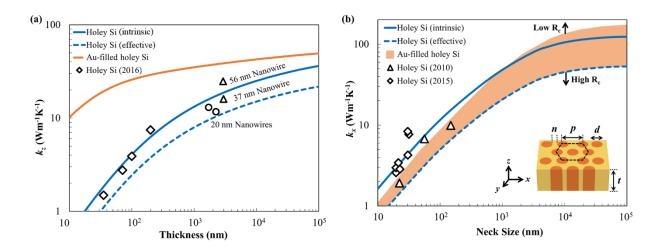

| Figure 2.2  | Cross- and in-plane thermal conductivity modeling of holey Si                                                                                   | 29   |

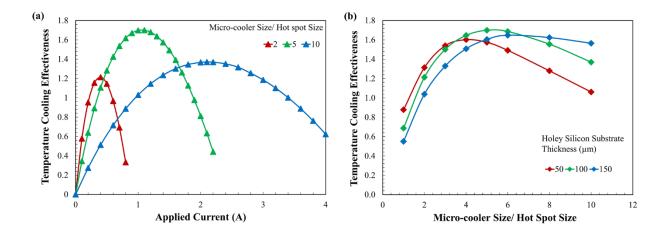

| Figure 2.3  | Temperature cooling effectiveness changes with current and dimensions                                                                           | 31   |

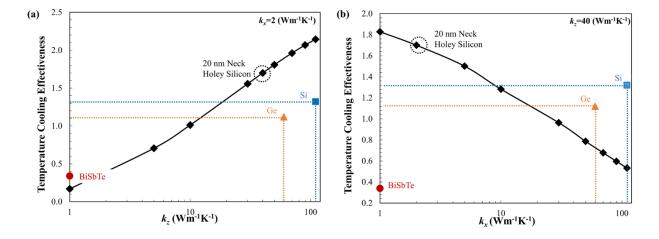

| Figure 2.4  | Temperature cooling effectiveness changes with in- and cross-plane thermal conductivities                                                       | 32   |

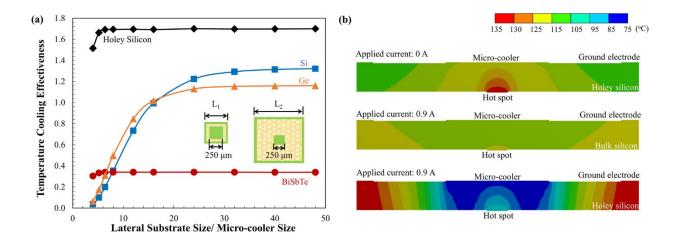

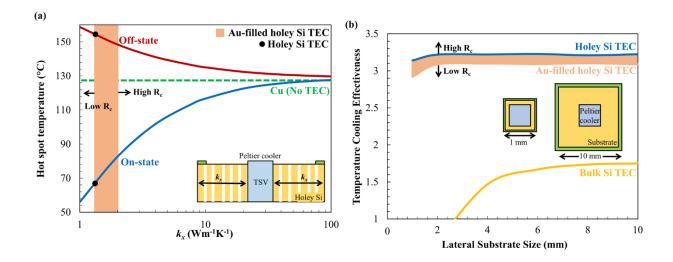

| Figure 2.5  | Temperature cooling effectiveness changes with lateral substrate size and cross-sectional temperature profiles of holey- and bulk Si-based TECs | 34   |

| Figure 3.1  | Schematic of TSV-inserted holey Si-based TEC for hot spot cooling                                                                               | 42   |

| Figure 3.2  | Cross- and in-plane thermal conductivity modeling of Au-filled holey Si                                                                         | 45   |

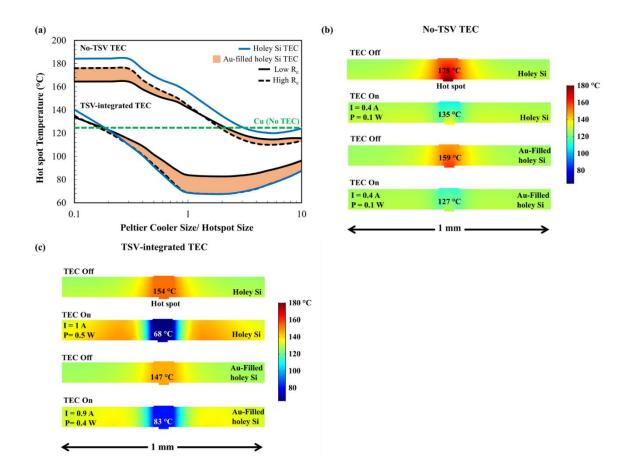

| Figure 3.3  | Hot spot temperature and temperature profiles of holey Si and Au-filled holey Si TECs with and without TSV                                      | 48   |

| Figure 3.4  | Hot spot temperature change with in-plane thermal conductivity and<br>temperature cooling effectiveness change with lateral substrate size      | 50   |

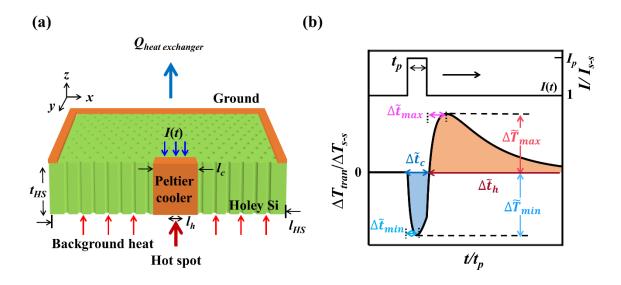

| Figure 4.1  | Schematic of holey Si TEC and transient hot spot temperature change                                                                             | 58   |

| Figure 4.2  | Temperature-dependent thermoelectric properties of 45 nm neck holey Si                                                                          | 60   |

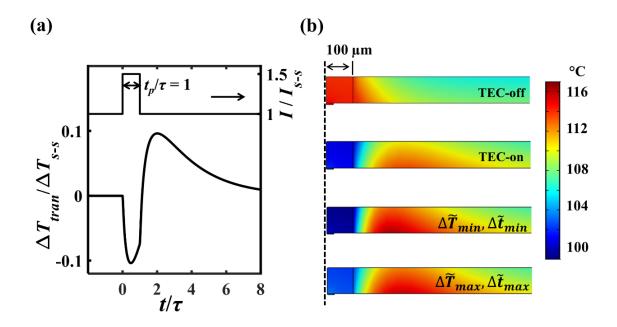

| Figure 4.3  | Hot spot temperature change with current pulse and temperature profiles                                                                         | 62   |

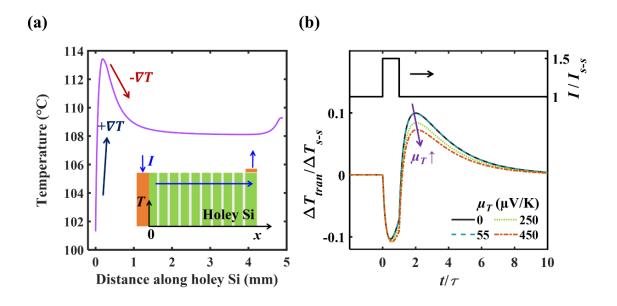

| Figure 4.4  | Temperature distribution in holey Si TEC and impact of the Thomson coefficient                                                                  | 64   |

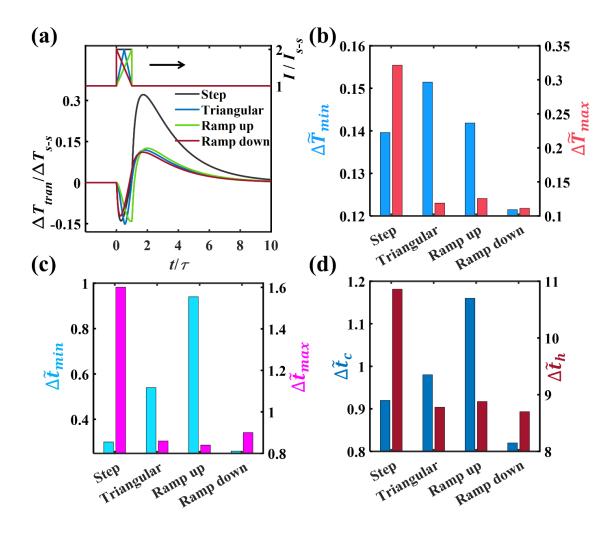

| Figure 4.5  | Impact of the current pulse shape                                                                                                               | 66   |

| Figure 4.6  | Impact of the consecutive current pulse                                                                                                         | 67   |

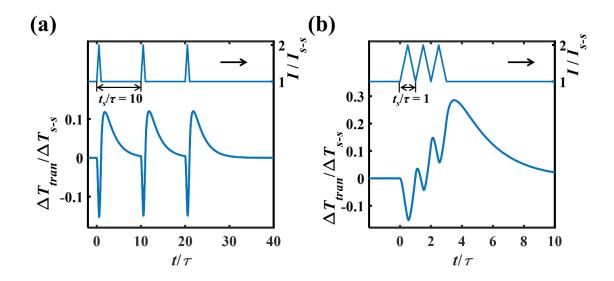

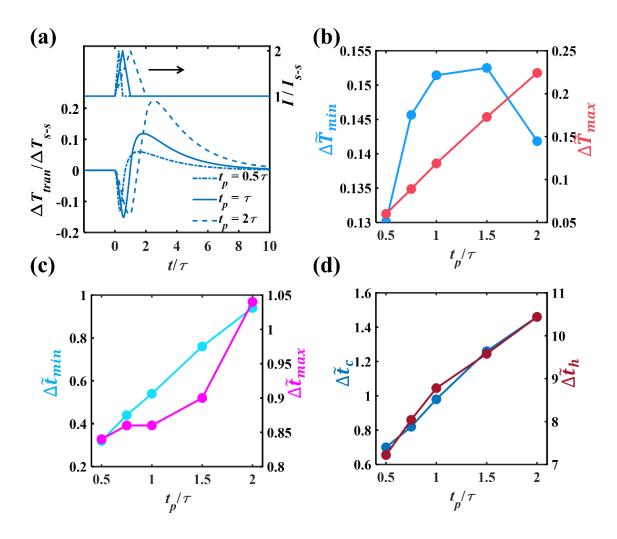

| Figure 4.7  | Impact of the current pulse amplitude                                                                    | 69  |

|-------------|----------------------------------------------------------------------------------------------------------|-----|

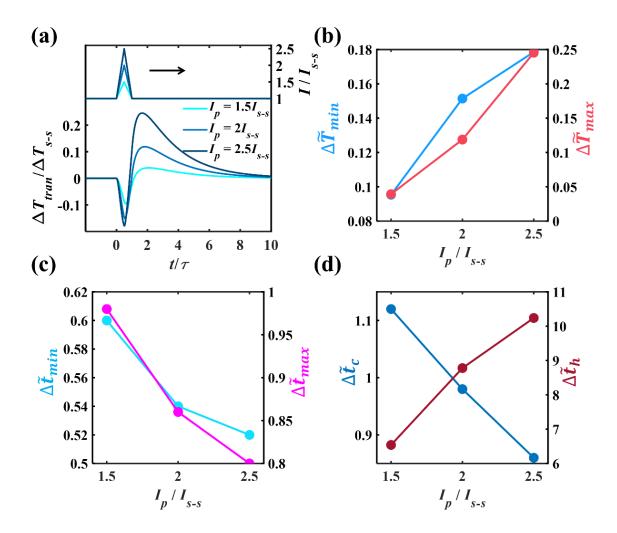

| Figure 4.8  | Impact of the current pulse duration                                                                     | 71  |

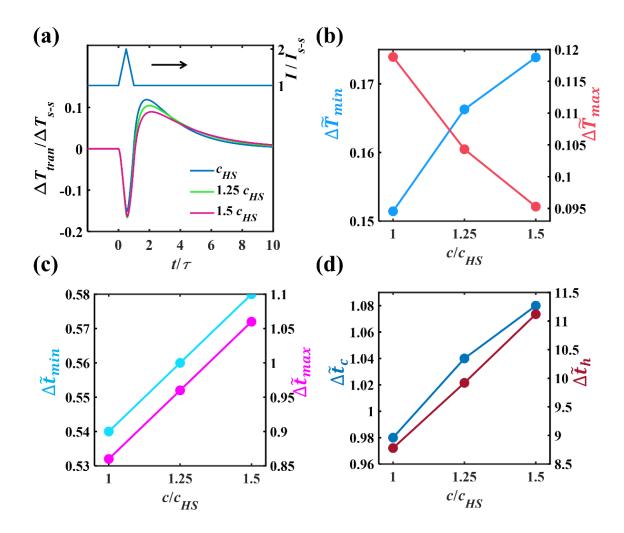

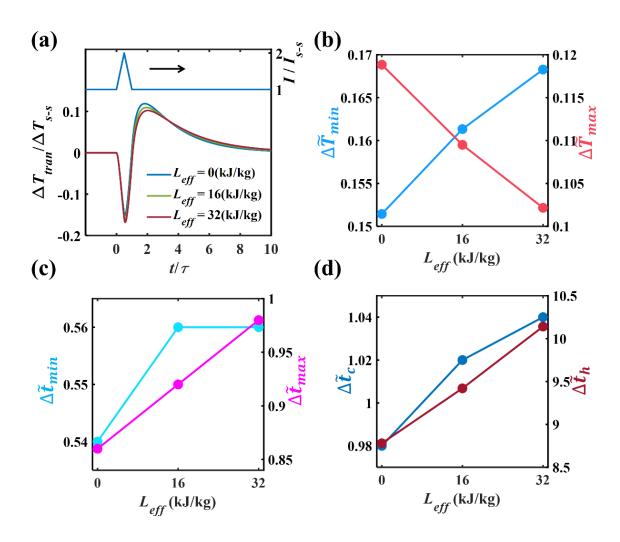

| Figure 4.9  | Impact of the filler volumetric heat                                                                     | 73  |

| Figure 4.10 | Impact of the filler latent heat                                                                         | 74  |

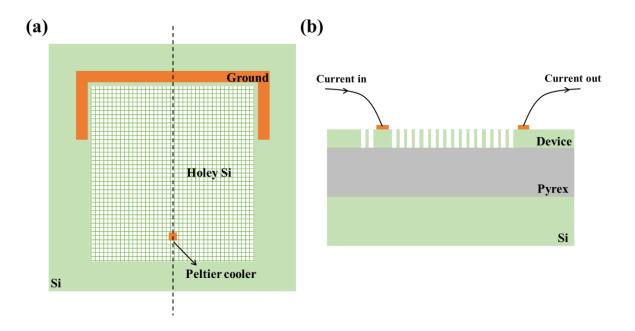

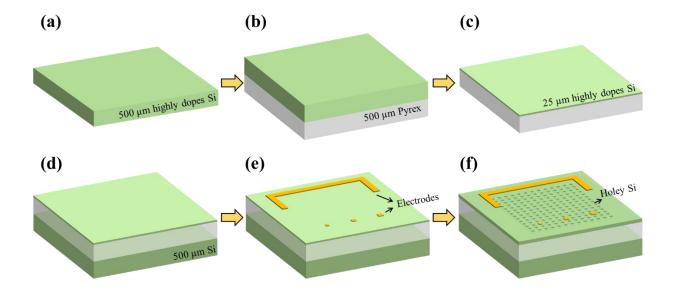

| Figure 5.1  | Schematics of the holey silicon-based TEC design                                                         | 79  |

| Figure 5.2  | The fabrication process of the holey silicon-based TEC                                                   | 81  |

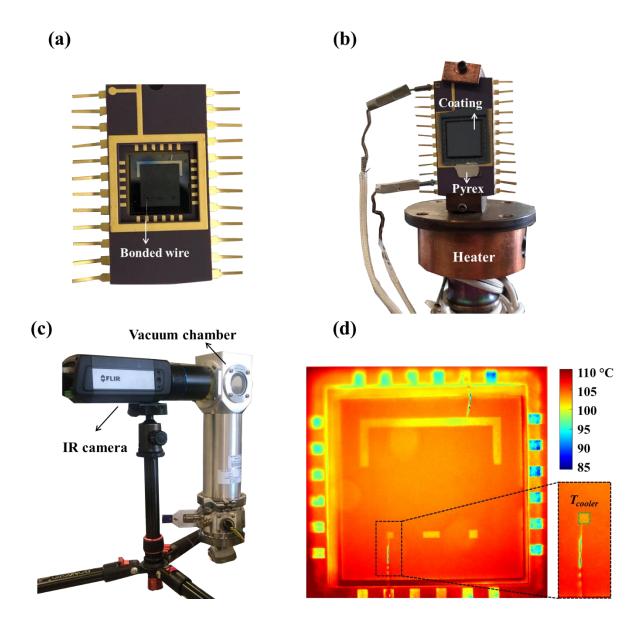

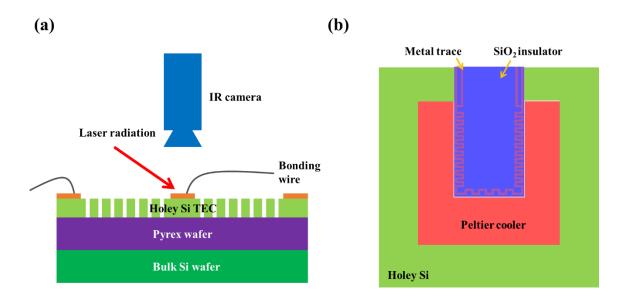

| Figure 5.3  | IR measurement setup for the holey silicon-based TEC                                                     | 83  |

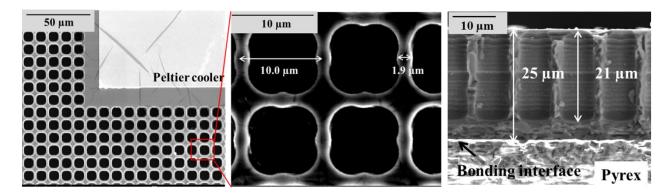

| Figure 5.4  | SEM characterization of the holey silicon-based TEC                                                      | 84  |

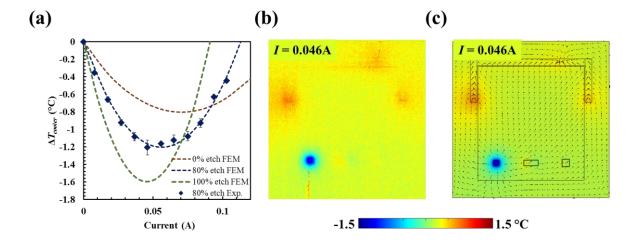

| Figure 5.5  | The cooler temperature change of the holey silicon-based TEC at 100 °C                                   | 86  |

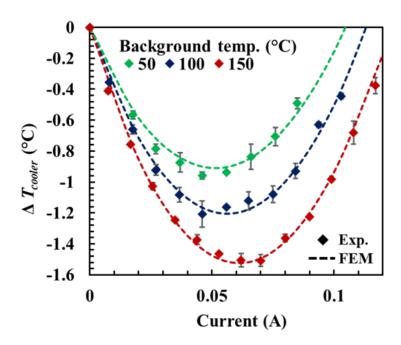

| Figure 5.6  | Cooler temperature change with different background temperatures                                         | 87  |

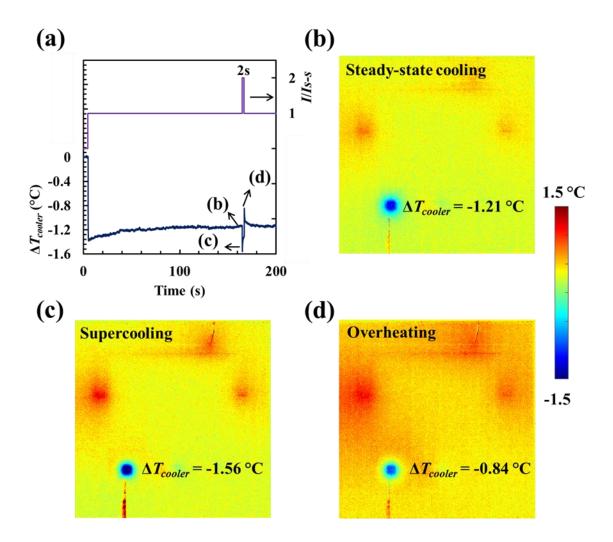

| Figure 5.7  | Demonstration of the transient supercooling                                                              | 88  |

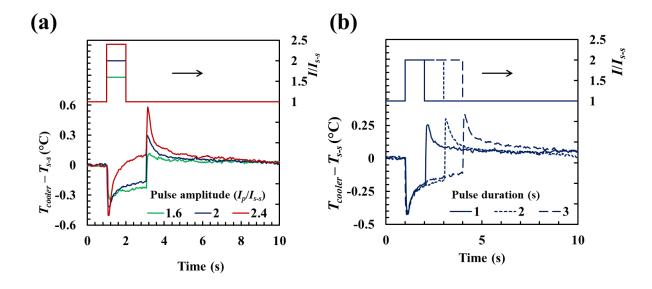

| Figure 5.8  | Impacts of current amplitude and duration                                                                | 89  |

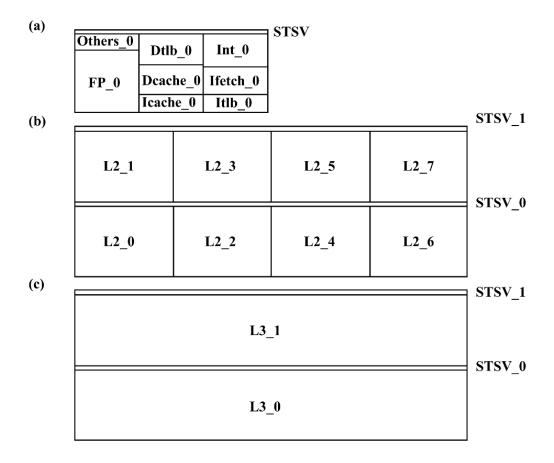

| Figure 6.1  | Floorplan of the 3D Nehalem                                                                              | 96  |

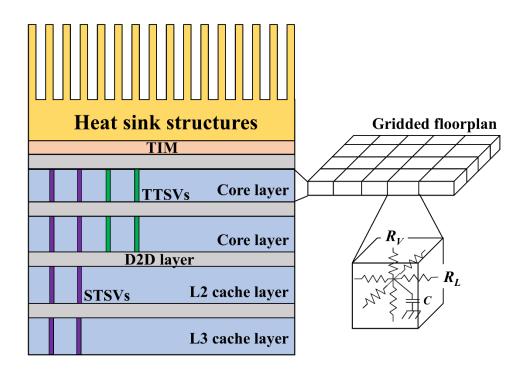

| Figure 6.2  | Schematic of the 3D Nehalem                                                                              | 98  |

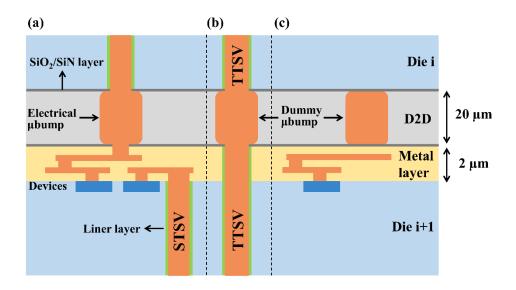

| Figure 6.3  | Schematic of the Si die, D2D layer, and the metal layer                                                  | 99  |

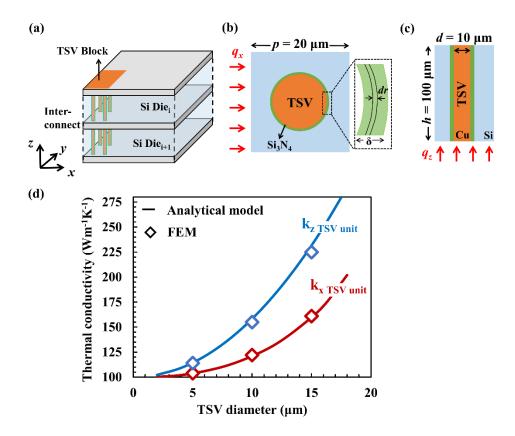

| Figure 6.4  | Schematic of the TSV block                                                                               | 102 |

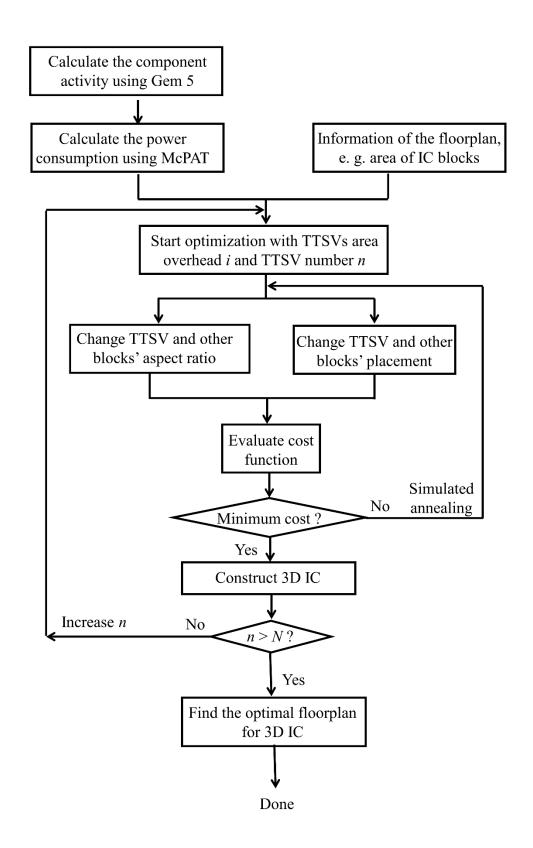

| Figure 6.5  | The floorplan optimization flow for the 3D Nehalme                                                       | 104 |

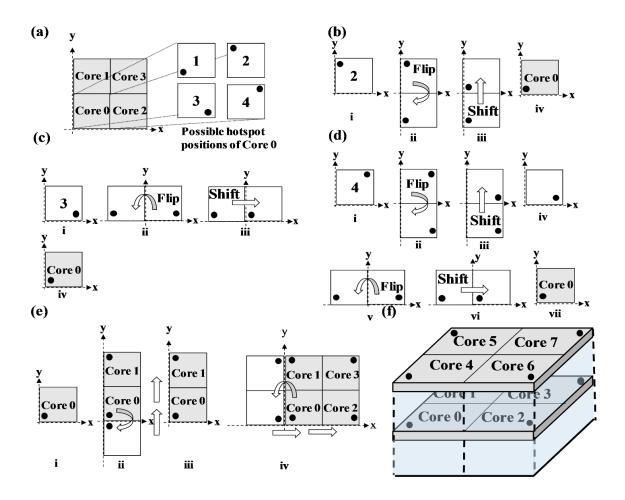

| Figure 6.6  | Schematic of the algorithm to generate the core layer floorplan                                          | 113 |

| Figure 6.7  | Power consumption of the Splash-2 benchmarks for each IC block                                           | 114 |

| Figure 6.8  | Convergence processes for area, wirelength, and peak temperature                                         | 115 |

| Figure 6.9  | The total chip area, wirelength, and peak temperature change with different TTSV area overheads          | 116 |

| Figure 6.10 | The wirelength change with different TTSV area overheads                                                 | 117 |

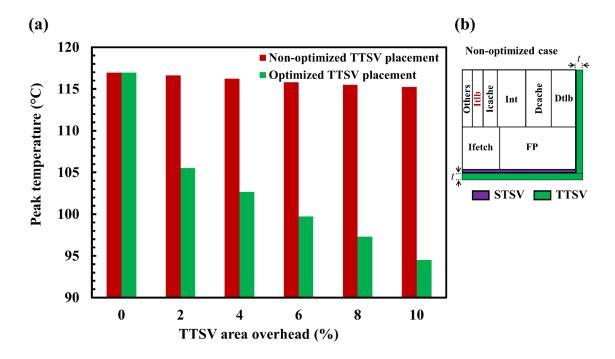

| Figure 6.11 | The peak temperature change of the 3D Nehalem with/without TTSV placement optimization                   | 119 |

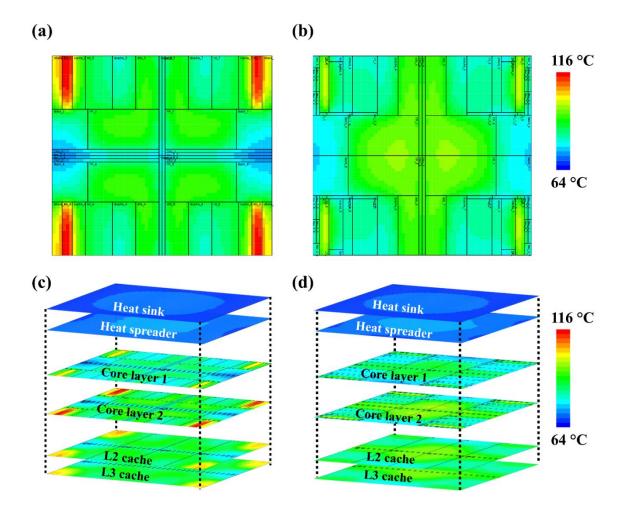

| Figure 6.12 | Temperature profiles of the 3D Nehalem with/without TTSV placement optimization at 6% TTSV area overhead | 121 |

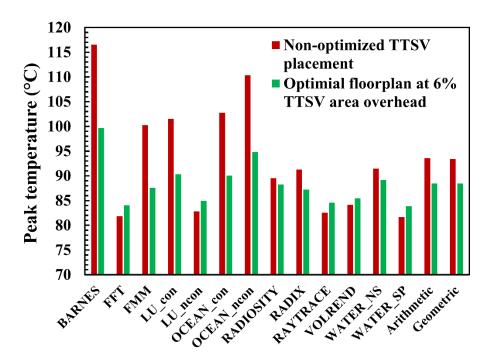

| Figure 6.13 | Peak temperature comparison of optimized and non-optimized 3D<br>Nehalem running Splash-2 benchmarks     | 122 |

| Figure 7.1  | Transient supercooling of holey silicon-based TEC for a dynamic hot spot                                 | 127 |

| Figure 7.2  | Experimental setup of holey silicon-based TEC for local hot spots                                        | 129 |

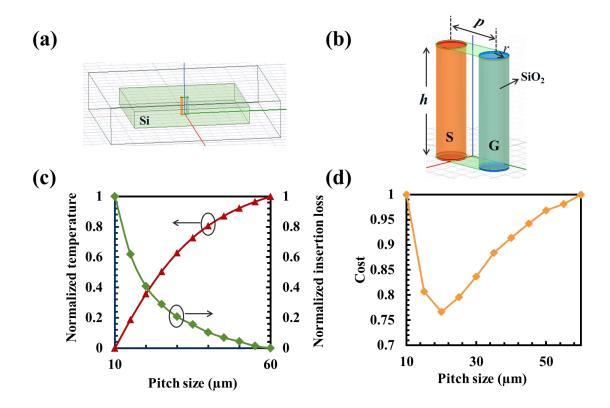

| Figure 7.3  | Thermal and electrical performance of signal-ground TSV pair                                             | 131 |

| Figure 7.4  | Thermal and electrical performance of coaxial TSV                                                        | 132 |

# LIST OF TABLES

|           |                                                            | Page |

|-----------|------------------------------------------------------------|------|

| Table 6.1 | 3D Nehalem parameters                                      | 97   |

| Table 6.2 | Properties and dimensions of the 3D Nehalem components     | 100  |

| Table 6.3 | Wire density for different IC blocks of the 3D Nehalem     | 107  |

| Table 6.4 | Simulated annealing parameters                             | 110  |

| Table 7.1 | Material properties and structure dimensions for the 3D IC | 130  |

# **ACKNOWLEDGEMENTS**

I would like to express my deepest appreciation to my committee chair, Professor Jaeho Lee, for his support, guidance, and supervision in my graduate study. He taught me how to think like a scholar and how to solve problems as a researcher. The mindsets of always thinking about the motivation before doing anything and focusing on the physics behind the phenomena impact me significantly. He encouraged me to explore new areas and never settle for average. I benefited from brainstorming sessions and fruitful discussions we had in research meetings. He supported me to collaborate with different groups, present my research at conferences, and reach out to the industry for internship opportunities. I will always remember and appreciate the valuable experience I have learned along the way. I would also like to thank Professor Yun Wang for being on my Qualifying Exam and Doctoral Dissertation committees. He told me always think about the mechanism and rationale of the research. I appreciate all the guidance and suggestions he gave to me. I thank Professor Nader Bagherzadeh for joining my Qualifying Exam and Doctoral Dissertation committees. I benefit a lot from the collaboration with Professor Bagherzadeh especially about knowledge in Computer Engineering. I enjoyed the nice tea and cookies that Professor Bagherzadeh prepared when we had a meeting together, which always relaxes me from the intense graduate study. I am grateful to Professor Bihter Padak and Professor Yoonjin Won for being on my Qualifying Exam Committee and providing insightful comments and suggestions to improve my research.

I thankfully acknowledge funding supports from the Henry Samueli School of Engineering, Semiconductor Research Corporation (SRC), and Samsung Electronics. I thank the SRC liaisons, Dr. Archana Venugopal from Texas Instrument, and Dr. Minki Cho from Intel for the helpful

discussions. The advice and information they provided from the industry point of view certainly expand my horizon. I thank Dr. Jae Choon Kim from Samsung Electronics for the research opportunity to fabricate the device that I designed. I also appreciate his mentorship and the personal advice he gave to me during his one-year visit. I would also like to thank Dr. Tae Hwan Kim, Dr. Young Hoon Hyun, and Dr. Ki Wook Jung from Samsung Electronics for all the helpful discussions and suggestions.

I owe many thanks to my labmates for their help and accompany. I especially thank Dr. Ziqi Yu for all the support in research, cleanroom work, and graduate life. I will always value the time we spent together in the lab to explore new ideas or solve research problems. I thank Dr. Laia Ferrer-Argemi, Shiva Farzinazar, Jonathan Sullivan, and Xiao Nie for the assistance, advice, and ideas in research, drinks, laughs, and group-outs. I would also like to thank Anirudh Krishna, Jungyun Lim, Jiahui Cao, Jiajian Luo, Yi Tuan, Charles Owens, and Hoyeon Park for their friendship, interactions, and advice in my research.

I would like to thank Dr. Ayed Alqahtani for sharing his knowledge and passion for research and programming. I would also like to thank Richard Chang, Chuanyun Lee, Mo Kebaili, and Jake Hes from the Integrated Nanosystems Research Facility. I am always impressed with their experience in microfabrication. They are very patient with my questions and are always willing to share their thoughts and ideas.

Most importantly, I would like to thank my family for their unconditional love, support, and encouragement for my study in the United States. They support me to overcome challenges, encourage me to improve myself, and share all the pressures and joys with me. I dedicate this dissertation to them.

#### **VITA**

# **Zongqing Ren**

| 2011-15   | B.S. in Materials Science and Engineering, Tianjin University                    |

|-----------|----------------------------------------------------------------------------------|

| 2015-17   | M.S. in Materials and Manufacturing Technology, University of California, Irvine |

| 2017-2019 | Teaching Assistant, Mechanical and Aerospace Engineering, University of          |

|           | California, Irvine                                                               |

| 2017-2021 | Research Assistant, Mechanical and Aerospace Engineering, University of          |

|           | California, Irvine                                                               |

| 6-9/2020  | Graduate Student Intern, Materials Technology Development, Intel Corporation     |

#### FIELD OF STUDY

Micro/nanoscale thermal transport, thermal metamaterials, thermoelectric cooling, thermal management of electronics

#### **PUBLICATIONS**

# Peer-reviewed Journals

- J1. **Zongqing Ren**, and Jaeho Lee. "Thermal conductivity anisotropy in holey silicon nanostructures and its impact on thermoelectric cooling." *Nanotechnology* 29, no. 4 (2017): 045404.

- J2. Ayed Alqahtani, **Zongqing Ren**, Jaeho Lee, and Nader Bagherzadeh. "System-level analysis of 3D ICs with thermal TSVs." *ACM Journal on Emerging Technologies in Computing Systems* (*JETC*) 14, no. 3 (2018): 1-16.

- J3. **Zongqing Ren**, Ziqi Yu, Jae Choon Kim, and Jaeho Lee. "TSV-integrated thermoelectric cooling by holey silicon for hot spot thermal management." *Nanotechnology* 30, no. 3 (2018): 035201.

- J4. Ziqi Yu, **Zongqing Ren**, and Jaeho Lee. "Phononic topological insulators based on six-petal holey silicon structures." *Scientific reports* 9, no. 1 (2019): 1-8.

- J5. **Zongqing Ren**, Ayed Alqahtani, Nader Bagherzadeh, and Jaeho Lee. "Thermal TSV Optimization and Hierarchical Floorplanning for 3-D Integrated Circuits." *IEEE Transactions on Components, Packaging and Manufacturing Technology* 10, no. 4 (2020): 599-610.

- J6. Jae Choon Kim, **Zongqing Ren**, Anil Yuksel, Ercan M. Dede, Prabhakar R. Bandaru, Dan Oh, and Jaeho Lee. "Recent Advances in Thermal Metamaterials and Their Future Applications for Electronics Packaging." *Journal of Electronic Packaging* 143, no. 1 (2021).

- J7. **Zongqing Ren**, Jae Choon Kim, and Jaeho Lee. "Transient Cooling and Heating Effects in Holey Silicon-based Lateral Thermoelectric Devices for Hot Spot Thermal Management." *IEEE Transactions on Components, Packaging and Manufacturing Technology* (2021).

# Conference Proceedings

- C1. **Zongqing Ren**, and Jaeho Lee. "Thermoelectric Cooling Device Based on Holey Silicon." In 2018 17th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), pp. 701-706. IEEE, 2018.

- C2. Shiva Farzinazar, **Zongqing Ren**, and Jaeho Lee. "Thermal Conductivity of Graphite Microlattices." In 2018 17th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), pp. 252-255. IEEE, 2018.

- C3. Ziqi Yu, **Zongqing Ren**, and Jaeho Lee. "Investigation of Thermal Metamaterials based on Nanoporous Silicon Using Ray Tracing and Finite Element Simulations." In 2019 18th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), pp. 13-22. IEEE, 2019. (**Best paper award**)

- C4. **Zongqing Ren**, Ziqi Yu, Jae Choon Kim, and Jaeho Lee. "Hotspot Management by Holey Silicon-Metal Composites for 1 kW/cm 2 and Beyond." In 2019 18th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), pp. 1253-1259. IEEE, 2019.

- C5. **Zongqing Ren**, Ayed Alqahtani, Nader Bagherzadeh, and Jaeho Lee. "Thermal Analysis of 3D ICs With TSVs Placement Optimization." In *ASME 2019 International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems*. American Society of Mechanical Engineers Digital Collection, 2019.

# ABSTRACT OF THE DISSERTATION

Holey Silicon and Through Silicon Vias for Thermal Management of Next-Generation Electronic Systems

by

# Zongqing Ren

Doctor of Philosophy in Mechanical and Aerospace Engineering

University of California, Irvine, 2021

Professor Jaeho Lee, Chair

The trends of electronic systems toward nanoscale, high power, and 3D integration have made heat dissipation from local hot spots to heat sink structures ever more challenging. Meanwhile, recent advances in fabrication and manufacturing technologies have enabled the development of unique structures and brought new opportunities to address thermal management challenges. This doctoral research focuses on the use of holey silicon and through silicon vias to provide device-level and system-level cooling solutions for next-generation electronic systems.

Lateral thermoelectric coolers where Peltier cooling and heating occur in the lateral direction offer solid-state hot spot cooling capability. While most advanced thermoelectric materials with low thermal conductivities provide necessary temperature gradients for thermoelectric conversion, the heat generation in electronics is detrimental to the system where high thermal conductivity is preferred. The contrasting needs of thermal conductivity are evident in thermoelectric cooling systems which call for a fundamental breakthrough. In this dissertation, we show a silicon nanostructure with vertically etched holes, or holey silicon, uniquely combines low thermal conductivity in the in-plane direction and high thermal conductivity in the cross-plane

direction, and this anisotropy is ideal for lateral thermoelectric devices. The low in-plane thermal conductivity due to substantial phonon boundary scattering in small necks sustains temperature gradients for the Peltier effect. The high thermal conductivity in the cross-plane direction due to persistent long wavelength phonons effectively dissipates heat from a hot spot to the heat sink structure. Furthermore, cooling performance of holey silicon-based thermoelectric coolers can be significantly enhanced by integrating a metallic through silicon via that directly draws heat from a hot spot. Beyond the steady-state operation, we demonstrate a transient supercooling effect, driven by the temporal and spatial interplays between the interfacial Peltier effect and the volumetric Joule heating effect. Holey silicon with anisotropic thermal conductivity is favorable by delaying the heat diffusion in the lateral direction while allowing rapid heat dissipation in the vertical direction. The transient cooling performance can be further improved by incorporating phase change materials within holey silicon, in which their melting process delays the temperature overshoot. Apart from simulations, we fabricate holey silicon-based thermoelectric coolers through standard semiconductor processes and experimentally demonstrate their cooling performance through an infrared thermography-based measurement. The cooler temperature reduction can be improved by increasing the operating temperature. Transient supercooling is also achieved by applying a current pulse, where the cooler temperature can be temporarily lower than the minimum value in steady state.

While lateral thermoelectric devices provide extraordinary device-level cooling performance, the recent development of three-dimensional integrated circuits demanding system-level cooling solutions to advance processor design and enable continued performance scaling. Through silicon via is the main structure that enables 3D integrated circuits and provides electrical connection between dies. Thermal through silicon vias are dummy vias that facilitate heat transfer

across stacked dies. However, the insertion of thermal through silicon vias extends the distance between functional units and increases the signal delay. In this dissertation, we develop a hierarchical approach to optimize the floorplan of a 3D integrated circuit through simulated annealing to address the trade-off between the peak temperature, chip area, and performance. Compared to the floorplan with a fixed thermal via placement between cores, our algorithm optimally places thermal vias between functional units and offers the optimal floorplan.

This dissertation presents that the use of holey silicon and through silicon vias can provide effective device-level and system-level thermal management solutions for next-generation electronic systems. Holey silicon with anisotropic thermal conductivity is ideal for lateral thermoelectric devices, which enables breakthroughs in addressing local hot spots under steady-state and transient conditions. Thermal through silicon vias reduce the peak temperature of 3D integrated circuits. The hierarchical floorplanning method that includes thermal via early in the processor design process could address the trade-off between thermal and electrical performance and provide optimal floorplans for next-generation electronic systems.

# **Chapter 1: INTRODUCTION**

# 1.1 Thermal Management Challenges for Advanced Electronics

The trends of semiconductor technology toward shrinking feature size, increasing transistor density, and three-dimensional (3D) integration are making the heat dissipation of electronics ever more challenging. For the past 20 years, the development of new process technologies and device structures scale the minimum feature size of transistors by approximately 0.7 times every two years as shown in Figure 1.1(a) [1].

While the size of a transistor continuously decreases, the area of a die remains relatively unchanged, and the transistor density increases dramatically, which leads to a significant increase in power density. Figure 1.1(b) shows the power densities for various processors developed over the past 40 years. When the power density exceeds  $100 \text{ W} \cdot \text{cm}^{-2}$ , heat dissipation becomes a major challenge and device engineers have been forced to increase the number of cores to keep increasing the overall performance [2]. Moreover, the power distribution is highly non-uniform, which creates regions with elevated heat flux that can be in the order of  $1 \text{ kW} \cdot \text{cm}^{-2}$  [3]. For high-power semiconductor devices, where the energy processed and dissipated is much larger than typical logic chips, the hot spot heat flux can be even higher. In the double-diffused metal-oxide-semiconductor (DMOS), the transient power density can reach  $40 \text{ kW} \cdot \text{cm}^{-2}$  [4]. In the GaN-based devices, 1 W power is dissipated in a footprint of  $0.5 \text{ }\mu\text{m} \times 0.5 \text{ }\mu\text{m}$ , resulting in a power density of  $4 \text{ MW} \cdot \text{cm}^{-2}$  and a temperature rise of 100 °C [5]. The hot spot temperature limits the device's performance and compromises reliability. The thermal management of hot spots is the key to improve a device's efficiency.

Figure 1.1 (a) The scaling trend of minimum feature size for Intel logic chips. Image adapted from [1] (b) Power densities for various commercial processors over the past 40 years. Image adapted from [2].

As the transistor size keeps shrinking, the development of new technology nodes becomes slower due to the increased process complexity. Moreover, as the minimum feature size approaches 5-7 nm range, it will be difficult to operate any transistors based on MOS due to the physical limitation [6]. To continue the success of semiconductor devices, stacking the dies on top of each other to fully utilize the vertical dimension to increase the transistor density becomes a promising solution.

In three-dimensional integrated circuits (3D ICs), through silicon vias (TSVs) run across the silicon die to provide electrical connections between active layers. Compared to 2D or 2.5D package platforms, 3D integration provides clear advantages in lowering latency, reducing power consumption, increasing interconnect bandwidth, and enabling heterogeneous integration [7]. However, thermal management has become a severe problem for 3D ICs as a direct result of the stacked structure.

As shown in Figure 1.2(a), for 2D ICs, the heat generated from the active circuits can be easily dissipated through the bulk silicon die to the heat sink. While for 3D ICs, the thermal resistance increases due to the stacked dies and interconnection layers as shown in Figure 1.2(b). The power consumption of 3D IC is expected to decrease due to the reduced wirelength, while the power density increases due to the high number of active devices per unit volume [8]. Heat removal through stacked dies is also a problem. The interconnect layers usually consist of micro-bumps and underfills, which have thermal conductivities of around 40 W·m<sup>-1</sup>K<sup>-1</sup> and 1.5 W·m<sup>-1</sup>K<sup>-1</sup>, respectively, that are much lower compared to that of the bulk silicon (150 Wm<sup>-1</sup>K<sup>-1</sup>) [9]. Moreover, the die thickness in 3D ICs is also constrained by system configuration or TSV design, which affects the thermal spreading effect significantly [7]. For the thermal management of 3D ICs, it is hard to directly cool the stacked chips or dissipate heat laterally from the dies.

Figure 1.2 (a) The package structure of a 2D IC. BEOL and TIM represent back end of line and thermal interface material, respectively. (b) The package structure of a 3D IC. Images adapted from [8].

# 1.2 Thermoelectric Cooling Devices

#### 1.2.1 Introduction to the thermoelectric effect

The thermoelectric effect describes direct conversion between thermal and electrical energy, which involves three phenomena: the Seebeck effect, the Peltier effect, and the Thomson effect [10,11]. Thermoelectric power generators produce electrical energy using a temperature gradient based on the Seebeck effect, while thermoelectric coolers (TECs) use electrical energy to provide a temperature gradient based on the Peltier effect. The Thomson effect is the heat absorption or release in a medium carrying an electrical current while sustaining a temperature gradient and is a result of the temperature dependence of the Seebeck coefficient.

The Seebeck effect is shown in Figure 1.3(a). An open-circuit voltage can be generated when two dissimilar conductors are jointed at two points with a temperature gradient. The Seebeck coefficient is defined as  $S = \lim_{\Delta T \to 0} \frac{\Delta V}{\Delta T}$ . With a known Seebeck coefficient, the temperature difference can be measured by measuring the voltage difference.

The Peltier effect is shown in Figure 1.3(b). When two dissimilar conductors are connected and an electrical current is flowing across them, heat will be generated or absorbed at the interface at a constant rate. The heat rate is directly proportional to the applied current I and the Peltier coefficient  $\Pi$  as:  $q_{Peltier} = \Pi_{AB}I$ , and changes sign if the current changes direction. The Peltier effect and the Seebeck effect are related as:  $\Pi_{AB} = S_{AB}T$ , where T is temperature.

An example of the Thomson effect is shown in Figure 1.3(c). When an electrical current is flowing through a conductor with a temperature gradient over its length, heat will be absorbed or released depending on the directions of the current and temperature gradient. The volumetric heat generation can be expressed as:  $q_{Thomson}^{\prime\prime\prime} = -\mu_T \nabla T j$ , where  $\mu_T$  is the Thomson coefficient, and j

is the current density. The Thomson coefficient can be derived from the Seebeck coefficient as:  $\mu_T = T \frac{dS}{dT}.$

The performance of a thermoelectric material is usually defined using the thermoelectric figure of merit  $zT = \frac{S^2\sigma}{k}T$ , where S,  $\sigma$ , and k are the Seebeck coefficient, electrical conductivity, and thermal conductivity, respectively [12].

Figure 1.3 (a) Schematic of the Seebeck effect. (b) Schematic of the Peltier effect. (c) Schematic of the Thomson effect. When the current and temperature gradient is in the same direction, heat is absorbed with a positive Thomson coefficient.

# 1.2.2 Thermoelectric cooling devices for hot spot management

Thermoelectric cooling devices provide solid-state operation and have shown great promise for the thermal management of high heat flux hot spots with sizes in the order of tens or hundreds of micrometers.

A conventional TEC consists of an array of series connected p-type and n-type thermoelectric elements and electrical conductors. Figure 1.4 shows the basic schematic of a TEC

with one p-type and one n-type leg. A DC electrical power is used to activate the TEC. When the electrons move from the electrical conductor to the p-type thermoelectric elements or move from the n-type thermoelectric element to the electrical conductor, heat is released at the interface as electrons are dropped down to a lower energy level. When the electrons move from the p-type thermoelectric element to the conductor or move from the conductor to the n-type thermoelectric element, heat is absorbed at the interface as electrons are bumped to a higher energy level. The thermoelectric cooling performance of a TEC is related to the TEC configuration and thermoelectric properties of the materials.

Figure 1.4 The basic schematic of a TEC with one n-type and one p-type leg.

Commercial thermoelectric coolers can only provide a cooling flux in the order of 10-100 W·cm<sup>-2</sup>, limiting its application for high heat flux hot spots [13]. To increase the cooling flux, Dr. Bar-Cohen and his group have developed mini-contact enhanced TECs to concentrate the cooling flux over a small area [14,15]. A 5 °C temperature reduction has experimentally demonstrated for a 613 W·cm<sup>-2</sup> hot spot. Later, a micro-contact TEC with a pillar directly etched in the substrate is

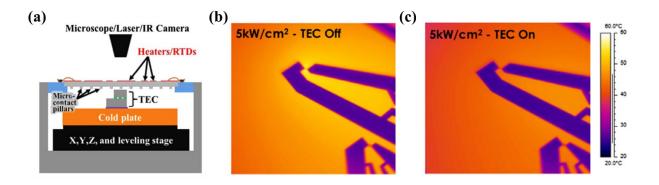

developed to reduce the thermal contact resistance between the micro-contact and the substrate [16,17]. Figure 1.5(a) shows the experimental setup of the micro-contact enhanced TEC [17]. The hot side of the thermoelectric module is attached to a liquid cooled plate. The cold side of the thermoelectric module provides a cooling flux of 66 W·cm<sup>-2</sup>, which is in contact with the SiC micro-pillar (500  $\mu$ m  $\times$  500  $\mu$ m). An infrared (IR) camera is used to capture the temperature distribution in the SiC substrate, while the actual hot spot temperature is determined by the change in the resistivity of the Platinum heater. Figure 1.5(b) and (c) show the temperature distribution change with TEC off and on. The temperature change of a 200  $\times$  200  $\mu$ m<sup>2</sup> hot spot with a heat flux of 5 kW·cm<sup>-2</sup> is measured with RTD (resistance temperature detector), which can be reduced by 12 °C when the TEC is on.

Figure 1.5 (a) Schematic of the micro-contact testing apparatus. IR images of the temperature distribution in the SiC substrate with TEC (b) on and (c) off. Images adapted from [17].

Commercial thermoelectric materials are usually based on alloys of  $Bi_2Te_3$  with  $Sb_2Te_3$  (ptype) and  $Bi_2Te_3$  with  $Bi_2Se_3$  (n-type) that have a room temperature zT around 1. Low dimensional materials such as quantum dot structures or superlattices provide new opportunities to manipulate the electrical and thermal properties of a material [18].

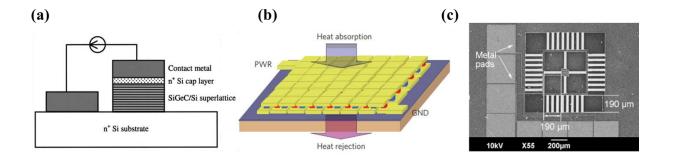

Dr. Shakouri and co-workers have developed thin film SiGe/Si and SiGeC/Si microrefrigerators based on superlattice structures fabricated by molecular beam epitaxy [19–23]. Figure 1.6 (a) shows the schematic of a superlattice-based microrefrigerator. A probe is used to send electrical current to the superlattice through the metal contact. A secondary metal contact is fabricated at the back side of the silicon chip to increase the thermal resistance between the heating and cooling junctions. The 3D thermal and current spreading effects provide a high cooling flux. The SiGeC/Si superlattice micro-cooler with a cooler size of  $40 \times 40 \,\mu\text{m}^2$  can provide temperature reductions of 2.8 °C and 6.9 °C at 25 °C and 100 °C, respectively, which correspond to a cooling flux in the order of 1 kW·cm<sup>-2</sup> [19].

Chowdhury *et al.*, have fabricated TECs based on nanostructured  $Bi_2Te_3$  thin film superlattice that is grown by metal-organic chemical vapor deposition on GaAs substrates [24]. The final TEC has  $7 \times 7$  p-n couples with a total dimension of  $3.5 \times 3.5 \times 0.1$  mm<sup>3</sup> as shown in Figure 1.6(b). The TEC is later integrated between a Si chip and a heat spreader and can provide a 15 °C temperature reduction for a 1300 W·cm<sup>-2</sup> hot spot.

Bulman *et al.* have achieved a cooling flux of 258 W·cm<sup>-2</sup> using thin film Bi<sub>2</sub>Te<sub>3</sub>-based superlattice thermoelectric modules [13]. The Bi<sub>2</sub>Te<sub>3</sub> superlattice is fabricated using metalorganic chemical vapor deposition and has a thickness of around 8 μm. Su *et al.* have demonstrated a planar TEC based on nanograined SiGe thin film as shown in Figure 1.6(c) [25,26]. A maximum cooling of 10.3 °C is achieved in the single-stage microrefrigerator with a power consumption of 56 μW, while a maximum cooling of 11.2 °C is achieved in the two-stage microrefrigerator with a power consumption of 0.41 mW at room temperature.

Figure 1.6 (a) Schematic of the SiGeC/Si microcooler. Image adapted from [19] (b) Schematic of the  $7 \times 7$  superlattice thin-film thermoelectric array. Image adapted from [24]. (c) Scanning electron microscope (SEM) image of the two-stage nanograined SiGe thin film microrefrigerator. Image adapted from [25].

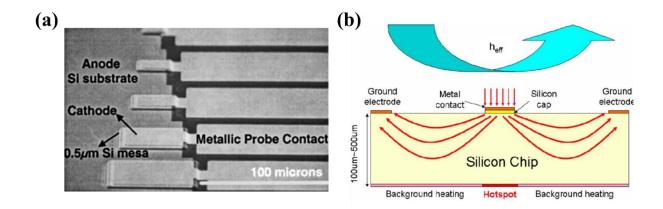

Silicon-based TECs have been developed due to the clear advantage in the fabrication process and a high power factor ( $S^2\sigma$ ). Zhang *et al.* have experimentally demonstrated a silicon-based monolithic cooler as shown in Figure 1.7(a) [27]. The bulk silicon is p-type doped with a doping concentration around  $10^{19}$  cm<sup>-3</sup> and has an electrical resistivity in the range of  $0.001 \sim 0.006$   $\Omega \cdot \text{cm}$ . A metal layer of Pt/Al/Pt/Au with a thickness of 0.1/1.0/0.1/1.5  $\mu$ m is deposited as the metal contact for the current supply. The temperature reduction for a  $40 \times 40 \,\mu\text{m}^2$  micro-cooler at room temperature is 1.2 °C, which is equivalent to a cooling flux of  $580 \,\text{W} \cdot \text{cm}^{-2}$ .

Wang *et al.* have theoretically explored the cooling performance of a silicon-based lateral TEC [28]. At 100 °C, it is found that the silicon micro-cooler with 100 μm × 100 μm cooler size can achieve a peak cooling of 6.2 °C, which is equivalent to a cooling flux of 1 kW·cm<sup>-2</sup>. Wang *et al.* further investigate the cooling performance of bulk silicon micro-cooler on a 70×70 μm<sup>2</sup>, 680 W·cm<sup>-2</sup> hot spot [29]. The schematic is shown in Figure 1.7(b). A 3D analytical thermal model of the silicon chip, including the localized Peltier cooling, Peltier heating, Joule heating, hot spot and background heating, and conductive/convective cooling is developed to predict the hot spot

temperature change. With the optimal conduction, the hot spot temperature can be reduced by 3 °C.

Figure 1.7 (a) SEM image of the silicon micro-cooler array. Image adapted from [27]. (b) Silicon thermoelectric micro-cooler for on-chip hot spot cooling. The arrows indicate the current direction. Image adapted from [29].

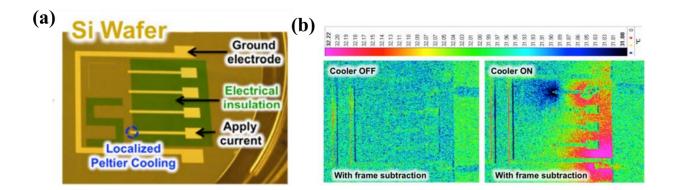

Manno *et al.* have fabricated the bulk silicon-based TEC as shown in Figure 1.8(a) [30]. A 300 nm SiO<sub>2</sub> is used as the insulation layer and a 1 μm Au is used as the electrical conductor. The temperature distribution of the TEC is measured using an IR camera. The device temperature distribution of a 500 μm cooler with/without current is shown in Figure 1.8(b), which also shows parasitic effects, such as Joule heating generated at the solder pads. Due to the low emissivity of the metal electrodes, it is hard to measure the cooler temperature, and the Peltier cooling temperature reduction in the surrounding silicon substrate is measured to be around 0.5 °C.

Figure 1.8 (a) Photograph of monolithic thermoelectric cooler fabricated on a silicon wafer. (b) IR images showing the temperature distribution on the silicon chip when the cooler is off and on. Images adapted from [30].

The hot spot cooling performance of the silicon-based TEC is also measured. The test setup involves the silicon cooler, an IR camera, an electrical power supply, and a laser heat source as shown in Figure 1.9(a). The hot spot is generated by a laser on the backside of the silicon wafer with a heat flux of around 15  $W \cdot cm^{-2}$ .

The transient response of the hot spot temperature with TEC is also investigated. Figure 1.9(b) shows the hot spot temperature as a function of time. When the cooler is activated with a 0.5 A applied current, the hot spot temperature immediately reduces and approaches its steady-state value. Figure 1.9(c) shows the time-dependent hot spot temperature with a current pulse that has a magnitude three times greater than the optimal steady-state applied current. With the current pulse, the hot spot temperature reduces immediately due to the increased Peltier cooling, and gradually increases due to the diffusion of the Joule heating. When the current is removed, there is a sharp increase in hot spot temperature, which is caused by the removal of Peltier cooling but continued diffusion of the Joule heating.

Figure 1.9 (a) Schematic of the measurement setup used to test the hot spot cooling capability of the silicon micro-cooler. Hot spot temperature reduction over time with (b) optimal current under steady-state and (c) a current pulse of three times large magnitude than that of the optimal current under steady-state. Images adapted from [30].

# 1.3 Silicon-based thermoelectric materials

#### 1.3.1 Size effect in silicon

As the most widely used semiconductor material, silicon has recently received much attention in thermoelectric applications due to the advantages of its abundance, non-toxicity, and easy integration in electronics [31].

The lattice thermal conductivity of silicon can be obtained using kinetic theory as  $k=\frac{1}{3}Cv\Lambda$ , where C, v, and  $\Lambda$  are the volumetric heat capacity, speed of sound, and phonon mean free path (MFP), respectively [32]. The phonon MPF represents the average distance a phonon travels without scattering with other phonons and can be calculated using Matthiessen's rule as  $\frac{1}{\Lambda} = \frac{1}{\Lambda_U} + \frac{1}{\Lambda_d} + \frac{1}{\Lambda_{e-ph}} + \frac{1}{\Lambda_b}$ , where  $\Lambda_U$ ,  $\Lambda_d$ ,  $\Lambda_{e-ph}$ , and  $\Lambda_b$  represents the phonon MFP determined by the Umklapp, defect, electron-phonon, and boundary scatterings. The first three terms are intrinsic

phonon MFP in bulk materials and the last term becomes much more important at very low temperatures or with small critical dimensions. Silicon nanostructures are promising for thermoelectric applications because of the difference in the average MFP between electrons and phonons in silicon. It is possible to reduce the thermal conductivity without significantly impact the electrical conductivity.

The reduced thermal conductivity from its bulk values has been demonstrated in silicon micro- or nano- structures due to the boundary scattering. Ju and Goodson have measured the inplane thermal conductivity of silicon thin films with thickness down to 74 nm and demonstrated a strong size effect in silicon thin film that the thermal conductivity can be reduced by 50% at room temperature [33].

Later, the thermal conductivity of silicon nanowires has also been studied and the measured thermal conductivity of silicon nanowires can be two magnitudes lower than that of the bulk value [34,35]. Hochbaum *et al.* have studied the impact of surface roughness and measured the thermal conductivity of rough silicon nanowires with diameters in the range of 20-300 nm. The thermal conductivity of a 50 nm diameter rough silicon nanowire is 100 times smaller than that of its bulk value, yielding a room temperature zT of 0.6 [36]. Silicon nanowires demonstrate significantly improved thermoelectric properties, however, their weak mechanical strength and strong dependence on both diameter and surface morphology remain as big challenges for thermoelectric applications [37].

# 1.3.2 Thermoelectric properties of holey silicon

Silicon thin films have demonstrated reduced thermal conductivity due to the size effect and the thermal conductivity can be further reduced by introducing microporous or nanoporous structures to enhance the phonon boundary scattering.

Song and Chen have measured the thermal conductivity of silicon membranes with periodic etched through-membrane pores [36]. The neck size of the microporous silicon is in the range of 2-10  $\mu$ m. Its thermal conductivity is smaller than silicon thin film with the same thickness suggesting strong size effects.

Yu *et al.* have measured the thermal and electrical conductivities of silicon nanomesh with neck sizes of 18 nm and 23 nm and a thickness of 22 nm [38]. The silicon nanomesh has substantially reduced thermal conductivity as low as 1.9 W·m<sup>-1</sup>K<sup>-1</sup> at room temperature while preserving bulk-like electrical conductivity.

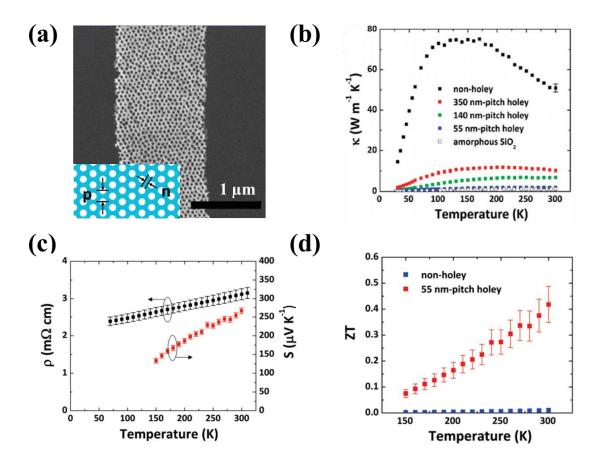

Tang *et al.* have fabricated and measured thermoelectric properties of holey silicon, where high-density nanoscopic holes are created in thin single-crystalline silicon membranes using block copolymer lithography [37]. The holey silicon has a pitch size (p) in the range of 55-350 nm and a neck size (n) in the range of 23-152 nm. The SEM image of holey silicon with 55 nm pitch size and 23 nm neck size is shown in Figure 1.10 (a).

The in-plane thermal conductivity of holey silicon is significantly reduced due to a strong "necking effect". The thermal conductivity reduces with smaller necks and the thermal conductivity of a 23 nm neck holey silicon can be as low as 1.73-2.03 W·m<sup>-1</sup>K<sup>-1</sup> at room temperature as shown in Figure 1.10 (b).

The electrical conductivity and Seebeck coefficient of the 23 nm neck size holey silicon are also measured with a doping concentration of  $5 \times 10^{19}$  cm<sup>-3</sup> as shown in Figure 1.10(c). Since

the electron MFP in highly doped silicon is in the range of 1-10 nm and is smaller than the neck size, the power factor of holey silicon is moderately deteriorated compared to that of the silicon thin film. Due to the strong "necking effect" on the thermal transport, the zT of a 55 nm pitch size holey silicon at room temperature is increased to 0.4 as shown in Figure 1.10(d).

Figure 1.10 (a) SEM images of holey silicon with 23 nm neck size (n), 55 nm pitch size (p) and 100 nm thickness. (b) Temperature-dependent thermal conductivities of silicon thin film, amorphous silica, and holey silicon with different neck sizes. (c) Temperature-dependent electrical properties of boron-doped 23 nm neck holey silicon. (d) Temperature-dependent zT of silicon thin film and 23 nm neck holey silicon. Images adapted from [37].

Kim *et al.* [39] and Nakagawa *et al.* [40] have measured the thermal conductivity of silicon phononic crystal with a neck size in the range of tens or hundreds of nanometers. The measured thermal conductivity is significantly reduced compared to that of the bulk silicon.

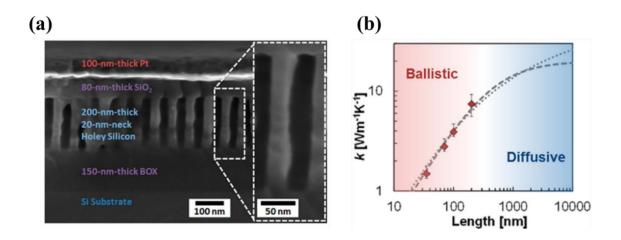

Lee *et al.* have measured the cross-plane thermal conductivity of holey silicon with 20 nm neck size and a thickness in the range of 35 - 200 nm [41]. The holey silicon device is fabricated using block copolymer. The holey silicon with different thicknesses is fabricated by consuming silicon via thermal oxidation and buffered hydrofluoric acid etch.  $3\omega$  method is used to measure the thermal conductivity and the cross-sectional image of the holey silicon device is shown in Figure 1.11(a).

The length-dependent thermal conductivity of holey silicon is shown in Figure 1.11(b). With the same neck size, the strong length dependence of the thermal conductivity indicates that ballistic phonon transport dominates heat conduction in the cross-plane direction of holey silicon. A simple scaling model using the average MFP of bulk silicon is shown by the gray dashed line in Figure 1.11(b). A semiempirical model accounting for the phonon spectral dependence attributes the length-dependent data to the presence of long-wavelength phonons that have the MFP greater than the length of holey silicon nanostructures is shown by the gray dotted line in Figure 1.11(b).

Figure 1.11 (a) Cross-plane thermal conductivity experimental setup. (b) Length-dependent thermal conductivity of holey silicon at room temperature with 20 nm neck size. The strong length dependence indicates that ballistic phonon transport dominates heat conduction in the length scale of 35-200 nm. Images adapted from [41].

Anufriev *et al.* have measured the thermal conductivity of phononic crystals with different neck sizes and lattice types [42]. They find that when the neck size is down to several tens of nanometers, thermal conductivity is controlled by the neck size and becomes independent of the surface-to-volume ratio, lattice type, and other geometrical parameters.

Lim *et al.* have simultaneously measured thermoelectric properties of holey silicon in one microdevice [43]. The holey silicon has a neck size in the range of 16-34 nm and a fixed pitch size of 60 nm. At room temperature, holey silicon with neck size of 16 nm provides the minimum measured thermal conductivity of  $1.8 \text{ W} \cdot \text{m}^{-1} \text{K}^{-1}$ , while the 24 nm neck size holey silicon provides the maximum zT values of 0.05. The zT value is mainly limited by the reduced electrical conductivity due to the ion implantation and surface defects but is still 5 times larger compared to that of the silicon thin film.

Lee *et al.* have measured the thermal conductivity of silicon nanomesh with periodic and aperiodic patterns [44]. They conclude that the phonon coherence is unimportant for thermal transport with periodicities of 100 nm or higher and temperatures above 14 K, while phonon backscattering, or size effect, is responsible for the thermal conductivity reduction.

Ma *et al.* have measured the electrical properties of holey silicon thin film with a neck size between 120 and 230 nm [45]. They find that while the electrical conductivity of holey silicon is close to that of the bulk silicon with comparable doping, the power factor of holey silicon at optimal doping is 50% lower than that of the bulk silicon due to the phonon drag effect that reduces

the Seebeck coefficient. They also predict that the holey silicon with 20 nm neck size and the optimal doping of  $2\times10^{19}$  cm<sup>-3</sup> will provide the maximum zT of 0.5 at room temperature.

Liu *et al.* have measured the thermoelectric properties of holey silicon with neck size of 45 nm and doping concentration around  $3\text{-}10 \times 10^{19}$  cm<sup>-3</sup> at elevated temperatures [46]. They find that the zT of holey silicon device is around 0.09 at room temperature and at least 0.29 at 650 K. The zT of holey silicon can be further improved by optimizing the feature sizes and using surface doping.

# 1.4 Outline of Doctoral Research

Chapter 2 presents the thermal conductivity anisotropy in holey silicon and its impact on the lateral thermoelectric cooling devices for hot spot thermal management. The effects of microcooler size, thermal conductivity anisotropy, and substrate size and thickness are evaluated in detail. Chapter 3 presents the TSV-integrated holey silicon-based TEC that combines passive and active cooling solutions. This chapter also explores the metal-filled holey silicon and its impact on the on-state and off-state TEC performance. Chapter 4 demonstrates the transient supercooling effect in the holey silicon-based lateral TEC. The effects of the Thomson coefficient, current pulse shapes, consecutive pulses, current pulse amplitudes, and durations are studied in detail. The transient performance of holey silicon-based TEC with phase change material fillers is also investigated. Chapter 5 presents the experimental demonstration of the holey silicon-based TEC. The holey silicon TEC is fabricated through standard semiconductor processes, and its performance is measured through infrared thermography. The steady-state and transient performances of holey silicon are investigated in detail. Chapter 6 demonstrates a floorplan optimization algorithm for the thermal management of 3D ICs to address the trade-off between

thermal and electrical performance. The impacts of TTSVs on the wirelength, area, and peak temperature of the 3D IC are investigated in detail. Chapter 7 offers concluding remarks on the thermal management of hot spots through holey silicon-based active thermoelectric cooling and TTSV-based passive cooling strategies. The opportunities for future research are also discussed.

# Chapter 2: Thermal Conductivity Anisotropy in Holey Silicon Nanostructures and Its Impact on Thermoelectric Cooling

Artificial nanostructures have improved prospects of thermoelectric systems by enabling selective scattering of phonons and demonstrating significant thermal conductivity reductions. While the low thermal conductivity provides necessary temperature gradients for thermoelectric conversion, the heat generation is detrimental to electronic systems where high thermal conductivity is preferred. The contrasting needs of thermal conductivity are evident in thermoelectric cooling systems, which call for a fundamental breakthrough. In this chapter, we show a silicon nanostructure with vertically etched holes, or holey silicon, uniquely combines the low thermal conductivity in the in-plane direction and the high thermal conductivity in the crossplane direction, and that the anisotropy is ideal for lateral thermoelectric cooling. The low in-plane thermal conductivity due to substantial phonon boundary scattering in small necks sustains large temperature gradients for lateral Peltier junctions. The high cross-plane thermal conductivity due to persistent long-wavelength phonons effectively dissipates heat from a hot spot to the on-chip cooling system. Our scaling analysis based on spectral phonon properties captures the anisotropic size effects in holey silicon and predicts the thermal conductivity anisotropy ratio up to 20. Our numerical simulations demonstrate the thermoelectric cooling effectiveness of holey silicon is at least 30% greater than that of high-thermal-conductivity bulk silicon and 400% greater than that of low-thermal-conductivity chalcogenides; these results contrast with the conventional perception preferring either high or low thermal conductivity materials. The thermal conductivity anisotropy is even more favorable in laterally confined systems and will provide effective thermal management solutions for advanced electronics.

## 2.1 Introduction

Recent trends toward nanoscale and high power electronics have made heat dissipation from local hot spots to heat sink structures increasingly challenging [47–50]. Among various thermal management solutions, thermoelectric cooling offers unique attributes including solidstate operation [51] and system scalability [52] that are particularly attractive for addressing the local heat dissipation issues [3,24,53]. While advances in thermoelectric materials through nanostructuring and controlled doping have made significant progress in improving the figure of merit [54,55], most materials are based on complex semiconductors [55,56] and low-dimensional structures [57,58] that are incompatible with microelectronic processes. Silicon, on the other hand, offers clearly favorable attributes that facilitate the integration with existing microelectronic processes. However, the high thermal conductivity of silicon has worked against conventional metrics of thermoelectric applications, in which large temperature gradients are desirable. In recent studies, silicon nanostructures have demonstrated significant thermal conductivity reductions and improved the prospects of thermoelectric technology [36,37,59]. The low thermal conductivity nanostructures, however, are not favorable for cooling electronics, and the contrasting needs of thermal conductivity are evident in lateral thermoelectric cooling systems. Using bulk silicon for lateral thermoelectric cooling [29], the high thermal conductivity will require a large system size to maintain the necessary temperature gradients for the Peltier junctions. Using conventional nanostructures, the low thermal conductivity will limit the heat dissipation. Here we show a silicon nanostructure with vertically etched holes, or holey silicon [37,41,43], uniquely combines the low thermal conductivity in the in-plane direction and the high thermal conductivity in the cross-plane direction, and that the anisotropy is ideal for lateral thermoelectric cooling. In this chapter, we identify the fundamental mechanisms of anisotropic thermal conductivities in the in-plane and the

cross-plane directions of holey silicon using spectral phonon transport theories and develop size dependent models to predict the impact of the anisotropy in lateral thermoelectric cooling systems. We further evaluate the thermoelectric cooling effectiveness of holey silicon, in comparison to other material systems, at varying dimensions and attribute its excellent performance to the thermal conductivity anisotropy.

# 2.2 Analytical and Numerical Modeling Methods

## 2.2.1 Cross-plane and in-plane thermal transport in holey silicon

The cross-plane thermal conductivity of holey silicon has been characterized by experiments, for holey silicon with a neck size of 20 nm, a pitch size of 60 nm, and a thickness ranges of 35-200 nm, the cross-plane thermal conductivity ranges from 1.5 to 7.5 W·m<sup>-1</sup>K<sup>-1</sup> [41]. Size dependent thermal conductivities of silicon thin films and nanowires have been reasonably well understood by approximating the phonon mean free path (MFP) to a critical dimension such as the film thickness or the diameter [37,43,44,60,61]. For holey silicon, the cross-plane thermal conductivity is accurately described by the consideration of an effective cross-sectional area that accounts for the neck size and the pitch size [41]. Figure 2.1 shows a schematic of a holey silicon unit cell with the effective cross-sectional area that captures the dominant phonon boundary scattering effect. Here we have reproduced the spectral scaling model to predict the cross-plane thermal conductivity of holey silicon ( $k_{HS_p}$ ) with varying neck sizes (n) and thickness (t):

$$k_{HS_z} = \int_0^{\omega_D} k_{z_\infty}(\omega, n) \times \left(1 + \frac{\lambda_{z_\infty}(\omega, n)}{t/2}\right)^{-1} d\omega$$

(2.1)

where  $\omega$  is the phonon frequency,  $\omega_D$  is the Debye cut-off frequency, and  $k_{z_{\infty}}(\omega, n)$  and  $\lambda_{z_{\infty}}(\omega, n)$  is the thermal conductivity and the phonon MFP of a silicon nanowire which can

be calculated by Landauer formalism [60]:

$$k_{Z_{\infty}} = \frac{2L}{\pi^2 d_{eff}^2} \int_0^{\infty} \left( \frac{N_1(\omega)}{1 + L/\lambda_l(\omega)} + \frac{N_2(\omega)}{1 + L/d_{eff}} \right) \frac{\hbar^2 \omega^2}{k_B T^2} \times \frac{\exp\left(\hbar \omega / k_B T\right)}{\left(\exp\left(\hbar \omega / k_B T\right) - 1\right)^2} d\omega \tag{2.2}$$

where T is the temperature, L is the length and  $d_{eff}$  is the effective diameter that represents an equivalent cross-sectional area of a nanowire. For each holey silicon, the effective diameter is determined by the neck size (n) and the pitch size (p) by  $d_{eff} = \sqrt{\frac{\sqrt{3}}{\pi}} p^2 - \frac{(p-n)^2}{2}$ . The use of  $d_{eff}$  in the scaling model is known to accurately captured the thermal conductivity data of holey silicon.  $\lambda_l(\omega)$  is the frequency dependent MFP due to lateral boundary scattering which can be expressed as  $\lambda_l(\omega) = 4\pi^2 \times (4B\frac{\hbar^2}{d^3}\left(\frac{\omega}{\omega_D}\right)^2 + AB\frac{\hbar^2}{a^2d}\left(\frac{\omega}{\omega_D}\right)^4)^{-1}$  [62], where A and B are dimensionless fitting parameters and a is the lattice spacing. The  $\lambda_{z_\infty}(\omega,n)$  is determined by combining the lateral boundary scattering with bulk silicon Umklapp scattering  $(\lambda_U(\omega))$  and point-defect scattering  $(\lambda_D(\omega))$  [41,63]:

$$\lambda_{z_{m}}(\omega, n) = (\lambda(\omega)^{-1} + \lambda_{U}(\omega)^{-1} + \lambda_{D}(\omega)^{-1})^{-1}$$

(2.3)

The total number of modes at a given frequency is defined as  $N = 4 + C(\frac{d}{a})^2 \times (\frac{\omega}{\omega_D})^2$  where C is the fitting parameter [62].  $N_1(\omega)$  is the number of modes with mean free path  $\lambda_l(\omega)$  which is given by  $N(\min(\omega, v/h))$ , where h is the surface disorder and v is the average phonon group velocity.  $N_2(\omega)$  is the number of modes with MFP limited to d which is defined as  $N - N_1$ .

The in-plane thermal conductivity of holey silicon with varying neck sizes have been characterized in separate studies [37,43], but analytical models have not been presented to capture the scaling trend. Consistent with the scaling model approach that captured the length (thickness) dependence in the cross-plane thermal conductivity of holey silicon, we extend the analysis to

predict the neck size dependence in the in-plane thermal conductivity. Based on the Matthiessen's rule [63,64] we can express the thermal conductivity in terms of MFPs. Assuming the properties of holey silicon do not change with varying n except for the MFP limited by boundary scattering between holes ( $\lambda_{holes}$ ), we can show the in-plane thermal conductivity of holey silicon ( $k_{HS_x}$ ) as follows:

$$k_{HS_x} = \frac{1}{3} C v \left( \frac{1}{\lambda_U} + \frac{1}{\lambda_D} + \frac{1}{\lambda_{thickness}} + \frac{1}{\lambda_{holes}} \right)^{-1} = \frac{1}{3} C v \left( \frac{1}{\lambda_{x_{\infty}}} + \frac{1}{\lambda_{holes}} \right)^{-1} = k_{x_{\infty}} \left( 1 + \frac{\lambda_{x_{\infty}}}{\lambda_{holes}} \right)^{-1}$$

(2.4)

where  $\lambda_U$  is the MFP limited by Umklapp scattering,  $\lambda_D$  is the MFP limited by point-defect scattering.  $\lambda_{thickness}$  is the MFP limited by boundary scattering at top and bottom surfaces and  $\lambda_{holes}$  is the MFP limited by boundary scattering at hole surfaces.  $k_{x_{\infty}}$  is the in-plane thermal conductivity of holey silicon of infinitely long neck size, which corresponds to a silicon film with no holes.  $\lambda_{x_{\infty}}$  is the average MFP of a silicon film and  $\lambda_{holes}$  is approximated as n/2 assuming the average distance allowed for thermal transport in the in-plane direction is one-half of the neck size [41,65]. We use a spectral scaling model to account for the phonon frequency dependence [66,67] and predict the in-plane thermal conductivity of holey silicon as a function of the neck size and the thickness as follows:

$$k_{HS_{\chi}} = \int_0^{\omega_D} k_{\chi_{\infty}}(\omega, t) \times \left(1 + \frac{\lambda_{\chi_{\infty}}(\omega, t)}{n/2}\right)^{-1} d\omega$$

(2.5)

We use an adjusted Debye cut-off frequency  $(\omega_D, \sim 52 \text{ THz})$  that is determined by the experimental data, as suggested by Mingo *et al* [63].  $k_{x_{\infty}}(\omega, t)$  and  $\lambda_{x_{\infty}}(\omega, t)$  are the in-plane thermal conductivity and the phonon mean free path of silicon thin film.  $k_{x_{\infty}}(\omega, t)$  is then computed by the Holland model [68]:

$$k_{x_{\infty}} = \frac{1}{3} \sum_{j} v_j^2 \int_0^{\frac{\theta_j}{T}} C_{V,j}(x_{\omega}, T) [\tau_j(x_{\omega}, T, t) \times F(\delta)] dx_{\omega}$$

(2.6)

The subscript j indicates transverse and longitudinal phonon modes,  $v_j$  is the phonon group velocity of different modes.  $x_{\omega} = \hbar \omega / k_B T$  is the non-dimensional phonon frequency.  $C_{V,j}(x_{\omega},T)$  is the phonon specific heat per unit volume,  $\Theta_j$  is the Debye temperature and  $\tau_j(x_{\omega},T,t)$  is the phonon relaxation time in the absence of the vertical phonon boundary scattering. The vertical boundary scattering effect is then captured by the reduction function [69–71]:

$$F(\delta) = 1 - \frac{3(1-s)}{2\delta} \int_{1}^{\infty} \left(\frac{1}{t^{3}} - \frac{1}{t^{5}}\right) \times \frac{1 - \exp(-\delta t)}{(1 - s \times \exp(-\delta t))} dt$$

(2.7)

where  $\delta = d/\lambda_{x_j}$ , is the ratio of the thickness (d) for silicon thin films to the phonon mean free path  $(\lambda_{x_j} = v_j \times \tau_j(x_\omega, T, t))$  and s is the specularity. The specularity s ranges from 0 to 1, indicating fully diffuse to fully specular surface conditions. In this manuscript, we assume the surface boundaries of holey silicon are fully diffuse (s=0) [72]. For transverse and longitudinal phonon modes, the  $\lambda_{x_\infty}(\omega, t)$  is defined as  $\lambda_{x_\infty}(\omega, t) = v_j \times \tau_j(x_\omega, T, t) \times F(\delta)$ , respectively.

#### 2.2.2 Numerical simulations of the on-chip cooling system

The device-level heat transfer and thermoelectric effects are simulated using ANSYS<sup>TM</sup>, and the finite element simulations account for thermal conductivity size effects in holey silicon by using the properties predicted from the semi-classical phonon transport models (Eq. (2.1 - 2.7)). Figure 2.1 shows the structure of the holey silicon thermoelectric on-chip cooling system. The heat generation by electronics is modeled as a combination of 70 W·cm<sup>-2</sup> background heating and 700 W·cm<sup>-2</sup> hot spot heating, which is chosen as representative values for modern electronics and to be consistent with previous thermoelectric cooling studies [29,73,74]. A metal contact is integrated into the center as micro-cooler and a ground electrode is designed to carry electric current. For the

exploration of system dimensions, the micro-cooler size, lateral substrate size, and holey silicon substrate thickness are varied from  $50 \times 50 \ \mu m^2$  to  $500 \times 500 \ \mu m^2$ ,  $12000 \times 12000 \ \mu m^2$  to  $1000 \ \times 1000 \ \mu m^2$  and 50 to  $150 \ \mu m$ , respectively. The top of the holey silicon undergoes convective heat transfer to  $25 \ ^{\circ}$ C ambient air. In our simulations, we use a constant convection coefficient value of  $8700 \ W \cdot m^{-2} K^{-1}$  to represent the use of an advanced heat exchanger [29,74]. With moderate heat exchangers, we may expect a lower convection coefficient value [75], the impact of thermoelectric cooling will be greater due to increased temperature gradients within solids and the increase importance of thermoelectric effects. For p-type holey silicon, the whole system is activated by the electric current entering the metal contact, flowing laterally through the holey silicon substrate and exciting at the ground electrode. Inside p-type holey silicon, the flow of positive holes serves to transport the absorbed heat away from the micro-cooler/substrate interface and dissipates it at the secondary interface between holey silicon and ground electrode. Previous study revealed that the electric contact resistance between metal and highly doped silicon is between  $1 \times 10^{-11}$  and  $1 \times 10^{-10} \Omega \cdot m^2$  [76.77], in this study, the electric contact resistance of  $1 \times 10^{-10} \Omega \cdot m^2$  is applied.

A temperature cooling effectiveness (TCE) is defined to evaluate the cooling performance [29]:

$$\Delta T^* = \frac{T_{heating ON, cooling OFF} - T_{heating ON, cooling ON}}{T_{heating ON, cooling OFF} - T_{heating OFF, cooling OFF}} = \frac{\Delta T_{thermoelectric cooling}}{\Delta T_{hotspot heating}}$$

(2.8)

The  $T_{heating\ ON/OFF,cooling\ ON/OFF}$  is the hotspot temperature when the hot spot heat flux is applied/not applied and the micro-cooler is working/not working. If  $\Delta T^* >= 1$ , the micro-cooler effectively cools down the hot spot to a temperature that is smaller than the case of background heating only. If  $0 < \Delta T^* < 1$ , the micro-cooler can reduce the hot spot temperature, but the

temperature is higher than is the case of background heating only. If  $\Delta T^* \ll 0$ , the Joule heating generated by the applied current exceeds the thermoelectric cooling.

Figure 2.1 A holey silicon-based thermoelectric cooling system. The black arrows indicate heat flows from an integrated circuit chip to holey silicon substrate ( $Q_{integrated\ circuits}$ ), and conventional heat flows to a heat exchanger in the vertical direction ( $Q_{heat\ exchanger}$ ), respectively. The red arrows indicate the heat flow inside the holey silicon substrate in the lateral direction ( $q_x$ ) and vertical direction ( $q_z$ ). The holey silicon neck and pitch sizes are presented by n and p, respectively. The effective diameter ( $d_{eff}$ ) and effective cross-sectional area of silicon nanowire and holey silicon is shown by the blue area.

# 2.3 Results and Discussion

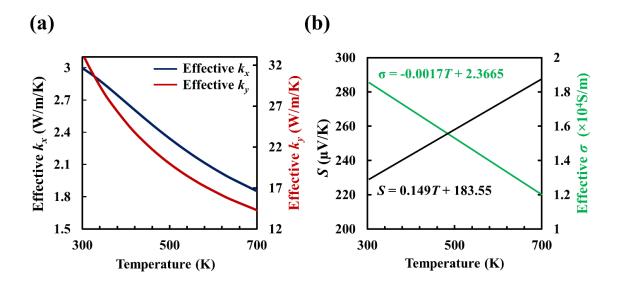

# 2.3.1 Thermal and electrical properties of holey silicon

Figure 2.2(a) shows the cross-plane thermal conductivity prediction of holey silicon with neck sizes of 10 nm to 60 nm and thicknesses of 10 nm to 100  $\mu$ m. The neck size determines the cross-sectional area of transport, and the phonon boundary scattering induced by the neck is