# **UC Irvine**

# **ICS Technical Reports**

# **Title**

BIF: a behavioral intermediate format for high level synthesis

## **Permalink**

https://escholarship.org/uc/item/74g6g7p2

# **Authors**

Dutt, Nikil D. Hadley, Tedd Gajski, Daniel D.

# **Publication Date**

1989-02-10

Peer reviewed

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.)

z 699 C 3 no. 89-03

# BIF:

# A Behavioral Intermediate Format For High Level Synthesis

BY

Nikil D. Dutt Tedd Hadley Daniel D. Gajski

Technical Report 89-03

Information and Computer Science University of California at Irvine Irvine, CA 92717

#### Abstract

This report describes a new intermediate format for behavioral synthesis systems, based on annotated state tables. It supports user control of the synthesis process by allowing specification of partial design structures, user-bindings and user modification of compiled designs. It is a simple and uniform representation that can be used as an intermediate exchange format for various behavioral synthesis tools. The format captures synchronous and asynchronous behavior, and serves as a good interface to the user by linking behavior and structure at each level of abstraction in the behavioral synthesis process.

# TABLE OF CONTENTS

# $\mathbf{CHAPTER}$

| 1. | Introduction                                          | 1  |

|----|-------------------------------------------------------|----|

|    | 1.1. Problem Description                              | 1  |

| 2. | Behavioral Synthesis Framework                        | 5  |

|    | 2.1. Synthesis Tasks                                  | 5  |

|    | 2.2. Typical Synthesis Environment                    | 6  |

| 3. | BIF: The Behavioral Intermediate Format               | 10 |

|    | 3.1. General Description                              | 10 |

|    | 3.2. The Operations-Based State Table Format          | 13 |

|    | 3.3. The Unit-Based State Table Without Connections   | 14 |

|    | 3.4. The Unit-Based State Table With Connections      | 15 |

|    | 3.5. The Control-Based State Table                    | 15 |

|    | 3.6. Asynchronous Behavior                            | 22 |

| 4. | User Interaction Scenarios                            | 25 |

|    | 4.1. User Specified Structural Constraints            | 25 |

|    | 4.2. User Specified Bindings                          | 26 |

|    | 4.3. Modification of Compiled Designs                 | 27 |

|    | 4.4. State Table Modification                         | 28 |

| 5. | Summary                                               | 29 |

|    | 5.1. Acknowledgements                                 | 29 |

|    |                                                       |    |

| 6. | References                                            | 30 |

| ΑF | PPENDIX A. A Tutorial Introduction to BIF             | 31 |

|    | A.1. General Description                              | 31 |

|    | A.2. Specific Descriptions of Each State Table Format | 35 |

| ΑF | PPENDIX B. BIF Syntax                                 | 38 |

|    | B.1. Operations Based State Table Syntax              | 38 |

|    | B.2. Unit Based State Table Syntax                    | 43 |

|    | B.3. Control Based State Table Syntax                 | 48 |

#### CHAPTER 1.

#### Introduction

#### 1.1. Problem Description

The task of high level synthesis spans the continuum from the automatic generation of a design from a purely behavioral specification, down to the compilation of a completely specified structural design consisting of a set of components from a given library and their interconnection. In the first case (automatic generation), the behavior is specified as a set of assignment statements to variables, possibly with timing constraints for input-output pairs. There is no binding of operations to time or to functional units, no binding of variables to storage elements, and the description does not have any connectivity specified between storage and functional units. At the other extreme, compilation of structure consists of mapping generic components (or components from one library) to components derived from another library. The main objective is optimization of that mapping to satisfy technology constraints such as time, area, power, testability, etc.

The traditional view of behavioral synthesis ([GrKP85] [Thom86] [McPC88] etc.) assumes that the the synthesis system automatically generates the structural design from a user specified abstract behavior. Such systems do not permit the user to interact in the design synthesis and evaluation loop. The major drawback with this appraoch is that the user cannot impose structural constraints (in the form of an initial design structure), or provide design hints (in the form of behavioral operators and variables bound to structural components and connections). The need for such user input is evidenced by the fact that

research in behavioral synthesis algorithms is still in its infancy. Existing algorithms for synthesis tasks like state allocation, component binding, etc. are either limited to certain narrow application areas (e.g. Digital Signal Processing applications), or use restrictive and simple models which fail to generate realistic designs (e.g. unit-delay, unit-cost models, [PaPM86]). By allowing the user to interact with the design process, the system permits the user to guide the synthesis tasks by incorporating the designer's knowledge and expertise.

An attempt to rectify this drawback is described in [ThBR87], where "links" are maintained between the abstract behavioral entities (variables, operators) and the resultant structural design (state, component, connection). These links are a useful representation for performing multi-level simulation, enabling behavioral verification of the synthesized structure. But on closer examination, this behavior-to-structure linking does not really help the designer explore different design alternatives. If the synthesized design does not meet the constraints, the user is forced to re-synthesize the design automatically from the abstract behavior by changing some high level constraint.

For instance, knowing that variable "A" in some statement of the behavior is bound to register R1 in state 2 of the synthesized design doesn't really help the user decide on how to improve the design; it merely serves as a debugging aid to verify the correctness of the synthesis algorithms that generated that particular design. Instead, what is really needed is a mechanism that permits the user to selectively specify the binding of certain behavioral variables and operators to specific structural components and connections. The user is then able to directly influence synthesis of the structural design to meet the desired constraints.

Several requirements emerge from the previous discussion:

- (1) partial design specification: the user should be able to specify a partially designed structure as an initial constraint; the synthesis tools should then be able to complete the rest of the design.

- (2) user-bindings: the user should be able to selectively bind behavioral operations to particular states, behavioral operations to components, and behavioral variables to storage components (e.g. registers) or connections (e.g. buses, wires).

- (3) modification of compiled designs: the user should be able to modify a structural design during or after synthesis <sup>1</sup>.

- (4) modification of synthesis tools: a consistent and readable intermediate format is required to enable the addition of new tools and the modification of existing synthesis tools; the format must allow description of the complete design with links to the behavior at each stage of the design process.

In this report, we describe a new intermediate representation using annotated textual state tables which supports the above requirements. We will show how this representation can be used to describe the design at each level of abstraction in the synthesis process. It facilitates easy translation to and from the internal data structures of synthesis algorithms, thereby allowing interchangeability (and upgrading) of synthesis tools. It also serves as a useful linking mechanism between the behavior and the structure. Furthermore, users can interact with the representation at each of the intermediate levels, allowing for user modification of the partial designs. The state-table based format is flexible yet simple with

<sup>&</sup>lt;sup>1</sup> Modification of compiled design is described in more detail in Section 4, User Scenarios.

an overall consistency throughout the levels of abstraction; designers will find this to be a convenient interface mechanism for interacting with a behavioral synthesis system.

#### CHAPTER 2.

#### Behavioral Synthesis Framework

# 2.1. Synthesis Tasks

Behavioral synthesis is the process of mapping an abstract behavior to a structural design that satisfies the behavior. The behavior is normally described by a sequence of language variables and operators, while the structural design is an interconnection of functional units, storage elements operating on a state-by-state basis. The functional units, storage and connection elements are normally drawn (or allocated) from a given library. There are several behavior-to-structure mappings that comprise this synthesis task; these mappings are called bindings. Some of the important mappings are mentioned below.

Resource allocation is the task of determining the type and number of functional units, storage elements and connections to be used in the ensuing design. The allocated resources must satisfy the designer's high level constraints.

State binding is the temporal assignment of operation sequences in the behavior to states of the structural design. A state, in this context, has the implicit notion of a synchronous clock which determines the duration of the state.

Unit binding is the task of assigning functional and storage units to particular behavioral operators and variables.

Connection binding is the task of providing connections between structural components to effect the data transfers specified in the behavior. Control synthesis is the task of generating control logic which sequences the design through the final states of the design, and which produces control signals for performing operations within each state.

Each of these tasks can be followed by an optimization phase, where, for instance, unit merging follows unit binding, or connection merging follows connection binding. These allocation, binding and optimization tasks are closely inter-related; there is no optimal ordering of the tasks and current research in this area attempts to understand their interaction. This underscores the need for a standard intermediate format that captures the complete design at each of these levels.

# 2.2. Typical Synthesis Environment

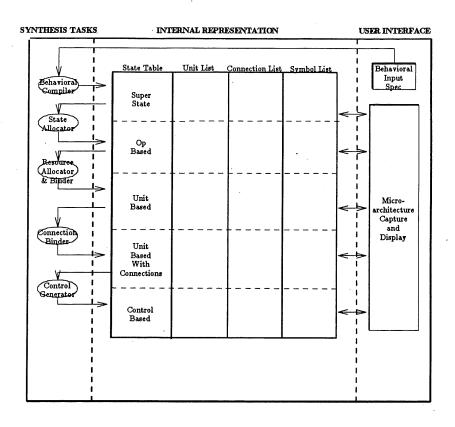

We will use the environment shown in Figure 1 as the synthesis framework to show the utility of the intermediate form. The figure is organized into three columns: the synthesis tasks on the left, the user interface on the right, and the intermediate representation in the middle. The intermediate representation is composed of four basic components: the state table, the unit list, the connections list, and the symbol list.

The user typically specifies the behavior of the design in a behavioral specification language like VHDL [LiGa88] or EXEL [DuGa88]. The language compiler parses the input into a data structure which is captured in the first level of the intermediate form, by creating the the symbol list and the operation sequence table. In addition, if the user has specified some structure along with the behavior, this structure is captured in the unit and connectivity lists. Since the designer may not know the duration of the clock while describing the behavior, the input is naturally described using sequences of groups of operations.

Figure 1. A Typical Behavioral Synthesis Environment

This description forms a two-level hierarchy, where the first level is the sequence of operation groups, and the second level consists of each operation group individually. The operation group is much like a basic-block in a standard programming language; it may span several states depending upon the duration of the system clock. We refer to this intermedi-

ate form as the *super-state table* <sup>1</sup>. This table describes the operations performed in each super-state, and the sequencing between super-states.

In the next level of design, we use a state allocator to "slice" the super-states into states of the design. Operation sequences are assigned to specific states of the final design. This task is also called *state scheduling* in the literature [PaKn87] [PaGa87]. The *op-based state table* is generated by this synthesis task. This table uses conditional triplets to capture the behavior of the design on a state-by-state basis. Each triplet describes the condition tested, the operations performed and the next state to be executed. At this point in the synthesis framework, the temporal ordering of operations has been fixed, but we have not specified how exactly these operations are to be performed in hardware; this is determined by the tasks of resource allocation and binding.

Resource allocation determines the type and number of structural components needed to implement the structural design. These components are typically drawn from a generic library [Dutt88], which contains information about each type of component. Since buses are also treated as components, this task updates both the unit list and the connection list.

Resource binding assigns specific instances of functional and storage components to abstract operations and variables in the op-based state table. At this point, the design is stored in the unit-based state table. This table uses triplets to describe the structural operation of the design on a state-by-state basis. Each triplet describes the unit generating the conditional, the units performing the conditional operations, and the next state to be executed. The operations in the unit-based state table only specify which components are to be used as inputs for the operation; they do not specify the paths for these inputs.

<sup>&</sup>lt;sup>1</sup> The term "super-state" is used to indicate two levels of hierarchy: sequences of super-states, and the actual

The task of connection binding adds these connection paths to the unit-based state table to create a *unit-based state table with connections*. This table describes the complete structure of the synthesized data path, but lacks the control signals for the components.

Finally, the task of control generation creates control lines for every functional or storage unit that needs to be controlled. The *control based state table* captures this functionality with triplets that describe the control lines conditionally activated in each state, and the subsequent next state.

At each level of the synthesis process, the appropriate synthesis task can be performed automatically (by a set of algorithms and rules), or can be performed manually by the user through the user interface. The user interface displays the units and connections in the form of a schematic, and displays the state tables visually. This permits the user to comprehend the complete behavior and structure of the design at each level.

Note that we have introduced this particular framework solely for the purpose of illustrating the use of the intermediate form. The tasks of state binding, resource allocation, unit binding, connection binding and control generation can be performed in different combinations; the annotated state tables described in this report can still be used as the intermediate exchange format between the various synthesis tasks, regardless of their order of invocation.

states within a super-state.

CHAPTER 3.

BIF: The Behavioral Intermediate Format

3.1. General Description

The Behavioral Intermediate Format (BIF) makes use of state tables annotated with a

list of symbols, units, and connections to describe a design at each level of abstraction in

the synthesis process. Conceptually, a state table is composed of entries which indicate

what actions are performed in each state, the conditions under which those actions are to

occur, and the next state to proceed to after completion of the actions. However, since the

design spans several levels of abstraction (as illustrated in Figure 1), we maintain a slightly

different format for each abstraction level in the design process.

The state tables and associated information lists are progressively updated as the syn-

thesis process proceeds. At each level of abstraction the user can, either directly or through

the use of tools, modify the state table and/or any of the information lists.

In this section, we will use a simple example to illustrate the basic format of the anno-

tated state tables at each level in the design process. A brief tutorial of the intermediate

form is described in Appendix I, while the detailed syntax is given in Appendix II.

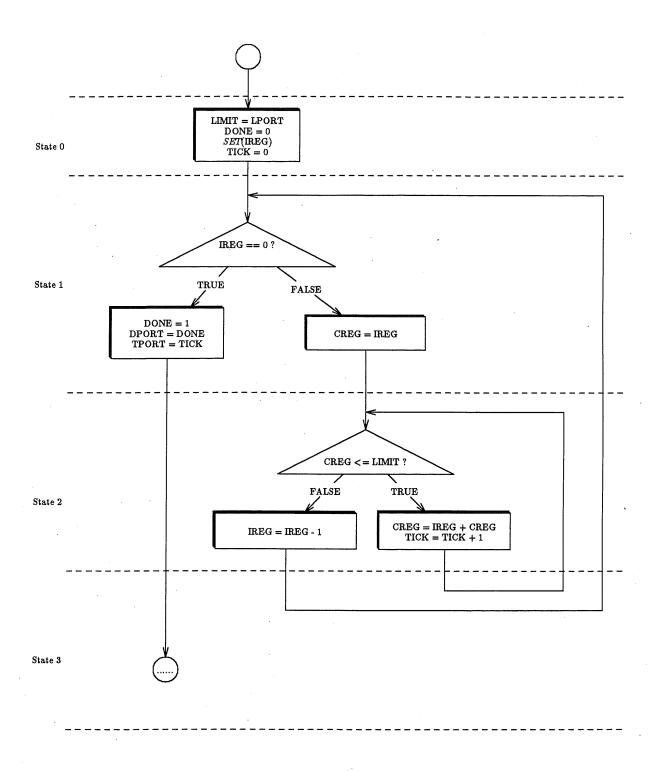

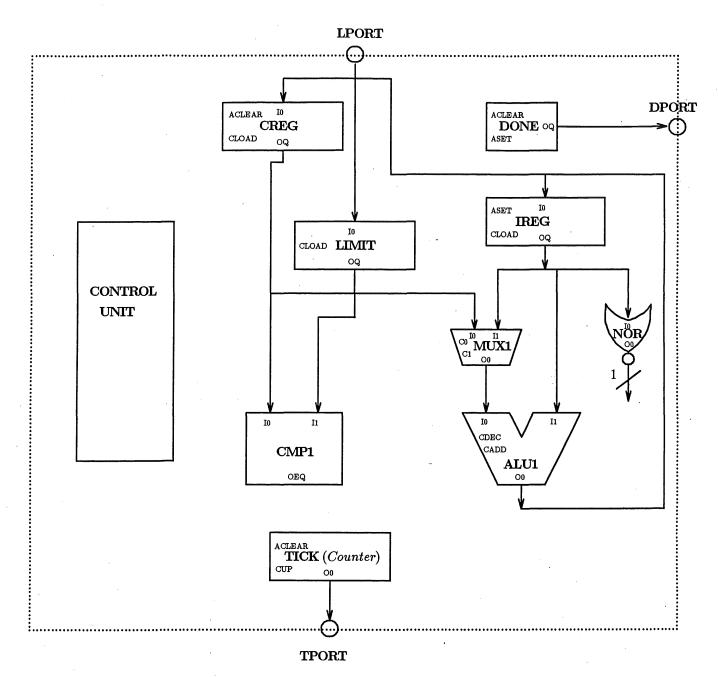

Figure 2 shows a flowchart for a design that performs the function:

$$\sum_{i=1}^{IREG} (LIMIT \bmod i)$$

The design accumulates the sum of all moduli for an externally specified value (LIMIT),

Figure 2. Moduli Accumulator Behavior

with respect to every number equal to and below the value set in an internal register IREG.

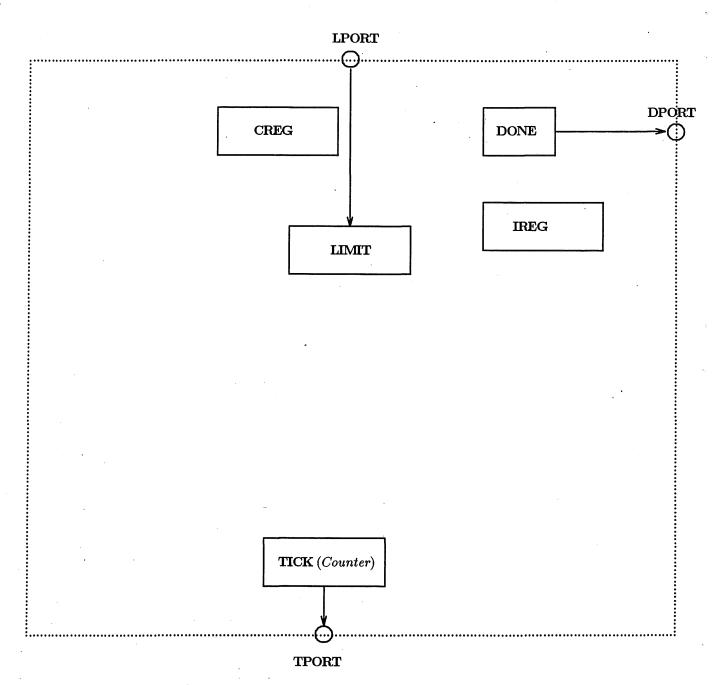

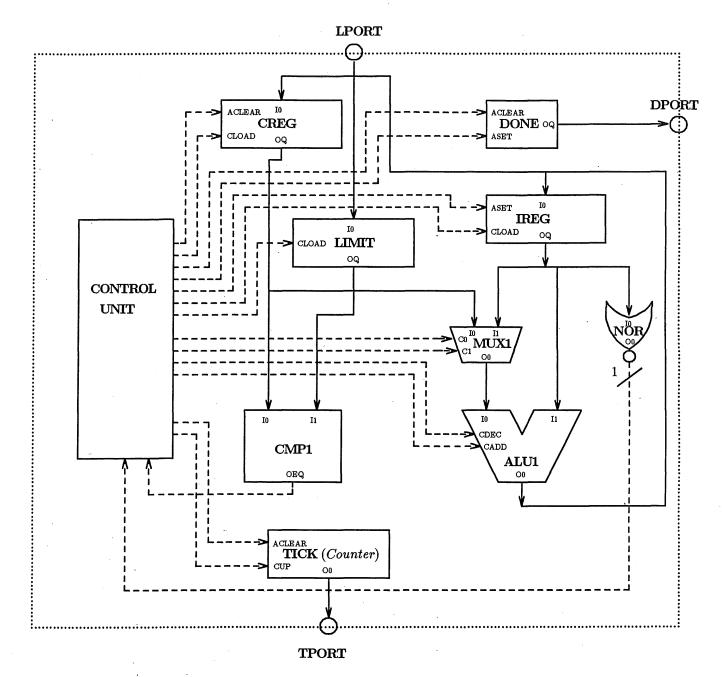

In this specification, we assume that the user has already specified the states of the machine. The initial structure specified by the user is shown in Figure 3. LPORT is the port through which the external limit is specified, while TPORT and DPORT are used to

Figure 3. Moduli Accumulator Initial Structure

output the accumulated sum and a flag signifying end of the task. Internally, the user has specified the several components and connections: registers IREG, CREG, DONE and LIMIT; the counter TICK; and the connections between ports LPORT, TPORT, DPORT and LIMIT, TICK and DONE respectively. IREG is set to a pre-determined start value for the algorithm, while CREG functions as a temporary register, and TICK keeps track of the accumulated moduli. LIMIT is loaded with the external value with respect to which the accumulated moduli is to be computed. DONE indicates the status of the completed task.

In state 0 of the behavior, we load the LIMIT register with the value on LPORT, clear DONE and TICK, and set IREG to the predetermined value.

States 1 and 2 describe a nested loop, where the outer loop decrements IREG by one, and the inner loop computes the modulus of LIMIT with respect to the current value of IREG.

When IREG is equal to 0, the task is completed. DONE is set to 1 and is asserted on DPORT, while the accumulated sum in TICK is sent out on TPORT.

#### 3.2. The Operations-Based State Table Format

Since the input behavior already has states assigned to it, we capture initial behavior using the operations-based state table (OBST). The OBST contains triplets for each state, describing the condition tested, conditional operations performed, and the next state information.

Figure 4 shows the operations-based state table for the example shown in Figure 2. In this example, the user has also specified a partial structure consisting of the external ports

| Present State | Condition     | (Value) | Actions                                   | Next State |

|---------------|---------------|---------|-------------------------------------------|------------|

| 0             | -             | TRUE    | LIMIT = LPORT DONE = 0 SET(IREG) TICK = 0 | 1          |

|               |               | TRUE    | DONE = 1                                  | 2          |

| 1   IREG == 0 | IREG == 0     | FALSE   | CREG = IREG                               | 3          |

|               |               | TRUE    | CREG = CREG + IREG<br>TICK = TICK + 1     | 2          |

| 2             | 2 CREG <= LIM | FALSE   | IREG = IREG - 1                           | 1          |

| 3             |               |         |                                           |            |

Figure 4. Operations-Based State Table

and a few registers. This structure is stored in the symbol list and the unit list of the OBST. The structure is identical to that of Figure 3, since no additional units or connections have been allocated.

## 3.3. The Unit-Based State Table Without Connections

The task of unit allocation and unit binding assigns additional components (if necessary) and binds operations in the OBST to specific units. The output of this phase is the

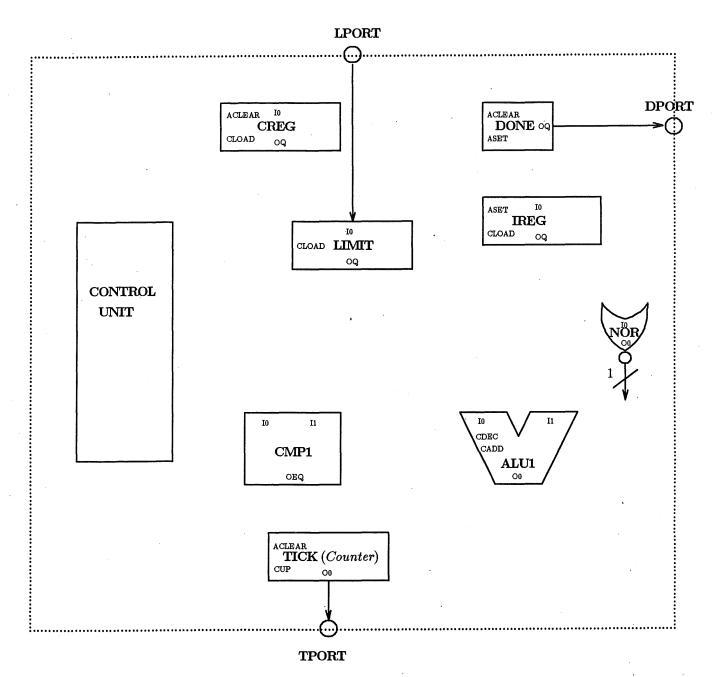

unit-based state table without connections (UBST). Each triplet in this table describes the condition tested, the unit name and the operation performed by the unit, the list of inputs used for the operation, and the next state information. Figure 5 shows the UBST for the design after unit allocation and binding. Figure 6 is a schematic displayed from the unit and connection lists associated with the UBST. Note that at this point in the design, all the components have been allocated to the design by the synthesis system, but no connections have been generated.

#### 3.4. The Unit-Based State Table With Connections

The task of connection binding traverses the UBST to determine the connections required to effect data transfers between various components in the design. The unit-based state table with connections (UBCST) is created after connection binding is performed. The resulting design describes the complete data path excluding control signals for units and registers. For our running example, Figure 7 shows the UBST for the design after unit allocation and binding. Figure 8 shows the complete data path schematic generated from the unit and connection lists associated with the UBCST.

#### 3.5. The Control-Based State Table

The control-based state table (CBST) is created in preparation for the task of control compilation. Like the previous state table, each entry is a triplet which describes the condition tested, the control signals asserted on that condition, and the next state information. Figure 9 shows the CBST for the design after control generation, while Figure 10 shows the schematic of this complete design generated from the unit and connection lists. The complete synthesized design is now represented by the CBST annotated with the unit and

| Present State | Condition        | (Value) | Actions                                                                                                                                            | Next State |

|---------------|------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 0             | -                | TRUE    | LIMIT(REG; Ops: LOAD; Inps: LPORT) DONE(REG; Ops: CLEAR) IREG(REG; Ops: SET) TICK(COUNTER; Ops: CLEAR)                                             | 1          |

|               |                  |         | DONE(REG; Ops: SET) NOR(GNOR_GATE; Ops: GNOR; Inps: IREG.OQ)                                                                                       | 2          |

| 1 NOR.00 == 1 |                  | FALSE   | CREG(REG; Ops: LOAD) NOR(GNOR_GATE; Ops: GNOR; Inps: IREG.OQ)                                                                                      | 3          |

|               |                  | TRUE    | ALU1(ALU; Ops: ADD Inps: CREG.OQ, IREG.OQ) CREG(REG; Ops: LOAD; Inps: ALU1.O0) TICK(COUNTER; Ops: UP) CMP1(CMP; Ops: LEQ; Inps: CREG.OQ, LIMIT.OQ) | 2          |

| 2             | 2 CMP1.OLEQ == 1 | FALSE   | ALU1(ALU; Ops: DEC Inps: IREG.OQ) IREG(REG; Ops: LOAD; Inps: ALU1.O0) CMP1(CMP; Ops: LEQ; Inps: CREG.OQ, LIMIT.OQ)                                 | 1          |

| 3             |                  |         |                                                                                                                                                    |            |

Figure 5. Unit-Based State Table

Figure 6. UBST Annotated Structure

| Present State | Condition      | (Value) | Actions                                                                                                                                                                              | Next State |

|---------------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|               | -              | TRUE    | LIMIT(REG; Ops: LOAD; Inps: LPORT) DONE(REG; Ops: CLEAR) IREG(REG; Ops: SET) TICK(COUNTER; Ops: CLEAR)                                                                               | 1          |

|               |                | TRUE    | DONE(REG; Ops: SET) NOR(GNOR_GATE; Ops: GNOR; Inps: IREG.OQ)                                                                                                                         | 2          |

| 1             | NOR.O0 == 1    | FALSE   | CREG(REG; Ops: LOAD) NOR(GNOR_GATE; Ops: GNOR; Inps: IREG.OQ)                                                                                                                        | 3          |

| 2             | CMP1 OLEO 1    | TRUE    | MUX1(MUX; Ops: I0; Inps: CREG.OQ) ALU1(ALU; Ops: ADD Inps: MUX1.O0, IREG.OQ) CREG(REG; Ops: LOAD; Inps: ALU1.O0) TICK(COUNTER; Ops: UP) CMP1(CMP; Ops: LEQ; Inps: CREG.OQ, LIMIT.OQ) | 2          |

| 2             | CMP1.OLEQ == 1 | FALSE   | MUX1(MUX; Ops: I1; Inps: IREG.OQ) ALU1(ALU; Ops: DEC; Inps: MUX1.O0) IREG(REG; Ops: LOAD; Inps: ALU1.O0) CMP1(CMP; Ops: LEQ; Inps: CREG.OQ, LIMIT.OQ)                                | 1          |

Figure 7. Unit-Based State Table With Connections

Figure 8. UBCST Annotated Structure

| Present State | Condition      | (Value) | Actions                                                       | Next State |

|---------------|----------------|---------|---------------------------------------------------------------|------------|

| 0             | -              | TRUE    | LIMIT.CLOAD = 1 DONE.ACLEAR = 1 IREG.ASET = 1 TICK.ACLEAR = 1 | 1          |

|               | NOD OO 1       | TRUE    | DONE.ASET = 1                                                 | 2          |

| 1             | 1 NOR.O0 == 1  | FALSE   | CREG.CLOAD = 1                                                | 3          |

|               |                | TRUE    | MUX1.CI0 = 1 ALU1.CADD = 1 CREG.CLOAD = 1 TICK.CUP = 1        | 2          |

| 2             | CMP1.OLEQ == 1 | FALSE   | MUX1.CI1 = 1<br>ALU1.CDEC = 1<br>IREG.CLOAD = 1               | 1          |

| 3             |                |         |                                                               |            |

Figure 9. Control-Bases State Table

Figure 10. CBST Annotated Structure

connection lists.

#### 3.6. Asynchronous Behavior

Designs exhibiting asynchronous behavior can also be described using BIF. Asynchronous behavior is described using the notions of events and event-states. An "event" is a change in the value of a signal (or variable) which activates an "event-state"; the event-state describes the condition(s) tested, the operations to be performed and the next event-state information. BIF uses a separate event column in the state tables to describe the event condition which activates the particular state.

In synchronous designs, the system clock is the default event that sequences the design through different states of the machine. We therefore omit the event field in purely synchronous design descriptions. However, when a design exhibits a mixture of synchronous and asynchronous behavior, the clock can be used as an explicit event to indicate states that are entered synchronously.

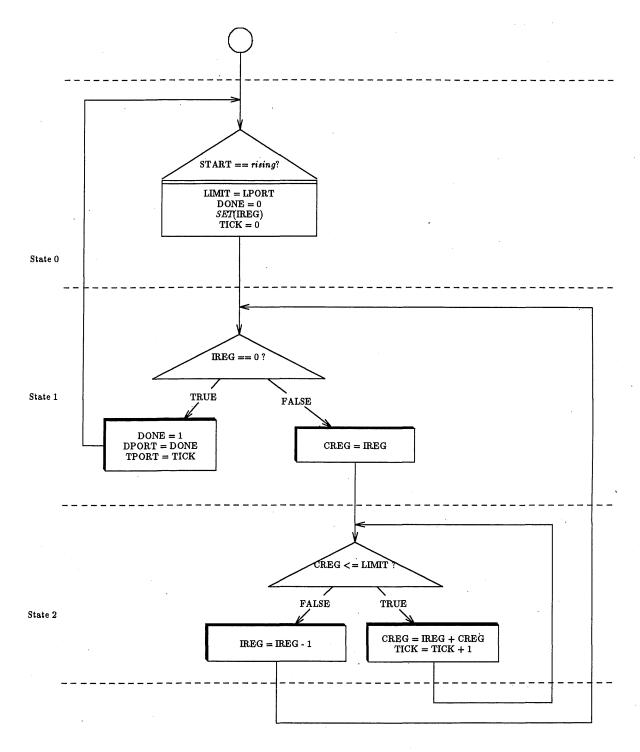

We will use a modified version of the moduli accumulator shown in Figure 2 to illustrate the use of an op-based event state table. Figure 11 shows a flowchart describing a similar moduli accumulator which begins operation only when the signal on the port START rises. State 0 of the design is entered when this event occurs. Subsequently, states 1 and 2 are synchronous with respect to the clock and therefore use the system clock as the default event.

Figure 12 shows the operations-based event state table for this new moduli accumulator behavior. The table has an extra column which describes the event triggering entry into the next event-state. State 0 in this table is entered only on the event START RIS-ING, while states 1 and 2 have the clock as the default events.

Figure 11. Moduli Accumulator with External Event

| Present State | Condition       | (Value) | Actions                                   | Next State | Next State Event |

|---------------|-----------------|---------|-------------------------------------------|------------|------------------|

| 0             |                 | TRUE    | LIMIT = LPORT DONE = 0 SET(IREG) TICK = 0 | 1          | (clock)          |

| . 1           | IREG == 0       | TRUE    | TPORT = TICK DONE = 1 DPORT = DONE        | . 0        | START == RISING  |

|               |                 | FALSE   | CREG = IREG                               | 3          | (clock)          |

|               |                 | TRUE    | CREG = CREG + IREG<br>TICK = TICK + 1     | 2          | (clock)          |

| 2             | CREG <= LIM FAL | FALSE   | IREG = IREG - 1                           | 1          | (clock)          |

Figure 12. Operations-Based Event State Table

#### CHAPTER 4.

#### **User Interaction Scenarios**

The annotated state table representation described in this report serves as a standard exchange format for use by various synthesis tasks. This format not only permits modification, upgrading and replacement of the tools for various synthesis tasks, but also provides a "manual override" feature by allowing the user to perform any or all of these synthesis tasks manually. This is a unique advantage of the state table representation over flowgraph-based representations, which only capture the abstract behavior, or netlist-based representations which capture pure structure. In this chapter we describe several user interaction scenarios that demonstrate the utility of the state table format as a convenient intermediate representation.

#### 4.1. User Specified Structural Constraints

Quite often, the designer may want to specify some initial hardware allocation or some partial design structure as a starting point for the synthesis tasks. By doing this, the user is specifying structural constraints before the task of synthesis begins.

#### 4.1.1. Partial Resource Allocation

If the user partially allocates resources such as a certain number of functional units, storage elements and buses, these resources are stored in the unit list. These pre-specified units constrain the task of resource allocation (see Figure 1).

#### 4.1.2. Partial Design Structure

The user may wish to specify a partial design structure consisting of an interconnection of pre-allocated functional units, storage elements and buses. The components in the partial design are stored in the unit list, while the connections are captured in the connection list. This partial design constrains both the task of resource allocation and connection binding.

# 4.2. User Specified Bindings

In addition to specifying partial resources and their connections, the user may wish to selectively bind certain behavioral operations and variables to components and connections. This is useful, for instance, when the designer has determined the critical path in the design, and wants to force the binding of fast components along the critical path in the behavior. Some input behavioral languages like EXEL [DuGa88] have special constructs that allow the user to selectively bind resources to abstract variables and operations.

This type of binding is a user specified behavior-to-structure "link" that must be used as a constraint through all the synthesis levels. The pre-allocated components constrain the resource allocation task, while the user-bindings constrain both the resource and connection binding tasks. We represent each such binding explicitly in the state table by annotating the corresponding behavioral variable or operator with the structural component or connection it is bound to.

# 4.3. Modification of Compiled Designs

An experienced designer who sees the structure generated by an automatic synthesis system can, quite often, eyeball parts of the synthesized structure that are inefficient, unrealistic or which just seem odd to the experienced eye. The designer may want to correct the design by manually modifying parts of the compiled structural design. This type of user modification is a unique feature supported by BIF; existing behavioral synthesis systems do not permit such modifications.

A typical example would be an automatically synthesized structure where a register A is cleared by loading the value "0" from a constant register  $^1$ . If the register A is loaded through another source, the design also has a mux at the input to register A to switch between the two sources. For this design, the designer would like to modify the generated design manually by replacing loading of the zero register with the activation of the asynchronous clear input on the register. This eliminates the zero register, as well as the mux at the input to register A.

These kinds of changes are handled very cleanly in BIF. Structural changes to the compiled design are updated in the unit list and the connection list. Since there is no guarantee that the design will still function correctly after user-modification, the behavior must be verified on this new design structure by simulation. If the simulation does not satisfy the intended behavior, the complete synthesis process must be restarted from the beginning, using the user specified structural changes as an additional structural constraint.

<sup>&</sup>lt;sup>1</sup> The design model behind most existing synthesis tools cannot handle asynchrony, and hence cannot generate the asynchronous signal required to clear the register.

If the designer modifies the synthesized design by changing the unit list, the synthesis process must start from the state binding phase. If only the connections have been modified in the structure, then resynthesis can begin at the connection binding phase.

#### 4.4. State Table Modification

If we allowed complete freedom for the user to perform any or all of the synthesis tasks in the design process, the user would have to modify the state table in addition to the unit and connection lists.

Since this type of modification can easily cause the behavior of the design to be violated, state table modification must immediately be followed by a simulation to verify that the functionality of the original specification has not changed. Following verification, synthesis tasks can begin from the level where the user change is affected.

For instance, if the user modifies the op-based state table, we first require a verification of the new op-based state table. If the behavior of the new table is unchanged, we use this new state table as a starting point for the ensuing synthesis tasks of resource allocation, resource binding, connection binding and control generation.

#### CHAPTER 5.

#### Summary

In this report, we described BIF, an intermediate representation format that captures the complete behavior and structure of a design at each level of the behavioral synthesis process. This representation obviates the need to maintain complex behavior-to-structure links from the abstract behavior down to the final structure, by capturing these links only where necessary: at each level of the design process.

BIF is an intermediate form which supports several novel design scenarios: specification of partial design structures, user binding of behavioral constructs to structural elements, and user modification of compiled designs. This permits synthesis tools to be interchanged, and also allows the user to manually replace the task of a synthesis tool.

The resulting design paradigm allows an evolution towards completely automatic synthesis, where synthesis tasks that are not fully understood may be performed manually by a designer, while well understood tasks are performed using synthesis algorithms. Synthesis algorithms can therefore be easily incorporated, modified, upgraded or replaced as necessary.

#### 5.1. Acknowledgements

The authors are grateful to Joe Lis and Nels Vander Zanden for their helpful comments.

#### CHAPTER 6.

#### References

- [ChGa89] G. D. Chen and D. D. Gajski, "An Intelligent Component Database for Behavioral Synthesis," Technical Report (in preparation), U.C. Irvine, February, 1989.

- [DuGa88] N. D. Dutt and D. D. Gajski, "EXEL: An Input Language for Extensible Register Transfer Compilation," *Technical Report* 88-11, U.C. Irvine, April, 1988.

- [Dutt88] N. D. Dutt, "GENUS: A Generic Component Library for High Level Synthesis," Technical Report 88-22, University of California at Irvine, September, 1988.

- [GrKP85] J. Granacki, D. Knapp, A. Parker, "The ADAM Advanced Design Automation System: Overview, Planner and Natural Language Interface," 22nd Design Automation Conference (June, 1985).

- [LiGa88a] Y.-L. Lin and D. D. Gajski, "LES: A Layout Expert System," *IEEE Trans. on Computer-Aided Design*, Vol. CAD-7, Number 8, Aug. 1988.

- [LiGa88b] J. S. Lis and D. D. Gajski, "Synthesis from VHDL," Proc. ICCD, Oct. 1988.

- [McPC88] M.C. McFarland, A.C. Parker and R. Camposano, "Tutorial on High Level Synthesis," 25th Design Automation Conference, July 1988

- [PaGa86] B. Pangrle, D. Gajski, "Slicer: A State Synthesizer for Intelligent Silicon Compilation" *Proceedings ICCAD*86 Santa Clara, CA, (Oct, 1986).

- [PaKn88] P.G. Paulin and J.P. Knight, "Force Directed Scheduling in Automatic Data Path Synthesis," Proc. 24th IEEE Design Automation Conference, Miami, FL, June 1987.

- [PaPM86] A. C. Parker, J. Pizarro, M. Milnar, "MAHA: A Program for Datapath Synthesis" 23rd Design Automation Conference IEEE, Las Vegas, NV (July, 1986).

- [THBR87] D. E. Thomas, R. L. Blackburn and J. V. Rajan, "Linking the Behavioral and Structural Domains of Representation for Digital System Design," *IEEE Trans. CAD*, Vol. CAD-6, No. 1, January 1987.

- [Thom86] D. E. Thomas, "Automatic Data path Synthesis," Design Methodologies, (S. Goto, editor), Chapter 13, Elsevier Science Publishers, 1986.

- [VaGa88] N. Vander Zanden and D. D. Gajski, "MILO: A Microarchitecture and Logic Optimizer," *Proc.* 25th D. A. C., Anaheim, CA, June 1988.

#### APPENDIX A.

## A Tutorial Introduction to BIF

#### A.1. General Description

This section is devoted to a syntactical description of the text-based form for state table representation. The row-column approach to state table display (e.g. Figure 4) does not work well for text viewers or editors. It is necessary to provide an alternate format that is easy to enter or edit using a common text editor such as vi or emacs. This format depicts row entries as successive vertical entries in a text file with corresponding key words representing the various state table constructs.

Each of the four state tables has a common structural format composed of a constant ordering of keywords and delimiters.

## • Table Identifier

At the beginning of a given table there is a keyword which identifies which of the four state tables it is.

```

OPS_BASED /* operations-based. */

... /* table entries */

UNIT_BASED_NC /* unit-based without connections. */

... /* table entries */

UNIT_BASED /* unit-based with connections. */

... /* table entries */

CONTROL_BASED /* control-based. */

... /* table entries */

```

#### State Entries

Following the table identifier are any number of state entries composed of the keyword STATE, a colon (':'), a number identifying the state, a possible unconditional action entry, and a number of triplets describing the conditions, the actions to be performed in that state, and the next state, along with an optional event for the next state. Commas (',') separate all entries following state number, and a semicolon (';') terminates the list of entries. (The ellipses ('...') in all of the following examples indicate entries omitted for readability).

```

STATE: 2 /* state two. */

..., /* first entry */

..., /* nth entry */

...; /* last entry */

```

#### Unconditional Action Entry

The unconditional action entry specifies an action that is to always take place in that state. It is delimited by curly brackets ('\{\}') and is composed of the keyword UNCOND\_ACTIONS, a colon, and a list of actions in a format identical to the actions list in a triplet entry (See below).

```

{

UNCOND_ACTIONS:

...

}

```

#### Triplets

Each triplet is delimited by curly brackets and is composed of three parts: condition, actions, and next state information.

}

#### Conditions

Conditions are indicated by the keyword COND, a colon, an expression possibly enclosed in parentheses (()), and a semicolon.

# Expressions

The expression in the condition is any kind of logical construct that will evaluate to either TRUE (non-zero) or FALSE (zero). (Keywords true and false are legitimate expressions). Currently, sum-of-products form of boolean equations, comparison to constants, and equality checks against constants are allowed, with variables having slightly different meanings in the operations-based state table form. Operators are too numerous to describe here. See appendix B for a BNF description of expressions and operators.

```

COND: (X OR Y); /* Operations-based state table */

...

COND: (X OR Y > 4); /* Operations-based state table */

...

COND: (AU1.SUM > 64); /* any other state table */

...

COND: (AU1.sum AND CMP1.ogt); /* any other state table */

```

## • Else Expression

The else special-case is evaluated uniquely among the expressions. If the expression in a condition is the keyword ELSE then all conditions in previous triplets up to a previous ELSE expression (or the beginning of the state entry) are considered to be relevant to this condition. That is, if all previous conditions fail then the ELSE condition evaluates to TRUE. If one or more previous conditions do not fail then the ELSE condition evaluates to

FALSE. (NOTE: This may require restructuring of the entries by the user to ensure correct condition grouping).

#### • Next State Specification

The state to proceed to after completing the list of actions is indicated by the keyword NXTSTATE, a colon, a state number, an optional event specification and a terminating semicolon.

NXTSTATE: 4; /\* Proceed to state 4 after actions \*/

#### • Events

The optional event triggering the next state transition is specified by the keyword **EVENT** followed by a colon and an expression using the **EXEL** [DuGa88] syntax form for asynchronous event timing. For sequential designs where states are activated by the clock the keyword **CLOCK** can be used.

NXTSTATE: 4, EVENT: GPORT == rising; NXTSTATE: 5, EVENT: CLOCK; Note that omitting the event specification for the next state implies a transition on the next clock.

#### Actions List

Actions to perform in a given state are indicated by the keyword ACTIONS, a colon, and a comma separated action list terminated by a semicolon.

# ACTIONS: ..., /\* First action \*/ ..., /\* nth action \*/ ...; /\* Last action \*/

#### Actions

The specification format for a single action is differs among the four state table formats. See the specification for each table format under heading *Actions*.

Fields or entries that are not used in a particular state table can be left blank, or the keyword null can be used.

C-style commenting (i.e. /\* comment \*/) is allowed anywhere in the state table.

#### A.2. Specific Descriptions of Each State Table Format

#### A.2.1. Operations-based State Table

The operations-based state table describes actions to be performed in each state in terms of assignment statements. Variable names are not bound to units and instead represent values to be input and output at various stages of the design. • Actions

Actions, listed following the keyword **ACTIONS**, are expressions, variables, and constants combined by logical or arithmetical operators. See the **EXEL** [DuGa88] input language description for a complete description of the expression format.

# ACTIONS:

```

X = Y + 32, /* Addition */

X\{0..3\} = 0, /* Selector function */

Z = X * Y; /* Multiplication */

```

Unique to the operations based table is component binding specifications. Optionally immediately following any variable name can be a component name surrounded by curly brackets. This will be interpreted to mean that that variable will be represented by that component in that particular action.

#### A.2.2. Unit-based State Table With and Without Connections

Both the unit-based state table (UBCST) and the unit-based state table without connections (UBST) have the same syntax. Their differences are conceptual and external only.

#### Actions

Actions, listed following the keyword ACTIONS in the state table, are represented by a unit name followed by a group of attributes delimited by parentheses.

####

#### Unit Attributes

Unit attributes describe a unique unit name, the operations performed by the unit, and the inputs to the unit. They are listed within the parentheses as unit name, semicolon,

the keyword OPS, a colon, a list of operations corresponding to control input names, a semicolon, the keyword INPS, a colon, and a list of output pin names from other units.

CNT (counter; OPS: inc,dec; INPS: ALU1.sum, CTR.I[0])

#### • Pin Names

Pin names are formed by concatenating the actual pin name of the unit with the unique unit name.

**COND**: (ALU1.sum == 0) /\* unit-based state table \*/

#### A.2.3. Control-based State Table

The control-based state table describes actions in terms of the values of each unit's control input lines. At each state the pin names of each unit are given with the values they are to assume in that state, either 1 or 0.

#### **ACTIONS:**

ADD1.carryin = 0, ALU1.czero = 1, ALU2.crinhi = 1, SHF1.cen = 1;

#### APPENDIX B.

#### **BIF** Syntax

## **B.1.** Operations Based State Table Syntax

```

State Table

table_ident entries ';'

table

State\ Table\ Identifier

table_ident

OPS_BASED

State Table Entries

entry entries ';' entry

entries

Single State Table Entry

STATE ':' state triplets

entry

STATE ':' state UC_ACTIONS

uncond_actions triplets

Present State

dig_seq

state

Unconditional Actions

action | uncond_actions ',' action

uncond_actions

Triplets

triplet | triplets ',' triplet

triplets:

```

```

Single Triplet

```

```

triplet

empty |

COND ':' condition ';'

ACTIONS ':' actions ';'

NXTSTATE ':' state ';'

Condition

'('cond_expr')'

condition

Condition Expression

cond_expr

variable compare_op expr | pinname compare_op expr |

bool_expr

Compare Operation Types

'==' | '!=' | '<' | '>' | '<=' | '>='

compare_op :

Actions

: action actions ',' action

actions

Single Action

action

empty unit_action ops_action

Unit Based Action

comp_name '(' comp_type ';' operations ';' inputs ')'

unit_action

Operations Based Action

variable ':=' expr

ops_action

Component Name

```

```

comp_name : identifier

Component Type

comp_type : identifier

Operations

operations : empty | OPS ':' op_list

Operations List

op_list : op | op_list ',' op

Single Operation

: empty op_type

op

Operation \ Type

: identifier

op_type

Inputs

inputs : empty | INPS ':' inp_list

Input List

inp_list: input | inp_list ',' input

Single Input

input : empty | variable | pinname

Expression

: arith_expr | bool_expr | shift_expr

expr

```

#### Arithmetic Expression

arith\_expr

'(' arith\_expr ')' |

arith\_expr '+' arith\_expr | arith\_expr '-' arith\_expr | arith\_expr '\*' arith\_expr | arith\_expr '/' arith\_expr |

variable | pinname | dig\_seq

;

## Boolean Expression

bool\_expr

lgbl\_expr | btbl\_expr

#### Logical Boolean Expression

lgbl\_expr

'(' lgbl\_expr ')' |

lgbl\_expr LAND gbl\_expr | lgbl\_expr LOR gbl\_expr | lgbl\_expr LNOT gbl\_expr | lgbl\_expr LNAND gbl\_expr | lgbl\_expr LXOR gbl\_expr | lgbl\_expr LXNOR gbl\_expr |

variable | pinname | dig\_seq

Bitwise Logical Boolean Expression

btbl\_expr

;

'(' btbl\_expr ')'

btbl\_expr '&' btbl\_expr | btbl\_expr '|' btbl\_expr |

btbl\_expr '^' btbl\_expr | btbl\_expr '~' btbl\_expr |

btbl\_expr '~&' btbl\_expr | btbl\_expr '~' btbl\_expr |

btbl\_expr '^-' btbl\_expr | variable | pinname | dig\_seq

Shift Expression

shift\_expr

'(' shift\_expr ')'

shift\_expr SHL shift\_expr | shift\_expr SHR shift\_expr | shift\_expr ROTL shift\_expr | shift\_expr ROTL shift\_expr |

variable | pinname | dig\_seq

Variable

variable

value\_ident

Pin Name

pinname

comp\_name '.' portname

Port Name

portname

value\_ident

Port or Variable Identifier

value\_ident

identifier

identifier '[' dig\_seq ']' |

identifier '{' dig\_seq '..' dig\_seq '}' | identifier '{' bound\_component '}'

Bound Component

$bound\_component$

identifier

Identifier

Lex Format:  $[a-zA-Z][a-zA-Z0-9_]*$

identifier

**IDENTIFIER**

;

Digit Sequence

Lex Format: [0-9xX]+

dig\_seq

DIGSEQ

#### B.2.

# Unit Based State Table Syntax

```

State Table

table_ident entries ';'

table

State Table Identifier

table_ident :

UNIT_BASED

State Table Entries

entry entries ';' entry

entries

Single State Table Entry

STATE ':' state triplets | STATE ':' state UC_ACTIONS

entry

uncond_actions triplets

Present State

state

dig_seq

Unconditional Actions

action uncond_actions',' action

uncond_actions :

Triplets

triplet | triplets ',' triplet

triplets:

Single Triplet

triplet

empty

COND ':' condition ';'

ACTIONS ':' actions ';'

next_state_info ';'

```

**'}'**

```

Next State Information

```

next\_state\_info

NXTSTATE ':' state

NXTSTATE ':' state; event

Asynchronous Event

event

EVENT ':' cond\_expr |

CLOCK

Condition

condition

'('cond\_expr')'

$Condition\ Expression$

cond\_expr :

pinname compare\_op expr | bool\_expr

Compare Operation Types

compare\_op :

'==' | '!=' | '<' | '> ' | '<=' | '>='

Actions

actions

: action | actions ',' action

Single Action

action

: empty | comp\_name '(' comp\_type ';' operations ';' inputs ')'

;

Component Name

comp\_name :

identifier

Component Type

comp\_type

identifier

;

```

Operations

: empty OPS ':' op_list

operations

Operations List

op_list

op op_list ',' op

Single Operation

empty op_type

op

Operation Type

op_type

: identifier

Inputs

inputs : empty | INPS ':' inp_list

Input\ List

inp_list: input | inp_list ',' input

Single Input

: empty pinname

input

Expression

arith_expr | bool_expr | shift_expr

expr

Arithmetic\ Expression

'('arith_expr')' |

arith_expr'+'arith_expr|arith_expr'-'arith_expr|

arith_expr'*'arith_expr|arith_expr'/'arith_expr|

arith_expr

```

pinname | dig\_seq

# Boolean Expression

```

lgbl_expr | btbl_expr

bool_expr

Logical Boolean Expression

'(' lgbl_expr ')' |

lgbl_expr

lgbl_expr LAND gbl_expr | lgbl_expr LOR gbl_expr |

lgbl_expr LNOT gbl_expr lgbl_expr LNAND gbl_expr

lgbl_expr LXOR gbl_expr | lgbl_expr LXNOR gbl_expr |

pinname | dig_seq

Bitwise Logical Boolean Expression

'(' btbl_expr ')'

btbl_expr

btbl_expr '&' btbl_expr | btbl_expr '' btbl_expr |

btbl_expr '^' btbl_expr | btbl_expr '~' btbl_expr |

btbl_expr '~&' btbl_expr | btbl_expr '~' btbl_expr |

btbl_expr '^~' btbl_expr

pinname | dig_seq

Shift Expression

'(' shift_expr ')'

shift_expr

shift_expr SHL shift_expr | shift_expr SHR shift_expr |

shift_expr ROTR shift_expr | shift_expr ROTL shift_expr |

pinname | dig_seq

Pin Name

comp_name '.' value_ident

pinname

Port or Variable Identifier

identifier | identifier '[' dig_seq ']' |

value_ident

identifier '{' dig_seq '..' dig_seq '}'

Identifier

```

Lex Format:  $[a-zA-Z][a-zA-Z0-9_]*$

identifier

**IDENTIFIER**

$Digit\ Sequence$

$Lex\ Format: [0\text{-}9xX] +$

$\operatorname{dig\_seq}$

DIGSEQ

# B.3. Control Based State Table Syntax

```

State Table

table_ident entries ';'

table

State Table Identifier

table_ident

CONTROL_BASED

. ;

State Table Entries

entry entries ';' entry

entries

Single State Table Entry

STATE ':' state triplets | STATE ':' state UC_ACTIONS

entry

uncond_actions triplets

Present State

state

dig_seq

Unconditional Actions

uncond_actions

action uncond_actions ',' action

;

Triplets

triplets:

triplet | triplets ',' triplet

Single Triplet

triplet

empty

COND ':' condition ';'

ACTIONS ':' actions ';'

next_state_info ';'

```

```

Condition

condition

'(' cond_expr ')'

Condition Expression

pinname compare_op expr | bool_expr

cond_expr

Compare Operation Types

'==' | '!=' | '<' | '>' | '<=' | '>='

compare_op :

Actions

: action | actions ',' action

actions

Single Action

: empty | pinname ':=' dig_seq

action

Expression

arith_expr | bool_expr | shift_expr

expr

Arithmetic Expression

'(' arith_expr ')'

arith_expr

arith_expr '+' arith_expr | arith_expr '-' arith_expr | arith_expr '*' arith_expr | arith_expr '/' arith_expr |

pinname | dig_seq

Boolean\ Expression

bool_expr

lgbl_expr | btbl_expr

```

```

lgbl_expr : '(' lgbl_expr ')' |

lgbl_expr LAND

```

lgbl\_expr LAND gbl\_expr | lgbl\_expr LOR gbl\_expr | lgbl\_expr LNOT gbl\_expr | lgbl\_expr LNAND gbl\_expr | lgbl\_expr LXNOR gbl\_expr | lgbl\_expr LXNOR gbl\_expr |

pinname | dig\_seq

;

Bitwise Logical Boolean Expression

btbl\_expr

'(' btbl\_expr ')' |

btbl\_expr '&' btbl\_expr | btbl\_expr '|' btbl\_expr |

btbl\_expr '^' btbl\_expr | btbl\_expr '~' btbl\_expr |

btbl\_expr '~&' btbl\_expr | btbl\_expr '~' btbl\_expr |

btbl\_expr '^~' btbl\_expr |

pinname | dig\_seq

Shift Expression

shift\_expr

'(' shift\_expr ')'

shift\_expr SHL shift\_expr | shift\_expr SHR shift\_expr |

shift\_expr ROTL shift\_expr | shift\_expr ROTL shift\_expr |

pinname | dig\_seq

Pin Name

pinname

comp\_name '.' value\_ident

$Port\ or\ Variable\ Identifier$

value\_ident

identifier | identifier '[' dig\_seq ']' |

identifier '{' dig\_seq '..' dig\_seq '}'

Identifier

$Lex\ Format: [a\hbox{-} zA\hbox{-} Z][a\hbox{-} zA\hbox{-} Z0\hbox{-} 9\_]*$

identifier

;

**IDENTIFIER**

Digit Sequence

Lex Format: [0-9xX]+

dig\_seq

DIGSEQ