### University of California Santa Barbara

## Energy-Efficient Architecture and Dataflow Optimization for Spiking Neural Network Accelerators

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

Jeong-Jun Lee

### Committee in charge:

Professor Peng Li, Chair Professor Spencer L. Smith Professor Bongjin Kim Professor Michael Beyeler

| The Dissertation of Jeong-Jun Lee is approved. |  |

|------------------------------------------------|--|

|                                                |  |

|                                                |  |

|                                                |  |

| Professor Spencer L. Smith                     |  |

|                                                |  |

|                                                |  |

| Professor Bongjin Kim                          |  |

|                                                |  |

|                                                |  |

| Professor Michael Beyeler                      |  |

|                                                |  |

|                                                |  |

| Professor Peng Li, Committee Chair             |  |

August 2022

# Energy-Efficient Architecture and Dataflow Optimization for Spiking Neural Network ${\bf Accelerators}$

Copyright © 2022

by

Jeong-Jun Lee

### Acknowledgements

First and foremost, I would like to express my sincere gratitude to Prof. Peng Li, for his great support and invaluable guidance during the past years. His expertise, vision and insights in the research fields deeply inspired me, which not only motivated me to have broader perspectives and to pursue higher goals, but also taught me some valuable life lessons. It was a great pleasure working with Prof. Li and I could not have imagined having a better advisor for my Ph.D. study.

I would also like to thank my committee members, Prof. Spencer Smith, Prof. Michael Beyeler, and Prof Bongjin Kim for their constructive and insightful feedback on my research. I truly appreciate your valuable suggestions and they are extremely helpful for this dissertation.

Being in our group with great colleagues was more than a great experience. I would like to appreciate Dr. Yu Liu, Dr. Wenrui Zhang, Dr. Changqing Xu, Yu Wang, Renqian Zhang, Umang Garg and Jianhao Chen, who worked with me on some research topics. I would also like to thank Dr. Hanbin Hu, Dr. Myung Seok Shim, Richard Boone, Zheng Ke, Karthik Somayaji, Zihu Wang, and Yuxuan Yin for their support.

Finally, I would like to thank my family for their love and support. My family is the most priceless gift and more than everything to me. Without your dedicated support, this journey would have been much harder.

### Funding Sources and Disclaimer

This material is based upon work supported by the U.S. Department of Energy, Office of Science, Office of Advanced Scientific Computing Research under Award Number DE-SC0021319, and the National Science Foundation under Award Numbers 1948201 and 2000851.

This dissertation was prepared as an account of work sponsored by agencies of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

This dissertation is also supported by the UCSB ECE Dissertation Fellowship for Summer 2022.

## Curriculum Vitæ Jeong-Jun Lee

### Education

| Aug 2022 | Ph.D. in Electrical and Computer Engineering (Expected), University of California, Santa Barbara. |

|----------|---------------------------------------------------------------------------------------------------|

| Feb 2018 | M.S in Electrical and Computer Engineering, Seoul National University.                            |

| Feb 2016 | B.S in Electrical and Computer Engineering, Seoul National University.                            |

#### **Publications**

Lee, Jeong-Jun, and Peng Li. "Systolic Array Acceleration of Spiking Neural Networks with Application-Independent Split-Time Temporal Coding." 55th IEEE/ACM International Symposium on Microarchitecture (MICRO), 2022. \*submitted

Lee, Jeong-Jun, Wenrui Zhang, and Peng Li. "Parallel Time Batching: Systolic-Array Acceleration of Sparse Spiking Neural Computation." In 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA), pp. 317-330. IEEE, 2022.

Lee, Jeong-Jun, Wenrui Zhang, Yuan Xie, and Peng Li. "SaARSP: An Architecture for Systolic-Array Acceleration of Recurrent Spiking Neural Networks." ACM Journal on Emerging Technologies in Computing Systems (JETC) 2022.

Lee, Jeong-Jun, Jianhao Chen, Wenrui Zhang, and Peng Li. "Systolic-Array Spiking Neural Accelerators with Dynamic Heterogeneous Voltage Regulation." In 2021 International Joint Conference on Neural Networks (IJCNN), pp. 1-7. IEEE, 2021.

Lee, Jeong-Jun, and Peng Li. "Reconfigurable dataflow optimization for spatiotemporal spiking neural computation on systolic array accelerators." In 2020 IEEE 38th International Conference on Computer Design (ICCD), pp. 57-64. IEEE, 2020.

Lee, Jeongjun, Renqian Zhang, Wenrui Zhang, Yu Liu, and Peng Li. "Spike-train level direct feedback alignment: sidestepping backpropagation for on-chip training of spiking neural nets." Frontiers in Neuroscience 14 2020: 143.

Hwang, Sungmin\*, Jeong-Jun Lee\*, Min-Woo Kwon, Myung-Hyun Baek, Taejin Jang, Jeesoo Chang, Jong-Ho Lee, and Byung-Gook Park. "Analog Complementary Metal-Oxide-Semiconductor Integrate-and-Fire Neuron Circuit for Overflow Retaining in Hardware Spiking Neural Networks." Journal of nanoscience and nanotechnology 20, no. 5 (2020): 3117-3122. doi: 10.1166/jnn.2020.17390 \*equally contributed

Lee, Jeong-Jun, Jungjin Park, Min-Woo Kwon, Sungmin Hwang, Hyungjin Kim, and Byung-Gook Park. "Integrated neuron circuit for implementing neuromorphic system with synaptic device." Solid-State Electronics 140 (2018): 34-40.

Lee, Jeong-Jun, Min-Woo Kwon, Hyungjin Kim, Sungmin Hwang, and Byung-Gook Park. "Implementation of inhibitory operation in neuromorphic system." In 2017 Silicon Nanoelectronics Workshop (SNW), pp. 113-114. IEEE, 2017.

Wang, Yu, Jeong-Jun Lee, Yu Ding, and Peng Li. "A scalable FPGA engine for parallel acceleration of singular value decomposition." In 2020 21st International Symposium on Quality Electronic Design (ISQED), pp. 370-376. IEEE, 2020.

Baek, Myung-Hyun, Taejin Jang, Hyungjin Kim, Jungjin Park, Min-Woo Kwon, Sungmin Hwang, Suhyeon Kim, Jeong-Jun Lee, and Byung-Gook Park. "Grain boundary induced short-term memory effect in fully depleted thin-polysilicon devices." Japanese Journal of Applied Physics 58, no. 10 (2019): 101004.

Hwang, Sungmin, Hyungjin Kim, Jungjin Park, Min-Woo Kwon, Myung-Hyun Baek, Jeong-Jun Lee, and Byung-Gook Park. "System-level simulation of hardware spiking neural network based on synaptic transistors and I&F neuron circuits." IEEE Electron Device Letters 39, no. 9 (2018): 1441-1444.

Park, Jungjin, Min-Woo Kwon, Hyungjin Kim, Sungmin Hwang, Jeong-Jun Lee, and Byung-Gook Park. "Compact neuromorphic system with four-terminal Si-based synaptic devices for spiking neural networks." IEEE Transactions on Electron Devices 64, no. 5 (2017): 2438-2444.

#### Abstract

Energy-Efficient Architecture and Dataflow Optimization for Spiking Neural Network

Accelerators

by

#### Jeong-Jun Lee

Spiking neural networks (SNNs) offer a promising biologically-plausible computing model and lend themselves to ultra-low-power event-driven processing on neuromorphic processors. Compared with the conventional artificial neural networks, SNNs are well-suited for processing complex spatiotemporal data. In this dissertation, we aim to address key difficulties in accelerating SNNs: developing bio-plausible and hardware friendly algorithm, efficient processing of the added temporal dimension, and handling unstructured sparsity emergent in both space and time.

First, training SNNs to reach the same performances of conventional deep artificial neural networks (ANNs), particularly with error backpropagation (BP) algorithms, poses a significant challenge due to inherent complex dynamics and non-differentiable spike activities of spiking neurons. In this dissertation, we present the first study on realizing competitive spike-train level backpropagation (BP) like algorithms to enable on-chip training of SNNs. We propose a novel spike-train level direct feedback alignment (ST-DFA) algorithm, which is much more bio-plausible and hardware friendly than BP. Algorithm and hardware co-optimization and efficient online neural signal computation are explored for on-chip implementation of ST-DFA. On the Xilinx ZC706 FPGA board, the proposed hardware-efficient ST-DFA shows excellent performance vs. overhead tradeoffs for real-world speech and image classification applications.

Despite its significance, dataflow optimization of spiking neural accelerator architec-

tures has not been extensively studied. Recognizing the need for efficient processing of complex spatiotemporal data while considering the all-or-none nature of spiking activities, we propose holistic reconfigurable dataflow optimization for systolic array acceleration of spiking convolutional networks (S-CNNs). A novel scheme is introduced for parallel acceleration of computation across multiple time points, which further allows for systemic optimization of variable tiling for a large performance and efficiency gains. Also, we pack multiple time points into a single time window (TW) and process the computations induced by active synaptic inputs falling under several TWs in parallel, leading to the proposed parallel time batching. It allows weight reuse across multiple time points and enhances the utilization of the systolic array with reduced idling of processing elements, overcoming the irregularity of sparse firing activities. We optimize the granularity of time-domain processing, i.e., the TW size, which significantly impacts the data reuse and utilization.

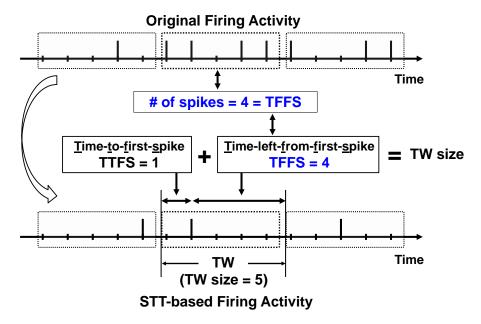

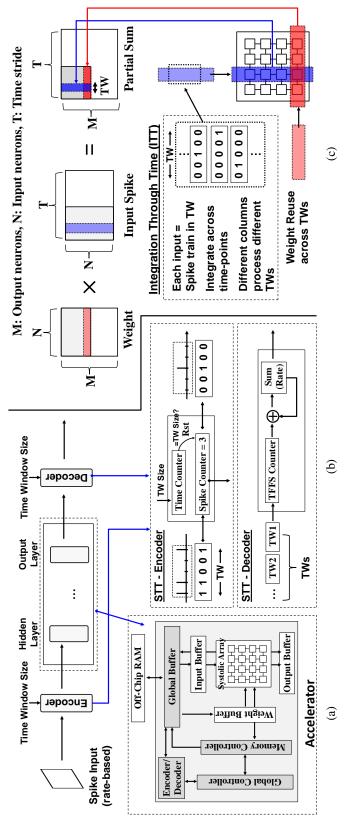

Lastly, we propose a novel technique and architecture that allow the exploitation of temporal information compression with structured sparsity and parallelism across time, and significantly improves data movement on a systolic array. We split a full range of temporal domain into several time windows (TWs) where a TW packs multiple time points, and encode the temporal information in each TW with Split-Time Temporal coding (STT) by limiting the number of spikes within a TW up to one. STT enables sparsification and structurization of irregular firing activities and dramatically reduces computational overhead while delivering competitive classification accuracy without a huge drop. To further improve the data reuse, we propose an Integration Through Time (ITT) technique that processes integration steps across different TWs in parallel with a systolic array.

In this dissertation, we provide unique and powerful solutions for the efficient acceleration of the spiking models with various datasets.

## Contents

| A  | cknowle                 | edgements                                                                                                                                          | v                                |

|----|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Di | sclaime                 | er                                                                                                                                                 | vi                               |

| Cı | ırriculu                | ım Vitae                                                                                                                                           | vii                              |

| Al | ostract                 |                                                                                                                                                    | ix                               |

| Li | st of Fi                | gures                                                                                                                                              | xiv                              |

| Li | st of Ta                | ables                                                                                                                                              | xviii                            |

| 1  | 1.2 Sp<br>1.3 Sp        | uction         euromorphic Computing Systems          biking Neural Network Algorithms          biking Neural Network Accelerators          utline |                                  |

| 2  | 2.2 Sp<br>2.3<br>2.3 Ds | round nique Characteristics of SNNs                                                                                                                | 7<br>7<br>8<br>8<br>8<br>9<br>13 |

| 3  | 3.1 Di<br>3.2 Sp        | g Neural Processor with Direct Feedback Alignment irect Feedback Alignment (DFA)                                                                   | 19                               |

|   |     | 3.2.2   | Derivation of ST-DFA                                              | 23 |

|---|-----|---------|-------------------------------------------------------------------|----|

|   |     | 3.2.3   | Simplification for Hardware Friendliness                          | 25 |

|   | 3.3 | SNN A   | Accelerators with ST-DFA On-chip Training                         | 26 |

|   |     | 3.3.1   | Architecture                                                      | 26 |

|   |     | 3.3.2   | On-chip Training                                                  | 28 |

|   |     | 3.3.3   | Neuron Unit Design                                                | 29 |

|   |     | 3.3.4   | Efficient On-chip S-PSP Calculation                               | 30 |

|   |     | 3.3.5   | Efficient On-chip ST-DFA Implementation                           | 32 |

|   | 3.4 | Experi  | ments and Results                                                 | 34 |

|   |     | 3.4.1   | Experimental Settings and Benchmarks                              | 34 |

|   |     | 3.4.2   | Classification Accuracies                                         | 35 |

|   |     | 3.4.3   | FPGA Hardware Evaluations                                         | 37 |

|   | 3.5 | Summ    | ary and Discussions                                               | 40 |

| 4 | Dat | aflow ( | Optimization for Spiking Neural Networks                          | 42 |

|   | 4.1 | Datafle | ow Optimization for Spiking CNNs                                  | 43 |

|   |     | 4.1.1   | Proposed parallel processing in temporal dimension                | 43 |

|   |     | 4.1.2   | Dataflow in Spiking CNNs                                          | 45 |

|   |     | 4.1.3   | Stationary schemes for S-CNNs                                     | 47 |

|   |     | 4.1.4   | Variable Tiling                                                   | 47 |

|   |     | 4.1.5   | Layer-dependent dataflow reconfiguration                          | 50 |

|   | 4.2 | SNN I   | Oataflow Simulator                                                | 51 |

|   |     | 4.2.1   | Modeling of systolic array and memory                             | 51 |

|   |     | 4.2.2   | Performance modeling                                              | 53 |

|   | 4.3 | _       | ments and Results                                                 | 54 |

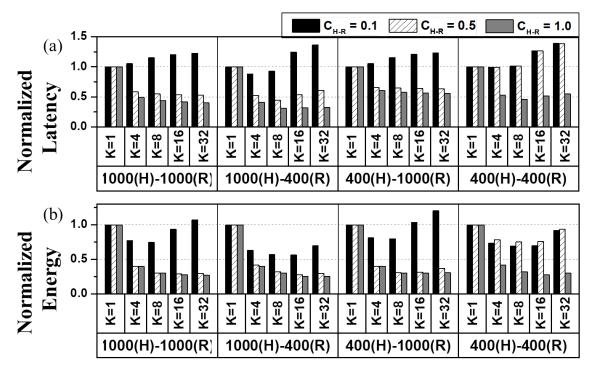

|   |     | 4.3.1   | Layer-specific dataflow optimization                              | 55 |

|   |     | 4.3.2   | Joint optimization of tiling and stationary flows                 | 57 |

|   |     | 4.3.3   | Joint layer-dependent reconfigurable dataflow and                 |    |

|   |     |         | hardware optimization                                             | 58 |

|   | 4.4 | Summ    | ary and Discussions                                               | 59 |

| 5 | Par |         | ime-Computation for Spiking Neural Computation                    | 62 |

|   | 5.1 | Challe  | nges of SNN Accelerators                                          | 63 |

|   |     | 5.1.1   | Spatial and Temporal Sparsity in SNNs                             | 63 |

|   |     | 5.1.2   | Existing SNN Accelerators                                         | 65 |

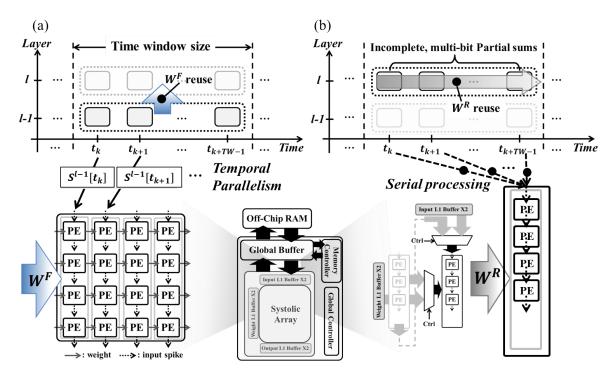

|   | 5.2 | -       | sed Architecture                                                  | 66 |

|   |     | 5.2.1   | Overview of the Proposed Architecture                             | 66 |

|   |     | 5.2.2   | Time Batch (TB) and TB-tag                                        | 68 |

|   |     | 5.2.3   | Parallel Time Batching (PTB)                                      | 71 |

|   |     | 5.2.4   | Spatiotemporally-non-overlapping Spiking Activity Packing (StSAP) | 73 |

|   | 5.3 | -       | ments and Results                                                 | 75 |

|   |     | 5 2 1   | Architecture Specifications and Ronchmarks                        | 75 |

|   |     | 5.3.2    | Optimization of Array Dimension                                    | 76  |

|---|-----|----------|--------------------------------------------------------------------|-----|

|   |     | 5.3.3    | Comprehensive Evaluation                                           | 79  |

|   | 5.4 | Summ     | ary and Discussions                                                | 83  |

| 6 | Rec |          | Spiking Neural Network Acceleration                                | 87  |

|   | 6.1 | Recur    | rent Spiking Neural Network Accelerators                           | 87  |

|   |     | 6.1.1    | Recurrent Spiking Neural Network                                   | 87  |

|   |     | 6.1.2    | R-SNN accelerators                                                 | 88  |

|   | 6.2 |          | SP: Proposed Architecture                                          | 91  |

|   |     | 6.2.1    | Decoupled feedforward/recurrent synaptic integration               | 91  |

|   |     | 6.2.2    | Proposed SaARSP architecture                                       | 93  |

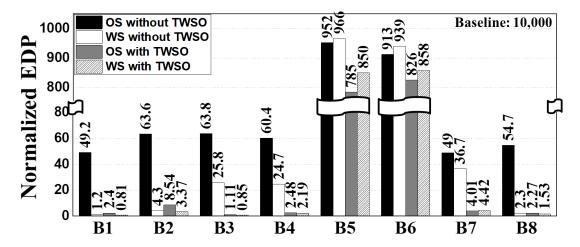

|   |     | 6.2.3    | Time-window size optimization (TWSO)                               | 96  |

|   | 6.3 | _        | iments and Results                                                 | 98  |

|   |     | 6.3.1    | Configurations and Setups                                          | 98  |

|   |     | 6.3.2    | Spiking neural network benchmarks                                  | 101 |

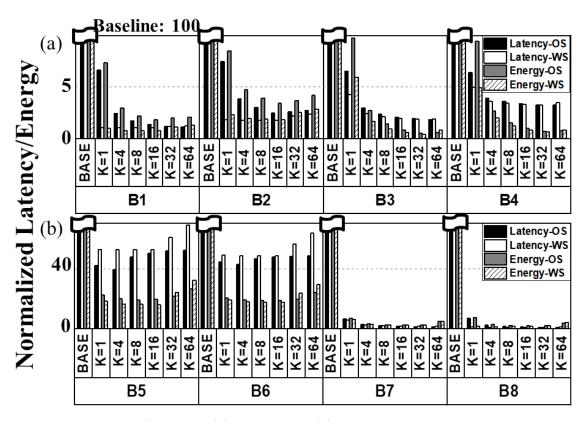

|   |     | 6.3.3    | Acceleration of feedforward layers with output stationary dataflow | 104 |

|   |     | 6.3.4    | Acceleration of recurrent layers with output stationary dataflow . | 105 |

|   |     | 6.3.5    | Comprehensive evaluation and optimization of recurrent layer ac-   |     |

|   |     |          | celeration                                                         | 107 |

|   | 6.4 | Summ     | ary and Discussions                                                | 111 |

| 7 | App | olicatio | on-Independent Split-Time-Temporal Coding                          | 113 |

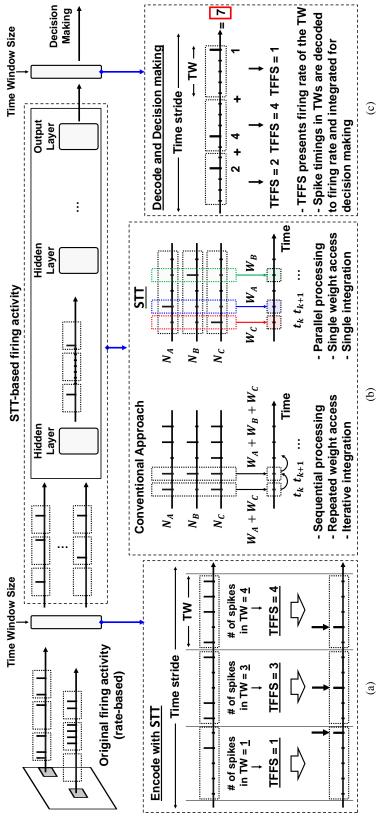

|   | 7.1 | Split-7  | Γime Temporal coding (STT)                                         | 114 |

|   |     | 7.1.1    | Proposed STT                                                       | 116 |

|   |     | 7.1.2    | STT-based Acceleration                                             | 117 |

|   |     | 7.1.3    | Machine Learning Performance with STT                              | 118 |

|   | 7.2 | _        | sed Architecture                                                   | 119 |

|   |     | 7.2.1    | Overview of the Proposed Architecture                              | 119 |

|   |     | 7.2.2    | Integration Through-Time (ITT)                                     | 121 |

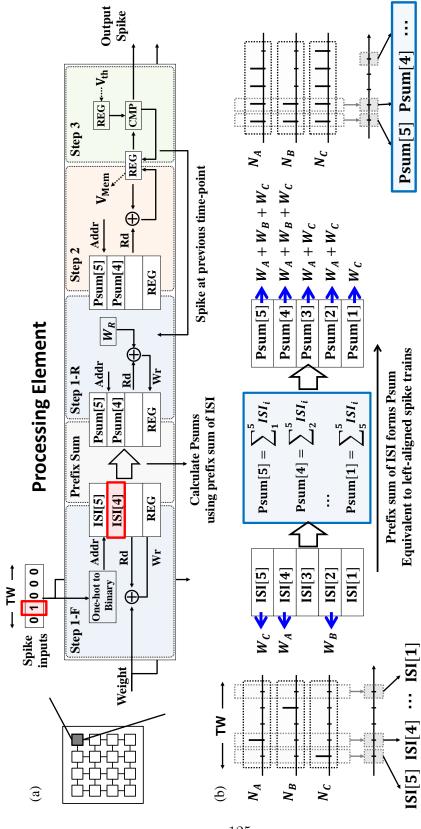

|   |     | 7.2.3    | Mapping to Systolic Array                                          | 122 |

|   |     | 7.2.4    | STT-based Layer Acceleration                                       | 124 |

|   | 7.3 |          | iments and Results                                                 | 127 |

|   |     | 7.3.1    | Configurations and Setups                                          | 128 |

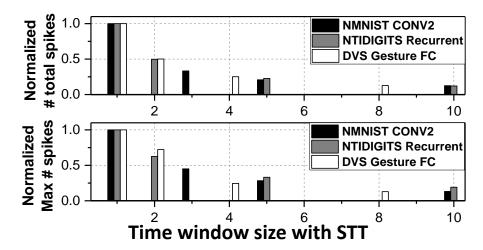

|   |     | 7.3.2    | STT: Temporal Information Compression                              | 128 |

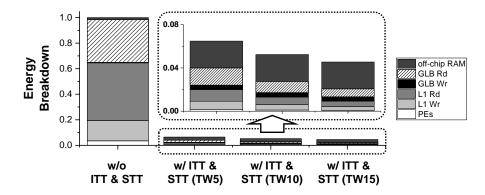

|   |     | 7.3.3    | ITT: Data Reuse                                                    | 130 |

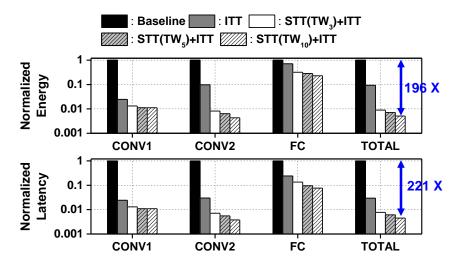

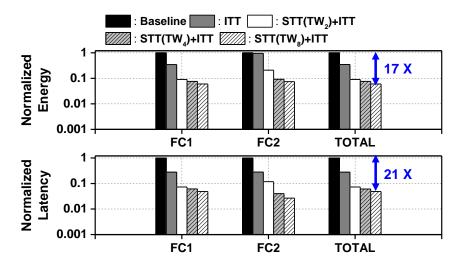

|   |     | 7.3.4    | Comprehensive Evaluations                                          | 131 |

|   | 7.4 | Summ     | ary and Discussions                                                | 136 |

| 8 | Con | clusio   | n                                                                  | 138 |

|   | 8.1 | Canal    |                                                                    | 138 |

|   | 0.1 | Concu    | asion                                                              | 190 |

## List of Figures

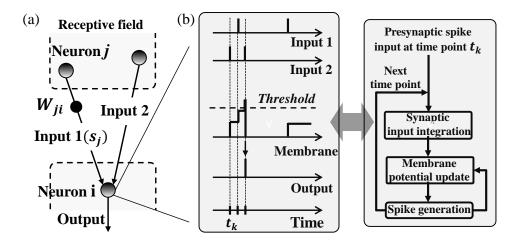

| 2.1        | (a): Layer operation in SNNs. (b): Main steps of spatiotemporal operation in a spiking neuron                                                                                                                                                                                          | 8    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

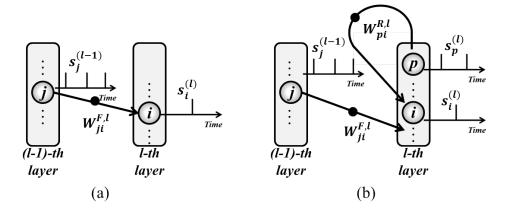

| 2.2        | (a): Schematic for feedforward layer operation in SNN. (b): Schematic for recurrent layer operation in R-SNN                                                                                                                                                                           | 9    |

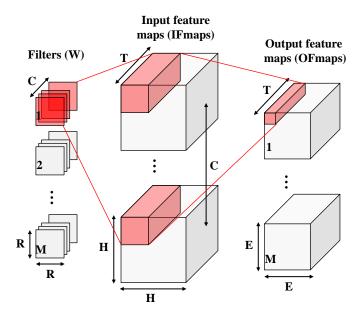

| 2.3        | Computation of convolution layer in S-CNNs                                                                                                                                                                                                                                             | 12   |

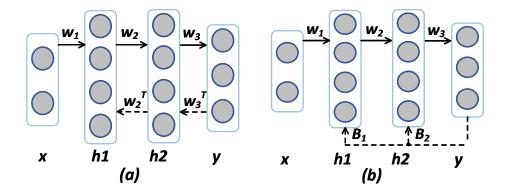

| 3.1        | (a) Backpropagation (BP) vs. (b) direct feedback alignment (DFA). Solid arrows indicate feedforward paths and dashed arrows indicate feedback paths. The feedback matrices $\boldsymbol{B}_1$ and $\boldsymbol{B}_2$ need not be symmetric to $\boldsymbol{W}_2$ or $\boldsymbol{W}_3$ | 19   |

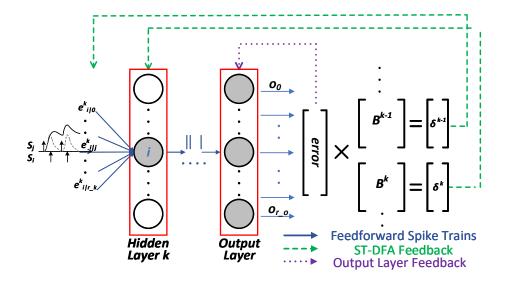

| 3.2        | The proposed spike-train level DFA (ST-DFA)                                                                                                                                                                                                                                            | 23   |

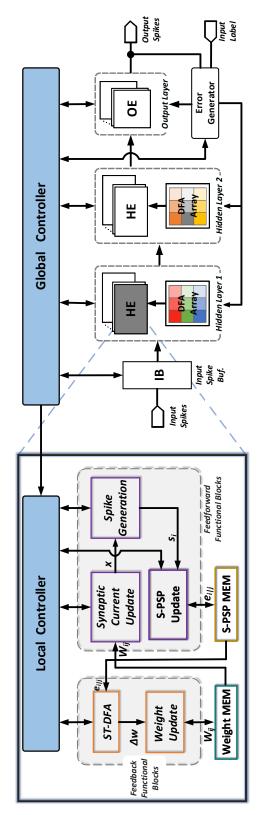

| 3.3        | Proposed architecture of multi-layer SNNs with onchip ST-DFA training. HE represents a digital hidden neuron element; and OE represents a digital output neuron element.                                                                                                               | 27   |

| 3.4        | On-line S-PSP calculation onchip                                                                                                                                                                                                                                                       | 32   |

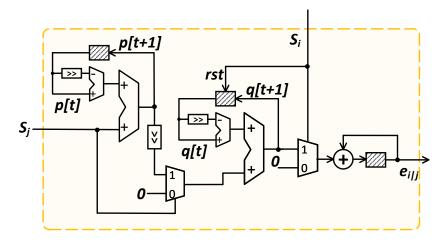

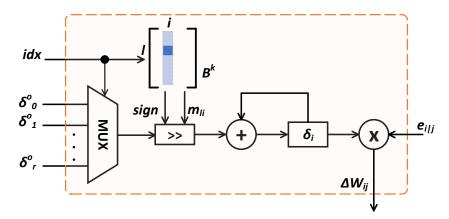

| 3.5        | On-chip ST-DFA weight update computation                                                                                                                                                                                                                                               | 33   |

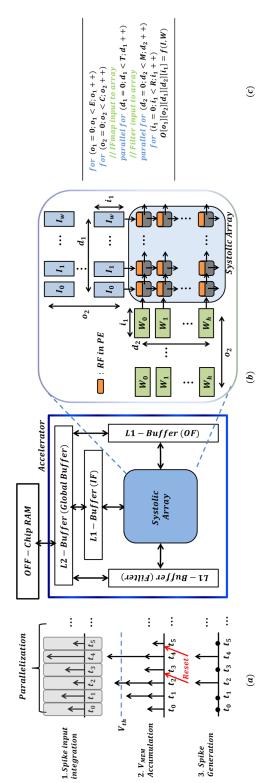

| 4.1        | Overview of the proposed work: (a) parallelization in temporal dimension, (b) systolic accelerator design, and (c) generalized loop representation of the mapped tiling strategy                                                                                                       | 44   |

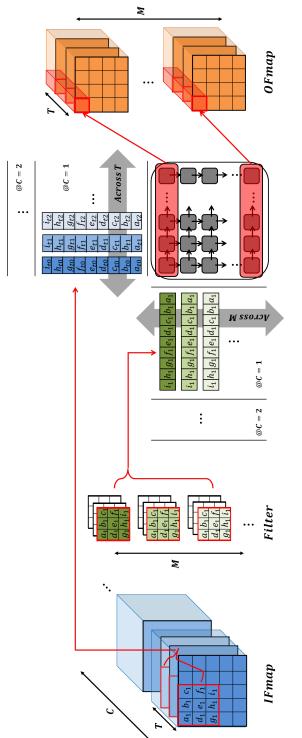

| 4.2        | Mapping of a <i>Psum-friendly</i> output-stationary dataflow onto a systolic array accelerator                                                                                                                                                                                         | 46   |

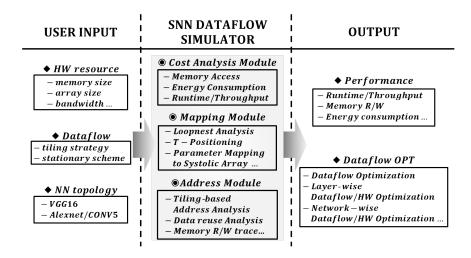

| 4.3        | An overview of SNN dataflow simulator framework                                                                                                                                                                                                                                        | 51   |

| 4.4        | (a) The throughput of three dataflows for VGG-16 CONV1 and CONV11 with OS and WS. (b) Energy dissipation of various dataflows for VGG-16 CONV11 and CONV11. AC refers to accumulation expertion                                                                                        | E 77 |

|            | CONV1 and CONV11. AC refers to accumulation operation                                                                                                                                                                                                                                  | 57   |

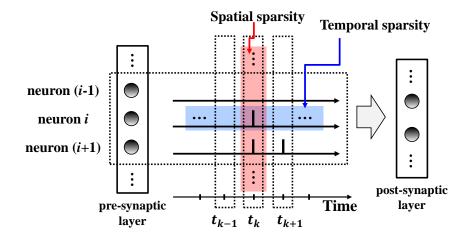

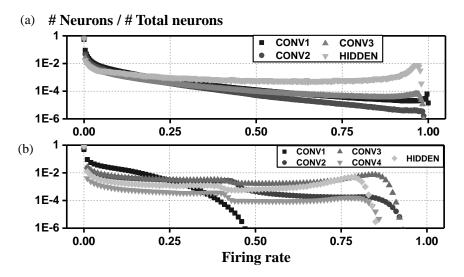

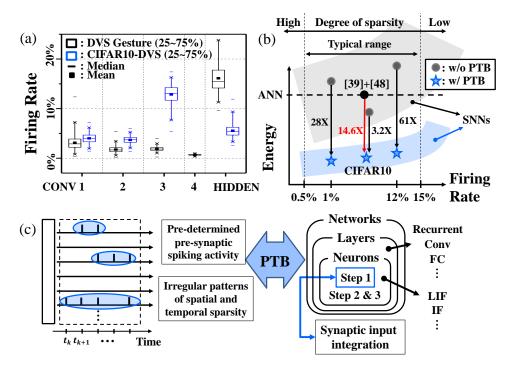

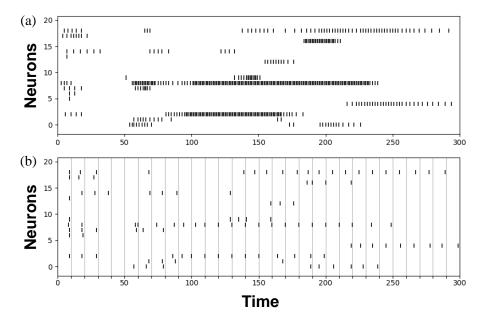

| 5.1<br>5.2 | Spatial and temporal sparsity emergent in SNNs                                                                                                                                                                                                                                         | 63   |

|            | and (b): CIFAR10-DVS                                                                                                                                                                                                                                                                   | 64   |

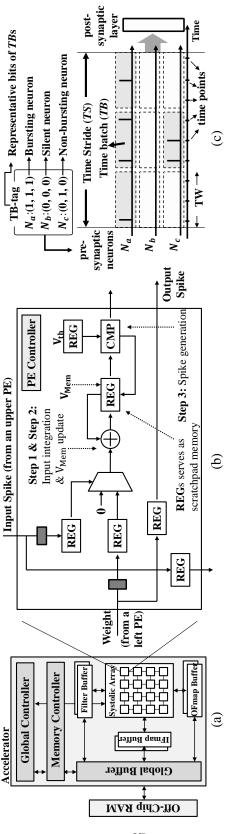

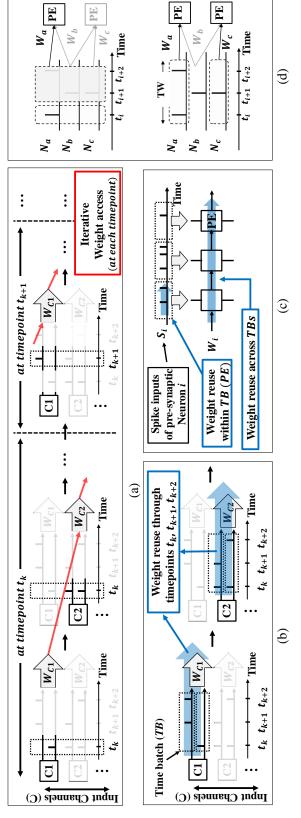

| 5.3  | (a): Overall architecture. (b): Simplified schematic representation of the processing element (PE) in systolic array. (c): Schematic representation                                                                                                                                                                                                                                 |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | of time point, time batch (TB), TB-tag and time stride (TS)                                                                                                                                                                                                                                                                                                                         | 67  |

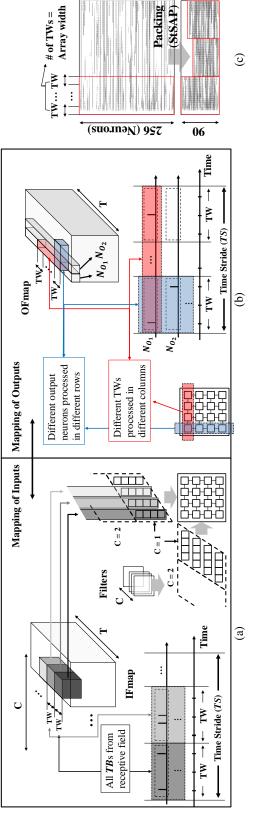

| 5.4  | Mapping of the (a): inputs and (b): outputs into the systolic array. (c): Example of enhanced spike input density in DVS-Gesture dataset with                                                                                                                                                                                                                                       |     |

|      | temporally-non-overlapping spikingactivity packing (StSAP)                                                                                                                                                                                                                                                                                                                          | 69  |

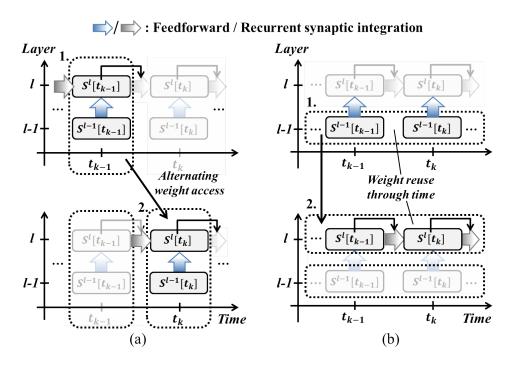

| 5.5  | Simplified schematic representations of (a): Conventional approach which lacks parallel processing in time domain (executions are performed in time-serial manner). It requires alternating weight access. (b): Proposed approach using parallel time batching (PTB). (c): Weight reuse within, and across TBs. (d): Hiding the absence of spike with TB (grouped spiking activity) | 70  |

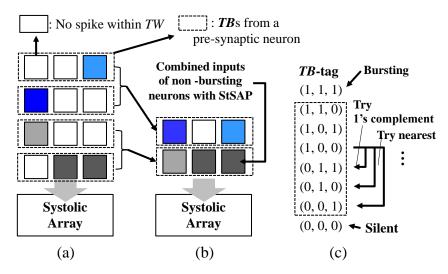

| 5.6  | Schematic representation of StSAP. Mapping of the spike inputs from non-bursting neurons (a): without StSAP, (b): with StSAP. (c): Greedy policy                                                                                                                                                                                                                                    |     |

|      | applied to find nearest 1's complement based on TB-tag                                                                                                                                                                                                                                                                                                                              | 74  |

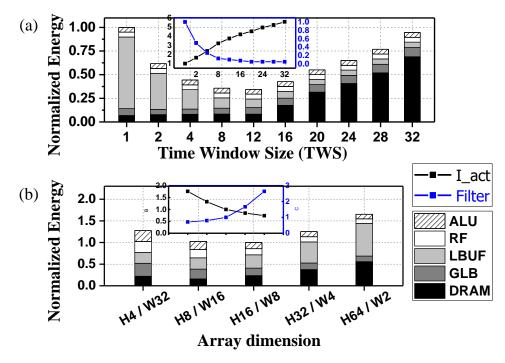

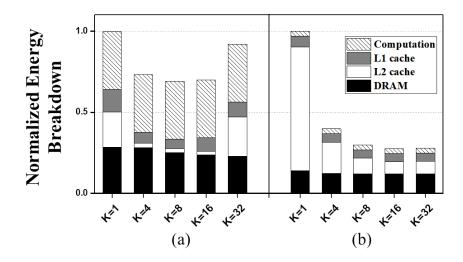

| 5.7  | Energy dissipation breakdown of CONV2 in DVS-Gesture with different (a): TW size. (b): array size (TW=8)                                                                                                                                                                                                                                                                            | 77  |

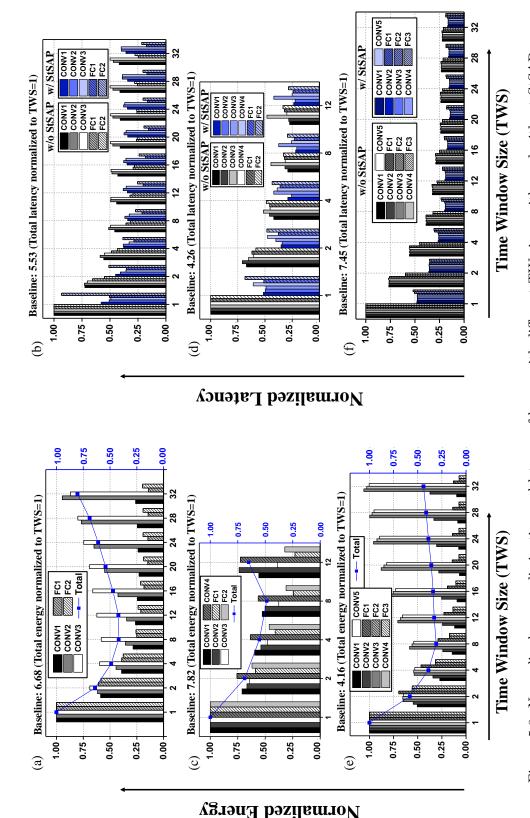

| 5.8  | Normalized energy dissipation and latency of layers with different TW                                                                                                                                                                                                                                                                                                               |     |

|      | sizes, with- and without StSAP, in each dataset. (a),(b): DVS-Gesture,                                                                                                                                                                                                                                                                                                              |     |

|      | (c),(d): CIFAR10-DVS, and (e),(f): Alexnet. PTB with non-                                                                                                                                                                                                                                                                                                                           |     |

|      | optimized TW size (TWS=1) improves the total energy dissipation and                                                                                                                                                                                                                                                                                                                 |     |

|      | latency by DVS-Gesture: 6.68X and 5.53X, CIFAR10-DVS: 7.82X and                                                                                                                                                                                                                                                                                                                     |     |

| - 0  | 4.26X, and Alexnet: 4.16X and 7.45X, over the baseline.                                                                                                                                                                                                                                                                                                                             | 78  |

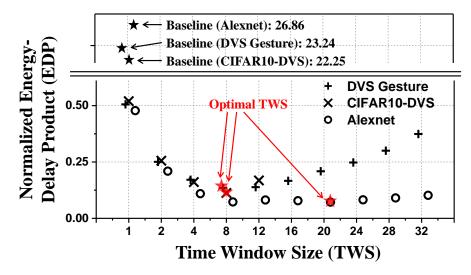

| 5.9  | Total energy-delay product (EDP) of three different benchmarks. EDP                                                                                                                                                                                                                                                                                                                 |     |

|      | values are normalized to the baseline result, which exclude merging and                                                                                                                                                                                                                                                                                                             | 01  |

| 5.10 | TW size optimization                                                                                                                                                                                                                                                                                                                                                                | 81  |

| 5.10 | energy efficiency across wide range of sparsity-levels. With PTB, SNN                                                                                                                                                                                                                                                                                                               |     |

|      | showed better result than ANN. (c) PTB supports diverse family of spiking                                                                                                                                                                                                                                                                                                           |     |

|      | models.                                                                                                                                                                                                                                                                                                                                                                             | 85  |

|      |                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 6.1  | Schematic representation of (a): Time-serial processing in conventional                                                                                                                                                                                                                                                                                                             |     |

|      | SNNs, (b): Decoupling scheme to separate feedforward and recurrent                                                                                                                                                                                                                                                                                                                  | 0.0 |

| c o  | steps. Layer l: Recurrent layer                                                                                                                                                                                                                                                                                                                                                     | 90  |

| 6.2  | Overview of the proposed SaARSP architecture. (a): Array computation for feedforward integration ( <b>Step A</b> , OS dataflow) (b): Array computation                                                                                                                                                                                                                              |     |

|      | for recurrent integration (Step B, OS dataflow)                                                                                                                                                                                                                                                                                                                                     | 93  |

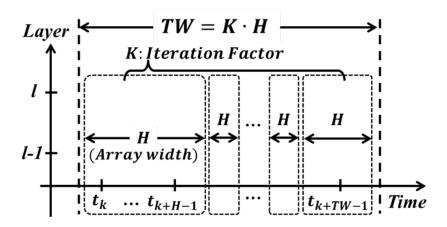

| 6.3  | Operate the array accelerator with a chosen time window size $TW$ for $K$                                                                                                                                                                                                                                                                                                           | 0.0 |

| C 4  | array processing iterations                                                                                                                                                                                                                                                                                                                                                         | 96  |

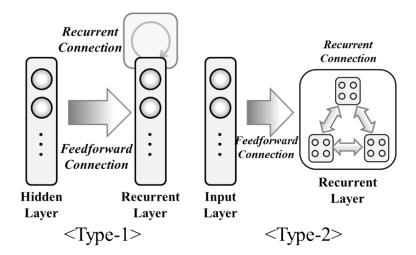

| 6.4  | Two spiking recurrent layer topologies: (a) Type 1 - uniform, and (b) Type 2 - population based                                                                                                                                                                                                                                                                                     | 100 |

|      | Δ - population based                                                                                                                                                                                                                                                                                                                                                                | 100 |

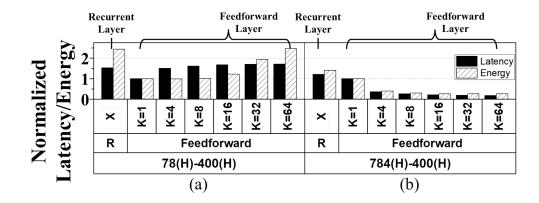

| 6.5  | Normalized latency/energy of two feedforward layers in comparison with recurrent layers, with $C_{H-R}$ =1.0 and $C_{R-R}$ =0.3. The values are normalized latency for the first comparison with                     | 104                               |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 6.6  | ized to those of the feedforward layer with time-iteration factor $K=1$ Normalized energy dissipation of recurrent layer acceleration under output                                                                   | 104                               |

| 6.7  | stationary dataflow                                                                                                                                                                                                  | 105<br>107                        |

| 6.8  | Latency/energy of (a) Type-1, and (b) Type-2 recurrent networks with OS and WS dataflows normalized to that of the baseline design, which follows conventional approaches                                            | 108                               |

| 6.9  | Normalized EDP in recurrent layer of eight benchmarks with OS and WS. EDP values are normalized to the baseline result using 1-D array. The EDP of OS and WS with and without the time window optimization is shown. | 111                               |

| 7.1  | Local structurization and sparsification with the proposed STT. Time-left-from-first-spike (TFFS) presents the firing rate of the corresponding TW                                                                   | 114                               |

| 7.2  | Schematic representations of STT-based network operations. (a): STT-encoder at the input layer (b): Comparison between the operations in conventional approaches and the proposed STT-based approach (c): STT-       |                                   |

| 7.3  | decoder at the output layer                                                                                                                                                                                          | <ul><li>115</li><li>117</li></ul> |

| 7.4  | (a): Overall architecture of the proposed accelerator (b): STT-encoder and decoder at the input and output layer, respectively (c): Mapping of the inputs and outputs into the systolic array with the proposed ITT  | 120                               |

| 7.5  | Schematic representations of (a): Operations in a PE for accelerating feed-<br>forward and recurrent layer (b): Calculating partial sums (Psums) using<br>a prefix sum of the integrated synaptic inputs (ISI)       | 125                               |

| 7.6  | Normalized number of total spikes and maximum number of spikes in a neuron with different time window sizes                                                                                                          | 127                               |

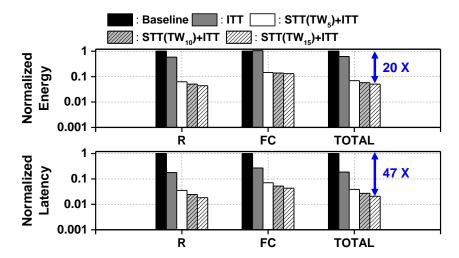

| 7.7  | Normalized energy dissipation and energy breakdown with and without the proposed techniques                                                                                                                          | 129                               |

| 7.8  | Normalized energy dissipation and latency of layers with different TW sizes for NMNIST                                                                                                                               | 130                               |

| 7.9  | Normalized energy dissipation and latency of layers with different TW sizes for DVS-Gesture                                                                                                                          | 131                               |

| 7.10 | Normalized energy dissipation and latency of layers with different TW sizes for NTIDIGITS.                                                                                                                           | 132                               |

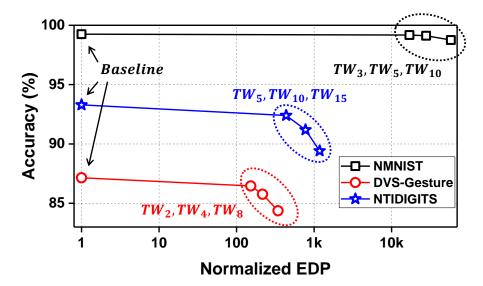

| 7.11 Machine learning performance (inference) - Accelerator performance (nor- |     |

|-------------------------------------------------------------------------------|-----|

| malized EDP) tradeoffs on various datasets                                    | 136 |

## List of Tables

| 2.1               | Shape parameters of a CONV layer in S-CNNs                                                                                                                                                                                                             | 12       |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1               | Inference accuracy comparison of HM2BP, ST-DFA and ST-DFA-2. All SNNs are fully connected networks with a single hidden layer of 800 neurons. MNIST: 28x28 input resolution; N-MNIST: 2,312 input spike trains; 16-speaker TI46: 78 input spike trains | 36       |

| 3.2               | Overheads and inference performances of the fully-connected SNNs with on-chip ST-DFA-2                                                                                                                                                                 | 39       |

| 3.3               | Overheads of an FPGA SNN with on-chip HM2-BP vs. ST-DFA-2 (Network size:196-100-100-10)                                                                                                                                                                | 39       |

| 4.1               | Layer-specific comparison of tiling strategies in output stationary (OS) dataflows for the VGG-16 net                                                                                                                                                  | 54       |

| 4.2               | Joint layer-dependent dataflow and accelerator optimization under different optimization-targets for VGG-16                                                                                                                                            | 56       |

| 4.3               | Joint layer-dependent dataflow and accelerator optimization under different optimization-targets for Alexnet.                                                                                                                                          | 56       |

| 4.4               | Normalized runtime, energy dissipation, and EDP under different optimization targets and hardware area constraints for VGG-16 and Alexnet. The SNN dataflow from [30] is denoted by ref*                                                               | 60       |

| 5.1               | Summary of key features in existing and our SNN accelerators                                                                                                                                                                                           | 65       |

| 5.2               | A high-level overview of the input parameters                                                                                                                                                                                                          | 76       |

| 5.3               | Architecture specifications                                                                                                                                                                                                                            | 76       |

| 5.4               | Performance comparison of ANNs and SNNs                                                                                                                                                                                                                | 83       |

| 6.1<br>6.2<br>6.3 | A high-level overview of the user-specified inputs to the simulator Architecture specifications                                                                                                                                                        | 99<br>99 |

| 6.4               | neurmorphic image/speech recognition datasets with $C_{R-R}=1.0$ , $C_{R-R}=0.2$ .<br>R-SNN benchmarks used in this work                                                                                                                               |          |

| 0.4               | n-binin denominarks used in this work                                                                                                                                                                                                                  | 103      |

| 6.5 | Detailed performance metrics: PE utilization, number of operations and data reuse in each integration (feedforward/recurrent) step | 110 |

|-----|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.1 | A high-level overview of the user-defined inputs                                                                                   | 128 |

| 7.2 | Architecture specifications                                                                                                        | 128 |

| 7.3 | Performance on fully-connected and convolutional networks: NMNIST and                                                              |     |

|     | DVS-Gesture. TWS denotes the applied time window size                                                                              | 134 |

| 7.4 | Performance on recurrent networks: N-TIDIGITS. TWS denotes the ap-                                                                 |     |

|     | plied time window size                                                                                                             | 135 |

## Chapter 1

## Introduction

## 1.1 Neuromorphic Computing Systems

Conventional non-spiking artificial neural network models, or simply ANNs, employ only rate coding where continuous-valued signals resulted from activation functions such as sigmoid and rectified linear unit (ReLU) correspond to average firing rates. On the other hand, spiking neural networks (SNNs) more closely resemble biological neurons, explicitly model all-or-none firing spikes across both space and time, and can leverage a rich family of rate and temporal codes for complex spatiotemporal information processing.

<sup>© 2022</sup> IEEE. Reprinted, with permission, from Jeong-Jun Lee, Wenrui Zhang and Peng Li, "Parallel Time Batching: Systolic-Array Acceleration of Sparse Spiking Neural Computation", 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA), May 2022. © 2022 ACM. Reprinted, with permission, from Lee, Jeong-Jun, Wenrui Zhang, Yuan Xie, and Peng Li. "SaARSP: An Architecture for Systolic-Array Acceleration of Recurrent Spiking Neural Networks." ACM Journal on Emerging Technologies in Computing Systems (JETC), 2022 © 2021 IEEE. Reprinted, with permission, from Jeong-Jun Lee, Jianhao Chen, Wenrui Zhang and Peng Li, "Systolic-Array Spiking Neural Accelerators with Dynamic Heterogeneous Voltage Regulation", 2021 International Joint Conference on Neural Networks (IJCNN), Sep 2021. © 2020 IEEE. Reprinted, with permission, from Jeong-Jun Lee and Peng Li, "Reconfigurable Dataflow Optimization for Spatiotemporal Spiking Neural Computation on Systolic Array Accelerators", 2020 IEEE 38th International Conference on Computer Design (ICCD), Dec 2020. © 2020 Frontiers. Reprinted, with permission, from Lee, Jeongjun, Renqian Zhang, Wenrui Zhang, Yu Liu, and Peng Li. "Spike-train level direct feedback alignment: sidestepping backpropagation for on-chip training of spiking neural nets." Frontiers in Neuroscience 14 (2020): 143.

Recent studies reported competitive performances for various image and speech tasks with biologically inspired [1, 2] and backpropagation based [3, 4] SNN training methods. With great potentials in ultra-low power event-driven learning leveraging the spatiotemproal dynamics of SNNs [5], neuromorphic processors have gathered significant interest in both academia and industry, resulting in well-known neuromorphic chips including IBM's TrueNorth [6] and Intel's Loihi [7].

## 1.2 Spiking Neural Network Algorithms

Despite the recent progresses in SNNs and neuromorphic processor designs, fully leveraging the theoretical computing advantages of SNNs over traditional artificial neural networks (ANNs) [5] to achieve the state-of-the-art performance for real-world applications remains challenging. One chief difficulty here lies in training of SNNs in terms of achievable performance and computational complexity.

Inspired by the success of error backpropagation (BP) and its variants such as stochastic gradient decent in training conventional ANNs [8], various SNN BP methods have emerged, aiming at attaining the same level of performance [9, 10, 11, 4]. The major challenges in BP training of SNNs stem from the non-differentiability of spike events and temporal dynamics that prevent straightforward derivative computation. SpikeProp [9] is the first BP algorithm to train SNNs by BP. However, SpikeProp is limited to single-spike training for learning simple functions like XOR. [10] proposes a BP algorithm which differentiates neuron's membrane potential instead of discrete output spikes. [11] improves [10] by capturing temporal effects with backpropagogation through time (BPTT) [12]. However, the error gradient is still computed by differentiating the membrane potential, leading to inconsistency w.r.t the rate-coded loss function. More recently, [4] proposes a hybrid macro/micro level backpropagation (HM2-BP) algorithm for training multi-layer

SNNs, which addresses the aforementioned issues. HM2-BP precisely captures the temporal behavior of the SNN at the microscopic level and directly computes the gradient of the rate-coded loss function w.r.t tunable parameters. As a result, HM2-BP demonstrates the state-of-the art learning performances on widely adopted SNN benchmarks such as MNIST [13] and Neuromorphic-MNIST (N-MNIST) [14], outperforming all other existing BP algorithms based on the leaky integrate-and-fire model.

While achieving excellent results, the aforementioned SNN BP algorithms are hampered by several limitations. The error signal is propagated backward layer by layer through weights symmetric to the feed-forward weights. This is considered not biologically-plausible. Furthermore, BP algorithms involve complex layer-by-layer backward computations, which is expensive to implement on-chip and introduces high training latency. For instance, while HM2-BP improves the scalability of BPTT [11] by operating on the spike-train level, i.e. application of BP does not discretize time, it still involves complex computations and its latency in the backward phase is proportional to network depth.

## 1.3 Spiking Neural Network Accelerators

Spiking neural networks (SNNs) more closely resemble biological neurons, explicitly model all-or-none firing spikes across both space and time, and can leverage a rich family of rate and temporal codes for complex spatiotemporal information processing. Recent studies reported competitive performances for various image and speech tasks with biologically inspired [1, 2] and backpropagation based [3, 4] SNN training methods. With great potentials in ultra-low power event-driven learning leveraging the spatiotemporal dynamics of SNNs [5], neuromorphic processors have gathered significant interest in both academia and industry, resulting in well-known neuromorphic chips including IBM's TrueNorth [6] and Intel's Loihi [7].

Nevertheless, hardware acceleration of spike-based models is complicated by temporal computation and sparse spiking activities in both space and time, two new challenges that are absent in accelerators of non-spiking networks such as DNNs. The added temporal dimension is fundamental to SNNs but introduces difficulties in managing compute and data movement. Furthermore, biological brains and engineered SNN models often exhibit a great deal of firing activity sparsity across both space and time, manifesting their promising efficiency. The sparse spiking activities of a well-trained SNN may vary from neurons to neurons, and from time points to time points. To fully explore the benefits of SNNs, one must address the challenges brought by irregular patterns of spatial and temporal sparsity.

Compared to the large body of work on DNN accelerators, e.g., [15, 16, 17, 18, 19], much less research has been devoted to SNN hardware accelerator architectures [20, 21, 22, 23, 24]. The two best-known industrial neuromorphic chips, IBM's TrueNorth [6] and Intel's Loihi [7], are based on a many-core architecture, comprising neuro-synaptic cores with an asynchronous mesh for core-to-core communication. Each neuromorphic core emulates a certain number of spiking neurons in a time-sequential manner. While both architectures target large-scale spiking neural computations with low power, there exist two primary disadvantages in these two designs: 1) lack of parallelism in each core: the computations associated with different spiking neurons are executed sequentially, one neuron at a time, and from time points to time points; and 2) assumption of large core memory: as opposed to many practical cases, it is assumed that all weights of the network are fully stored on-chip, and hence efficient dataflows maximizing the reuse of weight data are not targeted. These issues limit the achievable throughput and/or do not well support SNN acceleration on resource-constrained hardware like ones for edge computing.

The recent SNN architecture SpinalFlow explores a novel compressed, time-stamped,

and sorted spike input/output representation [20]. The main drawback of SpinalFlow is that it only targets the class of temporally-coded spiking neuronal models in which each neuron fires at most once, which is a highly restrictive type and has limited accuracy for challenging learning tasks [25, 26]. While the smart exploration of such extreme temporal sparsity leads to large latency and energy efficiency benefits, SpinalFlow is not applicable to broader classes of SNNs employing rate and other types of temporal codes or a combination of thereof for high-accuracy decision making. Since the maximum firing count for each neuron is one, the structured sparse firing activities are handled as chronologically sorted inputs with a dearth of parallel acceleration through time.

## 1.4 Outline

The summary of the rest of this dissertation is as follows: In Chapter 2, we provide a brief background on unique characteristics of SNNs, basic operations in spiking neuron models, datasets and systolic arrays. In Chapter 3, we perform algorithm-hardware co-optimization and demonstrate the first on-chip hardware realization of Spike-Train level Direct Feedback Alignment (ST-DFA) for SNNs with significantly improved accelerator performance compared to conventional Back-Propagation (BP). In Chapter 4, we propose holistic reconfigurable dataflow optimization for systolic array acceleration of spiking convolutional networks (S-CNNs), and introduce SNN dataflow simulator to support systemic design space exploration. In Chapter 5, we introduce a novel technique for parallel acceleration in both space and time based on simultaneous processing of multiple time batches with a temporal granularity defined by the Time Window (TW) size, along with Spatiotemporally-non-overlapping Spiking Activity Packing (StSAP). In Chapter 6, we explore the proposed parallel acceleration technique to decouple the processing of feedforward synaptic connections from that of recurrent connections, for efficient acceleration

ation of complex spatiotemporal dynamics arising in R-SNNs. In Chapter 7, we propose a novel, application independent solution called Split-Time Temporal (STT) coding that allows the exploitation of temporal information compression with structured sparsity and parallelism across time, which is further supported by Integration-Through-Time (ITT). Chapter 8 summarizes this dissertation and includes discussions on potential future work.

## Chapter 2

## Background

## 2.1 Unique Characteristics of SNNs

Compared with non-spiking ANNs, the most distinctive features of SNNs are temporal data processing and data representation. All data types in ANNs, e.g., input/output feature maps (IFmap/OFmap) and filters data in widely adopted convolutional neural networks (CNNs), are multi-bit. The most commonly used data representations in non-spiking ANN hardware accelerators are based on 8- to 16-bit precision [15, 19, 27, 28], which may be further compressed using techniques such as weight quantization [29, 30]. On the other hand, input/output activations of a spiking layer are binary due to the all-or-none characteristics of spiking neural firing characteristics, which can be more compactly stored than multi-bit partial sum data. This disparity in data representations can be explored in dataflow optimization [21, 20].

While integration and activation steps in ANNs exclude temporal information, a spiking neuron integrates its inputs over time, as shown in Fig. 2.1(b). The spatiotemporal information processing in SNNs empower various models and applications [3, 31, 32]. However, the added temporal dimension causes intertwined spatiotemporal interactions,

Figure 2.1: (a): Layer operation in SNNs. (b): Main steps of spatiotemporal operation in a spiking neuron.

rendering SNN hardware accelerators to confront complex data movement/computation, which we address in later sections.

## 2.2 Spiking Neural Network Operations

## 2.2.1 Spiking Neurons

Common to literally all spiking neural models, operations in one spiking neuron comprise three main steps at each time point  $t_i$ , where time point is a minimum unit of time in SNNs: 1) integration of pre-synaptic spike inputs, 2) update of the post-synaptic membrane potential, and 3) conditional generation of post-synaptic spike output (action potential). As shown in Fig. 2.1 and during Step 1, if a particular pre-synaptic neuron fires, the induced pre-synaptic current will be integrated by the post-synaptic neuron. From a modeling perspective, in this case the corresponding synaptic weight between the two neurons, or more generally a quantity determined by the weight, will be added (accumulated) to the post-synaptic membrane potential. After integrating all pre-synaptic currents, in Step 2, the post-synaptic spiking neuron updates its membrane potential by

Figure 2.2: (a): Schematic for feedforward layer operation in SNN. (b): Schematic for recurrent layer operation in R-SNN.

adding to it the sum of integrated synaptic currents. Temporal decaying of the membrane potential can also be included if the neural model is leaky. In the last step, the spiking neuron compares its updated membrane potential with a pre-determined firing threshold and generates an output spike (action potential) if the membrane potential exceeds the threshold, as shown in Fig. 2.1(b). The same process repeats for all time points involved in a given spike-based task.

## 2.2.2 Spiking Neural Networks

Spiking neurons are wired to form a network. The aforementioned temporal processing of individual spiking neurons are brought into a network setting in which neurons communicate with each other and perform computation by receiving and generating stereotyped all-or-none spikes both spatially and temporally. This dissertation considers wide range of network types, including general the most general (deep) multi-layer feedforward (fully-connected) spiking neural network (SNN), convolutional spiking neural networks (S-CNN or spiking-CNN), and recurrent spiking neural network (R-SNN) architecture, which comprises multiple fully-connected or convolutional or recurrent layers or a combination of thereof.

#### Feedforward spiking layers

Conventional and the most natural approach for temporal data processing is to perform operations time point by time point in a sequential manner, for all time points in time stride. In feedforward spiking layers, operations in a single spiking neuron consist of three steps at each time point  $t_k$ :

**Step 1:** Synaptic input integration at  $t_k$ :

$$\vec{p}^{Post}[t_k] = \mathbf{W}_{Post,Pre} \times \vec{s}^{Pre}[t_k] \tag{2.1}$$

**Step 2:** Membrane potential update at  $t_k$ :

$$\vec{v}^{Post}[t_k] = \vec{v}^{Post}[t_{k-1}] + \vec{p}^{Post}[t_k] - V_{leak}^{Post}$$

(2.2)

**Step 3:** Conditional spike output generation at  $t_k$ :

$$\vec{s}^{Post}[t_k] = \boldsymbol{f}(\vec{v}^{Post}[t_k]) \tag{2.3}$$

$$\mathbf{f}(v_i^{Post}[t_k]) = \begin{cases} 1, & \text{if } v_i^{Post}[t_k] \ge V_{th}^{Post} \to v_i^{Post}[t_k] = 0\\ 0 & \text{else } \to v_i^{Post}[t_k] = v_i^{Post}[t_k] \end{cases}$$

(2.4)

where the Post and Pre denote the pre-synaptic layer and the post-synaptic layer, and i represents the neuron indices in the post-synaptic layer.  $\vec{p}^{Post}[t_k]$ ,  $\vec{v}^{Post}[t_k]$ , and  $\vec{s}^{Post}[t_k]$  are vectors, representing the integrated partial sum of the spike inputs from the pre-synaptic layer, membrane potential and spike output of the neurons in the post-synaptic layer at time  $t_k$ , respectively.  $\mathbf{W}_{Post,Pre}$  is the matrix of the feedforward synaptic weights between pre- and post-synaptic layers,  $V_{th}$  and  $V_{leak}$  are the firing threshold and leaky

parameter in post-synaptic layer, respectively. f is a non-linear, all-or-non activation function with a given  $V_{th}$ . In the above steps, the synaptic input integration (Step 1) incurs matrix-vector multiplication and takes place at each time point, comprising the dominant complexity of SNN acceleration.

Importantly, the above steps are repeated at each time point, across all time points in time stride. The above steps present fundamental operations in any feedforward layers including fully-connected and convolutional layers.

### Recurrent Spiking Layers

Processing neural computations of a recurrent layer in SNNs follow the same three steps in the feedforward layer with additional synaptic inputs. In a recurrent layer, lateral recurrent inputs are also considered in addition to the feedforward input integration (Step 1) in (2.1):

**Step 1\*:** Feedforward synaptic input integration at  $t_k$ :

$$\vec{p}_F^{Post}[t_k] = \mathbf{W}_{Post,Pre} \times \vec{s}^{Pre}[t_k]$$

(2.5)

$$\vec{p}_R^{Post}[t_k] = \mathbf{W}_{Post,Post} \times \vec{s}^{Post}[t_{k-1}]$$

(2.6)

$$\vec{p}^{Post}[t_k] = \vec{p}_F^{Post}[t_k] + \vec{p}_R^{Post}[t_k] \tag{2.7}$$

where  $\vec{p}_F^{Post}[t_k]$ ,  $\vec{p}_R^{Post}[t_k]$  and  $\vec{p}^{Post}[t_k]$  are vectors, representing the partial sum of the feedforward input integration, recurrent input integration, and fully-integrated partial sum in the post-synaptic layer at time  $t_k$ , respectively.  $\mathbf{W}_{Post,Post}$  is the matrix of the

Figure 2.3: Computation of convolution layer in S-CNNs.

Table 2.1: Shape parameters of a CONV layer in S-CNNs

| Shape Parameter | Description                |

|-----------------|----------------------------|

| H / H           | ifmap width / height       |

| E / E           | ofmap width / height       |

| R / R           | filter width / height      |

| С               | # of ifmap/filter channels |

| M               | # of ofmap channels        |

| Т               | # of time steps            |

|                 |                            |

recurrent synaptic weights of the post-synaptic (recurrent) layer.

### Convolutional Spiking Layers

The fundamental operations of a single spiking neuron in spiking-CNNs (S-CNNs) follow the aforementioned three main steps  $(2.1)\sim(2.4)$  where the computation involves multiple filters:

### At a given time-point $t_k$ ,

**Step 1:** Integration of receptive field synaptic inputs at  $t_k$ :

$$\mathbf{P}[m][x][y][t_k] = \sum_{c=0}^{C-1} \sum_{i=0}^{R-1} \sum_{j=0}^{R-1} \mathbf{W}[m][c][i][j] \times \mathbf{I}[c][Ux+i][Uy+j][t_k]$$

(2.8)

Step 2: Membrane potential update:

$$\mathbf{V}[m][x][y][t_k] = \mathbf{V}[m][x][y][t_{k-1}] + \mathbf{P}[m][x][y][t_k]$$

(2.9)

**Step 3:** Conditional spike output generation:

$$\mathbf{O}[m][x][y][t_k] = \begin{cases} 1, & \text{if } \mathbf{V}[m][x][y][t_k] \ge V_{th}^O : \mathbf{V}[m][x][y][t_k] = 0\\ 0 & \text{else} : \mathbf{V}[m][x][y][t_k] = \mathbf{V}[m][x][y][t_k] \end{cases}$$

(2.10)

$0 \le x,y < E, E = (H - R + U)/U, 0 \le c < C, 0 \le m < M, 0 \le t < T$

Move onto the next time-point  $(t_{k+1})$ , and repeat the above three steps.

where  $\mathbf{P}$ ,  $\mathbf{V}$ ,  $\mathbf{O}$ ,  $\mathbf{I}$  and  $\mathbf{W}$  are the matrices of the partial sums (Psums), membrane potentials, output feature maps (OFmaps), input feature maps (IFmaps) and filters, respectively.  $\mathbf{P}[m][x][y][t_k]$  is the partial sum of the neuron at position (x,y) and in output channel m of the OFmap at time  $t_k$ . Other matrices are defined similarly. U is a given stride size, T is the number of processing time steps, and all the other shape parameters are listed and illustrated in Table 2.1 and Fig. 2.3.  $(2.8) \sim (2.10)$  correspond to each of the three steps discussed in  $(2.1) \sim (2.4)$ .

### 2.3 Datasets

We adopt various types of datasets for the evalutation including images/speeches, neuromorphic images/speeches, and neuromorphic videos.

#### **MNIST**

The MNIST handwritten digit dataset [13] contains 60k training and 10k testing samples, each of which is a  $28 \times 28$  grayscale image. Each pixel value of the MNIST image is converted into a spike train using Poisson sampling and the probability of spike generation is proportional to the pixel intensity. Thus, inputs are encoded into a 2D  $784 \times N_t$  matrix where  $N_t$  is the simulation time steps. Especially, due to the limited hardware resources available on the Xilinx Zynq ZC706 board, we crop each image to include only the  $14 \times 14$  pixels around the center for FPGA evaluation in chapter 3. For all other experiments, each pixel value of an MNIST image is converted into a real-valued input current.

#### Fashion-MNIST

The Fashion-MNIST dataset [33] is a MNIST-like, but much more difficult, clothing classification dataset which contains 28x28 grey-scale images of clothing items. Fashion-MNIST dataset contains 60k training examples and 10k testing examples with 10 classes.

#### CIFAR10-DVS

The CIFAR-10 dataset [34] consists of  $60,000~32\times32$  color images in 10 classes, with 6,000 images per class. The CIFAR10-DVS [35] dataset is a neuromorphic version of CIFAR10, using a dynamic vision sensor (DVS) camera, an event-stream dataset for object classification containing 10k examples with an event-based sensor, whose resolution is  $128\times128$  pixels.

#### TI46-Alpha

TI46 speech corpus [36] contains spoken English alphabets/digits audios from 16 speakers. In this dissertation, we only use alphabets of the full TI46 speech corpus. For the rest of this dissertation, we call this as TI46-Alpha or Ti46, where TI46-Alpha consists of 4142 and 6628 spoken English examples in 26 classes for training and testing, respectively. The continuous temporal speech waveforms are preprocessed by Lyon's ear model [37] with the sample rate of 12.5 kHz where each sample is encoded into 78 channels.

#### **N-MNIST**

Similar to CIFAR10-DVS, the N-MNIST dataset [14] is a neuromorphic version of the MNIST dataset using the dynamic vision sensor (DVS) [38] in front of static digit images on a computer monitor. Changes of pixel intensity at each location are encoded as spike trains where image size is  $34 \times 34$  rather than  $28 \times 28$  due to the relative shifts of each image. As in [39], we reduce the time resolution into a few hundred time steps since original dataset requires 300000 time steps.

#### **N-TIDIGITS**

TIDIGITS [40] is a speech dataset where each sample has 64 input channels, processed by CochleaAMS1b sensor and takes about 0.9s. The N-TIDIGITS [41] is a neuromorphic version of TIDIGITS, where connected-digit sequences are not considered and we only consider single-digit samples with 2,475 samples for training and 2.475 samples for testing. Similar to N-MNIST, we reduce the temporal resolution by compressing 1 us to 3 ms, forming 300 time steps.

#### **DVS-Gesture**

The DVS-Gesture dataset [42] consists of event streams of hand/arm gestures. Using the dynamic vision sensor (DVS) camera, the input frame is  $128 \times 128$  pixels with two channels where we follow the same preprocessing procedures in [43]. While each action (sample) lasts for about 6 s, we only consider the first 1.5 s of action video as in [39] and compress the temporal resolution to 5 ms which produced 300 time steps for each sample.

## 2.4 Systolic Array

Systolic array architectures offer efficient parallel processing with high spatiotemporal locality and compute density. In many prior works, a tightly coupled 2-D systolic array has been adopted for CNN accelerations with clear advantages [44, 19, 45, 18]. Systolic arrays propagate data horizontally and vertically, i.e., from left to right and from top to bottom through all processing elements (PEs) in a globally synchronized manner, hence naturally exploit high locality and compute density. For example, a unidirectional link is utilized in the vertical data propagation to allow each PE to receive the input from its upstream neighbor, perform the computation and store the results, and continue to pass the data to its downstream neighbor. Furthermore, data are fed from edges of the array to provide sufficient data distribution bandwidth. The above properties result in a streamlined accelerator platform for managing data fetching without requiring complicated inter-PE communication. With the advantages in terms of complexity, distribution bandwidth, locality, and compute density, systolic arrays are adopted for efficient acceleration of spiking computation in chapter  $4 \sim 7$ , which well-aligns with parallel-acceleration techniques introduced in this dissertation.

## Chapter 3

## Spiking Neural Processor with

## Direct Feedback Alignment

In this chapter, we present the first study on realizing competitive spike-train level back-propagation (BP) like algorithms to enable on-chip training of SNNs. We propose a novel spike-train level direct feedback alignment (ST-DFA) algorithm, which is much more bio-plausible and hardware friendly than BP. Algorithm and hardware co-optimization and efficient online neural signal computation are explored for on-chip implementation of ST-DFA. On the Xilinx ZC706 FPGA board, the proposed hardware-efficient ST-DFA shows excellent performance vs. overhead tradeoffs for real-world speech and image classification applications. SNN neural processors with on-chip ST-DFA training show competitive classification accuracy of 96.27% for the MNIST dataset with 4× input resolution reduction and 84.88% for the challenging 16-speaker TI46 speech corpus, respectively. Compared to the hardware implementation of the state-of-the-art BP algorithm HM2-BP, the design of the proposed ST-DFA reduces functional resources by 76.7% and backward training latency by 31.6% while gracefully trading off classification performance.

This work aims to answer the following questions: 1) Can biologically plausible mech-

anisms be developed to sidestep complex BP algorithms while delivering competitive performance? 2) Can such mechanisms be leveraged for efficient on-chip training of multi-layer SNNs?

# 3.1 Direct Feedback Alignment (DFA)

### 3.1.1 Direct Feedback Alignment

Backpropagation (BP) has been widely applied to train neural networks. It is based upon computing a global error at the output layer and then propagating the error signal to hidden neurons layer by layer. During this process, the errors of a preceding layer are multiplied with a weight matrix that is completely symmetric to the one for the feed-forward connections. This fact is not considered biologically plausible. A recent discover called Feedback Alignment (FA) [46] demonstrates that the weights used for propagating the error layer by layer need not be symmetric to the weights used for forward propagation to achieve good performance. The feedback weight matrix can be randomly generated and then stay unchanged since the network can learn how to make feedback useful through training. [47] applies FA for training SNNs.

A more disruptive approach called Direct Feedback Alignment (DFA) is proposed in DNNs [48]. DFA is compared with BP in Fig. 3.1. Unlike propagating the error back layer by layer in BP and FA, DFA feeds back the error through fixed random feedback connections directly from the output layer to each hidden layer, eliminating the need for layer-by-layer error backpropagation or feedback. DFA is considered more biologically plausible because the error is generated almost completely local with no long backpropagation/feed back train and symmetric weights are not required. [48] shows that for conventional multi-layer ANNs like DNNs, the use of DFA can achieve competitive

Figure 3.1: (a) Backpropagation (BP) vs. (b) direct feedback alignment (DFA). Solid arrows indicate feedforward paths and dashed arrows indicate feedback paths. The feedback matrices  $B_1$  and  $B_2$  need not be symmetric to  $W_2$  or  $W_3$ .

results with insignificant performance drops when compared with the state-of-the-art BP methods.

In this paper, we extend the DFA for conventional ANNs [48] for SNNs. To the best of our knowledge, this is the first work applying DFA to SNNs. Furthermore, our DFA approach, dubbed ST-DFA, operates on the spike-train level, hence offering improved scalability in both space (network depth) and time.

# 3.1.2 Spike-train Level Post-synaptic Potential

Before describing the proposed ST-DFA in Section 3.2, we present the concept of Spike-train Level Post-synaptic Potential (S-PSP) that is behind the spike-train level computation of ST-DFA.

The widely adopted leaky integrate-and-fire (LIF) model for spiking neurons is given by [49]:

$$\tau_m \frac{u_i(t)}{dt} = -u_i(t) + R \,\alpha_i(t), \tag{3.1}$$

with

$$\tau_s \frac{\alpha_i(t)}{dt} = -\alpha_i(t) + \sum_j w_{ij} \sum_{t_i^{(f)}} D\left(t - t_j^{(f)}\right), \tag{3.2}$$

where  $u_i(t)$  is the membrane potential of the neuron i,  $\alpha_i(t)$  is the first order synaptic model with time constant  $\tau_s$ , and  $\tau_m$  is the time constant of membrane potential with value  $\tau_m = RC$ . R and C are the effective leaky resistance and effective membra ne capacitance.  $w_{ij}$  is the weight of the synapse from the pre-synaptic neuron j to the neuron i.  $t_j^{(f)}$  denotes a particular firing time of the neuron j. D(t) is the Dirac delta function. R is set to 1 since it can be absorbed into synaptic weights.

Integrating (3.1) and (3.2) gives the spike response model (SRM) [4]: