# **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

### **Title**

Efficient use of execution resources in multicore processor architectures

#### **Permalink**

https://escholarship.org/uc/item/75h4k9fc

#### **Author**

DeVuyst, Matthew David

## **Publication Date**

2011

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Efficient Use of Execution Resources in Multicore Processor Architectures

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

Matthew David DeVuyst

## Committee in charge:

Professor Dean Tullsen, Chair Professor Clark Guest Professor Chandra Krintz Professor Sorin Lerner Professor Steven Swanson

Copyright

Matthew David DeVuyst, 2011

All rights reserved.

| The dissertation of Matthew David DeVuyst is approved,   |

|----------------------------------------------------------|

| and it is acceptable in quality and form for publication |

| on microfilm and electronically:                         |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

| Chair                                                    |

University of California, San Diego

2011

## DEDICATION

Soli Deo Gloria

## EPIGRAPH

For from Him and through Him and to Him are all things. To Him be the glory forever. Amen.

—Romans 11:36 (NASB version)

## TABLE OF CONTENTS

| Signature Pa  | age .                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                              | iii                                                                                  |

|---------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Dedication .  |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                              | iv                                                                                   |

| Epigraph .    |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                              | v                                                                                    |

| Table of Con  | ntents                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                              | vi                                                                                   |

| List of Figur | res .                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                              | ix                                                                                   |

| List of Table | es                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                              | хi                                                                                   |

| Acknowledg    | ement                                  | s                                                                                                                                                                                                                                                                                                                                                                                                                                            | xii                                                                                  |

| Vita and Pu   | ıblicat                                | ions                                                                                                                                                                                                                                                                                                                                                                                                                                         | xiv                                                                                  |

| Abstract of   | the Di                                 | issertation                                                                                                                                                                                                                                                                                                                                                                                                                                  | XV                                                                                   |

| Chapter 1     | Intro<br>1.1<br>1.2                    | Parallelizing Single-Threaded Code                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                    |

| Chapter 2     | Run<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Introduction Related Work 2.2.1 Transactional Memory 2.2.2 Dynamic Optimization 2.2.3 Dynamic Loop Parallelization 2.2.4 Speculative Multithreading Architecture 2.3.1 Code Transformation Overview Parallelization 2.4.1 Dynamic Optimization Framework 2.4.2 Partitioning the Iteration Space Code Generation 2.5.1 Transaction Wrapping 2.5.2 Forking and Halting Parallel Threads 2.5.3 Data Flow Through Registers 2.5.4 Function Calls | 9<br>9<br>11<br>15<br>17<br>18<br>19<br>20<br>22<br>24<br>28<br>28<br>32<br>34<br>41 |

|               | 2.6                                    | Experimental Methodology                                                                                                                                                                                                                                                                                                                                                                                                                     | 43                                                                                   |

|           |      | 2.6.1 Transactional Memory                                                                                                                         | 44 |

|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|           |      | 2.6.2 Simulation and Benchmarks                                                                                                                    | 45 |

|           | 2.7  | Results                                                                                                                                            | 47 |

|           |      | 2.7.1 Tile Size                                                                                                                                    | 48 |

|           |      | 2.7.2 TM Cache Granularity                                                                                                                         | 53 |

|           | 2.8  | Conclusion                                                                                                                                         | 55 |

| Chapter 3 | Unb  | alanced Scheduling on a Multithreading Multiprocessor                                                                                              | 57 |

|           | 3.1  | Introduction                                                                                                                                       | 57 |

|           | 3.2  | Related Work                                                                                                                                       | 60 |

|           | 3.3  | Architecture                                                                                                                                       | 63 |

|           | 3.4  | Scheduling Policies                                                                                                                                | 65 |

|           |      | 3.4.1 Sampling-based Policies                                                                                                                      | 66 |

|           |      | 3.4.2 Electron Policies                                                                                                                            | 68 |

|           |      | 3.4.3 Decision Metrics                                                                                                                             | 70 |

|           | 3.5  | Experimental Methodology                                                                                                                           | 72 |

|           |      | 3.5.1 Scheduling Parameters                                                                                                                        | 72 |

|           |      | 3.5.2 Workload Construction                                                                                                                        | 72 |

|           |      | 3.5.3 Simulation Methodology                                                                                                                       | 73 |

|           | 3.6  | Analysis and Results                                                                                                                               | 73 |

|           |      | 3.6.1 Scheduling for Both Energy and Performance                                                                                                   | 75 |

|           |      | 3.6.2 Scheduling for Other Metrics                                                                                                                 | 82 |

|           | 3.7  | Conclusions                                                                                                                                        | 84 |

| Chapter 4 | Exec | eution Migration on a Heterogeneous CMP                                                                                                            | 86 |

|           | 4.1  | Introduction                                                                                                                                       | 86 |

|           | 4.2  | Related Work                                                                                                                                       | 90 |

|           |      | 4.2.1 Homogeneous Migration and Checkpointing                                                                                                      | 91 |

|           |      | 4.2.2 Theoretical Models                                                                                                                           | 92 |

|           |      | 4.2.3 Early Work                                                                                                                                   | 92 |

|           |      | 4.2.4 Instrumenting Well-Typed C Code                                                                                                              | 93 |

|           |      | 4.2.5 Other Languages                                                                                                                              | 97 |

|           |      | 4.2.6 Other Directions                                                                                                                             | 98 |

|           |      | 4.2.7 Differences                                                                                                                                  | 99 |

|           | 4.3  | Overview of Migration                                                                                                                              | 00 |

|           | 4.4  | Memory Image Consistency                                                                                                                           | 03 |

|           |      | 4.4.1 Overall Section Structure                                                                                                                    | 04 |

|           |      | 4.4.2 Code Section Consistency $\dots \dots \dots$ | 04 |

|           |      | 4.4.3 Heap Consistency                                                                                                                             | 05 |

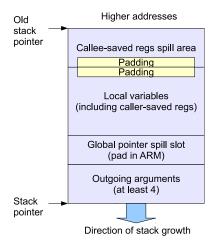

|           |      | 4.4.4 Stack Consistency                                                                                                                            | 06 |

|           | 4.5  | Migration Process                                                                                                                                  | 12 |

|           |      | 4.5.1 Stack Transformation Prerequisites                                                                                                           | 13 |

|           |      |                                                                                                                                                    | 22 |

|              | 4.6 | Experimental Methodology                      | . 125 |

|--------------|-----|-----------------------------------------------|-------|

|              |     | 4.6.1 High-Level Pass Modifications           | . 125 |

|              |     | 4.6.2 Measuring Runtime Performance           | . 127 |

|              |     | 4.6.3 Measuring Migration Overhead            | . 129 |

|              | 4.7 | Results                                       | . 129 |

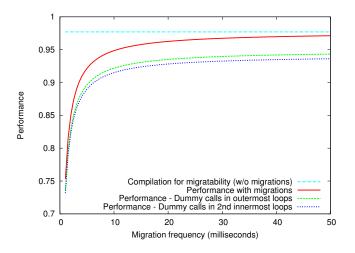

|              |     | 4.7.1 Runtime Performance of Migratable Code  | . 129 |

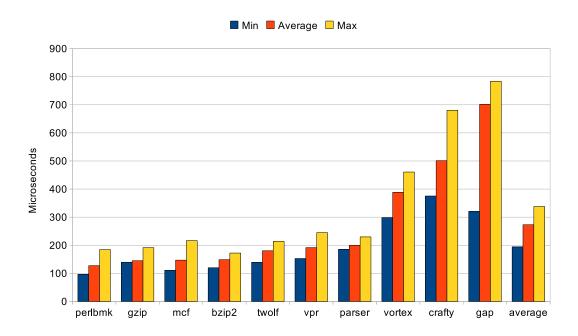

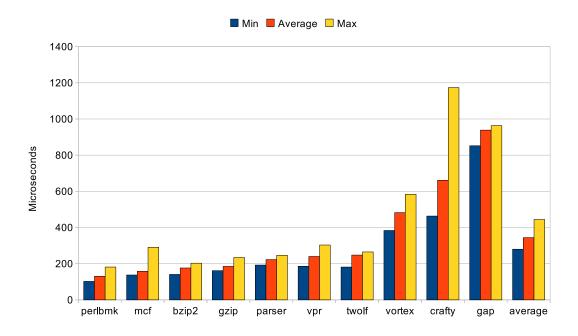

|              |     | 4.7.2 Migration Cost                          | . 130 |

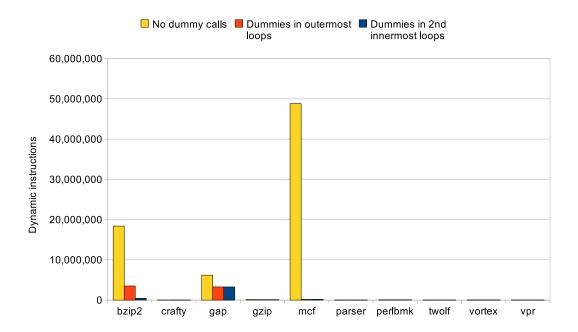

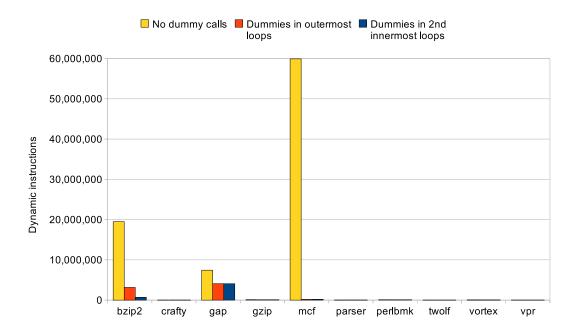

|              |     | 4.7.3 Frequency of Potential Migration Points | . 133 |

|              | 4.8 | Conclusion                                    | . 136 |

| Chapter 5    | Con | clusion                                       | . 138 |

| _            | 5.1 | Runtime Parallelization                       | . 139 |

|              | 5.2 | Scheduling for a Multithreaded CMP            | . 140 |

|              | 5.3 | Execution Migration                           | . 141 |

| Bibliography |     |                                               | 144   |

## LIST OF FIGURES

| Figure 2.1:  | Potential memory aliasing makes this loop hard to parallelize     | 20  |

|--------------|-------------------------------------------------------------------|-----|

| Figure 2.2:  | Wrapping the loop body in a transaction allows for safe and       |     |

|              | optimistic parallelization                                        | 21  |

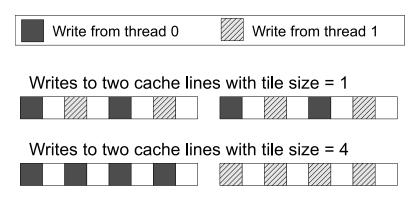

| Figure 2.3:  | Tiling eliminating false sharing                                  | 27  |

| Figure 2.4:  | C code to demonstrate loop early-exit procedure                   | 33  |

| Figure 2.5:  | Pseudo-assembly code to demonstrate induction code generation.    | 35  |

| Figure 2.6:  | C code to illustrate two kinds of register writes                 | 37  |

| Figure 2.7:  | Loads in induction code                                           | 40  |

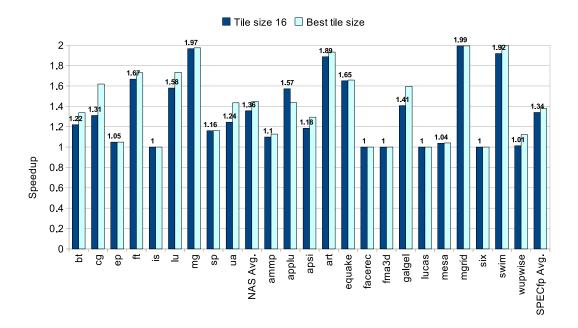

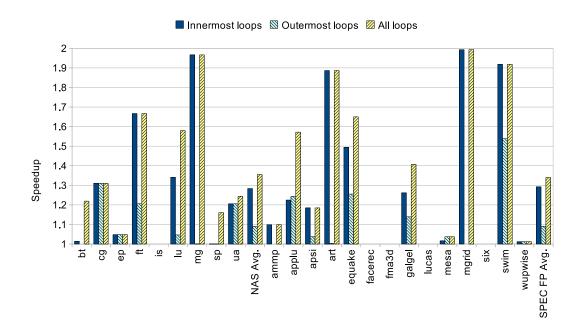

| Figure 2.8:  | Speedups of NAS and SPEC FP benchmarks                            | 48  |

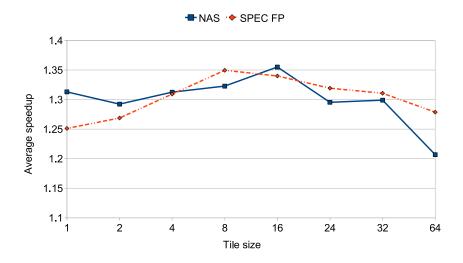

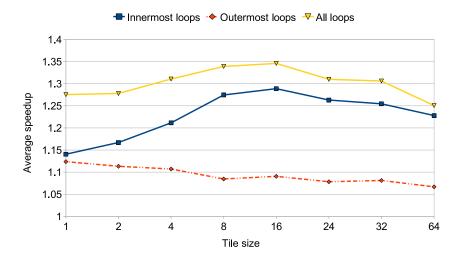

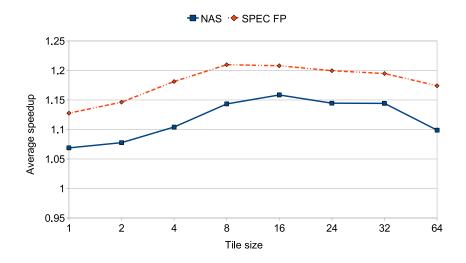

| Figure 2.9:  | Speedup across various tile sizes                                 | 49  |

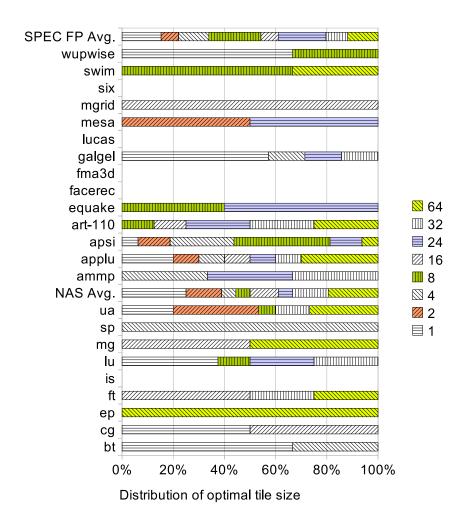

| Figure 2.10: | Ideal tile sizes                                                  | 51  |

| Figure 2.11: | Speedups of NAS and SPEC FP benchmarks under different            |     |

|              | loop selection policies: innermost loops only, outermost loops    |     |

|              | only, and unconstrained                                           | 52  |

| Figure 2.12: | Speedup across various tile sizes under different loop selection  |     |

|              | policies                                                          | 52  |

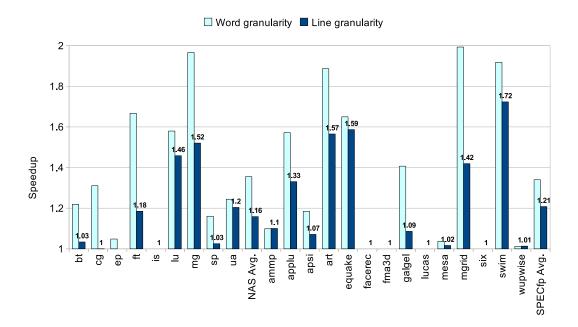

| Figure 2.13: | Speedups of NAS and SPEC FP benchmarks at different gran-         |     |

|              | ularities                                                         | 54  |

| Figure 2.14: | Speedup across various tile sizes                                 | 54  |

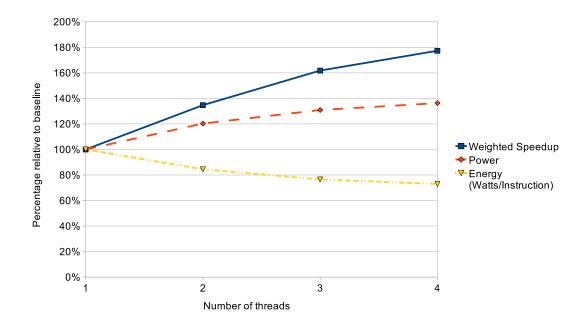

| Figure 3.1:  | Average marginal utility and cost of using each SMT context       |     |

|              | on a single core.                                                 | 76  |

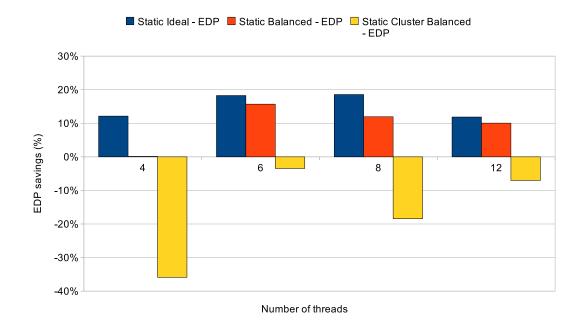

| Figure 3.2:  | The effectiveness of unbalanced and balanced static scheduling    |     |

| _            | policies in reducing energy-delay product                         | 77  |

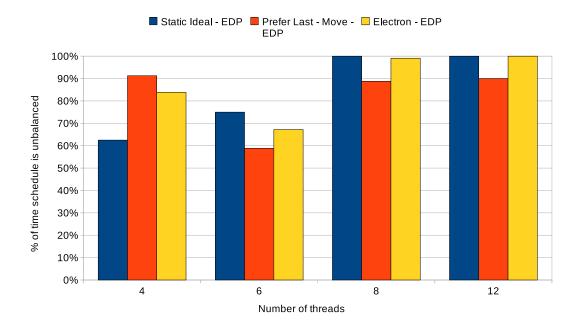

| Figure 3.3:  | Extent of imbalance for the best schedules found by static poli-  |     |

|              | cies targeting EDP                                                | 77  |

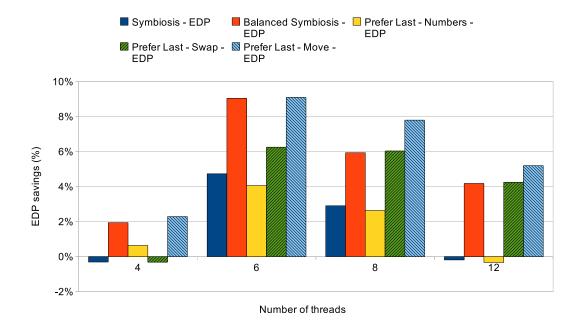

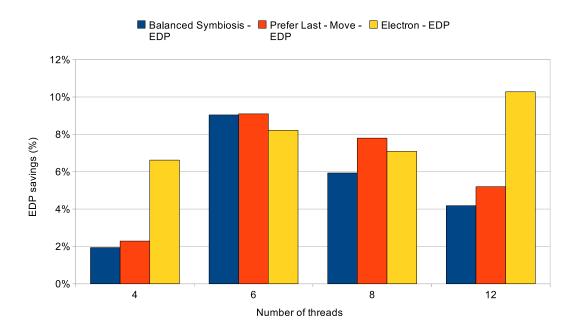

| Figure 3.4:  | Energy-delay product for sampling-based scheduling policies       | 79  |

| Figure 3.5:  | Effectiveness of the non-sampling electron policy, compared to    |     |

|              | two sampling policies                                             | 81  |

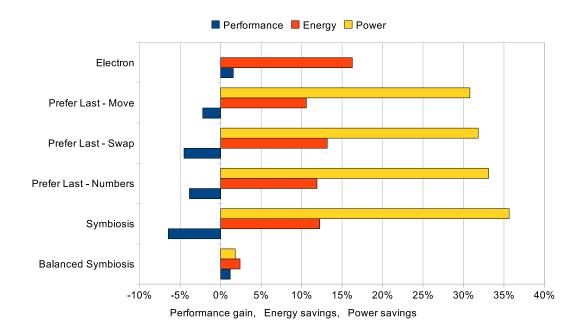

| Figure 3.6:  | The impact on performance, energy, and power of various thread    |     |

|              | scheduling policies                                               | 82  |

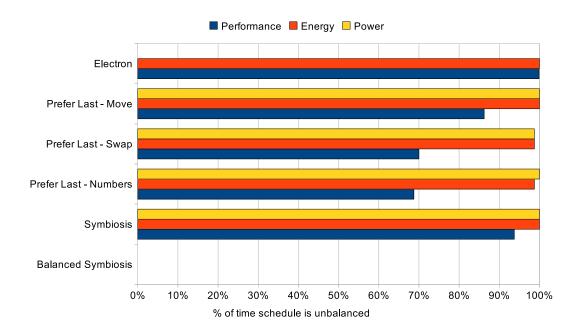

| Figure 3.7:  | Extent of imbalance in the dynamic schedules targeting the var-   |     |

|              | ious metrics                                                      | 83  |

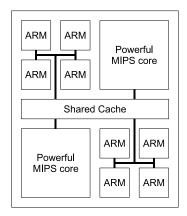

| Figure 4.1:  | Heterogeneous-ISA CMP block diagram                               | 102 |

| Figure 4.2:  | The organization of a non-leaf stack frame in a migration-capable |     |

| Ç            |                                                                   | 107 |

| Figure 4.3:  | Cost of state transformation for migration from ARM core to       |     |

| -            | <u> </u>                                                          | 131 |

| Figure 4.4:  | Cost of state transformation for migration from MIPS core to      |     |

|              | ARM core                                                          | 131 |

| Figure 4.5: | Performance vs. migration frequency             | 132 |

|-------------|-------------------------------------------------|-----|

| Figure 4.6: | Expected time to next call, among ARM binaries  | 134 |

| Figure 4.7: | Expected time to next call, among MIPS binaries | 135 |

## LIST OF TABLES

| Table 2.1: | Architecture Detail                        | 43  |

|------------|--------------------------------------------|-----|

| Table 3.1: | Architecture Detail                        | 65  |

| Table 3.2: | Benchmarks                                 | 74  |

| Table 3.3: | Workloads                                  | 74  |

| Table 4.1: | Architecture detail for ARM and MIPS cores | 128 |

#### **ACKNOWLEDGEMENTS**

First, and foremost, I would like to thank my Lord and Savior, Jesus Christ. "Whatever you do, do your work heartily, as for the Lord rather than for men" [Colossians 3:23, NASB]. This dissertation, therefore, is dedicated to the Lord. Indeed, it is only possible because of Him; the Apostle Paul writes, "I can do all things through Him who strengthens me" [Philippians 4:13, NASB]. I know I can do nothing apart from God's grace.

To my amazing wife, Lisa. You have been a pillar of support through most of my time in grad school, a constant source of encouragement, comfort, and love. Thank you for putting up with the long days (and nights) of work and for keeping me sane.

To my family, especially my mom and dad. Thank you for all your words of encouragement over the years—whether I succeed or fail, I know you'll love me just the same. Throughout my time in grad school, it was comforting to know that I had a place to go if I needed it. To my in-laws, Gil and Patty, thank you for all of your support and encouragement—you have become like second parents to me.

I would like to thank my advisor, Dean Tullsen, for excellent guidance and great patience. Thank you for all your help in editing papers, helping set a research direction, and offering great ideas when I was stumped. Without your help, this dissertation would not be possible.

Thanks to all of the people at UCSD that I've had the privilege of working with. Rakesh, in my early years of grad school, you set a great example of hard work and dedication; it was something I aspired to throughout my graduate career. Jeff, I cannot thank you enough for all of your help over the years. Not only were you a great guy to go to for technical advice, but our chats were much-appreciated times of refreshment amid the long hours of work. To all my other lab mates, Leo, M.D., Vasileios, Hung-Wei, Rick, Subhra, and Jack, thank you for all of the great feedback that helped make this dissertation possible. I'll always look back with fondness on my time with you at UCSD.

Chapter 2 contains material from "Runtime Parallelization of Legacy Code on a Transactional Memory System", by Matthew DeVuyst, Dean M. Tullsen, and Seon Wook Kim, which appears in Proceedings of the 6th International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC). The dissertation author was the primary investigator and author of this paper. The material in Chapter 2 is copyright ©2007 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

Chapter 3 of this dissertation contains material from "Exploiting Unbalanced Thread Scheduling for Energy and Performance on a CMP of SMT Processors", by Matthew DeVuyst, Rakesh Kumar, and Dean M. Tullsen, which appears in *Proceedings of the IEEE International Parallel and Distributed Processing Symposium 2006 (IPDPS)*. The dissertation author was the primary investigator and author of this paper. The material in Chapter 3 is copyright ©2006 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

#### VITA AND PUBLICATIONS

2000-2002 Computer Technician

Point Loma Nazarene University, IT Dept.

2001-2003 Internship

Central Intelligence Agency

2003 Internship

TrellisWare Technologies

2003 Bachelor of Arts in Computer Science

Point Loma Nazarene University

2003-2010 Teaching Assistant

University of California, San Diego

2004 Internship

Teradata/NCR

2004-2009 Research Assistant

University of California, San Diego

2006 Master of Science in Computer Science

University of California, San Diego

2011 Doctor of Philosophy in Computer Science

(Computer Engineering)

University of California, San Diego

#### **PUBLICATIONS**

"Exploiting Unbalanced Thread Scheduling for Energy and Performance on a CMP of SMT Processors" Matthew DeVuyst, Rakesh Kumar, Dean M. Tullsen. Proceedings of the IEEE International Parallel and Distributed Processing Symposium 2006 (IPDPS), April, 2006.

"Runtime Parallelization of Legacy Code on a Transactional Memory System" Matthew DeVuyst, Dean M. Tullsen, Seon Wook Kim. *Proceedings of the 6th International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC)*, January 2011.

#### ABSTRACT OF THE DISSERTATION

## Efficient Use of Execution Resources in Multicore Processor Architectures

by

#### Matthew David DeVuyst

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California, San Diego, 2011

Professor Dean Tullsen, Chair

As the microprocessor industry embraces multicore architectures, inherently parallel applications benefit directly as they easily transform into sets of homogeneous parallel threads. However, many applications do not fit this model. These applications include legacy binaries compiled for a single thread of execution and inherently serial applications. The inability of these two kinds of applications to exploit multicore architectures has created a crisis for the microprocessor industry: customers have come to expect significant performance improvements in all of their application every processor generation, but recent multicore architectures have failed to meet those expectations for many applications. This dissertation explores ways in which these applications can run efficiently on multicore platforms.

The performance of legacy binaries compiled for a single thread of execution can be improved through automatic parallelization. We introduce a new technique to automatically parallelize binaries as they are executing. The parallelization technique leverages the benefits of hardware transactional memory, a synchronization mechanism enabling optimistic concurrency. Our technique exploits this to parallelize code that a traditional parallelizing compiler would be unable to transform due to potential memory aliasing.

Applications with fundamentally serial code can benefit from core customization. The more heterogeneous the cores are, the more likely that a given application will find a core on which it runs efficiently. We investigate two forms of heterogeneity: that created on homogeneous hardware by unbalanced resource assignment, and heterogeneity created by hardware asymmetry. We first consider a homogeneous multicore system composed of multithreading cores. Often the best schedules on such a system are unbalanced. We propose a set of novel scheduling algorithms that consider unbalanced schedules to find good application-to-core assignments. We consider objective functions of both performance and energy. We also explore how applications can benefit from diverse ISAs by considering heterogeneous-ISA multicore systems. We propose a new technique to rapidly migrate a thread among cores of different ISAs, allowing applications to take advantage of hardware heterogeneity for performance gain or energy savings.

# Chapter 1

# Introduction

The last few years have seen a dramatic shift in the microarchitecture industry: from single-core to multicore architectures. Limitations on the power density of integrated circuits have forced a change in the paradigm of processor design. No longer do we look to instruction-level parallelism (ILP) as the primary source of increased performance potential. Instead, thread-level parallelism (TLP) has become the primary vehicle for better performance. Increasing transistor counts are being put to use to exploit thread-level parallelism, forcing computer engineers to rethink how to make the best use of the additional core resources.

Inherently parallel applications benefit directly from multicore architectures, as they easily transform into sets of homogeneous parallel threads. However, many applications cannot directly benefit from multicore architectures. These applications fall into two categories:

- 1. Legacy binaries compiled for a single thread of execution.

- 2. Inherently serial applications.

The former may include some inherent parallelism, but it is hidden from the hardware due to how the application was compiled. The latter simply lacks the threadlevel parallelism necessary to directly take advantage of multiple cores.

This has led to a crisis in the microprocessor industry, as customers have come to expect that all of their programs will perform significantly better every processor generation. Before the multicore era, performance gains for all applications were possible thanks to shrinking feature size and architectures that could increasingly exploit ILP (with superscalar pipelines and aggressive out-of-order engines). Now that architects have reached the limits of ILP exploitation and are using extra transistors to take advantage of TLP, applications not compiled for parallel execution or lacking TLP are falling behind. This dissertation explores ways in which these kinds of applications can be made to run efficiently on multicore platforms.

To improve the performance of legacy binaries that possess some inherent TLP but have been compiled for a single thread of execution, we automatically parallelize them at runtime. This is made difficult by the fact that the inherent parallelism is obfuscated during original compilation. Proving that memory accesses are thread-safe (i.e., are not aliased by potential parallel threads) is difficult (or impossible in some cases) for a traditional parallelizing compiler with source code access, but it is even more difficult when only the machine code is visible. The key to enabling parallelization in spite of this uncertainty is the use of hardware transactional memory (TM). Transactional memory is a promising synchronization mechanism enabling optimistic concurrency. It allows our dynamic recompiler to parallelize code that a traditional parallelizing compiler would be unable to parallelize due to potential memory aliasing.

Many applications (legacy or not) lack inherent TLP, making parallelization impossible. For these applications, we can improve their efficiency on multicore systems by taking advantage of heterogeneity. Traditional parallel applications are broken into sets of homogeneous parallel threads that easily map to homogeneous multicore systems. But the differing (heterogeneous) characteristics of single-threaded applications call for *heterogeneous* multicore systems to execute efficiently. The more heterogeneity, the more likely each application will find the right core to execute on—whether it be, for example, a powerful but under-utilized core for a CPU-intensive application, a small low-power core for a lightweight application, or a core with support for special instructions for a domain-specific application.

In this dissertation we explore how to leverage two different kinds of heterogeneity:

- 1. heterogeneity created by unbalanced load on homogeneous cores,

- 2. heterogeneity created by hardware asymmetry—a diverse set of different core types with multiple ISAs.

We first consider a homogeneous multicore system composed of multithreading (SMT) cores. This increasingly common architecture presents a difficult challenge because resource sharing, and therefore thread interaction, occurs in two dimensions. Applications running on different cores share relatively few resources; applications running simultaneously in different hardware contexts on the same core share many resources. Some combinations of applications share resources well, while others create heavy resource contention. Finding good schedules on these architectures proves to be a difficult task because the number of possible schedules to consider is large and positive thread interaction is difficult to predict. We observe that often the best schedules, especially when both performance and energy are primary concerns, are unbalanced ones—it is most efficient when some cores are more utilized than others.

Next, we consider a heterogeneous-ISA chip multiprocessors (CMP). The diversity of not only core types, but also ISAs creates a wide range of custom cores—each designed to efficiently execute a particular kind of application. But for programs to be able to take advantage of this heterogeneity, they must be free to move among cores. Migration can either be used to free up needed resources when new programs enter the system or to exploit different phase behavior within an application. We propose a new technique to quickly migrate programs among heterogeneous cores with a minimal sacrifice of runtime performance.

In the next section, we introduce our runtime parallelization technique for legacy binaries. In the following section we introduce our studies of two heterogeneous systems that use multiple cores to efficiently execute inherently serial applications.

## 1.1 Parallelizing Single-Threaded Code

Before the multicore era of general-purpose processor design, single-threaded legacy binaries saw significant performance improvements with every processor generation. Because multicore microarchitectures exploit TLP, not ILP, legacy binaries no longer experience significant performance gains.

Parallelization of single-threaded binaries, particularly at runtime, when more information is known about the behavior of the program, has been shown to be effective, to various degrees [CO03, OYOB02, THA<sup>+</sup>99, YF08, VRR<sup>+</sup>07, ZMLM08, vPCC07]. Many of these proposals show only modest performance gains, or show high performance gains but make assumptions about extensive new hardware support. From the prior research it is clear that some hardware support is necessary to achieve good speedup from parallelized legacy programs; but architects are reluctant to add expensive special-purpose hardware. We explore the re-use of hardware intended for a different purpose—hardware that is more likely to be implemented by processor makers: hardware transactional memory [HM93].

Transactional memory (TM) is a promising lock-free synchronization mechanism that has been the center of active research in the last few years with the explosion of multicore architectures. Transactional memory gives programmers and compilers powerful shared-memory synchronization primitives. Instructions are grouped into transactions that are guaranteed to commit atomically. TM provides optimistic concurrency: transactions are allowed to execute concurrently and the hardware monitors violations among memory operations contained in the transactions. If a violation is detected, the affected transaction is rolled back and restarted. Thus serialization is only imposed on parallel code if true memory aliasing is present; when it is not present (whether or not that can be guaranteed a priori), serialization is not enforced.

In this dissertation, we introduce a new runtime parallelization technique leveraging the optimistic concurrency of TM to automatically parallelize singlethreaded legacy programs. This work addresses a number of challenges posed by this type of parallelization and quantifies the trade-offs of some of the solutions, such as how to select good loops for parallelization, how to partition the iteration space among parallel threads, how to handle loop-carried dependencies, and how to transition from serial to parallel execution and back. The simulated implementation of runtime parallelization shows a speedup of 1.36 for the NAS benchmarks and a 1.34 speedup for the SPEC 2000 CPU floating-point benchmarks when using two cores for parallel execution.

## 1.2 Managing Heterogeneity

## 1.2.1 Scheduling in a CMP of SMT Cores

Applications that cannot be parallelized because they lack inherent TLP may still be able to benefit from multicore architectures, even homogeneous architectures, if they can take advantage of heterogeneity arising from unbalanced schedules to find the best core to execute on.

Before multicore architectures were common, scheduling on a processor that exposes only one hardware context was more about fairness (or responsiveness) than about efficiency, because there is almost no interaction among threads. Scheduling on a processor that exposes two or more hardware contexts of the same type (either multiple cores or multiple SMT contexts) creates a new challenge scheduling for efficiency—because the interactions of threads executing concurrently determines performance and power usage. Previous work has shown that the coscheduling of threads on an SMT processor greatly impacts performance [ST00]. This is due to the high degree of resource sharing among SMT contexts. The importance of good coschedules is somewhat diminished in a multicore processor because resource sharing is usually limited to the last-level cache (and perhaps one other level of shared cache). In architectures that combine SMT and multicore design, finding good schedules becomes more complicated, as there are two degrees of resource sharing among contexts. Not only is it necessary to find good schedules to maximize performance, but recently, energy has also become a first-class metric. Often this results in the best schedules being unbalanced ones, creating a type of heterogeneity. Deciding which core to run an application on becomes critical.

In this dissertation we propose a new thread scheduling technique for this

increasingly popular architecture—chip multiprocessors with simultaneous multithreading cores. We describe optimizations for both performance and energy efficiency. The key contribution of our scheduler is its consideration of unbalanced schedules. Conventional multiprocessor scheduling, applied to this architecture, will attempt to balance the thread load across cores. We demonstrate that this approach eliminates one of the biggest advantages of this architecture—the ability to use unbalanced schedules to allocate the right amount of execution resources to each thread. However, to accommodate unbalanced schedules, the search space of all schedules (both balanced and unbalanced) is much greater than that of the balanced schedules alone. This dissertation proposes and evaluates scheduling mechanisms that allow the system to identify and migrate toward good thread schedules, whether the best schedules are balanced or unbalanced.

## 1.2.2 Migrating Execution on Heterogeneous CMPs

In Chapter 4 we investigate how a different kind of heterogeneity—hardware heterogeneity—can benefit serial applications on multicore architectures. Research has shown that architectures with multiple cores of different types can achieve greater performance and power efficiency [KTJR05, HM08]. In the past, when processor design centered around a single core, architects sought to make cores as general as possible, capable of performing well on different types of code. The abundance of cores in new architectures affords architects the ability to specialize some of those cores to run certain classes of code more efficiently. Heterogeneity is a powerful tool to balance generality and specialization.

Another factor that drives heterogeneous design is energy efficiency. Architects designing general-purpose processors must strike a balance between performance and energy efficiency. Often the two goals are in conflict. However, in a heterogeneous chip multiprocessor, different cores can be selected all along the power/performance curve—some cores designed for high performance, others suited to low-power operation.

Designing software to run on heterogeneous CMPs with cores sharing a common ISA is simpler than for heterogeneous-ISA CMPs. Heterogeneous-ISA

CMPs enable a new dimension of heterogeneity. Just as architectures are designed with different goals, so are ISAs. Some ISAs as designed to support a wide variety of instruction types, including sets of special-purpose instructions. Some ISAs are engineered to facilitate small, simple architectures. Also, assumptions about cache and memory latencies play a big role in ISA design. Multicore architectures that are able to exploit these differences will have a power/performance advantage over homogeneous-ISA architectures.

Efficient thread scheduling on heterogeneous-ISA CMPs is difficult because good thread scheduling needs to be dynamic. Not being able to reschedule running threads on different core types limits how effective the system is in exploiting hardware diversity. For example, when the energy level that is available to the system changes, the system should be able to adapt, migrating execution to low-power cores. Or when program behavior changes, execution should migrate to a core that will be able to handle the workload most efficiently. Or when a new high-priority process enters the run queue, the most powerful core(s) should be made available to it. But for a scheduler on a heterogeneous CMP to adapt to such changes, it needs to be able to migrate execution across core types.

This dissertation proposes a novel execution migration technique for CMPs with heterogeneous ISAs. The critical feature of these architectures, that we take advantage of, is their shared memory. We leverage this advantage by keeping the memory image of a migratable process in a state that is almost completely ISA-neutral. This allows migration to be fast, as very little state has to be transformed. We rely heavily on the compiler to both enforce memory image consistency and to extract the information necessary to transform the remaining architecture-specific state. We achieve fast migration (308 microseconds on average) with a minimal sacrifice of runtime performance (performance without migrations)—2.3% on average.

The rest of this dissertation is organized as follows. Chapter 2 presents our solution to getting improved performance from legacy single-threaded code on multicore architectures. Chapters 3 and 4 describe how programs that cannot be parallelized can still thrive on multicore architectures by finding and exploiting

heterogeneity. Chapter 3 focuses how to make use of heterogeneity stemming from unbalanced schedules, and Chapter 4 focuses on a critical first step toward exploiting hardware heterogeneity: migration on heterogeneous-ISA systems. Chapter 5 concludes.

# Chapter 2

# Runtime Parallelization

## 2.1 Introduction

General-purpose microprocessor design has undergone a major shift in the last few years as the performance and thermal characteristics of large out-of-order microprocessors failed to scale. The multicore era is upon us, and as feature sizes continue to shrink, dies are divided up into ever more processing cores. The increase in hardware parallelism has outpaced the software industry; there is a large body of applications written for or compiled for a single thread of execution, and these applications do not take advantage of the extra parallelism being offered by modern microprocessors.

Some single-threaded legacy applications are rewritten to take advantage of the additional hardware parallelism, but this is often a difficult and expensive undertaking. Some legacy applications are recompiled with a parallelizing compiler that attempts to extract as much parallelism as possible. But this is not always possible for a number of reasons. It is not possible if the software vendor only distributed the application in binary form and they have gone out of business, no longer support the application, are unwilling to recompile the application because they are worried that it may introduce or uncover bugs, or rely extensively on a compiler that does not support parallelization. Sometimes the user is unwilling to pay more for an updated version.

The software industry recognizes the growing need to produce parallel mul-

tithreaded code to take advantage of the offered hardware parallelism to make the performance of their software products competitive. They are becoming increasingly interested in ways of making the writing of correct parallel code less difficult and error-prone.

What makes parallel programming so difficult to implement correctly is the need to control access to variables in shared memory. Most of the traditional paradigms for controlling access to shared memory involve using locks to control access to regions of code that may operate on shared memory. Often times it is not known by either the programmer or compiler if, at any given moment during the running of a program, multiple threads will attempt to operate on the same memory at the same time. To protect against the possibility of such a conflict, locks are used to conservatively guard access to shared memory.

Parallelization at runtime is even harder because high-level program information is lost. Because a static compiler has access to a higher-level representation of the program, it is in a better position to reason about potential memory aliasing. Runtime parallelization operates on machine code, where it is much more difficult to determine where potential aliasing may occur. Consequently, nearly all memory references must be treated as potentially aliased and guarded with synchronization primitives, like locks, which force serialization.

Transactional memory (TM) is a promising improvement over lock-based synchronization. It optimistically grants access to shared memory, forcing serialization only when a real conflict is detected [HM93, AAK+05, CNV+06, RHL05, YBM+07, MBM+06a, MBM+06b, HWC+04, ST95, HF03, HLMS03]. TM is an area of active research and has been gaining increasing acceptance in industry [DLMN09]. For example, the Rock processor from Sun Microsystems supports hardware transactional memory. We believe that in the near future we will see more microprocessor vendors including hardware support for transactional memory.

Leveraging hardware support for TM, we propose a new technique to automatically (without any user intervention) extract thread-level parallelism from legacy single-threaded binaries with minimal architectural change. We find that

transactional memory enables the parallel execution of many loops that are serialized by traditional synchronization. Our technique uses a dynamic optimization framework: frequently executed loops are identified by hardware at runtime, a dynamic recompiler is spawned in a free hardware context to transform the key loops into parallel code, and the recompiled parallel loops are patched in to the running program. The dynamic recompiler analyzes the loop (at the machine code level, not at the source code level) and, if possible, transforms it into a loop that can be executed in parallel. When the parallelized loop executes, parallel threads are forked onto free hardware contexts.

The primary contribution of this chapter is to show that the reduced overhead and optimistic concurrency of hardware transactional memory enables the effective parallelism of a number of legacy codes, despite the existence of unknown and possibly unknowable memory aliasing.

This chapter describes our parallelization technique and quantifies its effectiveness across a number of benchmarks. In Section 2.2 we give an overview of the related work. Section 2.3 describes our baseline processor architecture, including transactional memory and dynamic optimization implementations. An explanation of our parallelization technique is found in Section 2.4, and a description of the parallel code generation is found in Section 2.5. In Section 2.6 we describe our experimental methodology, and in Section 2.7 we present our results. Section 2.8 concludes.

## 2.2 Related Work

## 2.2.1 Transactional Memory

Our parallelization technique relies on data speculation to avoid frequent synchronization. This requires a mechanism to prevent erroneous execution that arises from unanticipated memory aliasing between loop iterations. We achieve this through the use of transactional memory.

Transactional memory was first proposed by Herlihy and Moss as a hardware implementation of lock-free concurrent synchronization [HM93]. Their model provides the programmer with guarantees about the memory accesses of instructions contained in transactions. One guarantee is that writes to memory within a transaction are not visible to other transactions until transaction commit (at which time all the writes in the transaction are atomically released). Another guarantee is that memory aliasing among transactions (e.g., a write in one transaction to the same address as a read in a concurrently-executing transaction) is detected and appropriate recovery actions taken (e.g., a transaction's state will be discarded and it will be restarted).

From this simple model, a number of significant improvements have been made, including more efficient ways of handling increased buffered state [AAK+05, CNV+06], virtualization [RHL05, YBM+07], improved conflict detection [MBM+06a], sub-cache line granularity [YBM+07], nested transactions [MBM+06b, YBM+07], faster transaction commits [MBM+06a], ordered transactions [HWC+04], and software-based transactional memory [ST95, HF03, HLMS03].

### Handling Increased Buffered State

Ananian et al. [AAK+05] assert that a TM implementation should not place restrictions on transaction size. They propose two related hardware TM implementations: *Unbounded Transactional Memory* (UTM) and *Large Transactional Memory* (LTM). LTM is a simplification of UTM that does not require modifications to the memory interface. They use an in-memory data structure, instead of the cache architecture, to track transactional state, allowing transactions to grow as large as system memory.

Chuang et al. [CNV<sup>+</sup>06] also propose a hardware TM implementation that does not place restrictions on transaction size. Their proposal, *Page-based Transactional Memory*, integrates transaction bookkeeping with the virtual memory system.

#### Virtualization

Some researchers have proposed ways to virtualize TM so that the programmer is shielded from platform-specific resource limitations. Rajwar et al. [RHL05] introduce *Virtual Transactional Memory*, a hardware-software hybrid TM implementation that uses virtualization techniques to deal with cache overflows and clock interrupts.

#### **Fast Transaction Commits**

In many TM implementations old memory state is kept in place until transaction commit, while transaction state is buffered. In order to make transactions commit faster, Moore et al. [MBM $^+$ 06a] propose updating memory immediately with transaction state and writing the old versions of data to a log in case of transaction abortion. Their implementation, LogTM, also extends a directory-based cache coherence protocol to achieve fast conflict detection.

### Sub-cache Line Granularity

LogTM Signature Edition [YBM+07] extends LogTM by adding signatures (hashes of read and write sets) to facilitate conflict detection. This decouples conflict detection from L1 cache tags and arrays. Because neither version management nor conflict detection are tied to the cache architecture, their hardware TM implementation can operate at granularities finer than cache lines. Our parallelization technique benefits significantly from this fine granularity (as we show in Section 2.7.2).

#### **Nested Transactions**

Many TM models support closed nested transactions, where all nested transactions are flattened into the outermost transaction. This preserves correctness when software composition is used (e.g., when module A opens a transaction and calls module B, which may open addition transactions), but may degrade performance. Moravan et al. [MBM+06b] propose support for open nested transactions, where an abort in an inner transaction does not cause the outer transaction to abort. They also allow escapes in the middle of a transaction in order to suspend transactional execution while non-transactional code (e.g., OS code) is invoked.

#### **Ordered Transactions**

In many TM implementations, transactions commit in an arbitrary order—whichever transaction completes first commits first. Recognizing that most parallel applications have places where one transaction must commit before another, Hammond et al. [HWC+04] introduce a hardware TM implementation, TCC, that supports ordered transactions. If the programmer wishes, he or she may specify the order of transactions in addition to the boundaries of each transaction. Hardware-managed phase numbers are associated with transactions; a transaction in a newer phase will stall if there are uncommitted transactions in older phases. Ordered transactions have also been proposed by Ceze et al. [CTTC06] and Porter et al. [PCT09].

#### **Software Transactional Memory**

First proposed by Shavit and Touitou [ST95], Software Transactional Memory (STM) is an alternative TM implementation strategy based completely in software. Performance is not as good without hardware support, but the solution is more portable and can be used on any machine that supports load-linked/store-conditional operations. Harris and Fraser [HF03] and Herlihy et al. [HLMS03] extend STM to object-oriented languages and propose implementations of dynamic STM—where transactions and transactional objects can be created dynamically.

#### Our TM Model

We assume hardware transactional memory, but otherwise, we are relatively insensitive to which implementation. We only require that the TM implementation support ordered transactions. Ordered transactions are only allowed to commit in a predefined order.

Advances in transactional memory should improve the performance of our parallelization technique. For example, faster transaction commits will lower the transactional overhead of our parallelization and improve performance; and support for the efficient buffering of more transactional state will allow for the parallelization of larger loops and more iterations per transaction.

## 2.2.2 Dynamic Optimization

A dynamic optimization framework supports our parallelization technique by efficiently discovering loops that are good candidates for parallelization, calling our dynamic recompiler to parallelize the candidate loops, and patching the parallel versions of loops into running code. Research on dynamic optimization is advancing rapidly. What follows is a summary of important advances.

Bala et al. [BDB00] In 2000 the first software-based dynamic optimization system was introduced. This framework, called *Dynamo*, is a software-only optimizer that is similar to, but also fundamentally different from Just-in-time (JIT) compilation. Like JIT compilers, Dynamo optimizes code as it is running; but unlike JIT, it optimizes native binaries, not bytecode. Dynamo operates by alternating between interpretation and direct execution—frequently executed portions of code (so-called *hot* traces) are optimized and placed in a code cache for direct execution (everything else is interpreted).

Chen et al. [CLG00] The dynamic optimization system *Mojo* is very similar to Dynamo, but adds support for exception handling and multithreaded code. It also distinguishes itself by supporting optimization for a CISC ISA—x86. As in Dynamo, in Mojo the optimization is typically performed in the same thread (and on the same hardware context) as the main execution.

Patel and Lumetta [PL01] They propose a hardware-based dynamic optimization framework, called *rePLay*, that enables aggressive optimizations by stringing together basic blocks in a single control flow called a *frame*. Frames are built speculatively and a hardware-based recovery mechanism reverts program state if an early exit is taken.

Bruening et al. [BGA03] They provide an interface to the software-based dynamic optimizer *DynamoRIO* (an IA-32 version of Dynamo) that makes it easy to create new optimizations. Their framework makes writing optimization modules for a dynamic compiler as easy as it is to write optimization passes for a static

compiler. The abstraction provided by their framework overcomes the difficulties (e.g., memory management) of interleaving the execution of the optimizer with the execution of the program being optimized.

Lu et al. [LCYcH04] In the ADORE dynamic optimization system, the execution of the optimizer is segregated to an OS-level thread. The framework uses the hardware performance counters in the Itanium 2 processor to detect hot regions of code; analysis and optimization is performed in software in the optimization thread. This hybrid hardware-software approach combines the best of both worlds. However, context switches to the optimization thread for profiling hamper performance.

## Our Dynamic Optimization Framework

The dynamic optimization framework that we employ is a simplified version of the *Trident* framework by Zhang et al. [ZCT05, ZCT06, ZTC07], which is similar to ADORE. In Trident all of the profiling is handled in hardware and the optimization thread is executed on a separate hardware context, completely eliminating interference from the optimization thread on the main execution. Trident supports a broad selection of optimizations, many of which are orthogonal and complementary to our parallelization optimization.

Hot traces (frequently executed regions of code) are detected by simple hardware performance monitors; finding hot traces in hardware incurs much less of a performance penalty on the monitored process. Since the loop analysis and parallelizing recompilation is much more complex, it is best done in software. To accomplish this, when a hot trace is detected, the processor will spawn a new thread in a free hardware context to run a software dynamic recompiler to analyze and optimize the code. In our case, the hot code regions are loops and the optimization performed is parallelization. As Zhang et al. point out, doing the profiling in hardware and the optimization in a separate thread in a separate hardware context results in very minimal performance impact on the target process.

## 2.2.3 Dynamic Loop Parallelization

Other researchers have proposed the use of dynamic optimization to aid in runtime parallelization of loops.

Jrpm [CO03] parallelizes Java bytecode at runtime in the Java Virtual Machine. They also exploit optimistic concurrency in their parallelization; but unlike our work, which uses transactional memory to achieve this, they use thread-level speculation (TLS). Also, in their work, programmer transformations are necessary to expose loop-level parallelism; our technique is fully automatic and does not require any programmer or user intervention. The goal of our work is to improve the performance of legacy binaries, and we target compiled machine code (not Java bytecode); we address code that does not have the advantages of running in a controlled virtual machine environment, like the Java Virtual Machine.

Ootsu et al. [OYOB02] also propose a runtime parallelization technique for binaries using a dynamic optimization framework. Their work builds on the parallelization technique of Tsai et al. [THA+99] by adding binary translation at runtime, instead of transformation at compile-time, to perform the parallelization. Unlike our work or Jrpm, they do not explore the use of any optimistic concurrency mechanisms to ensure correctness with regard to concurrent memory access. Instead they rely on an explicit serialization of all the instructions that compute all the store addresses in the loop body. To ensure correctness, this code is collected in a serially-executing phase they call TSAG (Target Store Address Generation), that is executed at every loop iteration in every parallel thread (in original program order). Then, as the main body of the loop is executed (in what they call the Computation phase), a special hardware structure called the Memory Buffer coordinates memory dependencies among parallel threads.

Yardimci and Franz [YF08] put forth a dynamic parallelization and vectorization technique for single-threaded binaries. Their technique involves only control speculation, not data speculation. Therefore, they introduce a complex control-flow analysis (especially to handle indirect branches); but they do not parallelize loops whose induction registers do not have deterministic fixed strides, loops that have stores in conditionally-executed code regions (i.e., in the *then* clause of an

*if-then* statement), or loops with potential cross-iteration data dependencies. Because our approach leverages transactional memory for data speculation, we find ways around all these limitations and are thus able to parallelize more loops.

Vachharajani et al. [VRR<sup>+</sup>07] add speculation to Decoupled Software Pipelining (DSWP). DSWP parallelizes a loop by partitioning the loop body into stages that are scheduled on threads and executed in a pipelined manner, communicating results via a message-passing or buffering mechanism. Speculative DSWP breaks some recurrence dependencies so that the loop body can be broken into smaller pieces to increase scalability and load balancing. Our work differs from theirs in three ways: our technique works at the machine code level, where analysis and transformation is more complicated due to compiler optimization and loss of information; we use a simpler, more common form of speculation, transactional memory—they use a complicated versioned memory system; their technique utilizes heavy inter-thread (cross-core) communication, potentially requiring hardware support for best performance.

Works by Zhong et al. [ZMLM08] and Von Praun et al. [vPCC07] leverage TM for parallelization, but rely on programmer and/or heavy compiler support; our technique requires neither.

## 2.2.4 Speculative Multithreading

Speculative multithreading [SBV95, MGT98, KT99] is an alternate approach that attempts to get parallel speedup from serial code. They do so by executing serial code in parallel and recover from misspeculation. They typically rely heavily on data value speculation and prediction, as well as some type of memory versioning. Conversely, we create more conventional parallel code (dynamically), without data prediction, and only exploit speculative execution to the extent that transactional memory already supports it.

## 2.3 Architecture

Hardware transactional memory provides several key advantages over traditional synchronization, particularly with regard to the problem of runtime parallelization. The key problem in runtime parallelization, that has made it an essentially unsolvable problem except in the most simple cases, is that in the absence of any high-level program information, nearly all loads and stores must be treated as potentially aliased—the necessarily conservative handling of these potential dependencies serializes the code. Transactional memory, by supporting optimistic concurrency, solves a whole set of problems. First, because code is only serialized when there is true aliasing, conservative placement of synchronization has no cost. Second, we can include many writes in a single transaction, minimizing synchronization overhead with no significant loss in concurrency. Because transactional semantics require no correlation between the synchronization mechanism and the data that is protected, parallelization is simply enabled, yet still catches even unanticipated dependencies.

To illustrate the power of this technique, consider the pseudo-assembly code of the loop in Figure 2.1. This code loops over an array of structures: for each structure element, a pointer field is extracted and followed, and the data at that pointer location is modified. Assume this loop is executed many times, is part of a single-threaded application (for which we do not have the source code), and is running on a modern multicore processor on which there are one or more unutilized cores.

Using hardware performance counters, a dynamic optimization framework can detect that this loop executes frequently and can transform it automatically into parallel code—with different iterations of the loop running in different threads. Without the high-level code, we cannot guarantee that parallel iterations of this loop will not attempt to modify the same data in memory. With traditional lock-based synchronization primitives, our parallelizer would transform the loop such that a lock would have to be acquired and released on every iteration of the loop. Since only one thread may hold the lock at any time, even though the loop would be parallelized across multiple threads, the frequent synchronization would force a

```

loop: sub r1, r1, 256

add r5, r1, r6

load r2, 64(r5)

load r3, 0(r2)

add r3, r4, r3

store r3 0(r2)

bne r1, 0, loop

```

Figure 2.1: Potential memory aliasing makes this loop hard to parallelize.

serialization of loop iterations. However, if the loads and stores are not frequently aliased in neighboring iterations, the serialization is unnecessary.

If the optimizer instead uses transactional memory to make the code threadsafe, then when aliasing is infrequent, unnecessary serialization does not hinder performance. Each iteration is wrapped in a transaction and the transactions execute concurrently. Thus, with minimal analysis of the code, we still get guaranteed serialization of iterations when there are dependencies, and parallel execution in the absence of dependencies.

Transactional memory constructs are frequently utilized by programmers or compilers with a high-level (source code) view of the application. At this level alias analysis is much more feasible than at the machine code level. Synchronization code need not be applied in cases where it can be proven that aliasing is not possible. But a dynamic optimizer analyzes and transforms machine code. At this level it often impossible to prove that aliasing will not occur; so very conservative synchronization code is necessary. This makes TM a more attractive synchronization primitive.

#### 2.3.1 Code Transformation Overview

We now present a high-level overview of the code transformation. Section 2.4 provides more details on this process.

Figure 2.2 shows what the transaction-wrapped transformed code from Fig-

```

fork fix

branch btx

loop:

EndTransaction

fix:

sub r1, r1, 256

btx:

BeginTransaction

sub r1, r1, 256

add r5, r1, r6

load r2, 64(r5)

load r3, 0(r2)

add r3, r4, r3

store r3 0(r2)

bne r1, 0, loop

EndAllTransactions

join:

```

**Figure 2.2**: Wrapping the loop body in a transaction allows for safe and optimistic parallelization.

ure 2.1 would look like when targeting two parallel threads. Some details (mostly for bookkeeping) have been omitted to simplify the example. The code first forks a new thread to start executing at the label fix. This is a lightweight fork—no new stack is created, only registers are copied and the program counter is set. The newly-created thread will execute the induction code to bring the loop-carried registers up-to-date in preparation to execute the second iteration of the loop: in this example 256 is subtracted from register r1. Then, a new transaction begins and the loop body is executed. Meanwhile, the original thread will branch to the label btx, open a new transaction, and execute the first iteration of the loop. When a thread completes an iteration, i, of the loop, it will close the transaction and open a new transaction to execute iteration i + 2. The ordering of the transactions will ensure that state from each iteration is committed (i.e., data is stored to memory) in original program order. When the loop is done executing, all the transactions

will be closed, the spawned threads will be terminated, and execution will resume in the original thread at the *join* label.

Having ordered transaction commits ensures that we do not commit values out of order, and also ensures that the value of the last write to each memory location in the loop is the value that is visible at loop exit.

# 2.4 Parallelization

There are several things we need in order to enable dynamic parallelization of legacy serial code. First, we need some kind of dynamic optimization framework that can (1) identify candidate loops to parallelize, (2) spawn a thread to analyze each loop and generate parallel code, and (3) patch in the new version. We also need hardware support to catch dependencies between iterations assumed to be parallel (transactional memory, in our case). We need our parallelizer to solve the problem of selecting the right granularity of parallelism. We also need to ensure that we maintain the semantics of sequential execution, particularly as viewed by the code following the parallel region—transactions accomplish this for memory, but registers must be handled in software. Our solutions for each of these issues will be presented in this section and the following one. This section focuses on the overall design of the parallelization process, including the dynamic optimization framework that orchestrates the parallelization process and the scheduling of parallel code on threads. The next section will focus on aspects of the parallel code generation itself.

# 2.4.1 Dynamic Optimization Framework

The basic unit of optimization targeted by our technique is the loop. To identify loops most effectively, we combine two techniques—a whole-program control-flow analysis that identifies loops, combined with a hardware monitor that identifies frequent branches. This provides a more accurate view of important loops than trying to identify loops based on hot-branch addresses.

When a new process is started, a loop analyzer begins in a spare hardware

context to perform a quick loop analysis of the binary code. Since this is a static analysis, it can be performed once and the results even saved to a file for all future executions. The static analysis is not required, but improves the quality of discovered loops. Because it runs in a separate context and typically requires only a few milliseconds, it neither slows the main thread nor impedes our dynamic parallelizer in any but the shortest of applications.

The loop analyzer operates as follows. First, instructions are grouped into basic blocks; the control flow among basic blocks is modeled with a directed graph. A dominator graph is built; and any edge  $i \rightarrow j$  in the control flow graph from a node i to a node j that dominates node i is the back edge of a natural loop (composed of all the basic blocks that form that cycle in the graph) [Muc97]. Loops that contain system calls or computed branches are filtered out because parallelizing such loops would be problematic. Information about each natural loop, like the address of the backward branch instruction, the branch target, the size of each loop, and the list of basic blocks that make up the loop is stored in a software buffer called the Loop Information Store (LIS) that is mapped into the address space of the target process.

As the program executes, a hardware-based profiler, like the Hot Path Profiler in [ZCT05], finds frequently executed loops, called *hot* loops. When a hot loop is identified, hardware monitors measure the average number of cycles required to execute one iteration of the loop. Once the baseline performance of the hot loop has been measured, a dynamic recompiler is spawned in a spare hardware context to attempt to parallelize the hot loop. The recompiler receives from the hardware profiler the identification of the hot loop and it finds a more detailed analysis of that loop in the LIS.

If the dynamic recompiler is able to parallelize the loop, it produces the machine code of a parallel version and inserts it into a region of memory, called the code cache, in the target process' address space. It modifies the first instruction of the serial (original) version of the loop to be a branch instruction to the parallel version of the loop. On the next instance of the loop, the parallel version will be executed.

One of the first instructions in the new version of the loop is a fast fork instruction. When this instruction is executed, a new thread is created on a spare hardware context. This is not a traditional heavy-weight fork. No new stack is created for the new thread and no registers are set, except for the program counter, which is set by adding the current PC to the offset encoded in the fork instruction. Because only the PC has to be set in the newly-created thread, the fork can be very fast.

As the parallel version of the loop executes, its performance is monitored in hardware. The average number of cycles per iteration of the parallel execution is compared to the average number of cycles per iteration of the serial execution. If the parallel version of the loop is not performing any better than the serial version, the parallel version is eventually removed, as in [ZCT05]. After all the iterations of a parallelized loop complete, parallel threads are terminated and serial execution continues on the original thread.

# 2.4.2 Partitioning the Iteration Space

Loop iterations are distributed among threads in a round-robin fashion. In our baseline implementation, this distribution is done at the granularity of individual iterations. We also experiment with distributing groups of iterations among threads, where each group is wrapped in a single transaction. The idea of partitioning the iteration space among threads as groups of iterations is commonly referred to as *tiling* and has been studied in part by [YF08]. The *tile size* is the number of consecutive loop iterations grouped together and treated as a unit of parallel work.

Large tile sizes are advantageous for three reasons. First, because multiple iterations are wrapped in a single transaction, the overhead of transaction start and commit is amortized. Second, loop induction code (code run before every tile to bring the loop-carried register state up-to-date) can be compacted. The simplest example of this is a register that is incremented by a fixed amount every iteration. Suppose we have two parallel threads and a loop that iterates 100 times, and the value in register r1 is incremented by one each iteration. With a tile size

of one, before every iteration of the loop, r1 will be incremented by one to account for the previous iteration that was executed on the other parallel thread. This will result in 99 dynamic instructions of overhead. With a tile size of 10, the value in r1 can be incremented by 10 to account for the previous 10 iterations. This will only result in nine dynamic instructions of overhead. Finally, the last advantage of large tile size is applicable in cache configurations where false sharing is possible (e.g., for line-granularity transactional memory). If a loop's memory access pattern is such that a single cache line is written across multiple iterations, then false sharing can arise, resulting in frequent transaction restarts that hurt performance. This is an issue we directly address and will discuss in more detail later in this section.