# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

### **Title**

Achieving Flexibility and Performance for Packet Forwarding and Data Center Management

### **Permalink**

https://escholarship.org/uc/item/76s772g3

### **Author**

Moon, Daekyeong

### **Publication Date**

2010

Peer reviewed|Thesis/dissertation

# Achieving Flexibility and Performance for Packet Forwarding and Data Center Management

by

Daekyeong Moon

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Scott J. Shenker, Chair Professor Ion Stoica Professor Tapan Parikh

Spring 2010

# Achieving Flexibility and Performance for Packet Forwarding and Data Center Management

Copyright © 2010

by

Daekyeong Moon

#### Abstract

Achieving Flexibility and Performance for Packet Forwarding and Data Center Management

by

Daekyeong Moon Doctor of Philosophy in Computer Science University of California, Berkeley

Professor Scott J. Shenker, Chair

Although today's networking equipment has achieved high performance and low cost by embedding forwarding logic in hardware, this has come at the price of severely reduced flexibility. In this dissertation, we address the problem of achieving both flexibility and performance in two networking domains: packet forwarding and data center networking. In packet forwarding, we present *Software Defined Forwarding*, a hybrid design that attempts to combine the high speed and low cost of hardware with the superior flexibility of software. Within the data center context, we propose *Ripcord*, a platform for data center routing and management. Through simulation, prototype implementation and testbed experiments, we demonstrate that these solutions achieve both flexibility and high performance in their respective contexts.

Professor Scott J. Shenker Dissertation Committee Chair

To my family and Hayan.

# Contents

| Li       | st of | Figure  | es                                               | v  |

|----------|-------|---------|--------------------------------------------------|----|

| Li       | st of | Tables  | 3                                                | v  |

| 1        | Intr  | oducti  | on                                               | 1  |

|          | 1.1   | Proble  | em statement                                     | 2  |

|          | 1.2   | Contri  | bution                                           | 2  |

|          |       | 1.2.1   | Software Defined Forwarding                      | 2  |

|          |       | 1.2.2   | Ripcord: Data Center Routing/Management Platform | 3  |

|          | 1.3   | Dissert | tation Organization                              | 4  |

| <b>2</b> | Bac   | kgrour  | nd                                               | 5  |

|          | 2.1   | The St  | tatus Quo in Packet Forwarding                   | 5  |

|          | 2.2   | Data (  | Center Networking Aspects                        | 7  |

|          | 2.3   |         | ary                                              | 8  |

| 3        | Soft  | ware I  | Defined Forwarding                               | 9  |

|          | 3.1   | Goals,  | Limitations, and Applicability                   | Ö  |

|          |       | 3.1.1   | Goals                                            | Ö  |

|          |       | 3.1.2   | Limitations                                      | 10 |

|          |       | 3.1.3   | Applicability                                    | 10 |

|          | 3.2   | Overvi  | iew                                              | 11 |

|          |       | 3.2.1   | System Functionality and Components              | 11 |

|          |       | 3.2.2   | Forwarding Steps                                 | 13 |

|          |       | 3.2.3   | Sound Familiar?                                  | 14 |

|          | 3.3   | Systen  | n Design                                         | 15 |

|          |       | 3.3.1   | API                                              | 15 |

|          |       | 3.3.2   | System Software                                  | 19 |

|          |       | 3.3.3   | Hardware                                         | 20 |

|          | 3.4   | Impler  | mentation                                        | 22 |

|          |       | 3.4.1   | NetFPGA prototype                                | 22 |

|          |       | 3 1 2   | Microbenchmarks                                  | 2/ |

|   | 3.5 | Summ    | nary                                              |

|---|-----|---------|---------------------------------------------------|

| 4 | SDI | F Use   | Cases 2                                           |

|   | 4.1 | Accele  | erating Existing Software Routers                 |

|   | 4.2 |         | alization                                         |

|   | 4.3 |         | menting Forwarding Algorithms                     |

|   |     | 4.3.1   | L2 Learning Switch                                |

|   |     | 4.3.2   | IPv4 and IPv6 Forwarding                          |

|   |     | 4.3.3   | <u> </u>                                          |

|   |     | 4.3.4   |                                                   |

|   | 4.4 |         | nary                                              |

| 5 | SDI | F Perfe | ormance Study 3                                   |

| • | 5.1 |         | nption                                            |

|   | 5.2 |         | urning                                            |

|   | 5.3 |         | forwarding                                        |

|   | 5.4 |         | mance under stressful conditions                  |

|   | 5.5 |         | nary                                              |

| 6 | Rin | cord:   | Platform for Data Center Routing and Management 4 |

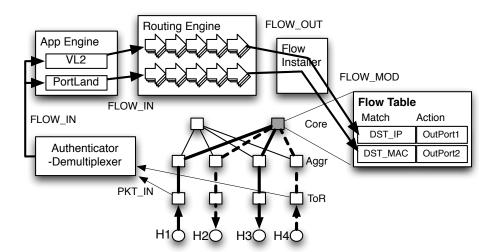

| U | 6.1 |         | riew                                              |

|   | 0.1 | 6.1.1   | Design Requirements                               |

|   |     | 6.1.2   | Key Criteria for Data Center Networking           |

|   |     | 6.1.3   | Ripcord's Design Principles                       |

|   |     | 6.1.4   | Prototype                                         |

|   | 6.2 |         | n                                                 |

|   | 0.2 | 6.2.1   | Example Walkthrough                               |

|   |     | 6.2.1   | Components                                        |

|   | 6.3 | -       | mentation                                         |

|   | 0.5 | 6.3.1   | Configuration & Policy Database                   |

|   |     | 6.3.2   | Topology Engine                                   |

|   |     |         | Authenticator-Demultiplexer                       |

|   |     | 6.3.4   | App Engine and Management Apps                    |

|   |     | 6.3.5   | Routing Engine and Per-tenant Routing Pipeline    |

|   |     | 6.3.6   | Monitoring Implementation                         |

|   |     | 6.3.7   | Flow Installer                                    |

|   |     | 6.3.8   | Virtual-to-Physical Mapping                       |

|   | 6.4 |         | studies                                           |

|   | 0.4 | 6.4.1   | Proactive L2 routing                              |

|   |     | 6.4.1   | VL2                                               |

|   |     | 6.4.2   | PortLand                                          |

|   |     | 6.4.3   | Additional Capabilities 5                         |

|   |     | 1144    | AUGUSONAL VADADIIISES                             |

| •  |  |

|----|--|

| 1V |  |

|    | 6.5   | Evaluation                                      |

|----|-------|-------------------------------------------------|

|    |       | 6.5.1 Software testbed                          |

|    |       | 6.5.2 Hardware testbed                          |

|    |       | 6.5.3 Experiments on Software Testbed           |

|    |       | 6.5.4 Experiment on Hardware Testbed            |

|    |       | 6.5.5 Flow Table Size                           |

|    |       | 6.5.6 Running Simultaneous Ripcord Applications |

|    | 6.6   | Scalability                                     |

|    | 6.7   | Related Work                                    |

| 7  | Cor   | aclusion                                        |

|    | 7.1   | Contribution Summary                            |

|    | 7.2   | Future Directions                               |

| Bi | bliog | graphy                                          |

# List of Figures

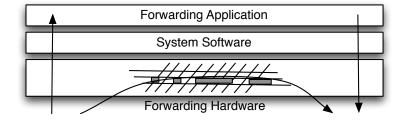

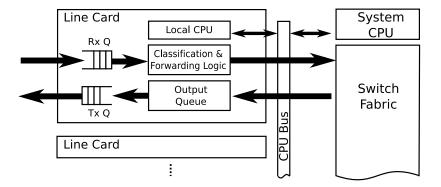

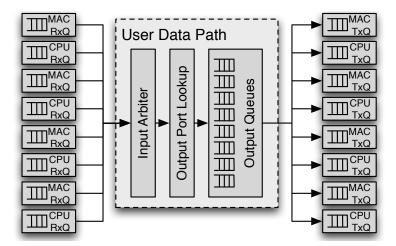

| 3.1<br>3.2<br>3.3 | High-level view of software defined forwarding                                                                                                  | 11<br>20<br>23 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.1               | Supporting an existing software router by a simple forwarding application implementing the forwarding engine abstraction of the software router | 27             |

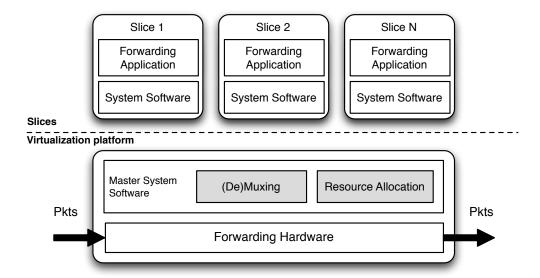

| 4.2               | Supporting network virtualization in SDF                                                                                                        | 29             |

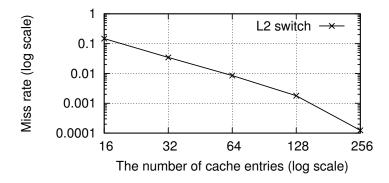

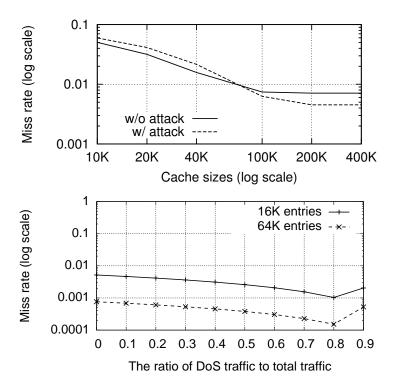

| 5.1               | Simulations of cache miss rates for L2 learning with the enterprise trace.                                                                      | 36             |

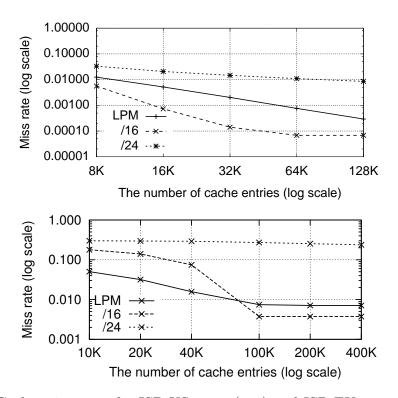

| 5.2<br>5.3        | Cache miss rates for ISP-US trace (top) and ISP-EU trace (bottom). Cache miss rates with forwarding on the /16 and /24 granularities for        | 37             |

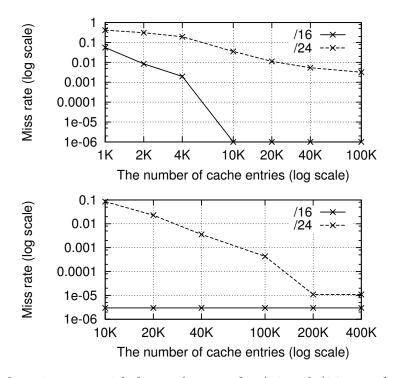

| 0.0               | the OC-48 (top) and the OC192-C trace (bottom)                                                                                                  | 38             |

| 5.4               | Cache miss rates with (and without) random DoS traffic comprising 50% of the traffic for the ISP-EU trace (top). Cache miss rates with          |                |

|                   | random DoS traffic for the ISP-US trace (bottom)                                                                                                | 39             |

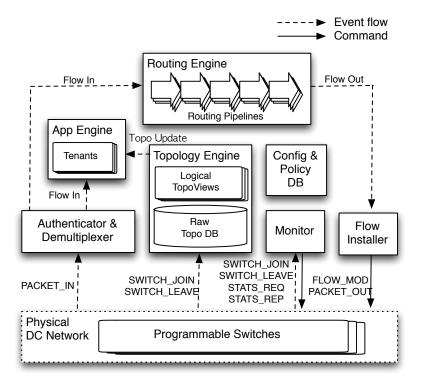

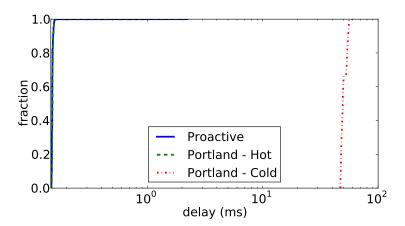

| 6.1<br>6.2        | Ripcord architecture and event flow diagram                                                                                                     | 46             |

|                   | modules                                                                                                                                         | 49             |

| 6.3               | Global routing policy example                                                                                                                   | 50             |

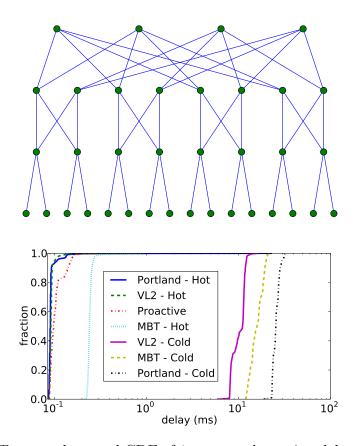

| 6.4               | Fat Tree topology and CDF of 1-to-many host ping delays on the soft-<br>ware test using the topology. Leaf nodes in the topology represent end  |                |

|                   | hosts. Proactive means proactively installed APSP                                                                                               | 57             |

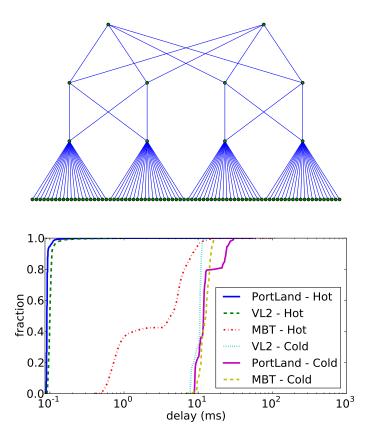

| 6.5               | Clos topology and CDF of 1-to-many host ping delays on the software testbed using the topology. Leaf nodes in the topology represent end        |                |

|                   | hosts.                                                                                                                                          | 58             |

| 6.6               | CDF of 1 to many host ping delays on the hardware testbed                                                                                       | 59             |

| 67                | Simultaneous running of multiple Ripcord Management Applications                                                                                | 62             |

# List of Tables

| 9, 91                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - · · · · · · · · · · · · · · · · · · ·                                | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Cache insertion/deletion performance of the NetFPGA prototype          | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Throughput of the NetFPGA prototype                                    | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Traces used in the cache hit-rate evaluations                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Network events that Ripcord expects from switch                        | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Switch commands expected by Ripcord                                    | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Ripcord's routing pipeline stages. Earlier stages in the table cannot  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| appear later in routing pipeline. Each routing module should be in one |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| of these stages                                                        | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Information included in a monitoring snapshot                          | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| API exposed by the monitoring module for active statistics collection. | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Lines of code of sample routing implementation                         | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OpenFlow entries realizing compact VL2 routing                         | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The number of flow entries installed at each switch by VL2 implemen-   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| tation with no flow idle timeout                                       | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The number of flow entries installed at each switch by VL2 implemen-   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| tation with flow idle timeout of 3 seconds                             | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                        | Throughput of the NetFPGA prototype.  Traces used in the cache hit-rate evaluations.  Network events that Ripcord expects from switch.  Switch commands expected by Ripcord.  Ripcord's routing pipeline stages. Earlier stages in the table cannot appear later in routing pipeline. Each routing module should be in one of these stages.  Information included in a monitoring snapshot.  API exposed by the monitoring module for active statistics collection.  Lines of code of sample routing implementation  OpenFlow entries realizing compact VL2 routing.  The number of flow entries installed at each switch by VL2 implementation with no flow idle timeout.  The number of flow entries installed at each switch by VL2 implementation with property installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at each switch by VL2 implementation with no flow entries installed at e |

### Acknowledgments

It is always difficult to write acknowledgements, since I am afraid of accidentally excluding people who really deserve appreciation. My life as a graduate student at UC Berkeley would never have been possible without help from my outstanding advisors, talented colleagues, and supportive friends and family. Therefore, my graduation is merely an opportunity to acknowledge their valuable help and great kindness to me. In a sense, this space is too small to enumerate all their names. Despite a dissertation bearing only a single name, I believe that it must be they who most deserve the recognition.

My appreciation for my research advisor, Professor Scott J. Shenker, has no bounds. He was the best source of research ideas and the most dependable person to ask for feedback throughout my Ph.D. course. The ideas in this dissertation could not have been fully explored without his great insight and guidance. Not only has he guided me in research, he has also treated me as an individual and encouraged me when I was at my most difficult moments. I also believe that I have learned a lot from his humility and respect for others.

I am very grateful to my dissertation committee members Professor Ion Stoica and Professor Tapan Parikh for their valuable feedback during my qualifying exam and review of this dissertation. I also greatly enjoyed working with Ion as his teaching assistant. I also have to thank Professor Randy H. Katz for serving on my qualifying exam committee and providing valuable comments.

It is my great fortune to have had the chance to work with Martin Casado and Teemu Koponen. It was Martin who has occasionally provided me with high-level research direction and inspired me to pursue this dissertation. I marveled at Teemu's broad and in-depth understanding of computer networking and technologies. I learned a lot from discussion with him and from his source code.

I also deeply appreciate the help of my colleague students in the Shenker group. Projects with them has taught me about teamwork and collaboration. Especially, I thank Andrey Ermolinskiy and Byung-gon Chun for the Minuet project and Junda Liu, Igor Ganichev and Kyriakos Zarifis for the SDF project and NOX-related projects. I also have to thank Brandon Heller, David Erickson and Professor Nick McKeown at Stanford for their amazing collaboration during the Ripcord project.

I am grateful to my parents who have remained consistently supportive throughout my studies. Finally, I thank Hayan Yoon for encouraging me throughout the last three years.

# Chapter 1

# Introduction

It is a tired cliché to remark on the success that the Internet has over the last two decades, but that success is undeniable and unprecedented. Much of this success is due to the structure of the Internet architecture, with its "narrow waist" of IP enabling radical innovations both above and below this internetworking layer. The networking industry has in turn built equipment (i.e. routers and switches) with rapidly improving performance/cost ratios by embedding IP and other features in the forwarding hardware.

Although the use of specialized hardware has succeeded in offering high performance, it often requires a major infrastructure upgrade to implement changes in network architecture. This hardware rigidity has created an innovation deadlock; new ideas require infrastructure support to evaluate and verify, while operators won't deploy new ideas until they are verified through experiments and implemented in hardware. By relying on specialized hardware for its implementation of the forwarding path, the networking industry has given up the ability to innovate on the forwarding path in return for performance. Therefore, the today's Internet has difficulty accommodating new networking requirements (e.g., security, management, etc.) and operating environments (e.g. data centers, developing regions, etc.).

Researchers have tried to overcome this innovation impasse. For example, research on overlay networks blossomed in early 2000s, and these networks have great flexibility, but their performance is lacking. Many thought network processors would the answer in this regard, but they have not proven capable of providing the necessary performance for a reasonable price.

The lack of innovation is not only felt in the standard networking settings, but also in more recent operating environments such as data center networking and networking in developing regions. Designs for these new operating environments often adopt home-brewed solutions to tackle domain-specific problems (e.g., full bisectional bandwidth in the data center, delay-tolerance in developing regions, etc.). Hence, solutions are barely interchangeable, even in the same domain. This means new operating environments are at the risk of being locked into non-standard architectures/protocols by their hardware rigidity.

For instance, the many proposals (e.g., [12, 14, 17, 20, 32]) for data center networking make specific assumptions about the low-level topology or are otherwise limited in their applicability. A more flexible approach, that can apply to a broader set of use cases, would be far more desirable. In this way, achieving flexibility in data center networking shares many high-level ideas with accomplishing flexibility in packet forwarding.

### 1.1 Problem statement

This dissertation focuses on how to achieve both high flexibility and low cost in two networking domains: classical packet forwarding and data center networking.

### 1.2 Contribution

Our contribution is twofold:

- 1. We present a new hardware design approach called "Software Defined Forwarding" to the classical high-speed packet-forwarding problem. We have implemented and evaluated the proposed approach in both software and hardware.

- 2. We propose a general routing and management platform called "Ripcord" for data center networking. We have implemented a prototype and evaluated it by running recent data center routing algorithms.

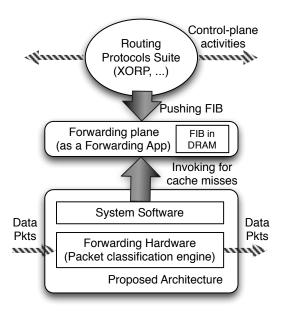

## 1.2.1 Software Defined Forwarding

In packet forwarding, we propose a hybrid design that attempts to combine the high speed and low cost of hardware with the superior flexibility of software. We motivate our approach by noting that current hardware-accelerated packet-forwarding implements the forwarding logic in hardware. In contrast, in our approach all forwarding decisions are first made in software and thereafter *imitated* by hardware. The hardware uses a classification engine to match software-made decisions with the incoming packets to which they apply (e.g., all packets destined for the same prefix). Thus, the hardware does not need to understand the logic of packet forwarding, it merely stores the results of forwarding decisions (previously made by software) and

applies them to packets with the appropriate headers. In short, hardware caches the decisions made by software and executes them at high-speed.

Similarly, the forwarding software is not tied to a particular hardware implementation. Instead, forwarding algorithms are programmed against a high-level API, which increases portability and reduces the complexity of implementation. This forwarding software is not speed-critical, so it can be written in a high-level language (in our implementations we have used Python as well as C++).

For lack of a better term, we call this decision-caching approach Software-Defined Forwarding (SDF), since all forwarding decisions are made in software. To demonstrate the viability of SDF, we built a complete system in hardware and software. On top of it, we have implemented a number of conventional forwarding algorithms (L2 Ethernet forwarding and L3 longest-prefix-matching), ported an existing code base (XORP), as well as implemented several recently proposed algorithms (SEATTLE, i3, Chord). We have also implemented a virtualization layer in software that allows multiple forwarding algorithms to operate in parallel on the same hardware; doing so did not require any change to the hardware forwarding model.

### 1.2.2 Ripcord: Data Center Routing/Management Platform

In data center networking, we present (based on joint work with the Stanford team) a new routing and management platform, called Ripcord. Ripcord provides a uniform control interface to a physical network so as to abstract high-level data center networking solutions from underlying network. This control interface is logically centralized so that schemes using the interface do not suffer from the need to implement complex distributed algorithms.

In addition, Ripcord supports multiple tenants. Each tenant on Ripcord is a logical entity (e.g., data center customers, services, jobs, etc) requiring a separate treatment in routing/management. These tenants are isolated from each other and can customize their routing and management with Ripcord modules. A researcher may use this capability to evaluate two schemes side by side (or even simultaneously); an experimental data center can host multiple researchers at the same time; a multi-tenant hosting service may provide different customers with different logical networks; and a multi-service data center may use schemes optimized for different services. For example, one scheme could be for MapReduce, alongside another for video streaming. We later illustrate this by running VL2 [12] and Portland [32] at the same time.

Ripcord is also modular in order to facilitate code re-use and rapid prototyping. Ripcord consists of a collection of key components with a well-defined interface and additional routing/management modules. Thus, data center operators may develop a new module for their data centers or share modules to add features into their data centers. Tenants can easily benefit from the new features in additional modules.

We guided the development of Ripcord from our observation that recent data center networking proposals (e.g., VL2 [12], Monsoon [14], BCube [17], PLayer [20], and PortLand [32]) present solutions based on specific requirements, some of which overlap across solutions, but may be prioritized differently in each solution. As a consequence, specific architectural choices often make it difficult to accommodate new requirements, changes to data center environments or modifications to the solution that attempt to tailor/tweak it for another data center environment. Ripcord is not in direct competition with any of these networking proposals; rather, it provides a platform that allows network administrators to experiment with one or more data center networking proposals (side by side if necessary), make modifications, and evaluate the proposal in their own data center environments.

# 1.3 Dissertation Organization

In the following chapter, we review the limitation of current design options to build packet-forwarding devices and discuss the incompatibility of data center networking solutions. Chapter 3 presents the SDF approach and describes our prototype implementation, followed by the use case study and performance study of SDF in Chapters 4 and Chapter 5. In Chapter 6, we describe the Ripcord framework and demonstrate how Ripcord can achieve flexibility in data center networking by implementing recent data center algorithms.

# Chapter 2

# Background

This chapter reviews the shortcomings of current design approaches to building packet forwarding devices and discuss the inability of data centers to implement changes.

# 2.1 The Status Quo in Packet Forwarding

As network speeds increase, and network requirements diversify, networking hardware vendors are being pressed on two distinct fronts. To remain competitive, they must continually improve their cost/performance ratio at a pace faster than Moore's Law. Over the past fifteen years, enterprise network speeds have increased by three orders of magnitude, from 10Mbps to 10Gbps, requiring that the cost of a unit of bandwidth (a gigabit port, or Gport) drop precipitously. At the same time, networks are expected to address myriad application, management and security requirements that were unheard of fifteen years ago, creating pressure to develop network forwarding devices that can flexibly accommodate these new demands as they arise. This trend is reflected in the many "open" platform initiatives launched by system vendors [29, 9, 21].

Despite significant research and engineering efforts, the industry has failed to simultaneously achieve low cost/performance and high flexibility. There are three basic approaches to building network forwarding devices currently pursued in the field and, as we relate below, they offer quite different tradeoffs between these two goals.

<sup>&</sup>lt;sup>1</sup>When we refer to flexibility, we mean the flexibility in forwarding algorithms, not general programmability for sophisticated packet processing. As we clarify later, we are not addressing network "appliances" that provide deep packet inspection. Our concern here is *only* for packet forwarding decisions: to which output port does this packet go, and how should its header be rewritten?

In the commercial world, where cost concerns dominate, the most prevalent approach to building network forwarding devices (this includes both switches and routers, but hereafter we will use the term "switch" as shorthand) involves embedding the basic forwarding logic in ASICs. There are commodity forwarding chips (from, for example, Broadcom, Marvell, and Fulcrum) that cost as little as \$20/10Gport, a price-point that would have been unthinkable only a few years ago. Multi-layer switches using these commodity chips support 240Gbps (24x10Gbps) of capacity for under \$100/10Gport, and 640Gbps (64x10Gbps) chipsets will be generally available this year which should lower the cost even further. However, one cannot modify the hardware forwarding algorithm without respinning the chip. This forces packet forwarding to evolve on hardware design timescales, which are glacially slow compared to the rate at which network requirements are changing.

In the research community, where flexibility is paramount, there has been renewed interest in purely software-based switches (i.e., switches running commodity operating systems on general-purpose CPUs); see, for example, [10]. These designs have the requisite flexibility, since new forwarding algorithms merely require additional programming, but their port-density and cost/performance remains poor. For example, software routers on general CPUs have been shown to support 10Gbps of trivial forwarding for minimum size packets [10], achieving roughly \$1000/10Gport, an order of magnitude more than the ASIC-based switches. While prevalent in low-speed wireless devices, pure software switches have made almost no penetration into the high-speed, high-fanout wireline market.

The industry has tried to bridge the divide between these two extremes with "network processors", whose goal was to provide programmable functionality at nearcommodity hardware costs. Unfortunately, network processors have not realized this goal, as designers have yet to find a sweet-spot in the tradeoff between hardware simplicity and flexible functionality. The cost/performance ratios have lagged well behind commodity networking chips and the interface provided to software has proven hard to use, requiring protocol implementors to painstakingly contort their code to the idiosyncrasies of the particular underlying hardware to achieve reasonable performance.<sup>2</sup> These two problems (among others) have prevented network processors from dislodging the more narrowly targeted commodity packet-forwarding hardware that dominates the market today. One area in which network processors are widely used is in network appliances, which go beyond mere forwarding to do deep packet inspection; but even here, after initial success, network processors are starting to lose market share as the forwarding performance of general-purpose CPUs has significantly improved. Today many market-leading middleboxes (such as load balancers) are implemented on standard x86 platforms.

<sup>&</sup>lt;sup>2</sup>However, CAFE [27] is a promising approach for datacenter forwarding.

# 2.2 Data Center Networking Aspects

The meteoric growth of data centers over the past decade has redefined how they are designed and built. Today, a large data center may contain over one hundred thousand servers and tens of thousands of individual networking components (switches, routers or both). Data centers often host many applications with dynamic capacity requirements, and differing service requirements. For example, it is not uncommon for the same data center to host applications requiring terabytes of internal bandwidth, and others requiring low-latency streaming to the Internet.

Their sheer scale, coupled with application dynamics and diversity, makes data centers unlike any systems that have come before. And to construct and manage them, network designers have had to rethink traditional methodologies. A prevailing design principle is to use "scale-out" system design. Scale-out systems are generally characterized by the use of redundant commodity components. Managed workloads are constructed so the system can gracefully tolerate component failures. Capacity is increased by adding hardware without requiring new configuration state or system software.

While scale-out design is well understood for building compute services from commodity end-hosts, it is a relatively new way to build out network capacity while retaining a rich service model to applications. Researches [12, 32] have explained clearly how traditional data center networks stood in the way of supporting highly dynamic applications, scale-out bandwidth, and the commodity cost model such systems are suited for.

Due to these limitations, the research community, and the largest data center operators – those with the deepest pockets – innovate fast, moving towards new schemes that allow them to construct systems with the requisite properties for their operations. While many schemes remain proprietary and unpublished, some notable data center network designs have been described. VL2 [12] uses Valiant load balancing [24, 53] and IP-in-IP encapsulation to spread traffic over a network of unmodified switches. On the other hand, PortLand [32] modifies the switches to route based on a pseudo-MAC header, and aims to eliminate switch configuration. Other researchers have proposed Monsoon [14] and FatTree [1]; Trill [51] and DCE [8] have been proposed as standards.

Each proposal holds a unique point in the design space, and subtle differences can have large ramifications on cost and performance, leading research questions that how we can evaluate which scheme is best for a given data center (or service) and how we can build on the work of others, modifying an existing scheme to suit particular needs.

# 2.3 Summary

In this chapter, we have described the current practices to design packet forwarding hardware and data center networking. All the traditional approaches to building packet forwarding equipments have limitations to simultaneously achieve flexibility and low cost/performance. In data center networking, due to use of home-brewed solutions data centers suffer inability to compare solutions and to adopt foreign solutions.

In the next chapter, we present software defined forwarding (SDF) and explain how SDF enables packet forwarding equipments both high flexibility and low cost/performance, leaving our solution to data center networking for Chapter 6.

# Chapter 3

# Software Defined Forwarding

As described in Chapter 2, current design approaches to building switches do not simultaneously guarantee flexibility in forwarding algorithms and high performance-to-cost rate. In this chapter, we explore a new design point, called "Software Defined Forwarding (SDF)", in the design spectrum. SDF is a hybrid approach that attempts to combine the high speed and low cost of hardware with the superior flexibility of software. In SDF, all the forwarding decisions are first made in software and then mimicked by hardware by caching them in a classification engine.

In the rest of the chapter, we first clarify the goals and limitations of SDF, then present its design details, and finally, describe our prototypes in software and hardware. In the following Chapter 4 and 5, we illustrate how a wide range of forwarding behaviors can be implemented on top of SDF and present its performance study results, respectively.

# 3.1 Goals, Limitations, and Applicability

Before delving into design details and performance results, we first articulate SDF's goals, limitations and applicability.

#### 3.1.1 Goals

The immediate goal of the SDF approach is to build switches with more forwarding flexibility by having all forwarding decisions determined completely in software and then imitated by hardware. This will allow networks to deploy new forwarding algorithms (such as to support a new protocol) without changing their networking hardware. In fact, as we discuss later, this will enable networks to run several different forwarding algorithms in parallel on the same switch. The longer term goal is to create an environment where both hardware and software designers can independently focus on their respective tasks. Hardware designers can focus on building "decision caches" with higher speeds, greater fanouts, larger memory, lower power and lower cost. Similarly, software designers can address emerging networking requirements by implementing new forwarding algorithms against a simple and fixed hardware interface. This strict separation of concerns should engender rapid progress in both hardware and software.

### 3.1.2 Limitations

We reiterate that the SDF approach only supports standard header-based forwarding and does not apply to more complex networking behaviors such as deep-packet inspection or arbitrary packet modification (like encryption). More specifically, the forwarding decisions can depend only on the header of the incoming packet (where the definition of "header" is the first n bits of the packet, where n is flexible) and on the internal state of the forwarding logic implementation. The output packets can differ from the incoming packet in the content (and the length) of the header, but this new header content can not depend on any forwarding logic state modified per packet (that is, for all packets matching a particular entry, the headers must be modified in the same way). Thus, the model does not include, for example, en/de-capsulation, en/de-cryption, nor complex modifications to the packet payload. Such operations requiring unique modifications per packet are handled outside the model, by a logical output port to which the packet is forwarded to. We note this is consistent with the model commonly used in routers and switches of using logical interfaces for tunneling (e.g., Percentage). IPsec or GRE).

While the packet processing model is limited, we have been surprised by how broadly it applies to traditional and newly proposed forwarding paradigms. For example, the SDF approach can implement aggregation, basic tagging, address overwriting (e.g., VLAN, or layered addressing), dynamic learning and filtering, all without changes to the hardware forwarding model.

## 3.1.3 Applicability

The SDF approach is most relevant in settings that need a high degree of flexibility. Research is an obvious arena where it would be important to deploy new forwarding algorithms, running at high speeds on commercial-grade equipment, merely by rewriting the forwarding software. In addition, the ability to run several forwarding algorithms in parallel, as is envisioned in GENI and other networking testbeds, would be very valuable.

However, it is an open question whether production networks need this degree of flexibility. Some have predicted that the future of networking lies in the ability to virtualize low-level packet transport, in which case this flexibility would be crucial. But it is also true that current forwarding algorithms evolve slowly, which suggests that perhaps flexibility is not relevant to production networks. The question is whether this slow evolution reflects the inability to evolve more quickly or the lack of a need to. We don't pretend to know the answer.