#### University of California Santa Barbara

## Modeling, Simulation, and Optimization of Variation-Aware Runtime-Reconfigurable Optical Interconnects

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering

by

Yuyang Wang

#### Committee in charge:

Professor Kwang-Ting Cheng, Co-Chair Professor John E. Bowers, Co-Chair Professor Yuan Xie Professor Clint L. Schow Professor Zheng Zhang

September 2021

| The Dissertation of Yuyang Wang is approved.   |

|------------------------------------------------|

|                                                |

|                                                |

| Professor Yuan Xie                             |

|                                                |

|                                                |

| Professor Clint L. Schow                       |

|                                                |

| Professor Zheng Zhang                          |

| 1 folessof Zheng Zhang                         |

|                                                |

| Professor John E. Bowers, Committee Co-Chair   |

|                                                |

|                                                |

| Professor Kwang-Ting Cheng, Committee Co-Chair |

# $\label{thm:configurable} \mbox{Modeling, Simulation, and Optimization of Variation-Aware Runtime-Reconfigurable}$ $\mbox{Optical Interconnects}$

Copyright © 2021

by

Yuyang Wang

To my wife, Crystal

#### Acknowledgements

My sincerest thanks go to my advisor, Professor Kwang-Ting Cheng, for being my role model of academic professionalism and a true mentor over the past six years. I am eternally grateful for his intellectual and personal advice and his support in all forms, all of which have encouraged me to become an independent researcher, a dependable collaborator, and above all, a better person.

I am deeply grateful to the rest of my dissertation committee, Professor John E. Bowers, Professor Yuan Xie, Professor Clint L. Schow, and Professor Zheng Zhang, for their insightful guidance and valuable feedback on my research, as well as their generous help in facilitating collaboration and internship opportunities over the years. Besides, I sincerely thank Professor Nadir Dagli for his vital input to my research, and Professor Larry Coldren, Professor Margaret Marek-Sadowska, Professor Li-C. Wang, Professor Forrest Brewer, Professor Behrooz Parhami, Professor Jason Marden, and Dr. Robby Nadler for their informative lectures.

I gratefully acknowledge the financial support from Semiconductor Research Corporation (SRC) and American Institute for Manufacturing Integrated Photonics (AIM Photonics) during my Ph.D. study.

I extend my heartfelt gratitude to my industry collaborators at Hewlett Packard Labs, Dr. M. Ashkan Seyedi, Dr. Peng Sun, Dr. Jared Hulme, Dr. Marco Fiorentino, Dr. Raymond G. Beausoleil, and Mudit Jain, for sharing firsthand data of fabricated devices and providing thoughtful input to our collaborative papers. I also thank Dr. Tsung-Ching Huang for offering his professional advice on various occasions.

I greatly appreciate the invaluable help from Professor Jiang Xu at HKUST, who offered me opportunities to promote my research in various workshops and departmental seminars and shared his extensive experience and broad vision of the field. I am also grateful for the mentorship I received from Dr. Gilles Lamant and Dr. Ahmadreza Farsaei during my internship at Cadence Design Systems, Inc.

I sincerely thank my fellow collaborators at UCSB, including Dr. Rui Wu, Dr. Zeyu Zhang, and Dr. Chong Zhang, for stimulating fruitful discussions and contributing to several of our research projects. I also thank Dr. Fan Lan, Dr. Di Liang, and Dr. Ping-Lin Yang for patiently answering my technical questions and offering helpful suggestions during my research.

I gratefully acknowledge the dedicated service of the staff of the ECE Department, including Valerie De Veyra, Shannon Gann, Robin Jenneve, Adriana Aguirre, Olivia La Pierre, Tori Smith, and Paul Gritt, for providing all sorts of help and relieving me from the burden of paperwork. I also thank the staff of the OISS and the Housing Services of UCSB for their indispensable support.

I extend my special thanks to my labmates unmentioned, Dr. Miguel A. Lastras Montaño, Dr. Amirali Ghofrani, Dr. Nicole Fern, Dr. Chun-Kai Hsu, Dr. Fan Lin, Dr. Chong Huang, and Dr. Leilai Shao, for our time together in the lab and our discussions on various topics. I also appreciate the friendship offered by fellow students from other research groups at UCSB, including Dr. Peng Gu, Dr. Maohua Zhu, and Fengqiao Sang. Besides, I thank my friends at HKUST, including Dr. Xuanqi Chen, Dr. Zengqiang Yan, Shichao Li, Guang Chen, Jeffry Wicaksana, and Weihang Dai, for their hospitality during my visit.

Finally, I would like to express my eternal gratefulness to my family: my parents, Dr. Zhihua Wang and Xuefei Yang, for their selfless devotion to my growth and education over the past 28 years; my late grandma, for her continued love and encouragement; my sister, Jacqueline, for simply being there for me; and my wife and life partner, Crystal, for her unconditional trust, support, and companionship, without which I would not have been able to make this journey.

#### **Curriculum Vitæ**

#### Yuyang Wang

#### **Education**

| 2021 | Ph.D., Electrical and Computer Engineering (Expected),<br>University of California, Santa Barbara, California, USA. |

|------|---------------------------------------------------------------------------------------------------------------------|

| 2018 | M.S., Electrical and Computer Engineering,<br>University of California, Santa Barbara, California, USA.             |

| 2015 | B.Eng., Electronic Engineering,<br>Tsinghua University, Beijing, China.                                             |

#### **Professional Experience**

| Fall 2019   | Visiting Intern, Hong Kong University of Science and Technology,<br>Clear Water Bay, Hong Kong SAR, China.                               |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Winter 2019 | <i>Teaching Assistant</i> , Department of Electrical and Computer Engineering, University of California, Santa Barbara, California, USA. |

| Summer 2018 | Design Engineering Intern, Cadence Design Systems, Inc.,<br>San Jose, California, USA.                                                   |

| Summer 2014 | Student Intern, Rice University, Houston, Texas, USA.                                                                                    |

#### **Publications**

**Yuyang Wang** and Kwang-Ting Cheng, "Traffic-Adaptive Power Reconfiguration for Energy-Efficient and Energy-Proportional Optical Interconnects," in *IEEE/ACM International Conference on Computer-Aided Design (ICCAD)*, Nov. 2021.

**Yuyang Wang**, Peng Sun, Jared Hulme, M. Ashkan Seyedi, Marco Fiorentino, Raymond G. Beausoleil, and Kwang-Ting Cheng, "Energy Efficiency and Yield Optimization for Optical Interconnects via Transceiver Grouping," *IEEE/OSA Journal of Lightwave Technology*, vol. 39, no. 6, 2021.

**Yuyang Wang**, Jared Hulme, Peng Sun, Mudit Jain, M. Ashkan Seyedi, Marco Fiorentino, Raymond G. Beausoleil, and Kwang-Ting Cheng, "Characterization and Applications of Spatial Variation Models for Silicon Microring-Based Optical Transceivers," in *ACM/IEEE Design Automation Conference (DAC)*, Jun. 2020.

**Yuyang Wang** and Kwang-Ting Cheng, "Task Mapping-Assisted Laser Power Scaling for Optical Network-on-Chips," in *IEEE/ACM International Conference on Computer-Aided Design (ICCAD)*, Nov. 2019.

**Yuyang Wang**, Leilai Shao, Miguel A. Lastras-Montaño, and Kwang-Ting Cheng, "Taming Emerging Devices' Variation and Reliability Challenges with Architectural and System Solutions [Invited]," in *IEEE International Conference on Microelectronic Test Structures (ICMTS)*, Mar. 2019.

**Yuyang Wang**, M. Ashkan Seyedi, Jared Hulme, Marco Fiorentino, Raymond G. Beausoleil, and Kwang-Ting Cheng, "Bidirectional Tuning of Microring-Based Silicon Photonic Transceivers for Optimal Energy Efficiency," in *ACM/IEEE Asia and South Pacific Design Automation Conference (ASP-DAC)*, Jan. 2019.

**Yuyang Wang**, M. Ashkan Seyedi, Rui Wu, Jared Hulme, Marco Fiorentino, Raymond G. Beausoleil, and Kwang-Ting Cheng, "Energy-Efficient Channel Alignment of DWDM Silicon Photonic Transceivers," in *IEEE Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Mar. 2018.

Rui Wu, M. Ashkan Seyedi, **Yuyang Wang**, Jared Hulme, Marco Fiorentino, Raymond G. Beausoleil, and Kwang-Ting Cheng, "Pairing of Microring-Based Silicon Photonic Transceivers for Tuning Power Optimization," in *IEEE/ACM Asia and South Pacific Design Automation Conference (ASP-DAC)*, Jan. 2018.

Zeyu Zhang, Rui Wu, **Yuyang Wang**, Chong Zhang, Eric J. Stanton, Clint L. Schow, Kwang-Ting Cheng, and John E. Bowers, "Compact Modeling for Silicon Photonic Heterogeneously Integrated Circuits," *IEEE/OSA Journal of Lightwave Technology*, vol. 35, no. 14, 2017.

Rui Wu, **Yuyang Wang**, Zeyu Zhang, Chong Zhang, Clint L. Schow, John E. Bowers, and Kwang-Ting Cheng, "Compact Modeling and Circuit-Level Simulation of Silicon Nanophotonic Interconnects," in *IEEE Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Mar. 2017.

Amirali Ghofrani, Miguel A. Lastras-Montaño, **Yuyang Wang**, and Kwang-Ting Cheng, "Inplace Repair for Resistive Memories Utilizing Complementary Resistive Switches," in *ACM International Symposium on Low Power Electronics and Design (ISLPED)*, Aug. 2016.

Chao Xu, Felix X. Lin, **Yuyang Wang**, and Lin Zhong, "Automated OS-level Device Runtime Power Management," in *ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS)*, Mar. 2015.

#### **Abstract**

Modeling, Simulation, and Optimization of Variation-Aware Runtime-Reconfigurable

Optical Interconnects

by

#### Yuyang Wang

The explosive growth of data volume brought by the pervasiveness of artificial intelligence (AI) applications is calling for interconnect technologies that enable higher bandwidth capacity at a lower cost. In particular, optical interconnects based on silicon photonics are considered a promising substitute for electrical ones, given their cost-effectiveness and scalability enabled by a CMOS-compatible fabrication process. However, as the optical interconnects further penetrate the shorter-reach regime, several issues arise from the growing complexity of system integration and pose challenges to their design quality, including 1) inadequate support from design automation methodologies for the modeling and simulation of the optical interconnects, 2) oversimplified characterization of process variations, resulting in variation alleviation techniques with limited effectiveness, and 3) the lack of runtime reconfiguration strategies for the optical interconnects under traffic dynamics, leading to unoptimized energy efficiency. This dissertation is devoted to addressing the above issues by solutions proposed at the device, link, and system levels, paving the way to the quality design of variation-aware runtime-reconfigurable optical interconnects with optimized energy efficiency.

The first part of this dissertation focuses on device-level methodologies for electronic-photonic design automation (EPDA), including compact models developed for lasers and modulators and a novel hierarchical spatial variation model characterized for silicon microring resonators. Extensively validated by measurement data, the library of device-level

models enables accurate circuit-level simulation of optical links and variation-aware estimation of the link power budget, serving as the fundamentals of the optimization techniques proposed at the link and system levels.

The second part of this dissertation proposes three link-level techniques to improve the energy efficiency of the optical interconnects under wafer-scale process variations. The three techniques exploit, respectively, 1) sub-channel redundancy of carrier wavelengths, 2) a combination of electrical and thermal tuning mechanisms, and 3) optimal mixing and matching of a batch of fabricated transceivers, achieving significant reductions in the energy required for transmitting a single bit of data.

The third and final part of this dissertation proposes two strategies at the system level that further improve the energy efficiency of the optical interconnects under traffic dynamics by reconfiguring the link power at application runtime. The two strategies incorporate assistance from 1) traffic adjustment enabled by task mapping exploration and 2) traffic adaptability enabled by traffic prediction, respectively, and achieve substantial improvements in energy consumption with minimal overhead to application execution time, notably outperforming existing strategies.

## **Contents**

| Cı | urricı  | ılum Vitæ                                            | vii |

|----|---------|------------------------------------------------------|-----|

| Ał | ostrac  | et                                                   | ix  |

| Li | st of l | Figures                                              | xiv |

| Li | st of ' | Tables                                               | xix |

| Li | st of A | Abbreviations                                        | xx  |

| Pa | art I   | Introduction and Literature Review                   | 1   |

| 1  | Intr    | oduction                                             | 2   |

|    | 1.1     | Background of Optical Interconnects                  | 3   |

|    | 1.2     | Scope of Challenges to be Addressed                  |     |

|    |         | Clarification on Energy Efficiency                   |     |

|    | 1.4     | Dissertation Outline                                 | 10  |

|    | 1.5     | Permissions and Attributions                         | 12  |

| 2  | Prio    | or Work                                              | 14  |

|    | 2.1     | Device-Level Design Automation and Optimization      | 14  |

|    | 2.2     | Link-Level Design Automation and Optimization        | 21  |

|    | 2.3     | System-Level Design Automation and Optimization      | 26  |

| P  | art I   | Device-Level Modeling and Variation Characterization | 30  |

| 3  | Con     | npact Modeling for Lasers and Modulators             | 31  |

|    | 3.1     | Introduction                                         | 31  |

|    | 3.2     | Device Characterization and Model Implementation     | 33  |

|    | 3.3     | Link-Level Simulation and Model Validation           | 42  |

|    | 3.4     | Model-Based Design Optimization                      | 47  |

|   | 3.5   | Concluding Remarks                                                | . 48  |

|---|-------|-------------------------------------------------------------------|-------|

| 4 | Spa   | tial Variation Modeling for Microring Resonators                  | 50    |

|   | 4.1   | Introduction                                                      | . 50  |

|   | 4.2   | Overview and Data Preprocessing                                   | . 53  |

|   | 4.3   | Hierarchical Variation Characterization                           | . 58  |

|   |       | Applications of the Variation Model                               |       |

|   | 4.5   | Concluding Remarks                                                | . 68  |

| P | art I | II Link-Level Variation Alleviation                               | 70    |

| 5 | Red   | lundant Laser Comb Lines for Microring-Based Optical Transceivers | 71    |

|   | 5.1   | Introduction                                                      | . 72  |

|   | 5.2   | Overview and Data Preparation                                     | . 74  |

|   | 5.3   | Power Models and Assumptions                                      | . 77  |

|   | 5.4   | Channel Alignment Schemes                                         | . 79  |

|   | 5.5   | Design Space Exploration                                          | . 83  |

|   | 5.6   | Concluding Remarks                                                |       |

| 6 |       | irectional Tuning of Microring Resonance Wavelengths              | 87    |

|   | 6.1   | Introduction                                                      | . 88  |

|   | 6.2   | Overview and Data Preparation                                     |       |

|   | 6.3   | Power Models and Assumptions                                      |       |

|   | 6.4   | Problem Formulation                                               |       |

|   | 6.5   | Evaluation                                                        |       |

|   | 6.6   | Polynomial-Time Approximation                                     |       |

|   | 6.7   | Concluding Remarks                                                | . 103 |

| 7 |       | nsceiver Grouping for Microring-Based Optical Interconnects       | 105   |

|   |       | Introduction                                                      |       |

|   | 7.2   | Background                                                        |       |

|   |       | Problem Formulation                                               |       |

|   | 7.4   | 1                                                                 |       |

|   | 7.5   | Evaluation                                                        |       |

|   | 7.6   | Concluding Remarks                                                | . 134 |

| P | art I | V System-Level Runtime Power Reconfiguration                      | 135   |

| 8 | TMA   | ALPS: Task Mapping–Assisted Laser Power Scaling                   | 136   |

|   |       | Introduction                                                      | . 136 |

|   |       | Background                                                        |       |

|   |       | Problem Formulation                                               | 1/2   |

|    | 8.4   | Simulation Setup                                                 | 144 |

|----|-------|------------------------------------------------------------------|-----|

|    | 8.5   | Evaluation                                                       | 147 |

|    | 8.6   | Concluding Remarks                                               | 154 |

| 9  | Poi   | ESTAR: Power Level Scaling with Traffic-Adaptive Reconfiguration | 155 |

|    | 9.1   | Introduction                                                     | 156 |

|    | 9.2   | Background                                                       | 159 |

|    | 9.3   | Strategy Design and Motivation Analysis                          | 163 |

|    | 9.4   | Simulation Setup                                                 | 171 |

|    | 9.5   | Evaluation                                                       | 178 |

|    | 9.6   | Concluding Remarks                                               | 189 |

| Pa | art V | <b>Discussion</b>                                                | 190 |

| 10 | Con   | nclusion and Future Work                                         | 191 |

|    | 10.1  | Dissertation Conclusions                                         | 191 |

|    | 10.2  | Possible Future Directions                                       | 192 |

| B  | iblio | ography                                                          | 195 |

## **List of Figures**

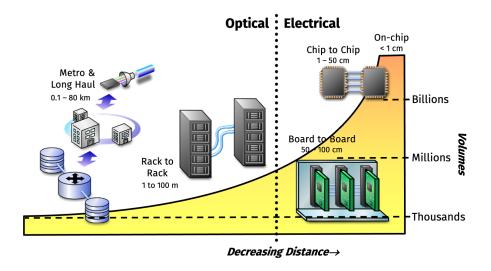

| 1.1        | Evolution of optical interconnects toward snorter reach (courtesy of intel Cor-                                                                          |    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | poration)                                                                                                                                                | 3  |

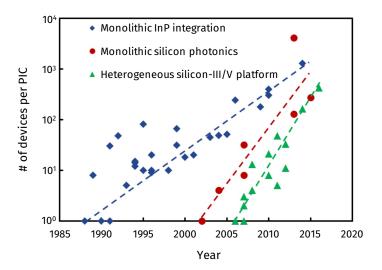

| 1.2        | Number of photonic devices integrated on a photonic integrated circuit (PIC)                                                                             |    |

|            | over the past decades for three technology platforms of integrated photonics                                                                             | _  |

|            | (data from [9])                                                                                                                                          | 5  |

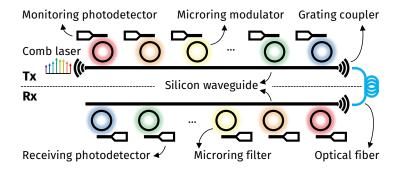

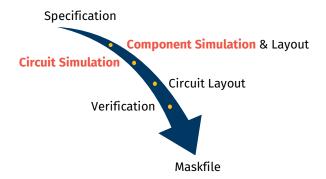

| 1.3<br>1.4 | Architectural illustration of a silicon microring–based optical transceiver Design automation methodologies required for designing a PIC, as envisioned  | 6  |

|            | by [31], where the modeling and simulation methodologies for photonic de-                                                                                |    |

|            | vices and circuits are at the foundation                                                                                                                 | 7  |

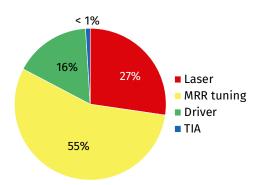

| 1.5        | Energy decomposition of a microring-based optical link reported in [32] showing the shares of the laser, microring resonator (MRR) tuning (for variation |    |

|            | rectification), electronic drivers, and transimpedance amplifiers (TIAs)                                                                                 | 8  |

| 1.6        | Overview of the solutions proposed in this dissertation                                                                                                  | 11 |

|            |                                                                                                                                                          |    |

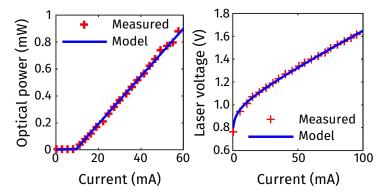

| 3.1        | Measured and simulated light-current (LI) and current-voltage (IV) curves of                                                                             |    |

|            | the distributed feedback (DFB) laser (light output is from one facet)                                                                                    | 35 |

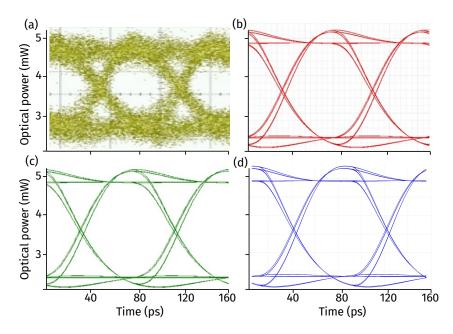

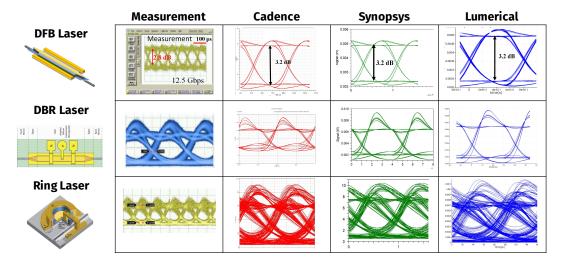

| 3.2        | Eye diagrams of a 12.5 Gb/s directly-modulated DFB laser [214]: (a) measure-                                                                             |    |

|            | ment; (b) simulation in Cadence Virtuoso; (c) simulation in Synopsys Rsoft                                                                               |    |

|            | Optsim Circuit; and (d) simulation in Lumerical INTERCONNECT. The mod-                                                                                   |    |

|            | ulation depth is 3 dB in all four eye diagrams. In both the experiment and simulation setups, the laser is biased at 2.14 V and driven by a pseudorandom |    |

|            | binary sequence (PRBS) signal with 0.75 Vpp. The eyes share the same axes                                                                                | 36 |

| 3.3        | DFB, distributed Bragg reflector (DBR), and microring laser models simulated                                                                             |    |

|            | in multiple design automation platforms                                                                                                                  | 37 |

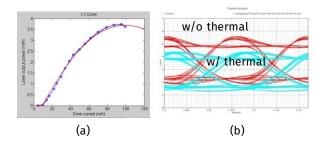

| 3.4        | Laser thermal effects modeling: (a) extraction of thermal-dependent coeffi-                                                                              |    |

|            | cients from measured LI roll-over; and (b) simulated degradations in the eye                                                                             |    |

|            | diagram                                                                                                                                                  | 38 |

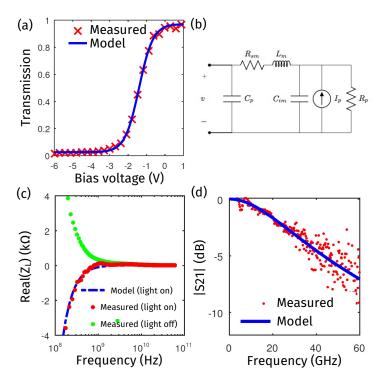

| 3.5        | (a) Electroabsorption modulator (EAM) transmission characteristics plotted                                                                               |    |

|            | as a function of bias voltage; (b) quasi-static circuit model for the EAM; (c) real                                                                      |    |

|            | part of the EAM load impedance as a function of modulation frequency; and                                                                                |    |

|            | (d) S21 (electro-optical (EO)) response of the EAM                                                                                                       | 40 |

|            | (, (                                                                                                                                                     | -0 |

|            |                                                                                                                                                          |    |

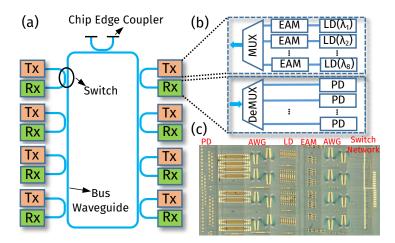

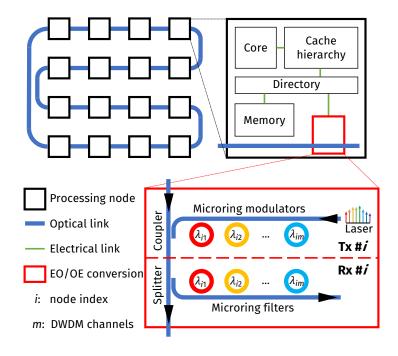

| 3.6  | (a) Target optical network-on-chip (ONoC) architecture; (b) enlargements of a transmitter (Tx) and a receiver (Rx); and (c) microscopic image of the fabri- |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | 1 0                                                                                                                                                         | 43  |

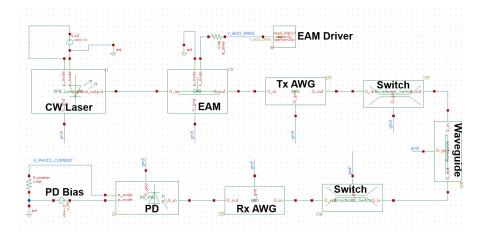

| 3.7  | Schematic view of the transceiver link in Cadence Virtuoso. The $50 \Omega$ resis-                                                                          | 4.  |

| 3.7  |                                                                                                                                                             |     |

|      | tors in the EAM driver and after the photodetector (PD) represent the internal                                                                              | 1/  |

| 2.0  | 1 0                                                                                                                                                         | 44  |

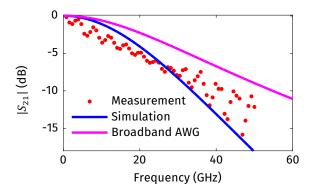

| 3.8  | Simulated and measured frequency responses of the modeled single-channel                                                                                    |     |

|      | transceiver link. The pink line represents the predicted frequency response                                                                                 |     |

|      | of the transceiver link integrated with broadband arrayed waveguide gratings                                                                                |     |

| 2.0  |                                                                                                                                                             | 44  |

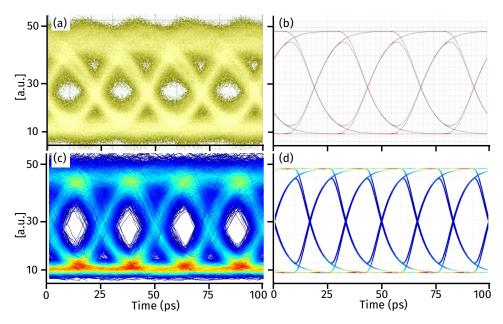

| 3.9  | (a) Measured eye diagram of the single-channel transceiver link at 40 Gb/s;                                                                                 |     |

|      | (b) noise-free full-link eye diagram simulated in Cadence Virtuoso at 40 Gb/s;                                                                              |     |

|      | (c) full-link eye diagram simulated in Lumerical INTERCONNECT at 40 Gb/s,                                                                                   |     |

|      | where the power spectral density (PSD) of the noise source at the laser and                                                                                 |     |

|      | the modulator are set to $1 \times 10^{-17}$ W/Hz, and the PD thermal noise variance                                                                        |     |

|      | is $3.328 \times 10^{-22} \text{ A}^2/\text{Hz}$ ; (d) simulated noise-free transceiver link eye diagram                                                    |     |

|      | at 60 Gb/s in Lumerical INTERCONNECT with the AWGs removed, where the                                                                                       |     |

|      | software-calculated extinction ratio is the same as the noise-free eye diagram                                                                              | 4.5 |

| 0.10 |                                                                                                                                                             | 45  |

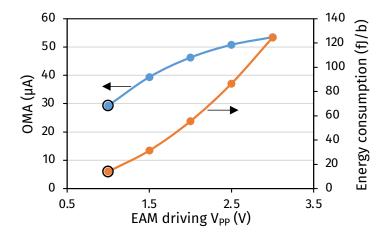

| 3.10 | Optical modulation amplitude (OMA) and modulation energy consumption                                                                                        |     |

|      | w.r.t. different EAM driving voltages, the black circles indicating the operating                                                                           |     |

|      | points of the EAMs in the measured and simulated ONoC                                                                                                       | 49  |

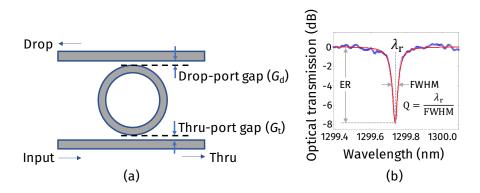

| 4.1  | Illustrations of the typical (a) geometry design and (b) thru-port transmission                                                                             |     |

|      | spectrum of a microring resonator, where FWHM denotes the full width at half                                                                                |     |

|      |                                                                                                                                                             | 53  |

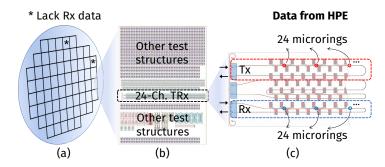

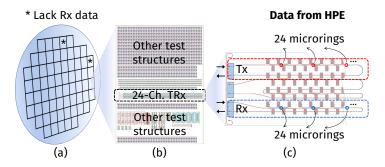

| 4.2  | Organization of measured devices: (a) a wafer of 66 dies; (b) each die consist-                                                                             |     |

|      | ing of one TRx; and (c) each Tx/Rx consisting of 24 microrings                                                                                              |     |

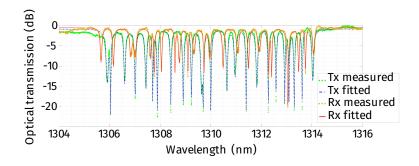

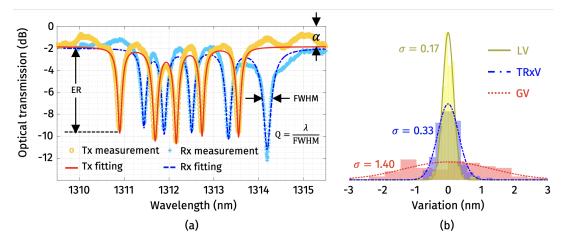

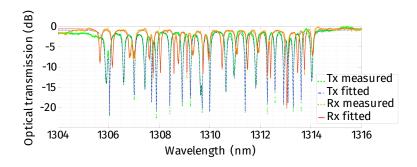

| 4.3  | Measured and fitted transmission spectra of a 24-channel transceiver                                                                                        |     |

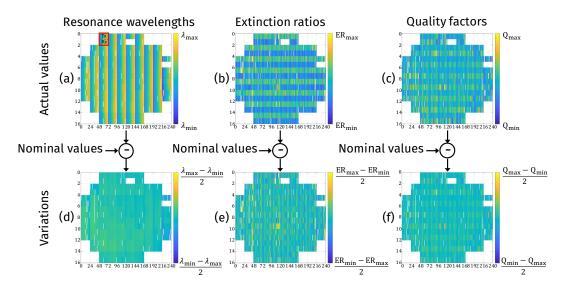

| 4.4  | Wafer maps for the (a–c) actual values, and (d–f) variations of $\lambda_r$ , ER, and Q                                                                     |     |

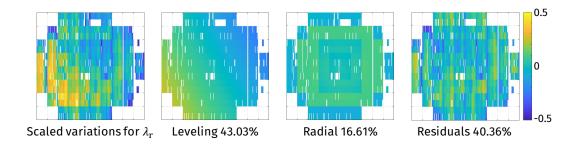

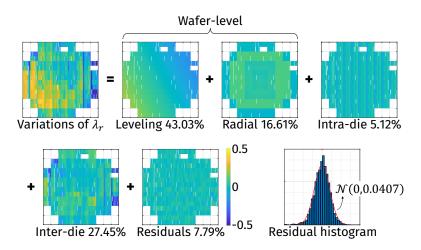

| 4.5  | Wafer-level variation components for $\lambda_r$                                                                                                            |     |

|      | Analyses of wafer-level residuals for $\lambda_r$                                                                                                           |     |

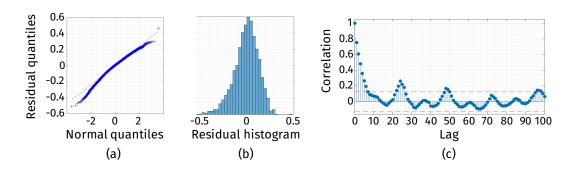

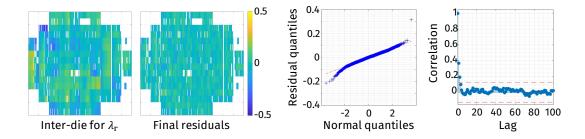

| 4.7  | Intra-die variation patterns and residual analyses for $\lambda_r$                                                                                          |     |

| 4.8  | Intra-die variation patterns for Q                                                                                                                          |     |

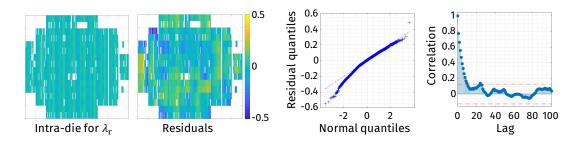

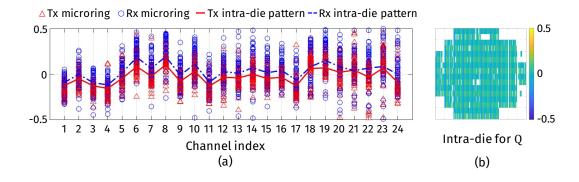

|      | Inter-die variation characterization and final residual analyses for $\lambda_r$                                                                            |     |

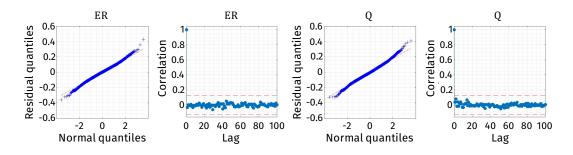

|      | Final residual analyses for ER and Q                                                                                                                        | 63  |

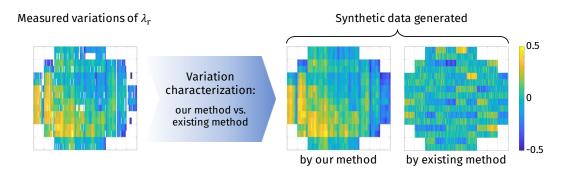

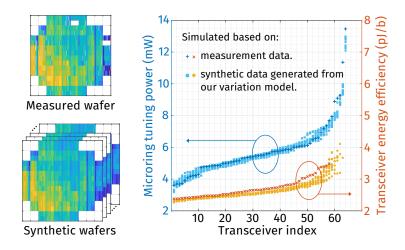

| 4.11 | Comparison of the synthetic data generated by our method and the existing                                                                                   |     |

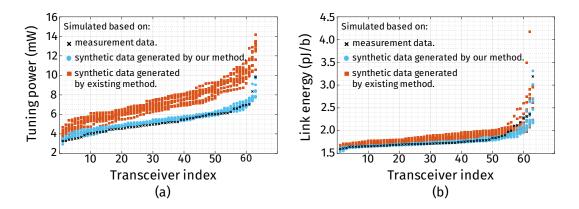

|      | method from [105]                                                                                                                                           | 65  |

| 4.12 | Simulations of tuning power and link energy efficiency show better quality of                                                                               |     |

|      | our synthetic data compared to that of [105]                                                                                                                |     |

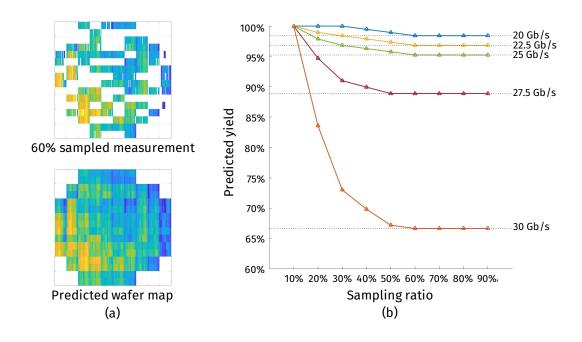

| 4.13 | Predicted yield at various sampling ratio                                                                                                                   | 68  |

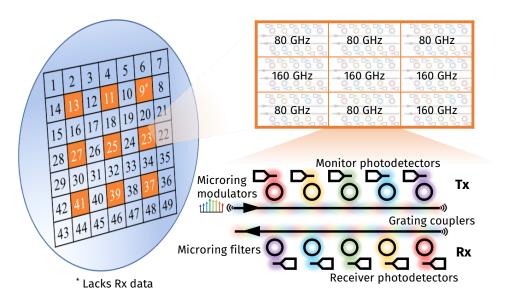

| 5.1        | Illustration of the fabricated transceivers from which the process variation model for resonance wavelengths is extracted                                                                                                                                                                                                                                                        | 75             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

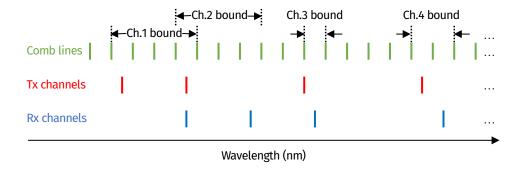

| 5.2        | (a) Measured optical spectrum of a five-channel transceiver with 80 GHz chan-                                                                                                                                                                                                                                                                                                    | Ö              |

|            | nel spacing, and (b) distributions of the variation components and the fitted                                                                                                                                                                                                                                                                                                    |                |

|            | 1 0                                                                                                                                                                                                                                                                                                                                                                              | 76             |

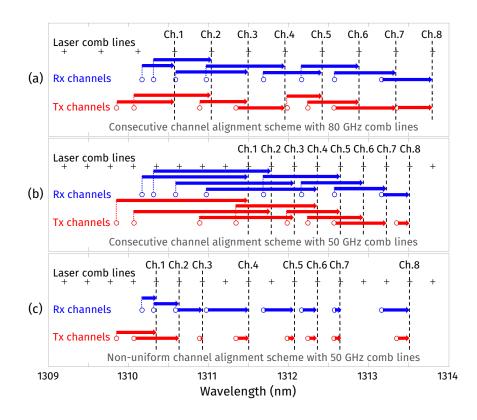

| 5.3        | Illustration of the tuning distance computed for (a) the consecutive channel alignment scheme with 80 GHz–spaced laser comb lines, (b) the consecutive channel alignment scheme with 50 GHz–spaced laser comb lines, and (c) the proposed non-uniform channel alignment scheme with 50 GHz–spaced laser comb lines. The microring channels are of 80 GHz spacing with variations |                |

|            | added on top                                                                                                                                                                                                                                                                                                                                                                     | 30             |

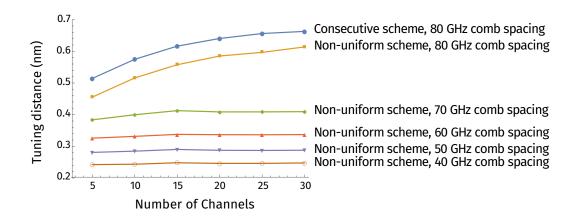

| 5.4        | Average tuning distance per microring for various channel counts using the traditional consecutive channel alignment scheme and our proposed non-                                                                                                                                                                                                                                |                |

|            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                            | 31             |

| 5.5        | Saving of the link energy per bit under different channel counts using the proposed channel alignment scheme compared to using the consecutive scheme.                                                                                                                                                                                                                           | 32             |

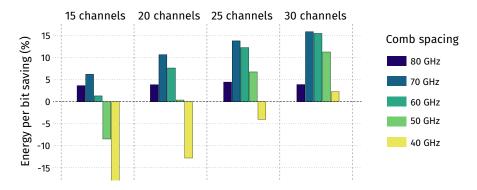

| 5.6        | Design space exploration using our non-uniform channel alignment scheme                                                                                                                                                                                                                                                                                                          | ,_             |

|            | with a target aggregated data rate of (a) 200 Gb/s, and (b) 100 Gb/s. The smi-                                                                                                                                                                                                                                                                                                   |                |

|            | ley sign in each subplot stands for the configuration that leads to the lowest                                                                                                                                                                                                                                                                                                   |                |

|            | energy per bit value                                                                                                                                                                                                                                                                                                                                                             | 34             |

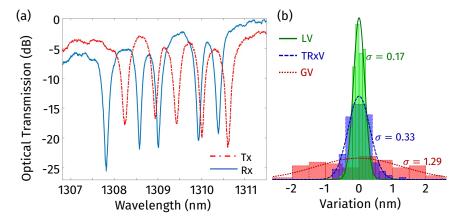

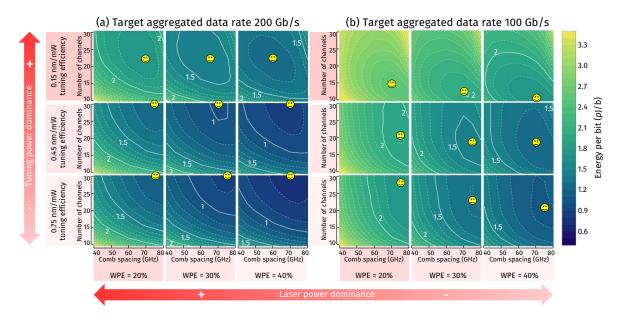

| 6.1        | (a) Microscopic image and (b) architectural illustration of a 5-channel microring based transaciver febricated by CEA Leti                                                                                                                                                                                                                                                       | 20             |

| 6.2        | (a) Measured and fitted spectra of a 5-channel transceiver, where FWHM denotes the full width at half maximum, and (b) variation characterization for                                                                                                                                                                                                                            | 90             |

| c 2        | 0                                                                                                                                                                                                                                                                                                                                                                                | 92             |

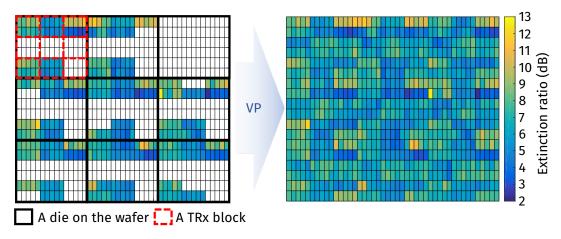

| 6.3        | Relative locations of measured ER (left) and predicted values for unmeasured microrings by Virtual Probe (right)                                                                                                                                                                                                                                                                 | 92             |

| 6.4        |                                                                                                                                                                                                                                                                                                                                                                                  | 94             |

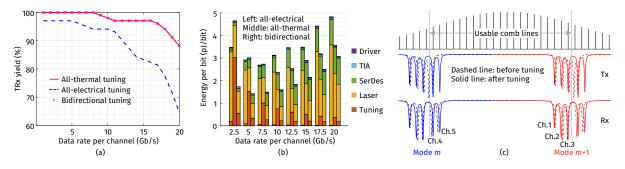

| 6.5        |                                                                                                                                                                                                                                                                                                                                                                                  | 96             |

| 6.6        | Evaluation of bidirectional tuning on measurement data: (a) yield comparison; (b) energy-per-bit comparison; and (c) bidirectional tuning opportunities                                                                                                                                                                                                                          |                |

|            | identified by our strategy                                                                                                                                                                                                                                                                                                                                                       | <del>)</del> 8 |

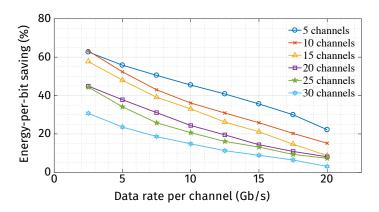

| 6.7        | 07 1                                                                                                                                                                                                                                                                                                                                                                             |                |

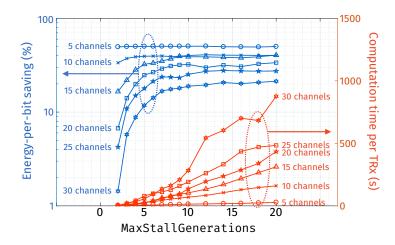

| <i>c</i> 0 | tuning on synthetic data of 5–30-channel transceivers                                                                                                                                                                                                                                                                                                                            |                |

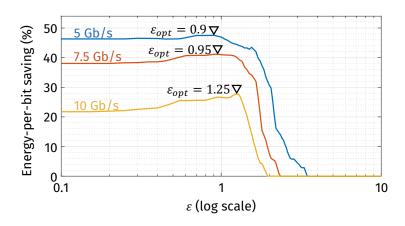

| 6.8<br>6.9 | Energy-per-bit savings vs. computation time for bidirectional tuning 10 Effect of $\varepsilon$ on the energy-per-bit savings of the polynomial-time approxima-                                                                                                                                                                                                                  | JU             |

| 0.9        | tion method                                                                                                                                                                                                                                                                                                                                                                      | 02             |

| 7.1        | Illustration of an optical network with a ring topology                                                                                                                                                                                                                                                                                                                          | ეფ             |

| 7.2        | Measured and fitted transmission spectra of a 24-channel TRx                                                                                                                                                                                                                                                                                                                     |                |

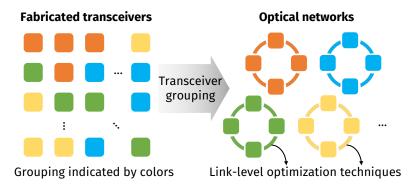

| 7.3        | Illustration of transceiver grouping and its relationship with existing link-level                                                                                                                                                                                                                                                                                               |                |

|            | optimization techniques [173, 174, 175, 176, 225, 226]                                                                                                                                                                                                                                                                                                                           | 11             |

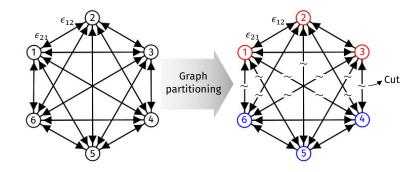

| 7.4         | Transceiver grouping as a graph partitioning problem                                                       | . 114 |

|-------------|------------------------------------------------------------------------------------------------------------|-------|

| 7.5         | Organization of measured devices: (a) a wafer of 66 dies; (b) each die consist-                            |       |

|             | ing of one TRx; and (c) each Tx/Rx consisting of 24 microrings                                             | . 119 |

| 7.6         | Wafer-scale variation characterization for $\lambda_r$ , same process applied to ER and                    | 100   |

|             | Q                                                                                                          |       |

| 7.7         | Synthetic data generation and validation                                                                   | . 121 |

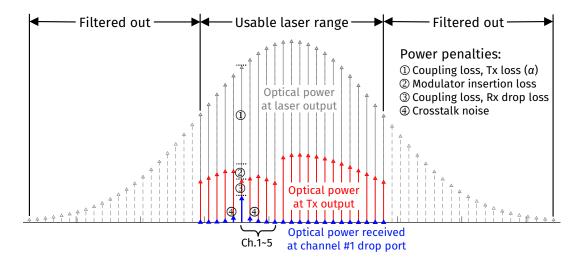

| 7.8         | Power losses in a microring-based optical link, plotted for five channels for                              |       |

|             | illustration purpose, including ① coupling loss and modulator passing loss;                                |       |

|             | ② modulator insertion loss; ③ coupling loss, propagation loss, and Rx drop-                                |       |

| <b>7</b> 0  | port loss; and ④ crosstalk noise.                                                                          | . 123 |

| 7.9         | Illustration of grouping schemes for $N = 16$ and $n = 2$ at a target data rate of                         | 10-   |

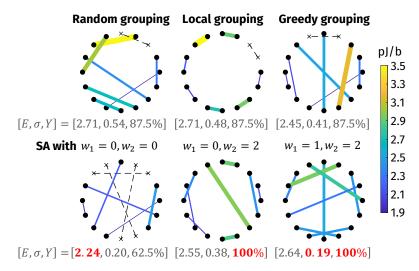

| <b>-</b> 10 | 30 Gb/s per channel                                                                                        | . 125 |

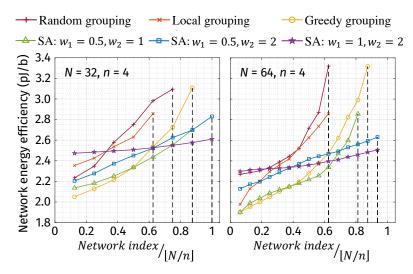

| 7.10        | Comparison of grouping schemes for $N = 32,64$ and $n = 4$ at a target data rate                           | 105   |

| <b>-</b> 11 | of 30 Gb/s per channel                                                                                     | . 127 |

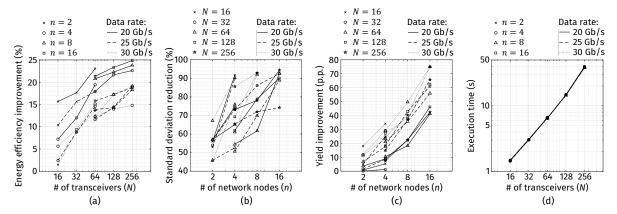

| 7.11        | (a)–(c) Improvement achieved by our simulated annealing (SA)-based algo-                                   |       |

|             | rithm with $w_1 = 1$ and $w_2 = 2$ over the random grouping scheme in energy ef-                           |       |

|             | ficiency, yield, and uniformity, evaluated for various network configurations,                             |       |

|             | and (d) execution time of our SA-based algorithm for various network config-                               | 100   |

| 7 10        | urations                                                                                                   | . 128 |

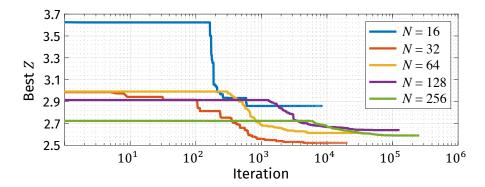

| 1.12        | Evolution of the cost value with SA iterations, plotted for $n = 4$ and 30 Gb/s per channel as an example. | 120   |

| 7 12        | Comparison of the Pareto fronts of $E$ , $\sigma$ , and $Y$ produced by SWEEP, MOPSO,                      | . 129 |

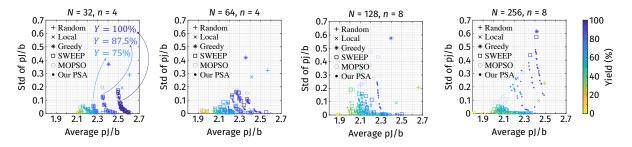

| 7.13        | and our Pareto simulated annealing (PSA)-based algorithm for (a) $N = 32$ , $n = 30$                       |       |

|             | 4, (b) $N = 64$ , $n = 4$ , (c) $N = 128$ , $n = 8$ , and (d) $N = 256$ , $n = 8$ , at a target data       |       |

|             | rate of 30 Gb/s per channel                                                                                | 132   |

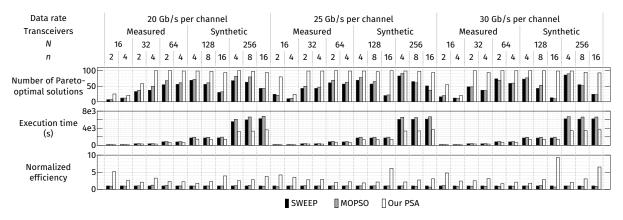

| 7 14        | Number of Pareto-optimal solutions, execution time, and efficiency compari-                                | 152   |

| 1.17        | son of SWEEP, MOPSO, and our PSA-based algorithm                                                           | 133   |

|             | oon of overlar, from oo, and our for based algorithms.                                                     | 100   |

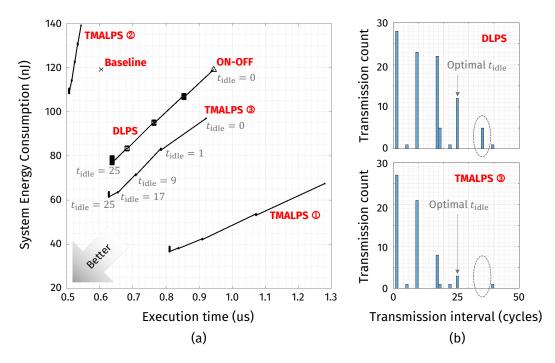

| 8.1         | Illustration of an MWMR ONoC architecture                                                                  | 139   |

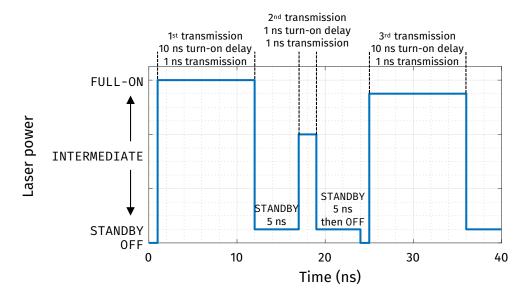

| 8.2         | Example of Dynamic Laser Power Scaling (DLPS) [199] with $t_{\text{idle}} = 5$                             |       |

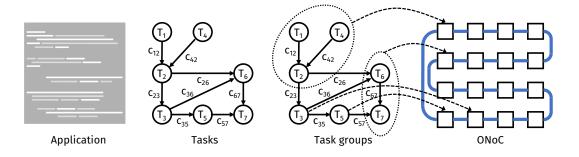

| 8.3         | Illustration of task partition, grouping, and mapping                                                      | 142   |

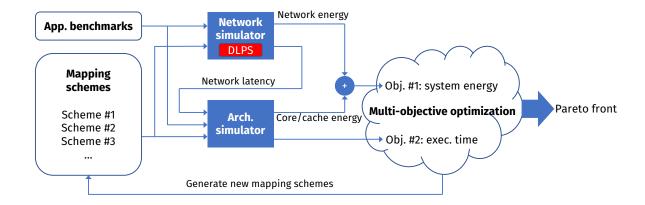

| 8.4         | TMALPS optimization framework                                                                              | 144   |

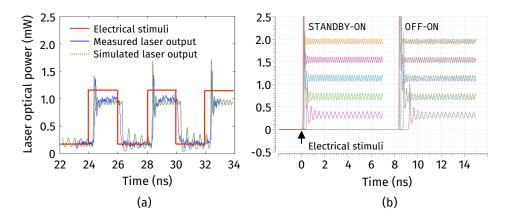

| 8.5         | (a) Laser transient model, and (b) turn-on delay simulation where different                                |       |

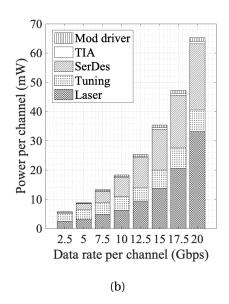

|             | colors correspond to different final states                                                                |       |

| 8.6         | (a) Power models and (b) power vs. data rate for an optical channel                                        | 146   |

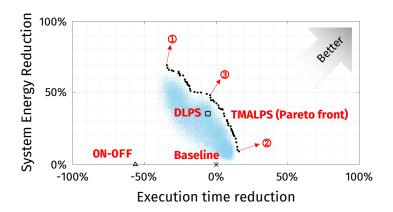

| 8.7         | Pareto front of system energy reduction and execution time reduction for RS-                               |       |

|             | encoder given by our TMALPS framework                                                                      | 149   |

| 8.8         | Task mapping exploration improves DLPS effectiveness by eliminating unfa-                                  |       |

| 0.0         | vorable transmissions.                                                                                     | 150   |

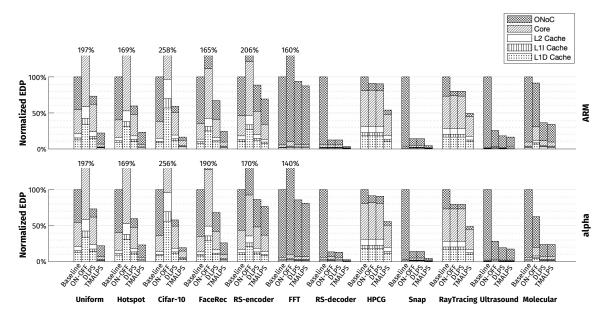

| 8.9         | Evaluation of our TMALPS framework on 12 application benchmarks profiled                                   |       |

|             | under 2 instruction set architectures (ISAs)                                                               | 152   |

| 9.1         | Illustration of a silicon microring–based optical transceiver                                              | 159   |

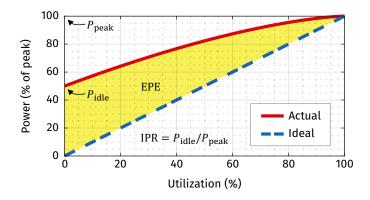

| 9.2  | Illustration of energy proportionality metrics                                              | 162 |

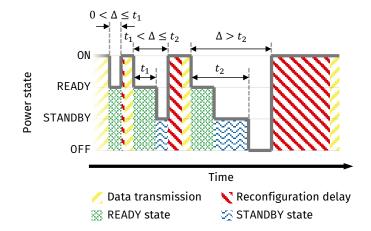

|------|---------------------------------------------------------------------------------------------|-----|

| 9.3  | Power state reconfiguration for idle links (not drawn to scale for illustration             |     |

|      | purpose). $\Delta$ denotes the idle time since the last transmission                        | 164 |

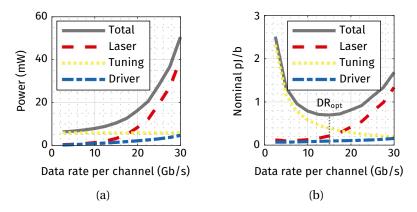

| 9.4  | (a) Power consumption and (b) nominal energy efficiency of an optical link as               |     |

|      | functions of the data rate per channel                                                      | 166 |

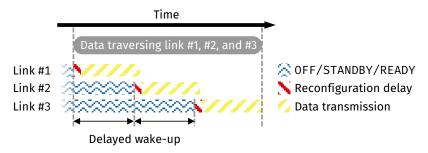

| 9.5  | Illustration of delayed wake-up of downstream links for a network activity                  |     |

|      | traversing multiple links                                                                   | 166 |

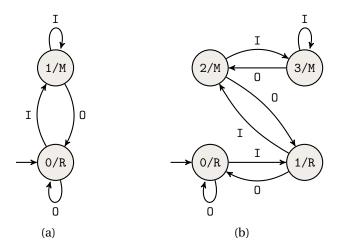

| 9.6  | State diagrams of the one-level idle threshold adjustment mechanism using                   |     |

|      | (a) a 1-bit saturating counter and (b) a 2-bit saturating counter, where I: $\Delta_{last}$ |     |

|      | in-range (Eq. (9.12a)); 0: $\Delta_{last}$ out-of-range (Eq. (9.12b)); M: match operation   |     |

|      | (Eqs. (9.13a) and (9.13b)); and R: reset operation (Eq. (9.14))                             | 170 |

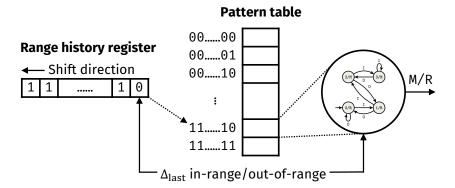

| 9.7  | Illustration of the 2-level idle threshold adjustment mechanism, where M de-                |     |

|      | notes the match operation (Eqs. (9.13a) and (9.13b)) and R denotes the reset                |     |

|      | operation (Eq. (9.14))                                                                      | 171 |

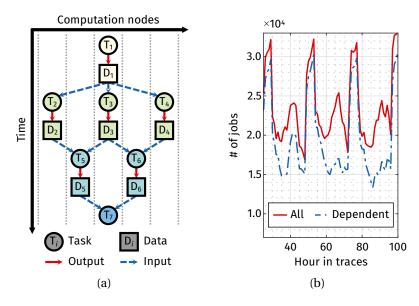

| 9.8  | (a) Directed acyclic graph (DAG) representation of a job containing multi-                  |     |

|      | ple tasks and data dependencies and (b) temporal distribution of jobs in the                |     |

|      | Alibaba traces                                                                              | 172 |

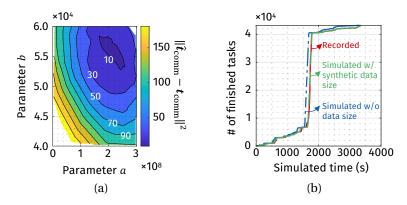

| 9.9  | Data size generation and simulator calibration: (a) finding proper values for               |     |

|      | a and $b$ in Eq. (9.17) by optimizing Eq. (9.18); (b) simulated vs. recorded task           |     |

|      | execution with and without data size information                                            |     |

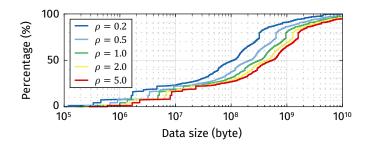

|      | Cumulative distributions of data sizes w.r.t. different values of $\rho$                    | 175 |

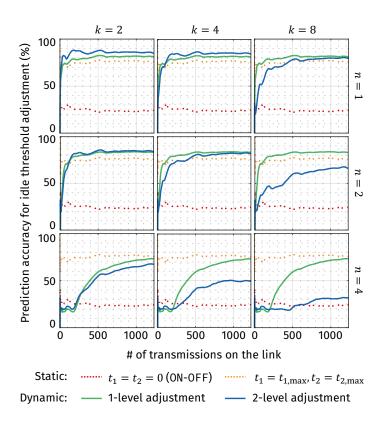

| 9.11 | Prediction accuracy comparison for various idle threshold adjustment mech-                  |     |

|      | anisms and settings                                                                         | 179 |

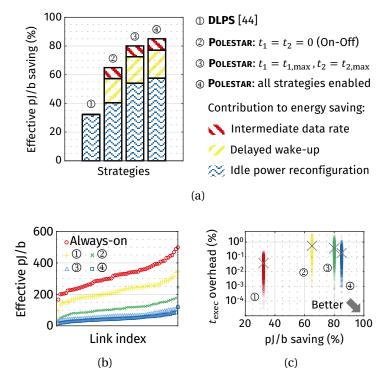

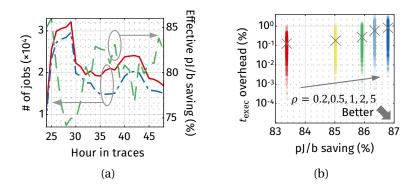

| 9.12 | Case study of POLESTAR for a 64-node Fat-Tree topology: (a) improvement of                  |     |

|      | effective energy efficiency for the network; (b) effective energy efficiency for            |     |

|      | individual links; and (c) trade-off between energy saving and application exe-              |     |

|      | cution time.                                                                                | 182 |

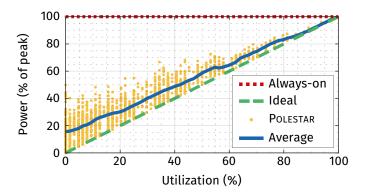

| 9.13 | Energy proportionality curve for the overall network with POLESTAR, averaged                |     |

|      | from the simulated utilization-power pairs                                                  | 184 |

| 9.14 | Evaluation of Polestar strategies for (a) different hours in the traces, showing            |     |

|      | fluctuations of attainable energy saving with workloads; and (b) different val-             |     |

|      | ues for $\rho$ , showing increased energy saving as well as execution time overhead         |     |

|      | with $\rho$                                                                                 | 185 |

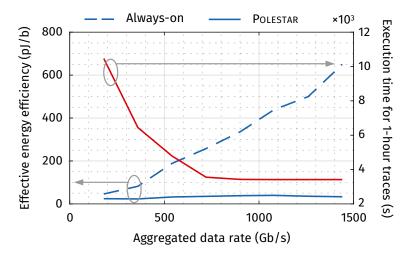

| 9.15 | Impact of the aggregated data rate on network energy efficiency and task exe-               |     |

|      | cution time                                                                                 | 188 |

## **List of Tables**

| Distributed feedback (DFB) laser parameter list                               |

|-------------------------------------------------------------------------------|

| Electroabsorption modulator (EAM) parameter list                              |

| Characteristics of measured and simulated eye diagrams of the transceiver     |

| (TRx) link                                                                    |

| Photodetector (PD) design space and simulated optical modulation ampli-       |

| tude (OMA)                                                                    |

| Summary of spatial variation decomposition                                    |

| Polynomial-time approximation vs. genetic algorithm evaluated on synthetic    |

| data at 7.5 Gb/s per channel for energy-per-bit saving and computation time   |

| per TRx                                                                       |

| Summary of spatial variation decomposition                                    |

| Models and assumptions for link power computation                             |

| Architectural configurations for evaluating TMALPS                            |

| Application benchmarks used for evaluating TMALPS                             |

| Available power states for idle links                                         |

| Power models for optical links                                                |

| Corner cases for the reconfiguration delay                                    |

| Energy improvement of Polestar at four technology corners                     |

| Energy improvement of Polestar for different topologies and network sizes 189 |

|                                                                               |

## **List of Abbreviations**

A

| 11                                       | DVI 5 dynamic voltage and nequency         |

|------------------------------------------|--------------------------------------------|

|                                          | scaling.                                   |

| AC alternating current.                  | <b>DWDM</b> dense wavelength-division      |

| AI artificial intelligence.              | multiplexing.                              |

| AIM Photonics American Institute for     |                                            |

| Manufacturing Integrated                 | E                                          |

| Photonics.                               | EAM alastrochaspration madulator           |

| <b>AWG</b> arrayed waveguide grating.    | <b>EAM</b> electroabsorption modulator.    |

|                                          | <b>EDA</b> electronic design automation.   |

| В                                        | EDP energy-delay product.                  |

| DED 1                                    | <b>EEE</b> effective energy efficiency.    |

| BER bit error rate.                      | EME eigenmode expansion.                   |

| <b>BPM</b> beam-propagation method.      | EO electro-optical.                        |

| C                                        | EPDA electronic-photonic design            |

| C                                        | automation.                                |

| CMOS complementary                       | ER extinction ratio.                       |

| metal-oxide-semiconductor.               | _                                          |

| CMT coupled-mode theory.                 | F                                          |

| CW continuous-wave.                      | <b>FDTD</b> finite-difference time-domain. |

| Cw continuous-wave.                      | <b>FEM</b> finite-element method.          |

| D                                        |                                            |

|                                          | <b>FFT</b> fast Fourier transform.         |

| DAG directed acyclic graph.              | FSR free spectrum range.                   |

| <b>DBR</b> distributed Bragg reflector.  | <b>FWHM</b> full width at half maximum.    |

| DC direct current.                       | G                                          |

| DCN data center network.                 | d                                          |

| <b>DFB</b> distributed feedback.         | GA genetic algorithm.                      |

| <b>DGTD</b> discontinuous Galerkin       | GII gonetie algorianii.                    |

| time-domain.                             | Н                                          |

|                                          |                                            |

| <b>DLPS</b> Dynamic Laser Power Scaling. | <b>HDL</b> hardware description language.  |

| DML directly-modulated laser.            | <b>HPC</b> high-performance computing.     |

| DRC design rule checking.                |                                            |

| <b>DSE</b> design space exploration.     | I                                          |

|                                          | XX                                         |

|                                          |                                            |

**DVFS** dynamic voltage and frequency

**ISA** instruction set architecture. **IV** current-voltage.

#### L

LCA lightwave component analyzer.

LI light-current.

LVS layout versus schematic.

#### M

MPD monitoring photodetector.MPSoC multi-processor system-on-chip.MRR microring resonator.MWMR multiple-reader-multiple-writer.

**MZM** Mach-Zehnder modulator.

#### N

NEE nominal energy efficiency.

NoC network-on-chip.

NP nondeterministic polynomial-time.

#### $\mathbf{0}$

**OMA** optical modulation amplitude. **ONoC** optical network-on-chip. **OOK** on-off keying.

#### P

p.p. percentage point.

P2P point-to-point.

PARAFAC parallel factor.

PCE polynomial chaos expansion.

PCell parameterized cell.

PD photodetector.

PDA photonic design automation.

PDK process design kit.

PIC photonic integrated circuit.

PRBS pseudorandom binary sequence.

PSA Pareto simulated annealing.

**PSD** power spectral density.

#### Q

Q quality factor.QCSE quantum-confined stark effect.QD quantum-dot.QQ-plot quantile-quantile plot.

#### R

RCWA rigorous coupled-wave analysis. RIN relative intensity noise. Rx receiver.

#### S

SA simulated annealing.

SDL schematic-driven layout.

SerDes serializer/deserializer.

SIE surface integral equation.

SNR signal-to-noise ratio.

SOA semiconductor optical amplifier.

SOI silicon-on-insulator.

SPICE Simulation Program with Integrated Circuit Emphasis.

SSM split-step method.

#### Т

TDTW time-domain traveling-wave.

TIA transimpedance amplifier.

TO thermal-optical.

TRx transceiver.

Tx transmitter.

#### $\mathbf{v}$

**VCSEL** vertical-cavity surface-emitting laser. **VIE** volume integral equation. **VP** Virtual Probe.

#### $\mathbf{W}$

**WDM** wavelength-division multiplexing. **WPE** wall-plug efficiency.

## Part I

**Introduction and Literature Review**

## Chapter 1

## Introduction

Optical interconnects enabled by silicon photonics are promising to solve the communication bottleneck in future data center networks (DCNs) and high-performance computing (HPC) systems, a problem with growing prominence due to the rapid expansion of data volume in the era of artificial intelligence (AI). However, the practical application and broad adoption of optical interconnects in short-reach datacom solutions rely on methodologies and techniques for addressing the issues that arise from the increasing complexity of system integration, notably including 1) inadequate support from photonic design automation methodologies, 2) limited effectiveness of techniques for alleviating process variations, and 3) deteriorated energy efficiency under runtime traffic dynamics. This dissertation aims to tackle these issues by solutions proposed at the device, link, and system levels, paving the way to the quality design of variation-aware runtime-reconfigurable optical interconnects with optimized energy efficiency.

By briefly introducing the background of optical interconnects and identifying the challenges posed to their design automation and optimization, this chapter describes the motivation and the scope of this dissertation.

### 1.1 Background of Optical Interconnects

#### 1.1.1 Evolution Toward Shorter Reach

Optical interconnects offer potential benefits of higher bandwidth capacity, lower propagation delay, and greater tolerance of electromagnetic interference compared to electrical ones [1]. As the optical communication technologies continuously evolve over the past few decades to become more energy-efficient, the substitution of traditional electrical interconnects by optical ones gradually unrolls from the long-reach telecom regime to the short-reach datacom regime [2]. As of today, optical interconnects have dominated the data communication solutions above the rack-to-rack level in data centers and HPC systems, as illustrated in Fig. 1.1.

In recent years, the explosive growth of data-intensive AI applications has stimulated advances in computational capability through hardware parallelism and specialization, which further shifts the performance bottleneck of parallel computing infrastructures from computation to communication [3]. For avoiding data-starved computation nodes, the peak

Figure 1.1: Evolution of optical interconnects toward shorter reach (courtesy of Intel Corporation).

Introduction Chapter 1

bandwidth requirement provisioned for DCNs and HPC interconnects has exceeded hundreds of Gb/s, a data rate at which traditional electrical interconnects become uneconomical even for short distances within a rack [4]. On the other hand, short-reach optical links leveraging dense wavelength-division multiplexing (DWDM) have demonstrated an aggregated data rate of 400 Gb/s [5], and technologies toward the Tb/s class are under active investigation [6, 7]. In the foreseeable future, optical interconnects are expected to continue their penetration into the intra-rack regime to provide high-throughput and cost-effective communication solutions at the board-to-board, chip-to-chip, and ultimately core-to-core levels [8].

The evolution of optical interconnects toward shorter reach is inevitably accompanied by the need for addressing greater integration complexity. According to data from [9], the number of devices integrated on a photonic integrated circuit (PIC) grows exponentially over the years, as summarized in Fig. 1.2, often referred to as the Moore's Law for photonics [10]. To this end, silicon photonics has drawn particular attention, among various enabling technologies for optical interconnects, for its cost-effectiveness and scalability achieved by a CMOS-compatible fabrication process [11, 12, 13]. The plasma dispersion effect of the silicon material enables the implementation of electro-optical (EO) modulators in silicon without the need to modify the CMOS process [14]. Although it is hard to implement light emitting or amplifying devices in silicon due to its indirect bandgap, several solutions have emerged using wafer-bonded or directly grown III-V materials on silicon [15, 16].

### 1.1.2 Overview of Optical Devices and Interconnect Architectures

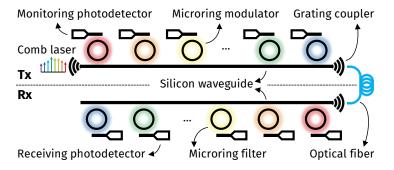

An optical network is a collection of optical links that provide data communication between various processing nodes. The basic building block of an optical network is the optical transceiver (TRx), which, in turn, comprises several essential components, including

Figure 1.2: Number of photonic devices integrated on a PIC over the past decades for three technology platforms of integrated photonics (data from [9]).

lasers, modulators, photodetectors (PDs), and the medium for light propagation, namely waveguides and optical fibers. The adoption of wavelength-division multiplexing (WDM) has become a standard practice for better bandwidth capacity, which transmit multiple wavelengths in the same medium concurrently [17].

From the perspective of laser integration, optical interconnects can be categorized by using either off-chip or on-chip lasers, the latter gaining in popularity for less coupling loss, better energy proportionality, and greater layout flexibility [18]. In terms of the multiplexing architecture, optical interconnects can be distinguished by using either an array of single-wavelength lasers multiplexed by an external multiplexer [19] or a quantum-dot (QD) comb laser that generates a group of evenly-spaced comb lines from a single device output [20,21]. As for the modulation scheme, optical interconnects may opt for either directly-modulated lasers (DMLs) or continuous-wave (CW) lasers modulated by external modulators [22]. Some of the popular modulators implemented in silicon photonics include the electroabsorption modulator (EAM) [23], the Mach-Zehnder modulator (MZM) [24], and the silicon microring modulator [25].

Introduction Chapter 1

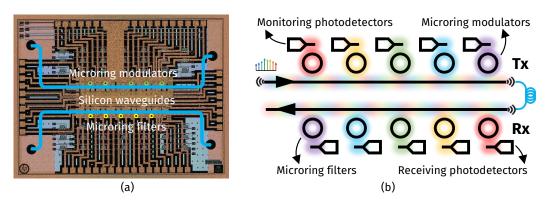

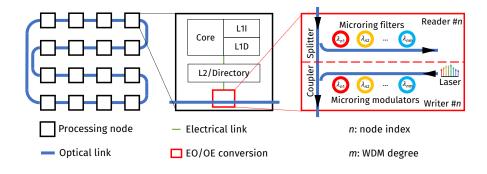

Figure 1.3: Architectural illustration of a silicon microring-based optical transceiver.

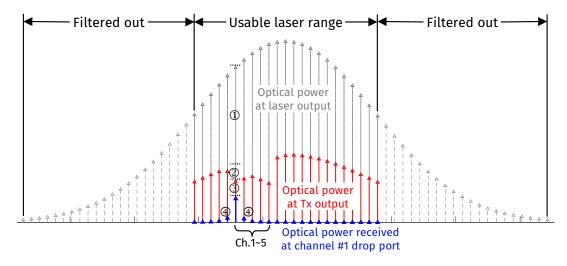

In recent years, optical transceivers based on QD comb lasers and silicon microring resonators have drawn increasing attention for its (de)multiplexer-free architecture that achieves DWDM within compact footprints [26,27,28,29]. Fig. 1.3 illustrates the architecture of a microring-based optical transceiver, showing cascaded microrings deployed alongside a shared waveguide. At the transmitter (Tx) side, each microring modulator modulates a specific wavelength at its resonance. At the receiver (Rx) side, a corresponding microring filter couples the signal out for detection. Optical interconnect architectures based on other types of lasers and modulators have also been reported [30].

### 1.2 Scope of Challenges to be Addressed

Despite the legacy of the well-developed CMOS process that is partially reusable for reducing the production cost of silicon photonics, new challenges still emerge with the increasing number of devices that require close integration, as well as the growing complexity of traffic patterns in modern computing infrastructures, manifesting themselves in the design difficulty and the energy efficiency issues of the optical interconnects.

#### 1.2.1 Compact Modeling and Simulation

The first and fundamental challenge is the insufficient support for the design automation of PICs, especially the compact modeling and simulation methodologies that are indispensable for the co-design of photonic devices and their electronic driving circuitry. According to the 2020 Integrated Photonic Systems Roadmap on electronic-photonic design automation (EPDA) [31], the modeling and simulation of photonic devices and circuits are at the foundation of the EPDA framework, among other essential methodologies like layout and verification of curvilinear structures, collaboratively envisioned by task forces from both academia and industry, as illustrated in Fig. 1.4. Therefore, it is desirable for the modeling and simulation methodologies for optical interconnects to build upon the successful experience of the electronic design automation (EDA) community by incorporating support for photonic features, such as optical power and phase, into existing EDA toolsets. In addition, the development of link- and system-level optimization techniques for optical interconnects also relies on credible models and simulation methodologies validated by actual measurement data of fabricated devices.

Figure 1.4: Design automation methodologies required for designing a PIC, as envisioned by [31], where the modeling and simulation methodologies for photonic devices and circuits are at the foundation.

Introduction Chapter 1

#### 1.2.2 Variation Characterization and Alleviation

Another major challenge posed to optical interconnects stems from their particular vulnerability to process variations. Due to the relatively large ratio between the device size and the operating wavelength, photonic devices are inherently more sensitive to geometry uncertainties than electronic ones, even leveraging the same fabrication process. For wavelength-critical devices, such as microring resonators (MRRs) [25], post-fabrication tuning mechanisms are mandatory for rectifying the deviation of the resonance wavelengths of the MRRs caused by the process variations. In a microring-based optical transceiver as illustrated in Fig. 1.3, each microring is typically fabricated with a resistive thermal tuner that can be electrically heated up to shift its resonance wavelength. As the power consumption for variation rectification can take up over half of that of a point-to-point (P2P) link (as shown in Fig. 1.5) [32], the energy efficiency of optical interconnects strongly depends on the effectiveness of link-level variation alleviation techniques, which, in turn, calls for accurate characterization of the variation patterns of fabricated devices.

Figure 1.5: Energy decomposition of a microring-based optical link reported in [32] showing the shares of the laser, MRR tuning (for variation rectification), electronic drivers, and transimpedance amplifiers (TIAs).

#### 1.2.3 Runtime Power Reconfiguration

A third critical challenge arises for optical interconnects in terms of deteriorated energy efficiency when operating in real-world systems under runtime traffic dynamics. Despite recent advances in device technologies [33, 34, 35] that are pushing the best-case energy efficiency of an individual link toward ~1 pJ/b, the effective energy efficiency of an interconnected network is often worse by orders of magnitude due to traffic dynamics [36], if without proper power reconfiguration for photonic devices at application runtime. Moreover, failure to properly manage the link power during idle or low-utilization periods is devastating to the energy proportionality of the network [37]. As the traffic patterns in modern DCNs and HPC systems are both temporally and spatially non-uniform [38,39], much different from the relatively steady patterns found in long-haul communication [40], the optical links in short-reach application scenarios frequently switch between idle and various utilization levels, intensifying the demand for traffic-adaptive power management. As a result, the need for system-level runtime reconfiguration strategies has become unprecedentedly imminent for developing energy-optimized optical interconnects.

### 1.3 Clarification on Energy Efficiency

As described in Sections 1.2.2 and 1.2.3, both the link-level variation alleviation techniques and the system-level runtime reconfiguration strategies aim to tackle the energy efficiency issues of the optical interconnects, nevertheless, from two different dimensions. This section thus clarifies the terminologies for describing the energy efficiency of optical interconnects.

The energy efficiency of optical interconnects is usually measured in pJ/b. However, in most literature, this metric is computed as mW/(Gb/s), a unit equivalent to pJ/b as 1W = 1J/s, reflecting the power required to attain a target data rate. In this dissertation, we refer

Introduction Chapter 1

to this power-oriented metric as the nominal energy efficiency (NEE) to distinguish it from the effective energy efficiency (EEE), the latter measuring the actual energy consumption associated with data movement.

**Definition 1.1** (nominal energy efficiency, NEE). The nominal energy efficiency describes the power consumption of an individual optical link required to communicate at a target data rate while maintaining the bit error rate (BER) below a given threshold (e.g.,  $10^{-12}$ ).

Thus, reducing the power consumption of various link components, such as the circuitry for variation rectification, is beneficial to the NEE of the optical link.

**Definition 1.2** (effective energy efficiency, EEE). The effective energy efficiency, on the other hand, measures the actual energy consumed by the optical interconnects, which may comprise multiple links, to transfer a total number of bits during the entire timespan of application execution.

In the presence of traffic dynamics, optical links without proper power management may still consume energy when they are idle, causing the EEE of the optical network to be orders of magnitude worse than the NEE of individual links. Therefore, traffic-adaptive runtime reconfiguration strategies are imperative for improving the effective energy efficiency of the optical interconnects.

#### 1.4 Dissertation Outline

For developing energy-optimized optical interconnects with the increasing complexity of system integration, this dissertation is devoted to resolving the three critical needs of Section 1.4 Dissertation Outline

Figure 1.6: Overview of the solutions proposed in this dissertation.

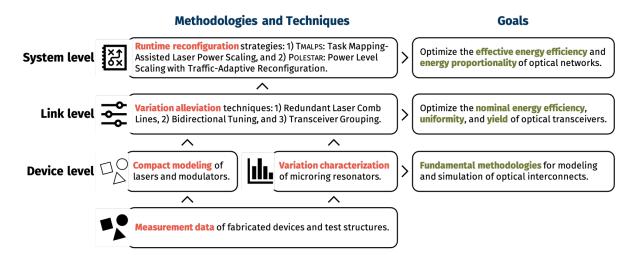

optical interconnects identified in Section 1.2, namely 1) validated methodologies for photonic modeling and simulation, 2) effective techniques for variation characterization and alleviation, and 3) runtime power reconfiguration strategies for traffic adaptability. Fig. 1.6 summarizes the solutions proposed in this dissertation and categorizes them into the device, link, and system levels, detailed in Parts II, III, and IV, respectively.

Part II focuses on device-level EPDA methodologies, including compact models developed for lasers and modulators (Chapter 3) and a novel hierarchical spatial variation model characterized for silicon microring resonators (Chapter 4). Extensively validated by measurement data, the library of developed models enables accurate circuit-level simulation of optical links and variation-aware estimation of the link power budget, serving as the fundamentals of the optimization techniques proposed at the link and system levels.

Part III introduces three link-level techniques for improving the energy efficiency of the optical interconnects under wafer-scale process variations. The three techniques exploit, respectively, 1) sub-channel redundancy of carrier wavelengths (Chapter 5), 2) a combination of electrical and thermal tuning mechanisms (Chapter 6), and 3) optimal mixing and matching of a batch of fabricated transceivers (Chapter 7), achieving significant reductions

Introduction Chapter 1

in the nominal energy efficiency of optical links.

Part IV further proposes two strategies at the system level that improve the effective energy efficiency of optical interconnects under traffic dynamics by reconfiguring the link power at application runtime. The two strategies incorporate assistance from 1) traffic adjustment enabled by task mapping exploration (Chapter 8) and 2) traffic adaptability enabled by traffic prediction (Chapter 9), respectively, and achieve substantial improvements in energy consumption with minimal overhead to application execution time, notably outperforming existing strategies.

#### 1.5 Permissions and Attributions

This dissertation has the following permissions and attributions:

- Chapter 3 contains material from "Compact Modeling for Silicon Photonic Heterogeneously Integrated Circuits," by Zeyu Zhang, Rui Wu, Yuyang Wang, Chong Zhang, Eric J. Stanton, Clint L. Schow, Kwang-Ting Cheng, and John. E. Bowers, which appears in *IEEE/OSA Journal of Lightwave Technology*, vol. 35, no. 14, 2017.