## UC Irvine ICS Technical Reports

**Title** Register allocation issues in embedded code generation

Permalink https://escholarship.org/uc/item/7976z7w0

**Author** Kolson, David J.

Publication Date 1998-06-12

Peer reviewed

## **Register Allocation Issues in Embedded Code** Generation

David J. Kolson

Technical Report UCI-ICS 98-24 Department of Information and Computer Science University of California, Irvine, CA 92697-3425

June 12, 1998

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.)

biology and consolid Letteration of second Welt algebra (1914) COLLED TROPPORT

#### UNIVERSITY OF CALIFORNIA Irvine

H

## Register Allocation Issues in Embedded Code Generation

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

> in Information and Computer Science by David J. Kolson

> > Committee in charge: Professor Alexandru Nicolau, Chair Professor Nikil Dutt Professor Rajesh Gupta

#### ©1998 DAVID JAMES KOLSON ALL RIGHTS RESERVED

The dissertation of David J. Kolson is approved, and is acceptable in quality and form for publication on microfilm:

H

Niuil Alm U

Committee Chair

University of California, Irvine

## Dedication

To my family and friends who supported me through a long education, and believed in me, even when I did not, my deepest and most sincere gratitude.

# Contents

,

| List of         | Illustrations                                           |  |  |  |  |

|-----------------|---------------------------------------------------------|--|--|--|--|

| List of Tables  |                                                         |  |  |  |  |

| Acknowledgement |                                                         |  |  |  |  |

| Curric          | ulum Vitae                                              |  |  |  |  |

| Abstra          | et                                                      |  |  |  |  |

| Chapt           | · · · · · · · · · · · · · · · · · · ·                   |  |  |  |  |

| 1.1             |                                                         |  |  |  |  |

|                 | 1.1.1 Optimizing Compilers                              |  |  |  |  |

|                 | 1.1.2 Parallelizing Compilers                           |  |  |  |  |

|                 | 1.1.3 Embedded Compilers                                |  |  |  |  |

| 1.2             | Motivation for Embedded Compiler Complexity 10          |  |  |  |  |

| 1.3             | Scope of Thesis                                         |  |  |  |  |

| Chapte          | er 2 Related Work 13                                    |  |  |  |  |

| 2.1             | Register Allocation and Assignment                      |  |  |  |  |

|                 | 2.1.1 Graph Coloring                                    |  |  |  |  |

|                 | 2.1.2 Interval Graphs 16                                |  |  |  |  |

|                 | 2.1.3 Optimal Register Allocation                       |  |  |  |  |

|                 | 2.1.4 Register Allocation and Program Transformation 16 |  |  |  |  |

| 2.2             | Memory-Related Transformations                          |  |  |  |  |

| 2.3             | Memory Access Models                                    |  |  |  |  |

| 2.4             | Memory Structure Synthesis                              |  |  |  |  |

| Chapte          | · · · · · · · · · · · · · · · · · · ·                   |  |  |  |  |

| 3.1             | A Parallelizing Compiler                                |  |  |  |  |

| 3.2             | Program Model                                           |  |  |  |  |

| 3.3             | Scheduling                                              |  |  |  |  |

| Chapter 4 Eliminating Redundant Memory Accesses 28 |                                                          |            |

|----------------------------------------------------|----------------------------------------------------------|------------|

| 4.1                                                | Introductory Example                                     | 30         |

| 4.2                                                | Detecting Redundancy                                     | 31         |

|                                                    | 4.2.1 Symbolic Expressions                               | 32         |

|                                                    | 4.2.2 Memory Disambiguation                              | 35         |

| 4.3                                                | Eliminating Redundancy                                   | 36         |

|                                                    | 4.3.1 Removing Invariants                                | 38         |

|                                                    | 4.3.2 Load-After-Load Optimization                       | 40         |

|                                                    | 4.3.3 Load-After-Store Optimization                      | 41         |

|                                                    | 4.3.4 A Note on Move Instructions                        | 42         |

|                                                    | 4.3.5 An Example                                         | 44         |

| 4.4                                                | Effects of Redundancy Elimination on Register Allocation | 45         |

|                                                    | 4.4.1 Examining the Effects of Optimization              | 45         |

|                                                    | 4.4.2 An Enhanced Redundant Elimination Algorithm        | 49         |

| Chapt                                              | er 5 Integrating Program Transformations                 | 54         |

| 5.1                                                | Introductory Example                                     | <b>5</b> 5 |

| 5.2                                                | Overview of Incremental Tree Height Reduction            | 56         |

| 0.2                                                | 5.2.1 Previous Work                                      | 56         |

|                                                    | 5.2.2 Definitions                                        | 58         |

|                                                    | 5.2.3 An Incremental THR Algorithm                       | 58         |

| 5.3                                                | Integrating Transformations                              | 60         |

| 0.0                                                | 5.3.1 The META-Transformation                            | 60         |

|                                                    | 5.3.2 Heuristic META-Transformation                      | 62         |

|                                                    | 5.3.3 An Example                                         | 67         |

| 5.4                                                | Effects of META-Transformation on Register Allocation    | 69         |

|                                                    | 5.4.1 Examining the Effects of Optimization              | 69         |

|                                                    | 5.4.2 An Enhanced META-Transformation                    | 75         |

|                                                    |                                                          |            |

| Chapte                                             |                                                          | 77         |

| 6.1                                                |                                                          | 79         |

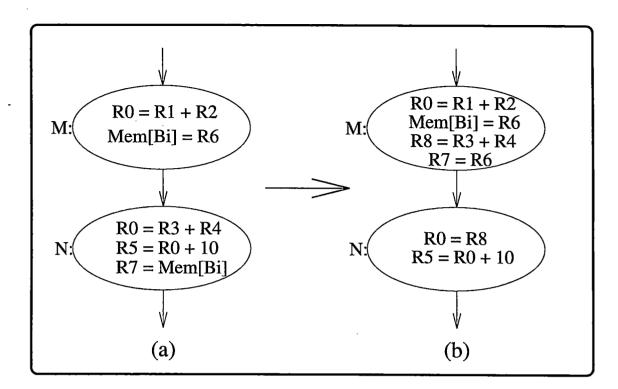

| 6.2                                                | Eliminating Copy Instructions                            | 81         |

|                                                    | 6.2.1 Definitions                                        | 83         |

|                                                    | 6.2.2 An Algorithm for Copy Elimination                  | 83         |

|                                                    | 6.2.3 Determining Minimal Number of Unrollings           | 90         |

|                                                    | 6.2.4 Heuristic Copy Elimination                         | 91         |

| <u> </u>                                           | 6.2.5 An Example                                         | 92         |

| 6.3                                                | Effects of Copy Elimination on Register Allocation       | 95         |

|                                                    | 6.3.1 Examining the Effects of Optimization              | 96         |

|                                                    | 6.3.2 An Enhanced Copy Elimination Algorithm             | 99         |

ļ

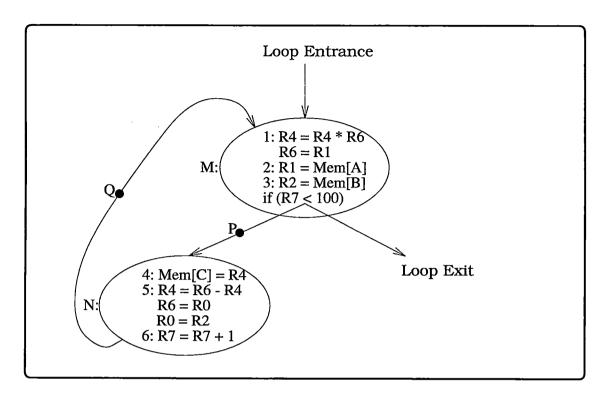

| $\mathbf{Chapt}$ | er 7 Allocating Registers to Loops                           |

|------------------|--------------------------------------------------------------|

| 7.1              | Optimal Allocation in Basic Blocks                           |

| 7.2              | Extending the Basic Block Algorithm to Loops                 |

|                  | 7.2.1 Terminology                                            |

|                  | 7.2.2 An Algorithm for Loop Register Allocation              |

|                  | 7.2.3 Heuristic Pruning                                      |

| 7.3              | Convergence and Optimality of the Loop Algorithm             |

|                  | 7.3.1 Convergence                                            |

|                  | 7.3.2 Optimality                                             |

| 7.4              | Extending the Loop Algorithm to Distributed Memories 114     |

|                  | 7.4.1 Adding Register Classes to the Model                   |

|                  | 7.4.2 Extension to Special-Purpose Registers                 |

|                  | 7.4.3 Extension to Multiple Register Files                   |

| 7.5              | Comparing Loop Register Allocation with Other Approaches 120 |

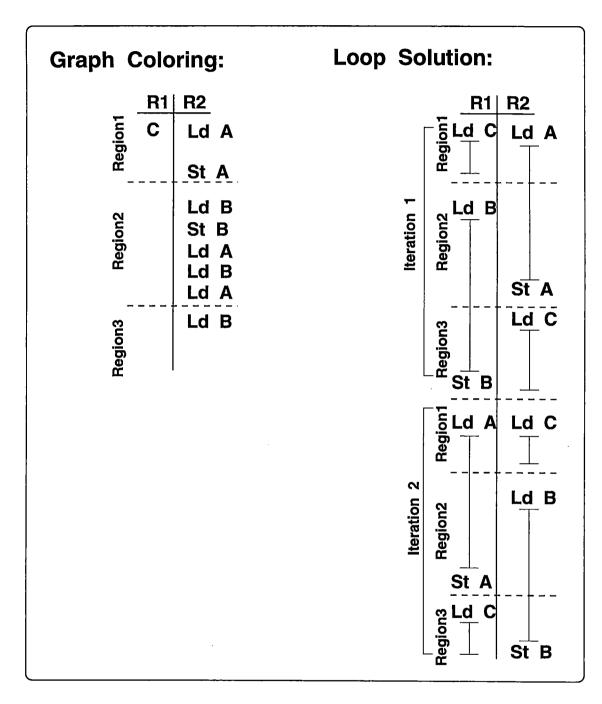

|                  | 7.5.1 Comparison with Graph Coloring                         |

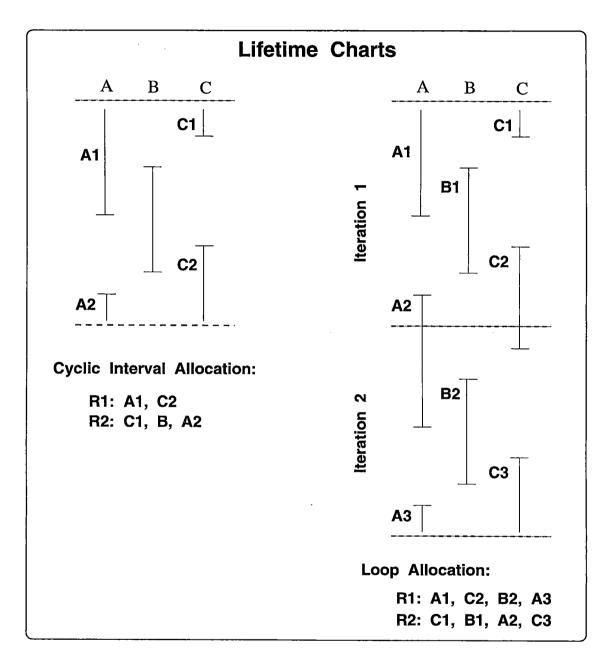

|                  | 7.5.2 Comparison with Cyclic Interval Graphs 122             |

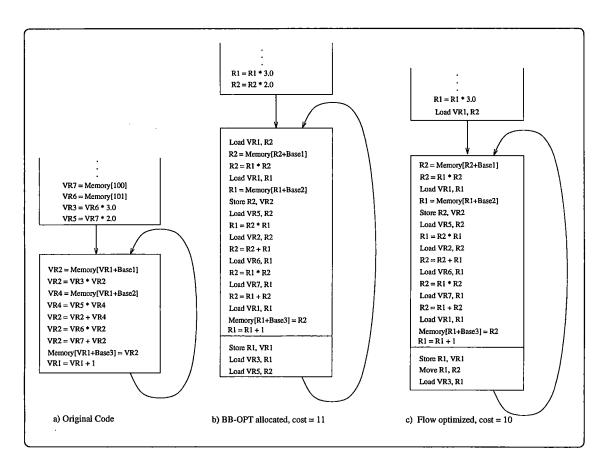

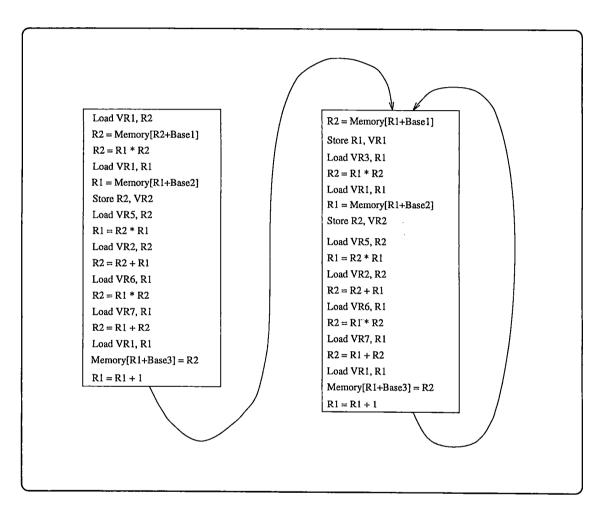

|                  | 7.5.3 Comparison with the Basic Block Strategy               |

|                  |                                                              |

| Chapt            | 1                                                            |

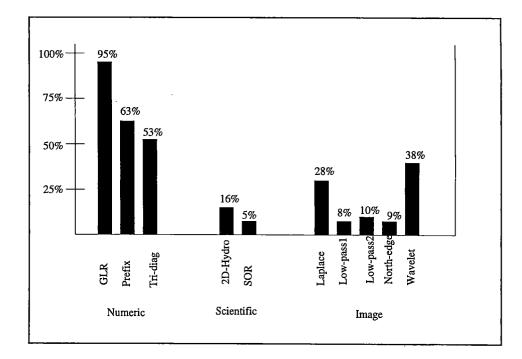

| 8.1              | Measuring Improvement                                        |

| 8.2              | Experimental Set-up                                          |

| 8.3              | Eliminating Redundancy                                       |

|                  | 8.3.1 Observed Results                                       |

| ~ (              | 8.3.2 Analysis                                               |

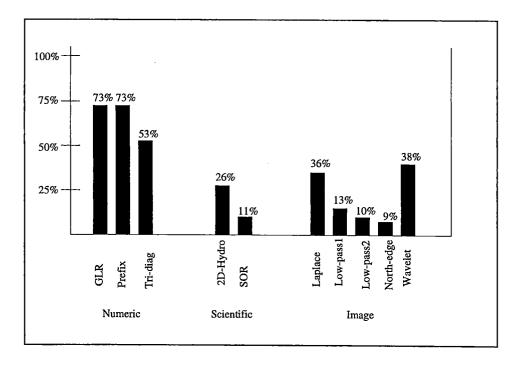

| 8.4              | Integrating Program Transformations                          |

|                  | 8.4.1 Observed Results                                       |

| ~ ~              | 8.4.2 Analysis                                               |

| 8.5              | Copy Elimination                                             |

|                  | 8.5.1 Observed Results                                       |

|                  | 8.5.2 Analysis                                               |

| 8.6              | Combining Techniques                                         |

|                  | 8.6.1 Observed Results                                       |

| 0 7              | 8.6.2 Analysis                                               |

| 8.7              | Allocating Registers to Loops                                |

|                  | 8.7.1 Experimentation with a Consolidated Model              |

| 00               | 8.7.2 Experimentation with Distributed Register Files 159    |

| 8.8              | Summary of Results                                           |

| Chapte           | er 9 Conclusions                                             |

# Illustrations

| $1.1 \\ 1.2 \\ 1.3 \\ 1.4$                                                  | Typical embedded system architecture.2Phases of an optimizing compiler.6Phases of a parallelizing compiler.9Available register organization.10                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c} 3.1\\ 3.2\end{array}$                                     | Code Generation process.23Datapath for microcode macro example.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

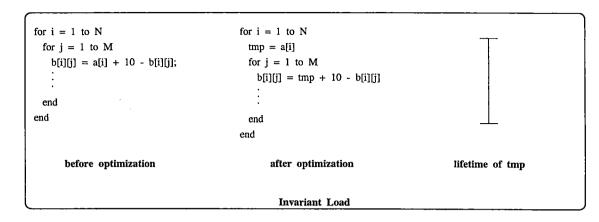

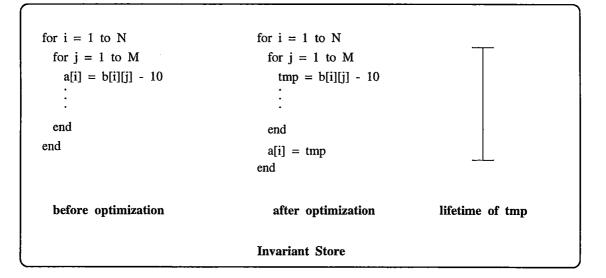

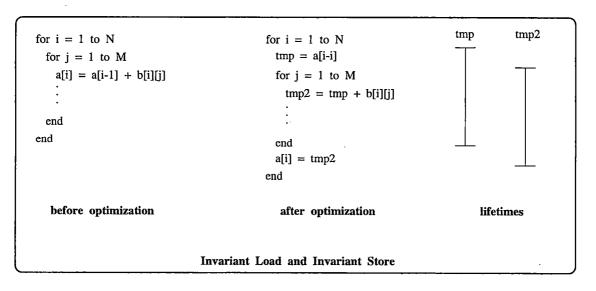

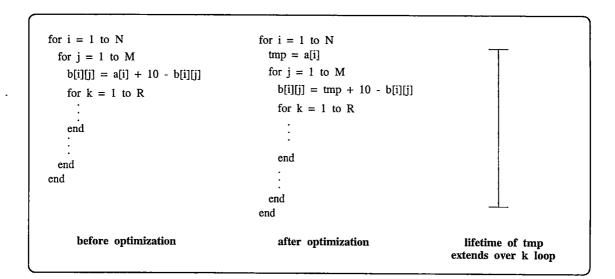

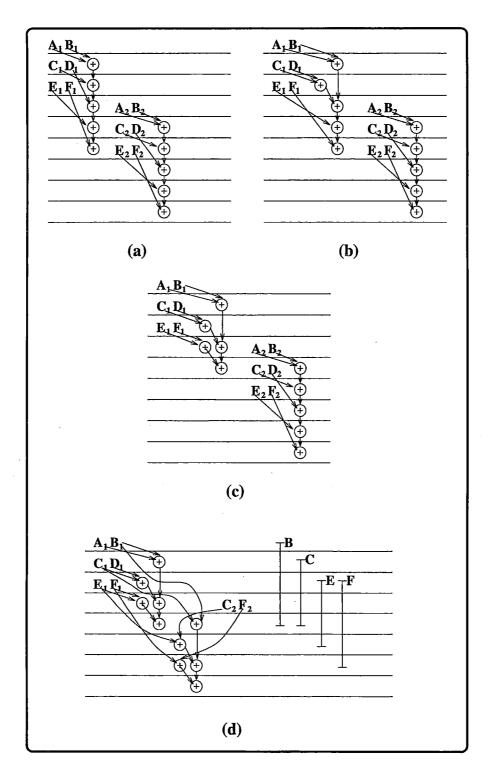

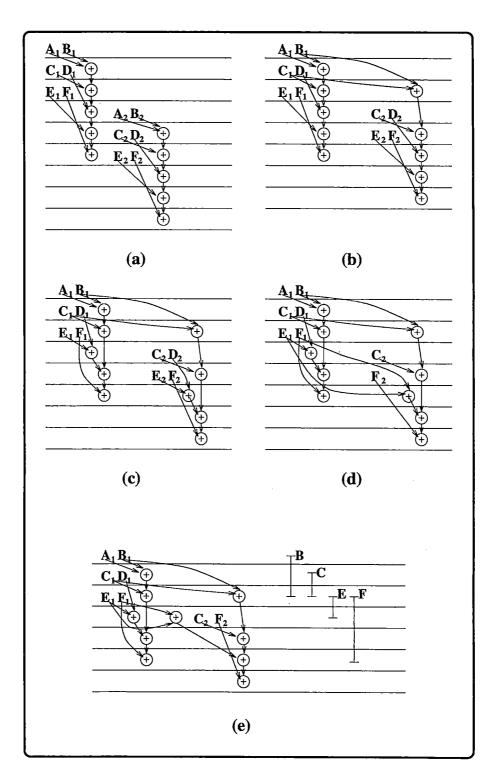

| 4.13                                                                        | Removing redundant memory traffic.29An algorithm to build symbolic expressions.33Symbolic expression example.34An algorithm for redundant elimination.37An algorithm for loop invariant removal.38An algorithm for the load-after-load optimization.40An algorithm for the load-after-store optimization.43Redundancy elimination example.44Invariant load removal.47Invariant store removal.48Multiple effects of invariant removal.49An algorithm for the load-after-store heuristic.50An algorithm for the load-after-store heuristic.50 |

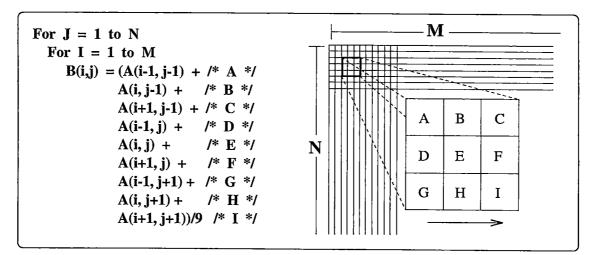

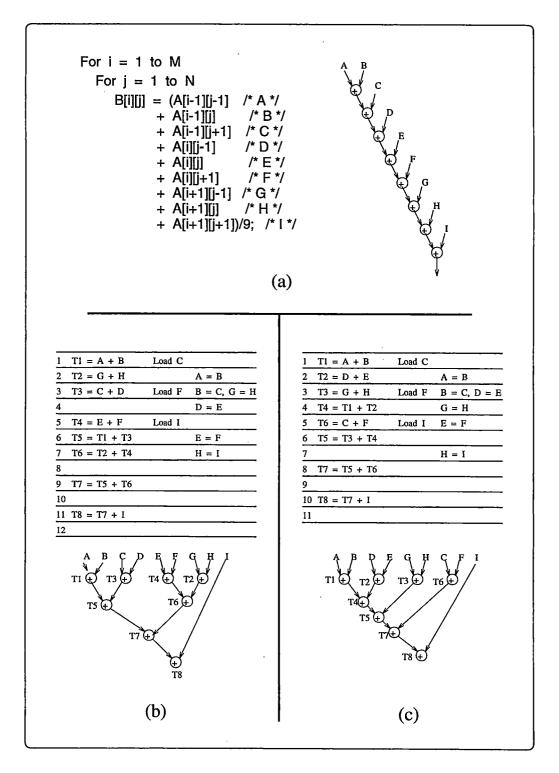

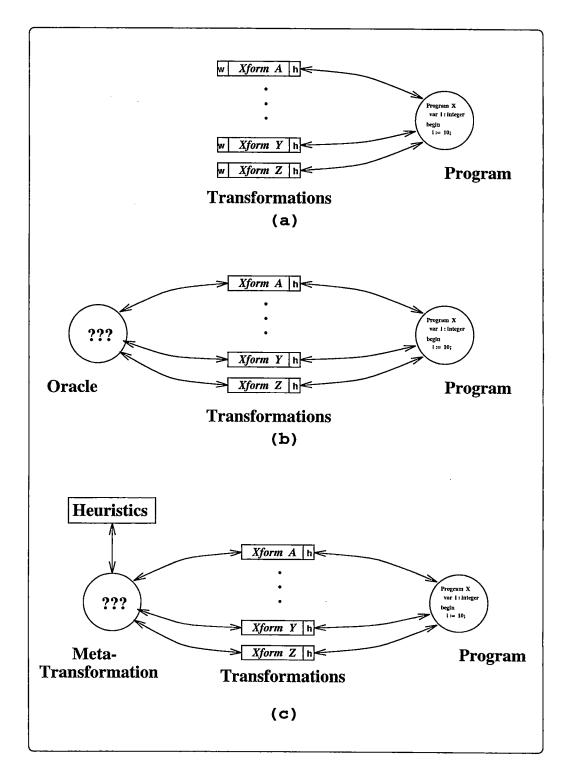

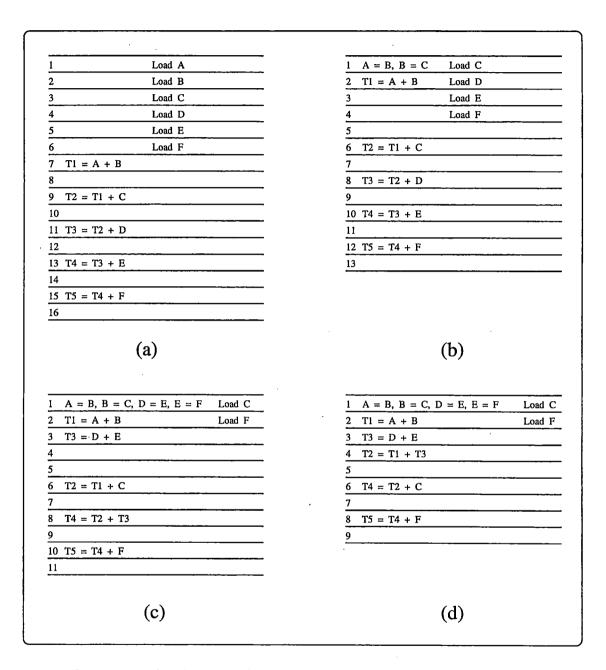

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11 | Example image convolution code.55Schedules for tree height reduced graphs.57Main procedure for incremental THR algorithm.59Methods of approach.61An algorithm for determining removal candidates.65Algorithm for propagating redundancy information.66The META-Transformation.68Application of META-Transformation on low-pass filter.70Pseudo code for an incremental scheduler.71Traditional scheduling approach.73                                                                                                                       |

| 6.1                                                                         | Introducing copy instructions into the code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

· · ·

| 6.2  | Loop code with copy instructions                                  | 80  |

|------|-------------------------------------------------------------------|-----|

| 6.3  | Unrolling loop code to eliminate copies                           | 82  |

| 6.4  | An algorithm for copy elimination.                                | 84  |

| 6.5  | An algorithm for computing register mappings                      | 87  |

| 6.6  | An algorithm for removing copies and updating register usages     | 89  |

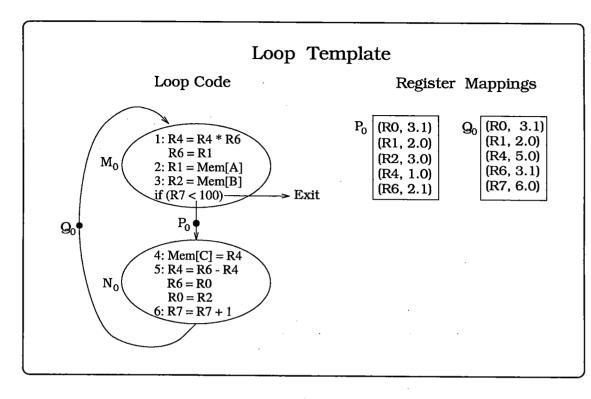

| 6.7  | Loop template for example.                                        | 92  |

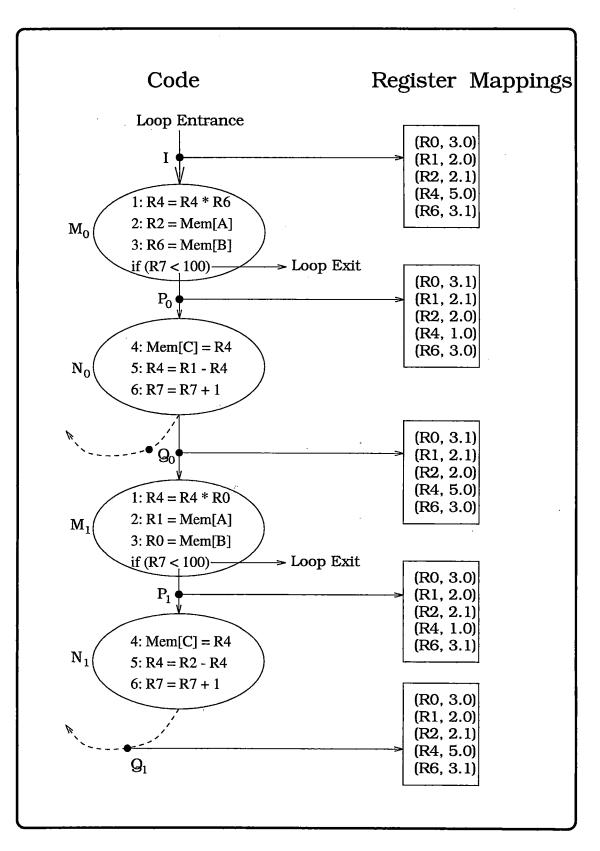

| 6.8  | Unrolling loop code to eliminate copies                           | 93  |

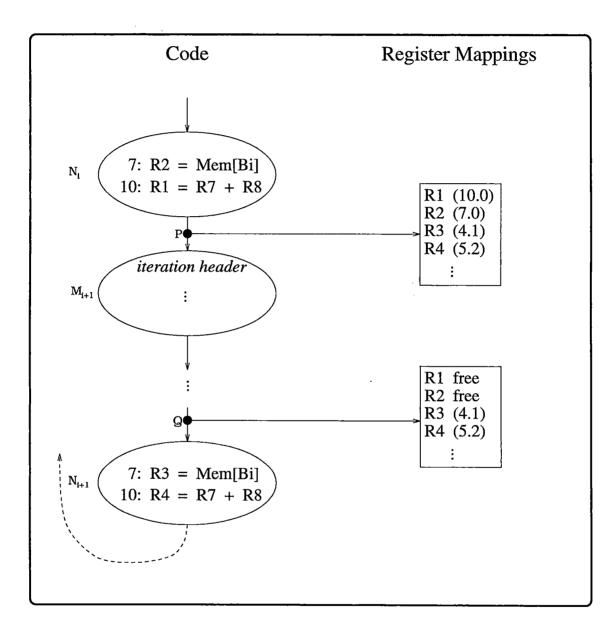

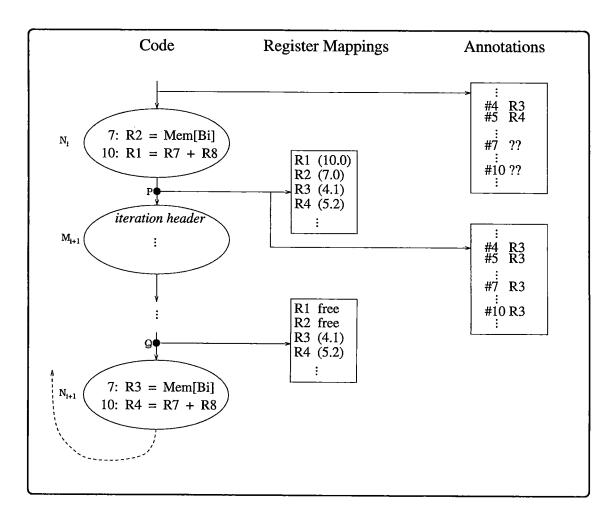

| 6.9  | Example code and register mappings during copy elimination        | 98  |

| 6.10 | Example code and register mappings with annotations               | 100 |

|      |                                                                   |     |

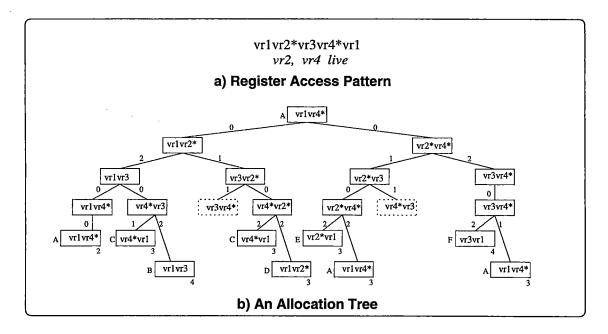

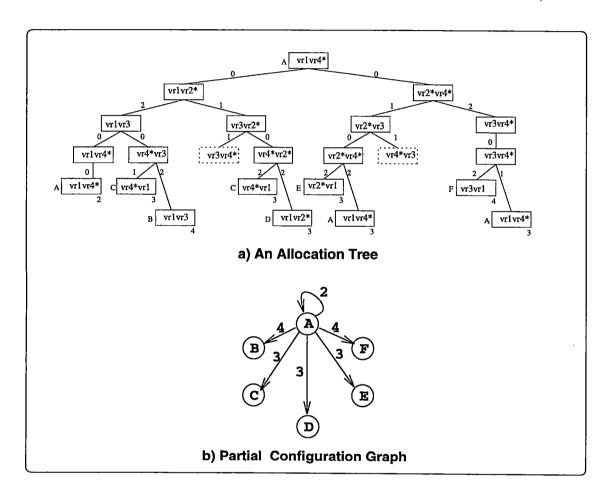

| 7.1  | An optimal register assignment algorithm for basic blocks.        |     |

| 7.2  | Building an assignment tree                                       |     |

| 7.3  | A loop register assignment algorithm.                             |     |

| 7.4  | Building a configuration graph from the assignment trees          |     |

| 7.5  | An algorithm to derive register classes                           | 115 |

| 7.6  | Extending BB-Opt to special-purpose registers                     | 117 |

| 7.7  | Extending BB-Opt to multiple register files                       | 119 |

| 7.8  | Example for graph coloring comparison.                            |     |

| 7.9  | Solution for graph coloring comparison                            |     |

| 7.10 | Example for cyclic interval graph coloring comparison.            |     |

| 7.11 | A loop basic block allocated with BB-Opt.                         |     |

| 7.12 | A Loop-Opt allocated loop basic block with cost nine              | 128 |

|      |                                                                   |     |

| 8.1  | Architecture model for experimentation.                           |     |

| 8.2  | •••                                                               | 138 |

| 8.3  | Average performance improvement with functional unit constraints. |     |

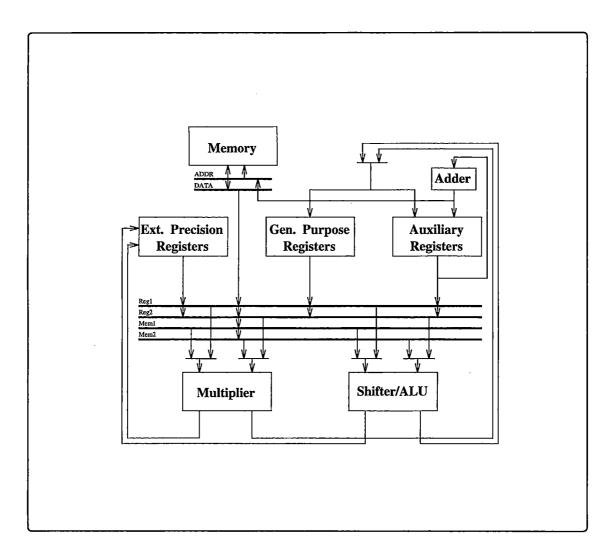

| 8.4  | A simplified view of the TMX320C44                                | 161 |

H

# Tables

| 6.1  | Register mappings for the code of Figure 6.2                      |

|------|-------------------------------------------------------------------|

| 8.1  | A description of the redundancy elimination benchmark suite 133   |

| 8.2  | Statistics for the redundancy elimination benchmark suite 134     |

| 8.3  | Results of experimentation with redundant elimination 135         |

| 8.4  | Results of experimentation with redundant elimination (con't) 136 |

| 8.5  | A description of the META-Transformation benchmark set 140        |

| 8.6  | Results of experimentation with META-Transformation               |

| 8.7  | A description of the copy elimination benchmark suite             |

| 8.8  | Results of experimentation with copy elimination                  |

| 8.9  | Results of experimentation with heuristic copy elimination 146    |

| 8.10 | A description of the benchmark suite for all transformations 147  |

| 8.11 | Remaining number of copy instructions after parallelization 147   |

| 8.12 | Results of experimentation with all transformations               |

| 8.13 | A description of the benchmark suite for register allocation 150  |

| 8.14 | Spill costs for the two methods of matching register maps 152     |

| 8.15 | Results of loop register allocation algorithm                     |

| 8.16 | Results of heuristic width restriction only                       |

| 8.17 | Results of heuristic depth of two                                 |

| 8.18 | Results of heuristic depth of three                               |

| 8.19 | Comparison of results between GCC and heuristic Loop-Opt 160      |

|      | Execution times of the various methods                            |

|      | Basic block optimal vs. Loop optimal for the TMX320C44 163        |

|      | Comparison of loop assignments for the TMX320C44                  |

|      | Comparison of loop code sizes for the TMX320C44                   |

| 8.24 | Comparison of running times for the TMX320C44.                    |

## Acknowledgement

In looking back over the past years of graduate study, a number of people have played an influential role on my development as a person and researcher. Here I wish to express my thanks, but these words alone cannot express the gratitude, nor the admiration that I hold for them.

Ħ

I would like to thank my advisor, Professor Alexandru Nicolau, who spent countless hours with me in enlightening and thought-provoking discussion. His insight and direction provided the focus and impetus for me to conduct high-quality research. His input and constructive criticism on written works and presentations greatly improved my communication skills.

I would like to thank Professor Nikil Dutt who has served as a co-advisor over the past years. He provided a different point-of-view that greatly improved the content of many manuscripts and research goals. His input and critique were also instrumental in the development of my presentation and communication skills.

I would like to thank Professor Rajesh Gupta for serving on my doctoral committee and providing valuable comments on earlier revisions of this manuscript.

I would like to thank Professor Daniel Gajski for serving on my doctoral candidacy committee and providing input over the years on my research.

I would like to thank Professor Tatsuya Suda for encouraging me to pursue a graduate career.

And, especially, I would like to thank my Mother and Father, my sister Kristin, my high-school friends, Albert, David, Ed and Steve, my lab colleagues, Dr. Joseph Hummel and Dr. Steven Novack, and the countless friends who were always there for me and whose support and encouragement helped me through the darkest times.

# Curriculum Vitae

| 1990      | B.S. in Information and Computer Science, University of<br>California, Irvine, Magna Cum Laude, Phi Beta Kappa                                                                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1990–1992 | Teaching Assistant, Department of Information and Com-<br>puter Science, University of California, Irvine                                                                                |

| 1993      | M.S. in Information and Computer Science, University of California, Irvine                                                                                                               |

| 1990–1998 | Graduate Student Researcher, Computer Systems Design<br>(CSD) Group, UCI-VLIW Compiler project, Department<br>of Information and Computer Science, University of Cali-<br>fornia, Irvine |

| 1998      | Ph.D. in Information and Computer Science, University of California, Irvine                                                                                                              |

Dissertation: Register Allocation Issues in Embedded Code Generation

#### Publications

- Kolson, D. J., Nicolau, A. and Dutt, N., Elimination of Redundant Memory Traffic in High-Level Synthesis, Transactions on Computer-Aided Design of Integrated Circuits and Systems (T-CAD), November, 1996.

- Kolson, D. J., Nicolau, A., Dutt, N. and Kennedy, K., Optimal Register Assignment to Loops for Embedded Code Generation, Transactions on Design Automation of Electronic Systems (TODAES), April, 1996.

- Kolson, D. J., Nicolau, A., Dutt, N. and Kennedy, K., A Method for Register Allocation to Loops in Multiple Register File Architectures, *IEEE 10th International Parallel Processing* Symposium (IPPS), April, 1996.

- Kolson, D. J., Nicolau, A., Dutt, N. and Kennedy, K., Optimal Register Assignment to Loops for Embedded Code Generation, IEEE 8th International Symposium on System Synthesis (ISSS), September, 1995.

- Kolson, D. J., Nicolau, A. and Dutt, N., Integrating Program Transformations in the Memory-Based Synthesis of Image and Video Algorithms, *IEEE International Conference on Computer-Aided Design (ICCAD)*, November, 1994.

- Kolson, D. J., Nicolau, A. and Dutt, N., Minimization of Memory Traffic in High-Level Synthesis, ACM/IEEE 30th Design Automation Conference (DAC), June, 1994.

- Kolson, D. J., Nicolau, A. and Dutt, N., Ultra Fine-Grain Template-Driven Synthesis, IEEE 7th International Conference on VLSI Design, January, 1994.

## Abstract of the Dissertation

# Register Allocation Issues in Embedded Code Generation by

David J. Kolson

Doctor of Philosophy in Information and Computer Science University of California, Irvine, 1998 Professor Alexandru Nicolau, Chair

In conventional compilation, register allocation—the mapping of program variables to the registers of the target architecture—plays an important role in the performance of application code. In particular, for load/store architectures, good register allocation is exceedingly important as all operands to instructions, in this type of architecture, must be contained within the register set.

Typical processors selected as the core unit or core processor for an embedded system closely resemble the load/store or RISC-type of architecture, and, thus, conventional register allocation techniques are applicable in the generation of code for an embedded processor. However, architectural features of the core processor, features designed to reduce core size/cost and/or are specific to the target application area for improved performance—such as disjoint register files and/or requirements that operands to particular instructions reside in specialized registers—complicate the register allocation process. This, coupled with the time-sensitive nature of typical embedded applications necessitates high-quality register allocation.

This thesis demonstrates that beyond the specific task of register allocation, there are subtle issues related to register allocation that must be addressed in order to generate high quality code for an embedded application. Issues

xiii

investigated relate to promotion of data items from secondary memory to primary memory, global guiding of transformation interaction, integrating register allocation and instruction scheduling and optimal allocation to loops.

This thesis presents a technique which eliminates redundancies found in array accessing over iterations of a loop. Essentially this technique allocates a register to an array data item that is used frequently over a loop or within a window of iterations of a loop, thus promoting it from the secondary memory to the primary memory.

Transformation interaction within a parallelizing compiler has been studied relatively little, however, it remains an important issue in generating high quality code. This thesis presents a paradigm for integrating transformations so that transformations are applied based upon global knowledge instead of local knowledge, leading to better resource/register allocation and the development of better scheduling/allocation heuristics.

One strategy which integrates register allocation and instruction scheduling performs register allocation "on-the-fly" by a technique called renaming. This has the disadvantage of adding many copy instructions to the code which adversely affects performance and this thesis presents a post-scheduling technique to unroll loop code and re-allocate registers to eliminate these copy instructions.

Finally, the issue of optimal register allocation to loops is addressed. Register allocation has been extensively studied with proposed solutions being heuristic in nature. However, for embedded applications which contain time-critical loops and/or loop kernels, an optimal allocation is necessary. This thesis presents a technique for optimal allocation of registers to loop code.

# <u>Chapter 1</u> Introduction

One of the goals in the field of Design Automation is the synthesis of a hardware solution from a problem specification. Typically, the problem is formulated as a behavioral specification in which the desired actions of the hardware are detailed from an algorithmic standpoint. Various high-level languages, such as VHDL and HardwareC, exist for expressing behaviors. Through the process of *High-Level Synthesis* a behavior is translated into a hardware solution in some format suitable for implementation [22, 35, 81].

Because it can be too costly and time consuming to completely re-synthesize hardware when slight behavioral changes are made, the sub-area of Hardware/Software Co-Design seeks to partition a given behavior into hardware and software components. The hope is that, for a given application domain, common characteristics or time-critical aspects of the applications can be extracted and implemented in hardware while the software component implements the various differences in the applications and allows for future refinement.

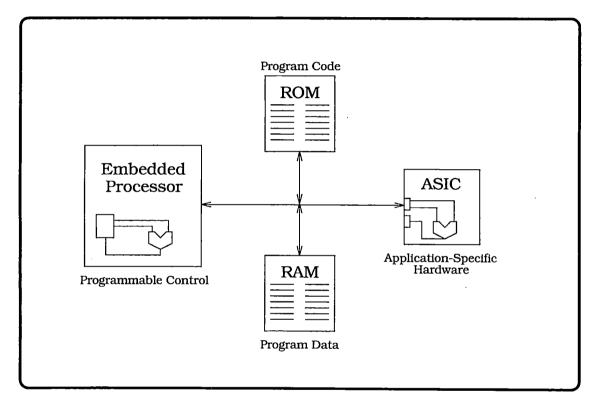

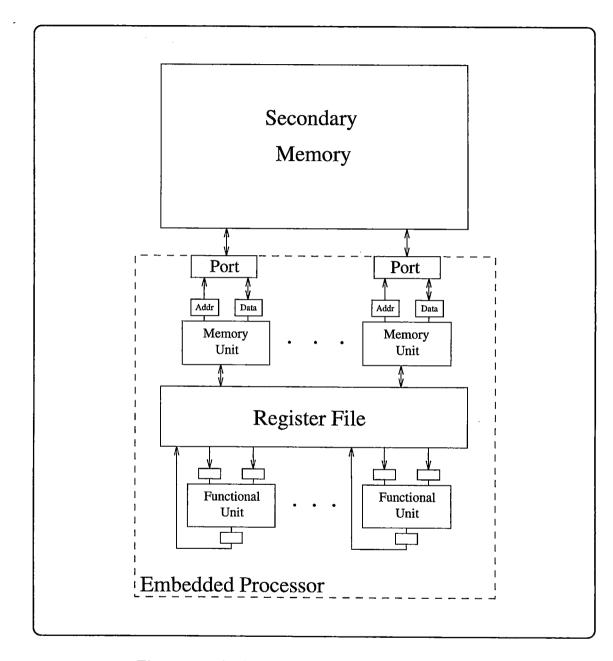

This type of architecture is depicted in Figure 1.1. This architecture integrates a programmable component, one or more specialized hardware components, a ROM (to store the sequence of instructions executed by the programmable component) and a memory (for storage, as necessary), has been termed an *embedded system*. Depending upon the required complexity of the system, various solutions exist for the programmable component of an embedded system. Solutions ranging from:

Figure 1.1: Typical embedded system architecture.

- micro-processors

- processor cores (a "stripped down" version of a given processor in which a subset of the processor's instruction set is implemented and/or the datapath bit-width is reduced).

- digital signal processors (DSPs) (processors with explicit instructions for supporting digital signal processing)

are all available. Typically, these processor's architecture's closely resemble the load/store or RISC-type of architecture where operands to instructions must be contained within the register set for execution of that instruction. Transfers of values between memory and the register set are explicitly performed by load and store instructions as necessary.

The process of "synthesizing" the instruction sequence corresponding to the software partition of the behavior (that which is to be executed by the embedded processor) is referred to as *code generation* and is closely related to the conventional task of compilation. One integral phase in the compilation process is that of *register allocation*—the mapping of program variables to the available registers of the target architecture.

Although good register allocation is exceedingly important as, in a load/store-type of architecture all operands to instructions must be in registers, this thesis demonstrates that there are subtle issues related to register allocation that must be addressed in order to generate high-quality code for a given application.

## 1.1 Code Generation and the Role of Register Allocation

Generating code for the type of system discussed previously involves the translation of application code written in a high-level language into the native instruction set (the machine language) of the programmable component.

However, because the target programmable architecture is flexible in its ability to contain some or all of the available application-specific datapaths, traditional compiler techniques must be refined to maximally utilize that provided flexibility and achieve high code performance.

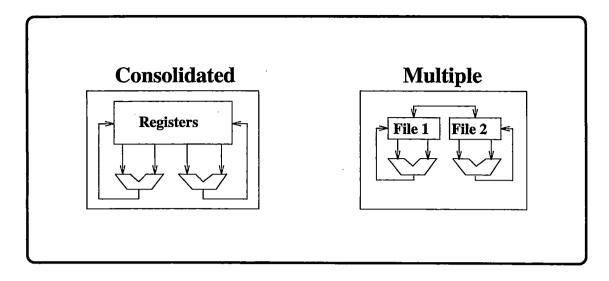

Previously, little investigation has been made into standard compilation techniques which focus on the implications of a partitioned registers set, as the traditional viewpoint is one of a consolidated register file with equal (all registers in the register set may be accessed at any time) and uniform (any register can be used as any operand of an instruction) access to the contained registers.

In contrast, an embedded processor may have the available registers partitioned into multiple memories and/or scattered singly throughout the architecture with some registers having restricted or specialized uses. The placement of data values then becomes an issue as certain instructions may require data in specific registers. Further, this may be complicated by data necessary in one register or register set for one instruction and then necessary in a different register or register set for some later instruction.

Below, the process of code generation is briefly reviewed in optimizing compilers, parallelizing compilers and embedded compilers and the role played by register allocation is noted.

#### **1.1.1 Optimizing Compilers**

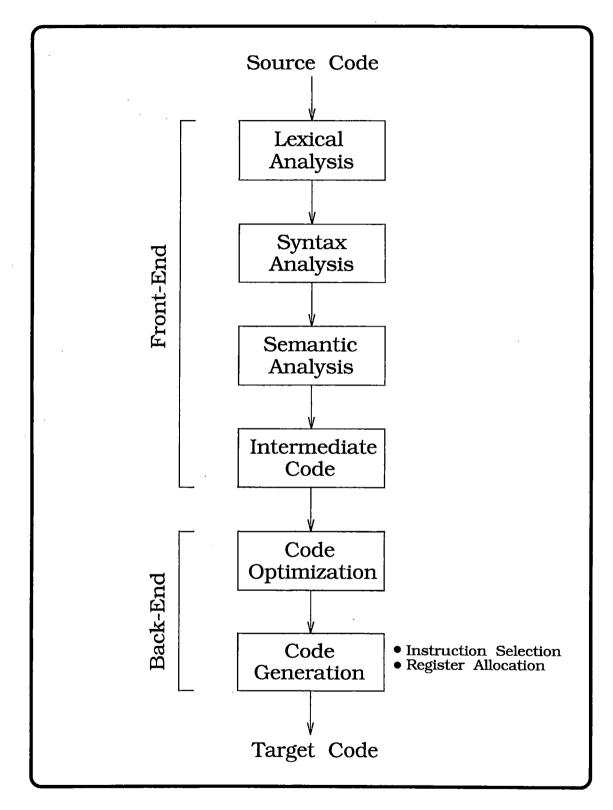

Classically, an optimizing compiler is divided into two main modules: the *front-end* and the *back-end* and is pictured in Figure 1.2. Traditionally, the front-end handles the language-specific details of the compiler; it parses the input (source) language (lexical analysis), determines if any syntax errors are present (syntax analysis), determines if variables, expressions, function calls, etc., are used correctly (semantic analysis), and finally, translates the input code into an intermediate form (intermediate code generation). The back-end, on the other hand, handles the machine-dependent aspects of the compiler; it performs

optimization<sup>1</sup> on the intermediate code (code optimization) and then generates instructions native to the target machine from the intermediate representation (code generation).

The influential view proposed by Backus [4] in the context of allocating index registers and Cocke [26] in the development of the PL.8 compiler, is to separate the tasks of code optimization and register allocation as this allows code optimization to proceed in a relatively simple manner and removes the complications arising from dealing with limited resources (registers). Also, optimizations could then be formulated and implemented in a general manner without the instruction set and register usages found in a particular architecture influencing development.

Thus, the tasks of instruction selection and register allocation are performed within the code generation phase. Instruction selection generates native instructions for the target machine from the internal intermediate representation. Register allocation performs mapping of the variables and temporaries to the registers of the target machine. When more live values than registers are present, *spill code*, explicit transfers of values between memory and the register set is necessary. Traditionally, the goal of the register allocator is to minimize the amount of spill code generated.

Typically, the target machine of an optimizing compiler is sequential in nature. That is, there is single flow-of-control and only one instruction may be issued per machine cycle. The register allocation produced by an optimizing compiler for a sequential architecture often exhibits heavy register re-use as during the instruction selection task, the instructions mapped to the various operators in the expression trees seek to evaluate the expressions generating as few temporaries as possible. This high re-use is a result of mapping those temporaries, whose lifetimes are short, to the available registers. This serves to reduce the amount of spill code produced for a sequential architecture.

<sup>&</sup>lt;sup>1</sup>Although not all code optimizations are necessarily specific to the particular architecture, typically all optimizations are grouped together into one module as optimizations which are machine-specific create opportunities for other optimizations to apply.

Figure 1.2: Phases of an optimizing compiler.

#### 1.1.2 Parallelizing Compilers

To increase the throughput of a sequential processor, two methods have been investigated and implemented: *pipelining* and *parallelism*. Pipelining divides a functional unit into a series of sub-units, while parallelism increases the number of functional units present in the architecture. In order to exploit the peak performance of architectures with functional pipelining and/or parallelism, a compiler must expose and exploit the parallelism inherent in an application as instructions independent of one another are necessary for issue bandwidth.

Exposing and exploiting parallelism are the responsibilities of the *code scheduler*. In a parallelizing compiler, optimizations and transformations are typically applied during scheduling so that their effects on the code are exploited. In fact, many transformations are designed to increase the available parallelism.

However, in order to schedule code, to map instructions in the native instruction set to the functional resources of the target architecture, the phase of instruction selection is required prior to scheduling. This also implies that a register allocation phase is necessary prior to instruction scheduling as knowledge of the location of instruction operands and the resources (functional as well as register) required by an instruction is essential.

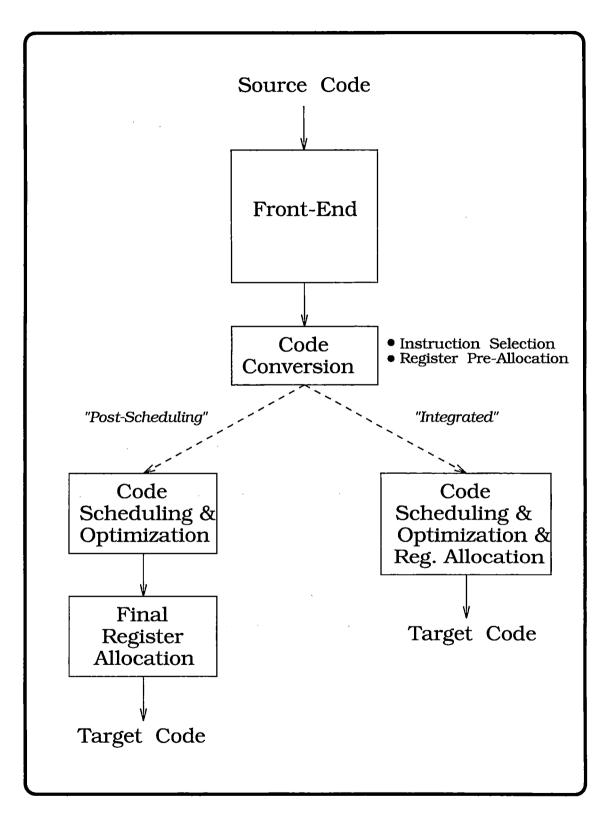

However, high register re-use leads to many false (anti-) dependencies that can potentially limit the extracted parallelism. As depicted in Figure 1.3, two strategies proposed by various researchers [13, 28, 38, 64] for overcoming this limiting factor are:

- Post-allocation "Pre-allocate" registers then perform scheduling with a "loose" number of register (more than is present in the architecture) and then apply final register allocation.

- Integrated scheduling and register allocation Perform code motion re-allocating registers "on-the-fly" as necessary to increase the exposed parallelism.

The first strategy has the advantage of simplicity, but has the disadvantage that spill code decisions and effects made after the scheduling process potentially

degrades the code's performance and possibly requires another scheduling phase. The second strategy has the advantage that spill decisions are factored into the code and spill instructions can be scheduled effectively, but these approaches tend to be more complex in terms of implementation and run-time.

Architectures targeted by a parallel compiler include VLIW, superscalar and heavily pipelined processors which may include mechanisms for multiple instruction issue and multi-way branching.

#### 1.1.3 Embedded Compilers

An embedded compiler encompasses the same features as a parallelizing compiler, as, parallelism in the architecture must necessarily be exploited for high performance, but also has other requirements due to the characteristics of the application domain and target architecture. Characteristics such as:

- timing constraints (time-critical code segments)

- code size

- application-specific datapaths

- available registers and their usages

all serve to place constraints on a compiler and thus affect the quality of the code generated.

Embedded applications are often time-critical, so timing constraints must be factored into the scheduling process, as well as the timing and interaction (if any) of the embedded processor with other system components.

The amount of code that is generated is also an issue as the code must be embeddable within the system. That is, the application code partitioned to the programmable component resides in ROM. Since ROM size directly affects the size of the embedded system, constraints are typically placed on ROM size, thus limiting the amount of memory available for application code.

Figure 1.3: Phases of a parallelizing compiler.

Figure 1.4: Available register organization.

Also, non-conventional (non-uniform) datapaths place stricter requirements on instruction selection and scheduling as some forms of computations may not be supported and alternative forms must be considered.

Lastly, the fewer number of available registers in the architecture and the presence of partitioned register sets increases the complexity of register allocation. Thus, effective register allocation plays a critical role in the generation of high-quality and high-performance code. Improving a register allocator to accomodate partitioned register sets and augmenting the heuristics which guide code optimization and transformation to make better use of registers allows this goal to be fulfilled.

## 1.2 Motivation for Embedded Compiler Complexity

Traditionally, one demand placed on a compiler is that of fast translation of source code to target code. Many compilers offer "switches," parameters to the compiler, that allow the user to specify the "level" of optimization, with higher levels requiring more compile time. Thus, most optimizations that are implemented with heuristics, utilize more complex heuristics as the level of optimization increases.

One reason for heuristic implementation of the optimizations is, for most application areas, absolutely "perfect" code is not necessary, highly optimized code is sufficient. However, for embedded systems, the best code possible is usually highly desirable as the application code is compiled once, but is resident and executed for the lifetime of the product being developed. Further, many embedded systems contain fewer numbers of registers than that found in traditional processors, so more complex program optimization is plausible.

Also, there is a lack of research, both in conventional compilation and embedded code generation focusing on the effects of optimizations on register allocation as well as developing heuristics for optimization which have the underlying goal of improving register allocation.

#### **1.3** Scope of Thesis

This thesis demonstrates that beyond the specific task of register allocation, there are subtle issues related to register allocation that must be addressed in order to generate high quality code for an embedded application. This thesis investigates:

- A technique which eliminates redundancies found in array accessing over iterations of a loop is presented in Chapter 4. This technique allocates a register to an array data item that is used frequently over a loop or within a window of iterations of a loop, thus promoting it from the secondary memory to the primary memory, thereby reducing the amount of memory traffic and, thus, the memory bandwidth requirements.

- Transformation interaction within a parallelizing compiler has been studied relatively little; however, it remains an important issue in generating high quality code. Chapter 5 presents a paradigm for integrating transformations so that transformations are applied based upon global knowledge (e.g., *across* basic blocks) instead of local knowledge (e.g., *within* basic blocks),

leading to better resource/register allocation and the development of better scheduling/allocation heuristics.

- One strategy which integrates register allocation and instruction scheduling performs register allocation "on-the-fly" by a technique called renaming. This approach has the disadvantage of adding overhead to the code in the form of many copy instructions which adversely affects performance. Chapter 6 presents a post-scheduling technique to unroll loop code and re-allocate registers to instructions so that copy instructions may be removed from the code.

- Register allocation has been extensively studied with proposed solutions largely being heuristic in nature. However, for embedded applications which contain time-critical loops and/or loop kernels, an optimal allocation is necessary. Chapter 7 presents a technique for optimal allocation of registers to loop code.

Chapter 8 presents the results of experimentation with these techniques and Chapter 9 presents some final remarks.

# Chapter 2 Related Work

Register allocation has been the subject of much research in the past, both in the areas of conventional compiler design and design synthesis. In conventional compiler design, the term *register allocation* refers to the task of determining which program constants and variables should be contained within a register while the term *register assignment* refers to the task of determining within which register a value should reside. Conventionally, in design synthesis, the term register allocation refers to the task of determining the number of registers that are necessary to store values across machine states, while the term register assignment refers to assigning variables to the available registers. In the sub-area of Hardware/Software Co-Design, the term register assignment refers to the same mapping problem as compilation, but, as the target architecture may be specialized for a given application domain, the available registers may be partitioned into multiple files with some registers having restricted or specialized usages.

This chapter provides a survey of register allocation and assignment techniques as well as other memory-related program transformations.

## 2.1 Register Allocation and Assignment

The general problem in conventional compilation of register allocation is to assign the variables and temporary values of a program to the registers of the target architecture, usually with uniform access to all available registers which are consolidated into one file. When more values exist than registers, some values will have to reside in main memory and spill code—loads and stores from main memory to the available registers—is generated when those values are referenced. The goal of a register allocator is to minimize the amount of spill code that is generated. This task is inherently NP-Hard [2, 36] and, as such, heuristic algorithms have been commonly utilized to determine some "sub-optimal, but good" solution.

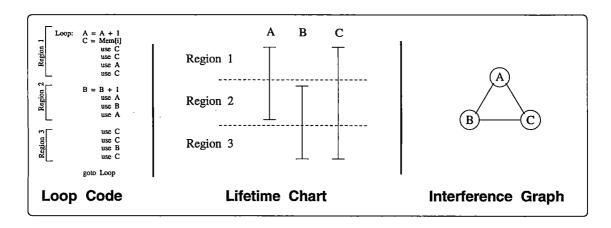

#### 2.1.1 Graph Coloring

H

One of the most popular heuristic approaches to allocating variables to registers is graph coloring [16, 23, 24]. In this strategy, the live ranges of program variables are examined. When two variable's lifetimes overlap they are said to *interfere*. An *interference graph* is then constructed wherein the nodes represent the variables and the edges joining nodes represent the interference of the two particular nodes being joined. The task is then to "color" the graph nodes with the same number of colors as registers. If no coloring of the graph is found, some variable is heuristically selected and spilled; all references to that variable then refer to that memory location. Once the original code has been updated with the spill code, a new graph is then constructed to reflect the new interferences and this process repeats until some colorable graph is found.

As the key to good register allocation in this scheme is the selection of a particular variable to spill, heuristics for selection have received attention [17] along with methods of coloring the graph [14]. Freiburghouse [34] suggests prioritizing coloring based upon the number of uses of a variable. Proebsting and Fischer [73] propose allocating registers to variables based upon the probabilities that a variable is "profitably" held in a register.

Bernstein *et. al.* [10] propose a strategy for reducing the amount of spill code generated by selecting between *multiple* heuristics to color the interference graph. Their results show that a best-of-three strategy results in less code and adds a

nominal amount of overhead to the graph coloring phase. Also, the authors propose a technique called *cleaning* to reduce the amount of spills generated for a particular variable. Rather than generating spill code each time that a spill candidate is referenced, the lifetime of the spill candidate is examined to determine if intervening stores and loads can be eliminated.

Chow and Hennessy [25] propose a method to split variable lifetimes when the interference graph is not colorable. After the lifetimes are split, a new interference graph results with the degree of some nodes (corresponding to those split variables) reduced and further coloring can become possible.

Leuh, Gross and Adl-Tabatabai [54] develop a global register allocation strategy similar to [25] which incorporates live range splitting and spilling. However, this strategy differs as execution probabilities are given primary importance when spill decisions are considered.

For large programs with many variables, the interference graph can become quite complex, necessitating large amounts of storage. Gupta *et. al.* [41, 42] propose a method to reduce the space requirements of a graph coloring register allocator by partitioning the program code, separately constructing and coloring the interference graphs for each partition and combining the colorings for a final program solution. Their results show significant improvements in space savings without sacrificing the quality of a graph coloring strategy.

Callahan, Carr and Kennedy [18] extend the graph coloring technique to handle arrays by *scalar replacement* which replaces repeated references to an array location by references to a (newly created) scalar variable.

Liem, May and Paulin [55] extend the left-edge register allocation scheme to allocate registers for architectures with registers which are specialized or have restricted uses. The proposed extension incorporates register classes into the model to specify a subset of the architecture's registers which are available for a given instruction.

#### 2.1.2 Interval Graphs

H

Another paradigm for the register allocation problem is that of modeling the interferences of variable lifetimes by *interval graphs*. The interference graphs of basic blocks belong to the class of graphs known as interval graphs and can be optimally colored in polynomial time [37]. However, by definition, interval graphs are not applicable to a global context for allocating registers over conditional branches and loops. Some work [43] has been done, however, to extend the interval graph approach to loops, but in order to reduce complexity, arbitrarily breaks the lifetimes of cyclic variables at loop boundaries. A consequence of this is that, since register usages must match at the top and bottom of the loop, register-to-register move instructions (which consume functional unit resources) are necessary to correctly map values contained within the registers while load/store operations are necessary to load values necessary at loop top that are not contained within the registers and to store live values that

#### 2.1.3 Optimal Register Allocation

Many researchers have felt that for particularly critical code segments, such as the innermost loops of time-sensitive applications, an optimal allocation is necessary. Horwitz *et. al.* [45] present a method for obtaining an optimal register allocation to *index* registers which minimizes the number of loads and stores due to added spill code. Further work either improves upon the efficiency of the Horwitz algorithm [60] or extends the basic algorithm to deal with simple loops [48], but in doing so loses optimality and degrades performance. More recent research has extended the basic idea in Horwitz's algorithm to include register allocation for *general purpose* registers [46].

#### 2.1.4 Register Allocation and Program Transformation

Research on integrating transformations has addressed the issue at both the fine-grain (register-transfer) and coarse-grain (source-code) levels. In fine-grain

compilation, the thrust is to integrate register allocation with instruction scheduling while in coarse-grain compilation, the thrust is to study the effects of ordering of coarse-level loop re-structuring transformations.

#### Fine-grain

Bradlee, Eggers and Henry [13] study the problem of integrating instruction scheduling and register allocation. Three strategies are examined: 1) register allocation preceeding scheduling; 2) register allocation after scheduling; and 3) an integrated approach which does pre-scheduling and global register allocation before final scheduling. Their results indicate that, for the i860 target architecture, the integrated approach generally produces better results than register allocation preceeding scheduling, while there were no significant differences between the schedules produced by the integrated approach and register allocation following scheduling.

Goodman and Hsu [38] investigate the integration of code scheduling and register allocation in the context of pipelined processors. Their scheduling algorithm alternates between two sub-algorithms: one which is devoted to filling pipeline latencies and avoiding pipeline interlocking and stalls, and another which re-organizes the code to reduce register pressure—the ratio of the number of allocated register to the total number of registers. Scheduling first starts with code re-organization to reducing register pressure, and, when the register pressure has been reduced to a threshold level, code motion to fill pipeline slots is done until the register pressure becomes too high when the process repeats. From analyzing performance results, the authors note that if a processor is heavily pipelined, with a possible interlock being very expensive, spills might be more profitable (i.e., reducing register pressure is less critical).

In [64] resource trade-offs are made dynamically ("on-the-fly") during scheduling to better utilize free resources which, in some cases, results in the modification of the code. For example, the computation X = 2 \* X can be performed by shift (X = SHL(X)), addition (X = X + X) or by multiplication (X = 2 \* X)depending upon which functional resources are currently free *at that point* in the schedule. This work, however, does not address the interaction of transformations

during scheduling or the effects that a transformation has on the resultant code.

Proposed techniques [67] typically make allocation decisions based on the parallelism automatically detected.

Rau et. al. [77] investigate register allocation heuristics for the strategy of register allocation following scheduling, specifically for DO loops that have been software pipelined via modulo scheduling. The issue in deriving a suitable heuristic for a register allocator centers around the expanded lifetimes created by modulo scheduling as well as lifetimes which have now become loop-carried. Two architectural types are considered: those with explicit support for modulo scheduling (i.e., a rotating register file) and those without (i.e., uniform, random access to all registers). Their results indicate that schedules for architectures which support modulo scheduling require more registers but have a reduced code size compared to those for other architectures.

Berson et. al. [11] integrate classic compiler optimizations such as constant propagation, loop invariant code motion, dead code elimination, etc., into the instruction scheduling process, as application of these techniques prior to scheduling can adversely affect the quality of the code produced. Their heuristics for application of the techniques to the code during scheduling focus on measures determine that the technique will be beneficial.

#### Coarse-grain

In [83] a tool for studying the ordering of coarse-grain transformations is discussed. However, this approach does not allow for assessing and making trade-offs between transformations.

#### 2.2 Memory-Related Transformations

Callahan, Cocke and Kennedy [19] present a technique which improves the balance of a loop—the ratio of memory words accessed to the number of operations performed. Their algorithm restructures the loop at the input level based upon estimated functional unit pipeline hazards and interlocking mechanisms, but deals only with single-dimension arrays and single flow-of-control within a loop body.

Callahan, Kennedy and Porterfield [20] investigate the idea of *software* prefetching—a technique to explicitly fetch data into a cache. Although the goal of the technique is to improve performance, memory traffic can actually increase in situations where a prefetched item is bumped from the cache before its use.

Davidson and Jinturkar [29] reduce memory traffic in the context of instruction set processors without a cache by combining (or "coalescing") multiple memory accesses into a single memory access. Their technique combines small bit-length accesses of adjacent data into one larger bit-length access. Two limitations to this strategy are: 1) architectural support (a wide bus) is necessary to be able to combine small bit-length adjacent accesses into a single larger access; and, 2) combining multiple memory accesses scattered throughout the program can adversely affect scheduling due to the new dependencies created.

Pöchmüller, Glesner and Longsen [68] discuss the notion of background memory management—the allocation of memory modules to arrays at the behavioral level. The authors note that background memory management is an important subtask in High Level Synthesis as it is necessary to remove unnecessary (redundant) array references due to the hardware that they generate.

Data blocking [53, 69] is another technique aimed at improving cache effectiveness. This approach partitions a large data-space that is not containable within a cache into smaller data *blocks* which are containable within a cache and then the program is restructured to improve data reuse within those blocks.

Work in scheduler transformations includes fast prototyping of architectures [75], the shortening critical path lengths in pipelined datapath synthesis [59], minimizing path explosion in path/trace-based systems [65], redundant operator creation to reduce execution time [58], level compression of expressions [80] and incremental tree height reduction [62].

# 2.3 Memory Access Models

Duesterwald, Gupta and Soffa [30] extend traditional dataflow analysis for scalar variables to include subscripted (array) variables through the use of *iteration distance values*. These values denote the number of iterations between the production of an array value and its final use and is utilized in analyzing dependencies between memory operations.

Verhaegh *et. al.* at Philips [82] utilize a *stream* concept to model periodicity in array references. Dependencies between streams are revealed by *stream graphs* which incorporate start times and periodic information of array references into *iteration vectors*. This information is then used to assess memory requirements.

Franssen *et. al.* at IMEC [33] use a complex *polyhedral dependency graph* to model multi-dimensional array references. A polyhedral dependency graph is a dataflow graph which contains sets of points defined by the ranges of variables used in an array's indexing expression. This graph then represents the dependencies between memory operations.

# 2.4 Memory Structure Synthesis

Another formulation of the memory allocation problem is to determine the number of registers necessary to preserve values produced in one control step and used in subsequent control steps. Kurdahi and Parker [52] present an algorithm which accomplishes this by analyzing variable lifetimes in the dataflow graph. Some work [39, 66, 79] has been done to improve register usage for loops which breaks a variable's lifetime at the loop boundary, creating two "coupled" variables which the assignment process tries to assign to the same register. Register sharing—the use of one register by multiple variables when the lifetimes of those variables do not overlap—is employed to reduce the necessary number of registers.

Goossens [39] uses a heuristic to fill the gaps between coupled variables and then

applies the left-edge algorithm. Stok [79] iteratively tries to improve an initial allocation produced by the left-edge algorithm by "permuting" variables in registers at loop end to match the variable assignment at loop beginning. Park, Kim and Liu [66] extend the left-edge algorithm to deal with behaviors having conditional and looping constructs.

A natural extension to this formulation is the grouping of those allocated registers into memory modules. Two issues arise in doing so: 1) the exact grouping of variables so as to minimize the number of modules used; and, 2) the interconnections now necessary to connect modules to functional units. Balakrisnan *et. al.* [6] provide a solution which places primary importance on variable grouping. Ahmad and Chen [1] extend Balakrishnan's approach to take into account the commutative property of operations, thus allowing the connection of a memory module to either input of a functional unit. Kim and Liu [49] note that the first issue heavily influences the second, and, thus, in their approach, they place primary importance on interconnection cost rather than variable grouping.

Ramachandran, Gajski and Chaiyakul [76] present an algorithm to allocate storage for array variables. Their algorithm performs *array-variable clustering* which allows more than one array to be allocated to the same memory module subject to user performance and cost criteria.

# <u>Chapter 3</u> Phases of Compilation

In this chapter, the phases of the parallelizing compiler used for the development of the techniques studied in this thesis are outlined and the underlying execution model is presented.

# **3.1 A Parallelizing Compiler**

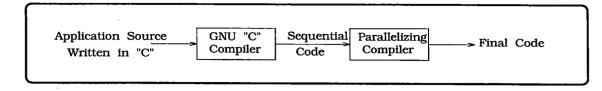

As illustrated in Figure 3.1, in the parallelizing compiler developed at UCI [70], the compilation process of application code written in "C" starts with a sequential version of that code produced by a version of the GNU "C" Compiler. This version has been modified to output code in a three-address instruction format for a load/store-type architecture model. This code is then input into the parallelizing compiler. After initial analysis of the code is performed, the bulk of the compiler's implementation performs code parallelization. It is during the loop pipelining phase, when iterations of a loop are overlapped to reveal a pattern in execution, that the transformations and optimizations implemented in the compiler are applied to the code. After loop pipelining, the code is maximally parallelized (subject only to data dependencies). Resource constraints are input and a scheduling phase applies resource constraints to the code. Once the code has been resource constrained, final code is generated.

Figure 3.1: Code Generation process.

## **3.2** Program Model

The compiler's internal representation of the input code is in the form of a control/data-flow graph. In this graph, nodes correspond to machine cycles and all instructions contained within a respective node are performed (issued) in parallel, while edges between nodes correspond to flow-of-control and determine the next set of instructions to be issued. Thus, nodes with multiple successor nodes must contain conditional branching instructions, the correct successor is chosen at run-time subject to the values of the condition codes being tested.

For all instructions contained within a node, the following three-phase execution model is used:

Phase 1: All instruction operands are read from registers.Phase 2: All instructions are executed.Phase 3: All results are written to the appropriate registers.

With this model, performing the instructions R1 = R2 and R2 = R1 in parallel will correctly swap two values as the operands will be read before the results are written.

## 3.3 Scheduling

Although the program model presented above is effective for scheduling uni-cycle instructions, modeling pipelining with this model is more complex. Especially in cases where hardware conflicts or pipeline hazards between different functional units occur. For example, consider a bus that is shared by two functional units, but used by those units in different stages of execution. If the first unit uses the bus in its second pipeline stage and the second unit uses it in its third pipeline stage, no conflicts occur if instructions are issued to both units in the same cycle. However, if an instruction is issued to the second unit in the current cycle and an instruction is issued to the first unit in the next, a conflict will occur.

Further, in some architectures with specialized hardware, each of the phases described above may not be atomic, but may encompass several lower level operations. This leads to a disparity between the relative performance of the generated code and the performance attained when the code is executed by the hardware.

These sorts of "lower-level" details are lost or are difficult to track at the fine-grain level as they are not made explicit to the scheduler. To remedy this, the sematics of an "atomic unit" are modified to allow these lower-level details to be made explicit. This lower-level of granularity has been termed the ultra fine-grain level and the extension of this compiler to the ultra fine-grain level is termed Ultra Fine-Grain Percolation Scheduling (UFG-PS).

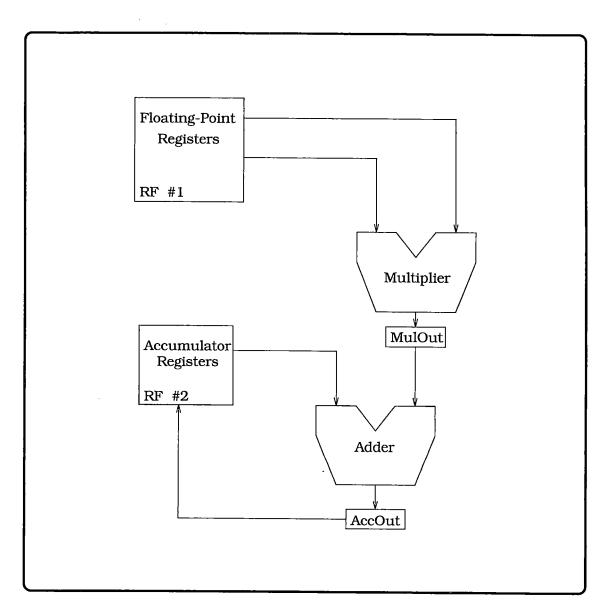

The lower-level or ultra fine-grain level characteristics of the architecture are detailed to the compiler via a set of *microcode macros*. The compiler uses these macros to translate fine-grain instructions into ultra fine-grain instructions as these macros detail explicitly the data transfers associated with each of the fine-grain instructions. For instance, if the target architecture has the floating-point multiply-accumulate unit as shown in Figure 3.2 with a three-cycle latency multiplier and a two-cycle latency adder (for a total latency of five cycles for the fine-grain level multiply-accumulate instruction), the following macro details this:

Figure 3.2: Datapath for microcode macro example.

Fmac @f1, @f2, @f3 ::

f1 = f1 + (f2 \* f3)

• Fmulst1 (RFread #1, @f2), (RFread #1, @f3)

perform 1<sup>st</sup> stage of f2\*f3

• Fmulst2 fmulst1latch, fmulst2latch 2<sup>nd</sup> stage of multiply

3<sup>rd</sup> stage of multiply

- Fmulst3 fmulst2latch, MulOut

- Faddst1 (RFread #2, @f1), MulOut  $1^{st}$  stage of  $f1 + multiply_result$

- Faddst2 faddst2latch, (RFwrite AccOut, #2, @f1)

$2^{nd}$  stage of add, writeback into f1

$\operatorname{END}$

The first instruction details the first stage of the multiplication when the reading of the operands from the floating-point register set are input into the multiplier unit. The next two instructions show the transfer of the calculation through the intermediate (internal) latches and the final writing of the multiplier output into the latch labelled "MulOut" in Figure 3.2. The next instruction, the first of the addition sequence, inputs the operands to the adder from the accumulator register set and the output of the multiplier. Finally, the last instruction performs the second stage of the addition and the writeback of the result into the accumulator register file.

During the initial analysis phase, the fine-grain instructions are converted into their equivalent microcode sequences, deriving an ultra fine-grain level graph which is then subject to transformations and parallelization techniques implemented within the compiler.

Thus, in this representation, lower-level conflicts can be efficiently handled and avoided and, as this allows a closer modelling of the underlying target architecture, better quality schedules can be generated. Also, the notion of a dependency is extended from data dependencies to include *architecture* dependencies. Pipeline conflicts between various functional units can then be

detailed as dependencies between the respective UFG instructions. During scheduling, the compiler honors these dependencies, thereby generating code without those conflicts.

# <u>Chapter 4</u> Eliminating Redundant Memory Accesses

T ypically, embedded systems which run applications that contain arrays employ a secondary store (e.g., a memory system) as a primary store (e.g., register storage) sufficiently large enough to completely contain all arrays would be impractical. References to arrays in the application code are accomplished by load and store instructions to the appropriate memories. Thus, array references in the application code translate into memory traffic, which can affect both the performance and memory bandwidth requirements of the resulting system.

In order to improve the performance and/or reduce the bandwidth requirements of an application, this chapter presents a technique to remove memory accessing instructions when those accesses are to locations that have been previously referenced. That is, this techniques eliminates memory instructions which *redundantly* load/store values from/to memory by first exposing any redundancy found in array (memory) accesses. Next, registers are selectively allocated to those values and the redundant memory accessing instructions are eliminated from the code. Future array references then become references to a register.

This transformation has many significant benefits. By eliminating redundant load instructions occurring on the critical dependency path through the code, the performance of the resulting schedule can increase dramatically as the length of the critical path can be shortened, thus generating more compact schedules and

for

$$i = 1$$

to N

for  $j = 2$  to N

$a[i] := a[i] + \frac{1}{2}(b[i][j-1] + b[i][j-2])$

$b[i][j] := fcn(b[i][j])$

end

end

#### before optimization

```

for i = 1 to N

t1 := a[i]; t2 := b[i][1]; t3 := b[i][0]

for j = 2 to N

t1 := t1 + \frac{1}{2}(t2 + t3)

b[i][j] := fcn(b[i][j])

t2 := t3; t3 := b[i][j]

end

a[i] := t1

end

```

after optimization

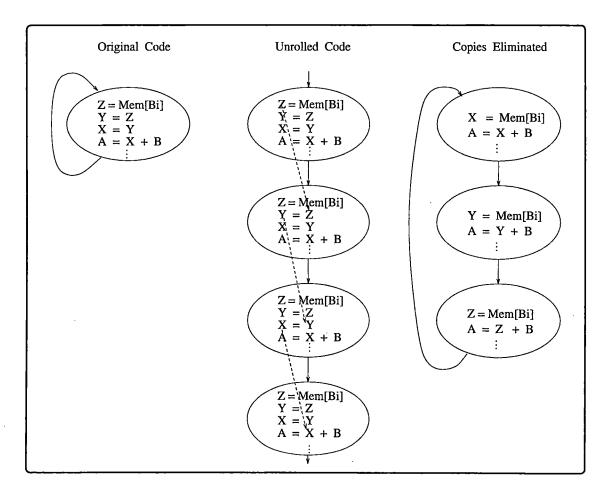

Figure 4.1: Removing redundant memory traffic.

reducing code size. In cases where array accesses are present in loops, elimination reduces the generated bandwidth over loop execution as well as the number of instructions that are executed as all of the instructions that are involved in an address calculation for a memory-accessing instruction are removed. Also, due to the transformation's local nature, it integrates easily into other parallelizing transformations [21, 65]. Finally, utilizing the transformation provides potential for savings in hardware due to the decrease in memory bandwidth requirements and/or the exploration of more cost-effective implementations.

# 4.1 Introductory Example

As an introductory example, consider the code in Figure 4.1. Before optimization, the inner loop requires four load and two store instructions per iteration:

| load | a[i]      |                 |

|------|-----------|-----------------|

| load | b[i][j]   | store $a[i]$    |

| load | b[i][j-1] | store $b[i][j]$ |

| load | b[i][j-2] |                 |

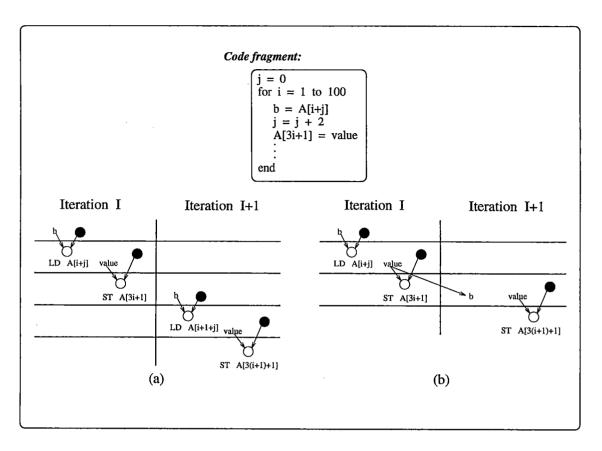

However, the value computed in the current j iteration with b[i][j] is the value that will be used by b[i][j-1] in the next iteration and b[i][j-2] in the subsequent iteration. At the end of the current iteration that value is stored to memory (necessary to preserve program semantics), and then re-loaded next iteration. The subsequent loads of that value may be circumvented by keeping the values in local storage—then only b[i][j] is necessarily loaded each iteration while previous values are available and passed to future iterations via local (register) storage.

Also, with respect to the inner loop, the address calculation of a[i] is invariant. Further, a[i] is being used only as temporary storage (it is continually overwritten), and, unless a[i] represents a memory-mapped input/output location, the load and store each iteration are unnecessary—the value loaded and stored can be kept in local memory.

Thus, as depicted in the Figure 4.1 after optimization code, only the load and store of b[i][j] are necessary each iteration, resulting in the elimination of three load instructions and one store instruction per iteration<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>Note that the assignment to t3 is not an actual memory fetching instruction—the value stored to b[i][j] is copied to t3.

# 4.2 Detecting Redundancy

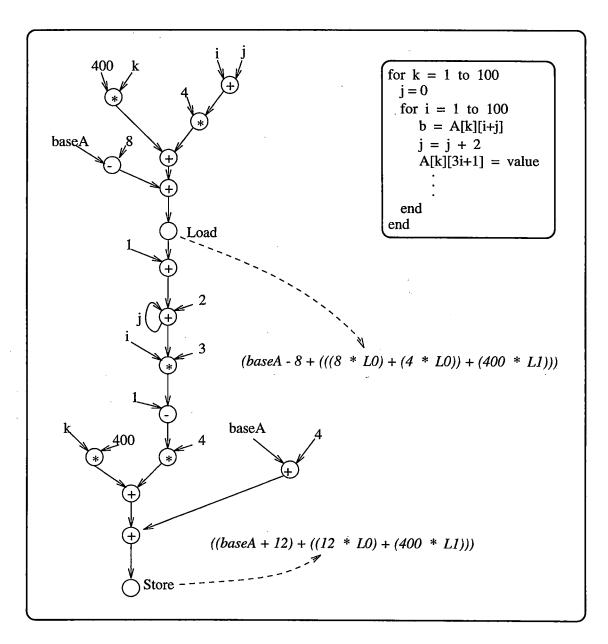

The strategy employed in this technique for optimizing memory access is to eliminate redundancy in memory interaction as it is found during scheduling. Such redundancies can be found *within* loop iterations, possibly over multiple paths, when compacting code. Also, redundancy is exhibited *across* loop iterations during loop pipelining [65, 71] when multiple iterations of the loop are overlapped (subject to data dependencies and resource constraints) to find a repeating pattern in loop execution. As each iteration is integrated and overlapped with the current loop schedule, memory instructions from the new iteration are exposed to the memory instructions from previous iterations. With the aid of memory disambiguation—the ability to discern whether two memory instructions refer to the same location—the recurrence patterns in array accessing become apparent from loop iteration to iteration as the new memory instructions move into cycles with loads and stores from previous iterations.

However, as many array mappings are possible—multiple arrays to the same module, separate modules for each array, splitting a (large) array among several (smaller) memories or any combination thereof—it is necessary with this approach to have a preliminary allocation and binding of array variables to storage (secondary memory). This information is then given to the compiler along with the system resource constraints (e.g., number of memory ports on secondary memories, size and number (if partitioned) of primary memories, number and type of functional units, functional and memory instruction latencies, etc.). This is in contrast to [7, 57], for instance, which both perform memory transformations before allocation.

The method used to support memory disambiguation is to derive *symbolic expressions* which formulate the address calculation without the program variables. The symbolic expressions are then used by the memory disambiguator to determine dependencies between memory instructions.

First, the method of deriving symbolic expressions for memory instructions is outlined and then memory disambiguation is briefly discussed.

#### 4.2.1 Symbolic Expressions

Each memory instruction contains an indexing function which is composed of the variables used in indexing each dimension of an array access, as well as either a *destination* for load instructions or a *value* for store instructions. The semantics of a load instruction are that issuing a load reserves the *destination* (local register storage) at issuance time (i.e., *destination* is unavailable during the load's latency) while the register storing the *value* argument of a store instruction is assumed free after the issuance of the store.

For the purpose of dependency analysis on memory instructions (memory disambiguation), every memory instruction contains a *symbolic expression* which is a string of symbols that formulates the memory address calculation without the source level variables [50]. The purpose of the symbolic expression is to be able to efficiently compare memory instructions for dependency analysis. In this approach, the variables used in the memory address calculation are "normalized" to a unique symbol for each loop thereby re-formulating the expression in as reduced a form as possible.

The *build\_symbolic\_exprs* algorithm in Figure 4.2 creates symbolic expressions for each memory instruction in the program by taking the induction variable (iv) definitions that define the current instruction's indexing function and deriving an expression for each. Next, the base of the memory structure is added to each expression. An instruction is then annotated with its expression, combining multiple expressions into a disjunctive form "(  $(expr1) \ or \ldots or (exprN)$ )."

The function derive\_expr constructs the expression "(LoopId \* Const)" if iv is self-referencing (e.g., i = i + const) where LoopId is the identifier of the loop over which iv inducts and Const is a constant derived from the constant in the iv instruction multiplied by a data size and possibly other variables and constants. If iv is defined in terms of another iv (e.g. i = j + 1, where j is an iv) then recursive calls are made on all definitions of that other iv. In this case, marking of iv's is necessary to detect cyclic dependencies which are handled by a technique called variable folding. Essentially variable folding determines an initial

| 1:  | Procedure <i>build_symbolic_exprs</i> (program)           |

|-----|-----------------------------------------------------------|

| 2:  | begin                                                     |

| 3:  | foreach mem_op in program                                 |

| 4:  | /* Set defs to all var defs $*/$                          |

| 5:  | foreach multiple def in defs                              |

| 6:  | /* Select subset of iv_defs - one def for each var. $*/$  |

| 7:  | $sym_expr = \phi$                                         |

| 8:  | foreach variable in the indexing fcns                     |

| 9:  | $new\_expr = derive\_expr(variable)$                      |

| 10: | /* Add the expressions sym_expr and new_expr. */          |

| 11: | $\mathbf{end}$                                            |

| 12: | /* Add the base offset to sym_expr. $*/$                  |

| 13: | if (/* mem_op's sym_expr is $\phi$ */)                    |

| 14: | /* Set mem_op's sym_expr to sym_expr. */                  |

| 15: | else                                                      |

| 16: | /* Combine sym_expr with mem_op's sym_expr with "or" $*/$ |

| 17: | end                                                       |

| 18: | end                                                       |

| 19: | end                                                       |

| 20: | end build_symbolic_exprs                                  |

| 1:  | function derive_expr(term)                                |