### UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Generator-Based Design of Custom Systems-on-Chip for Numerical Data Analysis

### Permalink

https://escholarship.org/uc/item/798657jg

### Author

Amid, Alon

### **Publication Date**

2021

Peer reviewed|Thesis/dissertation

Generator-Based Design of Custom Systems-on-Chip for Numerical Data Analysis

by

Alon Amid

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Co-chair Professor Krste Asanović, Co-chair Professor Bin Yu

Summer 2021

Generator-Based Design of Custom Systems-on-Chip for Numerical Data Analysis

Copyright 2021 by Alon Amid

#### Abstract

#### Generator-Based Design of Custom Systems-on-Chip for Numerical Data Analysis

by

Alon Amid

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Co-chair

Professor Krste Asanović, Co-chair

With the end of Dennard scaling and the subsequent demise of Moore's Law, the continuous demand for higher computing performance and efficiency is increasingly met through specialization of digital processors. In particular, numerical data processing and machinelearning applications incur high computational costs but often have common computational structures, acting as prime targets for hardware customization. Specialization of digital designs is accompanied by substantial non-recurring engineering (NRE) costs, which limit the proliferation of customized designs. This work presents tools and methodologies for the development of custom systems-on-chip (SoCs) for numerical data analysis applications. An integrated generator-based framework for SoC development is demonstrated through SoC customization and hardware/software co-design for numerical data analysis and machinelearning applications. The development of full-system support from hardware accelerators through system software leads to the identification of several co-design opportunities for increasing accelerator utility in custom SoCs. Specifically, we demonstrate the development of high-performance custom software library implementations to support accelerated numerical data analysis on custom SoCs developed using the Chipyard integrated generator-based framework for custom SoC design. We further identify a need to provide support for processing of a high variety of matrix shapes and sizes in SoC deep learning accelerator matrix engines for accelerated processing of numerical data analysis workloads, and demonstrate up to a  $1.25 \times$  improvement in the utilization of a matrix engine on small and rectangular matrices through hardware-managed static scheduling, dynamic scheduling, and hardwaremanaged commutative micro-threading.

# Contents

| Co       | onter                                   | nts                                           | i                                                                |

|----------|-----------------------------------------|-----------------------------------------------|------------------------------------------------------------------|

| Li       | st of                                   | Figures                                       | iii                                                              |

| Li       | st of                                   | Tables                                        | vi                                                               |

| 1        | 1.1                                     | Oduction       Hardware Specialization        | $egin{array}{c} 1 \\ 2 \\ 4 \end{array}$                         |

|          | $\begin{array}{c} 1.2\\ 1.3\end{array}$ | Numerical Data Analysis                       | $\frac{4}{5}$                                                    |

| <b>2</b> | Alg                                     | orithms for Numerical Data Analysis           | 8                                                                |

|          | $2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5$       | Machine Learning and Numerical Data Analysis  |                                                                  |

| 3        | Har                                     | dware for Numerical Data Analysis             | 19                                                               |

|          | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6  | Data Parallel Architectures                   | 19<br>21<br>22<br>25<br>28<br>33                                 |

| 4        | Ger                                     | nerator-based System-on-Chip Design           | 35                                                               |

|          | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6  | System-on-a-Chip                              | $35 \\ 37 \\ 38 \\ 40 \\ 42 \\ 40 \\ 42 \\ 40 \\ 40 \\ 40 \\ 40$ |

|          | 4.6                                     | Generator-based System-on-Chip Design Summary | 49                                                               |

| <b>5</b>     | The Chipyard Integrated SoC Development Framework5.1SoC Customization in Chipyard |     | <b>50</b><br>58 |

|--------------|-----------------------------------------------------------------------------------|-----|-----------------|

|              | 5.2 SoC Design Frameworks                                                         |     | 65              |

|              | 5.3 Agile Hardware Development Using Chipyard                                     |     | 67              |

|              | 5.4 Accessibility and Education                                                   |     | 73              |

| 6            | Generator-based SoC Hardware/Software Co-Design                                   |     | 87              |

|              | 6.1 Generator-Based SoC Design Space Analysis                                     |     | 88              |

|              | 6.2 Generator-based Software Debugging and Optimization                           |     | 99              |

|              | 6.3 Generator-based Performance Tuning                                            |     | 106             |

|              | 6.4 Generator-based SoC Hardware/Software Co-Design Summary                       | • • | 111             |

| 7            | Software Customization for Numerical Data Analysis                                |     | 113             |

|              | 7.1 Software Mapping to Specialized Accelerators                                  |     | 113             |

|              | 7.2 Software for Supplemental Use of DNN Accelerators for Numerical Data Ana      |     |                 |

|              | 7.3 BLAS and LAPACK                                                               |     | 121             |

|              | 7.4 BLAS Implementations                                                          |     | 123             |

|              | 7.5 BLAS/BLIS for Gemmini and Hwacha                                              |     | 127             |

|              | 7.6 BLAS-3 Performance Evaluation                                                 |     | 151             |

|              | 7.7 Application-Level Performance                                                 | • • | 152             |

| 8            | Hardware/Software Co-Design for Numerical Data Analysis                           |     | 164             |

|              | 8.1 Hardware/Software Co-Design for Supplemental-Use                              |     | 164             |

|              | 8.2 Matrix Engines for Numerical Data Analysis vs. DNNs                           |     | 165             |

|              | 8.3 Matrix Engine Controllers                                                     |     | 172             |

|              | 8.4 Matrix Engine Controller Scheduling                                           |     | 174             |

|              | 8.5 Memory Access Tail Latency                                                    |     | 178             |

|              | 8.6 Co-Design of Matrix Engine Controller                                         |     | 180             |

|              | 8.7 Hardware/Software Co-Design for Numerical Data Analysis Summary               | ••• | 193             |

| 9            | Conclusion                                                                        |     | 195             |

|              | 9.1 Summary and Contributions                                                     |     | 195             |

|              | 9.2 Future Work                                                                   |     | 196             |

| Bi           | bliography                                                                        |     | 198             |

| $\mathbf{A}$ | Observations on the RISC-V Vector Standards Process                               |     | 225             |

# List of Figures

| 2.1                                                            | Data analysis workload categories and overlaps between them                                                                                                                                                                | 10                         |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

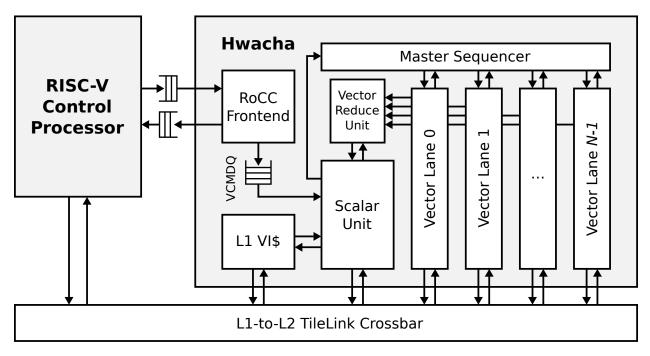

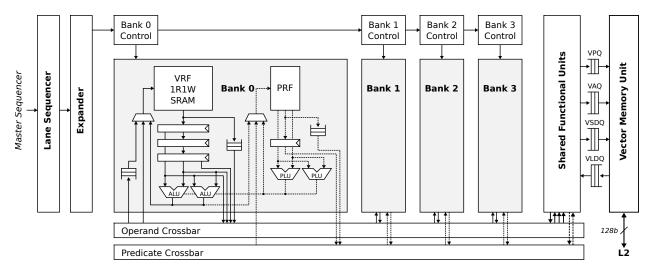

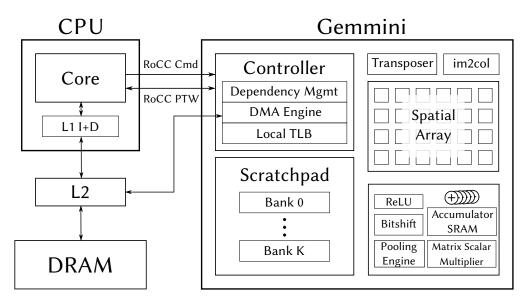

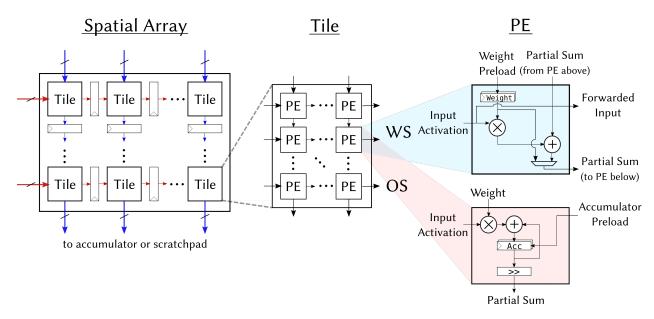

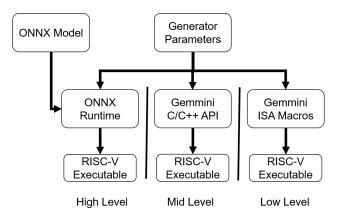

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                | Hwacha accelerator instance with N vector lanes.                                                                                                                                                                           | 24<br>25<br>29<br>30<br>33 |

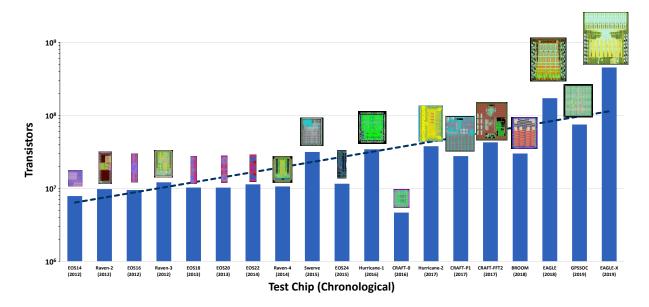

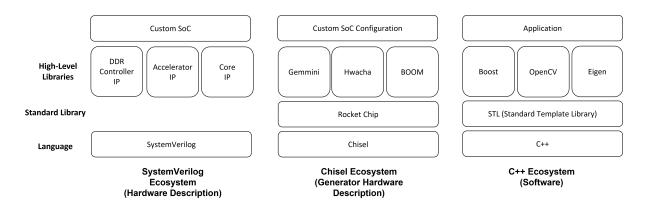

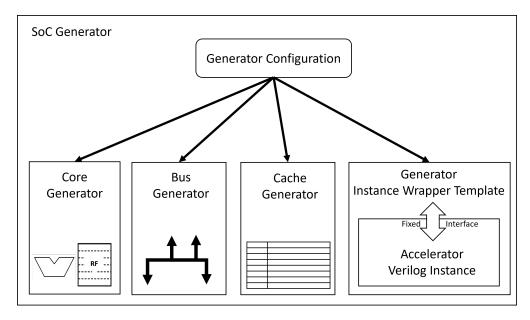

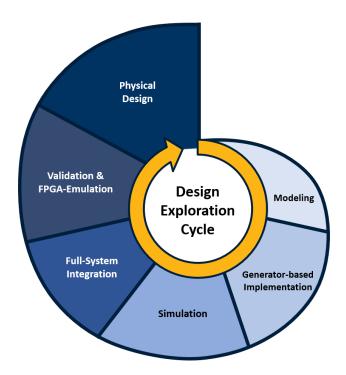

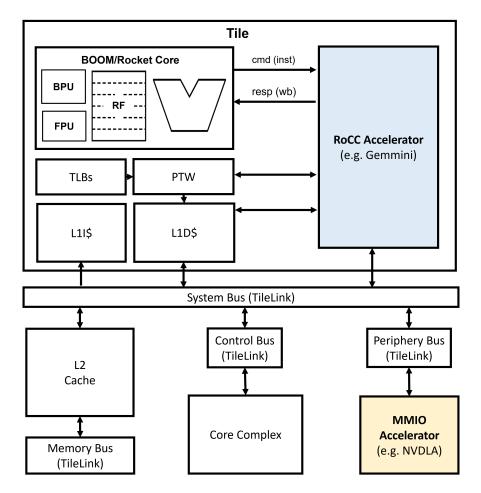

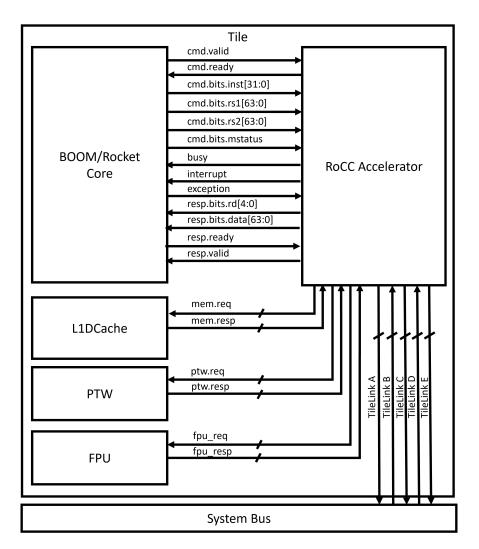

| <ol> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> </ol> | Increasing complexity of custom RISC-V SoC test chips built at Berkeley using<br>the Rocket Chip SoC generator between 2012-2019                                                                                           | 39<br>44<br>45<br>46       |

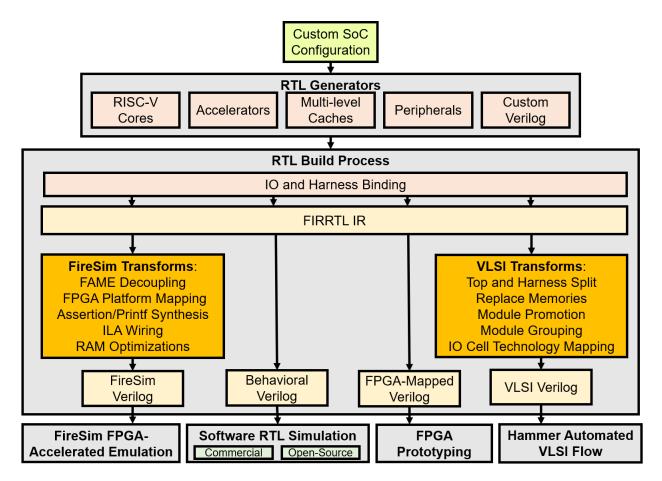

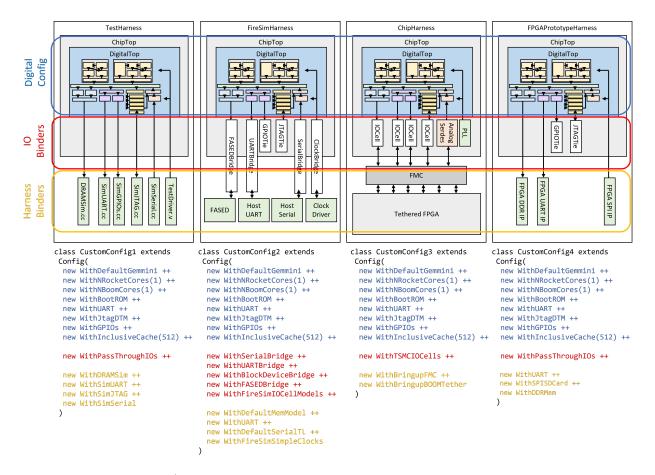

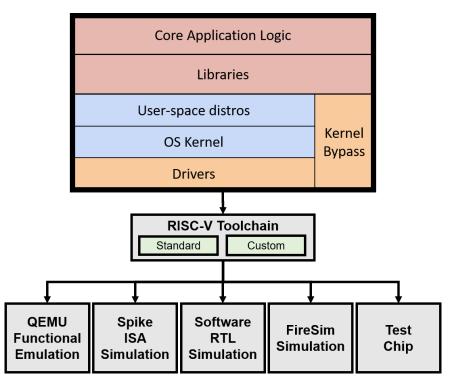

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                         | Chipyard design flow diagram                                                                                                                                                                                               | 51<br>56<br>58<br>61<br>64 |

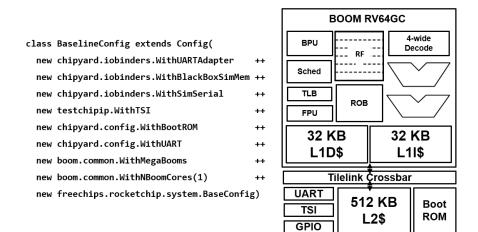

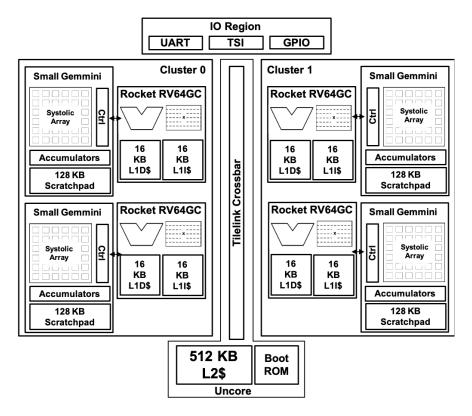

| 5.7                                                            | and GPIO peripheral interfaces                                                                                                                                                                                             | 69                         |

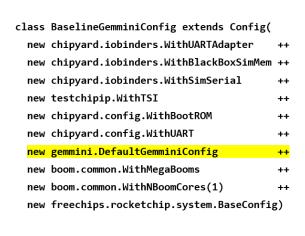

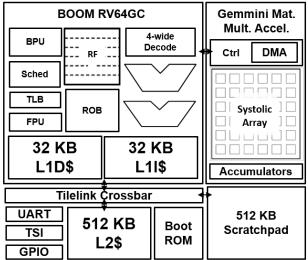

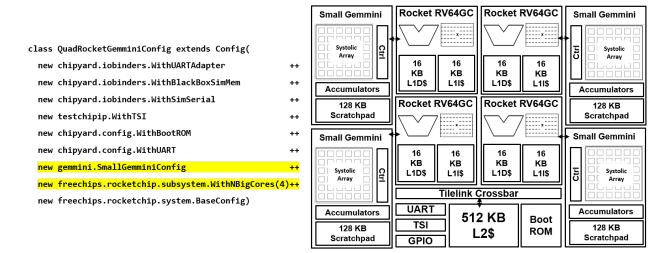

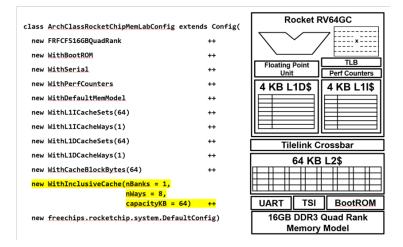

| 5.8                                                            | baseline SoC config using a single configuration line An SoC configuration replacing the single BOOM out-of-order core with 4 smaller<br>Rocket in-order cores and smaller Gemmini accelerators to evaluate PPA tradeoffs. | 69<br>71                   |

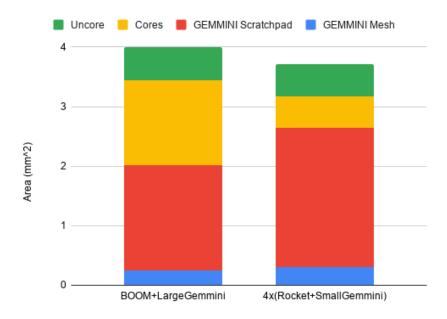

| 5.9                                                            | Post-synthesis area estimates using a commercial FinFET process comparing a powerful single-core system with an alternative equivalent parallel multi-core system.                                                         | 71                         |

| 5.10                                                           |                                                                                                                                                                                                                            | 73                         |

|                                                                | Example Chipyard generator configurations used in a memory hierarchy lab exercise.                                                                                                                                         | 80                         |

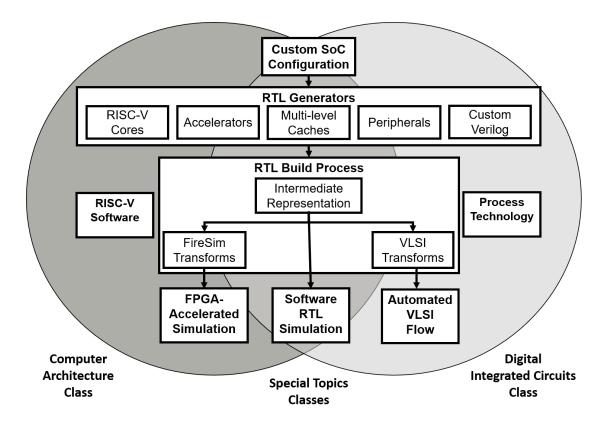

|                                                                | Multi-class flow using unified generator-based system framework.                                                                                                                                                           | 81                         |

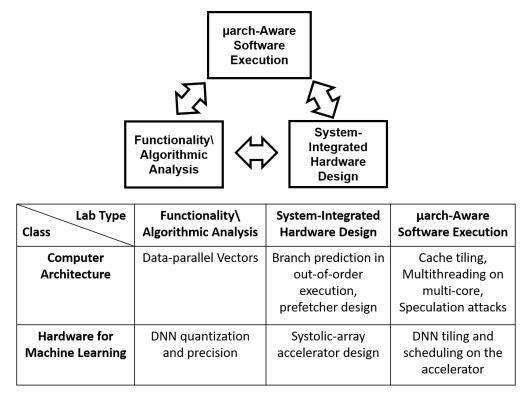

| 5.13                                       | Lab flows across multiple courses teaching both hardware and software consider-<br>ations                                                                                                                                                     | 82  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

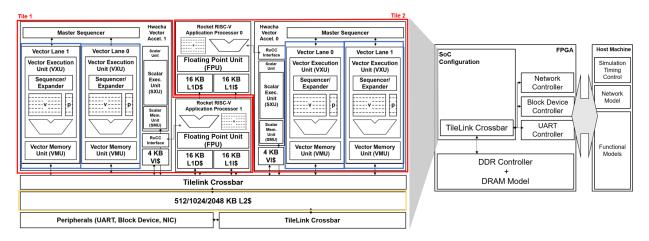

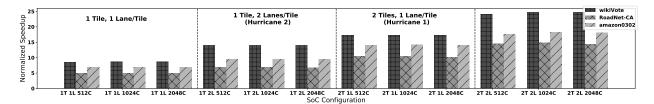

| 6.1                                        | FPGA-accelerated simulation of Hwacha-accelerated SoCs with DDR3, block de-<br>vice, network, and other peripheral models, using various configurations of gen-                                                                               |     |

| <i>c</i>                                   | erated target SoC RTL.                                                                                                                                                                                                                        | 90  |

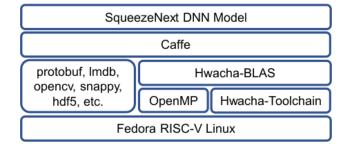

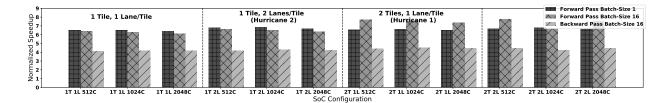

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$  | Dense DNN inference/training software stack                                                                                                                                                                                                   | 92  |

|                                            | pared to a minimal reference scalar implementation                                                                                                                                                                                            | 93  |

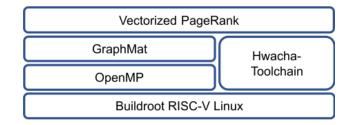

| $\begin{array}{c} 6.4 \\ 6.5 \end{array}$  | Sparse graph processing workload software stack                                                                                                                                                                                               | 94  |

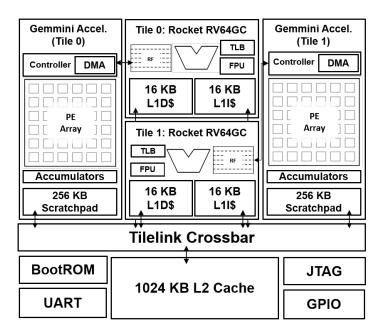

| 6.6                                        | sizes compared to a minimal reference scalar implementation Dual-core system-on-chip with Rocket Linux-capable RISC-V application cores, a Gemmini accelerator attached to each Rocket core, a shared L2 cache, and                           | 94  |

|                                            | standard peripherals                                                                                                                                                                                                                          | 96  |

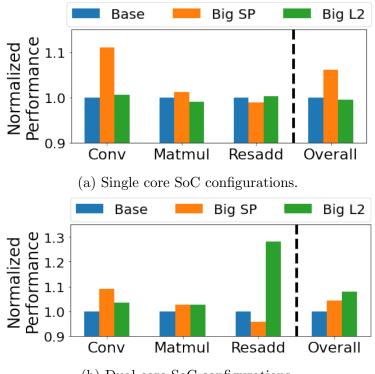

| 6.7                                        | ResNet-50 performance (by operation type), normalized to the performance of                                                                                                                                                                   |     |

|                                            | the Base configuration.                                                                                                                                                                                                                       | 98  |

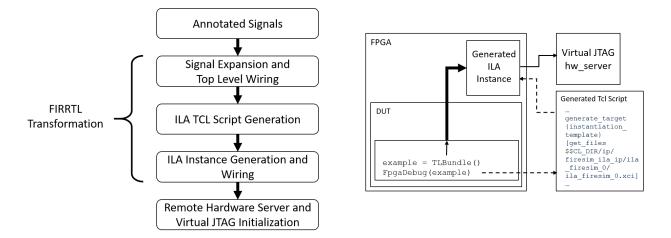

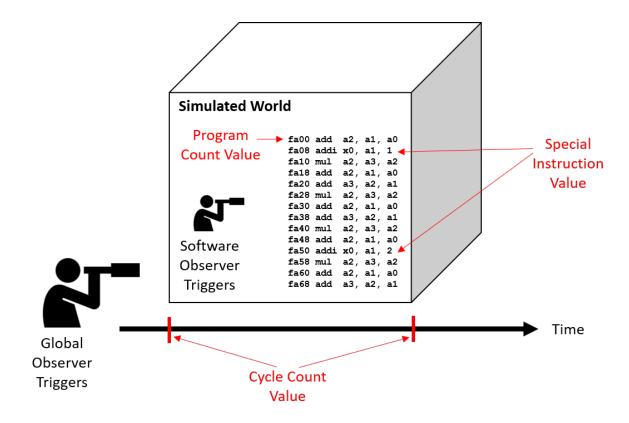

| $\begin{array}{c} 6.8 \\ 6.9 \end{array}$  | AutoILA generator-based integrated logic analyzer (ILA) integration flow<br>Debugging information segmentation triggering based on software-level informa-<br>tion within the simulated world as well as hardware-level global information in | 100 |

|                                            | FireSim                                                                                                                                                                                                                                       | 103 |

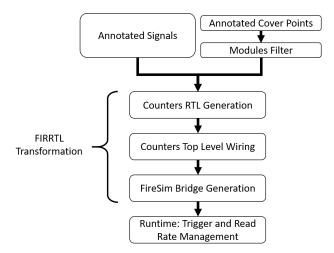

| $\begin{array}{c} 6.10\\ 6.11 \end{array}$ | AutoCounter generator-based out-of-band counter insertion flow                                                                                                                                                                                | 104 |

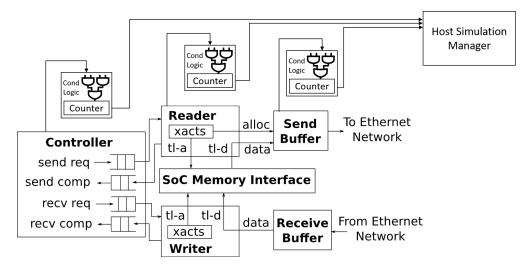

|                                            | design and connected out-of-band to the simulation manager. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                               | 106 |

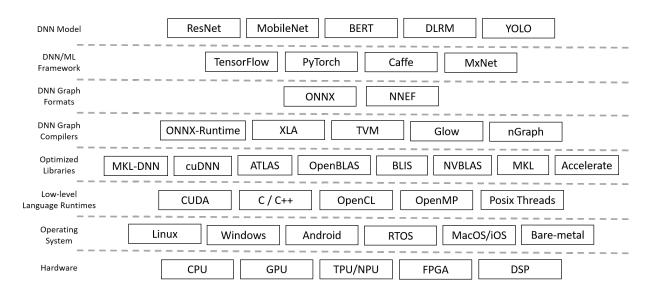

| 7.1                                        | Deep learning software ecosystem.                                                                                                                                                                                                             | 120 |

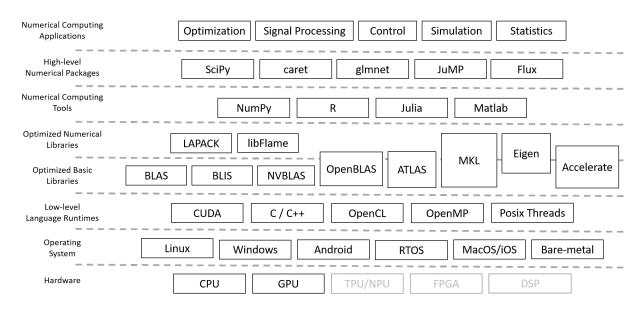

| 7.2<br>7.3                                 | Numerical computing software ecosystem                                                                                                                                                                                                        | 122 |

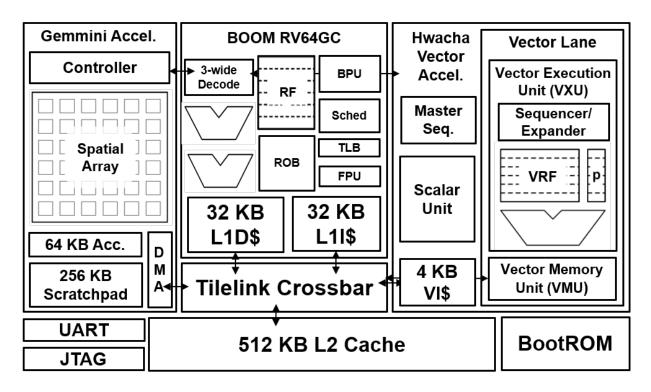

|                                            | mini and Hwacha.                                                                                                                                                                                                                              | 128 |

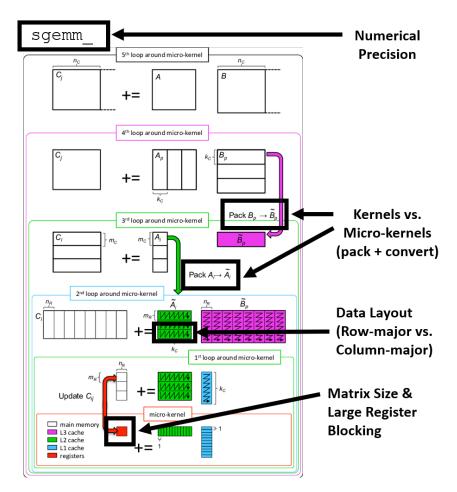

| 7.4                                        | Areas of special attention within the BLIS algorithm for the target micro-architectur                                                                                                                                                         | e   |

|                                            | using Gemmini and Hwacha                                                                                                                                                                                                                      | 129 |

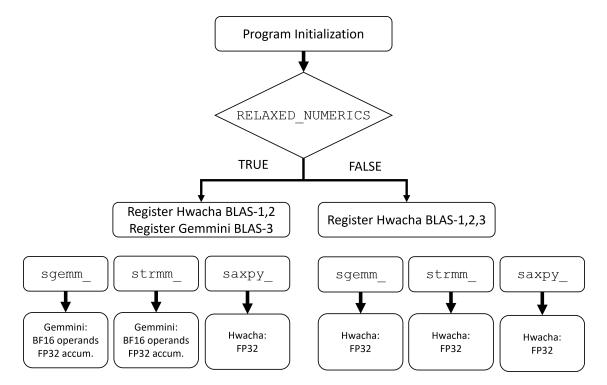

| 7.5                                        | Usage flow diagram of the RELAXED_NUMERICS POSIX environment variable                                                                                                                                                                         | 134 |

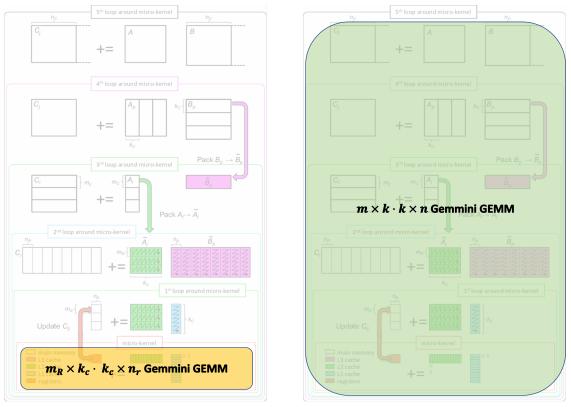

| 7.6                                        | BLIS kernels vs. microkernels and their projection on Gemmini.                                                                                                                                                                                | 135 |

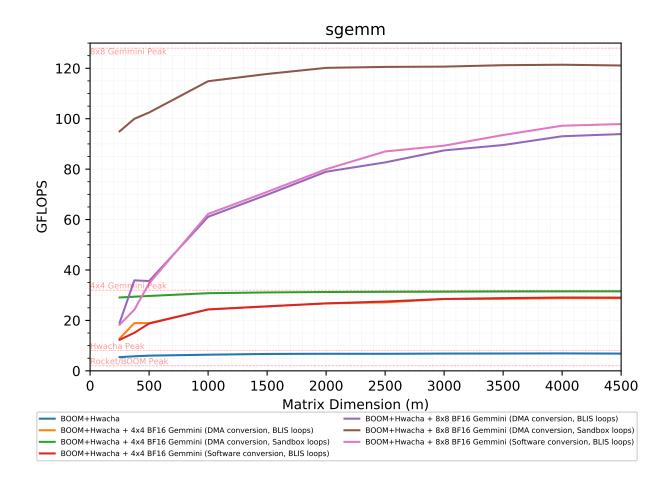

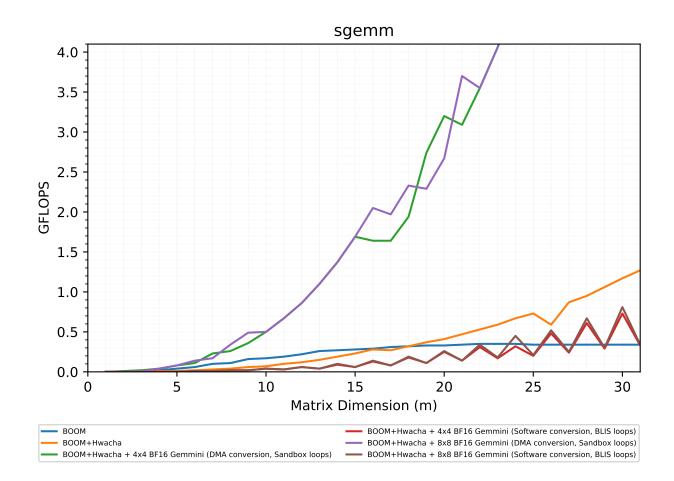

| 7.7                                        | SGEMM kernel performance on square matrices using a 1 GHz SoC with DDR3 backing memory.                                                                                                                                                       | 137 |

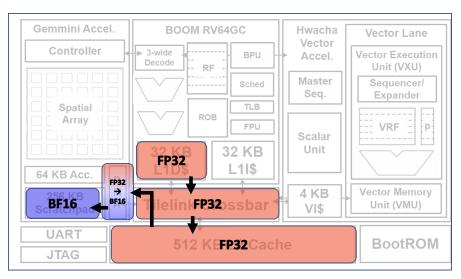

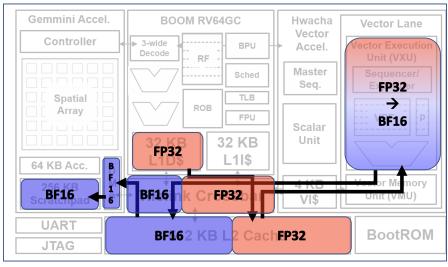

| 7.8                                        | Datatype conversion approaches from 32-bit single-precision floating-point to 16-                                                                                                                                                             | 107 |

|                                            | bit bfloat16 on the target SoC.                                                                                                                                                                                                               | 140 |

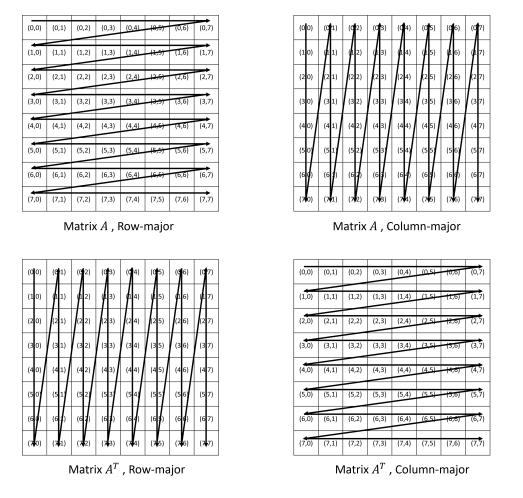

| 7.9                                        | Row-major and column-major matrix data layouts in contiguous memory for                                                                                                                                                                       |     |

|                                            | matrices and their transpose.                                                                                                                                                                                                                 | 142 |

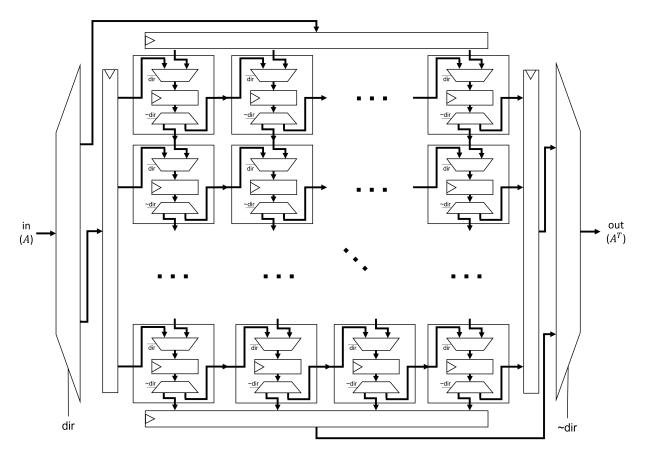

| 7.10                                       | Gemmini Hardware Transposer                                                                                                                                                                                                                   | 144 |

iv

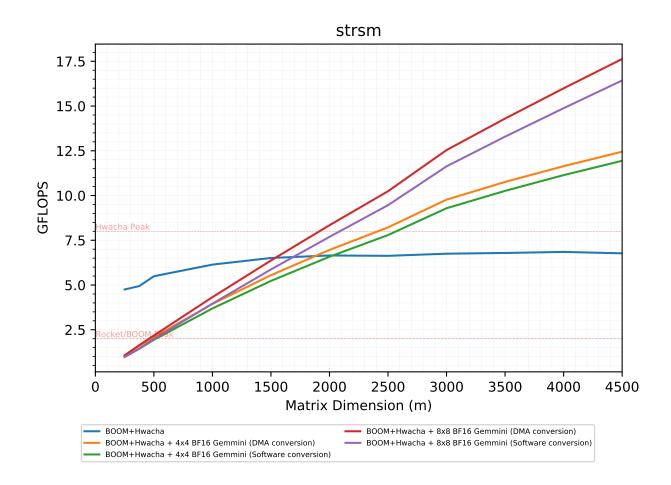

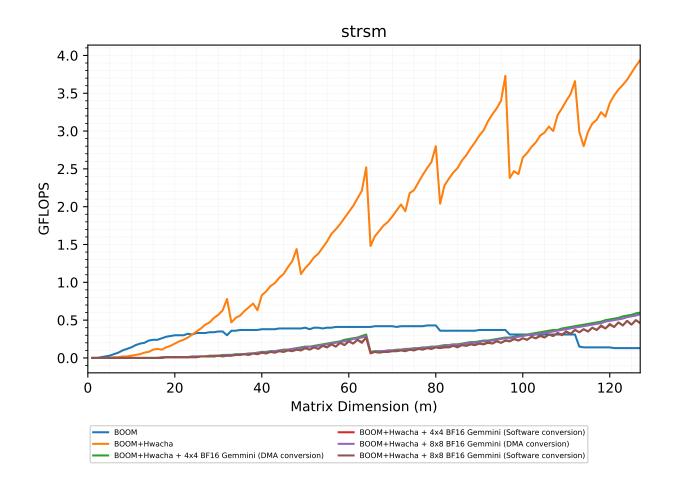

| 7.11         | STRSM kernel performance on square matrices using a 1 GHz SoC with DDR3                |     |

|--------------|----------------------------------------------------------------------------------------|-----|

| <b>-</b> 10  | backing memory.                                                                        | 14  |

| 7.12         | SGEMM kernel performance on small square matrices using a 1 GHz SoC with               | 1 / |

| <b>F</b> 10  | DDR3 backing memory.                                                                   | 14  |

| 7.13         | STRSM kernel performance on small square matrices using a 1 GHz SoC with               | 1 / |

| 714          | DDR3 backing memory.                                                                   | 14  |

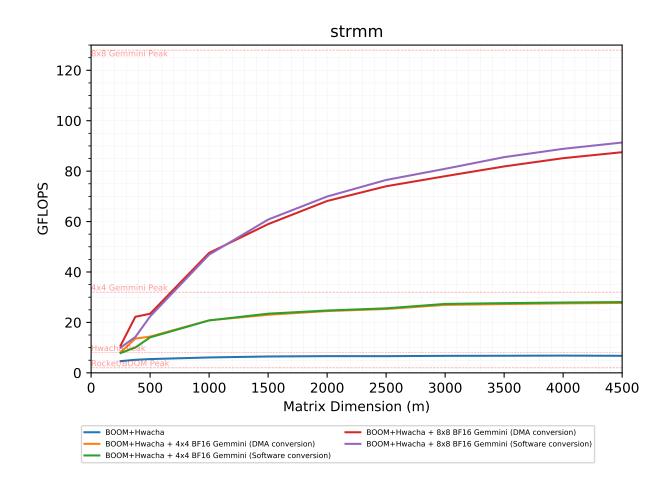

| (.14         | STRMM kernel performance on square matrices using a 1 GHz SoC with DDR3                | 1 5 |

| <b>P</b> 1 F | backing memory.                                                                        | 15  |

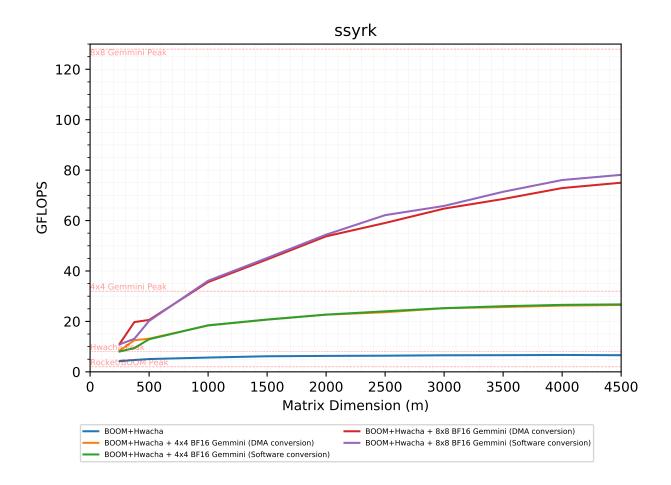

| 7.15         | SSYRK kernel performance on square matrices using a 1 GHz SoC with DDR3                | 1 8 |

| <b>F</b> 10  | backing memory.                                                                        | 15  |

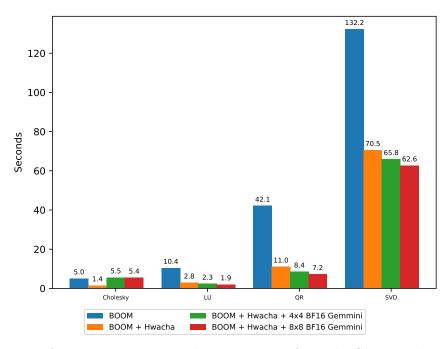

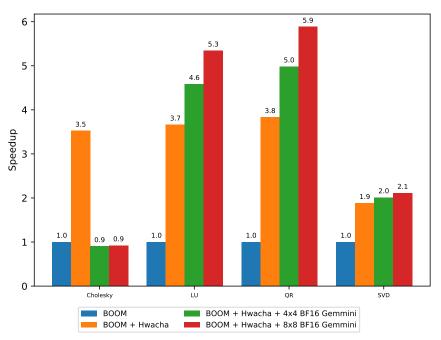

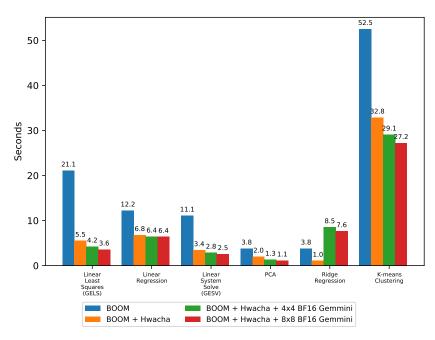

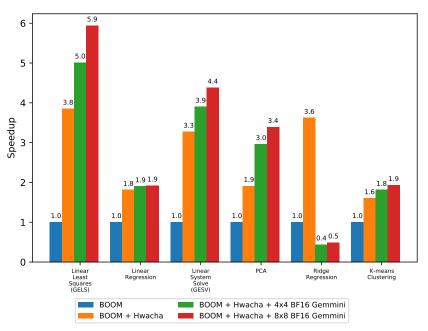

|              | Matrix decomposition performance using custom accelerator BLAS.                        | 15  |

| 7.17         | Application-level performance using custom accelerator BLAS                            | 16  |

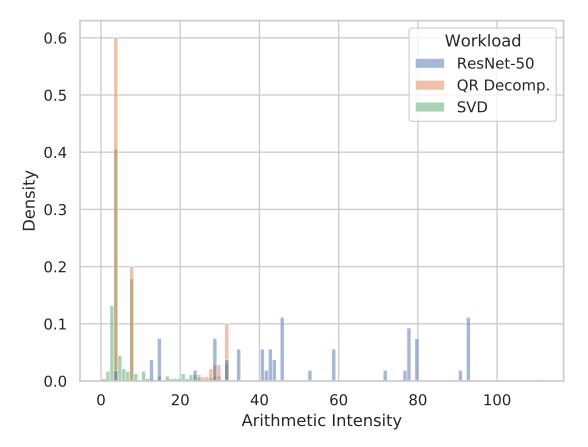

| 8.1          | Arithmetic intensity histogram of BLAS-3 operations within a batch-1 ResNet-50         |     |

|              | DNN forward pass, and a blocked-Householder QR decomposition and SVD of                |     |

|              | the UCI Human Activity Recognition training dataset.                                   | 16  |

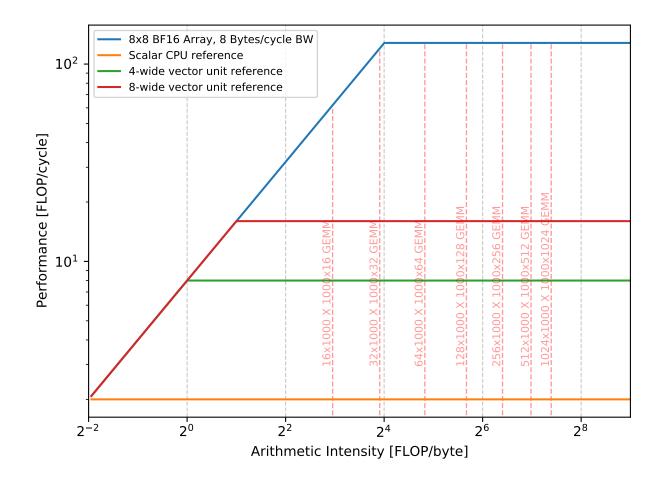

| 8.2          | Theoretical peak performance roofline model for a Gemmini matrix engine                | 17  |

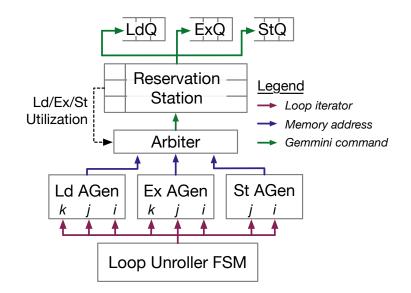

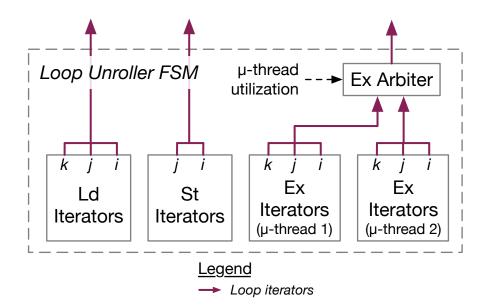

| 8.3          | Gemmini matrix multiplication hardware finite state machine controller                 | 17  |

| 8.4          | Arbitration mechanism between A matrix and B matrix loads in Gemmini's load-           |     |

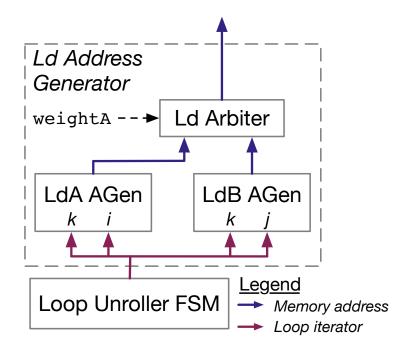

|              | address generator.                                                                     | 17  |

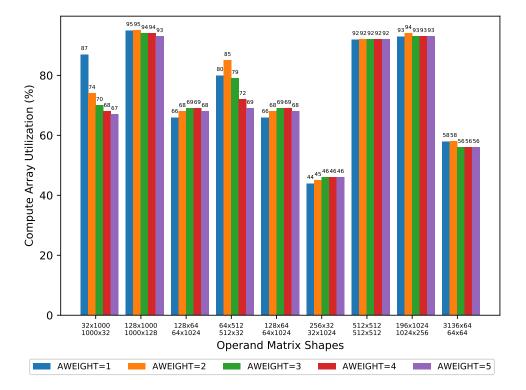

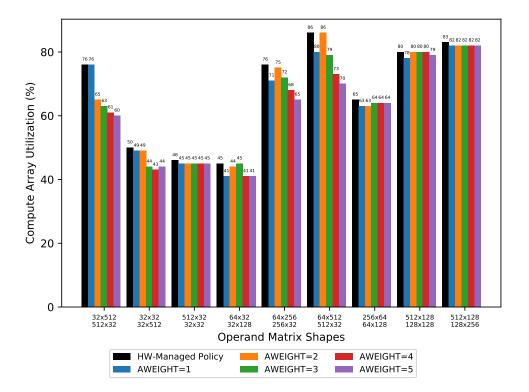

| 8.5          | Gemmini utilization under different hardware controller operand matrix com-            |     |

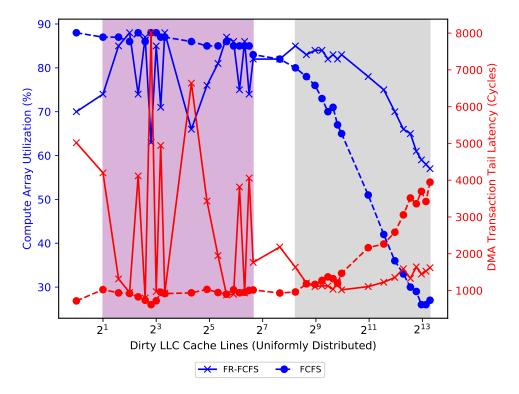

|              | mand arbitration parameter values                                                      | 17  |

| 8.6          | Gemmini utilization and observed DMA tail latency across different shared SoC          |     |

|              | memory system scenarios.                                                               | 17  |

| 8.7          | Gemmini $(8 \times 8)$ utilization using a hardware-managed static scheduling policy.  | 18  |

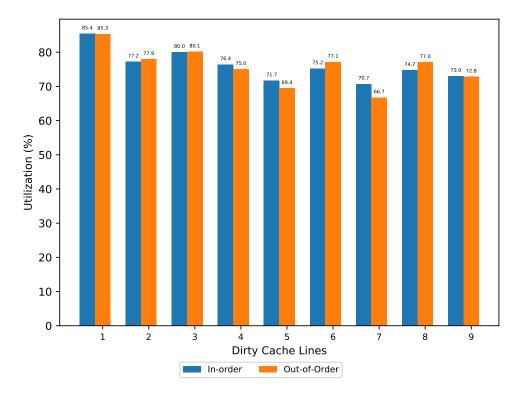

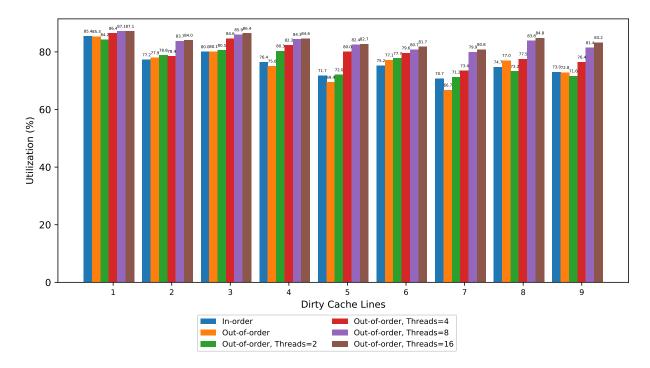

| 8.8          | Gemmini $(8 \times 8)$ in-order vs. out-of-order execution average utilization         | 18  |

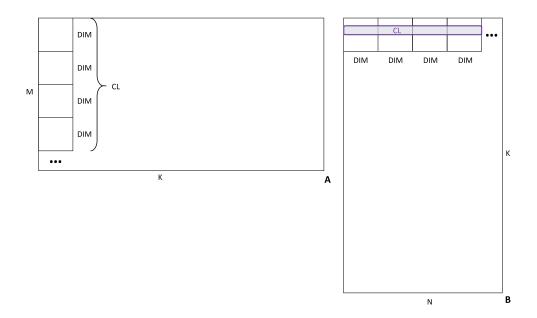

| 8.9          | Example matrix operation blocks depending on a single cache line.                      | 18  |

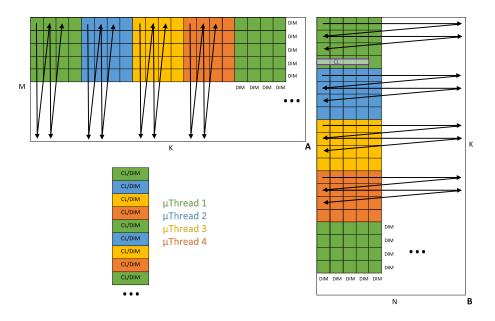

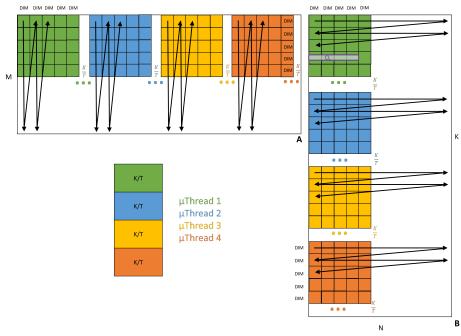

| 8.10         |                                                                                        | 18  |

| 8.11         | *                                                                                      | 19  |

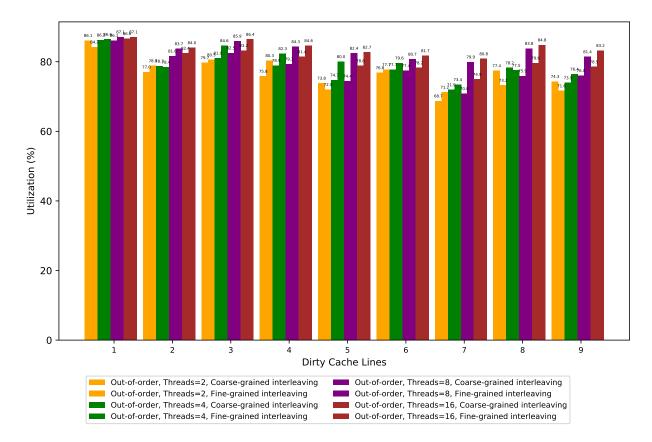

| 8.12         | Comparison of accelerator utilization across Gemmini micro-threads interleaving        |     |

|              | schemes.                                                                               | 19  |

| 8.13         | Gemmini utilization using hardware-managed commutative micro-threads                   | 19  |

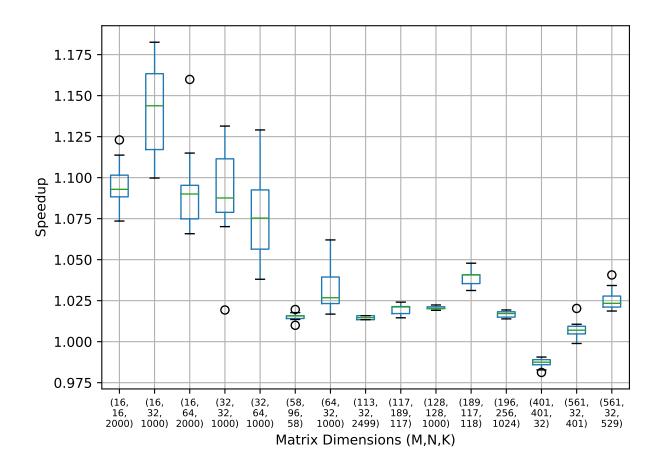

|              | Speedup distributions of an out-of-order $8 \times 8$ Gemmini controller with 8 commu- |     |

|              | tative micro-threads compared to a baseline in-order controller across a collection    |     |

|              | of matrix shapes.                                                                      | 19  |

# List of Tables

| $2.1 \\ 2.2$                              | Building blocks for numerical analysis and their characteristics | $\begin{array}{c} 15\\ 17\end{array}$ |

|-------------------------------------------|------------------------------------------------------------------|---------------------------------------|

| $3.1 \\ 3.2$                              | Example Gemmini generator parameters                             | 31<br>34                              |

| 5.1                                       | Comparison of non-commercial SoC design frameworks               | 68                                    |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Hwacha-based SoC configurations                                  | 90<br>97                              |

| $7.1 \\ 7.2 \\ 7.3$                       | Comparison of BLAS library implementations                       | 125<br>130<br>160                     |

| A.1                                       | RISC-V vector extension proposal draft version comparison table  | 227                                   |

#### Acknowledgments

There are so many people to thank and acknowledge as part of the experience of a PhD. It is often said that a PhD is an individual endeavour, but I believe that in the modern research age it is rare to find any type of work that can succeed without teamwork and collaboration.

I have been fortunate to work with world-class faculty at Berkeley; professors who challenged my way of thinking, but also introduced me to new ideas and perspectives on problemsolving and system trade-offs. I would especially like to thank my supervisors Bora Nikolić and Krste Asanović, as well as Yakun Sophia Shao, Ion Stoica, Kurt Keutzer, Jim Demmel, Randy Katz, and Jonathan Ragan-Kelly who have helped, collaborated, and advised on multiple projects and ideas. I would also like to thank Prof. Bin Yu for serving on the dissertation committee, and for her contributions to my understanding of applied statistics and data science.

As a person with interests spanning across the EE/CS divide, I was lucky to be affiliated with several research centers and labs within the Berkeley EECS department: ASPIRE, ADEPT, and BWRC. I would like to thank the staff who helped ensure that research operations run smoothly, and addressed any issue or question I had with incredible speed and diligence. I could not have completed the work in this dissertation without Tami, Ria, Roxanna, Kosta, and the incredible Candy Corpus. I would also like to thank the research staff who help maintain and expand the research infrastructure that was used in this dissertation - Jim Lawson, Chick Markley and James Dunn. When speaking of people who hold the EECS department together, it would be hard to imagine a Berkeley EECS PhD experience without Shirley Salanio - the guardian angel of EECS graduate students.

I would like to give special thanks to my main partners in crime and leaders of the Chipyard and FireSim projects, Sagar Karandikar, David Biancolin, Abraham Gonzalez and Jerry Zhao. I have learned so much about the computer architecture research community, open-source project management, and software development from them, as well as about what it takes to successfully engage in academic projects as a team, promote open-source projects, and support stable software releases and development cycles. These are invaluable skills that no paper or course could teach me. I would like to give another special thanks to my go-to technical guru, Albert Ou, who would always answer even my most trivial questions at any hour of the day (or night). I've learned countless debugging techniques from Albert, and I was always amazed by his breadth of knowledge across the entire spectrum of the computing stack. I'd also like to thank Hasan Genc, the leader of the Gemmini project, for countless hours of discussions on the phone, and for navigating the project through often challenging paths.

I thank my past and present colleagues, collaborators, and most importantly, friends, in the BAR, ADEPT, ASPIRE, and BWRC labs: Colin Schmidt, John Wright, Albert Magyar, Adam Izraelevitz, Donggyu Kim, Howard Mao, Martin Maas, Nathan Pemberton, Albert Ou, Jenny Huang, Sam Steffl, Seah Kim, Ameer Haj-Ali, Vignesh Iyer, Pranav Prakash, Harrison Liew, Daniel Grubb, Sean Huang, Ben Keller, Pi-Feng Chiu, Andrew Waterman, Jack Koenig, Chris Celio, Eric Love, Arya Reais-Parsi, Dan Fritchman, Dayeol Lee, Dima Nikiforov, James Dunn, Chick Markley, Jim Lawson, Lisa Wu Wills, David Kohlbrenner, Shweta Shinde, Paul Rigge, Keertana Settaluri, and Stevo Bailey. The people of BAR have been more than just colleagues, but friends who I've had the fortune of traveling with across California, in the mountains and on the beaches, in basketball arenas and airplane boneyards, and on countless Zoom lunches throughout the COVID-19 pandemic.

Throughout my time at Berkeley, I was fortunate enough to be an active member of several organizations, including the Electrical Engineering Graduate Student Association (EEGSA), and its CSGSA counterpart. While I initially joined simply as a favor to my friend David Fridovich-Keil to help with some finance and paperwork as a treasurer, I ended up finding an opportunity to make tangible changes impacting the EECS graduate student community and graduate student experience. I was fortunate enough to work with, and learn from, change-makers and friends such as Sylvia Herbert, Josh Sanz, Kelly Fernandez, Justin Yim, Avi Pandey, Sidney Buchbinder, Gabe Fierro, Kristina Monakhova, Kevin Laeufer, Eldon Schoop, Jake Sporrer, Laura Brink, Mike Danielczuk, Saavan Patel, Hani Gomez, Matt and Carolyn Matl, Mauricio Bustamante, Ryan Kaveh, and so many countless others who volunteer their time in order to make Berkeley EECS a better place for current and future graduate students, and make sure that EECS graduate students have an experience that goes beyond just research work.

I also found a welcoming home within the graduate student community of Berkeley Hillel. Whether it was weekly Shabbat dinners, holiday parties, or retreats to the mountains, I always felt the backing and support of the Jewish community and enjoyed contributing back to it. I would like to thank the graduate student community who welcomed me during my first year, including David, Zach, Zoe, Andy, Todd, Mark, Shante, Rosie, Dan, Sara, and Lauren, as well as the Berkeley Hillel staff, particularly Rabbi Adam, Lauren, Molly, Emily, and Danielle.

Looking back at the beginning of this experience, I probably would not have ended up in Berkeley if my friend Eyal Cidon did not convince me to apply for a PhD program in the US. Together with Jenya Pergament, having the support of two high school friends pursuing PhDs in EE and CS in the Bay Area was invaluable, and created an environment where I was always able to get a taste of home when I needed it. While we ended up pursuing our PhDs in rival universities across the bay, I could not have asked for a better high school class (Hebrew Reali School of Haifa class of 2007). Equally as important are my undergraduate professors at Technion who led me to this path, and kept in communication throughout my time in Berkeley, especially Avinoam Kolodny and Ran Ginosar. I'm also grateful to Ruth and Prof. Bob Brayton, who graciously hosted me when I first arrived in Berkeley. Having a place to land when I arrived relieved a lot of stress of the transatlantic relocation, and I will forever be grateful to them for hosting me during that time.

Finally, I would like to thank my family back home. My parents, Gil and Yael, my "fun car" sisters Gal and Maayan, and my newest family member Michael, who were always available for a phone call, video chat, or "half-way" meeting somewhere in Europe. I've had the privilege of growing up in a house with both a love for computers from a very young age,

as well as a sympathetic ear regarding any personal or professional concerns. I always know my family has my back with any choice I make or any problem I have, and that knowledge and feeling can overcome any distance.

This work was supported in part by the Defense Advanced Research Projects Agency through the Circuit Realization at Faster Timescales Program under Grant HR0011-16-C0052 and the Real Time Machine Learning Program under contract FA8650-20-2-7006; in part by the Advanced Research Projects Agency-Energy, U.S. Department of Energy, under Award DEAR0000849; in part by the NSF CCRI Award 2016662; in part by the NSF CISE SHF Award 1955450; and in part by ASPIRE and ADEPT Lab industrial sponsors and affiliates. The views and opinions of the author expressed herein do not necessarily state or reflect those of the U.S. Government or any agency thereof.

# Chapter 1 Introduction

Throughout the past decade, the computing industry has been slowly coming to terms with the reality and challenges of the end of Moore's law. This ending of Moore's law is due to a mix of technological factors, such as the limits of planar lithography-based atomic-scale devices and increased power density resulting from the end of Dennard scaling, as well as economic factors, such as the cost of sub-micron process technologies. Nevertheless, increasingly efficient computing remains a necessity, with the recent big data and machine learning revolutions acting as prime drivers for high-performance computing. Different communities within the computing world have been pursuing multiple research and development efforts in order to continue and meet the increasing computing requirements of the growing software industry. These can generally be classified into three main categories:

- 1. Scale-Out: Distribute the workload across many machines.

- 2. Device and Packaging Physics: New devices, process technologies, packaging technologies, or computing physics such as carbon nanotubes, quantum computing, phase-change memory, memristors, etc.

- 3. Specialization: Specialized hardware for particular applications with limited use-cases.

Each of these approaches provides different capabilities that enable increased computing performance and efficiency, but which also add constraints and assumptions regarding algorithms, software, and fabrication, that limit their usage scenarios when compared with traditional general-purpose computing.

Scale-out computing derives both its power and its limits from the properties of parallelism. Workloads which expose sufficient parallelism theoretically enable unlimited scaling, but at the same time are still limited by Amdahl's law. This ability to scale horizontally benefits from programming models which can generalize to arbitrary parallel programs, flexible application-dependent scaling, and mature software infrastructure platforms such as MPI, MapReduce, Spark, Ray, and DASK [243, 72, 284, 193, 219]. However, this same ability to scale can also incur a large power and energy cost, as synchronization and other overheads of parallel execution can result in less-than-optimal utilization of the underlying computation resources and large amounts of data movement.

Device and Packaging physics provides new properties and capabilities such a nonvolatility, low-power operation, sustainability, and tighter device integration across multiple dimensions. Nevertheless, there are still many open questions in terms of cost, yield, reliability, endurance, size, determinism, and other properties of such devices. Furthermore, such devices will require new design infrastructure, which will take time to mature, as well as new software abstractions that will be able to utilize these new device properties. While advances in device physics provides a long-term prospect for more efficient computing, and packaging innovations have the potential to enable better modularity and scalability, resolving the associated open questions will take time.

Hardware specialization provides the benefits of higher energy efficiency and performance improvements beyond simple parallelism [257], but is limited by programming models, developer productivity and challenging software stacks. Hardware specialization can be performed by using current technologies and tools, and provides immediate impact for a select number of applications. However, it requires an equally expensive investment in software support for each unique instance of hardware. Some examples of specialized hardware include digital signal processors (DSPs), artificial-intelligence (AI) accelerators, field-programmable gate arrays (FPGAs), and graphics processing units (GPUs).

The future of computing will require a combination of these different approaches: scaleout systems with specialized and heterogeneous hardware across different nodes and new device physics supporting custom hardware for lower power based on the specialized properties of each node. In this dissertation, we focus on the hardware-specialization aspects of computing, with a particular interest in machine-learning and data-analysis applications as target workloads and driving applications.

### 1.1 Hardware Specialization

While application-specific integrated circuits (ASICs) have existed since the early days of the microelectronics industry, with common applications in signal processing and communication, specialized hardware has taken the computing industry by storm in recent years. These include mobile application processors, graphics accelerators for gaming and movie production, video transcoders, and AI accelerators. In contrast to traditional ASICs, these specialized processors often involve complex software ecosystems, requiring various levels of programmability and integration with larger and more complex systems. These specialized processors require significant design and fabrication resources, but in return they demonstrate orders-of-magnitude better performance and energy efficiency compared to the general-purpose processor alternative.

In the academic community, specialized accelerators are often designed from scratch and tailored for a particular application or algorithm to demonstrate maximal efficiency of performance through tailored data paths and control paths. This approach is often taken in industry as well, although subsequent generations of the accelerator may build upon the first generation, allowing for some amortization of first-generation design costs.

Nevertheless, the development costs of this approach to specialization are extensive. The design of specialized hardware is a cumbersome process with immense non-recurring engineering (NRE) costs. The drivers of these NRE costs are diverse: they include architecture and detailed design, prototyping, verification, validation, physical design, IP qualification, software development, and much more. A contemporary custom chip can cost well over a hundred million dollars in NRE, and this means that only very high-volume chips are likely to amortize and justify their NRE.

Recent trends in open specifications and open-source software and hardware are helping reduce some of these costs. Free and open instruction set architectures (ISAs) such as RISC-V serve as a substrate for both hardware and software to build upon while providing the freedom for extension and specialization. Similarly, open-source hardware and software efforts help distribute the burden of development and maintenance of common building blocks which do not provide competitive or innovative advantages. This allows for the resources invested in specialization and customization to be re-directed towards innovation rather than boilerplate development.

The state-of-the-art in hardware customization and specialization has primarily focused on methods and tools for hardware description and synthesis. For example, high-level synthesis (HLS) for both ASICs and FPGAs [59, 240] is a tool-based method to rapidly generate hardware descriptions from software programs. However, HLS tools still require nonnegligible manipulation of the high-level software description in order to be able to generate synthesizable hardware. HLS is often a good fit for dataflow-centric hardware with limited control-flow, limiting it to only a subset of the specialized hardware spectrum, leaving open the challenge of full-system customization. Alternative high-level hardware-description frameworks such as Bluespec System Verilog [197] and Chisel [23] attempt to lower the cost of hardware customization by providing high-level hardware-description primitives and functionality while maintaining the RTL abstraction (in contrast to HLS tools, which use software abstractions). While these tools provide platforms for increased productivity in digital hardware design, their benefits remain at the hardware-description productivity level, while the majority of hardware customization costs are still incurred throughout the multiple design flows and system integration stages of hardware customization. To improve productivity at the hardware-system-level, generator-based approaches to processor and digital system design have been proposed as an additional layer on top of high-level hardware-description frameworks [198, 22, 170, 234, 126]. In these generator-based approaches, highly parameterized and modular implementations of digital designs using high-level programming language abstractions enable generation of a broad range of RTL designs. Generators describe digital designs at the RTL level in conjunction with additional functional programming and metaprogramming primitives to encode a high level of parameterization and modularity.

The advancements in hardware description, generation, and synthesis tools help increase hardware design productivity towards the desired goal of lowering the customization cost of complete systems-on-a-chip (SoC). The Oxford English Dictionary defines the word "customization" as modify (something) to suit a particular individual or task. As such, one key perspective in the customization of SoCs is to not start from scratch, but rather re-use components from existing SoCs. As a result, SoC design frameworks have been proposed as platforms for custom SoC design, intended to compose jointly with the aforementioned advancements in hardware developments tools [43, 26, 212]. Efficient re-use of hardware generators in combination with ad-hoc custom hardware description can significantly improve the productivity of custom digital hardware system design. In this work, we demonstrate SoC customization through composition of generators in order to lower the NRE of SoC development. This composition and customization does not end with the hardware description or IP blocks, but continues all along the SoC development flow, including verification, implementation, and software development.

### **1.2** Numerical Data Analysis

Numerical analysis predates the invention of modern computers by several centuries. Nevertheless, since the creation of modern electronic processors and micro-processors, numerical analysis has been a prime consumer of computing technologies and has affected many key developments in the computing industry, including the standardization of floating-point computation and parallel computing platforms.

Numerical computing has been at the core of many scientific modeling and data analysis applications from molecular and atomic dynamics to atmospheric and celestial mechanics. Computation for analysis at these scales requires immense computing capabilities which were the driving applications for the early supercomputers of the 20th century. However, high-performance numerical computing for data-driven analysis, which was once the realm of only scientists and mathematicians, has now become a necessity for a large number of commercial applications and household tasks. New professions in data science and machine-learning research are consuming ever-growing computation resources with the goal of developing data-driven models for insights and prediction. A recent refrain, highlighted in a 2017 article in *The Economist*, identifies data as "the new oil" [206]. The "big data" revolution enables new classes of applications and technologies, many of them centered around machine learning and data analysis.

Throughout the years, many techniques have been developed to extract information from large amounts of numerical data, from early classical statistics to modern deep learning. Optimization, linear modeling, dimensionality reduction, feature extraction, and neural networks require computation over large amounts of numerical data in order to obtain meaningful results. Through heavy reliance on linear algebra, these techniques have been able to utilize the large body of work on high-performance numerical computing using efficient linear-algebra algorithms to enable new tools and data-driven applications. Their high reliance on vector, matrix, and tensor data representations and linear-algebra computations, also make them amenable to hardware customization. As such, state-of-the-art numerical computing software often originates from the requirements of scientific computing and has utilized data-parallel and vectorized computation across platforms ranging from vector supercomputers [125, 223], through packed-SIMD ISA extensions such as Intel's SSE and AVX and ARM's NEON and SVE in general purpose processors [179, 248, 191], and most recently highly parallel programmable GPUs [55, 56]. Recently, the high computational demands of matrix computations in deep-learning applications have led to the addition of specialized matrix and tensor hardware units in processor architectures designed to support high-performance numerical computing [140, 56], as well as discrete tensor accelerators dedicated only to deep learning and the processing of large amounts of data [149]. Writing software for these specialized architectures requires careful attention to data parallelization opportunities, since general-purpose programming languages and tools have yet to achieve efficient automated mapping and compilation to processor architectures beyond traditional scalar processors. State-of-the-art software libraries used for numerical data analysis often manually map common linear algebra operations to specialized architectures in order to achieve high performance and efficiency.

As general-purpose computing increasingly exhibits diminishing performance and efficiency returns with the end of Moore's law, numerical computing and numerical data analysis continue to be a driving force for high-performance computing, with the range of target platforms extending from supercomputers to mobile devices. In this work, we focus on hardware that can be used for modern deep-learning applications as well as traditional statistics, and the customization required for it to be applicable to the broad field of numerical data analysis.

### **1.3** Dissertation Scope and Outline

This work presents tools and methodologies for the development of custom systems-on-chip (SoCs) for numerical data analysis applications. An integrated generator-based framework for SoC development is demonstrated through SoC customization and hardware/software co-design for numerical data analysis and machine learning applications. The development of full system support from hardware accelerators through system software leads to the identification of several co-design opportunities for increasing accelerator utility in custom SoCs.

Specifically, this works builds upon the aforementioned high-productivity hardware description tools and generator-based design approaches but focuses on the system-level aspects of SoC design, which include system configuration and component integration, design-flow integrity, system-level design space exploration, and system-level HW/SW co-design. We demonstrate how re-use and integration of several key generator-based tools together with a unified configuration abstraction provide new capabilities in SoC design, from pre-silicon inception and exploration stages to complete implementation and verification flows. We demonstrate how this approach differentiates generator-based SoC design from alternative SoC design approaches through multiple levels of configurability, and a single source of design truth across the entire hardware and software development flow.

The driving applications throughout the dissertation are numerical data analysis workloads, from deep learning through classical statistics. While the primary focus of recent stateof-the-art hardware specialization has been deep learning, this work highlights a broader class of applications which are based on linear algebra computations for numerical data analysis. This broader class of applications can be supported by custom hardware for vector and matrix computations. As part of the SoC customization process, we highlight generator-based specialized hardware for matrix and vector computations, and its integration as part of a custom SoC. We demonstrate the complete design and customization process, from hardware through software, and highlight the challenges and opportunities enabled through a rapid generator-based customization process for this class of numerical data analysis driving applications. In particular, we identify several co-design opportunities for improved support for small matrix computations, which can be enabled or disabled by the hardware generator during the SoC development process based on the requirements of the custom SoC target application class.

Chapter 2 provides background on numerical data analysis applications, their computational properties and motifs, and techniques used for high-performance numerical analysis.

Chapter 3 provides background on hardware architectures used to accelerate such computational patterns found in numerical data analysis workloads and introduces the Hwacha vector unit and Gemmini matrix engine which are used to accelerate the aforementioned computational patterns within the context of this dissertation.

Chapter 4 introduces ideas and methodologies pertaining to generator-based SoC design, challenges based on previous experiences applying those ideas in practice, and methodological approaches which help address those challenges and encode them using relevant tools and design flows.

Chapter 5 presents the Chipyard integrated SoC-development framework, which is the primary vehicle used to implement the generator-based SoC design methodology, through automation and integrated tooling. This chapter describes the main components and tools of the Chipyard framework, the ways it can be applied to custom SoC design, and its impact on accessibility of education related to custom generator-based SoC design.

Chapter 6 introduces several hardware-software co-design capabilities enabled by generator-based tools within the Chipyard framework. Specifically, it demonstrates full-system design space exploration enabled by generators, debugging and optimization enabled by generator-based FPGA-accelerated simulation, and performance tuning through templated integration of automatically generated software header files.

Chapter 7 presents the customization and mapping of the numerical data analysis software stack onto SoCs designs and hardware accelerators generated by the Chipyard framework, with a particular focus on mapping the data science application stack onto the Gemmini matrix engine.

Chapter 8 presents matrix engine hardware-software co-design opportunities for numerical data analysis applications, identified and evaluated through the mapping of the numerical computing software stack onto Chipyard-generated SoC.

#### CHAPTER 1. INTRODUCTION

Chapter 9 concludes the work by summarizing the key contributions of this dissertation and suggesting opportunities for future research directions.

# Chapter 2

# Algorithms for Numerical Data Analysis

With the extensive availability of digital data, data science has emerged as a discipline linking together knowledge from multiple industries and academic fields in order to harness data to its fullest extent. To this end, data scientists are combining traditional statistical modeling methods with modern deep learning methods to identify new insights from data analysis and construct efficient prediction, inference and training models.

### 2.1 Machine Learning and Numerical Data Analysis

Data analysis enabled by modern computing capabilities has propelled the data revolution into prominence across a multitude of application domains. From anomaly detection and business intelligence (BI) extracted through immense data logs, through biological and genomics research, recommendation systems, computer vision, and natural language processing enabled through advanced modeling methods, the ability to efficiently process large numerical data sets is impacting every aspect of our lives. As the size and diversity of data sets continue to grow, the science around their processing is evolving as well.

Data science spans a wide range of data processing tasks, from data acquisition and cleaning through exploratory analysis to modeling, prediction and inference. The latter parts are often aggregated and referred to as *Machine Learning* (ML). ML is a study of data-driven algorithm development, and is often considered to be a branch of both modern statistics and computer science. Machine-learning algorithms improve and evolve through the collection and refinement of data. The discipline has grown and expanded from traditional statistical methods through data-mining and unsupervised methods to modern deep neural networks. In particular, *numerical data*, in contrast to other data forms such as strings and objects, is amenable to processing founded on the basis of mathematical and statistical algorithms. Such numerical data can be collected through sensors and simulations or be used to model other real-world objects such as images and colors. In this work, we are interested in both exploratory data analysis as well as production data modeling and machine learning pipelines.

Data-modeling pipelines are used for both model construction and training, as well as prediction and inference based on the model. Data-modeling pipelines often require several types of methods, including data preparation, feature extraction, and model construction, all in order to generate insightful data-driven models and conclusions. Each step in these pipelines may require different numerical processing methods. Starting from the source of the data, data-modeling pipelines may compute and validate basic properties of the data such as covariance matrices. Next, numerical data often requires extensive pre- and post- processing to make it amenable for efficient data analysis or training in supervised learning models. Such processing includes data transformation through parsing, permuting and cleaning. An equally important part of processing may include clustering or other dimensionality-reduction techniques to identify important features or reduce the space of classification classes. Dimensionality reduction can also be used to efficiently communicate features and gradients between remote models. The incorporation of a theoretical or formal model within the pipeline may also require solving one or more linear systems in order order to encode additional features. Finally, data passes through the final parts of the modeling pipeline which can incorporate training or inference of various machine-learning models, including linear regressions, support vector machines, deep neural networks, or any other data-driven modeling algorithm. The composition of all these tools and methods often consists of both data movement and numerical transformation of the data, and in particular, linear-algebra-based transformations of the data.

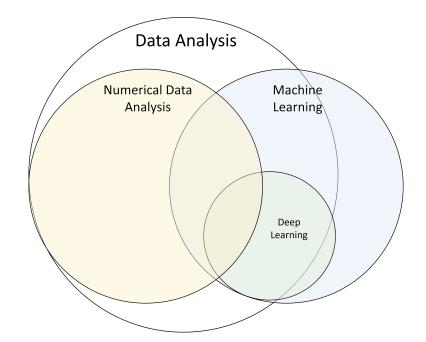

Due to the recent conflation of the terms "machine learning", "deep learning", and "deep neural networks" (DNN), in both scientific and popular literature, throughout this dissertation we will attempt to avoid the term "machine learning". We will use the term "deep learning" or "DNN" to describe machine learning based on deep neural networks, and we will use the term "data analysis" to describe exploratory data analysis as well as what may sometimes be referred to as "classical statistics" or "classical machine learning," which includes dimensionality reduction, clustering, linear models, and so on. Figure 2.1 helps illustrate the differences and overlaps between these categories of domains, with numerical data analysis being a subset of the broader data analysis domain overlapping with machine-learning and deep-learning.

### 2.2 Data Analysis Algorithms and Dense Linear Algebra

The foundation of numerical data analysis and classical statistics is linear algebra: weighted systems of equations, eigenvalue problems, projections, low-rank approximations, and leastsquares regressions, all require extensive numerical computations on tensors, matrices, and vectors. Deep neural networks, which have been the subject of some recent divergence from

Figure 2.1: Data analysis workload categories and overlaps between them.

classical machine learning and statistical methods for data modeling, are also heavily dependent on dense linear algebra computations, to some extent even more so than classical statistics and data analysis. Numerical data sets are typically represented as vectors, matrices, and tensors. Through the manipulation of the dimensionality and geometry of numerical data, dense linear algebra methods extract abstract features, generalizations and anomalies which form the building blocks of data-driven models.

Several examples of key data analysis methods and their associated linear algebra problems include:

- Principal component analysis (PCA) Linear dimensionality reduction by projecting data to a lower-dimensional space. Extracting and selecting the principal components of the data helps reduce the dimensionality of a high-dimensionality dataset while maintaining as much of the data's variation as possible. Dimensionality reduction is especially useful as part of exploratory data analysis, but can also be used as part of a data-modeling pipeline. PCA is in fact the singular value decomposition (SVD) from linear algebra, used to find the orthogonal projection of the matrix.

- Clustering Grouping data samples into groups (clusters) through an unsupervised process based on their numerical features. Two popular forms of clustering are K-means and spectral clustering. K-means clustering partitions the data into k clusters where a data sample belongs to a cluster with the nearest mean, which is typically found through a heuristic iterative process involving several matrix multiplications. Spectral clustering constructs a similarity matrix of the samples in the dataset (based

on some form of similarity), performs an eigen decomposition on the Laplacian of the similarity matrix, and performs K-means clustering on the first k eigen-vectors.

- Linear regressions Construction of a linear model of a system based on a dataset of samples and features. Typically consists of solving a linear least-squares problem on an overdetermined matrix (with the potential additional regularization), sometimes with regularization parameters (Ridge regression, Lasso regression). The linear leastsquares problems can be solved by directly solving the normal equations  $(A^T A x = A^T b)$ or using matrix decompositions such as QR decomposition or SVD.

- Deep neural networks (DNNs) Artificial neural networks with multiple layers between the input and the output, used as universal function approximators and universal classifiers. Artificial neural networks are biologically inspired computing structures, in which each layer is composed of multiple "neurons" which apply a potentially nonlinear transformation on the input. Common layers in DNNs are implemented using matrix-vector multiplications, matrix-matrix multiplications, and convolutions.

- Support vector machines (SVMs) A supervised learning algorithm used primarily for classification and regression. SVMs project the data into a higher-dimensional space in order to construct hyperplanes which can separate classes of data points with maximal margins. Training a support vector machine requires solving a quadratic problem, in which most optimization methods are based on dense linear algebra and matrix multiplications. Inference using SVMs requires summing over a simple matrix-vector or matrix-matrix multiplication related to a kernel function selected to suit the problem.

- Random projections techniques for dimensionality reduction based on probabilistic guarantees, where points from a sufficiently high dimensional space are projected to a lower-dimensional space while maintaining the pairwise distances between the points. The projection is performed by multiplying the original data matrix of size  $m \times n$  with a random matrix of size  $n \times k$ , where k is the desired lower dimension. The random matrix is initialized based on a known distribution (for example, Gaussian) and has normalized columns.

While this list in not exhaustive, in this work, we focus workloads that act as part of the data-modeling pipeline, including dimensionality reduction through clustering and PCA, linear modeling, and deep neural networks. Together, these techniques allow data scientists to construct and analyze complex numerical datasets with both explicit and latent properties.

### 2.3 High-Performance Numerical Data Analysis

The foundations of computer-based numerical data analysis lie in the lessons learned from years of research in high performance computing that have had long lasting implications on the modern data analysis software stack.

While early high-performance numerical computing libraries were designed primarily with re-usability in mind, their portability and taxonomy later enabled performance optimization techniques thanks to their well-defined interfaces and problem structures.

The high-performance computing community has identified that by partitioning linear algebra problems into "blocks" (or "tiles"), one can extract two primary advantages which assist in obtaining high performance from a parallel computer with a memory hierarchy: **parallel processing** both at the inter-block level and the intra-block level, and reduction of **communication** through a surface-to-volume effect for the ratio of operations to data movement [76]. These principles lie at the core of high-performance numerical data analysis in both hardware and software implementations.

#### Parallel Processing

Computer architecture literature traditionally recognizes three major types of parallelism: *instruction-level* parallelism (ILP), *thread-level* parallelism (TLP, sometimes also called task-level parallelism) and *data-level* parallelism (DLP):

- Instruction-level parallelism represents the ability to overlap the simultaneous execution of multiple instructions within a single instruction stream (or thread).

- Thread-level parallelism represents the ability to overlap the simultaneous execution of multiple independent instruction streams, implying multiple independent program counters.

- Data-level parallelism represents the ability of a single operation or instruction to be performed simultaneously on multiple elements of data (whether in a single instruction stream or multiple instruction streams).

All three types of parallelism can be exploited both through software techniques and hardware techniques, although some may be more prevalent than others. ILP is most commonly exploited in hardware implementations through pipelining, dynamic scheduling and speculation. High-performance software will extract ILP through software pipelining, loop unrolling and Very Long Instruction Word (VLIW) compilation to assist the hardware in overlapping independent instructions. TLP is most often exploited in hardware through multi-processors (sometimes called multi-core processors) and simultaneous multithreading (SMT) processors. Software will extract TLP using threading libraries such as POSIX threads (pthreads) or OpenMP. DLP can be exploited in hardware using single-instruction multiple-data (SIMD) instructions which enable static scheduling and wide datapaths. Software will utilize datalevel parallelism through explicit SIMD programming, auto-vectorizing compilers (which transform loops to SIMD instructions), and high-level data-parallel programming languages. ILP, TLP and DLP are not mutually exclusive, and are typically used in tandem in order to maximize processor performance.

#### Communication

Algorithms generally have two types of costs: arithmetic and communication. *Communication* is the cost of moving data between levels of a memory hierarchy or over an interconnect connecting processing units. The cost of communication can often be reduced to two main components: bandwidth and latency [27]. Communication can be observed in computer architecture across various levels of the computing system: I/O, on-chip networks, off-chip networks, and the memory hierarchy. Communication-avoiding algorithms have been researched since the early 1970s-1980s [155, 89, 147] with the goal of improving performance through reduction in communication costs.

While parallel processing may help reduce the arithmetic cost of an algorithm, it often incurs an additional communications cost. For example, a lower-bound on communication in parallel matrix multiplication for the "memory-scalable" case was found to be  $\Omega(n^2/\sqrt{P})$ , where P is the number of processors [142]. As can be observed, in a parallel system with P processors, this means that the lower bound on the total amount of communication in the system would be  $\Omega(P \times n^2/\sqrt{P}) = \Omega(\sqrt{P} \times n^2)$ , which is  $\sqrt{P}$  times the lower bound of communication in the single-processor memory-scalable case (P = 1).

Similar communication lower bounds pertaining to sparse and dense linear algebra problems have been proven in recent years [27], leading to advances in communication-optimal algorithms that are used across a variety of numerical data analysis problems. These communication-avoiding schemes can be captured both in software implementations and specialized hardware implementations which rely on high degrees of computational parallelism.

### 2.4 Arithmetic Intensity of Numerical Data Modeling Kernels

From a computational perspective, dense linear algebra is considered to be a computeintensive class of workloads. A useful measure of whether a workload is likely to be computebound or memory-bound is the arithmetic intensity (or operational intensity) of the workload [277]. Arithmetic intensity is a property of a workload or an algorithm (as opposed to a property of the "problem", or a property of the hardware). It measures the ratio between computational (arithmetic) operations to data movement operations. As such, it measures the ratio of operations which require processing capabilities vs. operations which require memory capabilities (or memory bandwidth). The definition of an "operation", as well as the exact units used to measure arithmetic intensity, may change based on the context of the problem. In high-performance scientific computing, arithmetic intensity is often measured in floating-point operations (FLOPs<sup>1</sup>), while data movement is measured in bytes.

<sup>&</sup>lt;sup>1</sup>Due to frequent confusion, we clarify that the notation "FLOPs" is the plural of FLOP (a **FL**oatingpoint **OP**eration), and measures operation count, while the notation "FLOP/s" or "FLOPS" is a measure of throughput, denoting floating-point operations per second

As a corollary, since deep-learning inference may use quantized integer computations rather than floating-point computation, the arithmetic intensity measure for deep neural networks uses integer operations (OPs) rather than floating-point operations. Similarly, some deeplearning researchers consider only the data movement of weight parameters rather than data movement of both weight and activation data [149]. In this work, we consider all necessary data movement, including DNN activation data.

Table 2.1 lists the arithmetic intensity properties of several key dense linear-algebra operations used for numerical data analysis. In particular, we focus on matrix operations and matrix decompositions, since numerical datasets are often represented in the form of matrices. We observe that most matrix operations have arithmetic intensity that grows with the size of the input matrix. There is a large body of work on increasing the arithmetic intensity of matrix decomposition algorithms and minimizing communication using blocking/tiling techniques. We further elaborate on these within the context of the LAPACK and BLAS software libraries in Chapter 7.

A particular subset of dense linear algebra and machine learning of recent interest are operations that compose deep neural networks (DNNs). DNNs have been at the forefront of advancements in computer vision, natural language processing (NLP) and additional datadriven modeling and prediction domains. They are made up of a large and diverse class of linear algebra operations ranging from convolutions, through sparse and dense matrixvector and matrix-matrix operations, and even optimization and gradient computations as part of the training process. Table 2.2 lists several key DNN operators and their arithmetic intensity properties. Typical layers in computer vision DNNs include spatial convolutions, which perform two-dimensional or three-dimensional convolutions over the input tensors  $(O_{k,p,q} = \sum_{r}^{R} \sum_{s}^{S} \sum_{c}^{C} X_{c,p+r-R/2,q+s-S/2} W_{k,c,r,s})$ ; fully connected layers, which multiply an input feature vector by a weight matrix  $(o_i = \sum_{j} W_{ij} x_j + b_i)$ ; and pooling layers, which reduce the dimensions of activation tensors through averaging, maximizing or minimizing across the size of a filter. Typical layers in NLP DNNs include embedding layers, which transform an object from a vocabulary encoded as a one-hot vector into a vector embedded within a high-dimensional space by performing a table-lookup operation; long short-term memory (LSTM) layers, which are recurrent layers that use feedback connections between features across the time dimension  $(h_t = NonLinearity(W_{ih}x_t + b_{ih} + W_{hh}h_{(t-1)} + b_{hh}))$  together with a set of gates to regulate the flow of information in order to control vanishing gradients; and attention layers, which build upon bi-directional LSTMs and add all-to-all relationships across input feature vectors through additional weight matrices (effectively resulting in a series of matrix multiplications) [266]. Notably, a large number of DNN operators exhibit arithmetic intensity that grows with the size of their parameters (a "surface-to-volume" effect).

Research on deep neural networks has traditionally focused on improving their inference accuracy and generalization ability, often through larger numbers of parameters and increased amount of computation. As such, compositions of operators such as spatial convolutions, fully connected layers, and attention, are continuously increasing the computational cost of deep neural networks. We note that throughout the evolution of deep neural net-

|                                                    | FLOPs                                             | Memory Footprint                                                    | Arithmetic Intensity                                                                                                |

|----------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Matrix-Vector<br>Multiplication                    | 2nm                                               | nm + 2m                                                             | $\frac{2n}{n+2}$                                                                                                    |

| Matrix<br>Multiplication                           | 2nmk                                              | nm + mk + kn                                                        | $\frac{2nmk}{nm+mk+kn}$                                                                                             |

| LU Decomposition                                   | $mn^2 - n^3/3$                                    | mn                                                                  | $\frac{mn^2 - n^3/3}{mn}$                                                                                           |

| QR Decomposition<br>(Blocked Householder*)         | $2mn^2 - 2n^3/3$                                  | $mn + \mathcal{O}(nb)$                                              | $\frac{2mn^2-2n^3/3}{mn+\mathcal{O}(nb)}$                                                                           |

| Cholesky<br>Decomposition                          | $n^3/3$                                           | $n^2/2$                                                             | $\frac{2}{3}n$                                                                                                      |

| Singular Value<br>Decomposition <sup>**</sup> [99] | $\Sigma: 4mn^2 - 4n^3/3$ $U, V: kRn + 2Rmn + 4Rn$ | $\Sigma: mn + \mathcal{O}(m)$ $U, V: m^2 + n^2 + \mathcal{O}(4n^2)$ | $\Sigma: \frac{4mn^2 - 4n^3/3}{mn + \mathcal{O}(m)}$ $U, V: \frac{kRn + 2Rmn + 4Rn}{m^2 + n^2 + \mathcal{O}(4n^2)}$ |

| Linear<br>System Solve                             | $\frac{2}{3}n^3 + 2n^2$                           | $n^2 + 3n$                                                          | $\frac{\frac{2}{3}n^3 + 2n^2}{n^2 + 3n}$                                                                            |

| Linear<br>Least Squares*                           | $2mn^2 - 2n^3/3 + 2mn + n^2$                      | mn + nb + m                                                         | $\frac{2mn^2 - 2n^3/3 + 2mn + n^2}{mn + nb + m}$                                                                    |

Table 2.1: Building blocks for numerical analysis and their characteristics (LAPACK 3.9.0 implementations, matrix size  $m \times n$ ).

\*The parameter *b* represents the block size in a blocked algorithm. We assume m > n. \*\*SVD is solved using iterative algorithms. Therefore, the number of FLOPs and memory footprint can only be estimated. We estimate the number of FLOPs based on the cost of various operations within the SVD listed in Golub and Van Luan [99], assuming *k* iterations, m >> n, and computing *R* singular vectors.

works, a subset of networks have focused on improving efficiency as opposed to accuracy of DNNs [280, 130]. This class of computationally efficient DNN models, which are designed to run within latency and energy constrained environments, is based on a set of computationally efficient operators with smaller parameter sets or higher arithmetic intensity. These operators include depthwise convolution, pointwise convolution, and group convolution, each of which reduces or partitions one of the dimensions of the traditional spatial convolution. The pointwise convolution is a traditional spatial convolution with a filter size of  $1 \times 1$ . As such, it has smaller parameter memory footprint, but also lower arithmetic intensity. A spatially separable convolution factorizes a square  $(R \times R)$  convolutional filter into two vectors  $(1 \times R \text{ and } R \times 1)$ , hence reducing the parameter memory footprint and arithmetic operation count by a factor of the filter size (R). The group convolution partitions the input channels and output channels to G groups, removing dependencies between the groups. This reduces

the number of compute operations and parameter size by a factor of G, but also reduces data re-use (due to the elimination of data-reuse across groups). A particular case of group convolution, in which the number of groups is equal to the number of input channels is called "depthwise convolution". This operation, which was popularized in DNNs models designed for small memory footprints (e.g. MobileNet [127]), has very low arithmetic intensity since it effectively maximizes the reduction in data re-use in group convolutions by maximising the number of groups, which may sometimes lead to a performance degradation despite the decrease in memory footprint and arithmetic operation count. We include several such efficient operators in Table 2.2 to demonstrate the impact of operator and layer selection on the arithmetic intensity of DNN inference.