# UCLA UCLA Electronic Theses and Dissertations

# Title

Microwave Power Limiters Exploiting the Insulator to Metal Transition of Lanthanum Cobalt Oxide

Permalink https://escholarship.org/uc/item/79w411qw

Author Bhattacharya, Rajashree

**Publication Date**

2023

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Microwave Power Limiters Exploiting the Insulator to Metal Transition of Lanthanum Cobalt Oxide

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Materials Science and Engineering

by

Rajashree Bhattacharya

© Copyright by

Rajashree Bhattacharya

## ABSTRACT OF THE DISSERTATION

# Microwave Power Limiters Exploiting the Insulator to Metal Transition of Lanthanum Cobalt Oxide

by

Rajashree Bhattacharya

Doctor of Philosophy in Materials Science and Engineering

University of California, Los Angeles, 2023

Professor Dwight Streit, Chair

The objective of this work is to leverage the unique insulator to metal transition of Lanthanum Cobaltite (LaCoO<sub>3</sub>, LCO) towards the next generation of power limiters for high temperature, wide bandwidth, and high-power operation. LaCoO<sub>3</sub> is a semiconducting perovskite that demonstrates a spin-state transition to metallic behavior about 500 K. In this dissertation we establish a wafer-scale reactive sputtering deposition process, characterize the temperature-dependent properties of thin film LCO, and estimate the thermally driven band gap collapse by near-IR absorption measurements.

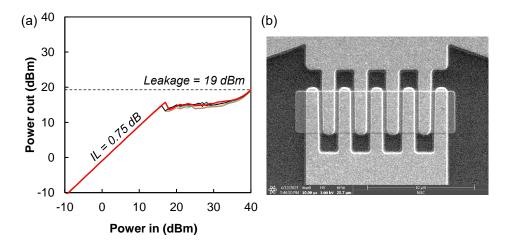

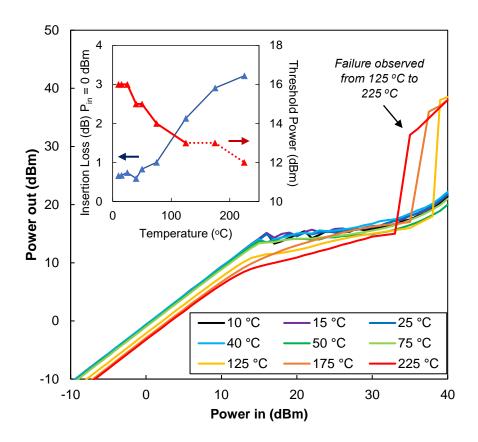

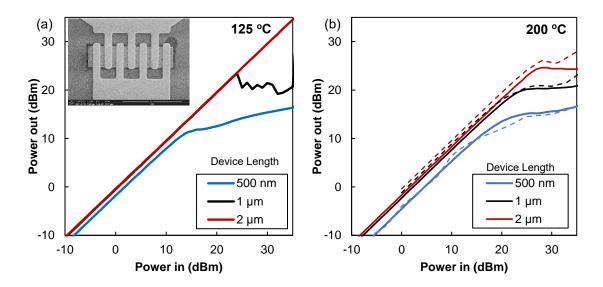

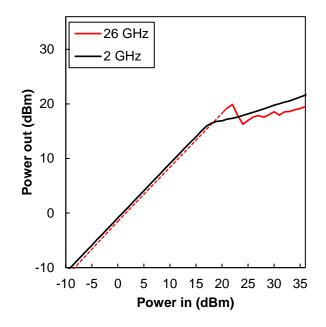

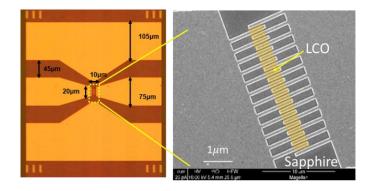

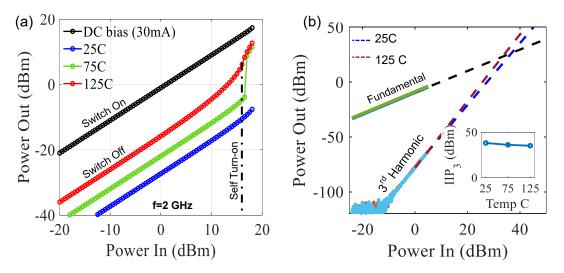

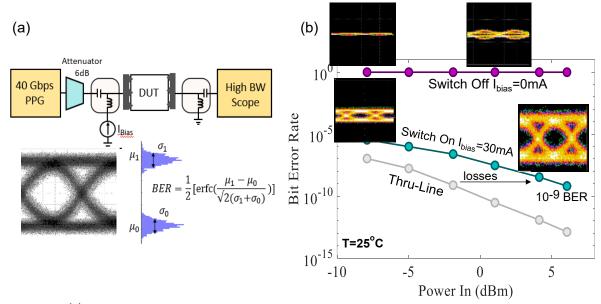

The aforementioned sputtering process was used in the fabrication of power limiters that can be triggered either by external DC bias or by self-turn on at an input power threshold around 16 dBm. We present a 2 GHz LCO-based shunt power limiter constructed on silicon carbide with continuous wave power handling capability of 40 dBm, flat leakage of 20 dBm, and insertion loss less than 1 dB over a broad operating temperature range of 10 °C to 75 °C. Furthermore, very high temperature limiting response is recorded up to 225 °C with a flat leakage of 15 dBm and power handling up to 33 dBm. LCO limiters of varied dimensions and geometries were studied to better understand the necessary tradeoffs in design for low insertion loss and high-power handling. To that end, a 3D COMSOL Multiphysics simulation was also developed that accurately predicts limiting performance and switching speed. This model is used to propose further improvements to the power limiter design.

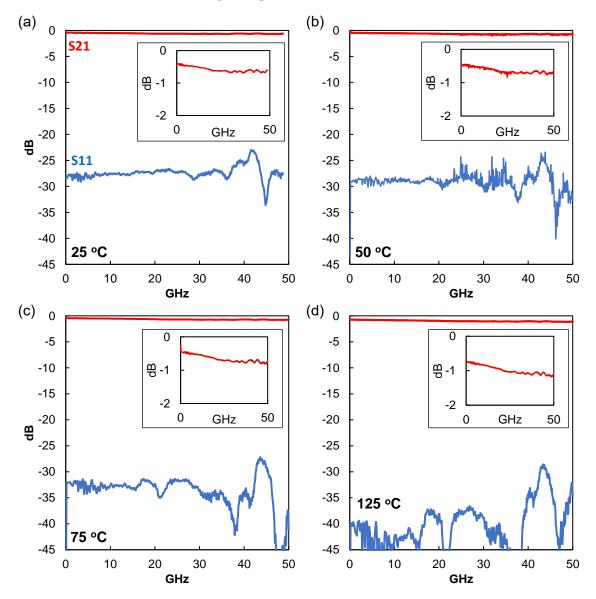

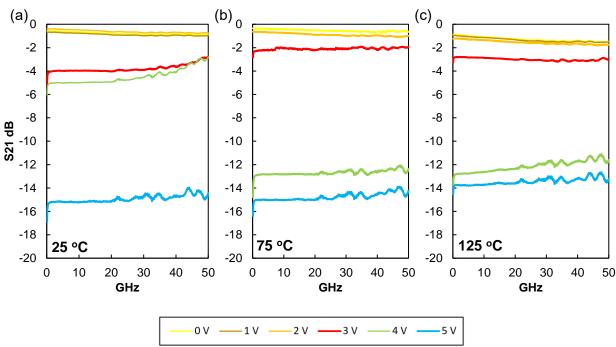

S-parameter testing was conducted from 0.1 to 50 GHz, verifying the broadband viability of LCO microwave devices. We present extremely low small signal losses, with a maximum insertion loss of 1.2 dB at 125 °C and 50 GHz. Benchmarking against both recent research art and commercial products indicates that LCO is a strong candidate for the next generation of microwave power limiters. Finally, we conclude the thesis with an evaluation of an LCO-based series radio frequency switch fabricated on sapphire substrate. We further summarize and discuss the significant potential of LCO in a wide range of thermally or electronically driven switching applications. The dissertation of Rajashree Bhattacharya is approved

Mark Goorsky

Aaswath Raman

Subramanian Iyer

Vincent Gambin

Dwight Streit, Committee Chair

University of California, Los Angeles

# DEDICATION

For Raja and Swetha Bhattacharya, with love and gratitude for all you gave

# TABLE OF CONTENTS

ABSTRACT OF THE DISSERTATION

| DEDICATION                                                    |

|---------------------------------------------------------------|

| TABLE OF CONTENTS                                             |

| LIST OF FIGURES                                               |

| LIST OF TABLES                                                |

| ACKNOWLEDGEMENTS                                              |

| VITA                                                          |

| Chapter 1: Background and Motivation 1                        |

| 1.1 Introduction to Radio Frequency Power Limiters 1          |

| 1.1.1 Metrics of Limiter Performance                          |

| 1.1.2 Current Art 4                                           |

| 1.2 "Smart Materials" and the Insulator to Metal Transition 7 |

| 1.2.1 Vanadium Dioxide 8                                      |

| 1.2.2 Lanthanum Cobalt Oxide10                                |

| 1.3 My contribution to the field15                            |

| Chapter 2: Deposition of Thin Film Lanthanum Cobalt Oxide17   |

| 2.1 Abstract                                                  |

| 2.2 DC Magnetron Sputtering17                                 |

| 2.2.1 Berg sputtering theory18                                |

| 2.3 Film Growth23                                             |

| 2.3.1     | Methodology                                        | 23 |

|-----------|----------------------------------------------------|----|

| 2.3.2     | Influence of substrate                             | 25 |

| 2.3.3     | Influence of stoichiometry                         | 27 |

| 2.4 E     | Estimation of Band Gap Collapse                    | 28 |

| 2.4.1     | Methodology                                        | 29 |

| 2.4.2     | Results                                            | 30 |

| 2.5 C     | Conclusions                                        | 31 |

| Chapter 3 | 3: 2-Terminal Voltage-triggered Switches           | 33 |

| 3.1 A     | Abstract                                           | 33 |

| 3.2 C     | Contact metal evaluation by transfer length method | 33 |

| 3.3 V     | Voltage-Triggered Abrupt Transition                | 36 |

| 3.3.1     | Methodology                                        | 36 |

| 3.3.2     | Results                                            | 37 |

| 3.4 T     | Fransient Switching Characteristics                | 41 |

| 3.4.1     | COMSOL Multiphysics Simulation Set-up              | 41 |

| 3.4.2     | Nano-second scale switch at 75 °C                  | 43 |

| 3.5 S     | Supplemental                                       | 44 |

| 3.5.1     | COMSOL Simulation Parameters                       | 44 |

| Chapter 4 | 4: LaCoO3 - based RF Shunt Power Limiter           | 46 |

| 4.1 A     | Abstract                                           | 46 |

| 4.2 M     | Methodology                                        | 47 |

| 4.2.1      | Device Structure and Fabrication47                    |

|------------|-------------------------------------------------------|

| 4.2.2      | RF Measurement: Power-in, Power-out49                 |

| 4.2.3      | Simulation set-up                                     |

| 4.3 Pil    | Po Results                                            |

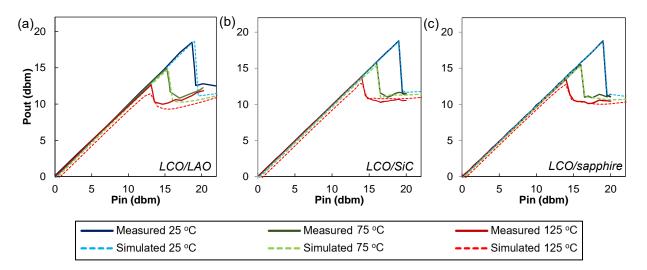

| 4.3.1      | Interdigitated Limiter on Various Substrates51        |

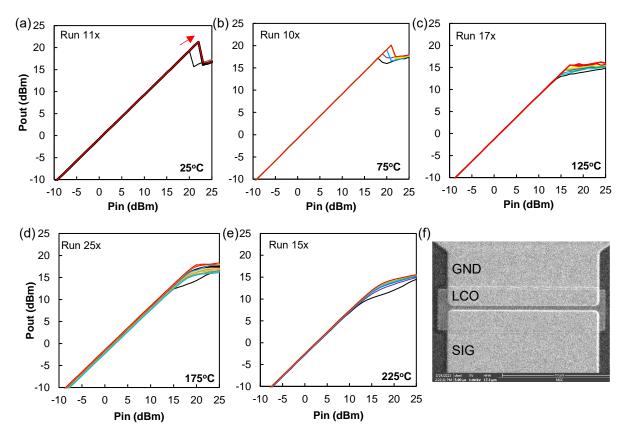

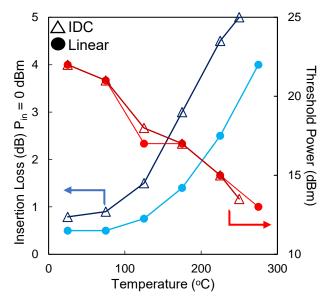

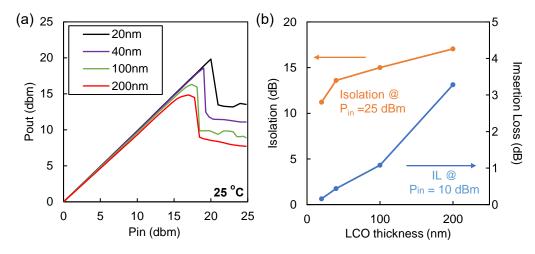

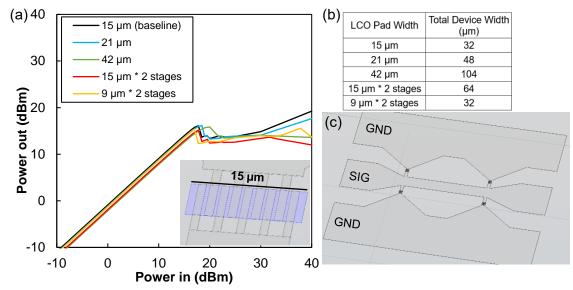

| 4.3.2      | Interdigitated versus Linear Geometry on SiC54        |

| 4.3.3      | Demonstrated Resilience up to 40 dBm58                |

| 4.3.4      | Increasing device length60                            |

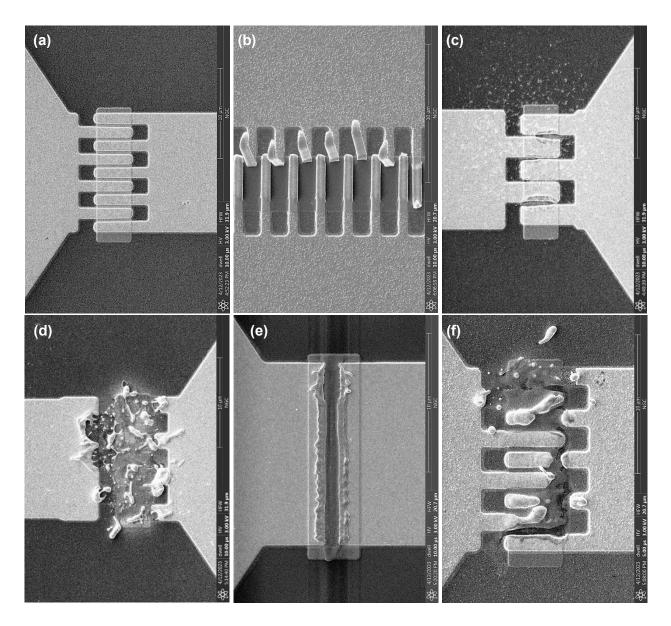

| 4.4 Fa     | ilure Analysis61                                      |

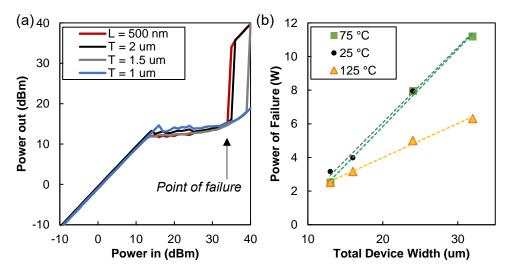

| 4.5 Si     | mulation Predictions of Changes to Limiter Geometry66 |

| 4.5.1      | Increasing LCO Thickness                              |

| 4.5.2      | Increasing Total Device Width67                       |

| 4.6 Be     | nchmarking69                                          |

| 4.7 Co     | nclusions70                                           |

| 4.8 Su     | pplementary72                                         |

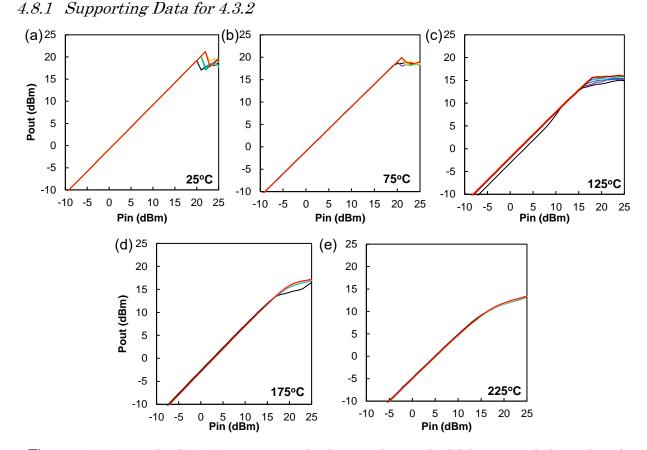

| 4.8.1      | Supporting Data for 4.3.272                           |

| 4.8.2      | COMSOL Simulation Accuracy against Measured Devices72 |

| Chapter 5: | High Frequency Performance and DC Bias Turn-on74      |

| 5.1 Ab     | ostract74                                             |

| 5.2 Me     | ethods74                                              |

| 5.2.1      | S-parameter Set-up75                                  |

| 5.3 Rea     | sults                                              |

|-------------|----------------------------------------------------|

| 5.3.1       | Effect of Temperature on Loss                      |

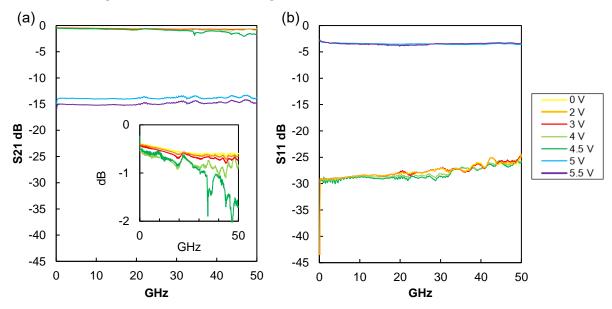

| 5.3.2       | DC bias Turn-on, Linear Device78                   |

| 5.3.3       | High frequency behavior, Interdigitated geometry80 |

| 5.4 Co      | nclusion81                                         |

| Chapter 6   | LaCoO3 - Beyond Power Limiters83                   |

| 6.1 Su      | mmary85                                            |

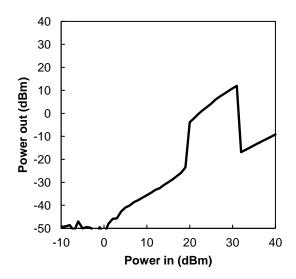

| 6.2 RF      | Series Switch                                      |

| 6.2.1       | Design and Fabrication83                           |

| 6.2.2       | Results                                            |

| 6.3 Otl     | her avenues of research87                          |

| References. |                                                    |

#### LIST OF FIGURES

- Figure 1.4 (a) compilation of resistance drop ratios for known IMT materials (b) comparison of transition profiles for bulk LaCoO<sub>3</sub> and polycrystalline VO<sub>2</sub>......11

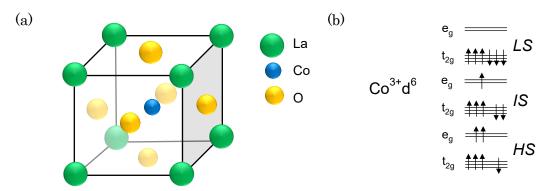

- Figure 1.5 (a) Pseudocubic perovskite structure for LaCoO<sub>3</sub> (b) progression of the Co<sup>3+</sup> spin state transition from Low Spin S=0, to Intermediate S=1, and High Spin S=2.....12

| Figure 2.6 X-ray diffraction                      | n pattern of 150 nr | n lanthanum | cobalt oxide | films at varying |

|---------------------------------------------------|---------------------|-------------|--------------|------------------|

| composition deposited on (a) LAO and (b) sapphire |                     |             |              |                  |

- Figure 2.8 Tauc plots, used to estimate band gap collapse over temperature for 150 nm sputtered LCO grown on (a) LAO (b) sapphire (c) fused quartz......30

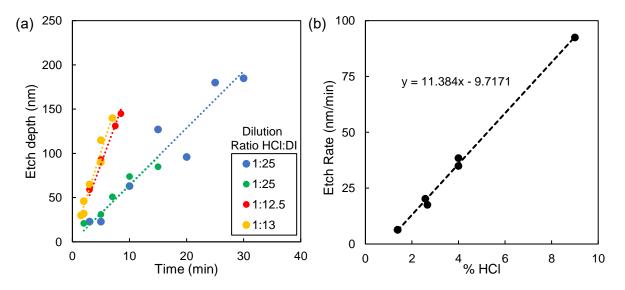

- Figure 3.3 (a) Trench etch depth for 100  $\mu$ m features for various dilution ratios of 37% HCl to DI water (b) calculated etch rate of LCO as a function of % HCl......36

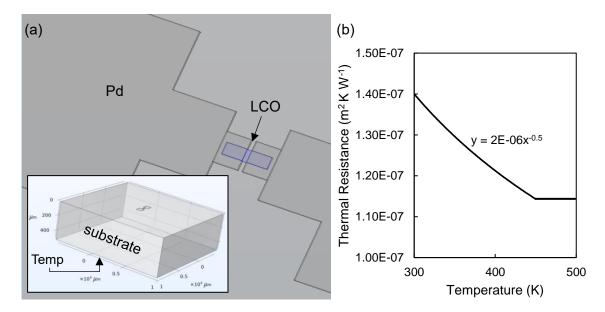

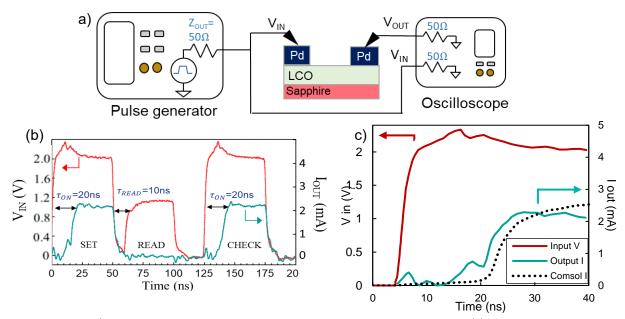

Figure 3.8: a) Schematic of set-up for fast pulsed measurement at 75 °C. (b) Repeated probing oscillating from set bias of 2 V to read bias of 1 V © IEEE 2022 (c) Zoom-in into turn-

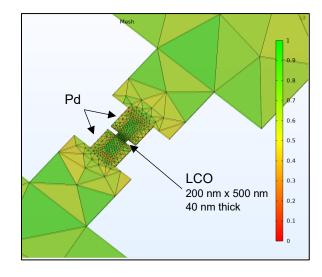

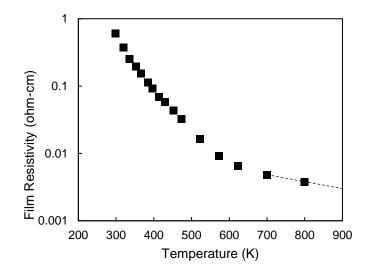

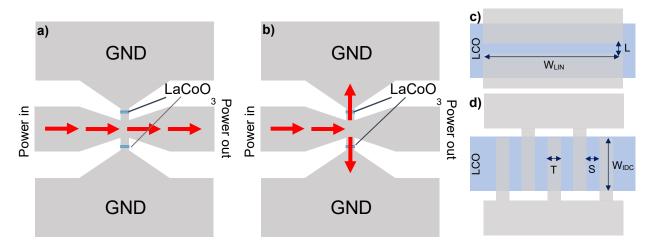

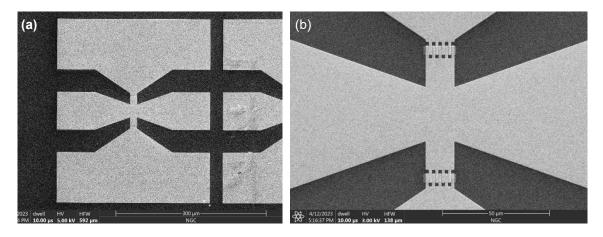

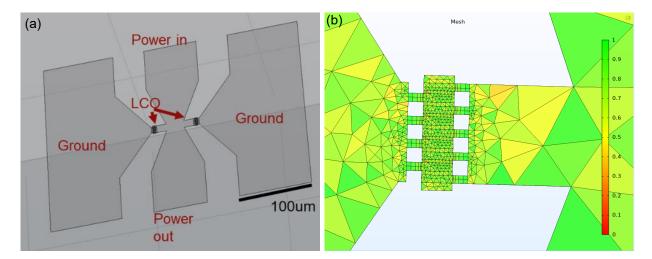

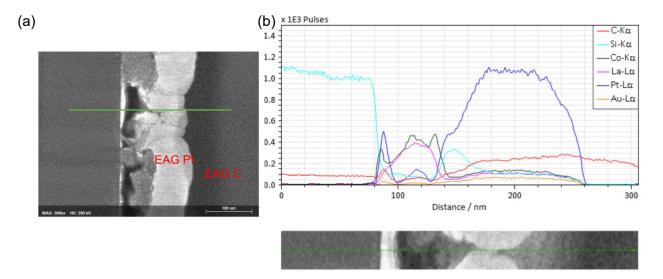

- Supplementary Figure 3.9 Adaptive mesh refinement is used to ensure high mesh quality throughout the model. Thus, high resolution is found at the thin LCO, with coarser mesh resolution at the contact pads. Scale is the default COMSOL-generated Supplementary Figure 3.10 LCO film resistivity is based on 4-point probe results (Chapter Supplementary Figure 3.11 Interfacial resistance to current flow for the LCO/Pd interface was based on the transfer length method conducted up to 473 K in Chapter 3.2.1, with Figure 4.1. Schematic of the shunt limiter depicts (a) OFF state signal flow when  $P_{in} < P_{th}$  (b) ON state when  $P_{in} > P_{th}$ . The LCO pads are found at the GND-SIG junctions. (c) closeup of one of the junctions in linear configuration. (d) close-up of the junction in an Figure 4.2 SEM images of fabricated LCO shunt limiters (a) full view including 130 µm pitch G-S-G planes (b) zoom-in to the active areas with interdigitated fingers of  $T = 1 \mu m$  and Figure 4.3 (a) screenshot of model of an interdigitated LCO shunt device (b) custom mesh Figure 4.4: 2 GHz PiPo results from 25°C to 125 °C for shunt limiters based on sputtered LCO grown on (a) LAO (b) SiC (c) sapphire © IEEE 2022. Solid lines indicate measured data, Figure 4.5: Repeated 2GHz PiPo sweep results for linear LCO limiter with device length 500 nm where the black line indicates the first run, and the red line represents device behavior that was repeated at least 5 times. Sweeps conducted at (a) 25 °C (b) 75 °C (c) 125 °C (d) 175 °C (e) 225 °C. (f) SEM image after measurement of one of the linear

- Figure 4.7 (a) Repeated high power PiPo sweeps at 25 °C for an interdigitated LCO limiter where the black line indicates the first run, and the red line represents device behavior that was repeated 3 times b) image of device after 40 dBm CW power input......58

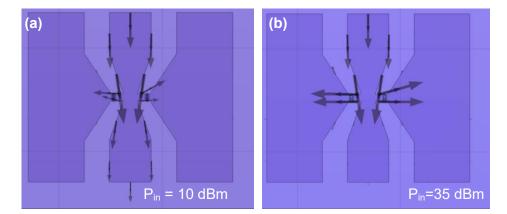

- Supplementary Figure 4.16. Model dimensions: Interdigitated configuration with T= 1  $\mu$ m, S = 500 nm, W<sub>IDC</sub> = 4  $\mu$ m, LCO = 0.065 × 4 × 15  $\mu$ m<sup>3</sup>. Visualization of current density for (a) OFF state at Pin = 10 dBm (b) ON state at Pin = 35 dBm......72

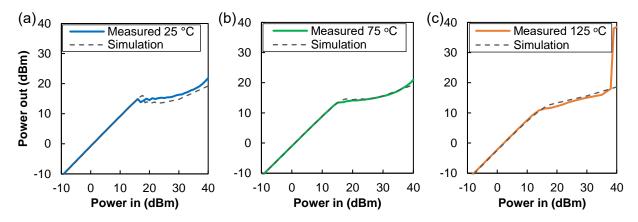

- Supplementary Figure 4.17 Comparison of measured PiPo data against simulated results at (a) 25 °C (b) 75 °C (c) 125 °C, showing the high accuracy of the model......73

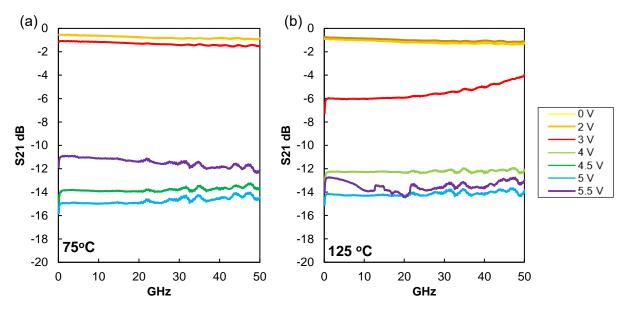

Figure 5.3: Transmission S-parameter S21 measurements at varied voltage bias on linear LCO shunt limiters with device length L = 500 nm at (a) 75 °C (b) 125 °C.....79

| Figure 6.4 Series LCO switch with linear geometry of device length 2 µm. 2 GHz PiPo sweep |  |

|-------------------------------------------------------------------------------------------|--|

| at 75 °C                                                                                  |  |

### LIST OF TABLES

#### ACKNOWLEDGMENTS

Throughout my graduate experience I have been fortunate to meet and work with many amazing people. Thank you, Professor Dwight Streit, for all your support, and for giving me the freedom and opportunity to conduct my PhD at the Northrop Grumman Corporation. There, I gained so much insight into industry and research that is hard to imagine I could have gotten any other way. My deepest appreciation goes to Vincent Gambin, my advisor at Northrop. You outlined the goals, but also allowed me the independence to explore what I wanted to. Thanks for supporting the work before the results were any good, and for giving sound advice when I was stuck. Your feedback has made me a better presenter and a better engineer.

To Carolina Adamo, YC Chen, Sean Armster, and Claire Pettiette-Hall: thank you for being such kind and welcoming mentors whenever I was in R6, especially in my first summer when I was just getting my bearings at NG. I also could not have completed my research at all without Minhdao Truong and Chris Bautista, who were always accommodating and patient teachers...no matter how many times I had thrown off their careful calibration of the RF testing station. Thank you to Kate Fountaine for working with me for weeks to build a custom optical set-up. Even though we ended up barely using it, I learned so much, and I suppose that's just a part of research. I am very grateful for the help of Tien Bui and Robert Mendoza, for dealing with the thankless task of keeping the BR systems functional. And finally, my admiration goes to the professionalism of all the engineers and technicians who ran the tools that made the fabrication of my devices possible.

I would also like to share my appreciation for our partners at the University of Notre Dame, Cornell, and Stanford, without whom this project wouldn't have gained as much traction. Thank you for the collaboration and co-authorships – you helped show me just how high the standards are.

I could not talk about graduate school without mentioning the friends I've made along the way. To my fellow interns: Eva, Clincy, Max, and Derek – our hard work merited every single one of those lunch breaks and boba outings. Also, shout out to all of my engineering graduate student association members (and to all of our very efficiently planned events). Vera, Jamie, Vikranth, Swapnil, Jean, Noor – your camaraderie kept me sane, and I can't thank you enough for adding fun and friendship to these last five years. To my pet bunnies Olive and Clove, adopted during lockdown: You are terrible housemates, you leave a mess everywhere, and you have ruined the carpet. But you're cute, so I love you anyway, and you were good company while I wrote this dissertation. And finally, thank you to my best friend and partner, my one and only grebe. I'm looking forward to post-grad life together.

#### VITA

| 2018      | B.S. in Chemical Engineering, University of California, Berkeley                                                  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2018-2023 | Co-President and Board Member, Engineering Graduate Student Association,<br>University of California, Los Angeles |  |  |  |  |

| 2019-2023 | Basic Research Intern, Northrop Grumman Corporation, Redondo Beach CA                                             |  |  |  |  |

| 2021-2023 | Graduate Student Teaching Assistant, University of California, Los Angeles                                        |  |  |  |  |

| 2022-2023 | New Ventures Fellow, Technology Development Group, University of California, Los Angeles                          |  |  |  |  |

#### PRESENTATIONS AND PUBLICATIONS

- 1. R. Bhattacharya, V. Gambin "Influence of crystallinity and stoichiometry on the high temperature semiconductor-metal transition of lanthanum cobalt oxide deposited by reactive dc sputtering" *Materials Science in Semiconductor Processing*, vol. 163, p. 107595 (2023)

- R. Bhattacharya, A. Khanna, B. Bosworth, N. Orloff, V. Gambin, D. Streit, P. Fay, S. Datta. "Thermally Resilient Microwave Switch and Power Limiter based on Insulator-Metal Transition of Lanthanum Cobalt Oxide", 2022 International Electron Devices Meeting (IEDM) (2022) 70–73.

- 3. R. Bhattacharya and V. Gambin, "LaCoO3 THIN FILM DEPOSITION BY DC METAL CO-SPUTTERING," U.S. Patent Filing 20220364219A1, May 12, 2021 (Patent Pending)

- 4. M. Islam, C. Perez, R. Bhattacharya, S. Wahid, T. Brown, Matthew Marcus, H. Ohldag, V. Gambin, S. Kumar, E. Pop. "Physics of Resistive Switching in LaCoO3 Revealed by X-Ray Absorption Spectromicroscopy" *Materials Research Society Spring Meeting 2023* (Oral presentation)

- 5. R. Bhattacharya, V. Gambin. "Materials Characterization of LaCoO3 Grown by Optimized Reactive DC Magnetron Sputtering" 64<sup>th</sup> Electronic Materials Conference 2022 (Oral Presentation)

- 6. R. Bhattacharya "New Materials for Fuses that Work in Space" UCLA GradSlam 2022 (Oral Presentation)

- 7. R. Bhattacharya, V. Gambin. "Material characterization and contact resistivity of LaCoO3 grown by optimized DC magnetron sputtering" *ACerS Electronics Materials and Applications Conference 2022* (Oral Presentation)

- 8. R. Bhattacharya, V. Gambin. "LaCoO<sub>3</sub> as an insulator-metal transition material for RF Power Limiters" *Northrop Grumman Basic Research Seminar 2021* (Oral Presentation)

# Chapter 1: Background and Motivation

## 1.1 Introduction to Radio Frequency Power Limiters

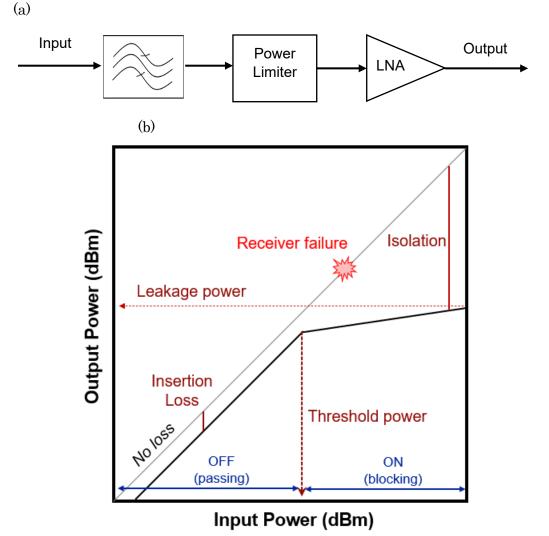

As our society grows increasingly dependent on wireless communications, having a robust satellite network is crucial. Malicious high power microwave signals can reach peak powers of 1 gigawatt and can easily cause irreversible damage to the sensitive components of receiver technology. Particularly for applications in GHz and THz frequency ranges, there is a growing need for advanced protection circuitry to defend against electronic warfare. Power limiters are front-end non-linear devices that prevent incident signal above a certain power threshold from passing, thus protecting downstream devices such as Low Noise Amplifiers (LNAs) that can typically only handle up to 20 dBm (100 mW). These components are typically arranged in receiver circuitry as depicted in Figure 1.1, ideally turning on well before the failure point of the LNA or other downstream components. The first block in Figure 1.1 (a) represents a bandpass filter, which narrows incoming signal to desired frequency bands. The limiter itself is then specifically designed to work within the frequency band with low insertion loss for the desired signals of sub-threshold power magnitude. We refer to a shunt-configuration limiter as being in the OFF state in the "normal operation" zone when signal is passing. At a given threshold input power, the device will transition to the ON state, or "limiting" range of operation (Figure 1.1(b)). Limiters can be designed to function both passively (self-activation from input signal) or actively (external turn-on via DC bias).

Figure 1.1 (a) typical positioning of a power limiter in receiver line. (b) targeted limiter attenuation input power response.

### 1.1.1 Metrics of Limiter Performance

There are many performance metrics for power limiters, including but not limited to 1) insertion loss 2) power handling and endurance 3) response time 4) frequency band 5) isolation and 6) environmental compatibility. Units of measurement of gain are denoted as dB. Magnitude of power (dBm) is defined in reference to 1 mW. The defining equations are:

$$dB = 10*log_{10}(P_1/P_2)$$

P<sub>dBm</sub> = 10\*log\_{10}(P\_watts/1 mW)

#### Insertion Loss:

Insertion loss refers to the signal loss or signal attenuation through the limiter in its OFF state and is defined as the ratio of powers from input to output in dB. The ideal limiter demonstrates zero insertion loss. However, most real-world devices perform between 0.2 to 1.5 dB loss. Because a major source of insertion loss is parasitic capacitance, it typically worsens at high frequencies.

#### Power Handling:

Peak power handling refers to the maximum one-time surge a limiter can handle before irreversible damage occurs, reported in dBm. Endurance of a limiter's function over time is also important, as even repeated bombardment by pulsed attacks below the peak power handling value has been known to gradually damage components. In this dissertation we describe continuous wave power handling characteristics, referring to the ability of components to survive sustained input signals applied for at least 100 microseconds.

#### **Response Time:**

If the input RF pulse has a faster rise time than the time for the limiter to transition to the ON state, some amount of RF power will get through and is called spike leakage. State of the art limiters respond in nanoseconds to block incoming signal, and the faster the response, the better the limiter's protection. Limiters must also be able to recover quickly to the OFF state after dangerous signal has been blocked. The scale of recovery times is typically in the hundreds of nanoseconds to micro-seconds.

#### **Frequency Band**

The ideal limiter has the same behavior across all frequency bands. Realistically, limiters must be optimized for small capacitance to avoid low shunt impedance in the OFFstate white maintaining high attenuation in the ON state with low frequency dependent response. In this research we focus on the microwave regime, testing devices from 0.1 GHz to 50 GHz. This range, for example, includes such common consumer applications at 2.4 GHz such as cordless telephones, Wi-Fi, and Bluetooth. The X and K<sub>a</sub> bands, from 8-12 and 26.5-40 GHz respectively, are often allocated for satellite communications, military aircraft, space telescopes, defense tracking, and air traffic control.

#### Isolation/ Flat Leakage

Isolation is the measure of attenuation of the limiter and is calculated the same as insertion loss, just for the device in its ON state. Maximum isolation is defined as the greatest attenuation measured for the device at the highest input power, reported in dB. Higher isolation is considered better performance. Flat leakage, in dBm, refers to the output power of the device in the limiting operation. Most limiters do not exhibit the ideal, a truly flat limiting performance, but instead the leakage will slope upward as input power increases.

#### Environmental compatibility

Satellites must perform efficiently within the harsh conditions of outer space. Power limiters must be robust at extreme temperatures, pressures, and against the onslaught of solar and cosmic radiation. The standard operating temperature rate of limiters is typically from -50 °C to 85 °C, sometimes up to 150 °C [1]. Reported metrics of performance such as insertion loss or isolation often include temperature dependence in units of dB/ °C.

#### 1.1.2 Current Art

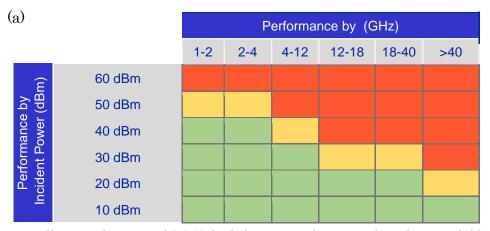

The conventional form of solid-state power limiter is the P-I-N diode, based on silicon. At the DC and low frequency limit, P-N and P-I-N diodes behave similarly. But the intrinsic region can store charge, and at radio frequencies, may not have time to completely deplete. This allows the flow of RF signal through a P-I-N diode. The thickness of the diode's intrinsic region determines the threshold power for switching and can also be influenced by DC bias. Below the threshold power, a P-I-N diode will produce a large impedance. When placed in a shunt configuration to the RF transmission line, this will result in low insertion loss. As the input power increases, however, carriers are pushed into the I-region, flooding the layer. Within nanoseconds, DC current is shunted through the loop formed by the diode and the return RF choke. Thus, input signal is blocked by either reflection back to the source or shunt to ground. However, the effectiveness of P-I-N diode limiters drops off at higher frequencies (Figure 1.2(a)), where power handling, response time, and leakage tradeoffs become an issue.

Figure 1.2 an illustrated review of P-I-N diode limiter performance, based on available products from one vendor, Microsemi [2]. The graphic highlights the typical constraints of commercial silicon P-I-N diode limiter function as a function of peak power and frequency. Green indicates good performance, red indicates poor or limited functionality

Power handling of limiters is directly related to their efficiency at dissipating power and avoiding damage. One mechanism for the P-I-N diode failure was detailed by Zhao *et.al.* [3], who demonstrated by microwave pulsed power tests that even 20 pulses of 2.5 GHz 63 dBm (~2 kW) input power can drastically deteriorate the insertion loss of a commercial diode designed for GHz operation. The P-I-N diodes show signs of ablation at the metal electrodes well below the material's melting temperature. The damage accumulation is attributed to ablation burn-out of first the I-region, then the N+ region above 600 pulses. One method of improving on this form of power failure would be to increase the size of the diode. However, this introduces response delays, increased spike leakage, and greater power consumption [4]. Additionally, if trying to reduce the thickness of the I-region to improve speed, parasitic capacitances arise that worsen high frequency insertion loss (capacitance=k εA/d). Thus, there is simply a material constraint in the use of traditional diodes for receiver protection, and the next generation of power limiters will have to look elsewhere.

While for the most part the commercially available power limiter is still the traditional Si diode, several alternate constructions have been recently emerging to tackle silicon's weaknesses. For one, GaAs-based diodes have acquired attention for high frequency operation. In general, a multi-stage design has thus far been required to approach the performance standards of a single-stage Si P-I-N diode. One group demonstrated a 4-stage GaAs P-I-N diode limiter with excellent 13 dBm flat leakage performance, under 1 dB insertion loss, and power capacity of 40 dBm [5]. Other novel materials for diode-based limiters are also on the horizon. For example, the high thermal conductivity and high breakdown field of diamond suggests improved power dissipation and power handling capabilities. A p-type diamond Schottky diode has been recently tested in a multi-stage limiter configuration, demonstrating operation up to 50 dBm, with a flat leakage of 27 dBm. The technology has only been reported at 1 GHz, though research is on-going [6]. While a multi-stage limiter is certainly a viable commercial option as well as single-stage, a smaller form factor and simpler construction is often desirable for greater signal sensitivity.

Other alternates to P-I-N diodes include the usage of high-power HEMT switches on AlGaN. Non-diode designs of power limiters also include gas-ionization based plasma limiters and micromechanical systems (MEMS). Plasma limiters work by using high power to ionize an inert gas discharge tube, thus allowing the power to dissipate, or be absorbed into the gas. While they have exhibited impressive power handling and frequency response, plasma limiters are constrained by recovery time and insertion loss [7]. Further, when the gas breaks down, ions are driven across the discharge gap and bombard the electrodes, which can lead to surface degradation over time [8]. MEMS switches can be actuated by thermal gradients or electrostatic fields and have recently achieved impressively low insertion losses below 0.1 dB with broadband response [9], but continue to suffer from reliability issues. The small moving parts in MEMS devices are highly sensitive to environmental effects such as vibration and acceleration as well as contact fatigue from deformation and melting [10,11].

# 1.2 "Smart Materials" and the Insulator to Metal Transition

Transition metal compounds that exhibit unusually rapid, reversible changes in conductivity as a function of temperature (a.k.a Insulator to Metal Transition, IMT) may present a new pathway to construction and a solution to the current constraints in limiter technology. Emerging technologies based on these "smart" materials can potentially achieve very high endurance and higher power handling.

In traditional band theory, a fermi level in a band gap leads to insulating behavior, and a finite amount of energy is required to excite an electron to the next highest accessible orbital to carry electric current. Band theory fails when other effects such as electron-electron interactions within orbitals or disorder cause unpredicted electron localization. A classic example is NiO. NiO would be a metal according to traditional band theory due to its partially filled 3d band, but it is in fact insulating. Mott and Hubbard proposed complementary explanations for the phenomenon. In the Hubbard model [12] of periodic potential systems, Coulombic electron repulsion potential (U) prevents hopping from one atomic (or molecular) orbital to the next. This allowed that even in the case of one electron per lattice site (half filling), localization would cause insulating behavior. The Mott transition [13] describes that at a critical carrier density (increased by doping or temperature), electrons flood the conduction band and charge screening allows for delocalization and metallic conduction. In a Mott insulator, the band gap is formed between like orbitals (eg. 3d-3d), as opposed to traditional valence/conduction bands formed by the energy difference between two spatially distinct orbitals (eg 2s-2p) or electron-periodic potential interaction. Unlike the Hubbard model, the Mott model is more general and does not require long-range order. For further distinction from other mechanisms, an Anderson insulator is based on electron-disorder interaction, and a Peierls insulator has a band gap based on electron-lattice deformation interaction. Theoretically, the Mott transition is first order and purely electronic. In reality, competing mechanisms and defects can often slow the transition or cause hysteresis.

#### 1.2.1 Vanadium Dioxide

There are many materials that exhibit the IMT transition; by far the most thoroughly studied is Vanadium dioxide ( $VO_2$ ).  $VO_2$  exhibits a first-order nano-second phase transition (high-temperate rutile to low-temperature monoclinic) at around 68 °C with high reversibility in conductivity and optical transmission in the near IR regime. The transition mechanism for VO<sub>2</sub> is Peierls-assisted Mott-Hubbard– the structural transition at 68 °C creates a lattice distortion and enables the injection of carriers into the conduction band. This screens repulsion and leads to electron delocalization and metallic behavior [14]. Given the strong dependence on lattice quality and periodicity, the magnitude and hysteresis of the VO<sub>2</sub> IMT is highly sensitive to deposition condition, crystallinity, and substrate. The best reported  $VO_2$ thin film achieves a four-order of magnitude on/off ratio when epitaxially grown on sapphire. In contrast, single crystal VO<sub>2</sub> can demonstrate five orders of magnitude. VO<sub>2</sub> also sees a significant drop in the on/off ratio for polycrystalline films over epitaxially grown materials, and easily devolves into other phases with slight off-stoichiometry [15,16]. Despite these challenges,  $VO_2$  has been heavily studied for a wide variety of novel devices including switches (2 and 3 terminal), optical devices, chemical sensors, thermal sensors, oscillators, and mem-resistive devices [16].

### **VO<sub>2</sub> Power Limiters**

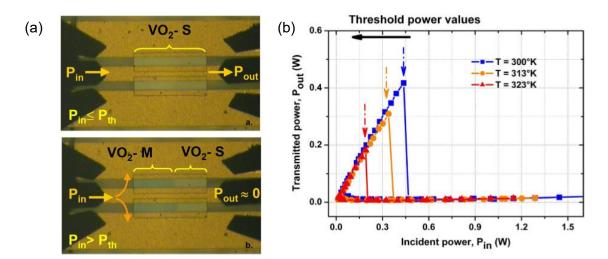

In 2010, Givernaud *et.al.* [17] presented a microwave power limiter constructed from 250 nm of VO<sub>2</sub> grown on sapphire. They used strips of VO<sub>2</sub> to fill the gap between the signal and ground lines of a co-planar waveguide Figure 1.3 (a). They reported RF-power triggering of the transition where above a certain power threshold, the VO<sub>2</sub> switched to a metallic state and highly attenuated the input signal. The threshold power of the device could be further reduced by application of voltage-controlled DC bias up to 22 V. The highest substrate temperature that Givernaud *et.al* reported switching the limiter was 50 °C (Figure 1.3 (b)). The article also outlines several multi-stage configurations and verification of broadband low insertion loss up to 40 GHz.

**Figure 1.3** (a) microscope image of a vanadium dioxide-based power limiter with (b) demonstrated self-turn on limiting behavior at 10 GHz and up to 50 °C as reported by [17] © 2010 IEEE

In 2018, Nordquist *et.al* [18] reported a similar planar shunt limiter based on thinfilm VO<sub>2</sub> on SiO<sub>2</sub>. This film achieved a resistance on/off ratio of 500 when measured at 40 °C and 100 °C by the four-point probe method. A tapered geometry was utilized to enable higher power handling, with repeatable operation up to 47 dBm. A summary of the VO<sub>2</sub>-based RF limiter performance is shown in Table 1.1.

| Insertion | Power     | Isolation | Test         | Test                   | Structure | Source |

|-----------|-----------|-----------|--------------|------------------------|-----------|--------|

| Loss (dB) | Threshold | (dB)      | Frequency    | Temperature            |           |        |

| 0.6       | 20-30 dBm | 26        | 10 GHz       | 25-50 °C               | co-planar | [17]   |

|           |           |           |              |                        | waveguide |        |

| 0.7       | 36 dBm    | 27        | $2~{ m GHz}$ | $25^{\circ}\mathrm{C}$ | tapered   | [18]   |

Table 1.1: Prior Work in IMT-based Power Limiters based on Vanadium Dioxide

In a similar vein of research, a free-space millimeter-wave photonic limiter based on nano-layer VO<sub>2</sub> has very recently been reported for W-band function [19]. Polycrystalline VO<sub>2</sub> was grown on a large area of sapphire substrate and presented with RF signal at 95 GHz and up to 60 W. Due to low absorbance of the signal into the film, neither significant self-heating nor self-turn-on was observed at room temperature even when presented with the maximum power. When the ambient temperature was raised closer to the critical transition of VO<sub>2</sub>, selfturn on was observed starting at 30 W and the device showed maximum isolation of 20 dB at ~47 dBm. Only a very slow switching time of 7 seconds was achieved in this proof-of-concept device [20]. It is worth noting that this photonic limiter was not designed to be positioned along the transmission line but instead to provide a wide area of protection, so the expectations of performance would be different.

Despite these developments, ultimately VO<sub>2</sub> power limiters devices are impractical. High on/off ratios are only achievable for films grown on sapphire substrate, restricting integration avenues. Furthermore, operational guidelines for many military and satellite applications requiring operation up to at least 85 °C because of the self-heating caused by high power shunting and the difficulty of cooling systems without convection in space. With VO<sub>2</sub>'s transition occurring below that point, the high temperature operation is thus constrained, and it has become necessary to look at other potential IMT materials.

#### 1.2.2 Lanthanum Cobalt Oxide

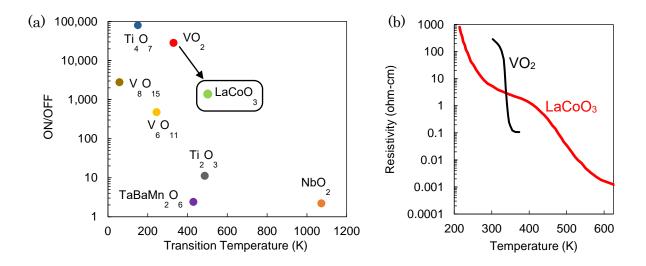

A graphic with extracted values from [14] displays the resistance on/off ratio of various IMT materials as a function of their switching temperature (Figure 1.4 (a)). Clearly, for higher temperature device operation, the next choice after VO<sub>2</sub> would be Lanthanum cobalt oxide (LaCoO<sub>3</sub>, LCO). It is worth highlighting that the figure assembled does not clarify the broad transition profile that makes LaCoO<sub>3</sub> distinct from VO<sub>2</sub>, which is then displayed in Figure 1.4 (b). This can provide both a benefit and a challenge. Without the sharp transition seen in VO<sub>2</sub>, LCO-based devices must be carefully designed to enable reasonably fast switching speed. However, the broader transition temperature range can also allow LCO devices to access a wide operating range with minimal loss in functionality.

**Figure 1.4** (a) compilation of resistance drop ratios for known IMT materials [14] (b) comparison of transition profiles for bulk LaCoO<sub>3</sub> and polycrystalline VO<sub>2</sub> [21,22]

LaCoO<sub>3</sub> is a perovskite previously most researched for catalytic applications and as a cathode in solid oxide fuel cells. It has a stable rhombohedral structure up to 1698 K, at which point it becomes cubic. The ideal cubic perovskite cell is structured as FCC-based, with oxygens at each face center, A-site ions at each corner, and B-site cations at the center of the cell (Figure 1.5 (a)). In LCO's slightly distorted R3C structure, the (100) planes are shifted diagonally to give one angle of 120° and lattice constants of 5.44 Å, 5.44 Å, and 13.13 Å. The pseudo-cubic LCO structure, assuming all angles are 90°, has lattice constant of 3.82 Å.

**Figure 1.5** (a) Pseudocubic perovskite structure for LaCoO<sub>3</sub> (b) progression of the Co<sup>3+</sup> spin state transition from Low Spin S=0, to Intermediate S=1, and High Spin S=2. The consensus is that the LS state exists below 100 K, and HS metallic state far above 500 K. However, the temperature transition boundaries and spin states' relative stability remain under debate. [23]

The cobalt ion in  $LaCoO_3$  holds the key to its spin state insulator to metal transition, which is similar to a traditional Mott transition. One can understand why the transition profile is so gradual by considering a two-stage transition. Below 35 K, LCO behaves as a nonmagnetic insulator where the cobalt lies in the low spin ground state (LS, <sup>1</sup>A<sub>1</sub>, t<sup>6</sup> <sub>2g</sub> e<sup>0</sup><sub>g</sub>) with a band gap estimated at 1.5 eV. With temperature, the cobalt eventually shifts to the high spin fully metallic state (HS, <sup>5</sup>T<sub>2</sub>, t<sub>2g</sub> 4e<sub>g</sub><sup>2</sup>) at some point above 500 K. Originally Goodenough *et.al.* proposed a LS-HS transition of based on Co (III) crystal splitting energy being only slightly larger than the exchange energy and electron repulsion, which mimics the makings of a Mott-Hubbard insulator [24,25]. In that original model, the mixed LS-HS phase between 100 K and 500 K provided semiconducting behavior. However, this model served insufficient to fit the magnetic susceptibility and thermal expansion properties of LCO, and was later updated to include an intermediate spin level (IS, <sup>3</sup>T<sub>1</sub>,t<sub>2g</sub> <sup>5</sup>e<sub>g</sub><sup>1</sup>) [26-28]. There continues to be discussion and disagreement about the exact mechanism for the transition. The low spin state of  $Co^{3+}$  is a highly symmetric octahedron. There may be significant stabilization of the orbitally ordered IS state by Jahn-Teller distortions. This orbitally ordered state formed by the hybridization of Co eg and O 2p orbitals may then "melt" around 500 K, giving rise to metallic conduction, and the HS state (which is not JT active) could then be occupied at higher temperatures above 800 K [28–31]. However, other groups counter this model, stating that there is a 3-stage LS-IS-HS transition, with the HS state beginning population and overtaking the stabilized IS state at the semiconductor-metal transition [27,32]. Even others reject the importance of the IS state altogether [33], offering that while it does exist (and thus shows up in Raman spectroscopy results), the LS-HS state crossover is the primary mechanism of transition, with no temperature region seeing domination by IS. They suggest that the short-range LS-HS order of the semiconducting region melts and leaves space for IS-HS coexistence at around 500 K and a Mott-like transition [34–36]. Based on the results of this work, we suggest that the spin state transition of LCO does not demonstrate the homogenous thermal transition with a critical carrier concentration as characteristic of a thermal Mott insulator. Instead, with increasing temperature, conductive HS clusters grow in an entropy driven transition as supported by other researchers [37,38].

For thin film LCO, it has been shown that the spin-state transition can be regulated by deliberate distortion of  $CoO_6$  octahedron by strained epitaxial growth. For example, LCO has previously been epitaxially grown on (100), (110), and (111) lanthanum aluminate (LaAlO<sub>3</sub>, LAO) substrate [39]. Of these, the (100) orientation best supported the Jahn Teller distortion by forcing the greatest elongation of Co-O bonds, leading to higher intermediate state population at lower temperatures and thus most likely the earliest transition to the metallic state.

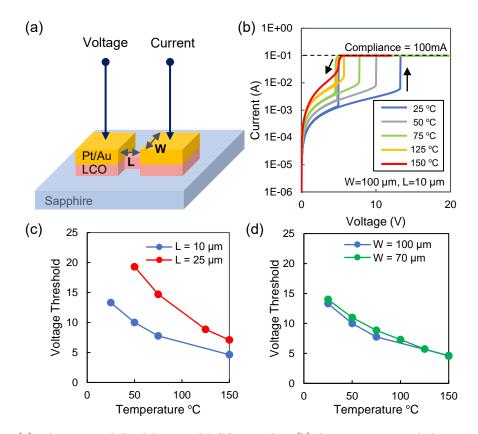

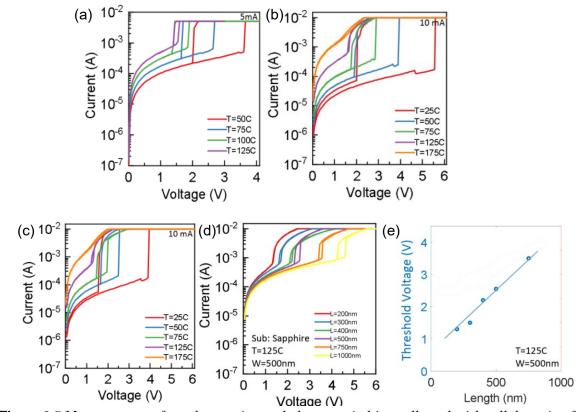

#### Previous work in LaCoO<sub>3</sub> electronic switches

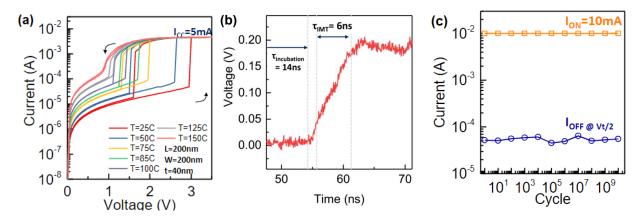

Despite all the debate over the mechanism of this electronic shift, practical application of  $LaCoO_3$  in an electronic switch had scarcely been explored before the inception of this project, conducted in cross-collaboration between the University of Notre Dame (UND), the Northrop Grumman Corporation (NGC), and University of California, Los Angeles (UCLA). Initial evaluation of LCO for use in electronic switches was conducted at UND using epitaxial material grown by molecular beam epitaxy [21] on Lanthanum Aluminate (LAO), a perovskite substrate with only -0.8% mismatch. As expected, the magnitude of the epitaxial film's transition was reduced compared to bulk material (3000x to 780x). This has been characterized previously by groups that show that epitaxial strain prevents population of the LS state at lower temperatures, thus reducing resistivity overall [40–43]. This epitaxial material was subsequently investigated for memory-selectors in 3D cross-point architecture [44]. LCO was fabricated into 2-terminal switches, and current-voltage sweeps demonstrated abrupt switching up to 125 °C. Voltage applied over a thin strip of LCO will trigger the switch to conductive state for small resistive domains. As each individual domain switches, the total current pushed through the material increases, the temperature increases by Joule heating, and a cascading effect allows for fast turn-on times of 20 nanoseconds. Scaled devices exhibited high endurance with minimal drift up to 10<sup>10</sup> cycles.

Figure 1.6 (a) I-V sweeps of 200 nm x 200 nm LCO 2-terminal device areas exhibit abrupt switching from 25 °C to 125 °C (b) Pulsed DC measurements at V<sub>in</sub>= 3 V are used to measure turn-on times. A 14 ns incubation delay time is followed by 6ns for the IMT transition (c) Repeated I-V sweeps demonstrate consistent non-linearity up to 1010 cycles. [44], all graphics reprinted with permission, © 2020 University of Notre Dame

Researchers at UND also fabricated prototype LCO RF switches (normally blocked, turns-on to pass signal) based on the MBE-grown material [44]. They demonstrated the ability to control the passing of RF signal through both temperature and DC-bias up to 50 GHz. The RF switch showed insertion loss of 3.2 dB in the on-state, 15.2 dBm isolation in the off-state at 20 GHz, and a cut-off frequency of 0.55 THz. Performance was similar across 25 °C to 125 °C, supporting our hypothesis on the potential broad operating range of LCO-based mm-wave switches.

### 1.3 My contribution to the field

Through the valuable efforts of my predecessors in this field, LaCoO<sub>3</sub> has been shown to possess the switching characteristics (speed, high temperature stability, endurance) that make it a promising candidate for power limiters. However, previous LCO deposition methods were not conducive to wafer-scale production or larger scale testing. Molecular beam epitaxy is a slow (0.2 nm/min) and non-economically scalable process with only a small central area of the lattice matched substrate, LAO, available for fabrication. Furthermore, the high dielectric constant of LAO (k=25) led to parasitic capacitances and high loss in the RF switches. Therefore, there was strong interest in depositing LCO onto a high thermal conductivity, low dielectric constant substrate such as silicon carbide (SiC). One objective of this project is to fulfill the need to deposit at wafer-scale on alternate low-k substrates. Additionally, in this research I have demonstrated the fabrication of RF limiters based on the sputtered LCO material. We have engaged in optimization of performance metrics such as thermal stability, insertion loss, frequency response, and power-handling through variations in device geometry. I also built a highly accurate COMSOL model to aid in the simulation of the influence of various device parameters. The following is the outline of each chapter of results of this thesis.

In Chapter 2, I report on the development of a reactive sputtering process of both polycrystalline and epitaxial LaCoO<sub>3</sub>. Thin-film material characterization and estimation of the temperature-driven band gap collapse of the sputtered films is also presented.

Chapter 3 expands upon 2-terminal DC bias triggered LCO switches collaboratively constructed with UND. Switches are fabricated and tested from sputtered LCO material grown at NGC. This chapter also presents the introduction of our transient Multiphysics COMSOL model, with accurate prediction of both the magnitude, incubation delay, and switching speed of the voltage triggered IMT.

In Chapter 4, we present polycrystalline LCO-based shunt power limiters characterized by Power-in-Power-out (PiPo) experiments at 2 GHz. Various configurations are tested to evaluate design trade-offs on performance. I report on the progression of different failure modes as the limiters' geometry and operating temperature is changed, as well as proposed improvements to the most recent configurations with simulation-backed substantiation.

In Chapter 5, I further evaluate the aforementioned LCO power limiters at high frequency and temperature. S-parameter tests are conducted up to 50 GHz, and we demonstrate DC-bias external activation of the devices.

Finally, Chapter 6 includes the characterization of sputtered-LCO RF series switches. I summarize the work presented in this dissertation and discuss the potential future of LCO in other thermally or electronically driven applications.

# Chapter 2: Deposition of Thin Film Lanthanum Cobalt Oxide

## 2.1 Abstract

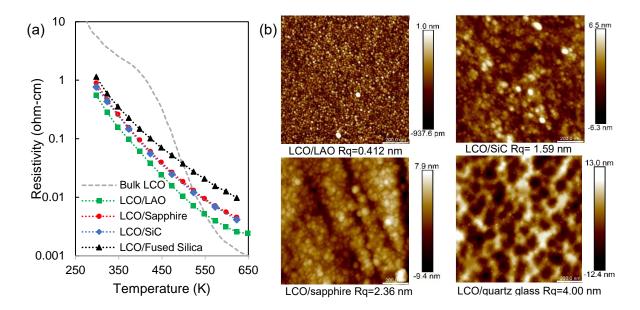

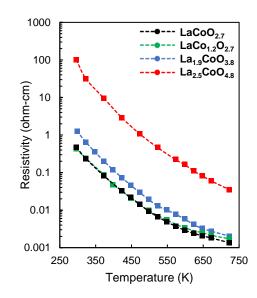

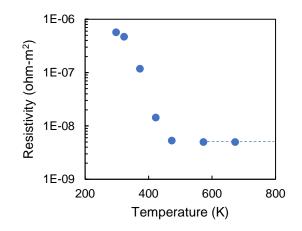

Much of this chapter is reprint from the published article [45]  $\[ \]$  Elsevier 2023. Lanthanum cobalt oxide (LCO) has garnered growing interest in electronic switch applications based on its unique insulator to metal transition. A single-step high temperature deposition process was developed for thin film LCO via reactive dc magnetron sputtering, starting with exploration of target poisoning within the context of Berg's theory. By tracking target voltage on metal targets during reactive deposition, we reason that increasing inert gas flux to the target improves target hysteresis, thus increasing target lifetime. Furthermore, it is shown that the onset of the critical region of oxide deposition has a stronger dependence on reactive gas flow rate than on partial pressure. The critical region is found at approximately 1.5 sccm and 5 sccm oxygen flow rate for the La and Co targets, respectively. We subsequently probed substrate and stoichiometry influence on LCO film quality and electronic properties. Epitaxial (100) LaCoO<sub>x</sub> (Rq = 0.412 nm) films grown on lanthanum aluminate (LaAlO<sub>3</sub>) demonstrate similar reductions in resistivity over 300 K to 623 K as polycrystalline LCO films on 4H-SiC and sapphire (Rq= 1.59, 2.36 nm respectively). However, La-heavy films, grown as La<sub>2.6</sub>CoO<sub>4.8</sub>, can demonstrate significantly steeper resistivity drops. Finally, we estimate the band gap collapse and insulator-metal transition of thin-film LCO over temperature by near-IR absorption.

## 2.2 DC Magnetron Sputtering

Magnetron sputtering is a vacuum physical vapor deposition process achieved by using magnets to confine an electron density that increases ionization rates. The resulting plasma strike that bombards a solid target thus ejects material towards a mounted substrate. Sputtering can be classified as DC or RF based on the power input. Typically, the inert gas used is argon, and reactive gases such as oxygen or nitrogen are introduced into the chamber for compound films. The vaporized target materials and ionized oxygen gas react in the chamber and deposit on the surface of the substrate. Having many tunable parameters allows for a wide range of film growth options. Grain size can be influenced by substrate temperature; higher substrate temperature encourages higher surface mobility for the arriving atoms, thus leading to larger grains. High surface mobility also tends to lead to smoother films as concavities are filled during the deposition [46]. Post-annealing at high temperatures can also allow grain growth, but the gain is reduced due to the high activation energy of thermal diffusion for already condensed species. The growth temperature of the perovskite structure is above 600 °C, so LCO film must either be deposited at or above that temperature [47]. Working pressure also has an influence on film roughness and deposition rate, as a higher working pressure reduces the mean free path between ion collisions. This could reduce the kinetic energy of atoms that diffuse towards the substrate, leading to lower surface mobility and higher roughness, particularly if the applied target power was also low. The deposition rate can also be expected to reduce at higher working pressures. In general, at lower temperatures and higher pressures, one can expect to see rough or columnar growth, and lower pressure and higher substrate temperature will favor smooth crystalline films [48].

### 2.2.1 Berg sputtering theory

A well-known complication of DC reactive sputtering is the non-linear relationship between oxygen partial pressure and film composition. The formation of an oxide layer on the target surface itself, known as poisoning, can lead to charge build-up and arcing, which will damage both target and film. Operating near the critical oxygen pressure for one reactive metal is difficult due to the inherent instability of a reactive sputtering process; co-sputtering two metals in that region is therefore exceedingly challenging. Here, we characterize the sputter behavior of the La-Co sputtering system in an oxygen-argon environment by cathode discharge voltage hysteresis experiments.

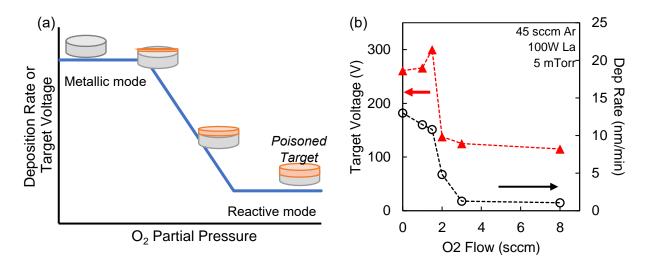

**Figure 2.1** (a) non-linearity of reactive sputtering has similar effects on deposition rate and target voltage from the cathode. (b) Deposition rate ( $\circ$ ) and target voltage ( $\blacktriangle$ ) as function of reactive gas flow rate for the La target at 100 Watts DC power. Dashed lines are provided to guide the eye [45]

The Berg model provides a simple reasoning for the reactive process non-linearity and hysteresis effect seen in reactive sputtering. The Berg model, with modification by Depla et.al, uses steady state equations to describe the mass balance of reactive gas flow [49]. The total reactive gas introduced to the system is equal to the sum of molecules consumed at the target, those exiting the chamber through the vacuum pump, and those that make it to the substrate to form a film. At the target, the gas can be consumed by either chemisorption at the surface or ion implantation by ionized molecules. At low oxygen flow rates, the system operates in metallic sputtering mode and can achieve high yield (high deposition rate), but the film will likely be oxygen deficient. As oxygen flux increases, it becomes harder to control the deposition rate as the target poisons. At a critical reactive gas flow where poisoning causes the deposition rate to drop sharply, the film is oxygen stoichiometric [50,51]. However, at the same time, oxygen partial pressure in the chamber spikes dramatically, as less target surface is available for reaction. Thus, further increasing the oxygen pressure could lead to an overly oxygenated film and arcing target [52]. One method of actively tracking the target condition during deposition is the discharge voltage,  $V_T = W/(q\gamma_e \epsilon)$ , where W is the average energy loss per ionization of the gas atom,  $\gamma_e$  describes the secondary electron emission yield, and epsilon is a probability value related to various possible energy loss mechanisms. Like deposition rate, the target voltage is roughly flat until the critical reactive gas flow rate and falls dramatically afterward. When the target is poisoned, the electron emission coefficient increases. There is a slight peak in voltage at the critical point that may be explained by the transition to the unaffected metal below the target's oxidized surface regions [49]. Discharge voltage hysteresis tests have been conducted for few other processes such as vanadium dioxide [53], and La-Fe co-sputtering [54], but not for the La-Co system. In this work, we determine the effect on target recovery of increasing the inert gas flow rate and co-sputtering reactive metals. We find a critical oxygen flow rate for a subsequent co-sputtering process that prevents both arcing and a prohibitively slow deposition process.

#### **Results:** Target Hysteresis

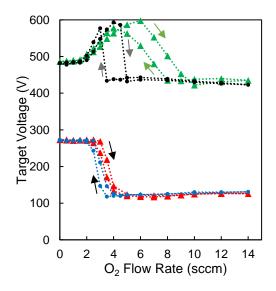

The sputter system used is an AJA Orion-8 fitted for 2" magnetron sources, equipped with 2 DC guns, one of which is capable of Pulsed DC operation. We conducted both individual and co-sputtered cathode voltage hysteresis tests for the La and Co metal targets in roomtemperature processes. Power (La=100 W, Co=200 W) and overall chamber pressure (5 mTorr) were set constant. Argon flow was set to 20 sccm, and oxygen flow was stepwise increased from 0 to 12 sccm, at which point both targets could be expected to be well into the reactive mode. The target voltage was noted after it reached a steady value between each step (approximately 1 minute). Then, oxygen flow was stepwise reduced until the target was in a fully metallic mode. These hysteresis experiments were repeated at a higher (45 sccm) Ar flow rate. In Figure 2.1 (b), the parallel influence of oxygen gas flow rate on target voltage and film deposition rate is depicted for the La target at 100 W DC power. We can clearly observe the expected simultaneous drop in both deposition rate and target voltage as predicted by Berg's theory on metal target poisoning. For metals, secondary electron emission is dominated by potential emission, or the ionization energy of the target material work function. On the other hand, for compounds such as La-O, emission is dominated by kinetic emission [49]. The sharp drop in target voltage in Fig. 1 corresponds with the rapid formation of a resistive oxygenated surface and thus an increase in the secondary emission coefficient  $\gamma_e$ . The poisoning of the Lanthanum target occurs at a relatively low oxygen flow rate, corresponding to the highly sensitive nature of this metal.

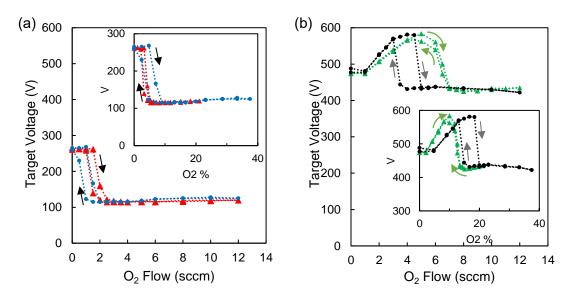

Figure 2.2 Target condition hysteresis as measured by target voltage as a function of reactive gas flow rate for (a) La target at 20 sccm Ar (●), 45 sccm Ar flow rate (▲). (b) Co target at 20 sccm Ar (●) and 45 sccm Ar (▲). Insets illustrate same data with x-axis converted to oxygen percentage [45]

The hysteresis of La and Co targets (when sputtered in isolation) is illustrated in Figure 2.2 (a-b). As expected for the Lanthanum metal target, the element is larger, more electropositive, and consequently more reactive with oxygen than Co. However, the oxide formed is surface-level – the low hysteresis effect on the La target indicates that most of the oxidized material is ejected from the target surface upon impact. Increasing the Ar flow rate slightly pushes out the La critical point by further enabling ejection of any reactive species from the surface and thus keeping  $\gamma_e$  low for longer.

For the cobalt target sputtered in 20 sccm Ar, the voltage curve is characteristic of a less reactive metal target, with a peak in target voltage at a higher value, 4 sccm O<sub>2</sub>. However, in contrast to La, Co shows strong target hysteresis upon reducing the oxygen flow rate, indicating deeper penetration of reactive species into the target. Increasing the argon flow rate serves to extend the critical region and greatly narrows the hysteresis curve. This indicates that higher argon flow rate, even as overall chamber pressure is held constant, limits formation of the oxide layer by continually cleaning the metal surface of the target. This effectively reduces the residence time of the reactive species and prevents deeper implantation. As this behavior is true both when data is plotted as a function of reactive gas flow rate or partial pressure, we infer that flux of gas particles is the controlling factor, rather than the ratio of inert to reactive gas.

Figure 2.3 Target voltage as a function of oxygen flow rate for co-sputtering target hysteresis experiments and both high and low inert gas flow rate. For 20 sccm Ar, La target is indicated by (●) and Co target by (●). At 45 sccm Ar, La is depicted by (▲) and Co by (▲) [45].

In Figure 2.3, we demonstrate the influence of co-sputtering the La and Co targets on the target condition. Here, La and Co express similar hysteresis profiles to the independently sputtered cases. However, at both low and high Ar flow rate, the reactive mode for Lanthanum when co-sputtered with Co starts at a higher oxygen flow rate. This implies that the Co target consumes some of the oxygen in the chamber, requiring a higher  $O_2$  flux to oxidize the target. The shared consumption of inert gas flow in returning to a metallic state works to favor the La target to faster clean its oxidized surface and slightly reduce hysteresis, while simultaneously worsening the hysteresis on the Co target at high pumping speeds.

# 2.3 Film Growth

### 2.3.1 Methodology

The La target was installed in the pulsed DC gun to protect against arcing using 50 kHz pulses with 4  $\mu$ s intermittent reverse biases to discharge the target. It is not expected that these short reverse bias times will have a significant effect on the deposition rate [55]. All films have been deposited at chamber pressures of 5 mTorr and on multiple substrates. LaAlO<sub>3</sub> (100) served as a closely lattice-matched substrate (a=3.787 A) with 0.9 % mismatch to LCO in this orientation. We also chose c-plane (0006) sapphire for transparency in the near-IR and visible regime for optical measurements of the LCO films. We additionally sputtered on 6-H (0006) silicon carbide, as it is a common substrate for high-power/high frequency switch applications. Fused silica was also tested, a thermally stable amorphous material also transparent in the near-IR regime, to study the properties of a non-crystalline LCO film. All substrates were prepared by rinses in acetone, isopropyl alcohol, and DI directly before being mounted into the sputtering chamber.

Gas flow rate, based on the results of the target voltage hysteresis experiments, have been set to 8 sccm  $O_2$  + 45 sccm Ar. These settings ensure stable reactive processes with little run-to-run drift. We heat the substrate above the crystallization temperature of LCO (600 °C) and hold there for at least 30 minutes before deposition to ensure uniformity [47]. The composition of the films was controlled by varying the DC power on the La and Co targets.

The sputtered LCO films were characterized by several techniques. Film thickness was measured by a Bruker DektakXT® profilometry tool. X-ray diffraction (2 theta-omega) is used to determine crystallinity and texture. X-ray photoelectron spectroscopy was used to characterize composition after a 50 second argon etch to clean the sample surface. Atomic force microscopy (Bruker Dimension Icon ®) was used to image the film surface.

Temperature dependent resistivity was determined by four-point measurements. The four-point probe method allows for the elimination of contact resistance and is conducted by forcing current through two outer probes and measuring voltage across two inner probes. Resistivity is calculated as resistivity  $\rho = 4.53Vt / I$ , where t is film thickness in centimeters. The collinear sense and force probes were connected to the 4200A-SC Keithley parameter analyzer with 62.5 mil tungsten probe spacing. Ohmic contact is achieved on the bare film surface. Samples were heated by a Linkam HFS600E temperature control stage. The temperature was stepped from room temperature up to 350 °C and at each point the force current is set so that the positive and negative sense readings match within 2%. We define the IMT on/off ratio as  $\rho_{25°C}/\rho_{350°C}$ .

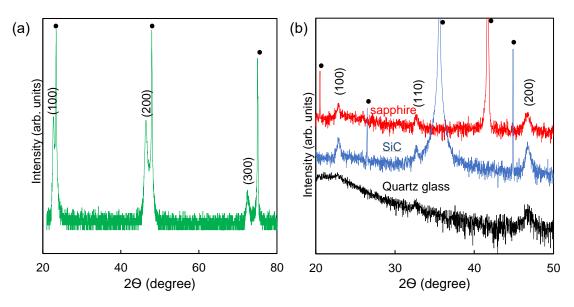

Figure 2.4 X-ray diffraction pattern for 150 nm LaCoO<sub>2.7</sub> film, epitaxially grown on (a) Lanthanum Aluminate and (b) sapphire, 4H-SiC, and fused glass. The substrate peaks are labelled with a ● [45].

Figure 2.4 (a) depicts x-ray diffractogram for a 150 nm LaCoO<sub>2.7</sub> film deposited lanthanum aluminate (LAO), indicating a highly textured epitaxial film grown oriented to the (100) direction. The out-of-plane lattice constant is estimated to be 3.91 Å by Nelson-Riley analysis. As the relaxed pseudo-cubic lattice parameter of LCO is 3.82 Å, this value aligns with the expectation of in-plane compression (out-of-plane expansion). In contrast, with their out-of-plane lattice constant calculated at 3.89 Å, the LCO films on sapphire and SiC (Fig. 4(b)), are more relaxed. Grown by Wolmer-Veber, or island, growth, the (110) peak of these films are also distinguishable in the x-ray diffraction pattern, indicating a polycrystalline, random orientation. On quartz glass the small peaks indicate a higher critical thickness for crystallization on the amorphous substrate.

**Figure 2.5** (a) 4-point resistivity measurements as a function of measurement temperature for 150 nm sputtered LCO film co-deposited on multiple substrates. Comparative results are shown for bulk material, extracted from [21] (b) corresponding 1 µm x 1 µm AFM images [45]

As shown in Figure 2.5 (a), the measured resistivity of thin film samples is lower than the bulk at room temperature and may be attributed to oxygen deficiency, with oxygen vacancies serving as donor impurities, leading to more semiconducting behavior at the lower temperatures [56]. In addition, the LCO spin state transition is dependent on unit cell volume. The high spin case is favored in higher cell volumes because high spin Co<sup>3+</sup> has a larger atomic radius. When the unit cell volume is constrained, the IS state is favored [57]. This reduction in on/off ratio moving from bulk to thin-film LCO has been similarly observed in strained films grown by molecular beam epitaxy [58]. However, four-point probe measurements reveal that despite the differences in texture and grain size, the films on sapphire, SiC, and LAO all demonstrated comparable resistivity on/off ratio of ~205 over the measured temperature range. The polycrystalline films on sapphire and SiC demonstrate an overall shift to higher resistivity, indicating increased grain boundary resistance that does not have a corresponding influence on the spin-state transition. In addition, the low crystallinity of the LCO on quartz substrate exhibits both the highest roughness, lowest on/off ratio (118x), and highest resistivity. This is understandable because while long-range order is not necessary for the mechanics of the Co spin state transition, local symmetry is required.

## 2.3.3 Influence of stoichiometry

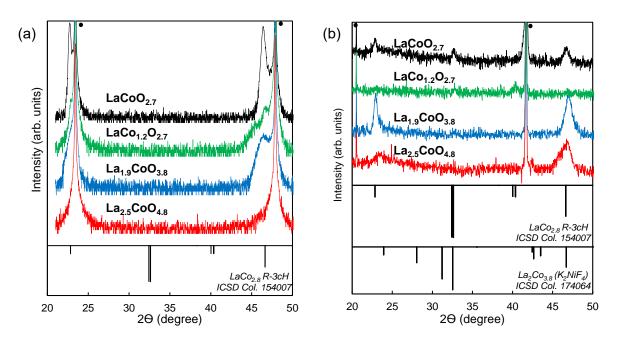

Off-stoichiometry may hold the key to an improved resistivity on/off ratio. There is little prior work exploring the resistivity drop and spin-state transition in off-stoichiometric lanthanum cobalt oxide phases. We deposited a set of LCO films with the x-ray diffraction pattern illustrated in Figure 2.6 (a), demonstrating deteriorating crystallinity grown on LAO as the La/Co ratio increases. We also find evidence that La-heavy films may grow as Ruddlesden -Popper (K<sub>2</sub>NiF<sub>4</sub>) phase on sapphire, given the close match to powder diffraction patterns of La<sub>2</sub>CoO<sub>4</sub> material (Fig. 2.6 (b)).

Figure 2.6 X-ray diffraction pattern of 150 nm lanthanum cobalt oxide films at varying composition deposited on (a) LAO and (b) sapphire. Reference diffraction patterns are obtained from ICSD database. Substrate peaks are labelled with a ● [45].

Furthermore, we have observed that the lanthanum-rich films have greatly increased overall resistivity and much higher switching ratios (Figure 2.7). For example, while the stoichiometric LCO film resistivity will drop ~200 times from room temperature to 350 °C,

the La<sub>2.6</sub>CoO<sub>x</sub> film demonstrates greater than 850 times drop over the same range. We do not entirely comprehend this phenomenon, which has not previously been reported. We may consider the formation of the RP-phase of La<sub>2</sub>CoO<sub>4</sub>, the layered perovskite phase, with a layer of O-Co-O confined two-dimensionally between Lanthanum layers. This phase reduces the degeneracy of the  $e_g$  energy level, stabilizing the IS state and pushing the resistivity higher. However, others have reached the conclusion that the IMT in single crystal La<sub>2</sub>CoO<sub>4</sub> would be suppressed and it would behave entirely as an insulator [59]. In sputtered films, perhaps the greater disorder from the sputtering process favors transition to the entropically favored metallic state. These intriguing composition-structure-property relationships demonstrate the high tunability of the LCO spin-state transition and provide a potential pathway of study.

Figure 2.7 Temperature dependent resistivity data for LCO/LAO demonstrates how increased La concentration increases steepness of the transition profile, as well as the overall resistivity [45].

## 2.4 Estimation of Band Gap Collapse

Near-IR absorption measurements allow for visualization of the band gap collapse as a function of temperature. For semiconductors and insulators, light is absorbed at wavelengths lower (energies higher) than the band gap.

### 2.4.1 Methodology

. Transmission, reflection, and absorption data were collected over the over the 900 nm to 1700 nm range, using a Fianium laser as a light source and calibrated against a GaAs standard. A Linkam temperature controller was modified to allow for simultaneous heating and transmission measurements through the sample holder and was carefully aligned to minimize secondary reflections. Measurements were taken in 25 °C increments from 25 °C to 350 °C. Use of a beam splitter allows two Germanium detectors to simultaneously collect transmission and reflection data. Because the laser power is expected to drift mildly over the course of the two hours of data collection time, all data is normalized to a third reference beam that is unobstructed by the sample. Transmission data is also normalized to a scan of the empty sample holder, and reflection data is normalized to a mirror standard. In total, the equations used are summarized below.

$$\frac{\frac{Sample_{Transmission}}{Sample_{Reference}}}{\frac{Empty_{Transmission}}{Empty_{Reference}}} = T\% \qquad \frac{\frac{Sample_{Reflection}}{Sample_{Reflection}}}{\frac{Mirror_{Reflection}}{Mirror_{Reflection}}} = R\%$$

Absorption % = 1 - Transmission - Reflection

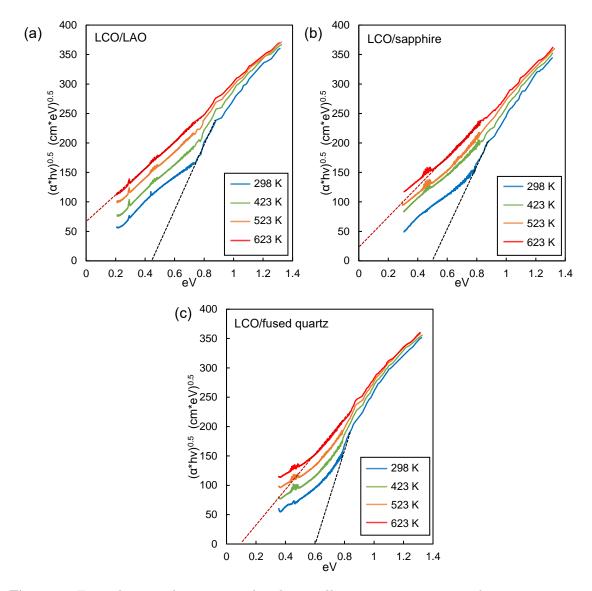

The Tauc method is used to estimate band gap. In this method the photon energy of the measurement wavelength (eV) is plotted against  $(\alpha h\nu)^{1/r}$  where  $\alpha$  is the absorption coefficient and r = 2 for indirect crystalline semiconductors. It is difficult to determine an exact band gap as there is a blurred onset due to the indirect nature [60]. Further, the sputtered film disorder and in-gap defect states leads to the formation of an absorption tail in the Tauc plot (known as the Urbach tail). However, by extracting a linear fit from the absorption data we can estimate the band gap value at the x-intercept and make comparisons between the magnitude of collapse for films.

Figure 2.8 Tauc plots, used to estimate band gap collapse over temperature for 150 nm sputtered LCO grown on (a) LAO (b) sapphire (c) fused quartz [45].

In Figure 2.8 (a-c) we illustrate the Tauc plots for 150 nm LaCoO<sub>2.7</sub> films grown different substrates, with measurements taken from 25 °C to 350 °C. At room temperature, the band gaps of the LCO films are estimated to be 0.45, 0.5, and 0.6 eV for films grown on LAO, sapphire, and fused quartz, respectively. The curvature of the Urbach tail is most prominent in the LCO/quartz glass measurements, which is as expected given the amorphous

nature of that film and thus the greater number of in-gap defects. At 350 °C, only LCO/quartz glass continues to express a bandgap greater than 0 eV (estimated at 0.1 eV based on the x-intercept of the Tauc plot). In contrast, both high temperature Tauc plots for the crystalline LCO/sapphire and LCO/LAO linearize and align with the absorption tail, leading to negative x-intercepts. A "negative" estimation of band gap magnitude suggests the completion of the semiconductor-semimetal transition by 523 K for those films. The near-IR absorption estimate of relative magnitude of band-gap collapse over temperature supports the observed magnitude of the temperature-dependent resistivity drop for all these films.

# 2.5 Conclusions

With the ultimate goal of depositing smooth lanthanum cobalt oxide films for electronics applications, we conducted cathode discharge hysteresis experiments in mixed Ar/O<sub>2</sub> atmosphere in order to better understand the reactive dc sputtering mechanics. This method allows for live tracking of target condition during deposition. Increasing inert gas flow (increasing pumping speed) reduces residence time of reactive species at the target surface, increasing target lifetime and process stability. However, it does not have a strong influence on the onset of the critical reactive sputtering range in terms of reactive gas flow rate. We further investigated the influence of sputter deposition parameters (stoichiometry, substrate) on the electrical properties of lanthanum cobalt oxide grown by a single-step, hightemperature low-pressure process. Firstly, we found, in accordance with previously reported epitaxial films grown on LAO, a reduction in room-temperature electrical resistivity due to strain on the unit cell. Polycrystalline LCO films were grown on SiC and sapphire with surface roughness under 2.5 nm, showing comparable resistivity switching ratio to epitaxial films. We reported that the switching ratio above 25 °C is much greater when the La/Co ratio is increased, with suggested crystallization of the Ruddlesden-Popper phase on sapphire. Near-IR absorption measurements indicated a semiconductor to semimetal transition at around 523 K for crystalline LCO films grown on sapphire and LAO. In contrast, amorphous LCO grown on quartz glass remained semiconducting up to 623 K.

# Chapter 3: 2-Terminal Voltage-triggered Switches

### 3.1 Abstract

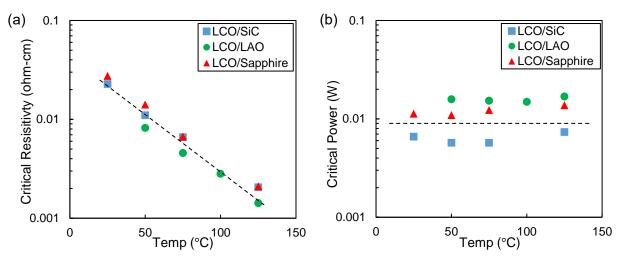

In this chapter I first evaluate various e-beam evaporated metals as ohmic contacts to LCO *via* the transfer length method. This method is used to determine the most thermally stable and lowest contact resistivity options to aid in integration of LCO into power devices. Next, two-terminal LCO switches were fabricated from sputtered films grown on LAO, sapphire, and SiC. We demonstrate an abrupt voltage-triggered transition from semiconducting to conductive state from 25 °C up to 150 °C. The threshold voltage for the switch is shown to have strong dependence on device length and weak dependence on device width. Rather than having a critical resistivity (critical carrier concentration) criterion as expected for homogenous Mott materials, the LCO switches demonstrate a critical power criterion as test temperature increases. This supports the theory that conductive HS clusters grow in a primarily entropy (and Joule-heating) driven mechanism [37,38]. Finally, we report that LCO switches can easily achieve nano-second switching speeds through pulsed voltage time-dependent measurements of scaled devices. In this chapter I also introduce the construction of a multi-physics COMSOL simulation that is proven to accurately predict the speed and magnitude of the LCO IMT.

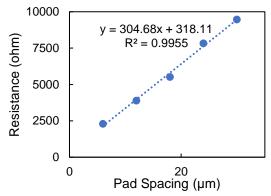

## 3.2 Contact metal evaluation by transfer length method

The transfer length method (TLM) is a technique for determining the specific contact resistivity between a metal and semiconductor. Two-point resistivity is measured between rectangular contact pads deposited over a blanket semiconducting film. By varying the distance between the pads, we may isolate metal-oxide contact resistance from the oxide sample resistance [61]. TLM structures are deposited over 150 nm of blanket sputtered LCO on sapphire substrate by e-beam evaporation (AJA), in the variations listed in Table 3.1.

**Figure 3.1** Example TLM plot for 40 nm Pt on LCO at 200 °C. Two-point resistance is typically measured at each spacing at 10  $\mu$ A. Calculated contact resistivity here is R<sub>c</sub>= 8.30 E-05 ohm-cm<sup>2</sup>

**Table 3.1**: Candidate contact metals tested by the transfer length method, along with the corresponding measured room temperature specific contact resistivity.

| Metal                | Room temperature specific contact resistivity<br>(ohm-cm <sup>2</sup> ) |

|----------------------|-------------------------------------------------------------------------|

| 50 nm Au only        | 4.44E-04                                                                |

| 40 nm Pt/ 40 nm Au   | 1.62E-03                                                                |

| 40 nm NiCr/ 40 nm Au | 3.80E-02                                                                |

| 10 nm Ti/ 40nm Au    | 9.42E-01                                                                |

| 40 nm Cr/40nm Au     | 9.21E-01                                                                |

| 40 nm Pd/ 40 nm Au   | 5.71E-03                                                                |

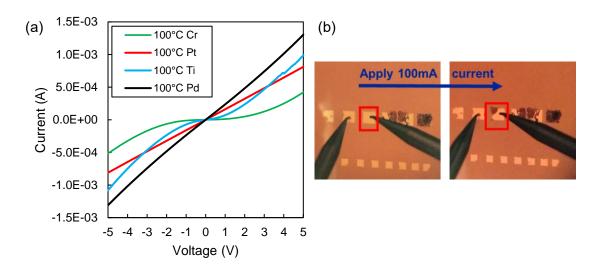

The conventional wisdom is that while a noble metal (Pt, Pd, or Au) will form a lower resistance contact, a reactive metal will provide better adhesion to the semiconductor surface [62]. At room temperature, we observed these expected results too. However, we require LCO-based devices to function at high temperatures and power. Only the noble contact metals of Pd and Pt remained ohmic when the samples were heated above 100 °C, as shown in Figure 3.2 (a). The contact resistivities of those metals when measured at 200 °C are 5.32 E-05 ohm<sup>-</sup> cm<sup>2</sup> and 8.30 E-05 ohm<sup>-</sup> cm<sup>2</sup>, respectively. However, for other contact metals, at higher temperatures and voltages, the slope of the I-V curve increases, indicating the formation of a resistive barrier to current passing. We deduced that reactive metals formed a parasitic oxide

against the LCO films, resulting in non-ohmic behavior from to the metal-insulatorsemiconductor junction.

**Figure 3.2** (a) I-V curves for various contact metals at 100 °C (b) microscope image of degradation of chromium contacts upon forcing of higher current.

Furthermore, the oxygen sensitive metals are physically unstable; when 100 mA was applied, for example, the Cr contact reacted and delaminated from the LCO surface (Figure 3.2 (b)). Similar results recurred even after attempting to anneal the contacts in nitrogen at 250 °C. Thus, practical LCO device contacts must comprise of a starting noble metal layer such as Pd or Pt, which consistently demonstrate lower Rc (~10<sup>-3</sup> to 10<sup>-5</sup> ohm<sup>-</sup>cm<sup>2</sup>) up to 300 °C. This layer also serves as a diffusion barrier to an Au contact layer deposited next. However, due to the poorer adhesion qualities of a noble metal, we find that thin Pt/Pd structures delaminate from LCO at higher input voltages. As described further in Chapter 4.3.4, the minimum line width of a Pt/Au metal contact on LCO should be 1 μm to avoid that form of device failure.

Future optimization in this area is needed, either in the use of other contact metals, or more complex stacks. It is not expected that molybdenum (which oxides rapidly at 500 °C) or indium (which melts at 156 °C), would be appropriate choices. However, we may consider the use of alloy metals, such as Sr or Al, at the LCO interface to assist in adhesion without forming a resistive barrier. We may also consider the use of other high melting point, refractory metals such as tungsten.

# 3.3 Voltage-Triggered Abrupt Transition

### 3.3.1 Methodology