## **UC Irvine**

### **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Advancing Compiler and Simulator Techniques for Highly Parallel Simulation of Embedded Systems

#### **Permalink**

https://escholarship.org/uc/item/7gk8x54f

#### **Author**

Cheng, Zhongqi

#### **Publication Date**

2020

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

Advancing Compiler and Simulator Techniques for Highly Parallel Simulation of Embedded Systems

#### **DISSERTATION**

submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in Computer Engineering

by

Zhongqi Cheng

Dissertation Committee:

Professor Rainer Dömer, Chair

Professor Mohammad Al Faruque

Professor Aparna Chandramowlishwaran

## **DEDICATION**

To Lindsay, for her unconditional love and support.

To my parents, for everything they have done—and still do—for me.

## TABLE OF CONTENTS

|            |              |                                                       |             | Page |

|------------|--------------|-------------------------------------------------------|-------------|------|

| TA         | ABLE         | OF CONTENTS                                           |             | iii  |

| LI         | ST O         | F FIGURES                                             |             | vi   |

| LI         | ST O         | F TABLES                                              |             | viii |

| LI         | ST O         | F ALGORITHMS                                          |             | ix   |

| <b>A</b> ( | CKNO         | WLEDGMENTS                                            |             | X    |

| CI         | U <b>RRI</b> | CULUM VITAE                                           |             | xi   |

| Al         | BSTR         | ACT OF THE DISSERTATION                               |             | xiv  |

| 1          | Intr         | oduction                                              |             | 1    |

|            | 1.1          | Parallel Simulation of Embedded System Models         | . <b></b>   | . 2  |

|            |              | 1.1.1 Discrete Event Simulation                       |             |      |

|            |              | 1.1.2 Synchronous Parallel Discrete Event Simulation  | . <b></b> . | . 5  |

|            |              | 1.1.3 Out-of-Order Parallel Discrete Event Simulation | . <b></b> . | . 7  |

|            | 1.2          | Recoding Infrastructure for SystemC                   | . <b></b> . | . 8  |

|            |              | 1.2.1 Segment Graph                                   |             |      |

|            |              | 1.2.2 SystemC Internal Representation                 |             |      |

|            |              | 1.2.3 Conflict Analysis                               |             |      |

|            |              | 1.2.4 Source Code Instrumentation                     |             |      |

|            |              | 1.2.5 Simulation Library                              |             |      |

|            | 1.3          | Related Work                                          |             |      |

|            | 1.4          | Goals                                                 |             | . 18 |

| 2          | Exte         | nding Static Analysis for Large Models                |             | 22   |

|            | 2.1          | Introduction                                          |             | . 22 |

|            | 2.2          | Problem Definition                                    |             | . 23 |

|            | 2.3          | Related Work                                          |             | . 24 |

|            | 2.4          | Partial Segment Graph                                 |             | . 25 |

|            |              | 2.4.1 Behavior Model and Segment Graph                |             | . 25 |

|            |              | 2.4.2 Concept of PSG                                  |             | . 25 |

|   |      | 2.4.3 Create PSG                                             |

|---|------|--------------------------------------------------------------|

|   |      | 2.4.4 Store and Load PSG                                     |

|   |      | 2.4.5 Integration Phase                                      |

|   | 2.5  | IP Protection and Security                                   |

|   | 2.6  | Experiments and Results                                      |

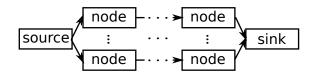

|   |      | 2.6.1 Producer-Consumer Example                              |

|   |      | 2.6.2 Canny Edge Filter                                      |

|   |      | 2.6.3 Bitcoin Miner                                          |

|   | 2.7  | Conclusion                                                   |

| 3 | Exte | ending Static Analysis for Modern Transaction Level Models 3 |

|   | 3.1  | Introduction                                                 |

|   | 3.2  | Background                                                   |

|   |      | 3.2.1 Motivation                                             |

|   |      | 3.2.2 TLM-2.0 Background                                     |

|   | 3.3  | Static Analysis for Blocking Transport Interface             |

|   |      | 3.3.1 Segment Graph for b_transport                          |

|   |      | 3.3.2 Socket Call Path                                       |

|   |      | 3.3.3 Variable Entanglement Analysis                         |

|   | 3.4  | Static Analysis for Direct Memory Interface                  |

|   | 3.5  | Static Analysis for Non-blocking Transport Interface         |

|   | 3.6  | Static Analysis for Debugging Transport Interface            |

|   | 3.7  | Static Analysis for Indirect Communication                   |

|   |      | 3.7.1 Hierarchical Communication                             |

|   |      | 3.7.2 Interconnected Communication                           |

|   | 3.8  | Experiments and Results                                      |

|   |      | 3.8.1 Demonstration Examples                                 |

|   |      | 3.8.2 DVD Player                                             |

|   |      | 3.8.3 Mandelbrot Renderer                                    |

|   |      | 3.8.4 Bitcoin Miner                                          |

|   | 3.9  | Conclusion                                                   |

|   | - 12 |                                                              |

| 4 | _    | roving Coding Guidelines For Faster OoO PDES 6               |

|   | 4.1  | Introduction                                                 |

|   | 4.2  | Proposed Coding Guideline                                    |

|   |      | 4.2.1 SG Granularity and Simulation Speed                    |

|   |      | 4.2.2 Estimation for Level of Parallelism                    |

|   |      | 4.2.3 Motivation                                             |

|   |      | 4.2.4 Overhead Consideration                                 |

|   |      | 4.2.5 Suggestions                                            |

|   | 4.3  | Experiments and Results                                      |

|   |      | 4.3.1 TGFF benchmarks                                        |

|   |      | 4.3.2 Real world examples                                    |

|   | 1 1  | Conclusion                                                   |

| 5 | Opt | imizing | Event Processing in Out-of-Order Parallel Simulation                   | 80  |

|---|-----|---------|------------------------------------------------------------------------|-----|

|   | 5.1 | Introdu | uction                                                                 | 80  |

|   | 5.2 | Relate  | d Work                                                                 | 82  |

|   | 5.3 | Backg   | round                                                                  | 82  |

|   |     | 5.3.1   | Event Notification Table with Prediction                               | 83  |

|   |     | 5.3.2   | Original Event Delivery Strategy                                       | 84  |

|   | 5.4 | Optim   | ized Event Delivery Strategy With Prediction                           | 87  |

|   |     | 5.4.1   | Optimized Event Delivery Algorithm                                     | 87  |

|   |     | 5.4.2   | Complexity Analysis and Optimization                                   |     |

|   | 5.5 | Experi  | iments and Results                                                     |     |

|   |     | 5.5.1   | TGFF Examples                                                          | 92  |

|   |     | 5.5.2   | DVD Player                                                             |     |

|   |     | 5.5.3   | GoogLeNet                                                              | 95  |

|   | 5.6 | Conclu  | usion                                                                  | 96  |

| 6 | Con | clusion |                                                                        | 97  |

|   | 6.1 | Contri  | butions                                                                | 97  |

|   |     | 6.1.1   | A Scalable Solution for Statically Analyzing 3 <sup>rd</sup> Party IPs | 98  |

|   |     | 6.1.2   | A Static Analysis Approach for SystemC TLM-2.0 Models                  | 98  |

|   |     | 6.1.3   | Coding Guidelines for RISC Users                                       | 99  |

|   |     | 6.1.4   | A More Efficient Event Delivery Algorithm in OoO PDES Scheduler Using  |     |

|   |     |         | Prediction Information                                                 | 99  |

|   | 6.2 | Future  | Work                                                                   | 99  |

|   |     | 6.2.1   | More Accurate Static Analysis for SystemC Models                       |     |

|   |     | 6.2.2   | More Efficient OoO PDES                                                | 100 |

## **LIST OF FIGURES**

|            | F                                                                                | age |

|------------|----------------------------------------------------------------------------------|-----|

| 1.1<br>1.2 | Level of abstraction in system design [28]                                       | 2   |

| 1.3        | Synchronous Parallel Discrete Event Simulation (PDES) scheduler for SystemC [33] | -   |

| 1.4        | Out-of-Order Parallel Discrete Event Simulation (OoO PDES) scheduler for Sys-    | U   |

| 1          | temC [34]                                                                        | 9   |

| 1.5        | RISC Compiler and Simulator for Out-of-Order PDES of SystemC [35]                | 10  |

| 1.6        | RISC software stack [35]                                                         | 10  |

| 1.7        | Example SystemC Code and corresponding SG                                        | 11  |

| 1.8        | SystemC IR in RISC compiler                                                      | 12  |

| 1.9        | Contributions in RISC tool flow                                                  | 20  |

| 2.1        | Scaled RISC tool flow with IP components                                         | 23  |

| 2.2        | SystemC Code and PSG                                                             | 25  |

| 2.3        | Integration of PSGs                                                              | 29  |

| 2.4        | SystemC model of Bitcoin miner                                                   | 30  |

| 2.5        | Original and redacted scanner.pd                                                 | 30  |

| 2.6        | SystemC model of Bitcoin miner                                                   | 34  |

| 2.7        | Original and modified PSG for scanner                                            | 34  |

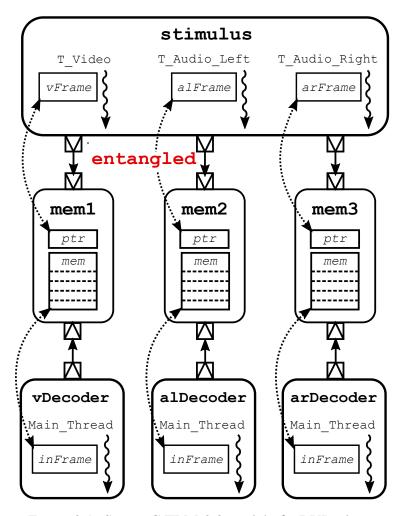

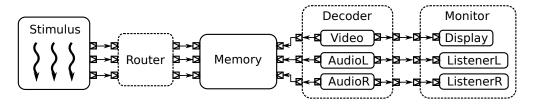

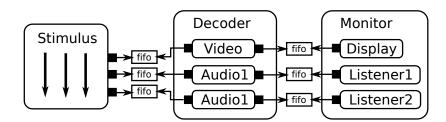

| 3.1        | SystemC TLM-2.0 model of a DVD player                                            | 38  |

| 3.2        | Partial SystemC Code for Figure 3.1                                              | 40  |

| 3.3        | Example of merged SGs of multiple callbacks                                      | 46  |

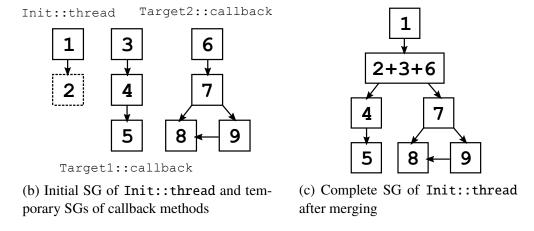

| 3.4        | SCP-included SG of Stimulus::T_Video in Figure 3.2                               | 47  |

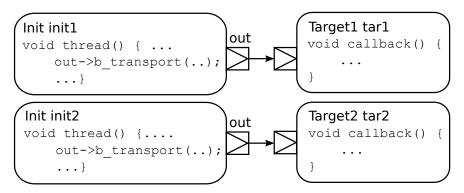

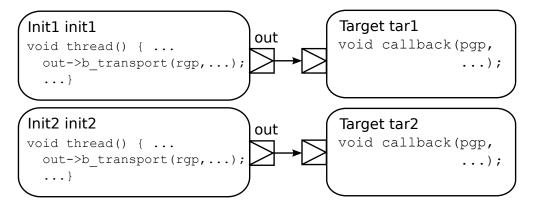

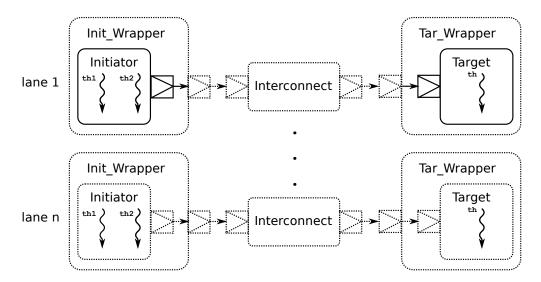

| 3.5        | SystemC model with two initiators and two targets                                | 49  |

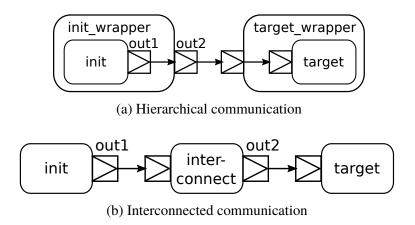

| 3.6        | Example of indirect communications                                               | 54  |

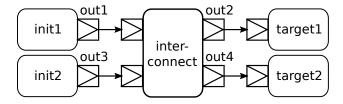

| 3.7        | Interconnected communication with multiple initiators and targets                | 55  |

| 3.8        | Block diagram for the demonstration example                                      | 57  |

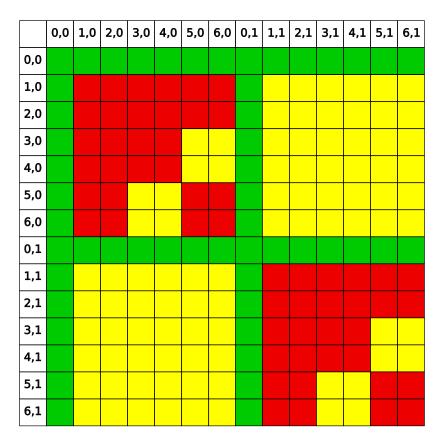

| 3.9        | Data conflict table for BTI+Inter+2-Lanes                                        |     |

| 3.10       | $\mathcal{E}$                                                                    | 62  |

| 3.11       |                                                                                  | 63  |

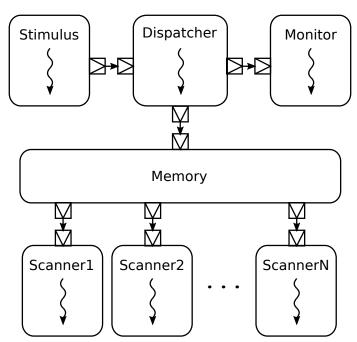

| 3.12       | Block diagram for the Bitcoin miner example                                      | 64  |

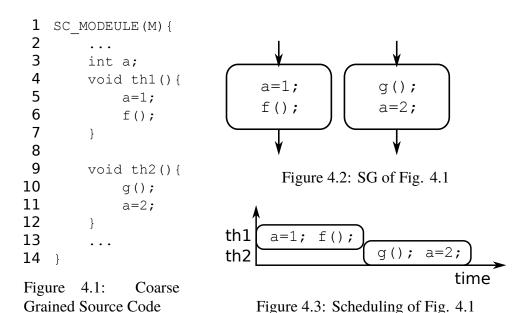

| 4.1        | Coarse Grained Source Code                                                       | 68  |

| 4.2        | SG of Fig. 4.1                                                                   |     |

| 4.3        | Scheduling of Fig. 4.1                                                           | 68  |

| 4.4  | Fine Grained Source Code                           | 69 |

|------|----------------------------------------------------|----|

| 4.5  | SG of Fig. 4.4                                     | 69 |

| 4.6  | Scheduling of Fig. 4.4                             | 69 |

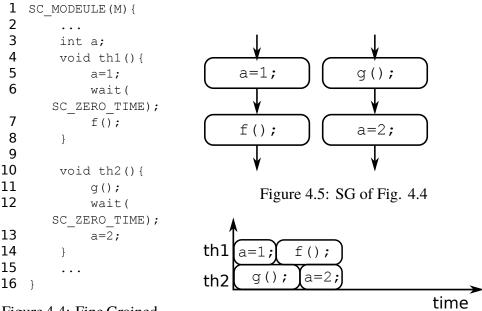

| 4.7  | Source Code for Module M                           | 73 |

| 4.8  | SG for Figure 4.7                                  | 73 |

| 4.9  | DCT for Figure 4.7                                 | 73 |

| 4.10 | Source Code for Module M after partitioning        | 74 |

| 4.11 | SG for Figure 4.10                                 | 74 |

| 4.12 | DCT for Figure 4.10                                | 74 |

| 4.13 | Block Diagram of TGFF Models                       | 76 |

| 4.14 | Original Source Code of Generated Testbench Model  | 76 |

| 4.15 | Optimized Source Code of Generated Testbench Model | 76 |

| 4.16 | Block Diagram of Audio/Video Decoder               | 78 |

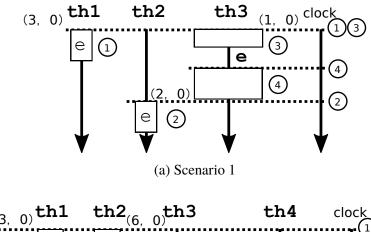

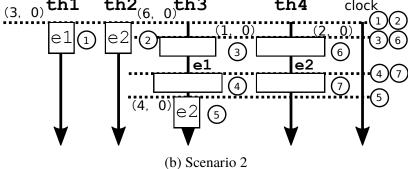

| 5.1  | SystemC model and OoO PDES scheduling              | 81 |

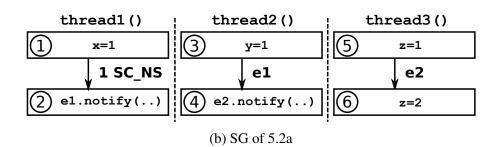

| 5.2  | Example of SG                                      |    |

| 5.3  | ETP for 5.2b                                       |    |

| 5.4  | Scenarios explaining requirement 1 and 2           |    |

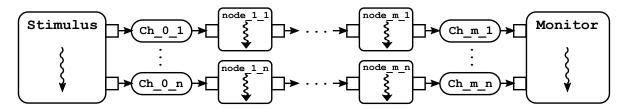

| 5.5  | SystemC model of synthetic examples                |    |

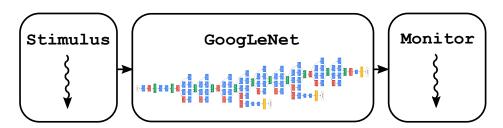

| 5.6  | SystemC model of GoogLeNet [85]                    |    |

## LIST OF TABLES

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                 |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 2.1<br>2.2                                    | PSG meta-data node attributes                                                                                                                                                                                                                                                                                                                                                                                              |                                      |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Results of BTI examples from Accellera: run-time (secs) and speedup (%) Results of DMI examples from Accellera: run-time (secs) and speedup (%) Results of NBTI examples from Accellera: run-time (secs) and speedup (%) Percentage of reduced false variable entanglements in the demonstration examples Results of DVD Player: run-time (secs) and speedup (%) Results of Bitcoin miner: run-time (secs) and speedup (%) | . 58<br>. 58<br>. 58<br>. 62<br>. 63 |

| 4.1<br>4.2<br>4.3                             | Performance of TGFF Benchmarks, Simulator run times (sec) and CPU utilization Performance of Canny Edge Detector                                                                                                                                                                                                                                                                                                           | . 78                                 |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Results of Synthetic Examples: run-time (secs) and speedup (%)                                                                                                                                                                                                                                                                                                                                                             | . 94                                 |

## LIST OF ALGORITHMS

|   |                                                    | Pa | age |

|---|----------------------------------------------------|----|-----|

| 1 | Partial Segment Graph Generation                   |    | 27  |

| 2 | Variable access analysis for entangled variables   |    | 51  |

| 3 | Optimized Event Delivery Strategy using Prediction |    | 88  |

## **ACKNOWLEDGMENTS**

It would have been impossible for me to pursue the doctorate degree without the help and support from the amazing people around me. Here, I would like to give particular mentions to some of whom for encouraging and inspiring me in this long journey.

First and foremost, I would like to express my gratitude to my Masters and Doctorate advisor, Professor Rainer Dömer, for his guidance and support during my graduate study in University of California, Irvine. When I just joined his team, I was not aware of what academic research was about. His insights and broad knowledge of embedded system design methodologies helped me a lot in finding my own research directions. He also taught me how to do high quality research and how to balance between academic values and engineering efforts, which are invaluable for my whole career. I also appreciate most his kind and patient personalities, which created an relaxing and enjoyable environment in the lab. Such working environment was very helpful for increasing the efficiency of my research.

I would also like to thank Professor Mohammad Al Faruque, Professor Aparna Chandramowlish-waran and Professor Kwei-Jay Lin. I took their courses during my Masters and learned a lot about embedded systems and parallel computing knowledge and techniques. This built a solid foundation for my Doctorate study. They also spent their precious time being my committee members and provided me constructive advice and feedback on my dissertation.

In addition, I would like to thank my team members, Guantao Liu, Tim Schmidt, Daniel Mendoza and Emad Arasteh. Guantao and Tim provided me endless help on understanding the existing technologies of our group when I just joined and shared frequently their thoughts and ideas about research in this area. Daniel worked closely with me on several projects and I appreciate very much his cleverness and hardworking, which inspired me a lot. I am also grateful to Emad for his friendship and for all fruitful discussions with him.

All the works I have done in the five years have been supported by funding from Intel Corporation. I thank Intel for the valuable support.

Furthermore, I would like to thank my wife Lindsay Yan. She always stood by my side when I got lost during my research and cheered me up. She is the love of my life and I would not be what I am without her.

Finally, I owe my deepest gratitude to my parents for their unconditional love for me and continuous encouragements throughout my entire study. Their supports are beyond any description in words. My accomplishments would not have been possible without them. Thank you.

## **CURRICULUM VITAE**

## Zhongqi Cheng

### **EDUCATION**

| Doctor of Philosophy in Computer Engineering | 2020               |

|----------------------------------------------|--------------------|

| University of California, Irvine             | Irvine, California |

| Master of Science in Computer Engineering    | 2017               |

| University of California, Irvine             | Irvine, California |

| Bachelor of Science in Microelectronics      | 2015               |

| Shanghai Jiao Tong University                | Shanghai, China    |

|                                              |                    |

#### RESEARCH EXPERIENCE

| Graduate Research Assistant      | 2016–2020          |

|----------------------------------|--------------------|

| University of California, Irvine | Irvine, California |

### TEACHING EXPERIENCE

| University of California, Irvine                                                                    | <b>2016</b><br>Irvine, California     |

|-----------------------------------------------------------------------------------------------------|---------------------------------------|

| <b>Teaching Assistant for Embedded Systems Modeling and Design</b> University of California, Irvine | <b>2017</b><br>Irvine, California     |

| <b>Teaching Assistant for Embedded Systems Modeling and Design</b> University of California, Irvine | <b>2018</b> <i>Irvine, California</i> |

| <b>Teaching Assistant for Embedded Systems Modeling and Design</b> University of California, Irvine | <b>2019</b><br>Irvine, California     |

| <b>Teaching Assistant for Embedded Software</b> University of California, Irvine                    | <b>2020</b><br>Irvine, California     |

#### REFEREED JOURNAL PUBLICATIONS

Zhongqi Cheng, Rainer Dömer. **Analyzing Variable Entanglement for Parallel Simulation of SystemC TLM-2.0 Models**. ACM Transactions on Embedded Computing Systems 18, 5s, Article 79 (October 2019).

#### REFEREED BOOK CHAPTERS

Zhongqi Cheng, Tim Schmidt, Rainer Dömer. **SystemC Coding Guideline for Faster Out-of-Order Parallel Discrete Event Simulation**. Chapter 6 in "Languages, Design Methods, and Tools for Electronic System Design" by T. Kazmierski, S. Steinhorst and D. Grosse, reprint of best papers at FDL 2018, Springer Nature, Switzerland, January 2020. (ISBN 978-3-030-31585-6)

#### REFEREED CONFERENCE PUBLICATIONS

Daniel Mendoza, Zhongqi Cheng, Emad Arasteh, Rainer Dömer. Lazy Event Prediction using Defining Trees and Schedule Bypass for Out-of-Order PDES. Proceedings of the Design, Automation and Test in Europe (DATE) Conference, Grenoble, France, March 2020.

Zhongqi Cheng, Emad Arasteh, Rainer Dömer. **Event Delivery using Prediction for Faster Parallel SystemC Simulation**. Proceedings of the Asia and South Pacific Design Automation Conference, Beijing, China, January 2020.

Daniel Mendoza, Ajit Dingankar, Zhongqi Cheng, Rainer Dömer. **Integrating Parallel SystemC Simulation into Simics(R) Virtual Platform'**. Proceedings of the Design and Verification Conference in Europe, Munich, Germany, October 2019.

Zhongqi Cheng, Tim Schmidt, Rainer Dömer. **Enabling IP Reuse and Protection in Out-of-Order Parallel SystemC Simulation**. Proceedings of the International Embedded Systems Symposium, Springer, Friedrichshafen, Germany, September 2019.

Zhongqi Cheng, Tim Schmidt, Rainer Dömer. **SystemC Coding Guideline for Faster Out-of-Order Parallel Discrete Event Simulation**. Proceedings of Forum on Specification and Design Languages, Munich, Germany, September 2018.

Tim Schmidt, Zhongqi Cheng, Rainer Dömer. **Port Call Path Sensitive Conflict Analysis for Instance-Aware Parallel SystemC Simulation**. Proceedings of Design, Automation and Test in Europe, Dresden, Germany, March 2018.

Zhongqi Cheng, Tim Schmidt, Rainer Dömer. Thread- and Data-Level Parallel Simulation in SystemC, a Bitcoin Miner Case Study. Proceedings of the International High Level Design

Validation and Test Workshop 2017, Santa Cruz, California, October 2017.

#### MASTER THESIS

Zhongqi Cheng. **Design and Evaluation of a Bitcoin Miner SystemC Model with Thread and Data-Level Parallelism**. Master's thesis, University of California, Irvine, California, June 2017.

#### **TECHNICAL REPORTS**

Guantao Liu, Tim Schmidt, Zhongqi Cheng, Daniel Mendoza, Rainer Dömer. **RISC Compiler and Simulator, Release V0.6.0: Out-of-Order Parallel Simulatable SystemC Subset**. Center for Embedded and Cyber-Physical Systems, Technical Report 19-04, September 2019.

Guantao Liu, Tim Schmidt, Zhongqi Cheng, Daniel Mendoza, Rainer Dömer. **RISC Compiler and Simulator, Release V0.5.0: Out-of-Order Parallel Simulatable SystemC Subset**. Center for Embedded and Cyber-Physical Systems, Technical Report 18-03, September 2018.

Guantao Liu, Tim Schmidt, Zhongqi Cheng, Rainer Dömer. **RISC Compiler and Simulator, Release V0.4.0: Out-of-Order Parallel Simulatable SystemC Subset**. Center for Embedded and Cyber-Physical Systems, Technical Report 17-05, July 2017.

#### **OPEN SOURCE SOFTWARE RELEASES**

**Docker image for RISC Compiler and Simulator, Release V0.6.0**. https://hub.docker.com/r/ucirvinelecs/risc060/, September, 2019.

**RISC Compiler and Simulator, Release V0.6.0**. http://www.cecs.uci.edu/~doemer/risc.html#RISC060, September, 2019.

RISC Compiler and Simulator, Release V0.5.0. http://www.cecs.uci.edu/~doemer/risc.html#RISC050, September, 2018.

RISC Compiler and Simulator, Release V0.4.2. http://www.cecs.uci.edu/~doemer/risc.html#RISC042, June, 2018.

RISC Compiler and Simulator, Release V0.4.0. http://www.cecs.uci.edu/~doemer/risc.html#RISC040, July, 2017.

### ABSTRACT OF THE DISSERTATION

Advancing Compiler and Simulator Techniques for Highly Parallel Simulation of Embedded Systems

By

#### Zhongqi Cheng

Doctor of Philosophy in Computer Engineering

University of California, Irvine, 2020

Professor Rainer Dömer, Chair

As an Electronic System Level (ESL) design language, the IEEE SystemC standard is widely used for testing, validation and verification of embedded system models. Discrete Event Simulation (DES) has been used for decades as the default SystemC simulation semantic. However, due to the sequential nature of DES, Parallel DES has recently gained an increasing amount of attention for performing high speed simulations on parallel computing platforms. To further exploit the parallel computation power of modern multi- and many-core platforms, Out-of-order Parallel Discrete Event Simulation (OoO PDES) has been proposed. In OoO PDES, threads comply with a partial order such that different simulation threads may run in different time cycles to increase the parallelism of execution. The Recoding Infrastructure for SystemC (RISC) has been introduced as a tool flow to fully support OoO PDES.

To preserve the SystemC semantics under OoO PDES, a compiler based approach statically analyzes the race conditions in the input model. However, there are severe restrictions: the source code for the input design must be available in one file, which does not scale. This disables the use of Intellectual Property (IP) and hierarchical file structures. In this dissertation, we propose a partial-graph based approach to scale the static analysis to support separate files and IP reuse. Specifically, the Partial Segment Graph (PSG) data structure is proposed and is used to abstract the behaviours and communication of modules within a single translation unit. These partial graphs

are combined at top level to reconstruct the complete behaviors and communication of the entire model.

We also propose new algorithms to support the static analysis for modern SystemC TLM-2.0 standard. SystemC TLM-2.0 is widely used in industrial ESL designs for better interoperability and higher simulation speed. However, it is identified as an obstacle for parallel SystemC simulation due to the disappearance of channels. To solve the problem, we propose a compile time approach to statically analyze potential conflicts among threads in SystemC TLM-2.0 loosely-and approximately-timed models. A new Socket Call Path (SCP) technique is introduced which provides the compiler with socket binding information for precise static analysis. Based on SCP, an algorithm is proposed to analyze entangled variable pairs for automatic and accurate conflict analysis.

Besides the works on the compiler side, we focus as well on increasing the simulation speed of OoO PDES. We observe that the granularity of the Segment Graph (SG) data structure used in static analysis has a high impact on OoO PDES. This motivates us to propose a set of coding guidelines for the RISC users to properly refine their SystemC model for a higher simulation speed.

Furthermore, in this dissertation, an algorithm is proposed to optimize directly the event delivery strategy in OoO PDES. Event delivery in OoO PDES was very conservative, which often postponed the execution of waiting threads due to unknown future behaviors of the SystemC model, and in turn became a bottleneck of simulation speed. The algorithm we propose takes advantage of the prediction of future thread behaviors, and therefore allows waiting threads to resume execution earlier, resulting in significantly increased simulation speed.

To summarize, the contributions of this dissertation include: 1) a scalable RISC tool flow for statically analyzing and protecting 3rd party IPs in models with multiple files, 2) an advanced static analysis approach for modern SystemC TLM-2.0 models, 3) a set of coding guidelines for RISC users to achieve higher simulation speed, and 4) a more efficient event delivery algorithm in OoO PDES scheduler using prediction information.

Together, these compiler and simulator advances enable OoO PDES for larger and modern model

| simulation and thus improve the design of embedded systems significantly, leading to better devices |

|-----------------------------------------------------------------------------------------------------|

| at lower cost in the end.                                                                           |

|                                                                                                     |

# Chapter 1

## Introduction

In recent years, embedded systems become ubiquitous and essential. They are included in almost every kind of devices, e.g. cell-phones [1, 2, 3, 4], automobiles [5, 6, 7, 8], medical instruments [9, 10, 11, 12], missiles [13, 14, 15, 16] and so on. However, as people are demanding faster and more functional electronic devices, this leads to a rapid growing of the complexity and heterogeneity of embedded systems [17, 18, 19]. It becomes much more difficult and complicated for developers to consider all aspects of the entire design. To solve this problem, Electronic System Level (ESL) design methodology was proposed and widely studied [20, 21, 22, 23]. Developers first model and evaluate a design at a high abstraction level with a main focus on functionalities and algorithms. Before converting the system level design into Register-Transfer Level (RTL) designs, the developers have to carefully verify the correctness of the model. One common verification approach is Simulation-based Validation [24, 25, 26], which simulates the given model and produces an accurate result.

IEEE SystemC [27] is a standard ESL design language and is widely used for testing, validation and verification of system level models. To utilize the parallel computation power of modern multi-core processors in SystemC simulation, parallel simulation approaches attract a lot of attention in the community. In this dissertation, we aim at designing and improving more advanced algorithms for

parallel simulation of modern SystemC models.

## 1.1 Parallel Simulation of Embedded System Models

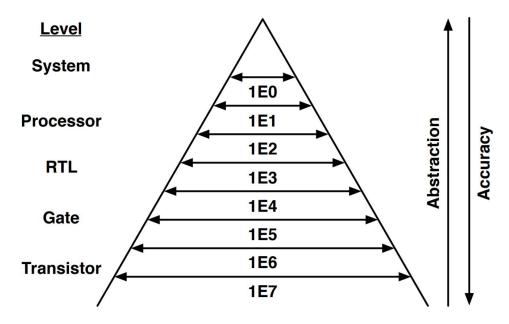

ESL design is a level above RTL design including both software and hardware of the whole system. Figure 1.1 illustrates the complexities of different levels of abstraction in a complete design flow [28]. It clearly illustrates the trade-off between complexity and model accuracy for different abstraction levels. ESL design is a promising approach at an early stage of the design flow.

Figure 1.1: Level of abstraction in system design [28]

SystemC [27] is a de-facto language for ESL design in industry. With more than 20 years' development, SystemC has been widely applied to system-level modeling, architectural exploration, performance modeling, software development, functional verification, and high-level synthesis. SystemC is often associated with ESL design and with transaction-level modeling (TLM). Technically, SystemC is a set of C++ classes and macros. Developers can easily write SystemC models following the C++ syntax. Although SystemC is capable for RTL modeling and simula-

tion, this dissertation mainly focus on modeling and simulation for un-timed, loosely-timed and approximately-timed TLM and TLM-2.0 [29] SystemC models.

SystemC provides an event driven simulation interface which enables the simulation of concurrent SystemC processes. In the next sections, we are going to describe different approaches of Discrete Event Simulation (DES) algorithms.

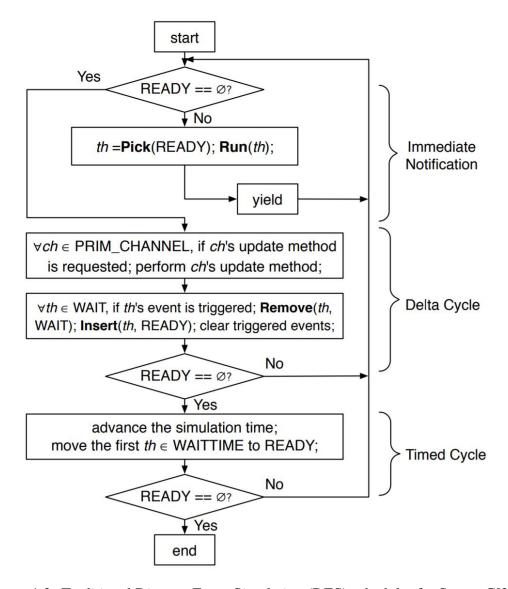

#### 1.1.1 Discrete Event Simulation

DES [30] is the inherent simulation approach for the SystemC language [31]. It utilizes a central scheduler to manage multiple concurrent threads, which results in temporal barriers (namely time and delta cycle) in the SystemC simulation. According to the cooperative multitasking semantics of the SystemC standard IEEE 1666-2011 [27], most SystemC simulator implementations have only one thread active at the same time and thus cannot utilize the parallel computing resources available on multi-core (or many-core) processor hosts. This significantly limits the execution speed of SystemC simulation. Figure 1.2 shows the algorithm for the traditional discrete event simulator [32].

Here, we formally define the data structures, states and operations used in DES:

1) In DES, we have the following thread queues:

- 1. **QUEUES** = {**READY**, **RUN**, **WAIT**, **WAITTIME**, **COMPLETE**}.

- 2. **READY** =  $\cup th$  where thread th is ready to run.

- 3. **RUN** =  $\cup th$  where thread th is running.

- 4. **WAIT** =  $\cup th$  where thread th is waiting for an event.

- 5. **WAITTIME** =  $\cup th$  where thread th is waiting for time advance.

- 6. **COMPLETE** =  $\cup th$  where thread th has completed its execution.

Figure 1.2: Traditional Discrete Event Simulation (DES) scheduler for SystemC[32]

- 2) In DES, we have the following simulation invariants:

- 1. THREADS = READY  $\cup$  RUN  $\cup$  WAIT  $\cup$  WAITTIME  $\cup$  COMPLETE.

- 2.  $\forall A, B \in \mathbf{QUEUES}$  and  $A \neq B, A \cap B = \emptyset$ .

- 3) In DES, we have the following operations:

- 1. Run(th): Dispatch thread th.

- 2. th = Pick(READY): Pick a thread from the **READY** queue.

- 3. Remove(*th*, **WAIT**): Remove thread *th* from the **WAIT** queue.

- 4. Insert (th, **READY**): Insert thread th to the **READY** queue.

- 4) In DES, we have the following initial states:

- 1. **THREADS** =  $\{th_{root}\}$ .

- 2. **RUN** =  $\{th_{root}\}$ .

- 3. **READY** = **WAIT** = **WAITTIME** = **COMPLETE** =  $\emptyset$ .

In DES, the simulated time contains two parts: the time cycle and the delta cycle. The time cycle represents the actual time advance during the simulation. The delta cycle is interpreted as the zero-delay semantics in digital systems.

The simulation is driven by events and time advances. At any time, the simulator runs a single thread from the **READY** queue. Once the **READY** queue is empty, the simulator checks the **WAIT** queue and move the threads that wake up to the **READY** queue. If the **READY** queue is still empty after event delivery, time will be advanced and corresponding threads in the **WAITTIME** queue are moved to the **READY** queue. If the **READY** queue is still empty, then the simulation reaches the end.

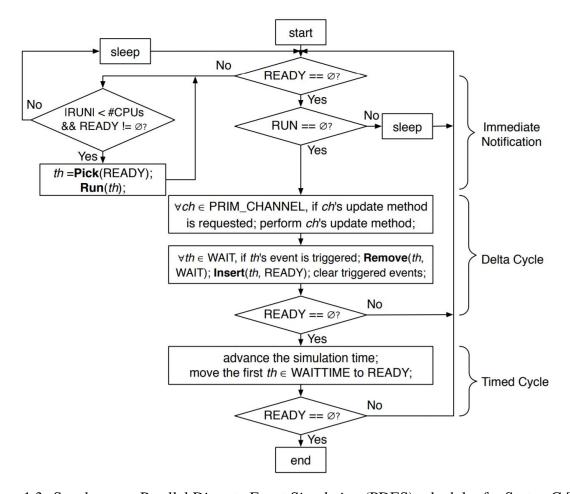

### 1.1.2 Synchronous Parallel Discrete Event Simulation

In order to provide faster simulation and due to the inexpensive availability of parallel processing on today's multi-core (and many-core) processors, Parallel Discrete Event Simulation (PDES) has recently gained significant attention [33]. The synchronous PDES simulator issues multiple threads (i.e. SC\_METHOD, SC\_THREAD and SC\_CTHREAD) at the same time and dispatches them

onto the available cores in parallel. Specifically, once the **READY** queue is not empty and there are still cores idle, threads will be dispatched from the **READY** queue to run on the idle cores, until no more threads remaining in the **READY** queue or all cores are used. In turn, the simulation speed increases significantly.

Figure 1.3: Synchronous Parallel Discrete Event Simulation (PDES) scheduler for SystemC [33]

The scheduler in the parallel simulator works in a similar way as the sequential simulator. There is still a main loop for handling event notifications. The main difference is that the parallel simulator picks multiple threads from the **READY** queue in each cycle, and runs them in parallel. The algorithm is shown in Figure 1.3. Note that in synchronous PDES, time advances happen globally. That is, earlier completed threads have to wait until all other running threads reach the same simulation

cycle, even if the threads do not have any conflict with each other in the future. The strict total order of time imposed by the synchronous PDES is still a limit to high performance parallel simulation.

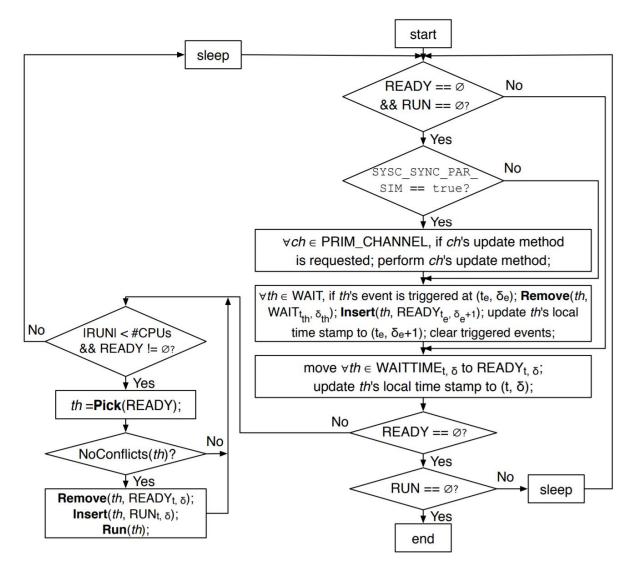

#### 1.1.3 Out-of-Order Parallel Discrete Event Simulation

To further utilize the parallel computation power of multi-core processors, Out-of-Order Parallel Discrete Event Simulation (OoO PDES) was proposed [34]. In OoO PDES, the simulation time is local to individual threads and events. It is formally defined as follows:

- 1. A thread *th* is assigned a local timestamp  $(t_{th}, \delta_{th})$ .

- 2. An event *e* is assigned a local timestamp  $(t_e, \delta_e)$ .

Timestamps have the following orders:

- 1.  $(t_1,\delta_1) = (t_2,\delta_2)$  iff  $t_1 = t_2$  and  $\delta_1 = \delta_2$ .

- 2.  $(t_1,\delta_1) < (t_2,\delta_2)$  iff  $t_1 < t_2$ , or  $t_1 = t_2$  and  $\delta_1 < \delta_2$ .

In OoO PDES, thread queues are separated into ones that correspond to different timestamps:

- 1. **QUEUES** = {**READY**, **RUN**, **WAIT**, **WAITTIME**, **COMPLETE**}.

- 2. **READY** =  $\cup$ **READY**<sub>t, $\delta$ </sub>, **READY**<sub>t, $\delta$ </sub> =  $\cup$ th where thread th is ready to run at  $(t, \delta)$ .

- 3. **RUN** =  $\cup$ **RUN**<sub> $t,\delta$ </sub>, **RUN**<sub> $t,\delta$ </sub> =  $\cup$  th where thread th is running at  $(t,\delta)$ .

- 4. **WAIT** =  $\cup$ **WAIT**<sub> $t,\delta$ </sub>, **WAIT**<sub> $t,\delta$ </sub> =  $\cup$ th where thread th is waiting for an event since  $(t,\delta)$ .

- 5. **WAITTIME** =  $\cup$ **WAITTIME**<sub> $t,\delta$ </sub>, **WAITTIME**<sub> $t,\delta$ </sub> =  $\cup$ th where thread th is waiting for a time advance at  $(t,\delta)$ .

6. **COMPLETE** =  $\cup$ **COMPLETE**<sub> $t,\delta$ </sub>, **COMPLETE**<sub> $t,\delta$ </sub> =  $\cup$ th where thread th has completed its execution at  $(t,\delta)$ .

In OoO PDES, initial states are refined as follows:

- 1. **THREADS** =  $\{th_{root}\}$  where  $(t_{root}, \delta_{root}) = (0,0)$ .

- 2. **RUN** = **RUN**<sub>0,0</sub> =  $\{th_{root}\}$ .

- 3. READY = READY<sub>0,0</sub> = WAIT = WAIT<sub>0,0</sub> = WAITTIME = WAITTIME<sub>0,0</sub> = COMPLETE = COMPLETE<sub>0,0</sub> =  $\emptyset$ .

Figure 1.4 depicts the algorithm of OoO PEDS. In OoO PDES, no global time order is imposed to the simulation threads. The scheduler aggressively moves any thread in **WAIT** that is notified by an event or any thread in **WAITTIME** to the **READY** queue. Note the NoConflicts(th) condition shown in Figure 1.4. Detailed dependency analysis is needed to avoid data or event conflicts for any shared variables among the parallel threads. Only if NoConflicts(th) is true, a new thread is issued for parallel execution (moved from the **READY** to the **RUN** queue). With the partial order of timing and advanced conflict analysis, the system model can be simulated without loss of accuracy with higher simulation speed.

We will be using advanced static compile-time analysis (and optionally dynamic run-time analysis) to identify all potential conflicts. Based on this information (a simple table look-up is sufficient), the OoO PDES scheduler can then at run-time quickly decide whether or not a set of threads has any conflicts with each other.

## 1.2 Recoding Infrastructure for SystemC

The Recoding Infrastructure for SystemC (RISC) [35] is essential to realize the OoO PDES approach. In this section, we briefly describe the basic concepts and notions in RISC.

Figure 1.4: Out-of-Order Parallel Discrete Event Simulation (OoO PDES) scheduler for SystemC [34]

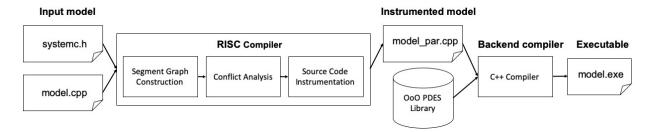

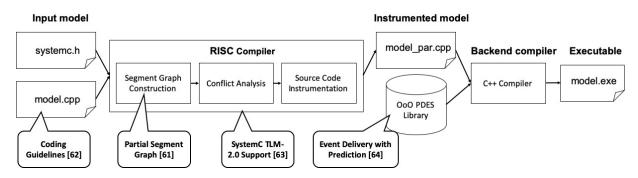

As described in Section 1.1.3, a dedicated SystemC compiler is implemented to provide essential information for the OoO PDES simulation library. Figure 1.5 shows the design flow using the RISC compiler and simulator [36]. As shown in this figure, the input SystemC model file is first sent to the RISC compiler, and the front-end RISC compiler generates an instrumented intermediate model. Then this model is linked against the parallel RISC SystemC library by the target compiler (a regular C++ compiler) to produce the final executable file. This is different from the conventional SystemC simulation where a regular C++ compiler includes the SystemC headers and links the input model directly against the SystemC library.

Figure 1.5: RISC Compiler and Simulator for Out-of-Order PDES of SystemC [35]

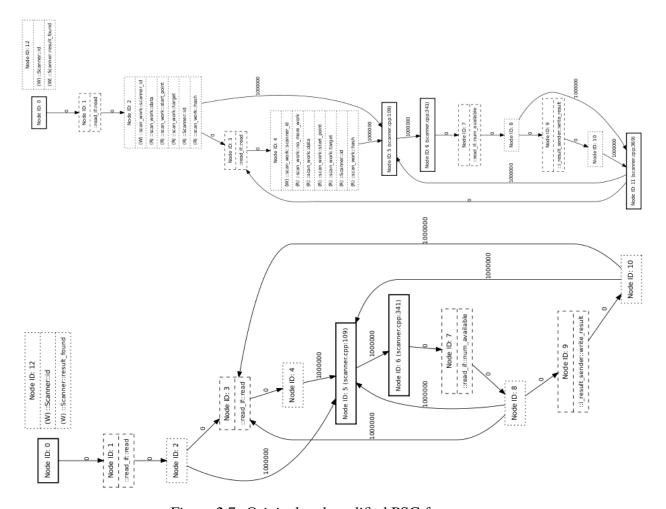

In RISC compiler four major tasks are performed. The compiler first constructs the Abstract Syntax Tree (AST) and builds the Segment Graph (SG) which describes the behaviors of SystemC processes. Next, it builds the Internal Representation (IR) of the SystemC model. Then, based on IR and SG, the compiler generates the conflict tables representing the data race conditions, segment dependencies and other information about the model. Finally, an intermediate model is created, containing all the conflict tables and other essential information for the OoO PDES library.

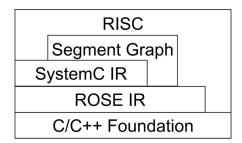

## 1.2.1 Segment Graph

RISC compiler relies on a complex software stack as its foundation, as shown in Figure 1.6. On top of the AST constructed using C/C++ standard libraries and ROSE infrastructure [37], RISC compiler generates the SG data structure.

Figure 1.6: RISC software stack [35]

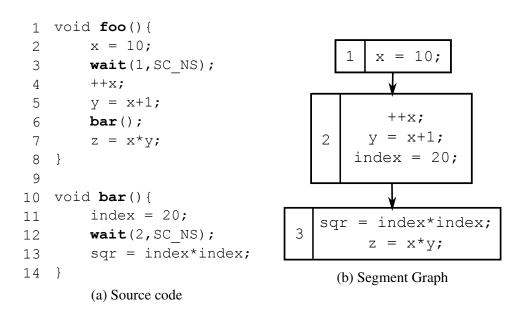

The SG is a directed graph where each node is a set of code statements executed between two scheduling steps [34]. A scheduling step is the entry to the scheduler domain from the application domain during execution of the model, which includes wait statement, start of a SystemC process and end of a SystemC process. An example of SystemC source code is shown in Figure 1.7a. The corresponding SG is shown in Figure 1.7b.

Figure 1.7: Example SystemC Code and corresponding SG

A SG is automatically built by the RISC compiler as discussed in Algorithm 5 in [38]. The algorithm analyzes every source code statement and groups them into segments. For instance, ++x in line 4 and y=x+1 in line 5 are assigned both to segment 2 as they are executed after the same scheduling step: wait(1,SC\_NS) in line 3. Function call is a special case because it may contain multiple statements and/or scheduling steps. When a function call is encountered, the algorithm first finds the definition of the function and constructs a temporary SG  $sg\_func$  for the function. Then,  $sg\_func$  is merged into the calling segment. In this example, bar() is first encountered while building segment 2. The RISC compiler identifies the definition of bar() in the AST and builds a SG  $sg\_func$  for bar(). Then,  $sg\_func$  is merged into segment 2.

### 1.2.2 SystemC Internal Representation

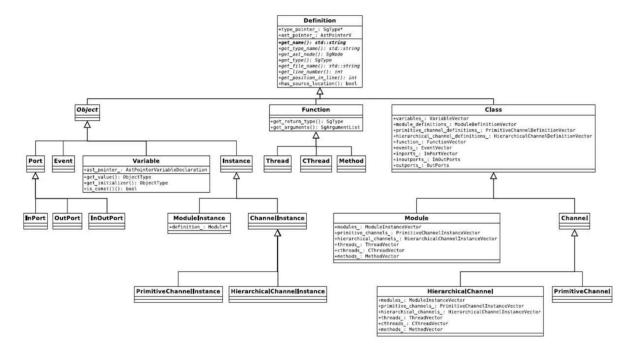

SystemC IR is built based on AST generated by ROSE infrastructure. It reflects the SystemC module and channel hierarchy, connectivity, and other SystemC-specific relations, as depicted in Figure 1.8. This is similar to the SystemC-clang representation [39]. More details are described in [36].

Figure 1.8: SystemC IR in RISC compiler

## 1.2.3 Conflict Analysis

Based on SG and SystemC IR, RISC compiler analyzes the conflicts at segment level. Potential conflicts in SystemC include data hazards, event hazards, and timing hazards, all of which may exist among the segments executed by the threads considered for parallel execution. The conflict information is used at runtime by the simulator to make sure that there is no thread dispatched if the thread has any potential conflicts against threads in the **RUN** or **READY** queue. The RISC compiler detects conflicts in two ways: static analysis at compile time and dynamic analysis in

the elaboration phase at run time. It should be emphasized that the accuracy of this analysis has significantly improved with the recent RISC release V0.6.0, which includes the advances presented in this work. As outlined in detail in [40], the RISC compiler now supports Port Call Path (PCP) sensitive conflict analysis which makes it aware of the actual channel instances used by threads from different modules. This much more precise analysis can avoid false positive conflicts in many cases and thus increases the efficiency of the simulation which, in turn, runs faster.

#### **Static Conflict Analysis**

Static analysis depends purely on the available information in the SystemC source code of the design model at input. In this case, the RISC compiler performs very conservative identification of the potential hazards in the model, as outlined in [36]. Identifying all possible hazards is a complex analysis task that requires the full understanding of the module hierarchy. Here we statically extract the module hierarchy and analyze the individual threads.

#### **Dynamic Analysis**

However, in most cases not all of the needed information can be gathered statically. For instance, design parameters may be passed via the command line to define the number of modules, certain channel characteristics, or other configuration information. In such SystemC models, the instantiated modules, channels, and ports are typically created through loops in a dynamic fashion. Thus, these exact parameters are only available at run time, so they cannot be statically analyzed. In these cases, dynamic analysis is needed.

In dynamic analysis, the compilation flow is extended by a preprocessing step. The input SystemC model is fed into the RISC elaborater which produces an executable model that only performs the SystemC elaboration phase. At the end of the elaboration phase, the executable model automatically traverses the created module hierarchy via the SystemC introspection API and dumps this detailed

structural design information into an instance connectivity file. This file is in turn provided as an input to the RISC compiler, so that the dynamically created design hierarchy and specific instance connectivity can be used for precise conflict analysis. The instance connectivity data file includes the actual module hierarchy, the specific port mapping, and the actual target variable mapping of references.

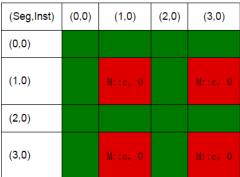

#### 1.2.4 Source Code Instrumentation

As a result of the conflict analysis (static, dynamic, or hybrid [36]), the RISC compiler generates several conflict tables that describe all possible conflicts between threads in any two segments. Using this conservative conflict information, the simulator can then at run-time quickly determine by a simple table look-up whether or not it is safe to issue any given thread in parallel or ahead of time.

As shown above in Figure 1.5, the RISC compiler and simulator work closely together. The compiler performs conservative conflict analysis and passes the analysis results to the simulator which then can make safe scheduling decisions quickly.

To pass information from the compiler to the simulator, we use automatic model instrumentation. That is, the intermediate model generated by the compiler contains instrumented (automatically generated) source code which the simulator can then rely on. At the same time, the RISC compiler also instruments user-defined SystemC channels with automatic protection against race conditions among communicating threads.

In total, the RISC source code instrumentation includes four major components:

- Segment and instance IDs: Individual threads are uniquely identified by a creator instance ID and their current code location (segment ID). Both IDs are passed into the simulator kernel as additional arguments to scheduler entry functions, including wait and thread creation.

- Data and event conflict tables: Segment concurrency hazards due to potential data conflicts,

event conflicts, or timing conflicts are provided to the simulator as two-dimensional tables indexed by a segment ID and instance ID pair. For efficiency, these table entries are filtered for scope, instance path, and reference and port mappings.

• Current and next time advance tables, and thread state prediction tables: The simulator can make better scheduling decisions by looking ahead in time if it can predict the possible future thread states. This optimization is discussed in detail in [41] and is available in the RISC Compiler and Simulator in versions 0.4.0 and later. Since thread state prediction for most models requires only little additional compile time but results often in higher simulation speed, it is enabled by default.

Note that the source code instrumentation is performed automatically by the RISC Compiler and no user interaction is necessary. However, the interested user may inspect the instrumented source code. It is stored in a file named risc\_model\_name.cpp which serves as the input file to the compiler back-end which in turn then generates the final executable.

With RISC version 0.6.0, source code instrumentation is optimized for large design models with many segments. Here, the conflict, time, and prediction tables can become fairly large, which unnecessarily slows down the code generation step during compilation. To avoid such inefficiency, a separate file (model\_name.risc) is automatically generated with binary images of the tables. This file is then read at run time (automatically, just like a shared library) to fill the conflict, time, and prediction tables needed by the simulator.

## 1.2.5 Simulation Library

Same as the classic Accellera proof-of-concept implementation, the RISC simulator is not an explicit tool, but a run-time library that the generated executable SystemC model is linked against. Thus, simulation is performed by execution of the compiled model, the same way as in the classic tool flow (just faster).

By default, the simulation library performs OoO PDES scheduling. However, when primary channels are detected in the model, or specified by the user, the RISC simulation library can fall back to Synchronous PDES or even DES.

DES is the inherent approach for SystemC simulation. However, due to its sequential nature,

### 1.3 Related Work

PDES is studied to take advantage of the parallel computing capabilities on multi-core and manycore hosts. The main idea of PDES is to execute a simulation program on a parallel computer by decomposing the simulation application into a set of concurrently executing processes [33]. In the past few decades, PDES has attracted tremendous attention and interest and grown fast. In [39] SystemC-clang is proposed. It analyzes SystemC models with a mixture of transaction-level and register-transfer level components. The authors in [42] studied the distributed parallel simulation, where SystemC models are organized into small executable units and distributed onto different host machines to run in parallel. A parallel SystemC simulation kernel is proposed in [43] which requires the user to manually translate the sequential design into a safe parallel design. [44] takes a survey about existing SystemC simulation approaches and concludes that most of these works do not fully support the parallel simulation of TLM-2.0 LT models due to shared variables. [45] proposes a tool that addresses this problem. A set of primitives is provided to the user to manually express tasks with duration such that parallelism in the model can be exploited and LT models are executing in parallel. In [46], a parallel SystemC simulation kernel is developed by reducing synchronization overheads of parallel threads. [47] proposes an efficient multi-threaded memory allocator named HMalloc which eliminates false sharing and lock contention and supports lock-free shared memory allocation and deallocation. [48] identifies the available parallelism between event scheduling and execution, highlights points of contention between the two, provides an algorithm to take advantage of the parallelism. [49] exploits hardware profiling facilities to build a hardwaresupported incremental check-pointing solution that enables the reduction of the event-execution cost in speculative PDES compared to the software-based counterpart. [50] proposes a system for predicting future situations through parallel simulations based on observation data. An optimistic simulation engine is introduced to support parallel simulation of many possible situations and dynamic simulation modification based on observation data acquired by sensors. [51] presents an approach that exploits reinforcement learning techniques for speculative Time Warp-based PDES. Rather than assuming an optimal control strategy, the authors seek to find the optimal strategy through parameter exploration. A value function that captures the history of system feedback is used, and no a-priori knowledge of the system is required. [52] presents a runtime support for speculative parallel processing of discrete event simulation models on multi-core architectures. It exploits Hardware-Transactional-Memory (HTM) facilities for the purpose of state recoverability, which can hence host conventionally developed discrete event models relying on the concept of event-handlers to be dispatched by an underlying simulation engine. [53] optimizes PDES by implementing a thread-based version of the ROSS simulator. The multi-threaded implementation eliminates multiple message copying and significantly minimizes synchronization delays. [54] presents a PDES scheme that enables cost- and time-efficient execution of large scale parameter studies on GPUs. Two orthogonal levels of parallelism are exploited: external parallelism among the inherently independent simulations of a parameter study and internal parallelism among independent events within each individual simulation of a parameter study.

In comparison with the above approaches for PDES, the work we propose in this dissertation is based on a specific PDES approach: OoO PDES. To achieve accurate results, Out-of-Order PDES relies on a static analysis approach to collect the context information of each simulation thread. Note that SystemC models are written in C++ code, and C++ based static analysis has been widely studied. [55] proposes three algorithms for statically analyzing virtual functions in C++ to reduce compiled code size and program complexity. [56] introduces a tool called ITS4 for scanning vulnerability in C and C++ programs based on static analysis. [57] presents the Parallel Pattern Analyzer Tool which aids the discovery and annotation of parallel patterns in source codes. It

supports for identifying Map, Farm, and Pipeline parallel patterns and evaluate the quality of the detection for a set of different C++ applications. SystemC-specific static analysis has also been studied.

OoO PDES has been studied for years. In [34], OoO PDES is first introduced to increase the simulation speed over the synchronous PDES. [58] proposes a dynamic load-profiling and segment-aware scheduling algorithm with optimized thread dispatching to maximize parallel SystemC simulation speed, which generally can be applied to all work-sharing PDES approaches for better multi-core scheduling. [59] defines the concept of core distance for many-core architectures and proposes an approach to optimize thread-to-core mapping in order to minimize on-chip communication overhead. In [60], the authors achieve a high simulation speed of SystemC models by exploiting data-level parallelization together with thread-level parallelization. An algorithm was proposed to automatically apply data-level parallelization to the source code. This is orthogonal to the focus of this dissertation and thus could be applied here as well. Port Call Path [40] is an advanced technique that helps the compiler to gain more specific context information about non-pointer variables in channels. This can reduce false positive conflicts in channels and result in significantly increased simulation speed. [61] integrates OoO PDES library into the Simics virtual platform.

## 1.4 Goals

As outlined in Section 1.2, RISC provides a tool chain for highly parallel simulation of SystemC models. However, there are several noticeable restrictions that limit the use of RISC in large designs. In this section, we briefly introduce these limitations, and then set corresponding goals to overcome them. In other words, we scale the OoO PDES approach beyond academic examples to real-world industrial design models.

In industrial designs, a SystemC model often comes as separate files and involves heavy use

of third-party libraries and Intellectual Properties (IP). The reuse-based design methodology is actively applied to achieve high design productivity to meet the demand for shorter design cycles and relax the time-to-market pressure. However, RISC compiler needs the complete source code of a SystemC model to build AST for further static analysis. Complete source codes from the IP providers can hardly be obtained because IPs are carefully protected. This limits the use of RISC in SystemC models using third-party libraries and Intellectual Properties (IP).

Another limitation is that current static analysis does not support the modern SystemC TLM-2.0 standard. SystemC TLM-2.0 standard is widely used in industrial SystemC models. It exploits the benefits of both temporal decoupling and traditional TLM standard for higher simulation speed. In SystemC TLM-2.0, communication between SystemC processes is done by passing transactions, where each transaction consists of a generic payload object, a timing object and a transaction phase (for non-blocking transportation). The SystemC TLM ports and channels no longer exist in SystemC TLM-2.0, instead, an initiator passes the reference of a transaction to a target by calling a registered callback method on the target side. RISC compiler was not able to handle communications outside channels and cannot analyze references and pointers, therefore, SystemC TLM-2.0 models were not able to be statically analyzed by RISC compiler, which was a large limitation.

In this dissertation, we are going to scale the RISC compiler and simulator so that industrial SystemC designs can be simulated correctly and fast. Specifically, our goals include:

- 1. **Static analysis for 3<sup>rd</sup> party libraries and IPs**: For those SystemC models that use third-party libraries and IPs, we aim to enable OoO PDES to effectively perform static analysis to build Segment Graphs and analyze conflicts.

- 2. **Static analysis for SystemC TLM-2.0 standard**: For those SystemC models that use SystemC TLM-2.0 standard, we would like to allow our RISC compiler to efficiently recognize the communication between modules and statically analyze the conflicts.

- 3. **Improving simulation speed of OoO PDES**: We aim to further increase simulation speed of OoO PDES by direct and indirect optimizations in the simulator.

In the following chapters, we present our approaches to achieve our goals. Chapter 2 realizes the first goal. Chapter 3 realizes the second goal. The third goal is addressed in Chapter 4 and 5 respectively. Figure 1.9 summarizes our contributions with respect to the tool flow of RISC.

Figure 1.9: Contributions in RISC tool flow

The rest of the dissertation is organized as follows:

In Chapter 2, we extend the static analysis design flow to support separate files and IP reuse by introducing Partial Segment Graph (PSG) abstraction [62]. We also propose approaches to prevent IP security leakage by using PSG. Experiments demonstrate the effective design flow and sustained speedup with parallel simulation.

In Chapter 3, we propose a compile time approach to statically analyze potential conflicts among threads in SystemC TLM-2.0 loosely- and approximately-timed models [63]. We introduce a new Socket Call Path (SCP) technique which provides the compiler with socket binding information for precise static analysis. We also propose an algorithm to analyze entangled variable pairs. Experimental results show that our approach is able to support automatically safe parallel simulation of SystemC models with TLM-2.0 Blocking Transport Interface, Direct Memory Interface and Nonblocking Transport Interface, resulting in impressive simulation speeds.

In Chapter 4, we propose for RISC users coding guidelines that increase the granularity of segments [64], so that the level of parallelism in the design increases and higher simulation speed becomes possible. The experimental results show the simulation speed of OoO PDES increases significantly by applying the coding guidelines.

In Chapter 5, we introduce a novel event delivery strategy that allows waiting threads to resume execution earlier based on predicted behaviors of all threads, resulting in significantly increased simulation speed [65]. Experimental results show that the proposed approach increases the OoO PDES simulation speed by a large amount.

Finally, Chapter 6 summarizes this dissertation with an outline of contributions. Future works are also discussed.

# Chapter 2

# **Extending Static Analysis for Large Models**

In this chapter, we first propose an algorithm that builds Partial Segment Graph for each individual SystemC translation unit, we then propose an algorithm that combines all PSGs to reconstruct the complete Segment Graph [62]. Based on the two algorithms, the RISC compiler is able to support SystemC models with multiple source file inputs, especially for the models that use Intellectual Properties.

### 2.1 Introduction

As described in Chapter 1, the complexity of system design has been growing with the increasing functionalities of modern embedded systems. Out-of-Order Parallel Discrete Event Simulation (OoO PDES) [34] was proposed to exploit the parallel computation of modern multi- and many-core platforms, and the Recoding Infrastructure for SystemC (RISC) [35] has been developed to implement OoO PDES for SystemC. The RISC compiler first builds the Abstract Syntax Tree (AST) of the input file and then derives from the AST the *behavior model (BM)* of the input SystemC design. BM is an abstraction of the execution of the SystemC processes in the design. The RISC

compiler represents BM with a statically built Segment Graph (SG) data structure. Based on SG, the RISC compiler is able to analyze the data conflicts, timing conflicts and event hazards in the design.

### 2.2 Problem Definition

To completely build the BM of the input SystemC design, the RISC compiler needs the entire AST for the input model. Thus the user has to provide all the source code in one single translation unit. In other words, the RISC compiler cannot build BM for SystemC designs whose source code are separately structured in multiple source files or third party Intellectual Properties (IP). With the wide use of IP, this requirement severely restricts the RISC compiler to meet industrial system level design needs.

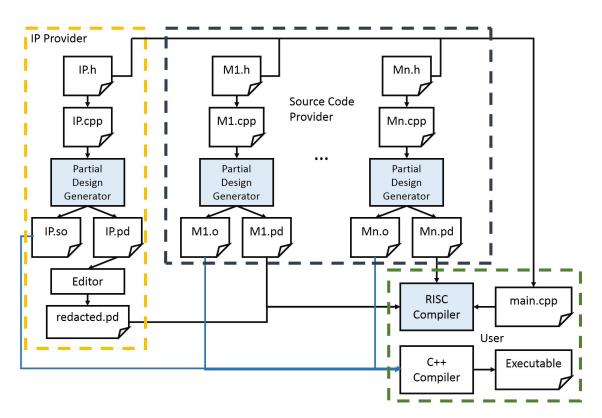

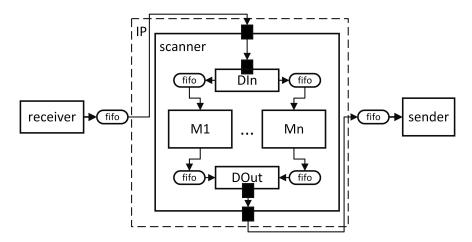

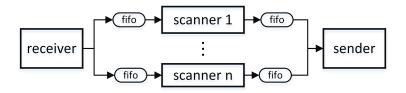

Figure 2.1: Scaled RISC tool flow with IP components

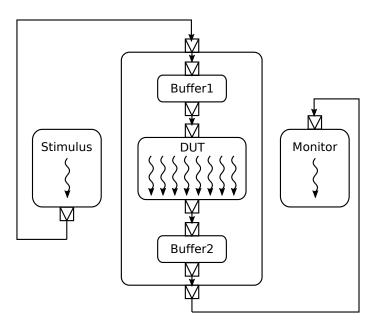

In this chapter [62], we propose a solution that scales the RISC compiler to support multiple file inputs, especially for the integration of IPs, as shown in Figure 2.1. In the new design flow, the construction of BM no longer relies on the complete AST. Besides the usual object and header files, component providers supply a *partial design (PD)* file that abstracts the BM of integrated design components. Specifically, in the PD file, the BM is abstracted by a *Partial Segment Graph (PSG)*. IP providers can inspect and redact the PD file, in order to further minimize the PSG, which protects the security of their IP. On the user's side, by combining all the received PSGs, the RISC compiler is able to reconstruct the BM of the whole design.

### 2.3 Related Work

IP reuse and protection have received a lot of attentions. In [66], the authors describe an effective methodology for IP reuse in SOC design. They studied the IP enhancement and also proposed a framework for the reuse of customer IP. [67] proposes a new preprocessing approach that embeds watermarks as constraints into the input of a black-box design tool and a new postprocessing approach that embeds watermarks as constraints into the output of a black-box design tool. [68] introduces a new technique for protecting the IP of both processor cores and application software in hardware/software systems. The approach is based on public-key cryptography and it has been implemented as a package in the JavaCAD distributed design and simulation environment.

In [69], the authors proposed a way to use pre-defined graphs to represent the BM of IP components. However, this simple approach requires the users to manually analyze the design and insert pragmas where needed. Furthermore, there are only three kinds of predefined graphs, which is insufficient. In contrast, we propose PSG as the data structure to represent the BM of IP components, which is accurate and is automatically built by a compiler.

### 2.4 Partial Segment Graph

We now describe the PSG technique that represents the BM in each separate translation unit.

### 2.4.1 Behavior Model and Segment Graph

The behavior model of a SystemC design can be described by the Segment Graph, which provides a way to analyze threads and their position during execution. The SG is a directed graph where each node is a sequence of code statements executed between two scheduling steps, i.e., wait statements [34]. Details about SG are described in Section 1.2.1

### 2.4.2 Concept of PSG

In our proposed design flow, we store the BM specified in each translation unit as a PSG in a PD file and when the PSGs are loaded and integrated together, they reconstruct the complete SG.

The main difference between PSG and SG is that PSG is built based on an incomplete AST, where

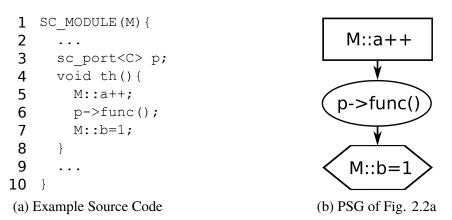

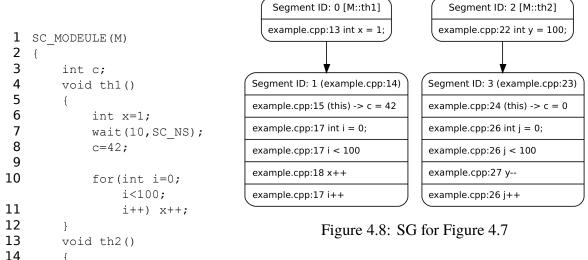

Figure 2.2: SystemC Code and PSG

definitions of function calls may be unknown. An example is shown in Figure 2.2a. It contains only the definition and implementation of module M. Function p->func() is called in M::th(),

but it is not defined in this translation unit. We refer to a function call that lacks the definition as a *non-defining function call*. Because the compiler cannot determine from the current AST if a non-defining function call contains scheduling steps or not, the simulation cycle of the code statements following the non-defining function call cannot be statically determined. In the example, we cannot know if line 5 and line 7 execute in the same cycle.

To deal with this uncertainty incurred by the non-defining function calls, we introduce three types of PSG nodes:

- Segment node contains a sequence of code statements executed in the same determined simulation cycle. In Figure 2.2a, M::a++ belongs to a segment node because its simulation cycle is determined, which is the first cycle of the sc\_thread M::th(). A segment node becomes a segment after the integration of PSGs.

- Partial segment node contains a sequence of code statements executed in the same non-determined simulation cycle. In Figure 2.2a, M::b=1 belongs to a partial segment node because it is executed after the non-defining function call p->func(). Later during the PSG integration phase, the partial segment node will be merged with other segment nodes.

- Partial function call node is created as a place holder for the non-defining function call in the PSG such that during the PSG integration phase, the partial function call node can be replaced by the sub-PSG corresponding to the function's definition. In Figure 2.2a, node 3 is a partial function call node for the non-defining function call p->func().

#### 2.4.3 Create PSG

A PSG is recursively built by traversing the AST of the current translation unit, as shown in Algorithm 1. If the current statement CurrStmt is a scheduling entry point (wait statement), then an empty segment node is created and connected to the nodes in the CurrNodes. On the

other hand, if CurrStmt is not a scheduling point, then it is added to all the nodes in CurrNodes. This is similar as in the *BuildSG* in [69]. The main difference is that to build PSG, the compiler also needs to deal with non-defining function calls. If CurrStmt contains a non-defining function call, for example f(), the compiler first builds a partial function call node NewNode and stores the qualified name M::f(). Next, the compiler connects NewNode to all the nodes in CurrNodes. Then, a partial segment node NextNode is created and connected to NewNode, and the compiler sets NextNode as the only node in the CurrNodes.

#### Algorithm 1 Partial Segment Graph Generation

```

1: function BuildPSG(CurrStmt, CurrNodes)

if isBoundary(CurrStmt) then

3:

NewNode ← new segmentNode

4:

for Node ∈ CurrNodes do

5:

AddEdge(Node, NewNode)

6:

end for

7:

return CurrNodes ∪ { NewNode }

8:

else if isNonDefiningFunctionCallStmt(CurrStmt) then

NewNode ← new partialFuntionCallNode

9:

10:

Mark(NewNode, getFuncName(CurrStmt))

for Node ∈ CurrNodes do

11:

12:

AddEdge(Node, NewNode)

13:

end for

14:

NextNode \leftarrow new partialSegmentNode

15:

AddEdge(NewNode, NextNode)

else if isControlFlow(CurrStmt) then

16:

BuildSG(CurrStmt, CurrNodes)

17:

18:

19:

end if

20: end function

```

#### 2.4.4 Store and Load PSG

The PD file stores an abstraction of the PSG. For each node, we omit the detailed code statements and store only the access types (R,W,RW) to non-local variables. This is sufficient for the RISC compiler to analyze the data and event conflicts. In addition, some meta-data is stored for each node, which is needed for the integration of PSGs, as listed in Table 2.1. Note that the PD file is compatible with dot format and the PSG therefore can easily be visualized. An example of PSG is

later shown in Figure 2.7.

A PSG is loaded from the PD file with a dot file parser. The parser reads the attributes of each PSG node, and reconstructs the data in memory. For example, a node has a variable access attribute (W)M::a, which indicates that M::a is been written in the node. To load the node into memory, the PSG parser locates the symbol of M::a in the AST and puts it into the *variable\_write\_list* of the node. PSG edges are constructed according to the connections specified in the PD file. After the loading of individual PSGs, the compiler integrates them together to construct the complete SG.

Table 2.1: PSG meta-data node attributes

| Attribute                  | Description                             |  |

|----------------------------|-----------------------------------------|--|

| Node type                  | Segment node, Non-segment node,         |  |

| rode type                  | Function call node                      |  |

| Written variables          | Qualified name of variables written     |  |

| Read variables             | Qualified name of variables read        |  |

| Notified events            | Qualified name of events notified       |  |

| Dependent events           | Qualified name of events waiting for    |  |

| Hosting function name      | Qualified name of function belonging to |  |

| Hosting module name        | Qualified name of module belonging to   |  |

| Is entry node              | Marker for function entry point         |  |

| Is exit node               | Marker for function exit point          |  |

| Is simulation process      | Marker for simulation process           |  |

| Non-defining function name | Qualified name of non-defining function |  |

### 2.4.5 Integration Phase

A complete segment graph is the basis for accurate static analysis. After loading all the PSGs, first the partial function call nodes are recursively replaced with the corresponding sub-PSG. Second, all the partial segment nodes are merged with segment nodes they follow. All remaining nodes in the graph are segment nodes (with underlying wait boundaries) and belong to determined simulation

cycles, such that the integrated graph by definition becomes a proper segment graph. With the reconstructed SG, the RISC compiler has the complete the BM and can perform the needed static analysis of the design.

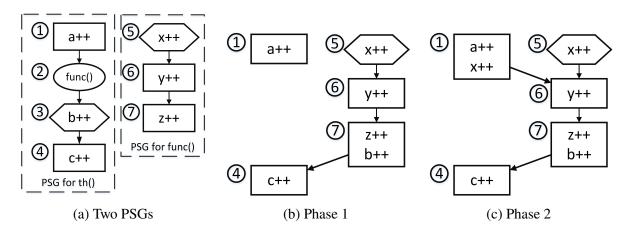

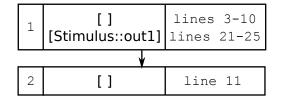

We illustrate the merging process of two PSGs in Figure 2.3a, 2.3b and 2.3c. In this example, *node\_2* is a partial function call node that holds the non-defining function call func(), and *node\_5*, *node\_6* and *node\_7* are loaded from the psg in func.pd and forms the sub-PSG of func(). *node\_5* and *node\_7* are respectively the entry and exit node of func(). First, *node\_3* is merged into *node\_7* because they belong to the same simulation cycle. After merging, *node\_4* is connected to *node\_7* since it was connected to *node\_3*. Then, *node\_5* is merged into *node\_1* because it is the starting node of func(). *node\_6* is connected to *node\_1* since it was connected to *node\_5*.

Figure 2.3: Integration of PSGs

### 2.5 IP Protection and Security

IP reuse is an important feature in semiconductor industry. Basically, an IP consists of two parts: a header file that describes the interfaces and protocols, and a binary file that implements the IP component. Since no implementation source code is provided, the IP is protected. The internal BM of the IP is hidden from the users.

However, static analysis cannot be performed without the BM. We need the IP provider to supply an abstract PSG of the IP to the user via PD files. For the IP provider not to reveal too much implementation detail and to solve this IP security leakage problem, we allow the IP provider to redact the PSG in the PD file, so that the implementation details remain hidden. If desired, misleading information can even be added. This way the users will not be able to obtain the inner implementation, while still maintaining the correctness of BM.

Figure 2.4: SystemC model of Bitcoin miner

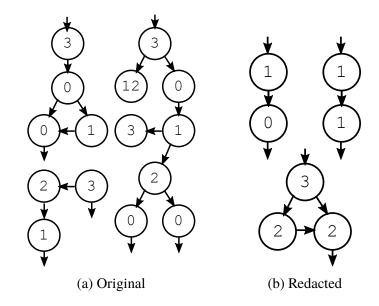

Figure 2.5: Original and redacted scanner.pd

Figure 2.4 shows the SystemC model of a Bitcoim miner [70]. It has several user defined modules

(receiver and sender) for data input and output, and uses an IP module (scanner) for number crunching. Three PD files (*receiver.pd*, *sender.pd*, *scanner.pd*) contain the corresponding BM of each module.

By default, in each PD file the RISC compiler stores (1) the qualified name of variables accessed and access types, (2) qualified name of events and dependencies, (3) PSG structure and timing advance. For *receiver.pd* and *sender.pd*, it is fine to have such information transparent because the two modules are user-defined. However, for *scanner.pd*, exposing the internals is risky from the perspective of IP protection.

The original and redacted versions of scanner.pd are shown in Figure 2.5. Here the numbers in the PSG nodes indicate the number of variable accesses stored. Compared to the original, the revised file has fewer nodes, and each node has fewer variable accesses stored. These modifications are carefully performed such that during the simulation, the model still executes correctly.

There are several possible changes that can be performed to redact the PSG:

- Reduce the amount of variable accesses: If two nodes share more than one internal variable

accesses, only one of them needs to be kept and others can be removed from the two nodes.

This does not change the data conflict of the two segments. Only externally visible variables

need to be retained. Furthermore, if a variable is read only in any node, it can be removed

because it cannot lead to data conflicts.