# **UC San Diego**

# **Technical Reports**

#### **Title**

**Predicting Performance Across Compilations**

#### **Permalink**

https://escholarship.org/uc/item/7j213325

#### **Author**

Lau, Jeremy

#### **Publication Date**

2007-06-16

Peer reviewed

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Predicting Performance Across Compilations

# A dissertation submitted in partial satisfaction of the requirements for the $$\operatorname{degree}$$

Doctor of Philosophy

in

Computer Science

by

Jeremy Lau

# Committee in charge:

Brad Calder, Chair Matthew Arnold Pamela Cosman Ranjit Jhala Chandra Krintz Geoff Voelker

Jeremy Lau, 2007

All rights reserved.

| The dissertation of Jeremy Lau is approved, and it is ac-  |

|------------------------------------------------------------|

| ceptable in quality and form for publication on microfilm: |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

| Chair                                                      |

University of California, San Diego

2007

# DEDICATION

For Mom

#### **EPIGRAPH**

The protean nature of the computer is such that it can act like a machine or like a language to be shaped and exploited. It is a medium that can dynamically simulate the details of any other medium, including media that cannot exist physically. It is not a tool, although it can act like many tools. It is the first metamedium, and as such it has degrees of freedom for representation and expression never before encountered and as yet barely investigated. Even more important, it is fun, and therefore intrinsically worth doing.

Alan Kay

# TABLE OF CONTENTS

|    | Signature Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iii                                          |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|    | Dedication Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | iv                                           |

|    | Epigraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V                                            |

|    | Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | vi                                           |

|    | List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | viii                                         |

|    | List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xi                                           |

|    | Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | xii                                          |

|    | Vita and Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xvi                                          |

|    | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xviii                                        |

| I  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1<br>2<br>3<br>4<br>7                        |

| II | Cross Binary Architectural Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10<br>13<br>13<br>17<br>21<br>23             |

|    | B. Capturing Program Behavior with Fixed and Variable Length Intervals  1. Issues with Fixed Length Intervals  2. Hierarchical Program Behavior  C. Software Phase Markers  1. Capturing Hierarchical Behavior with Call-Loop Graphs  2. Selecting Software Phase Markers  3. Support For Variable Length Intervals in SimPoint  4. Methodology  1. Methodology | 24<br>25<br>28<br>34<br>34<br>38<br>45<br>47 |

|     | <ul> <li>6. Applications: Data Cache Reconfiguration and SimPoint</li> <li>D. Cross Binary Simulation Points</li> <li>1. Selecting Cross Binary Simulation Points</li></ul> | 56<br>65<br>65       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | 2. Methodology                                                                                                                                                              | 73                   |

|     | 3. Cross Binary SimPoint Evaluation                                                                                                                                         | 74                   |

|     | E. Related Work                                                                                                                                                             | 83                   |

|     | F. Summary                                                                                                                                                                  | 85                   |

| III | Performance Audited Dynamic Optimization                                                                                                                                    | 87<br>91<br>91<br>92 |

|     | -1/                                                                                                                                                                         | 94                   |

|     | 1                                                                                                                                                                           |                      |

|     | 4. Building a Mapping Between Binaries                                                                                                                                      | 99                   |

|     | B. Performance Auditing                                                                                                                                                     | 102                  |

|     | 1. Motivating Empirical Search                                                                                                                                              | 103                  |

|     | <ol> <li>Performance Auditor Design</li> <li>Methodology</li> </ol>                                                                                                         | 106                  |

|     | 00                                                                                                                                                                          |                      |

|     | <ol> <li>Offline Convergence Study</li> <li>Online Performance Auditing</li> </ol>                                                                                          |                      |

|     | C. Lightweight Code Markers                                                                                                                                                 |                      |

|     | 1. Inserting Lightweight Code Markers                                                                                                                                       |                      |

|     | 2. Application to Performance Auditing                                                                                                                                      |                      |

|     | 3. Methodology                                                                                                                                                              |                      |

|     | 4. Evaluation: Perf. Auditing with Lightweight Code Markers                                                                                                                 |                      |

|     | 5. Other Potential Uses for Lightweight Code Markers                                                                                                                        |                      |

|     | D. Discussion                                                                                                                                                               |                      |

|     | E. Summary                                                                                                                                                                  |                      |

|     | 2. Summer                                                                                                                                                                   | 100                  |

| IV  | Conclusion and Future Challenges                                                                                                                                            | 160<br>161<br>161    |

|     | 2. Performance Audited Dynamic Optimization                                                                                                                                 | 165                  |

|     | C. Future Challenges                                                                                                                                                        | 166                  |

|     | 1. Cross Binary Architectural Simulation                                                                                                                                    | 167                  |

|     | 2. Performance Audited Dynamic Optimization                                                                                                                                 | 168                  |

|     | Ribliography                                                                                                                                                                | 171                  |

# LIST OF FIGURES

| Figure II.1  | Time varying graph for bzip2-graphic (first 64 billion     |    |

|--------------|------------------------------------------------------------|----|

|              | instructions)                                              | 14 |

| Figure II.2  | Time varying graph for gcc-integrate                       | 15 |

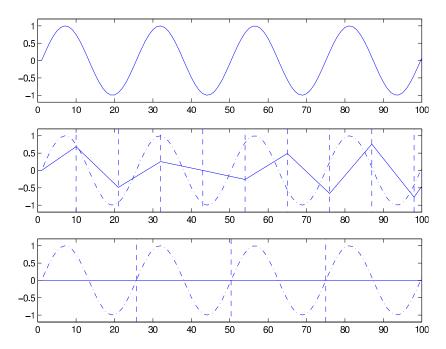

| Figure II.3  | An example of what happens to a signal (top figure)        |    |

|              | when it is sampled with different interval lengths         | 26 |

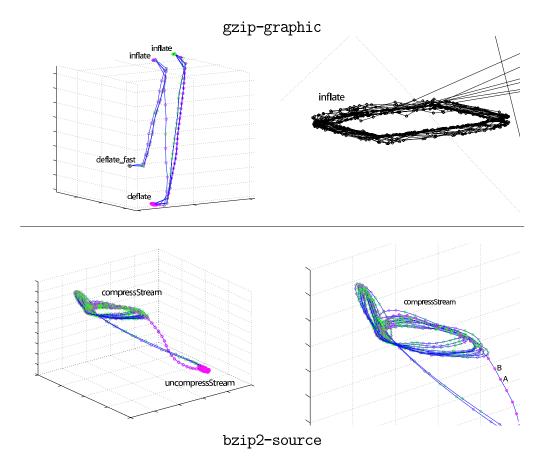

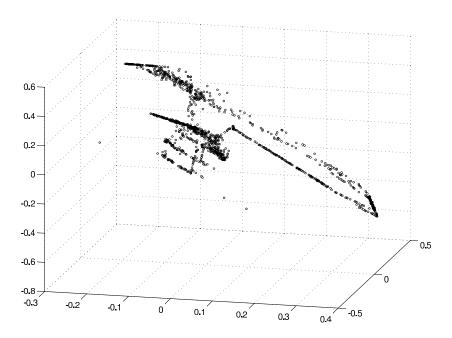

| Figure II.4  | Three dimensional non-accumulated representation of        |    |

| _            | gzip-graphic and bzip2-source                              | 29 |

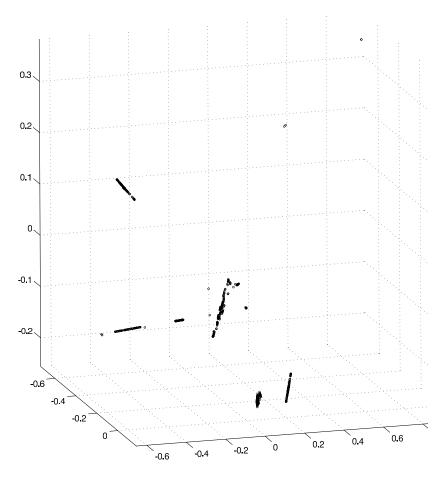

| Figure II.5  | Two dimensional accumulated representation of bzip2-       |    |

| J            | source                                                     | 30 |

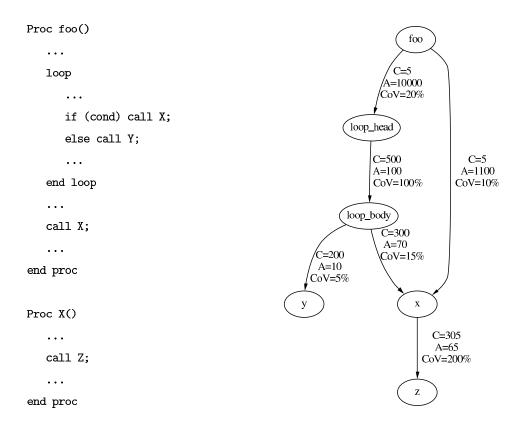

| Figure II.6  | Code example and Call-Loop graph for code example .        | 37 |

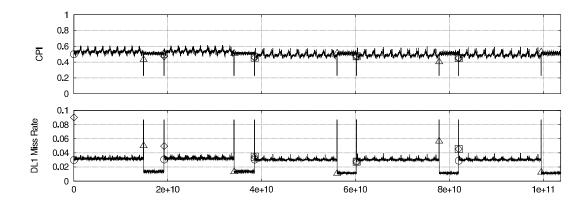

| Figure II.7  | Time varying graphs with phase markers for gzip-graphic    |    |

| J            | for an OSF Alpha executable                                | 48 |

| Figure II.8  | Cross-binary time varying graphs with phase markers        |    |

| O            | for gzip-graphic for Linux x86                             | 48 |

| Figure II.9  | Bzip2 fixed length execution intervals representation      | 50 |

| Figure II.10 | Bzip2 variable length execution intervals representation   |    |

| 0            | with phase markers                                         | 51 |

| Figure II.11 | Average instructions per interval                          | 54 |

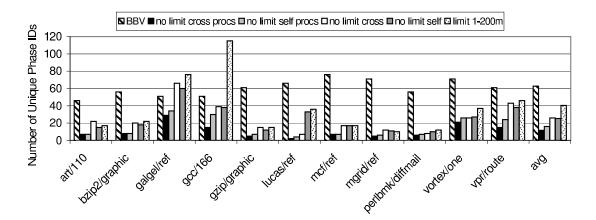

| Figure II.12 | Number of phases detected                                  | 54 |

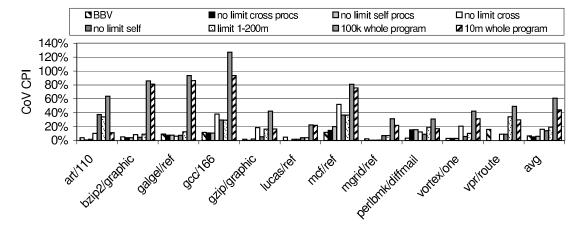

| Figure II.13 | Coefficient of variation of CPI. The "Whole Program"       |    |

| 0            | results show each program's variability if every interval  |    |

|              | is classified into a unique phase                          | 55 |

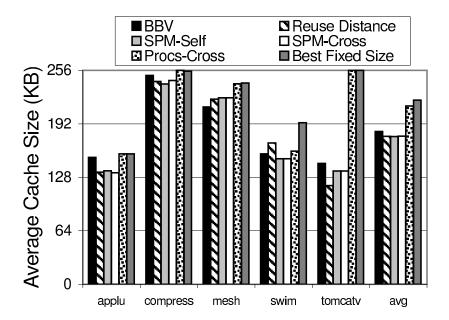

| Figure II.14 | Average cache size with no allowed increase in cache       |    |

| 0            | miss rate                                                  | 58 |

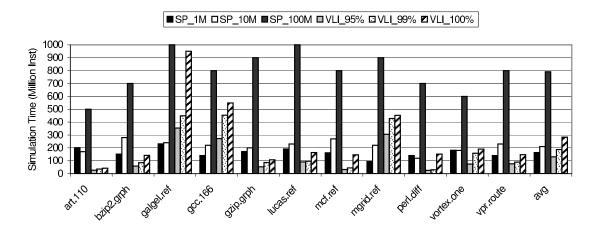

| Figure II.15 | Number of instructions simulated with SimPoint and         |    |

| 0            | phase markers                                              | 62 |

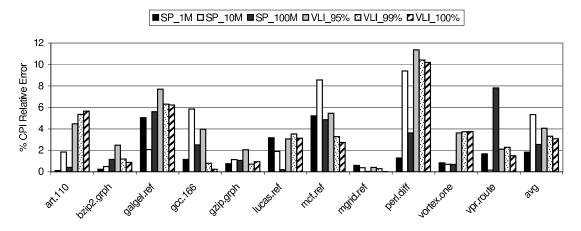

| Figure II.16 | Error in CPI estimates with fixed length intervals and     |    |

| 0            | variable length intervals from phase markers               | 62 |

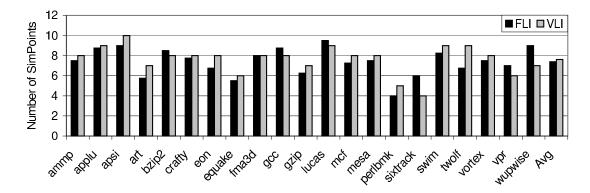

| Figure II.17 | Number of SimPoints for per-binary SimPoint (FLI)          |    |

| O            | and cross binary SimPoint (VLI). Each bar shows the        |    |

|              | average across all four binaries                           | 75 |

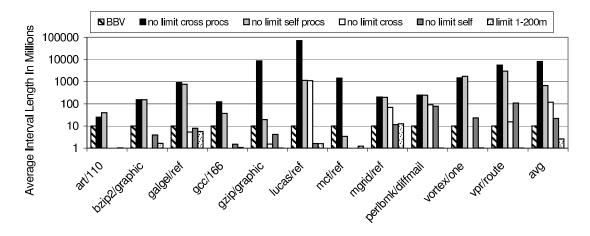

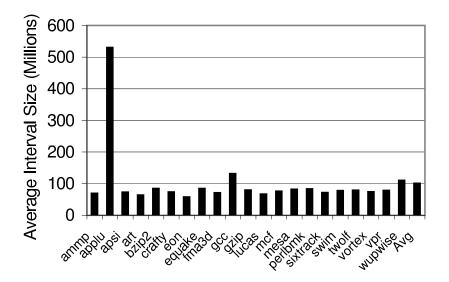

| Figure II.18 | Interval Size for cross binary SimPoint (VLI). Each bar    |    |

| O            | shows the average across all four binaries. The size of    |    |

|              | each interval in per-binary SimPoint, which uses fixed     |    |

|              | length intervals, is constant at 100 million instructions. | 75 |

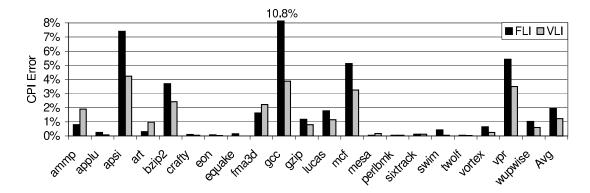

| Figure II.19 | CPI Error for per-binary SimPoint (FLI) and cross bi-      |    |

|              | nary SimPoint (VLI). Each bar shows the average across     |    |

|              | all four binaries                                          | 77 |

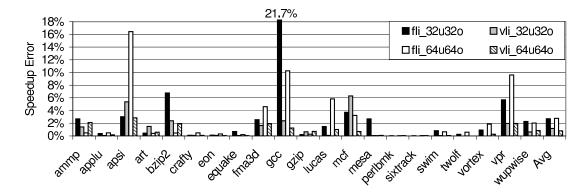

| Figure II.20  | Speedup error for per-binary SimPoint (fli) and cross binary SimPoint (vli)                                                                                                                                                |

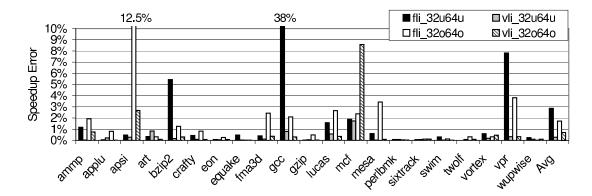

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure II.21  | Speedup error for per-binary SimPoint (fli) and cross binary SimPoint (vli). Speedup is computed across pairs                                                                                                              |

|               | of binaries on the <i>different</i> platforms (32-bit vs. 64-bit). 79                                                                                                                                                      |

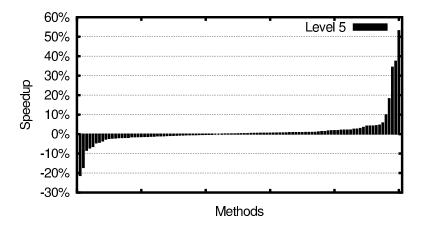

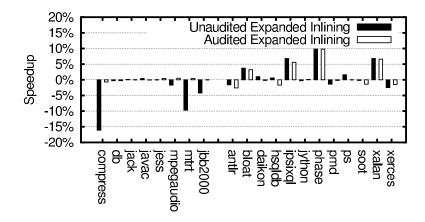

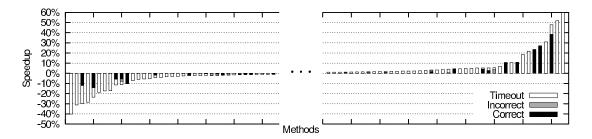

| Figure III.1  | Per-method performance impact of moving from optimization level 4 to level 5                                                                                                                                               |

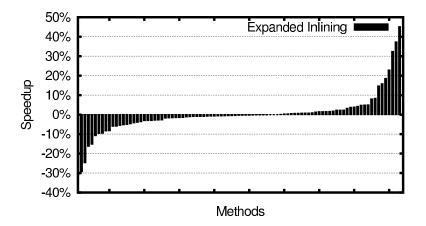

| Figure III.2  | Per-method performance impact of expanded inlining heuristic                                                                                                                                                               |

| Figure III.3  | Performance Auditor Overview 107                                                                                                                                                                                           |

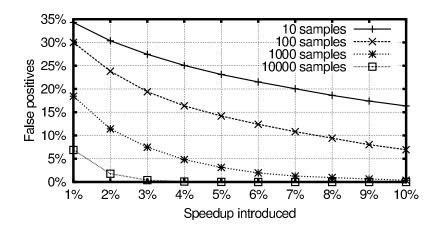

| Figure III.4  | Misprediction rate for a simple sampling approach in which a fixed number of method invocation (entry+exit) timings are collected, for various amounts of introduced                                                       |

|               | speedup                                                                                                                                                                                                                    |

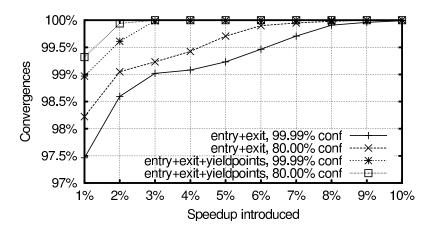

| Figure III.5  | Convergence rate for the proposed statistical approach.  This plot shows the percentage of hot methods for which                                                                                                           |

|               | confident predictions are generated, with a sampling limit of 2 minutes of CPU time for each method 116                                                                                                                    |

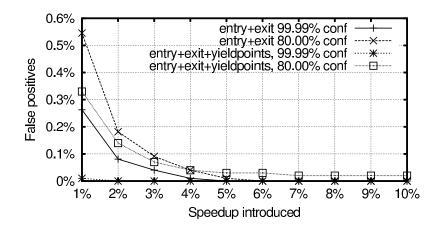

| Figure III.6  | limit of 2 minutes of CPU time for each method 116 Incorrect predictions. This plot shows the percentage of hot methods in which the analysis incorrectly predicts that $A$ is faster than $B$ . Results are averaged over |

|               | converged methods                                                                                                                                                                                                          |

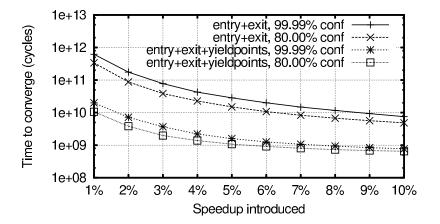

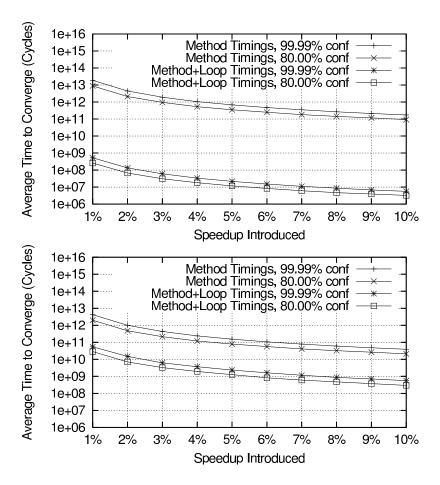

| Figure III.7  | Time to converge                                                                                                                                                                                                           |

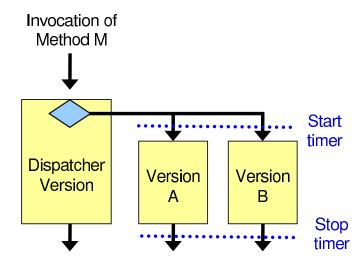

| Figure III.8  | Architecture for the <i>dispatcher</i> , to select method invo-                                                                                                                                                            |

| i igare iii.o | cations for timing                                                                                                                                                                                                         |

| Figure III.9  | Dispatch logic                                                                                                                                                                                                             |

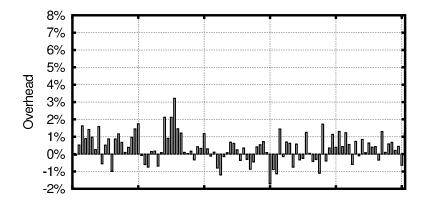

| Figure III.10 | Per-method overhead of the dispatcher fast-path. No                                                                                                                                                                        |

|               | timing samples are being taken                                                                                                                                                                                             |

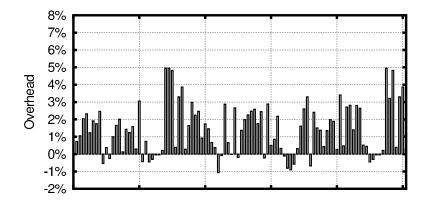

| Figure III.11 | Per-method overhead of the Performance Auditor when sampling 1 of 20 executions. Overhead includes record-                                                                                                                 |

|               | ing and processing the timing samples 125                                                                                                                                                                                  |

| Figure III.12 | Performance of the online system using the proposed                                                                                                                                                                        |

| T1 10         | statistical technique to guide inlining heuristic selection. 126                                                                                                                                                           |

| Figure III.13 | Accuracy of the online system using the proposed sta-                                                                                                                                                                      |

| Eigene III 14 | tistical technique to guide inlining heuristic selection 127                                                                                                                                                               |

| Figure III.14 | Speedup/slowdown observed when a marker is inserted                                                                                                                                                                        |

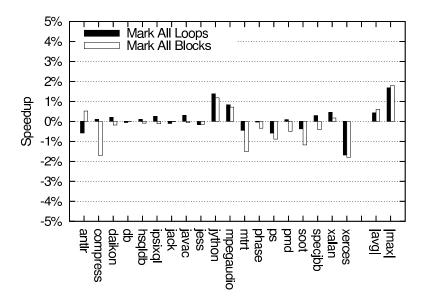

| Dicure III 15 | and removed in every loop or every block in every method. 135                                                                                                                                                              |

| Figure III.15 | Loop Selection Algorithm 137                                                                                                                                                                                               |

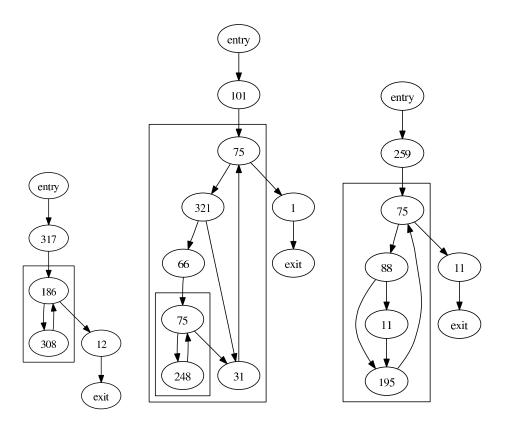

| Figure III.16 | Three CFGs selected for loop instrumentation, where      |

|---------------|----------------------------------------------------------|

|               | the loop selection algorithm was unable to find a satis- |

|               | factory timing point                                     |

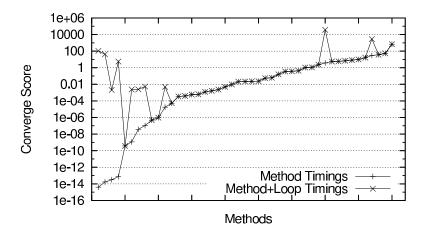

| Figure III.17 | Converge scores for hot methods, higher is better 147    |

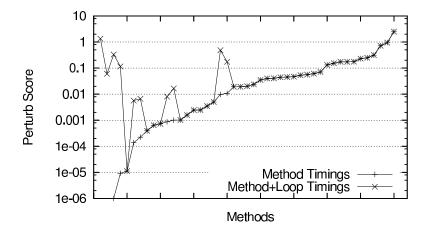

| Figure III.18 | Perturb scores for hot methods, lower is better 148      |

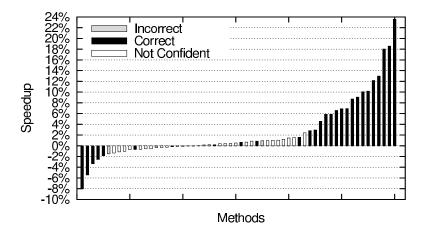

| Figure III.19 | Accuracy of our approach, where markers are inserted     |

|               | before optimization, and markers are replaced with full  |

|               | timing instrumentation after optimization 150            |

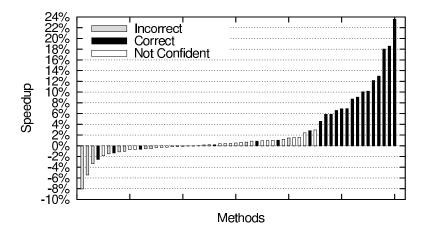

| Figure III.20 | Accuracy of the naïve approach, where full timing in-    |

|               | strumentation is inserted before optimization 151        |

| Figure III.21 | Convergence time, comparing method+loop timings to       |

|               | method timings. Top figure: convergence time for hot     |

|               | methods selected for loop instrumentation. Bottom fig-   |

|               | ure: convergence time for all hot methods 152            |

# LIST OF TABLES

| Table II.1  | Baseline Simulation Model                             | 46  |

|-------------|-------------------------------------------------------|-----|

| Table II.2  | Memory System Configuration                           | 72  |

| Table II.3  | Phase comparison across 32-bit unoptimized and 64-bit |     |

|             | unoptimized gcc binary versions                       | 81  |

| Table II.4  | Phase comparison across 32-bit optimized and 64-bit   |     |

|             | optimized apsi binary versions                        | 81  |

| Table III.1 | Benchmark suite                                       | 111 |

| Table III.2 | Benchmark suite                                       |     |

#### ACKNOWLEDGMENTS

This dissertation would not have been possible without my advisor, Professor Brad Calder. Over the last six years, he has not only taught me how to do research, but also taught me much about life. Thank you.

I must thank all my labmates in the Architecture Lab over the years. Thanks to Tim for being a second advisor, John for reminding me what it's all about, Jamison for keeping it brutal, Rakesh for the always insightful conversations, Jeff for being my partner in system administration, Satish for making everything look easy, Erez for the adventures, Stef for the moo-can, and Ganesh for all the rides to Black Mountain Road.

I must also thank my friends for putting up with too many of my work related disappearances over the last six years. Thanks to Louis for always finding time to hang out, Ethan for being down for whatever, James for dreaming, Lance, Ron, and Alex for a whole lot of bowling, and Lynne for listening.

My brother must be thanked for reminding me that there is much more to life than research.

Finally, and most importantly, my mother must be thanked for always believing in me, for always watching out for my best interests, for periodically verifying that I'm still alive, for reminding me that I am Chinese, for not letting me leave home without entirely too much food, for knowing how to grow, cook, fix, and/or clean anything imaginable... This list goes on for quite a while. For all these reasons and more, this dissertation is for you.

Cross binary simulation points, presented in section II.D, were developed in collaboration with Erez Perelman and Brad Calder at the University of California San Diego, Greg Hamerly at Baylor University, Tim Sherwood at the University of California Santa Barbara, and Harish Patil and Aamer Jaleel at Intel. I thank my co-authors for allowing me to present the results of our

collaboration in my dissertation.

The performance auditor presented in section III.B was the result of collaboration with Matthew Arnold and Michael Hind at IBM T.J. Watson, and Brad Calder at the University of California San Diego. I thank my co-authors for allowing me to present the results of our collaboration in my dissertation.

Section II.B contains material that appears in "Motivation for Variable Length Intervals and Hierarchical Phase Behavior", in *International Symposium on Performance Analysis of Systems and Software (ISPASS)*, Jeremy Lau, Erez Perelman, Greg Hamerly, Timothy Sherwood, Brad Calder. The dissertation author was the primary investigator and author of this paper. Portions of Section II.B are ©2005 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

Section II.C contains material that appears in "Selecting Software Phase Markers with Code Structure Analysis", in *International Symposium on Code Generation and Optimization (CGO)*, Jeremy Lau, Erez Perelman, Brad Calder. The dissertation author was the primary investigator and author of this paper. Portions of Section II.C are Copyright ©2006 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from

Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

Section II.D contains material that appears in "Cross Binary Simulation Points", in *International Symposium on Performance Analysis of Systems and Software (ISPASS)*, Erez Perelman, Jeremy Lau, Harish Patil, Aamer Jaleel, Greg Hamerly, Brad Calder. The dissertation author was the secondary investigator and author of this paper. Portions of Section II.D are ©2007 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

Section III.B contains material that appears in "Online Performance Auditing: Using Hot Optimizations Without Getting Burned", in Conference on Programming Language Design and Implementation (PLDI), Jeremy Lau, Matthew Arnold, Michael Hind, Brad Calder. The dissertation author was the primary investigator and author of this paper. Portions of Section III.B are Copyright ©2006 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

Section III.C contains material in "A Loop Correlation Technique to Improve Performance Auditing", submitted to Conference on Parallel Architectures and Compilation Techniques (PACT), Jeremy Lau, Matthew Arnold, Michael

Hind, Brad Calder. The dissertation author was the primary investigator and author of this paper.

#### VITA

| 2001 | Bachelor of Arts in Computer Science<br>University of California, Berkeley      |

|------|---------------------------------------------------------------------------------|

| 2003 | Internship<br>Microsoft Research, Redmond                                       |

| 2005 | Internship<br>IBM T.J. Watson Research Center, Hawthorne                        |

| 2007 | Doctor of Philosophy in Computer Science<br>University of California, San Diego |

#### **PUBLICATIONS**

"Cross Binary Simulation Points" Erez Perelman, Jeremy Lau, Harish Patil, Aamer Jaleel, Greg Hamerly, Brad Calder. *International Symposium on Performance Analysis of Systems and Software (ISPASS)*, April 2007, San Jose, CA, USA

"Online Performance Auditing: Using Hot Optimizations Without Getting Burned" Jeremy Lau, Matthew Arnold, Michael Hind, Brad Calder. Conference on Programming Language Design and Implementation (PLDI), June 2006, Ottawa, Canada

"Using Machine Learning to Guide Architecture Simulation" Greg Hamerly, Erez Perelman, Jeremy Lau, Timothy Sherwood, Brad Calder. *Journal of Machine Learning Research (JMLR)*, Volume 7, Pages 343-378, 2006

"Selecting Software Phase Markers with Code Structure Analysis" Jeremy Lau, Erez Perelman, Brad Calder. *International Symposium on Code Generation and Optimization (CGO)*, March 2006, New York, NY, USA

"Dynamic Phase Analysis for Cycle-Close Trace Generation" Cristiano Pereira, Jeremy Lau, Brad Calder, Rajesh Gupta. *International Conference on Hardware/Software Codesign and System Synthesis (CODES)*, September 2005, New York, NY, USA

"SimPoint 3.0: Faster and More Flexible Program Analysis" Greg Hamerly, Erez Perelman, Jeremy Lau, Brad Calder. Workshop on Modeling, Benchmarking and Simulation (MOBS), June 2005, Madison, WI, USA

"The Strong Correlation between Code Signatures and Performance" Jeremy Lau, Jack Sampson, Erez Perelman, Greg Hamerly, Brad Calder. *International Symposium on Performance Analysis of Systems and Software (ISPASS)*, March 2005, Austin, TX, USA

"Motivation for Variable Length Intervals and Hierarchical Phase Behavior" Jeremy Lau, Erez Perelman, Greg Hamerly, Timothy Sherwood, Brad Calder. *International Symposium on Performance Analysis of Systems and Software (ISPASS)*, March 2005, Austin, TX, USA

"Transition Phase Classification and Prediction" Jeremy Lau, Stefan Schoenmackers, Brad Calder. *International Symposium on High-Performance Computer Architecture (HPCA)*, February 2005, San Francisco, CA, USA

"Structures for Phase Classification" Jeremy Lau, Stefan Schoenmackers, Brad Calder. *International Symposium on Performance Analysis of Systems and Software (ISPASS)*, March 2004, Austin, TX, USA

"Reducing Code Size With Echo Instructions" Jeremy Lau, Stefan Schoenmackers, Timothy Sherwood, Brad Calder. *International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES)*, October 2003, San Jose, CA, USA

"Ninja: A Framework for Network Services" Eric Brewer, Nikita Borisov, Mike Chen, Rob von Behren, Matt Welsh, David Culler, Josh MacDonald, Jeremy Lau, Steven D. Gribble. *Usenix Technical Conference (USENIX)*, June 2002, Monterey, CA, USA

#### ABSTRACT OF THE DISSERTATION

Predicting Performance Across Compilations

bv

Jeremy Lau

Doctor of Philosophy in Computer Science

University of California, San Diego, 2007

Professor Brad Calder, Chair

Performance comparisons are ubiquitous in computer science. The proceedings of most conferences are filled with bar charts comparing the performance of some computer system to another. For example, computer architects compare the performance of processors, and compiler writers compare the performance of generated code. It is difficult to prove that one computer system is always faster than another for all possible workloads, so these performance comparisons are used as predictors: performance is compared on several representative workloads, and the results are used to argue that one computer system is generally faster than another. Unfortunately, there are many scenarios where it is difficult to make a fair performance comparison. This dissertation focuses on two such scenarios.

The first scenario involves simulations in computer architecture. Computer architects typically evaluate new processor designs through slow cycle-level simulation. Because of the poor performance of cycle-level simulators, accelerated simulation methodologies are very popular, where small samples of a program's behavior are simulated, and the results are extrapolated to predict the results of a whole-program simulation. But with these accelerated simulation techniques,

it is difficult to meaningfully compare performance estimates when multiple compilations of a program are involved. This dissertation will show that simulation samples must be selected consistently across compilations to produce comparable results, and a technique will be presented to apply accelerated simulation across compilations to produce comparable results.

The second scenario involves dynamic optimization systems. Dynamic optimizers must predict if their optimizations will actually improve performance before applying them — if an optimization is unlikely to improve performance, or if an optimization will degrade performance, the optimization should not be applied. This dissertation presents a new approach to guide dynamic optimization decisions by performing empirical performance evaluations as programs execute. The performance of differently-compiled versions of the same code are measured, and the results of the measurements directly guide optimization decisions. The challenge is that these performance measurements are collected as programs execute, so individual measurements are not directly comparable, because the program may run the code under analysis with different inputs over time. If a single pair of performance measurements indicates that one version of the code is faster than another, it may actually be faster, or it may be that the program chose to run one version on a smaller input than the other. To overcome this challenge, this dissertation presents a statistical technique to analyze pools of timing data to determine which version is the fastest.

# Ι

# Introduction

Historically, the complexity of the average desktop computer has increased drastically, and the trend continues toward more complex systems. Hardware complexity continues to grow as more transistors become available for each chip, and software complexity continues to grow as more layers of software are introduced with the increasing popularity of application frameworks, dynamic compilation, and virtualization. These trends make it more and more difficult for computer scientists to predict the performance of their systems.

Performance prediction is a simple idea that is used extensively throughout computer science: performance measurements are collected on a small representative workload to predict the overall performance of a computer system in the general case. As a simple example, if it is known that a particular loop runs for 10,000 iterations, the overall running time of the loop can be predicted by measuring the loop's running time for 1,000 iterations, and multiplying the result by 10. As another example, computer architects measure the performance of processors as they run the SPEC2000 benchmark suite to predict how processors will perform in everyday use.

This dissertation focuses on one specific type of performance prediction problem: predicting performance across compilations.

#### I.A Predicting Performance Across Compilations

It is more difficult to make performance predictions when multiple binary representations of the same program are being compared. Suppose a program is run through two different compilers, producing two binaries  $B_1$  and  $B_2$ . It is then reasonable to ask: which binary,  $B_1$  or  $B_2$ , will run faster, on average? It is also reasonable to answer this question by evaluating small samples of  $B_1$ 's and  $B_2$ 's performance. This is a scenario where performance must be predicted across compilations.

When predicting performance across compilations, the primary challenge is to collect measurements of  $B_1$ 's and  $B_2$ 's performance that can be meaningfully compared. To make the example more concrete, suppose  $B_1$  and  $B_2$  are compiled versions of a scientific program that first reads a large dataset into memory, then analyzes the dataset. The first half of execution is spent reading the dataset from disk, and the second half of execution is spent running the analysis. The goal is to evaluate the performance of  $B_1$  and  $B_2$  by collecting small samples of  $B_1$ 's and  $B_2$ 's performance. But the samples must be selected consistently — a sample taken from  $B_1$ 's analysis phase should be compared to a sample taken from  $B_2$ 's analysis phase. It does not make sense to compare a sample taken from  $B_1$ 's loading phase to a sample taken from  $B_2$ 's analysis phase.

The problem of selecting samples consistently across binaries is surprisingly difficult. It seemed simple in the preceding example, but that is because the example provided a high level description of the program's behavior. Binaries do not contain such descriptions. Without this type of high level information, a technique is needed to select samples in each binary so that high level program behaviors are comparably represented. This dissertation will present several techniques to collect samples consistently across binaries in order to draw meaningful conclusions about the overall performance of the binaries.

#### I.B Problem Areas

This dissertation focuses on two instances of the problem of predicting performance across compilations: one in the area of accelerated architectural simulation and another in the area of dynamic optimization.

Computer architects evaluate new processor designs through cycle-level simulation, where a simulator program models all the low-level effects of every instruction on a new processor design. But cycle-level simulation is extremely slow, due to the complexity of modern processors — simulator programs can easily execute thousands of instructions on a host processor just to simulate a single instruction on the simulated processor. Because of the poor performance of cycle-level simulators, accelerated simulation methodologies are very popular, where small samples of a program's behavior are simulated, and the results are extrapolated to predict the results of a whole-program simulation. These accelerated simulation techniques make cycle-level simulation feasible for real-world programs, but it is difficult to compare the results of these accelerated simulation techniques when multiple binaries of a program are involved. For example, if extensions to the instruction set are considered as part of the architectural design space exploration, multiple binary representations of the same benchmark program must be considered — one binary that uses the proposed instructions, and another binary that does not use the proposed instructions. This dissertation will show that the samples of program behavior selected for detailed simulation must be selected consistently across binaries to produce comparable results, and this dissertation will present a technique to apply an accelerated simulation technique across compilations so results are comparable.

Dynamic optimization systems improve the performance of programs as they execute by recompiling portions of programs with additional optimizations. A dynamic optimizer must predict if its optimizations will actually improve

performance before applying them — if an optimization is unlikely to improve performance, or if an optimization is likely to degrade performance, the optimization should not be applied. These optimization decisions are typically guided by heuristics. For example, an optimizer may decide to inline a procedure if the procedure contains less than N instructions. But as the complexity of computer systems increases, these types of heuristics become less reliable. This dissertation presents an alternative approach to guide dynamic optimization decisions by performing empirical performance evaluations as programs execute. The performance of differently-compiled versions of the same code is measured, and the results of the performance measurements are used to directly guide optimization decisions. The challenge is that the performance measurements are collected as programs execute, so individual measurements are not directly comparable, because the program may run the code under analysis with different inputs over time. If a single pair of measurements indicates that version X of the code is faster than version Y, it may be because version X is indeed faster than version Y, or it may be because the program happened to invoke version X on a smaller input than version Y. To overcome this challenge, this dissertation presents a statistical technique to analyze pools of timing data to determine which version is the fastest.

#### I.B.1 Cross Binary Architectural Simulation

To design the best processor for an application, processor designers must find the best design point in a huge design space. Intuition and common sense are used to pare down the design space, but at some point it becomes too difficult to think about all the performance implications of minor design changes. At this point, cycle-level simulators are typically used to measure the performance of benchmark programs on a set of potential processor designs. Unfortunately, cycle-level simulators are extremely slow due to the incredible complexity of modern processors. The primary goal of a cycle-level simulator is to determine how many cycles will be needed to execute a program on a candidate processor design. This means that a cycle-level simulator must model the low-level effects of every instruction on all aspects of the architecture, including branch predictors, caches, bus traffic, speculative execution, and out-of-order execution.

Modeling at this level of detail carries a significant performance cost — slowdowns on the order of 1,000 to 10,000 times are common. Simulation speed is a major concern in architecture research, because more design space explorations can be performed with faster simulators. To improve the speed of architectural simulations, a number of accelerated architectural simulation methodologies have been proposed. Several popular approaches rely on sampled simulation, where the performance of the processor on several small samples of the program is measured through cycle-level simulation, and the results are extrapolated to estimate the program's overall performance.

Accelerated simulation techniques such as SimPoint [78] work well when the goal is to estimate a single program's overall performance from small samples of the program's behavior, because the existing techniques are specifically designed for this purpose. But such techniques do not always work well when multiple binary representations of the same program are involved.

There are three main scenarios where multiple binaries must be used in architecture simulation. The first scenario involves instruction set extensions, where a new binary is created that uses new instructions, such as the 64-bit x86 extensions (x86-64). In this case, the performance of the original binary, which does not use the extensions, must be compared to the performance of the new binary, which does use the extensions. The second scenario deals with

examining completely different architectures, such as Itanium and x86-64. In this case, completely different compilers will be used. Finally, the third scenario involves developing compilers for new architectures. In this scenario, the compiler writers must evaluate the performance effects of their compiler optimizations through simulation, because working prototypes of a new processor are typically not available until very late in the development cycle. In this scenario, the new compiler may use the same instruction set as an existing compiler, but different binaries will be produced as optimizations are enabled, disabled, reordered, and adjusted.

When multiple binary versions of a program are used with an accelerated architectural simulation methodology, this dissertation will show that existing techniques do not work well, and this dissertation will show that samples of program behavior selected for cycle-level simulation must be selected consistently across the different binaries to produce comparable results. This dissertation will also present a technique to apply an accelerated simulation technique across compilations so that samples of program behavior are selected consistently across binaries, to produce comparable accelerated simulation results.

In the area of accelerated architectural simulation, the primary contributions of this dissertation are:

- A technique to identify software phase markers, which are code locations that indicate the beginning of a major change in program behavior when executed. Phase markers are associated with source code, and are thus portable across compilations.

- A technique to identify cross-binary simulation points, which allow the results of accelerated architectural simulation to be meaningfully compared across binaries. Cross-binary simulation points use phase markers to indicate where cycle-level simulation is required, so cycle-level simulation can

be run on semantically equivalent regions in all binaries, which allows for meaningful comparisons of sampled simulation results across binaries.

#### I.B.2 Dynamic Optimization with Performance Auditing

Dynamic optimization systems attempt to improve the performance of programs as they execute through recompilation. A dynamic optimizer must predict if its optimizations will actually improve performance before applying them — if an optimization is unlikely to improve performance, or if an optimization will degrade performance, the optimization should not be applied. But it becomes increasingly difficult to accurately predict if an optimization will actually improve performance as the complexity of software systems increases. As a simple example, when should an optimizer inline a procedure? Inlining should be done when it will improve performance, but it becomes increasingly difficult to predict if a particular inlining decision will actually improve performance as additional software layers such as application frameworks, Java virtual machines and hypervisors are introduced between a program and its processor. Optimizers typically rely on heuristics to predict if an optimization will improve performance. For example, an optimizer may inline a procedure if the procedure contains less than N instructions. But as software complexity increases, these types of heuristics become less reliable. This dissertation suggests an alternative approach called performance auditing where dynamic optimizations are guided by empirical performance measurements. With performance auditing, the performance of differently-compiled versions of the same code is measured, and the results of the performance measurements are used to directly guide optimization decisions.

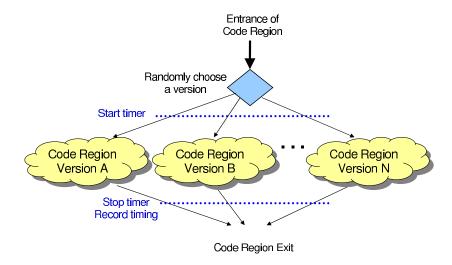

In the proposed performance auditing system, when a piece of code is selected for performance auditing, several differently-compiled versions of the code are generated. The program is allowed to run normally, but whenever the audited code region is entered, one of the compiled versions will be randomly selected and invoked. The system records the amount of time the program spent executing code in that compiled version of the code.

The main challenge in the proposed system is to meaningfully compare performance measurements that have been collected in this manner to make an accurate performance prediction. The goal is to answer the question: Which compiled version of the audited code runs the fastest in general? Answering this question is difficult because it is typically impossible to obtain single pieces of timing data for each of the differently-compiled versions of the code that are directly comparable, because timing data is collected continuously as the program executes. To overcome this challenge, this dissertation presents a statistical technique to analyze pools of timing data to determine which version is the fastest, or if there is not enough statistical evidence to make a confident decision. If statistical confidence is low, more timing data is collected, and the statistical analysis will run again later.

This challenge is very similar to the main challenge in building an accelerated architectural simulation system that produces comparable results across multiple compilations, which was discussed in the previous section. In both cases, the key challenge is to collect comparable performance samples from a set of binaries, such that the performance samples can be meaningfully compared, in order to accurately predict which binary runs the fastest.

In the area of performance auditing, the primary contributions of this dissertation are:

- A technique to empirically compare the effectiveness of optimizations online, despite changing program state.

- A description and evaluation of a prototype performance auditing system

built in IBM's J9 Java virtual machine.

- Lightweight code markers, which map between a program's source and its optimized binary without using heuristic matching, and without modifying the optimizer.

- A technique to improve statistical confidence in the proposed performance auditing system by using lightweight code markers to consistently split large timing samples into many small timing samples across compilations.

# TT

# Cross Binary Architectural Simulation

Modern computer architecture research requires understanding the cycle level behavior of a processor as it executes a program. To gain this understanding, researchers typically employ detailed simulators that model the processor's cycle-level behavior. Unfortunately, this level of detail comes at the cost of speed. Even with the fastest simulators, modeling the full execution of a single benchmark at the level required for computer architecture research can take weeks or months, and nearly all industry standard benchmarks require simulating the execution of a *suite* of programs. Therefore, instead of simulating entire programs, a few small samples of each program's execution are typically sampled instead. In this chapter, these samples are on the scale of 10 to 500 million instructions.

With sampled simulation, the primary challenge is to determine which simulation samples most accurately represent the program's full execution. To address this problem we created a tool called SimPoint [70, 78] that uses clustering algorithms from machine learning to automatically find repetitive patterns in a program's execution. By simulating one representative of each repetitive behavior

pattern, simulation time can be reduced to minutes instead of weeks for standard benchmark programs, with very little loss in accuracy. Several researchers have shown the SimPoint approach works well when exploring architecture designs with a *single* compiled binary version of a program [55, 70, 78, 95], but this dissertation focuses on the problem of using SimPoint with *multiple* compiled binary versions of a program.

There are three main scenarios where multiple binaries must be used in architecture simulation. The first scenario involves instruction set extensions, where a new binary is created that uses new instructions, such as the 64-bit x86 extensions (x86-64). In this case, the performance of the original binary, which does not use the extensions, must be compared to the performance of the new binary, which does use the extensions. The second scenario deals with examining completely different architectures, such as Itanium and x86-64. In this case, completely different compilers will be used. Finally, the third scenario involves developing compilers for new architectures. In this scenario, the compiler writers must evaluate the performance effects of their compiler optimizations through simulation, because working prototypes of a new processor are typically not available until very late in the development cycle. In this scenario, the new compiler may use the same instruction set as an existing compiler, but different binaries will be produced as optimizations are enabled, disabled, reordered, and adjusted.

In all three of these scenarios, semantically equivalent simulation samples must be identified in all binaries, or the simulation results can not be meaningfully compared.

This chapter presents two solutions to the problem of accelerated simulation with multiple binaries. The first approach applies the baseline SimPoint approach separately for each binary. SimPoint examines an execution trace and groups similar portions of execution into phases (clusters). The most representative interval from each phase is chosen as the simulation point to represent that cluster. SimPoint produces very accurate results when a single binary is used across different architectures, because the same code regions are simulated on each architecture, so the simulated code regions are semantically equivalent by definition.

But when SimPoint is applied to multiple binary representations of the same program, SimPoint can produce different clusterings for each binary. This means that the simulation points selected by SimPoint in each binary may actually represent different behaviors. And even if the simulation points do represent the same behaviors, the results still may not be comparable, because semantically equivalent portions of execution in one binary may be assigned to different phases in different binaries. So even if semantically equivalent simulation points are selected across binaries, those simulation points may represent different behaviors in different binaries. Results in Section II.D.3 show that these concerns are real.

To address these concerns, this chapter presents a technique called *cross binary SimPoint*. This approach identifies simulation points that are semantically equivalent across multiple binaries. The approach works by first profiling each binary and identifying a set of software phase markers in each binary that can be identified in all other binaries. These mappable simulation points are instructions in each binary corresponding to procedure calls or loop branches that can be consistently identified in all binaries. These mappable markers are potential boundaries for simulation regions. Program execution is split into intervals on these mappable markers for one of the binaries, and basic block vectors are collected. The basic block vectors are run through SimPoint, which selects a set of simulation points which are now mappable across all binaries. Then, detailed simulation can be performed on these mapped simulation points to compare per-

formance across binaries.

The outline of this chapter is as follows. First section II.A presents background and related work in the area of accelerated architectural simulation techniques. Section II.B demonstrates some issues with standard techniques for identifying repetitive program behaviors for the purposes of accelerated architectural simulation. These issues motivate the need for software phase markers, presented in section II.C. Software phase markers identify repetitive program behaviors based on high-level code structure, such as procedure calls and loop backedges, that mark the start of each repetitive behavior. A program's software phase markers are tightly coupled with the program's code structure, which makes them effective for applications such as dynamic hardware reconfiguration, but also makes them less effective when directly applied to accelerated architectural simulation. Cross binary simulation points, presented in section II.D, loosen this coupling between a program's phase markers and the program's simulation points by selecting specific dynamic instances of phase markers to identify the start and end of each simulation point. With cross binary simulation points, sampled simulation results can be meaningfully compared across multiple binaries. Section II.E presents work that is closely related to cross binary simulation points.

# II.A Background

This section presents background and related work in the area of accelerated architectural simulation techniques.

#### II.A.1 Time Varying Behavior and Phases

Before discussing accelerated architectural simulation techniques, a brief aside is necessary to discuss the time varying behavior of programs and phase

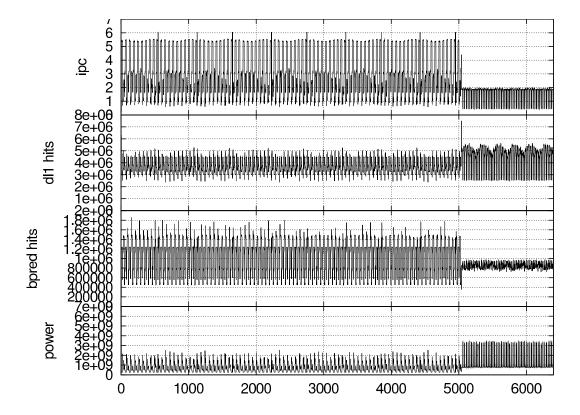

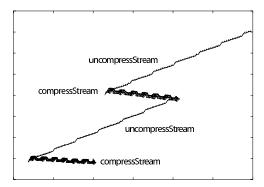

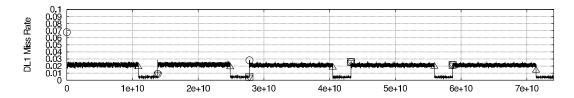

Figure II.1: Time varying graph for bzip2-graphic (first 64 billion instructions). Time is plotted on each X-axis, in tens of millions of instructions. Each data point on the Y-axes shows the average IPC, level 1 data cache hits, correct branch predictions, and power for each ten-million instruction interval.

behavior, which make accelerated simulation possible.

A program's behavior at any instant in time can differ drastically from the program's average overall behavior. Furthermore, programs exhibit phase behavior — their behavior will be stable for long periods of time, before moving on to another behavior pattern.

These statements about the time-varying behavior of programs may seen counterintuitive at first, but consider a block-based compression program as an example. The compression program will perform the same steps to compress each block of data. For example, the deflate compression algorithm used in gzip

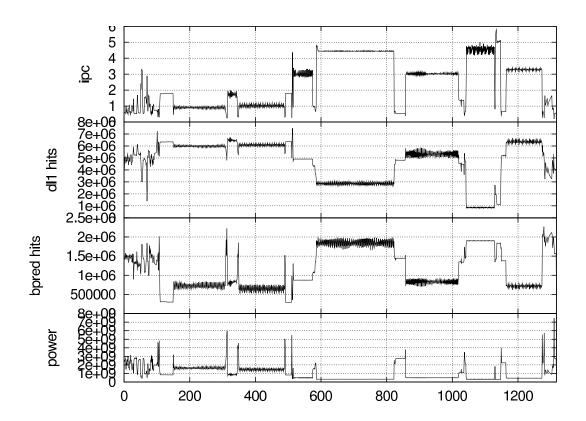

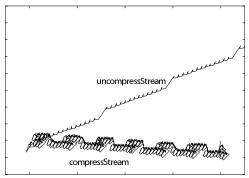

Figure II.2: Time varying graph for gcc-integrate.

first slides a window over the data to replace redundancies with backpointers, then applies Huffman coding to further compress the data. Different code will be executed in each of these steps, and the processor should behave differently in each of these steps. These two steps are performed for each block of data, and most inputs are split into many blocks of data, so these two steps should be performed over and over again to compress an input. These expectations lead to cyclic behavior patterns, which are common in compression programs.

Another example of phase behavior in programs are the stages of compilation. The different stages will exercise the machine in very different ways, because the algorithms change from stage to stage. For example, the algorithms used in lexing are usually very different from the algorithms used in register allocation. The compiler will do different work in each of its major stages, and it will spend a significant amount of time in each major stage, and similar work should be done within each stage. These expectations lead to phase behavior.

In general, the execution of most integer programs can be broken down into a series of major processing stages, like the stages of a compiler as discussed above. Most floating point benchmarks consist of one major "computation stage," like the compression example discussed above, but floating point benchmarks also exhibit strong phase behavior because they often spend most of their time in nested loops, which leads to cyclic behavior patterns.

Figure II.1 shows a graph of the time-varying behavior of bzip2. To produce this graph, bzip2's execution was partitioned into intervals of 10 million instructions, and the value of each metric listed on the Y-axes (IPC, data cache hits, correct branch predictions, power) was collected for each 10 million instruction interval. Time is plotted on the X-axes, in tens of millions of instructions. This means that each data point on the graph shows the *instantaneous* behavior of bzip2, where an "instant" is 10 million instructions long.

Only the first half of bzip2's execution is shown to make the graph more legible. The second half of bzip2's execution is very similar to the first half. Inspection of this figure reveals that this benchmark exhibits phase behavior on two levels: there is one high-level behavior pattern from 0-5000 on the X-axis, and another from 5000-6400. Within each of these high level phase patterns, there are lower-level phase patterns, which are most easily seen on the power graph. Each high-level phase exhibits a highly repetitive low-level phase pattern, yet the low-level phase patterns are completely different across the high-level phases.

Figure II.2 shows a time-varying graph of gcc's behavior. This figure poses more of a challenge to phase analysis. In this figure, two levels of phase behavior can also be seen. For example, gcc's behavior is mostly homogeneous between 150 and 300 on the X-axis. But upon closer examination, there are small periodic variations in behavior within each high-level phase. This time-varying graph shows that gcc is a difficult benchmark for phase analysis, because the small behavior variations within each high-level phase are not as regular as the low-level patterns exhibited by bzip2, and each high level phase is seen only once.

This section showed that even complex integer benchmarks from SPEC2000 such as bzip2 and gcc exhibit phase behavior: as they execute, they spend large amounts of time (millions to billions of instructions) exhibiting homogeneous behavior before quickly switching to another type of behavior.

#### II.A.2 Phase Analysis

Before phase behavior can be exploited for accelerated architectural simulations, phases must first be detected. The easiest way to detect phase behavior is to employ knowledge about the program to be run. For example, in an MPEG decoder, program behavior should be fairly homogeneous while decoding each MPEG frame type. Program behavior while decoding any I-frame should

be fairly similar, but behavior while decoding a P-frame should be very different. This subsection explores general techniques that do not rely on this type of program-specific knowledge.

First, some terminology:

- Interval An interval is a continuous slice of program execution. A program's execution is partitioned into intervals, so intervals may not overlap. The length of intervals is commonly referred to as the "granularity" of the intervals.

- Similarity A similarity metric is used to measure the similarity of program behaviors in two intervals of program execution. Similarity metrics depend on how program behavior for each behavior is represented, which will be discussed in the following subsection.

- *Phase* A phase is a collection of intervals with similar behavior. Typically, programs are partitioned into a large number of intervals, and those intervals are grouped into a small number of phases.

- *Phase Analysis* To detect phases in program behavior, a program's intervals must be classified into phases, typically using machine learning clustering techniques. This is called phase analysis.

Phases are identified by first partitioning a program's execution into intervals, then clustering the intervals into phases. A program's execution is partitioned into intervals, so intervals never overlap. Intervals can be fixed-length or variable-length. When a program's execution is partitioned into intervals, the main issue is setting an interval length. Fixed-length intervals are usually defined in terms of the number of instructions executed by the program in each interval—for example, a program may be partitioned into fixed-length intervals of 100 million instructions. This means that each fixed-length interval represents the

execution of 100 million instructions. The length of intervals is also referred to as the "granularity" — large intervals are "coarse" and small intervals are "fine." Hind et al. [37] provide a framework for defining and reasoning about program phase classifications, focusing on how to best define granularity and similarity for phase analysis.

After a program's execution has been partitioned into intervals, the intervals are clustered into phases. This process will be described in detail in the following subsections.

Phase behavior has been exploited to accelerate architectural simulations [77, 78], to save energy by dynamically reconfiguring caches and processor width [9, 79, 26, 25], to guide compiler optimizations [63, 10], to guide remote profiling [66], and to choose which core to run a process on in a multi-core architecture [54].

#### Basic Block Vectors

Phase analysis requires a signature of the program's behavior for each interval. This dissertation presents several techniques that rely on code-based signatures [55, 56], specifically, basic block vectors.

Basic Block Vectors (BBVs) [77] capture information about changes in a program's behavior over time. A basic block is a single-entry, single-exit section of code with no internal control flow. A *Basic Block Vector* (BBV) is a one dimensional array where each element in the array corresponds to each basic block in the program. Basic block vectors are essentially another way of looking at block profiles.

To collect a basic block vector, the profiler starts with an empty BBV (zero vector) at the beginning of each interval of execution. Throughout each interval, the profiler counts the number of times each basic block in the program

has been executed, and records the count in the BBV. For example, if the 50th basic block is executed 15 times in the current interval, then the profiler will set bbv[50] = 15. The profiler multiplies each count by the number of instructions in the basic block, so basic blocks containing more instructions will have more weight in the BBV.

Basic block vectors are used to evaluate the similarity of the intervals they were collected from [77, 78]. The intuition is that the behavior of a program in an interval is directly related to the code executed in that interval. Basic block vectors are fingerprints for each interval of execution, because each vector indicates what portions of code are executed, and how frequently those portions of code are executed: if the distance between the BBVs is small, then the two intervals spend about the same amount of time in roughly the same code, and therefore the overall behavior of the program in those two intervals should be similar.

There are many ways to collect a signature of program behavior from an interval of execution other than basic block vectors. Denning and Schwartz [23] were one of the first to analyze time-varying program behavior, by showing that patterns in program behavior can be detected by monitoring a program's data working set over time. Similarly, Dhodapkar and Smith [25, 26, 24] found relationships between patterns in program behavior and code working sets. Balasubramonian et al. [9] used hardware counters to collect miss rates, CPI and branch frequency information for every 100,000 instructions executed, and used the statistics to identify stable portions of program execution. Isci and Martonosi [45, 46] found that patterns in program behavior can be detected by monitoring the power consumption of architectural components. In [56], we examined several alternatives to basic block vectors, including several forms of code signature vectors where each dimension corresponds to procedure calls, procedure returns, or loop

branches instead of basic blocks. We found that many types of code signatures can be used effectively for phase analysis.

#### II.A.3 Accelerating Architectural Simulations with SimPoint

Architectural simulation is incredibly slow. Modern simulators can simulate around 400,000 instructions per hour, but typical benchmarks contain billions or even trillions of instructions [78]. The poor performance of architectural simulators makes it infeasible to perform detailed simulation for a full benchmark run. Additionally, processor designers are most interested in a processor's performance on a *suite* of benchmarks, rather than single benchmarks. This makes accelerated simulation methodologies even more important.

SimPoint [78] is a popular tool that uses phase analysis to accelerate architectural simulations. SimPoint is used by several of the techniques presented in this dissertation, so a summary of the SimPoint approach is provided in this section. [78] contains a more detailed description.

The underlying principle of the SimPoint approach by Sherwood et al. is that program behavior is a function of the code executed by the program. SimPoint detects phase behavior by examining basic block vectors (described in the previous subsection) collected from each interval of execution.

Basic block vectors can be quite large (gcc contains around 100 thousand static basic blocks), so the vectors are randomly projected to a lower dimensionality before analysis. Random projection first generates a M by N random projection matrix, where M is the number of static basic blocks in the program, and N is the desired lower-dimensional projection. The random projection matrix is filled with random numbers limited to a fixed range. Each vector is multiplied by this random projection matrix, resulting in smaller projected vectors. Random projection is best explained by example: to randomly project a 3-dimensional ob-

ject to 2 dimensions, you randomly position a camera at a fixed distance from the object (facing the object of course), and take a picture.

After randomly projecting the basic block vectors for each interval of execution, phases are detected by grouping the projected basic block vectors based on their similarity. Each vector is a point in N-dimensional space, where N is the number of dimensions projected to (typically 15). The Euclidean distance of a pair of vectors in this N-dimensional space is used to evaluate vector similarity.

SimPoint uses the k-means clustering algorithm [61] to partition the set of vectors into clusters of similar vectors. Each cluster produced by the clustering algorithm directly corresponds to a phase of program behavior, because intervals with similar vectors execute roughly the same code in roughly the same proportions, so they should exhibit similar behavior.

After clustering a program's intervals, SimPoint selects a single representative interval from each cluster by identifying the interval that is closest to the centroid (center) of each cluster. Only these representatives will be simulated in detail with a cycle-level simulator, and the simulation results will be weighted by the number of intervals in the phase that the representative represents. In this manner, the detailed simulation results for all the representative intervals from a program can be extrapolated to estimate the overall performance of the simulated processor when executing the program.

A summary of the SimPoint approach is provided below.

- 1. Profile the program by partitioning the program's execution into contiguous intervals, and collect a basic block vector for each interval. Normalize each basic block vector so that the sum of all the elements equals 1.

- 2. Reduce the dimensionality of the basic block vectors to a smaller number of dimensions using random linear projection.

- 3. Run the k-means clustering algorithm on the reduced-dimension BBVs for

a set of k values.