# UC Santa Cruz UC Santa Cruz Electronic Theses and Dissertations

# Title

DEMIS: Dynamic EMI Shifting

# Permalink

https://escholarship.org/uc/item/7k25146x

Author Gorman, Daphne Irene

Publication Date 2018

# **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA SANTA CRUZ

### **DEMIS: DYNAMIC EMI SHIFTING**

A dissertation submitted in partial satisfaction of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

in

# COMPUTER ENGINEERING

by

# **Daphne Irene Gorman**

June 2018

The Dissertation of Daphne Irene Gorman is approved:

Professor Jose Renau, Chair

Professor Matthew Guthaus

Professor Heiner Litz

Tyrus Miller Vice Provost and Dean of Graduate Studies Copyright © by

Daphne Irene Gorman

2018

# **Table of Contents**

| Li | st of F        | ligures  |                                             | v    |

|----|----------------|----------|---------------------------------------------|------|

| Li | st of <b>T</b> | ables    |                                             | vii  |

| Ab | ostrac         | t        |                                             | viii |

| Ac | know           | ledgmei  | nts                                         | xi   |

| 1  | Intro          | oduction | 1                                           | 1    |

| 2  | Back           | kground  | L                                           | 7    |

|    | 2.1            | Wireles  | ss Communication Technologies               | 8    |

|    |                | 2.1.1    | LTE                                         | 10   |

|    |                | 2.1.2    | Bluetooth                                   | 12   |

|    |                | 2.1.3    | WiFi and WLAN                               | 13   |

|    | 2.2            | EMI Ca   | auses in Processors                         | 14   |

|    |                | 2.2.1    | EMI as an effect of processor layout        | 14   |

|    |                | 2.2.2    | Layout and Metal                            | 17   |

|    |                | 2.2.3    | Square Waves                                | 18   |

|    | 2.3            | EMI in   | Computer Architecture                       | 20   |

|    |                | 2.3.1    | Profiling                                   | 20   |

|    |                | 2.3.2    | Security                                    | 21   |

|    |                | 2.3.3    | Other EMI Models                            | 22   |

|    |                | 2.3.4    | VLSI and System-Wide Tools                  | 22   |

| 3  | DEN            | AIS Prol | blem Space Exploration through Measurements | 26   |

|    | 3.1            | Setup    |                                             | 27   |

|    |                | 3.1.1    | Test Equipment                              | 27   |

|    |                | 3.1.2    | Benchmarks                                  | 28   |

|    |                | 3.1.3    | Bands Analyzed                              | 30   |

|    | 3.2            | Insights | s and Measurements                          | 30   |

|    |                | 3.2.1    | Measurement Repeatability and Accuracy      | 30   |

|    |       | 3.2.2 Compiler Impact on EMI                 | 32 |

|----|-------|----------------------------------------------|----|

|    |       | 3.2.3 Benchmark Impact on EMI                | 37 |

|    |       | 3.2.4 Cache Impact on EMI                    | 40 |

|    |       | 3.2.5 Memory Impact on EMI                   | 43 |

|    |       |                                              | 46 |

|    |       | -                                            | 51 |

|    | 3.3   |                                              | 51 |

| 4  | ME    | SC: Model for EMI from an SoC                | 53 |

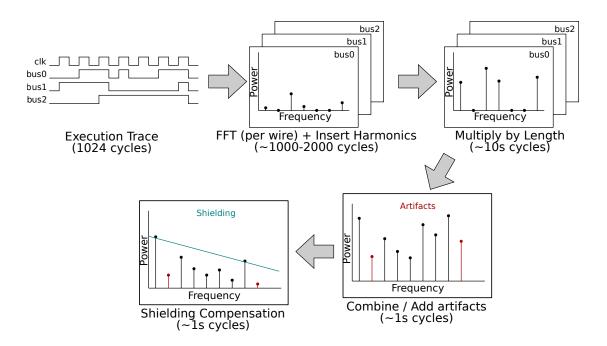

|    | 4.1   | MESC Flow                                    | 54 |

|    |       | 4.1.1 Sampling Strategy                      | 55 |

|    |       | 4.1.2 Converting to the Frequency Domain     | 56 |

|    |       | 4.1.3 Adding Harmonics                       | 58 |

|    |       |                                              | 59 |

|    |       |                                              | 61 |

|    |       |                                              | 63 |

|    |       |                                              | 63 |

|    | 4.2   |                                              | 64 |

|    |       | *                                            | 66 |

|    | 4.3   | •                                            | 67 |

|    | 4.4   | Conclusion for MESC                          | 71 |

| 5  | EM    | I CHopper: DEMIS for Layout                  | 72 |

|    | 5.1   |                                              | 73 |

|    | 5.2   | Flow                                         | 74 |

|    |       | 5.2.1 Modeling thread migration cost         | 75 |

|    |       |                                              | 76 |

|    | 5.3   |                                              | 77 |

|    | 5.4   | Conclusion for EMI CHopper                   | 80 |

| 6  | DEN   | MIS for Existing Processors                  | 82 |

|    | 6.1   | Related Work                                 | 83 |

|    | 6.2   | Evaluation                                   | 85 |

|    | 6.3   | Conclusion for DEMIS for Existing Processors | 87 |

| 7  | Con   | clusion and Future Work                      | 89 |

|    | 7.1   | Future work                                  | 90 |

| Bi | bliog | raphy                                        | 92 |

# **List of Figures**

| 1.1  | Impact of compilation options on SPEC2006 hmmer benchmark                                   | 4  |

|------|---------------------------------------------------------------------------------------------|----|

| 2.1  | Shannon-Hartley Theorem                                                                     | 9  |

| 2.2  | $1Hz$ Square wave in time and frequency domains $\ldots \ldots \ldots \ldots \ldots \ldots$ | 19 |

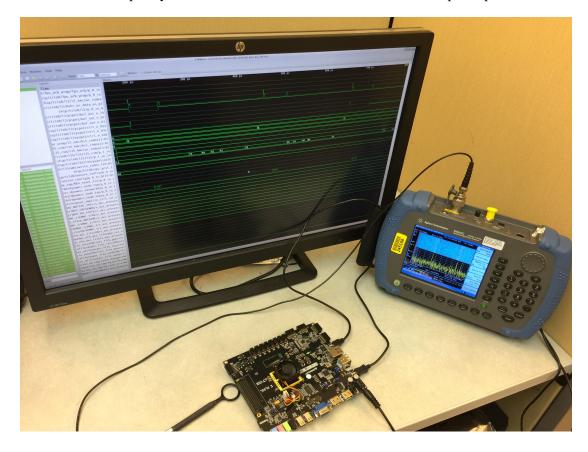

| 3.1  | Measurement setup for problem space exploration                                             | 29 |

| 3.2  | Interference emitted by A53_K620 running mcf 12 times                                       | 31 |

| 3.3  | mcf benchmark on A11_PI2 with different compilation options                                 | 33 |

| 3.4  | mcf benchmark on A8_A10 with different compilation optimizations                            | 34 |

| 3.5  | sjeng benchmark on A53_K620 with different compilation optimizations                        | 34 |

| 3.6  | hmmer benchmark on A11_PI2 with different compilation optimizations                         | 35 |

| 3.7  | EMI in the LTE 700 band with respect to execution time on the A53_K620                      | 36 |

| 3.8  | All SPEC2006 benchmarks with default settings on A53_K620 and A11_PI2 .                     | 38 |

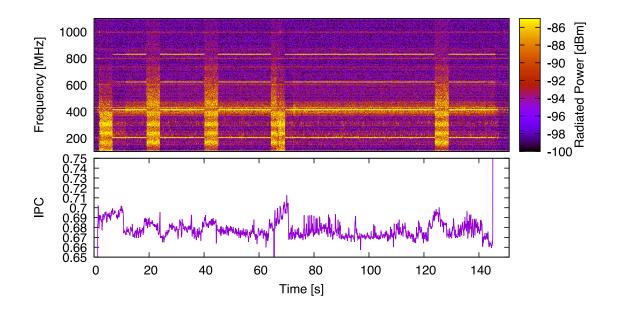

| 3.9  | mcf benchmark spectrograph and IPC on A11_PI2 over time                                     | 39 |

| 3.10 | sjeng benchmark spectrograph and IPC on A53_K620 over time                                  | 40 |

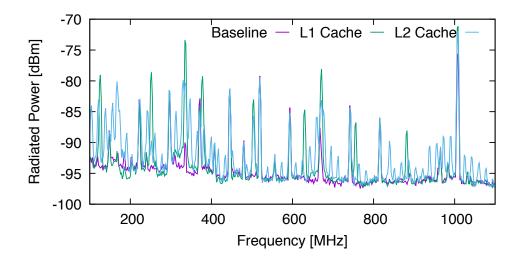

| 3.11 | A8_A10 L1 and L2 Cache accesses                                                             | 42 |

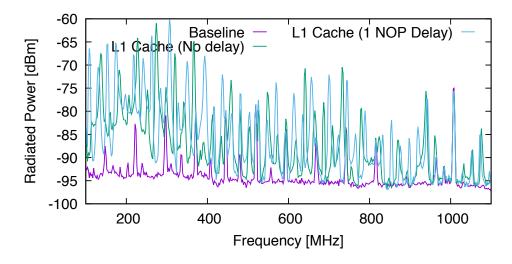

| 3.12 | A8_A10 L1 Cache accesses with and without delay                                             | 42 |

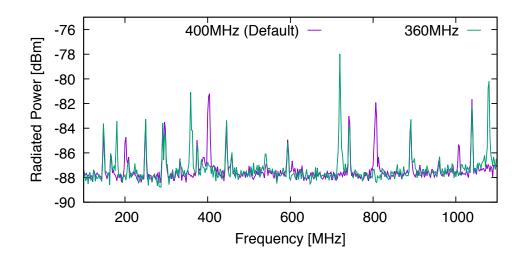

| 3.13 | Interference emitted by A11_PI2 using different SDRAM frequencies                           | 43 |

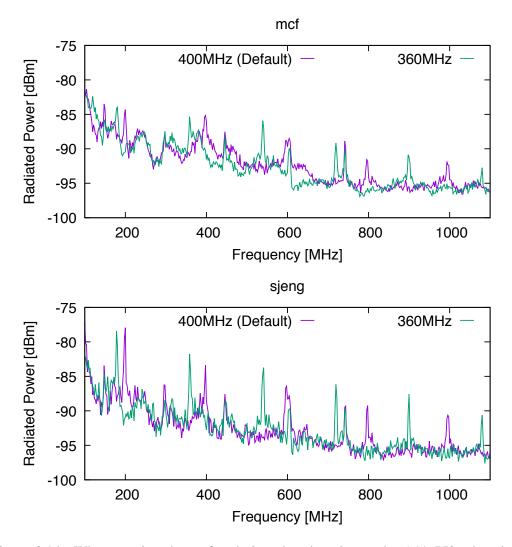

| 3.14 | mcf and sjeng benchmarks with varying DRAM speed on A11_PI2                                 | 45 |

| 3.15 | Floating-point vs integer-only calculations on A8_A10                                       | 47 |

| 3.16 | A8_A10 integer calculations with and without delay                                          | 47 |

| 3.17 | A8_A10 floating-point calculations with and without delay                                   | 48 |

|      | Benchmarks with default settings on A53_C2 and A53_K620                                     | 50 |

| 3.19 | Benchmarks with default settings on A15_XU4                                                 | 51 |

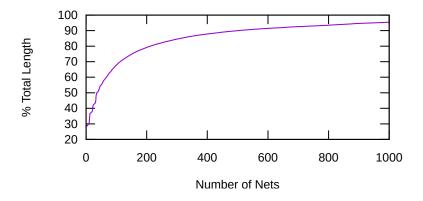

| 4.1  | Percentage of Length Covered By Nets                                                        | 56 |

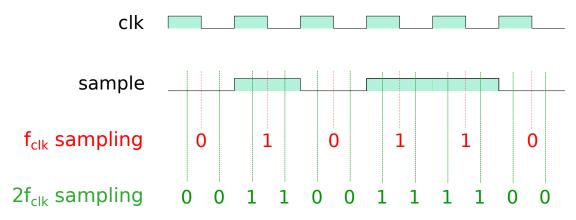

| 4.2  | Artificially increasing the sampling frequency                                              | 57 |

| 4.3  | Example of artifact detection                                                               | 60 |

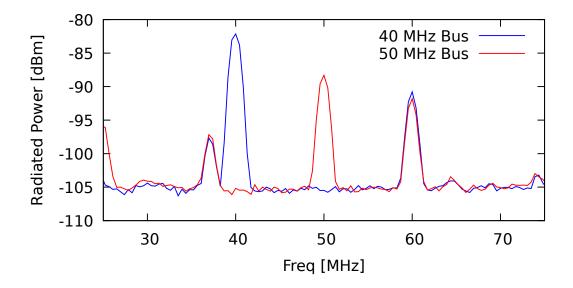

| 4.4  | EMI from a single bus toggling at different frequencies                                     | 61 |

| 4.5  | MESC flow                                                                                   | 63 |

| 4.6  | Measurement setup for MESC and EMI CHopper                                                  | 65 |

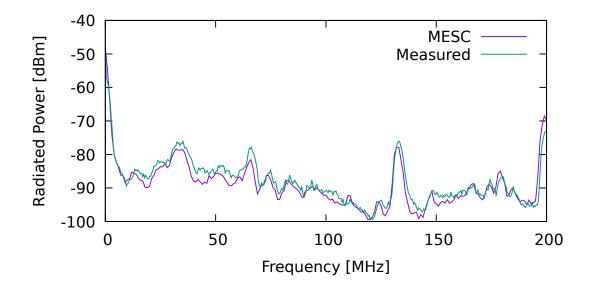

| 4.7  | Comparison of MESC and measured EMI of namd                                                 | 67 |

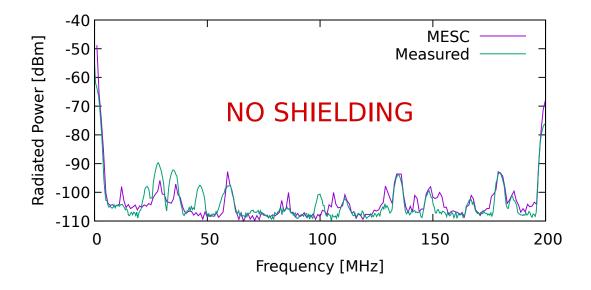

| 4.8  | Comparison of MESC without shielding to the measured EMI of three buses  | 68 |

|------|--------------------------------------------------------------------------|----|

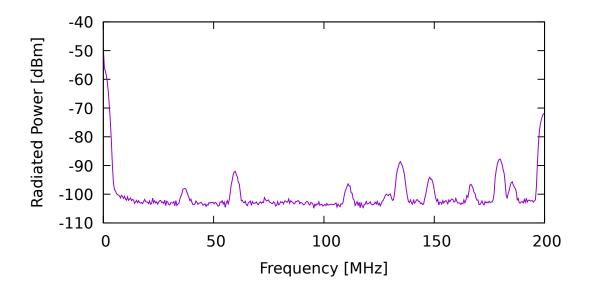

| 4.9  | EMI of the unprogrammed FPGA                                             | 69 |

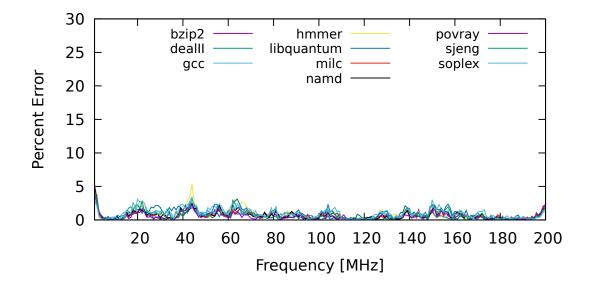

| 4.10 | MESC percent error over frequency                                        | 70 |

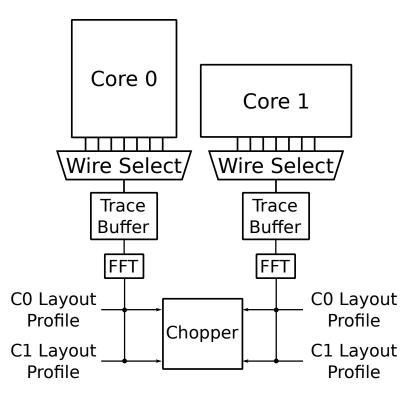

| 5.1  | EMI CHopper implementation                                               | 77 |

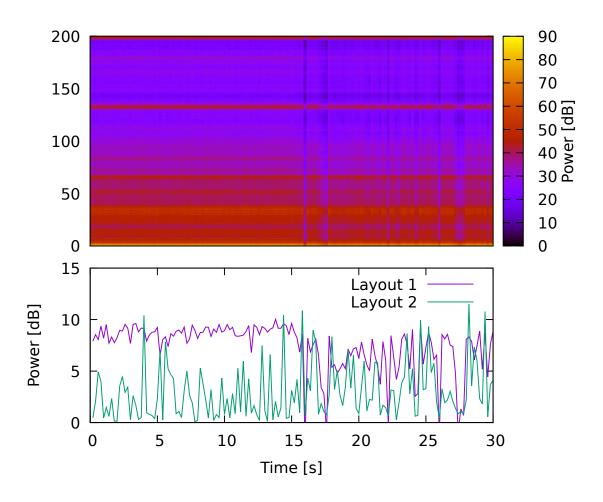

| 5.2  | Interference over time for sjeng                                         | 79 |

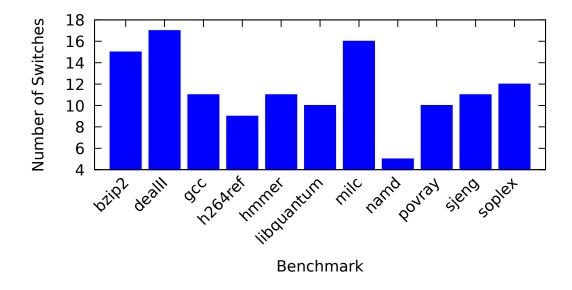

| 5.3  | Number of hops per benchmark                                             | 80 |

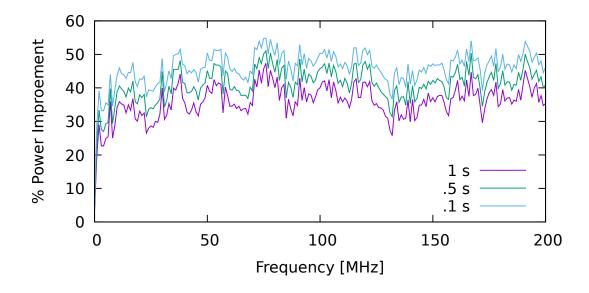

| 5.4  | Power Improvement over frequency for different migration rate thresholds | 81 |

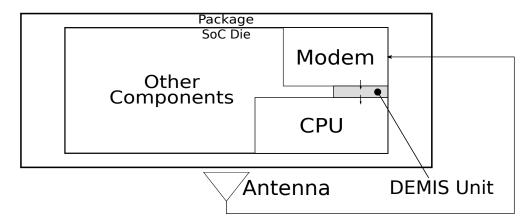

| 6.1  | Proposed DEMIS architecture                                              | 83 |

| 6.2  | Radiated power in LTE 800 band on A15_XU4                                | 86 |

| 6.3  | EMI Reduction on A15_XU4                                                 | 87 |

# **List of Tables**

| 2.1 | Wireless Communication Technologies   | 10 |

|-----|---------------------------------------|----|

| 3.1 | Device Specifications                 | 28 |

| 3.2 | Wireless Communication Bands Analyzed | 30 |

### Abstract

### **DEMIS:** Dynamic EMI Shifting

by

#### Daphne Irene Gorman

Processors emit non-trivial amounts of electromagnetic radiation, creating interference at frequencies that are used by wireless communication technologies such as cellular, WiFi, and Bluetoooth. I introduce the problem of in-band radio frequency interference as a form of electromagnetic interference (EMI) to the computer architecture community as a technical challenge to be addressed.

My research is the first to provide insights in the new area of dynamically shifting the EMI generated by a processor by evaluating several platforms and showing the EMI is sensitive to many architectural and compilation parameters through exhaustive measurements. Using these measurements, I propose the new idea of Dynamic EMI Shifting (DEMIS), where architectural and/or compiler changes allow the EMI to be shifted at runtime by a processor. DEMIS processors dynamically move the interference from frequency bands used during communication to other, unused frequencies. Unlike previous works that leverage static techniques, DEMIS dynamically targets specific frequency bands; the type of techniques used in my research are only possible from an architectural perspective.

Despite the fact that the EMI generated by a processor is deterministic, modeling the EMI has proven to be a complex challenge. Moreover, EMI has been shown to be layout dependent (affected by the location of functional units on the chip and the lengths of the wires) and binary dependent (affected by not only the application but also on the compilation options). I propose a Model for EMI from an SoC (MESC), a framework for modeling electromagnetic emissions from a core. MESC takes into account some layout information and the switching activity of a process to model the expected EMI emitted by an SoC. I validate MESC against a core running on an FPGA. My evaluation shows that MESC is able to predict EMI within 95% accuracy across time and across the frequency spectrum, even when using statistical sampling to obtain activity rates.

Using the results from MESC, I am able to propose that two different layouts of a single RTL can be leveraged to dynamically shift EMI using my technique EMI Core Hopper (EMI CHopper), a layout-based implementation of DEMIS. EMI CHopper uses a multi-core system, where each core has a different layout but the same RTL, and utilizes thread migration to have an application "hop" between cores to reduce in-band EMI on the fly. Leveraging MESC, EMI CHopper reduces in-band EMI by up to 50%, with only a small performance impact.

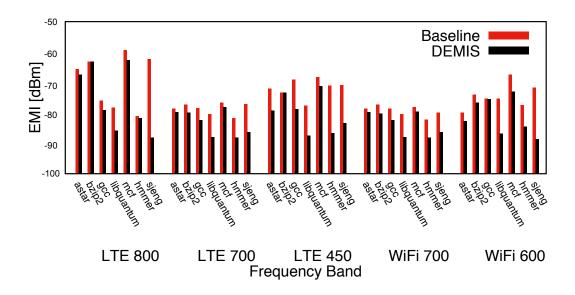

In order to implement DEMIS for existing systems, I propose utilizing higher level techniques, such as compiler optimizations and clock speeds. My evaluation over real systems shows a decrease of in-band EMI ranging from 3 to 15dB, with less than a 10% average performance impact. A 15dB EMI reduction for LTE can represent a bandwidth improvement of over 3 times for EMI bound communication.

The research presented in this thesis offers a new, architectural perspective on a prevalent problem in wireless communications. My findings based purely on architectural techniques show significant promise in improving wireless communications, and the tools I described offer many opportunities for further research.

# Acknowledgments

I would like to thank my committee for their valuable feedback and help throughout my graduate experience. In particular, my advisor Prof. Jose Renau who has provided me with help, guidance, and probably an unnecessary amount of leniency which allowed me to pursue this area of research.

My wonderful labmates in the MASC lab, especially Rafael, Gabriel, Elnaz, and Blake, encouraged me and kept me sane during crunch time before deadlines. Without these teammates and my other friends' help throughout the years, which ranged from working through a particularly complex piece of code with me to telling me to take a break and relax, I would never have made it through graduate school.

Last but not least, I want to thank my parents and sister for always being there for me and being supportive of my educational pursuits for many years. It was only through their influence that I was able to become the person I am today. Thank you for everything!

# **Chapter 1**

# Introduction

Communication breakdown It's always the same I'm having a nervous breakdown Drive me insane!

Led Zeppelin

The advances in integrated circuits and digital devices in recent years have brought to market a growing number of connected devices, which are getting smaller each generation. To meet commercial and technological goals, the space being allocated to electronic components is only a fraction of the already small device size, which requires tighter integration. However, a processor in a SoC can produce electromagnetic interference (EMI) that can disrupt wireless communication, reducing the effectiveness of the device.

As mobile devices become more ubiquitous and wireless communication technologies become more diverse, we want our mobile devices to be able to interact with a wide variety of communication technologies. I present to the computer architecture community the problem of in-band EMI caused by the processor. That is, when a processor is running, it may be emitting Radio Frequency (RF) interference, or EMI, at the same frequencies the device is using for wireless communication, causing interference. Unfortunately, the Shannon-Hartley theorem (explained more extensively in Section 2.1) states that this interference constrains the speed that data can be sent wirelessly.

Computer processors emit measurable amounts of electromagnetic radiation; enough that the EMI can be exploited as a security risk [15, 16]. In addition to being a security concern, EMI can also interfere with wireless communication, which is the focus of the work presented in this thesis. Even when running just the operating system, the processor will emit radiation at some frequencies. The EMI produced by a processor can create significant desensitization of the antenna, and is a well-known obstacle in the field, which many different publications and patents are dedicated to addressing [6,21,33,38]. Currently, one way to mitigate this problem is to place the computer processor as far away as possible from the antennas [21, 35] to minimize the effect of the processor's EMI. However, modems are placed as close as possible to the antennas in order to mitigate losses before the signals are processed. With the introduction of more integrated chips such as the Snapdragon series [42], some of which include wireless communication processors, designers may no longer be able to physically separate the CPUs and the antenna in this way. This problem also tends to worsen with the emergence of smaller, more integrated devices such as wearables, as processors and RF components (particularly antennas) can no longer be physically separated. This is because even though the transmitted power may be less, the power recieved decreases linearly with transmit power and quadratically with distance, which will be discussed more in depth in Chapter ?? during my analysis of Equation 2.4.

Much of this work is based on the observation that wireless communication systems use many frequency bands, but not all the bands are used simultaneously. This observation can alleviate the proposed problem by moving RF interference out of the bands being used for communication in a given time.

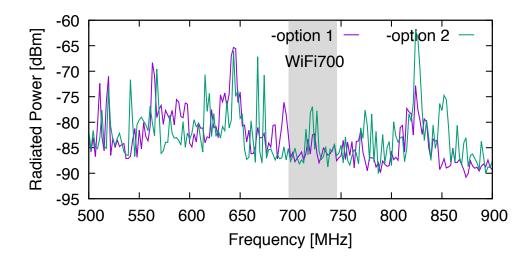

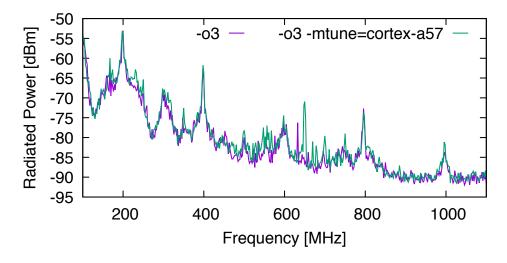

To illustrate this potential, Figure 1.1 shows the interference level captured from a spectrum analyzer for a Exynos 5422 processor (a 28nm chip running with a clock frequency of 2GHz) running SPEC2006 hmmer application. This type of plot has frequency in the x-axis and radiated power in dBm in the y-axis. The higher the radiated power the higher the EMI. The plot shows a SuperWiFi XR7 frequency band. From a communication point of view, we want the lowest possible amount of noise. Each line shows a different compilation option for hmmer from the SPEC2006 benchmark suite. The second option has a small 3% performance impact, but it has close to 6dB (or  $4 \times$  power) reduction of in-band noise. A more in depth analysis of this measurement will be provided in Chapter 3.

Since workload, compiler, architecture, and layout are necessary for understanding and addressing this problem, this belongs to the classical architectural domain where impact on execution performance and the interface between compiler/architecture/VLSI layers have different trade-offs. Computer architects are uniquely suited to provide solutions for minimizing in-band EMI from the processor.

Despite the fact that EMI is deterministic, there are no usable tools or methodology for modeling EMI for a given application, particularly at the micro-architecture level. This is because, despite its consistency, there are numerous factors that contribute to the EMI a proces-

Figure 1.1: Changing compile options for the SPEC2006 hmmer benchmark on an ODROID-XU4 (Exynos 5422 chip) causes a significant difference in noise in the SuperWiFi XR7 frequencies (grey) with only a small change in performance.

sor produces. EMI can be theoretically modeled as a combination of electromagnetic radiation being produced by alternating current in each wire of a processor. In any modern design, the complexity both in number of wires and in the data patterns on them do not make this prediction an easy task. The use of a full-wave simulation software [3,24,43] would provide accurate results, but takes an extremely long time, as the processor's layout would have to be taken into account as well as the activity of each wire. Also, because GDSII is necessary for this type of simulation, these tools are unusable until just before tapeout, which may be too late for significant design changes. To some extent this is similar to requiring a full SPICE simulation for a whole chip, which is not really feasible. However, the extreme accuracy provided by these fullwave simulators is most likely unnecessary for addressing the problem of processor-generated interference on wireless technologies, since compensation mechanisms, such as redundancy and error-correcting codes, already exist for wireless communication and make "interference-free" communication unnecessary. Designers lack usable models, and these models would be too complicated to actually run. Typically, designers do not realize they have an EMI problem until after a system has been prototyped and evaluated, which puts them in the unfavorable position of having to apply costly and usually ineffective patches, or going back and redesigning the system [21].

Furthermore, the EMI is also application/binary dependent, so the same layout will produce different EMI depending on the program executing. This adds additional challenges for designers, as it is difficult to account for the multitudinous, essentially infinite, applications a processor may execute. Then, modeling the EMI will necessarily imply characterization through specific benchmarks that can represent the EMI of a large range of applications. Thus, any model for EMI must be flexible enough to account for different processes.

In this thesis, I introduce the problem of in-band RF interference as a form of EMI generated by a processor, with an emphasis on micro-architecture. Included is a thorough exploration of the problem space as I analyze the effects specific architectural parameters have on EMI, as well as the concept of Dynamic EMI Shifting (DEMIS) to reduce in-band interference. Additionally, this thesis includes a technique for modeling the EMI a processor will generate as it executes an application and two implementation of DEMIS.

Chapter 2 provides background information relevant to my research. First, I provide a short description of wireless communication and some specific technologies. Then, I briefly cover some of the reasons EMI is produced in processors before providing a survey of other computer architectural research that focuses on EMI.

In Chapter 3, I provide an in-depth exploration of the architectural problem space

as it affects in-band EMI. This analysis consists of manipulating specific architectural and compilation parameters and measuring the resulting changes in RF interference.

MESC, the first Model for EMI from an SoC, is proposed in Chapter 4. MESC takes into account some basic layout information of a processor and the activity rates of individual nets for a process in order to approximate the expected EMI from that process.

Building on the model described in Chapter 4, Chapter 5 proposes the DEMIS technique for reducing in-band EMI emitted by a processor, EMI CHopper (EMI Core Hopper). EMI CHopper reduces EMI by causing processes to "hop" between cores that have the same RTL but different layouts.

The DEMIS technique for reducing in-band EMI, for existing processors is proposed in Chapter 6. This DEMIS implementation consists of shifting the EMI at runtime by changing architectural and/or compiler parameters during execution time.

Finally, Chapter 7 concludes with the significance and main findings of my research as well as some opportunities for future work.

# Chapter 2

# Background

Get your facts first, then you can distort them as you please.

Mark Twain

This chapter covers some background information about EMI, how it is produced in a core, and other useful information. I put special focus on the fact that communication does not use the entire frequency spectrum at a given time, but rather uses a single band. Thus, a processor does not need to minimize the EMI over the entire frequency spectrum, but rather just the frequencies being used for communication at that time.

Additionally, I will cover some of the current techniques and tools being used by architects today concerning EMI.

# 2.1 Wireless Communication Technologies

My work deals with the electromagnetic radiation from the processor that causes interference for the device's wireless communication. Since EMI may be an unfamiliar topic to parts of the computer architecture community, this section aims to provide an overview of the main concepts and technologies involved. This is not meant to be a complete introduction to the subject.

Wireless communication is an important feature of most modern computational systems, particularly for mobile devices. Wireless communication usually relies on allocating a specific frequency band in which data is transmitted according to a technology-specific protocol. Regardless of which specific protocol is being used, the theoretical amount of data that can be transferred through a channel depends on a certain number of factors, like the bandwidth and the Signal to Noise Ratio (SNR). This relation is governed by the Shannon-Hartley Theorem,

$$C = B * \log_2(1 + \frac{S}{N}), \tag{2.1}$$

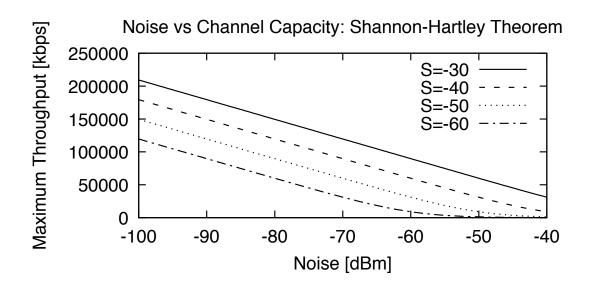

which states that the channel capacity (*C*), or the theoretical upper bound on the net bit rate, is affected by the bandwidth (*B*) and the SNR ( $\frac{S}{N}$ ). Since SNR is the quotient between noise and signal strength, the lower the noise the higher the channel capacity. Figure 2.1 shows a visualization of the Shannon-Hartley Theorem for typical values for the LTE standard for cellular communication, with a bandwidth of nine megahertz.

Therefore, for a fixed bandwidth and signal strength, increasing the amount of noise will reduce the total channel capacity available, reducing the total amount of data that could be transmitted through that channel. Throughout my research, I explore the noise emitted by the

Figure 2.1: The amount of noise drastically changes the maximum theoretical throughput at a particular frequency at different signal strengths (S = signal strength in dBm).

processor that could interfere with the wireless communication technologies in a device.

The focus of this work is to improve the SNR by reducing the noise. Particularly, I focus on reducing the noise caused by processor generated EMI. Increasing the SNR will result in an improved channel capacity.

Unfortunately, EMI is produced any time current is present in a system, and thus computer processors constantly emit non-trivial amounts of noise. Fortunately, wireless communication is dependent on specific frequencies, and thus a device only needs certain frequency bands to be less noisy at a given time. Common sources of noise are the clock, its harmonics, memory accesses, and even power converters; these will be discussed later.

| Network    | Range (MHz) | Max Channel Bandwidth (MHz) | Max Bandwidth (MHz) |

|------------|-------------|-----------------------------|---------------------|

| LTE        | 698–5925    | 20                          | 18 <sup>1</sup>     |

| Bluetooth  | 2400-2485   | 1                           | 1                   |

| WiFi       | 2400-2500   | 22                          | 40                  |

| WiFi 5GHz  | 5150-5850   | 160                         | 160                 |

| Super WiFi | 54–790      | 5                           | 32                  |

| WiFi HaLow | 755–928     | 4                           | 16                  |

Table 2.1: Wireless technology frequency ranges and maximum bandwidth used at a given time.

#### 2.1.1 LTE

LTE (Long Term Evolution) is the current standard for cellular communication and was developed with the main objective of improving the communication rates to and from a cell phone. However, with the invention of smartphones, the noise emitted from the phone's CPU can interfere with communication. This section provides a brief introduction to cellular communication technology LTE with a focus on components related to my research. LTE (and wireless communication in general) is commonly divided into frequency bands allocated to different users and uses.

The band selection is determined by many factors such as signal strength and band congestion and is usually out of the control of the user, since it is mostly defined by the tower, but higher-frequency bands are usually preferred since they can send more data.

Different times and situations may require different LTE frequency bands to be clear. For example, low frequencies can permeate solid objects better, so when using LTE inside, we would prefer to use a low-frequency band such as band 12 (699 to 716MHz). However, higher

<sup>&</sup>lt;sup>1</sup>LTE can utilize a total of 18 MHz, but the frequencies do not necessarily have to be contiguous. Future LTE technologies may expand this 18 MHz to 19.8 MHz, as the largest channel bandwidth is actually 20 MHz, but the edges of the band remain unused in order to prevent noise in adjacent bands.

frequencies can send more data, so when outside, it would be better to use a higher frequency band such as band 4 (1710 to 1755MHz).

In order to connect to a network tower, a device utilizes two different radio links, one for uplink (where the data goes from the device to the tower) and one for downlink (tower to device) [22]. Most LTE bands are Frequency-Division Duplex (FDD) meaning that the uplink (UL) and downlink (DL) connections operate at different frequency bands between 10 and 400MHz apart, thus allowing them to happen at the same time [1], meaning communication happens at multiple frequencies simultaneously. However, some LTE bands use Time-Division Duplexing (TDD), which means that UL and DL occur at the same frequency, but at different times.

Depending on which network carrier a device is utilizing, it accesses to different LTE bands. Currently in the US, there is no overlap between the bands provided by AT&T (bands 2, 4, 5, 17) and Sprint (bands 25, 26, 41). Furthermore, different countries use different bands as well. For example, the US and most of Europe tend to use FDD bands, whereas China tends to use TDD bands. Thus, the amount of viable frequencies for an LTE connection is largely dictated by which cellular network provider a device is using.

Cell networks can trigger a band switch when the EMI interference is high. An infrequent noisy spike at a certain frequency is enough to drop a call or lose data, but is not necessarily enough for a cellular network to switch frequency bands. On the other hand, if some noise does trigger a band switch, it is likely that the mobile device is now operating on a slower band. For example, when using the T-Mobile network in the US, a device may be using band 4 because it had less interference and congestion, but because it is currently running a process that creates in-band noise, the device will switch the noisier and more congested band 12. If the noise generated by the device were out of the band 4 frequencies, the device would have continued to operate on the higher band.

A noisy band may lead the network to trigger a band switch. The noise may be due to congestion, interference with other networks or simply because the CPU on the cell phone is emitting EMI. In my work, I show that architectural parameters can be manipulated to reduce the amount of in-band EMI while communication is happening to reduce interference from the core to the antenna.

The implication for my research is that to improve LTE bandwidth, only one or two bands of communication need to be cleared. The band to be cleared is not known a priori, and thus a dynamic band EMI management has high potential benefits.

### 2.1.2 Bluetooth

Another technology that is commonly implemented in mobile devices and could suffer from processor EM radiation is Bluetooth. Bluetooth operates at 2.4GHz, and the entire Bluetooth spectrum spans 83MHz. Each of the 79 Bluetooth channels has a bandwidth of 1MHz [10]. The reason for so many channels is that Bluetooth utilizes a Frequency Hopping Spread Spectrum (FHSS) technique, which utilizes each channel in a preset sequence negotiated by both the master and slave when they are first connected. The channel hopping occurs regularly according to that predetermined sequence known to both the transmitter and the receiver.

Bluetooth's high frequency limits the communication distance and also makes it more

susceptible to interference. Therefore, it is more crucial to prevent noise from a nearby source, such as that device's own CPU. Like in LTE, DEMIS and EMI CHopper can further reduce interference focusing on the bands being used at the moment.

### 2.1.3 WiFi and WLAN

Finally, another ubiquitous technology that may suffer from EMI from the CPU is WiFi, present in virtually every mobile device on the planet. WiFi operates at both the 2.4GHzand 5GHz (802.11a, n, and ac) frequencies. Older WiFi protocols use frequency hopping (similar to Bluetooth) or spread spectrum transmissions, while newer versions use Orthogonal Frequency Division Multiplexing.

Additionally, the 802.11af standard (also known as White-Fi or Super WiFi) operates in the 54 to 790MHz range (in bands licensed for TV, VHF, and UHF) and has been in use since 2014. White-Fi uses frequency channels with bandwidths ranging from 6 to 8MHz, and can use up to four channels at once in one or two contiguous blocks.

Although operating at different bands and having different bandwidths, WiFi also divides the spectrum in different bands, dynamically assigned to each device. The communication speed of WiFi and WLAN can also be reduced due to the presence of in-band noise created by the CPU, and thus could also be improved by DEMIS and EMI CHopper.

# 2.2 EMI Causes in Processors

From an RF perspective, any wire with a time dependent current passing through it behaves as an antenna. Traditionally, in integrated circuit design, one of the only concerns is capacitive coupling, and sometimes wires being subject to bit-flips within a wire, which can cause data corruption and/or invalid behavior in the circuit. In this work, I look into wires as transmitters. I am thus interested in the EMI being emitted by each wire with respect to the wireless communication.

### 2.2.1 EMI as an effect of processor layout

In general, the power and direction of the radiation depend on the form of an antenna and on the distance from which the interference is being measured. For instance, for very long wires,  $(L \gg d)$ , where L is the wire length and d is the distance of interest), the radiation occurs uniformly throughout the wire axis, varying only with distance. In that particular case edge effects are usually ignored. Another example is with closed loop antennas, where the radiation is directional and perpendicular to the loop plane. In the specific case of interest of my research, L is a length within a die and d is a distance within a device, thus usually  $d \gg L$ . Also, there is a large number of wires that will act as an antenna array, possibly emitting at multiple frequencies, all with different magnitudes. The resulting EMI will, thus, be a combination of all the EMI emitted by each wire.

For a real system, the wireless communication antenna will be located in the same plane as the chip, since mobile devices tend to be relatively flat. This can reduce the EMI observed by the antenna with regards to the maximum EMI observed in a plane parallel to the die plane. For the sake of simplicity, my model takes into account the maximum EMI, which is a more conservative approach since it is not known at design time which will be the direction of the die in respect to the antenna(s) in the device.

There are a few antenna equations that are relevant to my work regarding a processor layout's effect on interference, but the most relevant is the basic equation for antenna gain,

$$G = \frac{4\pi A}{\lambda^2}.$$

(2.2)

Equation 2.2 states that the gain of an antenna (G), or power multiplier, is directly proportional to the aperture, or effective area, A. While this works for aperture antennas, we also must consider linear antennas, for example a short dipole, which has a total radiated power of

$$P_{total} = \frac{\pi}{12} I_0^2 Z_0(\frac{L}{\lambda})^2, \qquad (2.3)$$

where  $I_0$  is the current amplitude (the signal fed into the dipole),  $Z_0$  is the admittance of free space  $\approx 376\Omega$ , and *L* is the length of the dipole, which to qualify as "short" must satisfy  $L \ll \frac{\lambda}{10}$ . Another important formula, known as Friis Transmission Formula,

$$P_R = \frac{P_T G_T G_R \lambda^2}{(4\pi d)^2} = \frac{P_T G_T G_R c^2}{(4\pi df)^2},$$

(2.4)

states that the received power  $P_R$  is the product of the transmitted power  $P_T$  multiplied by the TX and RX gains  $G_T$  and  $G_R$  multiplied by the wavelength squared (or multiplied by  $c^2$  and divided by the frequency squared  $f^2$ ) all divided by  $4\pi$  times the distance between the two antennas d. This means that the received power is proportional to  $\lambda^2$  or inversely proportional to  $f^2$ . In decibels, this formula is

$$P_R = P_T + G_T + G_R + 20\log_{10}(\frac{\lambda}{4\pi d}).$$

(2.5)

These equations [36] are used throughout my research, particularly in designing MESC.

One thing that is important to note is that most EMI measurements are taken in the frequency domain. That is, EMI is typically depicted as the amount of power being radiated at each frequency. Most of the measured and modeled plots in this thesis are also in the frequency domain. In my work, I utilize the Fast Fourier Transform (FFT) to convert samples taken over time (in the time domain) into the frequency domain. One important aspect of taking an FFT over a set of time-domain values is that the FFT can only provide values for frequencies up to half of the sampling frequency, the Nyquist frequency. Therefore, to get the frequency domain up to a frequency f, the sampling rate need to be 2f. As the primary objective in this work is to model and then reduce in-band EMI, using the frequency domain is a good way to visualize and isolate specific frequencies, as opposed to trying to determine frequencies from periodicity in time-domain plots.

The equation for the FFT is

$$X_k = \sum_{n=0}^{N-1} X_n \times e^{i2\pi nk/N},$$

(2.6)

where  $X_n$  are time domain samples,  $X_k$  are frequency domain samples, N is the number of time domain samples, and k spans the integers from 0 to N - 1. To get back into the time domain from the frequency domain, the Inverse FFT (IFFT),

$$X_n = \frac{1}{N} \times \sum_{k=0}^{N-1} X_k \times e^{i2\pi nk/N},$$

(2.7)

can be used.

RF Integrated Circuits (ICs) are vulnerable to on-chip in-band interferers [5], and may contain circuit-level RF noise couplings that would have a significant impact on systemlevel performance of wireless communication performance. Unfortunately, finding the cause of interferers is extremely complicated and have so many technical aspects, that achieving a reliable estimation using computer simulations is impossible.

### 2.2.2 Layout and Metal

To apply these RF principles to a processor, I work under the assumption that metal wires in the processor act as "antenna elements" or "radiators" that emit EMI. One fundamental rule is that the radiated power of an antenna is proportional to the antenna aperture, or the effective size. This means that if an antenna has twice as much metal, we would expect twice as much power to be radiated, as the gain has doubled (see Equation 2.2). Applied to a processor layout, a net that is twice as long or twice as wide should contribute twice as much EMI. Furthermore, long traces may add inductance, which could increase the EMI.

Additionally, the EMI power is proportional to the integral of the current distribution along the antenna. Basically, this means that areas on the chip that have higher current will radiate higher power EMI. If a circuit contains a loop, that loop may couple with an external magnetic field and act as a strong transmitting antenna. However, this effect can be minimized by reducing the size of the loop. Also, loops are not widespread in chip designs due to inductive effects that are usually undesirable.

#### 2.2.3 Square Waves

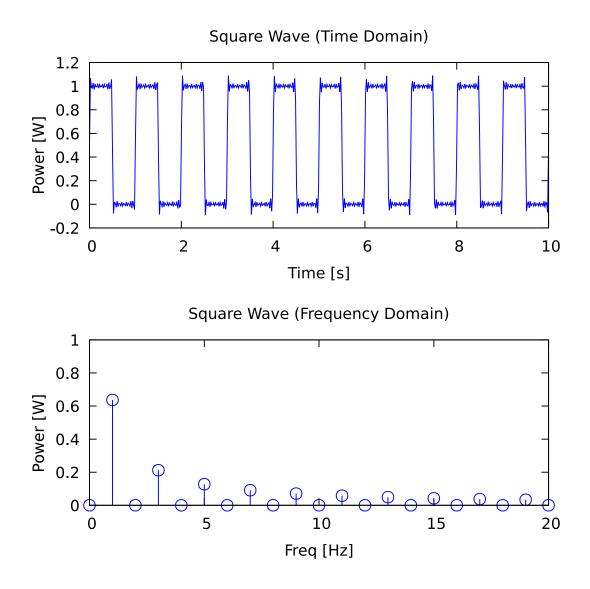

As my research focuses focuses on digital processors, a basic understanding of the EMI of square waves is required, as they have some unique properties that are not shared with simple sinusoidal waves.

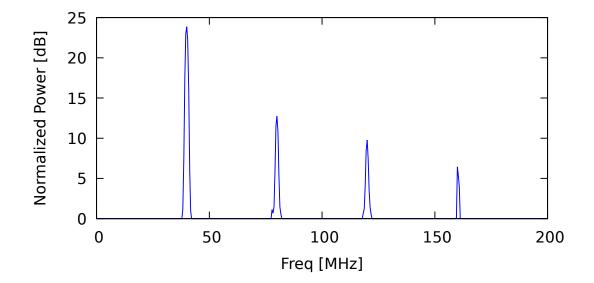

One important observation about square waves is that square waves produce strong odd harmonics and weaker even harmonics. That is, for a square wave for a frequency of f we would expect large amounts of power at f, 3f, 5f, 7f, etc.. However, at the even harmonics 2f, 4f, 6f, we would expect some radiated power, but significantly less than at the odd harmonics. Figure 2.2 shows the wave created by adding the first ten odd harmonics of a square wave as in the equation  $0.5 + \frac{2}{\pi} \sum_{k=1}^{10} sin(2\pi(2k-1)t)/(2k-1)$ , which produces a square wave with a frequency of 1Hz and an amplitude of 1. Below that is the same square wave depicted in the frequency domain, which shows the odd harmonics to have significant power, but the even harmonics to be zero.

Another common occurrence are power spikes that occur at subharmonics  $(\frac{f}{2}, \frac{f}{3}, \frac{f}{4},$  etc.). Potentially, we may even observe significant power at the harmonics of the subharmonics, which would could potentially put power spikes at unexpected frequencies.

An important observation is that in most data buses in a processor, the data is not truly periodic, that means that there is not a single frequency being produced over time. For instance, a bit of data can have a non-periodic pattern of values over time, like "00100011101" (where each bit corresponds to the value at a given clock cycle).

In order to design a realistic model, we must take into account all of these complexi-

Figure 2.2: A 1Hz square wave in the time domain (top) and the frequency domain (bottom). A square wave is constructed from a sine wave and its odd harmonics.

ties. In my model, we start from a cycle-accurate execution trace of the wires in the processor and, assume it is a relatively square wave to perform a Fourier transformation, which allows us to determine which frequencies are being affected by a specific data pattern.

# **2.3 EMI in Computer Architecture**

This section provides descriptions of some of the current research on EMI generated by processors. This section briefly covers topics from wireless communication, profiling, and security.

### 2.3.1 Profiling

Recently, there has been a push towards using EMI to profile code. Callan *et al.* [14] proposed ZOP: a zero-overhead approach to obtain profiling information via EMI measurements. ZOP first goes through a training phase in which it builds a model that associates different wave forms with different parts of the code. Using that model, ZOP can then go through its profiling phase, which monitors the EMI and can match the current EMI with what part of the code is being executed at that time.

Schatbakhsh *et al.* [40] were able to exploit the processor's EMI to perform zerooverhead spectral profiling. They have shown a correlation between the amount of time a loop takes (*T*) and a frequency "spike" in the EMI (f = 1/T). Some of our findings may be influenced by this phenomenon.

However, the measurements presented in my work show that two processors can exhibit very different EMI, even when the two processors have the same RTL and are running the same benchmark compiled with the same options. This clearly shows that Spectral Profiling [40] has potential, but it is not obviously applicable, and I consider it future work for potential improvements.

### 2.3.2 Security

There has been substantial research on EMI and security, and many tools have been published that address the EMI security side channel. One notable publication proposes FASE [16], which is a methodology for finding periodic signals (such as a clock signal) whose amplitude is dependent on processor or memory activity. The authors found that the signals generated by a processor fall into three main categories: strong signals from voltage regulators and power filtering components at the switching frequencies of the regulators, signals from memory-refreshes, and high frequency clock signals and clock harmonics, especially DRAM clocks. They note that all three of these types of signals are affected by what the processor is doing. For example, the signals from the voltage regulators are affected by how much activity is occurring in the processor —the more activity, the higher power consumption, the stronger the signal. The signal caused by memory refreshes are caused by activity by the memory controller, and the EMI from the DRAM clocks are dependant on DRAM activity.

Another tool, SAVAT [15] determines the impact a single instruction has on the RF signal produced by running a program. The authors were able to distinguish single instructions via studying differences in EM radiation. Thus, showing that radiation patterns of some hardware is dependent on what software is running. We can conclude that manipulating the architectural components of a processor will modify the EM emissions, as the same program will be executed differently.

As opposed to the publications that show how vulnerable processors are to side channel attacks, some publications use EMI to discern whether or not a process has been modified. For example, EDDIE detects code injections without introducing any overheads or changing the hardware or software [34].

### 2.3.3 Other EMI Models

Wang *et al.* have published a measurement procedure that searches for amplitudemodulated EMI [47]. The algorithm utilizes FASE and SAVAT in order to determine which circuits in a processor are most susceptible to EMI side channel attacks.

Werner *et al.* have proposed a method for determining the instruction-dependent magnetic field sources [48]. Their model determines the locations of the magnetic field sources at a single frequency. In fact, the user is encouraged to choose a "less noisy" frequency for this model. This is different from my proposed model MESC, which models the EMI over multiple frequencies from the processor, instead of modeling the processor from the EMI.

### 2.3.4 VLSI and System-Wide Tools

In general, not many tools for modeling or minimizing the EMI from a processor exist, even for a system-wide or VLSI perspective. Some PCB simulation tools contain rule checking for EMI, such as Hyperlynx [24], but that is only to comply with Federal Communications Commission (FCC) approval. Commercial full-wave simulation tools such as ANSYS [32], CST Microwave Studio [43], Ansoft HFSS [3] are all available and would provide in-depth and highly accurate predictions of the EMI created by a processor. However, these tools are costly and have long simulation times, and thus are not used in my work.

Most techniques implemented to minimize EMI from a system perspective address the

EMI generated by the clock. One widely used technique that is implemented in most modern processors is Spread Spectrum clock generation [26]. This lowers the EMI generated by the harmonics of a clock signal by modulating the clock. After modulation, the harmonic power decreases significantly. Another technique used to minimize the high frequency EMI produced by the system clock while keeping the skew and power minimal by changing buffer placement and sizing using dynamic programming [29].

Although not strictly EMI, EmerGPU [45] detects and mitigates resonance voltage noise (which causes EM noise) in GPUs. In order to reduce voltage noise, some techniques include reducing the slope of current changes via hardware or software mechanisms.

### **2.3.4.1** Interference from the clock

There has been a lot of work done on minimizing the interference from the clock [26, 27, 29, 30]. As clock speeds tend to be lower than the frequencies used by wireless communications, it is the clock harmonics that have an adverse affect on signal. Therefore, it is common for chips to have modulated clock signals, slightly changing the cycle time of the clock every cycle. By modulating the clock signal, the attenuation for the harmonics is significantly increased, and therefore the harmonics at the communication frequencies are much lower than for an unmodulated clock signal.

#### 2.3.4.2 Static Techniques to Reduce EMI

Currently, for LTE, the interference reduction techniques being utilized include only static techniques<sup>2</sup>. These techniques address two separate cases: noise from on-die interferers, and noise from an external source (such as the antenna itself).

The most consistent on-die interferer is the clock. Even low-frequency clocks tend to interfere with communication frequencies, as even the twenty fifth harmonic can create frequency spikes that add significant in-band EMI. In fact, some devices fully power down their cores in order to avoid noise during the transmit (TX) phases of communication.

Off-chip interference can be caused by power coupling issues. Even with separate power converters, some parasitics still propagate from core to core. Additionally, during simultaneous TX and receive (RX) actions, noise from the transmit antenna can overpower the received signal, and thus multiple high- and low-pass filters are utilized, and in some cases, the TX signal is fully subtracted out of the received communication. Furthermore, DRAM is often the cause of interference, especially when placed off-chip. However, moving the DRAM on-chip creates less interference.

For Bluetooth, successful operation in the presence of external interferers such as microwave ovens or WiFi networks is to provide some shielding or distance from the cause of the noise [11]. As Bluetooth operates at a relatively high frequency, any in-band interference degrades quickly as distance increases, and even more rapidly through physical objects.

However, if the same device is utilizing both WiFi and Bluetooth, reducing the interference becomes more complex. Currently, collaborative techniques (such as alternating

<sup>&</sup>lt;sup>2</sup>Information described in this and the following two paragraphs was acquired from personal contacts in industry.

transmissions between Bluetooth and WiFi, or managing packet transmissions based on signal strength) and non-collaborative techniques (such as classifying the Bluetooth channels and altering the channel hopping algorithm to avoid noisy channels) are being investigated [11].

# **Chapter 3**

# DEMIS Problem Space Exploration through Measurements

To boldy go where no one has gone before!

Jean-Luc Picard

In this chapter, I provide measurements of several processors running different applications to provide insights about EMI and better understand the problem space<sup>1</sup>. As expected (and shown in previous work [15, 16]), running different processes on the same core will produce different EMI. My work shows and quantifies that small changes in the application may cause significant EMI shifts. I show that running the same application on two different chips causes very different EMI, to the point that an application can have almost no EMI in a core, and that very same application produces strong interference when running on another core. Al-

<sup>&</sup>lt;sup>1</sup>This work is part of my publication at The 50th International Symposium on Microarchitecture, October 2017 [23].

though some processors have the same RTL, if they are manufactured in different fabs, they may not produce similar EMI. Running the same application on different processors may yield vastly different EMI.

In particular, I show that the interaction between core, process, and application has a deterministic, but very unpredictable result in EMI interference for a given frequency band. I experimentally show that small architectural changes with small performance impact have a profound impact on EMI. The main contributions of this chapter are as follows:

- · Showing that EMI produced by the core is dependent on architectural parameters

- Measuring several real devices to quantify the EMI produced

- Presenting the problem of in-band radio frequency interference as a form of EMI to the computer architecture community

## 3.1 Setup

In this section, I describe the experimental setup used in order to determine the effect architectural parameters have on EMI, to clearly define the problem space my research addresses. This section also includes a description of the hardware used and the benchmarks that were executed.

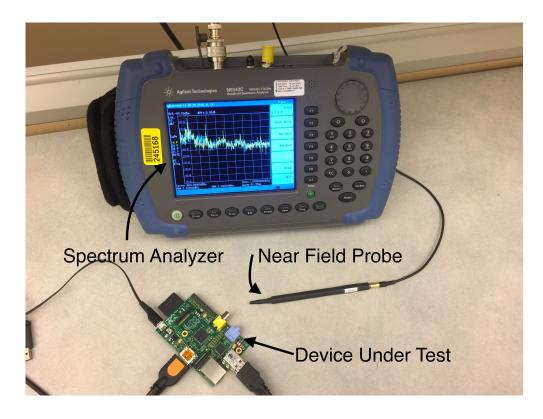

#### 3.1.1 Test Equipment

The measurements were taken using a Near-Field Probe set made by Keysight Technologies, which was attached to an N9342C Handheld spectrum analyzer from Agilent Tech-

| Device   | Commercial Name         | Processor        | ARM Core   | Operating System                |

|----------|-------------------------|------------------|------------|---------------------------------|

| A8_A10   | Allwinner A10           | Allwinner A10    | Cortex A8  | Ubuntu                          |

| A53_K620 | HiKey (LeMaker version) | Kirin 620        | Cortex A53 | Linaro                          |

| A11_PI2  | Raspberry Pi 2          | Broadcom BCM2835 | ARM11      | Arch Linux, Raspian (Dual Boot) |

| A53_C2   | ODROID-C2               | Amlogic S905     | Cortex A53 | Arch Linux                      |

| A15_XU4  | ODROID-XU4              | Exynos 5422      | Cortex-A15 | Ubuntu MATE                     |

Table 3.1: System specifications for each device measured.

nologies. This setup had a noise floor at -120dBm and all measurements were taken in a Faraday cage. The deployment is depicted in Figure 3.1. Additionally, I fixed the probe onto each device for consistency, as there can be a substantial differences in measured power when measuring different locations.

The relevant specifications of each of the five devices measured are provided in Table 3.1. One of each type of device was measured. The rest of this thesis will refer to the devices as in the first column of Table 3.1.

#### 3.1.2 Benchmarks

I measured each device while it was idling as well as while it was running a series of benchmarks. I utilized a set of in-house benchmarks, described in Section 3.2 and SPEC2006 [28] applications to determine if using architectural techniques would be effective for manipulating EMI in specific bands. From there, I utilized the SPEC2006 benchmarks to determine the effects on larger processes.

Each device ran all the benchmarks from the SPEC2006 benchmark suite<sup>2</sup> natively  $^{2}$ Due to compilation issues, gobmk, omnetpp, and xalancbmk were not included in this experiment.

Figure 3.1: I utilized a spectrum analyzer and near-field probes to accurately measure the EMI from multiple hardware platforms running a set of benchmarks.

during measurements with the default settings for each device (without modifying the clock speed, etc.) as a baseline. Then, the benchmarks were run when changing different architectural parameters, including compiler optimizations.

In the interest of avoiding repetitiveness, the results provided in this section focus more the mcf, sjeng, and libquantum benchmarks. These benchmarks were chosen because they emphasize specific architectural parameters: mcf is memory intensive, with many RAM accesses; sjeng causes many branch mispredictions and calculations; and libquantum triggers many cache misses and prefetching.

#### 3.1.3 Bands Analyzed

The noise was measured in the scope of wireless communication technologies and is reported as the difference between emitted power when running the benchmark and idling for five different RF communication frequency bands, described in Table 3.2.

Table 3.2: Wireless technology frequency ranges and maximum bandwidths used at a given time. This work will refer to each band as described in the first column.

| Band          | Technology                           | Lower Bound (MHz) | Upper Bound (MHz) |

|---------------|--------------------------------------|-------------------|-------------------|

| LTE 800 Lower | LTE band 18 (UL and DL)              | 815               | 875               |

| LTE 700       | LTE bands 12, 13, 14, 17 (UL and DL) | 699               | 798               |

| LTE 450       | LTE band 31 (UL and DL)              | 452.5             | 467.2             |

| SuperWiFi XR7 | Ubiquity XtremeRange7 WiFi           | 698               | 746               |

| SuperWiFi 600 | SuperWiFi in TV spectrum             | 600               | 630               |

# 3.2 Insights and Measurements

This section uses physical measurements of real systems to identify the effects of architectural and compiler parameters on RF interference. Through measuring in-house benchmarks on the hardware described in Table 3.1, I was able to determine that different parameters affect the RF interference differently. This section will describe my findings from measuring the differences in interference when applying different architectural manipulations.

#### 3.2.1 Measurement Repeatability and Accuracy

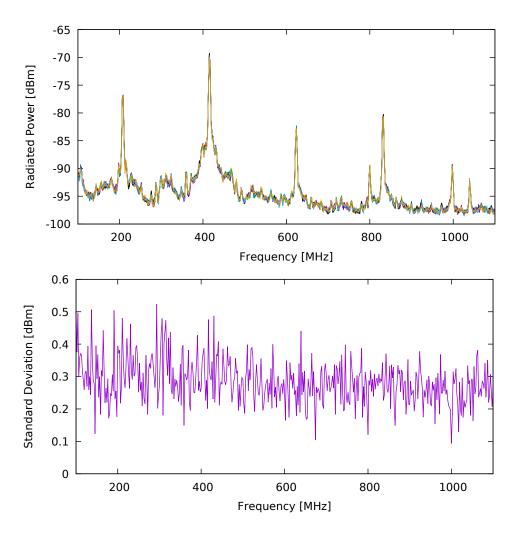

In order to ensure that the measurements taken are consistent, I measured the A53\_K620 running the mcf benchmark 12 times. The results are provided in Figure 3.2.

Figure 3.2: The EMI created by the A53\_K620 running the mcf benchmark is consistent across multiple measurements. These measurements were taken on at different times on different days. The standard deviation of the radiated power across these measurements is negligible in comparison to the total EMI.

As we can see, the measurements are repeatable across different days and times, with a maximum standard deviation of about 0.5*dBm*, a value that is a negligible amount compared to the measured power. Therefore, the rest of the measurements provided throughout this document will be presented without an error threshold.

#### **3.2.2** Compiler Impact on EMI

To evaluate small binary changes impact on EMI, I use different compilation options (different schedulers or optimizations) that should have small performance impact to see the EMI effect. For example, using the -O2 or the -O3 compilation options, or changing the scheduling using the -mtune option.

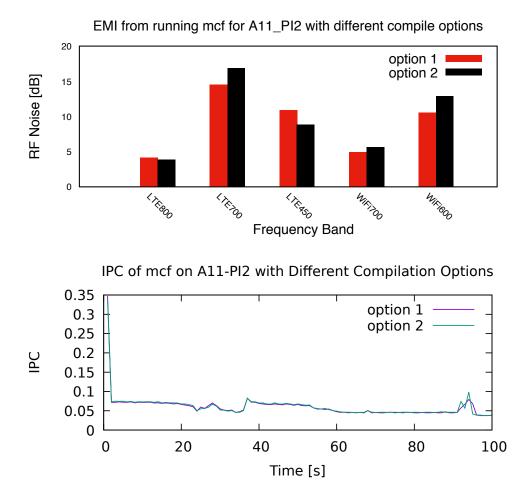

Figure 3.3 shows the interference level and the IPC for the first 100 seconds of execution of mcf when executed on the A11\_PI2. The IPC plot shows that the performance does not change when switching from -O2 (option 1) to -O3 (option 2) for mcf. Nevertheless, we see over 3dB interference reduction in the most noisy band (LTE 700) using -O2, while the LTE 450 band has an increase in interference with -O3. This means that for the mcf application, if we want to avoid interference in the LTE 450 band we should use -O3, whereas -O2 should be used if the communication is in the LTE 700 band.

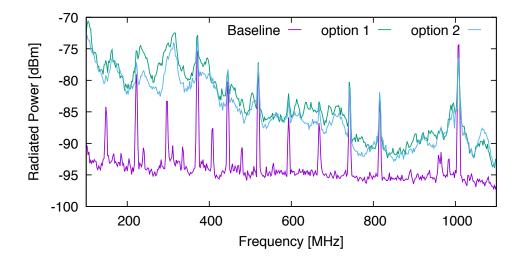

I repeated the same experiment on the A8\_A10 platform to understand the impact of hardware changes. The interference levels across the spectrum are shown in Figure 3.4, which also shows the baseline interference level when the core is powered on, but idle. Unlike in the A11\_PI2 case, the -O2 improves interference compared to the -O3 option for both LTE 700 (by 2dB) and LTE 450 (by 3dB). Again, for mcf the -O2 and -O3 does not significantly change the performance in this platform.

To analyze its impact on another application, Figure 3.5 depicts the EMI of the A53\_K620 processor running the sjeng benchmark after being compiled -O3 and -O2. In this case, the -O3 compilation option yields a 1% speedup. The interference shifts in frequency

Figure 3.3: Running mcf with different compile options on the A11\_PI2 yielded minimal difference in IPC, while still yielding a 3*dB* swing in maximum EMI at certain bands.

slightly, and in most cases the -O3 has a higher EMI. For this board mcf showed a similar behavior as sjeng with -O2 having less interference.

Figure 3.6 shows the case that only -mtune option is changed for hmmer application. I keep the default -march=native, which implies -mtune=native, and change the -mtune to cortex-a57. In this case, it has no performance difference when executing in the A11\_PI2. The plots shows another case of clear shift in the frequency around 600MHz with little performance

Figure 3.4: Different compilation options change the EMI in the mcf benchmark on the A8\_A10 processor without performance impact.

impact.

Figure 3.5: When running sjeng on the A53\_K620 processor, the EMI being produced changed based on the optimization the benchmark was compiled with.

The maximum interference reduction for the 5 analyzed bands playing with -O2, -O3 and -mtune options was 8dB in the bzip2 benchmark (not shown in the plots). Also, as expected,

the compilation options can have a big performance impact. For example, in bzip2 the -mtune has over 30% improvement when applied in the A15\_XU4 board (also not shown). For the applications of these findings, I exclude the cases with high performance impact.

Figure 3.6: Compiling hmmer with different -mtune options has no performance impact but a change in EMI.

In an attempt to further understand the effect of the compiler on the EMI, we performed an exhaustive set of measurements on the A53\_K620 board. I measured the EMI across multiple bands, disabling only one minor optimization from the full -O3 optimizations at a time. There are 11 gcc flags that differentiate between -O2 and -O3 with gcc 6.3.1.

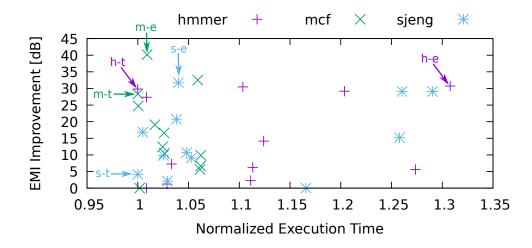

Figure 3.7 shows the normalized execution time versus the normalized EMI for LTE 700 for each of the compilation options. Each dot corresponds to the -O3 optimization with one of the 11 flags disabled. Since we also keep the -O3 optimization, there are 12 points per benchmark. The x-axis shows execution time normalized to the fastest execution for that benchmark, and the y-axis shows the EMI improvement with respect to the worst EMI for LTE 700 in dB. Unfortunately, I was unable to discern a consistent correlation between optimization,

Figure 3.7: In-band EMI in the LTE 700 band emitted by the A53\_K620 board with respect to execution time. I was unable to find a correlation between efficiency and EMI.

runtime, and EMI. For example, disabling the fgcse-after-reload optimization has a 40 dB EMI reduction with small slowdown for mcf, but only a 2 dB EMI reduction for hmmer, and 9 dB for sjeng (both also with small slowdowns).

In Figure 3.7, the points marking the fastest runtime and best EMI improvement are marked for each benchmark. For the hmmer benchmark, the point marked "h-e" for best EMI improvement ran with the fpeel-loops optimization disabled, and had a 1 dB improvement over the fastest run (marked "h-t"), which had the ftree-partial-pre optimization disabled. In the case of this benchmark, there is a 0.3x slowdown between the best EMI and the fastest execution time. The mcf benchmark ran fastest with the ftree-loop-vectorize optimization disabled ("m-t"), but with a 0.009x slowdown, disabling the fcse-after-reload optimization (marked "m-e") offered a 12 dB improvement. Lastly, the sjeng benchmark ran fastest with fpredictive-commoning disabled ("s-t"), but disabling the ftree-slp-vectorize optimization ("s-e") offers over 25 dB improvement with only a 0.03x slowdown.

Clearly, there is no correlation between the optimizations that is standard across benchmarks, even across different bands, there is no discernible relationship. Although potential for future work, we decided not to use multiple binaries, and we restrict ourselves to just -O2 vs -O3 in the rest of the thesis. Keeping many binary files would take up an excessive amount of space and raise tune/selection algorithm issues.

<u>The main conclusion</u> is that by adjusting the compilation options and constraining cases to a small performance impact, we can achieve up to 8dB interference reduction levels with many cases providing 3dB reduction. A source of difficulty managing the system is that the effect is not only compiler dependent but compiler/core/platform dependent. The same compilation options yield opposite results in different processors.

In Chapter 6 (which directly applies the techniques discussed in this chapter), when compiler techniques are mentioned, I mean to change the compiler options (-O2/-O3/-mtune) and select the binary with the lower interference in the band to protect. Although not covered, a JIT based system would be the best platform allowing to dynamically perform small binary changes to mitigate interference while monitoring the interference level impact.

#### 3.2.3 Benchmark Impact on EMI

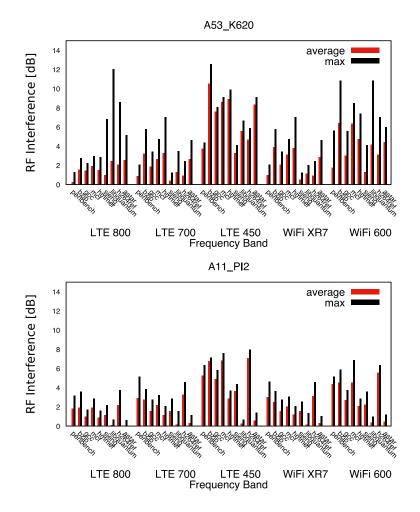

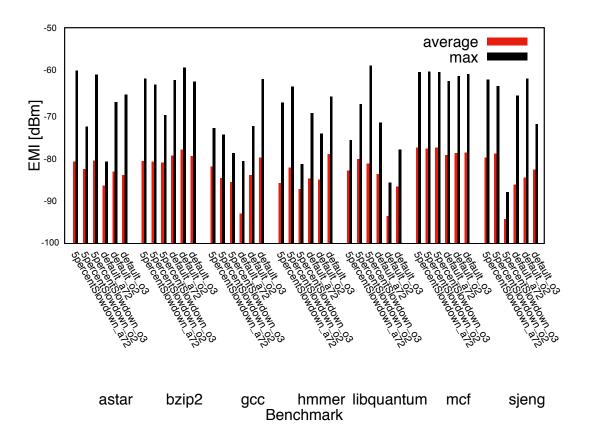

Clearly, EMI is different depending on the application [15, 16]. However, EMI also changes on a per-band basis. Figure 3.8 shows the average and maximum EMI in the five different RF bands on the A53\_K620 and the A11\_PI2. The interference depicted is the difference between emitted power when running the benchmark at each frequency with respect to an idling processor. However, it is hard to see a relationship between the in-band interference and

Figure 3.8: Interference created in each band running SPEC2006 benchmarks on the A53\_K620 and the A11\_PI2, without the base EMI created by the processors running only the operating system.

benchmark that is consistent across processors.

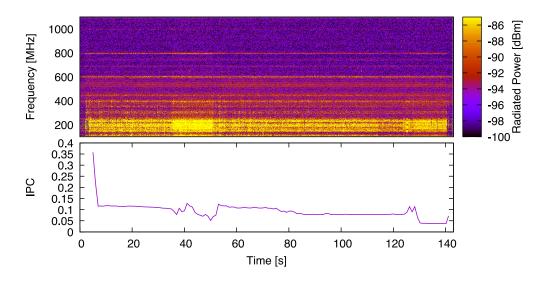

Thus far, all the measured data presented in this thesis have been the average of interference per frequency over a sustained amount of time. However, many programs go through different phases during execution. As the different phases tend to run different types of instructions, it stands to reason that the radiation at different frequencies will be different during different phases.

Figure 3.9: IPC and EMI for mcf on A11\_PI2. The processor goes through phases with different EMI patterns. In this case, it seems that when there is lower IPC, there is more EMI.

Figure 3.9 shows these phases as the mcf benchmark is run on the A11\_PI2 processor over time, the interference is shown as a color map per frequency and time. Interestingly, as the IPC decreases, there appears to generally be more RF emanations. From these results it is not clear why this behavior happens, but it could be related to changes in processor activity.

Figure 3.10 depicts the IPC and phases of the A53\_K620 processor running the sjeng benchmark. In contrast to the A11\_PI2 running mcf, in many cases the A53\_K620 has more interference when the IPC is higher for the sjeng benchmark. Nevertheless, the clear EMI fluctuations are related to IPC changes but it is not a direct function of IPC because sometimes higher IPC means lower interference in some bands (which can be seen in in the LTE 800 Lower band in Figure 3.10.

In addition to only observing the phases per benchmark, I also performed some measurements over time with different input sets. Although the different input sets caused each benchmark to spend different amounts of time in each phase, the EMI during each phase re-

Figure 3.10: For the sjeng benchmark on the A53\_K620, it is more clear that the processor goes through phases with different EMI patterns. When compared with the IPC, there is no clear higher/lower EMI correlation, just change.

mained unchanged for the benchmarks measured in this thesis.

<u>The main conclusion</u> is that there are clear program phases in IPC and EMI as the application executes, but the IPC phases are not necessarily correlated with EMI phases. Although sometimes an IPC increase results in an EMI increase, in many phases an IPC increase results in an EMI reduction. Adapting through phases has potential benefit and the phases can be detected with IPC phase changes.

#### **3.2.4** Cache Impact on EMI

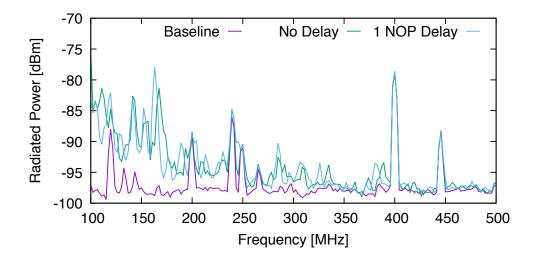

Cache accesses consistently affect the amount of RF interference being emitted by each chip. In order to observe how cache accesses affected the RF interference created by each processor, we utilized a synthetic program that emphasizes accessing a large 2D array and injected a delay before the cache misses (Listing 3.1).

Listing 3.1: Function for testing code with frequent cache accesses. Delays (nop calls) were inserted at line 5. The numbers in lines 3 and 4 were manipulated based on the cache sizes for each processor in order to ensure the desired cache misses were occurring (L1 or 2).

The first thing I noticed was that there was a distinct difference in frequency and amplitude between L1 and L2 cache accesses, as shown in Figure 3.11, which I determined by manipulating lines 3 and 4 in Listing 3.1. Clearly, L2 cache accesses trigger more interference than L1 cache misses, presumably because an L1 cache access (miss) is required for an L2 cache access to trigger. However, at some frequencies L1 cache accesses are noisier, which may be attributed to the fact that L2 caches are slower and would therefore interfere with different frequencies. Unfortunately, a processor would take a huge performance hit should it forgo accessing the L1 cache in favor of the L2 cache, so I focused on techniques that would take less

Figure 3.11: The interference created by accessing the L1 and L2 caches on the A8\_A10 processor is significantly different.

critical performance hits, despite the EMI benefits.

Figure 3.12: The interference created by accessing the L1 cache with and without delay on the A8\_A10 processor is significantly different.

Instead of switching which cache to access, I tried injecting a minimal delay before accessing the L1 cache by uncommenting line 5 in Listing 3.1. When I delayed the cache

Figure 3.13: By changing the SDRAM speed for the A11\_PI2, I was able to move the noisy peaks in frequency.

access slightly, I was able to reduce the interference, as shown in Figure 3.12. Clearly, there is a significant affect on the frequency response of the device: consistently a frequency shift of about  $15MH_z$ . Injecting this minimal single nop delay was able to trigger a significant response, where the power spike has moved more than a Bluetooth channel and most LTE channels.

<u>The main conclusion</u> is that caches have a big impact in delay and misses in the L2 tend to have a higher impact at lower frequency bands. Although this has potential to be a good technique, the DEMIS technique in Chapter 6 does not trigger cache delays or misses, I was constrained to measurements in real systems; it is not clear how to introduce affect cache behavior at runtime without RTL access.

#### 3.2.5 Memory Impact on EMI

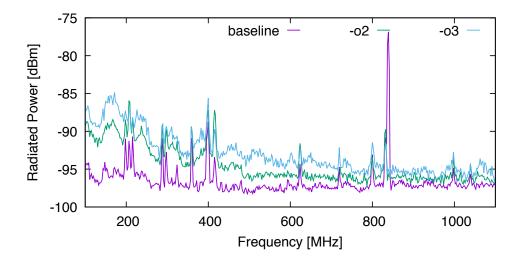

On the A11\_PI2, modifying the DRAM speed was a simple matter of modifying the BIOS parameters. I measured the EMI when the processor was running nothing but the OS. As

shown in Figure 3.13, modifying the sdram\_freq parameter in the config.txt file that serves as boot settings for the A11\_PI2 changes the frequency of certain noisy spikes when idling.

These frequency spikes appear to be directly caused by memory accesses because they occur at the DRAM frequency and at its harmonics. When the DRAM frequency was shifted to 360MHz, I was able to see the spikes shift accordingly: from 400MHz to 360MHz, and from 800MHz (the first harmonic) to 720MHz.

I measured the EMI produced by the A11\_PI2 with the default DRAM speed of 400 MHz as well as with a 10% slower speed of 360*MHz*. This time, however, I took these measurements while running the mcf and sjeng benchmarks. The results of these measurements are presented in Figure 3.14. The libquantum benchmark produced negligible EMI on the A11\_PI2 processor, so the results are omitted.

Reducing the DRAM decreases interference by *3dB* in the SuperWiFi 600 band, but adds a spike in the SuperWiFi XR7 band for the mcf benchmark. However, the default settings have less interference in the SuperWiFi XR7 band and more interference in the SuperWiFi 600 band for the same benchmark, so depending on what type of WiFi is being used, different DRAM speeds are better for this application.

Similar effects can be seen for the sjeng benchmark as well. For example, the default DRAM speed is better for the SuperWiFi XR7 and worse for the LTE 700 frequency bands than the slower DRAM speed.

<u>The main conclusion</u> is that DDR creates big spikes in interference. Even when the processor is idle there are big spikes because the DDR clock is kept running. If the band in use is affected by DDR, the only solution is to shift the DDR operating frequency. For the analyzed

Figure 3.14: When running the mcf and sjeng benchmarks on the A11\_PI2, changing the DRAM speed as little as 10% has a significant impact on EMI.

cases, small 10% DDR frequency change is enough to move the spikes out of most bands. For many benchmarks like sjeng, this has no performance impact but some benchmarks like mcf are very sensitive resulting in a 10% performance impact.

The DDR clock is one of the strongest EMI spikes I observed, even stronger than the processor clock. The reason is that processor clocks have a more effective modulation of the

clock signal. Future DDR designs may want to consider a better clock modulation requirement.

#### 3.2.6 Execution Core Impact on EMI

As seen in Figure 3.8, even the same benchmark will emit different EMI when run on different processors. Therefore, I launched a more specific investigation on the impact the execution core itself has on EMI.

```

1 int main () {

2 int total = 0;

3 for(int k=0;k<10000;k++) {

4 for(int i=1;i<10000;i++) {

5 total += k/i;

6 //asm("nop");

7 }

8

9 }

10 printf("total=%d\n",total);

11 }</pre>

```

Listing 3.2: Function for testing computation heavy code. This code was used for testing the FPU by changing all data types from int to float. Delays were added by uncommenting line 6, and adding as many nops as desired.

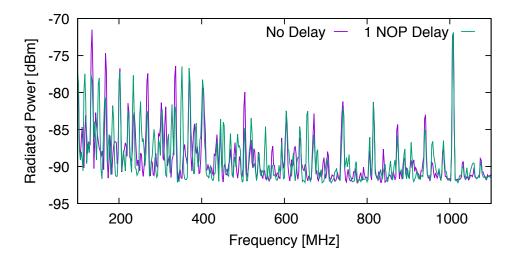

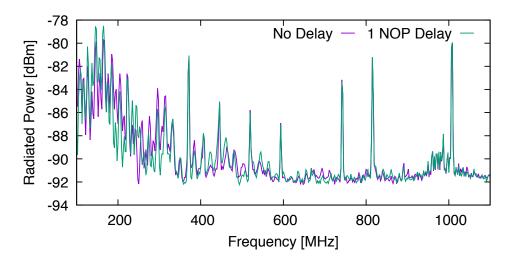

In order to test the interference generated from using the FPU, I performed multiple divisions, once using the int data type and once using the float data type. The source code for the benchmark used is in Listing 3.2 in the A8\_A10 hardware.

I noticed a substantial difference in EM radiation between the two test cases on the

Figure 3.15: When utilizing the FPU as opposed to doing simply integer calculations on the A8\_A10 processor, there was much less RF interference. Furthermore, different frequencies were affected differently.

Figure 3.16: RF interference created when performing integer calculations on the A8\_A10 processor. The frequency response differs with the addition of a single nop in the loop.

A8\_A10 as in Figure 3.15. Not only did the interference decrease, but I also observed that the lower frequencies tended to exhibit a more consistent interference during floating-point calculations, whereas higher frequencies observed consistently more interference from integer-

only calculations.

By injecting even a single nop into the calculations (uncommenting line 6 in Listing 3.2), I was able to observe a distinct difference between frequency responses for both integer calculations and floating point calculations as seen in Figure 3.16.

Figure 3.17: RF interference created when performing floating-point operations on the A8\_A10 processor. The frequency response differs with the addition of a single nop in the loop.

As the interference generated from the integer calculations exhibited frequent changes in power in each frequency, it is easy to determine that the power spikes undergo a frequency shift when one nop is injected into the code. Furthermore, the frequency spikes tend to have less power in the benchmark with a delay by almost 7dB in the lower bands and 5dB at higher frequencies. The measured power is presented in Figure 3.16.

Figure 3.17 shows the difference in frequency responses when running the floating point benchmark with and without a nop delay. As opposed to the integer calculations, the floating point calculations have wide-band low-frequency interference. However, by injecting a nop into the inner for loop, I was able to move the interference to different frequencies.

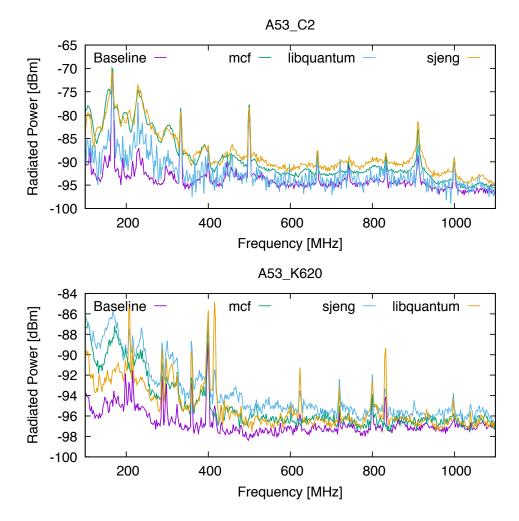

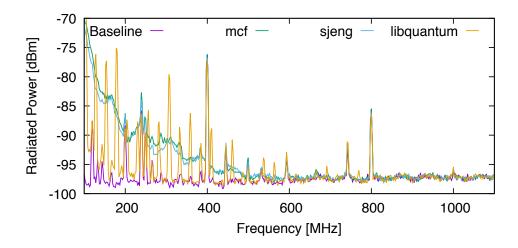

Figure 3.18 shows the radiated power from the A53\_C2 and A53\_K620 processors when running the three benchmarks without changing any of the default settings on the boards. The benchmarks were compiled without any optimizations. It is clear in these two figures that each benchmark yields a distinct radiation pattern on each processor. Also, the benchmarks tend to behave similarly across processors. As the processors all run at different frequencies, we expect some variations, but in general it is clear that specific architectural components produce distinct interference patterns.

It is important to note that the A53\_C2 and the A53\_K620 processors are fabricated from the same RTL in the same fab and process node. Therefore, it is surprising that the EMI is so different between the two processors.

Additionally, on the A53\_C2 processor, the libquantum benchmark produces less interference than sjeng, but on they are switched on the A53\_K620 processor. I found this to be quite common throughout our investigation.

I was also able to measure these benchmarks on an out of order (OoO) processor, the A15\_XU4 which features four OoO cores and four in-order cores. The results are provided in Figure 3.19. Interestingly enough, the OoO core appears to only emit noticeable radiation in frequencies less than 600MHz, which is below most wireless communication bands. However, running the libquantum benchmark introduces multiple 10dB spikes into the LTE 450 band, which could cause significant connectivity degradation.