# **Lawrence Berkeley National Laboratory**

**Lawrence Berkeley National Laboratory**

# Title

AN ULTRAFAST FOURIER TRANSFORM PARALLEL PROCESSOR

## **Permalink**

https://escholarship.org/uc/item/7k6746xv

#### **Author**

Greenberg, W.L.

# **Publication Date**

2013-06-27

# Lawrence Berkeley Laboratory

UNIVERSITY OF CALIFORNIA

OCT 21 1981

LIBRARY AND DOCUMENTS SECTION

AN ULTRAFAST FOURIER TRANSFORM PARALLEL PROCESSOR

William L. Greenberg (Ph.D. thesis)

April 1980

# For Reference

Not to be taken from this room

Ponner Laboratory

Biology &

Madicina

Division

#### LEGAL NOTICE

This book was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

#### AN ULTRAFAST FOURIER TRANSFORM PARALLEL PROCESSOR

William L. Greenberg

Ph.D. Thesis

April 1980

Department of Electrical Engineering & Computer Science and

Biology and Medicine Division Lawrence Berkeley Laboratory University of California Berkeley, CA 94720

This work was supported by the U.S. Department of Energy under Contract W-7405-ENG-48 and the National Institutes of Health.

|  |  | Ta. |

|--|--|-----|

|  |  |     |

|  |  |     |

|  |  |     |

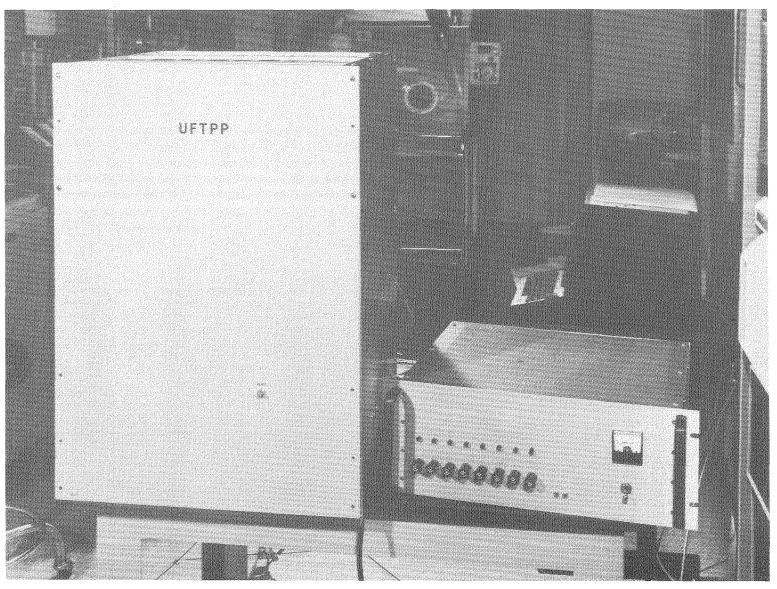

CBB804-4796

|  |  | 1<br>1<br>1<br>1<br>1                 |

|--|--|---------------------------------------|

|  |  | 1<br>1<br>1<br>1<br>1                 |

|  |  | 1<br>3 1<br>1<br>- 1<br>2 1           |

|  |  | 1<br>1<br>1<br>1<br>1<br>1            |

|  |  |                                       |

|  |  |                                       |

|  |  |                                       |

|  |  | e e e e e e e e e e e e e e e e e e e |

|  |  |                                       |

|  |  |                                       |

#### ABSTRACT

#### AN ULTRAFAST FOURIER TRANSFORM PARALLEL PROCESSOR

William L. Greenberg Ph.D.

Department of Electrical Engineering & Computer Science and Donner Laboratory (Biomedical Division of Lawerence Berkeley Laboratory) University of California, Berkeley, CA 94720 Sponsors: Department of Energy and the National Institutes of Health

A new, flexible, parallel-processing architecture is developed for a high-speed, high-precision Fourier transform processor. The processor is intended for use in 2-D signal processing including spatial filtering, matched filtering and image reconstruction from projections.

The flexible architecture is developed from the fully parallel architecture proposed by Pease. It is shown that the "perfect shuffle" data routing used by Pease may be used in a serial processor by use of a perfect shuffle generating function which generates the output address of each datum from its input address. Further development of this idea shows that the simplified architecture allowed by use or the perrect shuttle lends itself well to pipelining to effect horizontal parallel processing and increase execution speed. Finally, it is demonstrated that several (up to N/r, where N is transform size and r is the radix of the transform) pipelined arithmetic units may be put in parallel operation to further increase the speed of transform computation. Important design parameters such as the radix of the transform, number of arithmetic units, number representation and word size are examined with respect to their effect on accuracy, dynamic range, transform computation speed and memory fragmentation.

The Ultrafast Fourier Transform Parallel Processor (UFTPP) architecture is compared and contrasted with the classical architectures (serial, cascade, parallel and array) and is shown to have considerable advantages in most cases.

To demonstrate the feasibility of implementation of a processor designed using this architecture, a one-arithmetic unit version has been constructed which can compute up to a 4096 complex point transform with maximum throughput of 500,000 samples per second. A software system was also implemented that uses the UFTPP to perform 2-D spatial filtering, execute matched filtering between a scene and a template and reconstruct images from their projections using the Backprojection of Filtered Projections (BFP) reconstruction algorithm. Two new techniques for determining filters to be used with the BFP algorithm are cited. The first new filter, proposed by Gullberg, incorporates attenuation correction of emission data from Computer Assisted Tomography (CAT) studies into the reconstruction operation. The second, proposed by Tsui, uses a stochastic filter to allow considerable dose reduction in CAT. Both require computation of a large number of Fourier transforms and are excellent applications for a high speed processor such as the UFTPP.

In summary, the outstanding characteristics of the UFTPP are:

- (1) A pipelined "butterfly" computation module

- (2) Flexible parallel processing architecture easily expandable to achieve extremely high speeds.

- (3) Use of recently available LSI multiplier chips

- (4) Use of the "perfect shuffle" data routing algorithm

- (5) Extremely simple control logic

- (6) Low cost

Approved:

Chairman, Dissertation Committee

# TABLE OF CONTENTS

| 1.0   | Introduction                                           | ٠   | ٠ | 0 | 0 | ]  |

|-------|--------------------------------------------------------|-----|---|---|---|----|

| 1.1   | Previous Work                                          | 0   |   | 9 | 9 | 1  |

| 1.2   | New Work                                               | 0   | 0 |   | 9 | 3  |

| 2.0   | FFT Derivation and Modification                        | •   | ٠ | • | • | 8  |

| 2.1   | Cooley-Tukey FFT Derivation                            | ۰   | Ð | ٠ | • | 8  |

| 2.2   | FFT Modification for Parallel Processing               | 0   | • | o | 6 | 10 |

| 2.3   | The Perfect Shuffle Generating Function                | 9   | • | ь | 9 | 15 |

| 3.0   | Architecture                                           | •   | 0 |   | 8 | 20 |

| 3.1   | Arithmetic Unit Implementation for Different Radices   | 9   | • | ø | • | 20 |

| 3.2   | Perfect Shuffle Data Handling                          |     | 6 | 9 | ۰ | 23 |

| 3.3   | Pipeline Architecture for UFTPP (Horizontal Parallel   |     |   |   |   |    |

|       | Processing)                                            |     | ə | 6 | ٠ | 24 |

| 3.4   | Multiple Arithmetic Units (Vertical Parallel Processin | ıg) |   |   |   | 26 |

| 3.5   | Comparison of the UFTPP Architecture with Other        |     |   |   |   |    |

|       | Architectures                                          | ٠   | 9 |   | • | 29 |

| 4.0   | Number Representation & Arithmetic                     | •   | ۰ |   | • | 32 |

| 4.1   | Fixed Point vs. Floating Point Representation          | e   |   | 0 | Ð | 32 |

| 5.0   | Processor Implementation                               | •   | е | 0 | 0 | 41 |

| 5.1   | Overall System Description                             |     | • | 0 | 0 | 41 |

| 5.2   | The Arithmetic Unit                                    | c   | • | 9 | ø | 43 |

| 5.3   | The Memory System                                      | e   | • | o | 0 | 49 |

| 5.4   | The Multiplexer System                                 | G   | 0 |   | e | 52 |

| 5.5   | The Pipeline                                           | 0   |   | • |   | 55 |

| 5.6   | Overall Timing and Control                             | 0   | • | o |   | 56 |

| 5.6.1 | l The Perfect Shuffle Address Generator                |     | 6 |   |   | 57 |

| 5.6.2 Control/Status Register and the N - Register | er       | •          |     | ٥   | ۰ | 9 | 9 | 57 |

|----------------------------------------------------|----------|------------|-----|-----|---|---|---|----|

| 5.6.3 The Iteration Counter                        |          | •          | о е | 9   | • | в | 0 | 58 |

| 5.6.4 The Finite State Generator                   |          | 0          |     | ۰   | 0 | o | 0 | 58 |

| 5.6.5 Memory Counter                               | •        | •          |     | 6   | • | 0 | 9 | 59 |

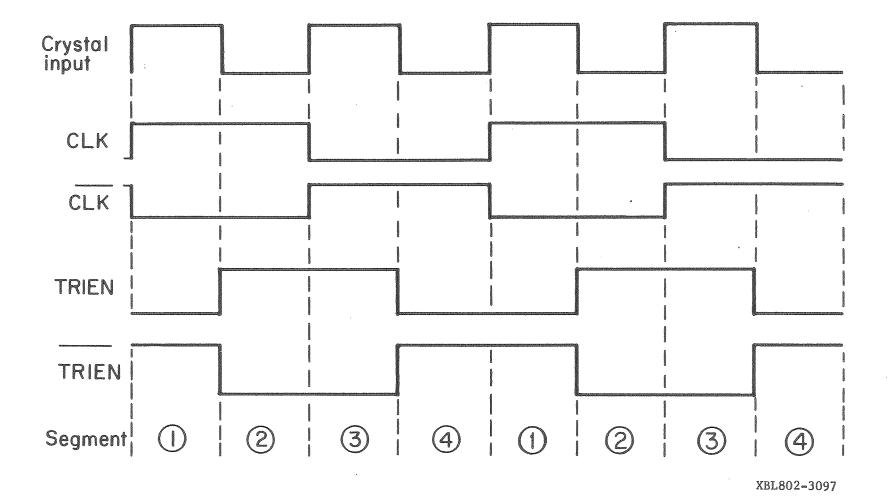

| 5.6.6 Clock Generation and Distribution            | <b>5</b> | <b>0</b> 1 | e 6 | . • | o | 6 | o | 59 |

| 5.7 Computer I/O Interfaces                        | 9        |            | e o | 9   | • | ۰ | ۵ | 61 |

| 5.8 Computer Operation and I/O                     | •        | •          |     | 0   | ٠ | 0 | 0 | 63 |

| 5.9 Implementation Costs                           | •        |            | 0 9 | 0   | 6 |   |   | 64 |

| 6.0 Applications                                   | 0        | •          | 9 0 | 0   | 0 | ۰ | 0 | 65 |

| 6.1 Implementation                                 |          | 0 (        |     |     | 6 |   | 0 | 65 |

| 6.2 Image Processing Applications                  | e ·      | 9 ,        | e 0 | 0   | ۰ | ۰ | 0 | 65 |

| 6.2.1 High & Lowpass Filtering                     |          | e :        | 0 0 | a   | o | o | 9 | 65 |

| 6.2.2 Matched Filtering                            |          | 9 1        | o   |     | e | ۰ | 0 | 67 |

| 6.3 Image Reconstruction from Projections          |          | 0 1        | o e | 0   | • | 0 | ۰ | 70 |

| 7.0 Conclusion                                     | a (      | • •        | o o | 0   | • | • | e | 78 |

| REFERENCES                                         |          |            | a a | e   | ۰ |   |   | 81 |

#### ACKNOWLEDGEMENT

I would like to thank Professor Thomas F. Budinger for his invaluable advice, encouragement and support in what sometimes seemed like a never ending endeavor. His confidence in me provided the momentum to carry me over the "inertia" barriors and pushed me to strive for excellence. For this I am truly grateful.

I would also like to thank Professor Martin Graham for lending his hardware expertise to the solution of some of my worst problems and Profesor Walter Freeman for his valuable comments at the thesis stage.

Certainly the least formal, but possibly some of the most valuable comments on the project were received in conversations with Drs. Ron Huesman and Steve Derenzo and Mr. John Cahoon.

Probably the most time consuming portion of this project was the actual wiring of the circuit boards. I would like to express my deep appreciation to my "technical support" group": Mimi Winer, Peggy Eisenbach, Valerie Budinger, Jamie Halpern and Kelly Finnerty (all of whom donated their time). I would also like to thank Mimi and Peggy for their help in preparation of the thesis.

In addition to her technical assistance, I would like to thank Mimi for her incredible patience and support in our relationship which sufferred the brunt of my frustration on many occasions.

Finally I would like to express my deep gratitude to the entire Research Medicine group at Donner Laboratory for providing me with the excellent experience in scientific research that I have gained during the past 4 3/4 years. Further, in all sincerety, the comaraderie among the members of the group has made the job truly enjoyable. The friendships I have developed will be sorely missed.

This work was supported by the U.S. Department of Energy under Contract W-7405-ENG-48 and the National Institutes of Health.

#### GLOSSARY OF TERMS

- Array architecture a Fourier transform processor architecture with  $N/r \log_r N$  arithmetic units. After a latency of  $\log_r N$  cycles, a new transform is completed every cycle. Data routing may be by the Cooley-Tukey algorithm or by the perfect shuffle algorithm. The transforms are fixed length.

- "Butterfly" operation the basic computation performed in Fourier transformation consisting of a complex multiplication followed by a complex addition and a complex subtraction. The name is derived from the patterns present in the signal flow diagrams of the Fourier transform.

- Cascade architecture a Fourier transform processor architecture containing m=log\_N arithmetic units arranged sequentially. The output from an arithmetic unit becomes the input to the next. A given unit processes points separated by r<sup>-i</sup> where i is the position of the arithmetic in the cascade. After a latency of N cycles, frequency coefficients begin to emerge from the output one per cycle. From this point on computation may be continuous. A new time or space sample may be input each cycle and a new frequency coefficient read from the output each cycle. The size of transforms computed is fixed.

- Parallel architecture a Fourier transform architecture with N/r arithmetic units. Transforms are computed every log<sub>r</sub>N cycles. Data routing is via the perfect shuffle algorithm. Size of the transform is fixed.

- Perfect shuffle -- an algorithm used for pairing the correct data values at each iteration in Fourier transform computation which maintains a uniform manipulation of data throughout all iterations as opposed to the Cooley-Tukey data routing which changes

at each iteration. It is called the perfect shuffle since it is similar to shuffling a deck of playing cards.

- Serial architecture an FT processor architecture containing one arithmetic unit. It processes the data exactly as the Cooley—Tukey algorithm. A transform is computed in N/r  $\log_r$ N cycles. It can be set up to process variable length transforms.

- "Twiddle factor" -- in the butterfly operation one of the complex inputs is a value composed of a cosine term in the real part and a sine term in the imaginary part. This complex value, known as the "twiddle factor" multiplied times one of the input data values.

- UFTPP architecture -- a flexible Fourier transform processor architecture with a variable number of arithmetic units which computes a transform in

$$\frac{N}{r}$$

·  $\frac{\log_r N}{P}$  cycles.

P is the number of arithmetic units. May be programmed to compute different length transforms. The maximum number of arithmetic elements is N/r.

#### CHAPTER 1

#### INTRODUCTION

Fourier analysis has long been recognized as a major technique of signal processing for accomplishing such tasks as filtering, cross-correlation, auto-correlation, power spectrum deternmination, and other computations involving frequency domain manipulations. Prior to the advent of digital computing machines, most Fourier analysis was done by analog methods. When calculating machines and computers began to become available, discrete methods for calculation of spectra became important. The discrete Fourier transform has long been known to mathematicians and engineers as an algorithm which computes the discrete spectrum of a sampled time or space varying signal at a speed proportional to  $N^2$  (where N is the number of complex points in a transform). In 1965, Cooley and Tukey published their now famous paper [18] which gave an algorithm for computation of discrete spectra in a time proportional to N log, N. This algorithm, now known as the Fast Fourier Transform (FFT), had been in use in various forms as early as 1904, but was not widely known until the Cooley-Tukey rediscovery in 1965.

The N log<sub>2</sub>N speed of the Cooley-Tukey algorithm showed a huge increase in efficiency over the N<sup>2</sup> algorithms; but even digital computers could not perform this number of operations fast enough to allow real-time computation (i.e. to compute a transform in the same amount of time as it takes to acquire the N sample points). This thesis gives a method for accomplishing the FFT on large data arrays using a hard-wired processor.

#### 1.1. Previous Work

Almost immediately after the Cooley-Tukey algorithm was published, engineers began to explore designs for its implementation in a dedicated processor which had a cycle time short enough to allow real-time computation to be realized. Over the past ten years a great body of literature has accumulated in the area of hardware FFT processors. Initially, brute force approaches produced serial

architectures [3,5,6,62] that iteratively processed the input data exactly as the software that preceded them. Subsequently, the serial architecture was improved to the cascade architecture, sometimes called a pipeline [5,6,37] (the term "pipeline" here is different from the pipelining technique for increasing execution speed that will be discussed). The cascade architecture contains  $m=\log_2 N$  stages each of which processes data in blocks of  $r^{(m-i)}$  ( $1 \le i \le m$ ). The advantage of this architecture is that samples can be fed continuously into the input end and at fixed time later the transformed values emerge.

Parallel and array processor architectures which are faster than those just mentioned have been proposed by Pease [48] and Bergland [7]. However, these are much more complex and much more expensive due to the large amount of hardware necessary for their implementation.

One major obstacle impeding all of these architectures was the time and hardware complexity in performing multiplication of complex numbers. Algorithms for determining the product of two binary numbers were well known, but relatively slow compared to the desired cycle times of the processors. Several ingenious techniques were developed to avoid direct multiplications, notably the CORDIC technique [71] used by Despain [26] and a somewhat similar technique developed by Liu and Peled [45]. These schemes rely on bitwise generation of the products through various algorithms. Recently, LSI multiplier chips have become available commercially. These chips function at high speed and are relatively inexpensive in comparison to the cost of parallel implementations of the bitwise algorithms just mentioned. These chips remove the obstacle that the alternate techniques were trying to circumvent.

Other algorithms due to Rader and Brenner [57] and Winograd [74] have been developed which convert the complex multiplications into pure real or pure imaginary operations. While these are excellent techniques in architectures where multiplications are relatively expensive (in terms of time or hardware), the LSI multipliers make them less attractive than algorithms such as will be proposed in this

thesis. The Winograd algorithm does not generate a scheme which allows reduction of hardware when the complex multiplications are done as a parallel operation since some of the operations are between two real numbers, some between two imaginaries and some between a real and an imaginary.

The design put forth in this proposal is based in good part on algorithmic concepts by Pease. Others [34,36,70,73] have discussed hardware implementations using Pease's ideas, but none has recognized its true flexibility and possibilities for modularity. Also, Corinthios [20,21,22] has used the formalism of Pease to implement an algorithm (previously noted by Cochran, Cooley, et. al. [16]) which does not produce the output in bit reversed order. However, the shuffle operation which affects data routing is different for each iteration of the transform, and the associated control circuitry is more complicated.

#### 1.2. New Work

This thesis presents a new hardware implementation of a modification of the FFT algorithm. The processor exhibits the following characteristics:

- 1) A pipelined "butterfly" operation computation module

- 2) Parallel processing architecture easily expandable to achieve very high speeds (e.g. computation of a 60 million point transform in 10 seconds).

- 3) Use of recently available LSI multiplier chips.

- 4) Use of a "perfect shuffle" operation to accomplishing data routing.

- 5) Extremely simple control logic

- 6) Low cost

The intended application areas for the specific processor which was constructed as a demonstration of this design strategy are image processing and image reconstruction from projections. Image processing is the process of manipulating an image to obtain increased visual impact or to emphasize interesting structures in order that

more information may be extracted from the image. Any linear modification of an image may be expressed as an operation on its frequency spectrum. Thus, Fourier filtering is a convenient tool to use in effecting the modifications since quantitative description of the changes (in terms of resolution, SNR, contrast texture, etc.) is easily obtained and interpreted through the transfer function of the filter. Up to the present, image processing investigators have been hindered by the inablility to perform complex image processing operations in a timely manner due to software Fourier transform implementations. However, a high speed hardware Fourier transform processor such as will be described should provide investigators with the means to carry out such work.

Some of the image processing operations that are easily carried out in the frequency domain are lowpass filtering to improve visual impact, highpass filtering for edge detection or deblurring and matched filtering for object identification and location.

Image reconstruction from projections has become a very important area since the advent of Computer Assisted Tomography (CAT) as a diagnostic medical tool. Rapid reconstruction (< 10 secs.) of large images (e.g. 256 x 256 pixels) from a large number of projections (e.g. 150) necessitates high-speed special purpose hardware. There are several algorithms for reconstruction which utilize the Fourier transform and, thus, could be implemented using a hardware processor. Further, it is of great interest in this field to perform dynamic imaging. That is, acquiring "snapshots" of an area of the body at several closely spaced (e.g. 100 msec) points in time to observe a system in operation. This increases the need for high data throughput and accentuates the need for high speed hardware.

In addition to two dimensional signal processing, a high performance Fourier transform processor such as will be described is useful for one-dimensional signal processing where the amount of computation necessary makes implementation impractical. Some of these areas are image reconstruction from projections chemical analysis using NMR techniques, NMR flow imaging and X-ray crystallography.

While Fourier analysis is an extremely powerful tool, the image processing investigator must remain aware of its limitations. Mathematically, there are functions which do not have Fourier transforms. There are 3 sufficient conditions for the existence of the Fourier transform of a function, f(x):

- 1) The integral of f(x) from  $-\infty$  to  $+\infty$  exists.

- 2) The number of discontinuities in f are finite.

- 3) f(x) is of bounded variation.

The first two conditions are self-explanatory. The third is a bit more complicated and its treatment is beyond the scope of this thesis. Suffice it to say that a function that is of bounded variation has a finite number of maxima and minima in any finite interval. Sin  $\mathbf{x}^{-1}$  is a good example of a function without bounded variation. There are also functions whose Fourier transforms do not strictly exist, but are said to have transforms in the limit. Impulses and purely periodic functions are in this class.

Any physical waveform that can be measured has a Fourier transform by virtue of its physical existence. However, whenever mathematical modeling or analysis is used to represent a physical entity, one must be careful not to violate these conditions of existence.

Further, one must be careful to realize the assumptions that are made in applying Fourier analysis to a physical system. The most important is that the system is linear. That is, the output from the sum of a set of inputs is the same as the sum of their individual outputs. Secondly, the system must be time stationary. The action referred to above does not change with time.

Finally, the investigator must be aware of the rules which must be followed in moving from continuous Fourier analysis to the use of any of the discrete Fourier transform techniques. An example of this is the Shannon Sampling Theorem.

While real-time image processing is still a thing of the future, a system utilizing an Ultrafast Fourier Transform Parallel Processor (UFTPP) will increase processing speed by several orders of magnitude

over software and at least an order of magnitude over other hardware transform devices. This increase in processing speed brings image processing to the interactive level. That is, an image processing investigator may be able to perform an operation on an image and see the results within a few seconds (e.g. ~10 sec.). This allows the investigator more continuity of thought and the ability to exercise subjective judgment much more easily than previously when several minutes of computation were necessary to perform a single operation on an image. Further, when the investigator arrives at an image which satisfies him/her, one can quantitatively describe what processing has been done by description of the various filters which have been applied.

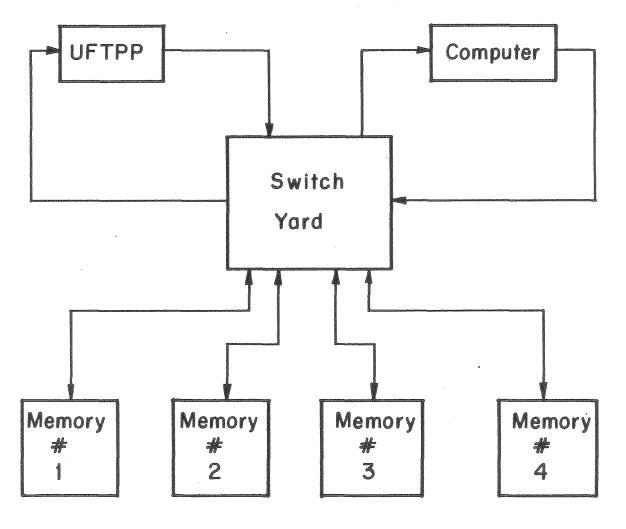

A system such as the one described in this thesis might be utilized as shown in Figure 1. The UFTPP looks like any other peripheral to the central processor of the host computer; the programmer may view it as an extremely fast FFT subroutine. A typical image processing session may proceed as follows:

- User sits down at the terminal and calls up an image stored on the host computer's mass storage.

- 2) The user inputs a frequency domain filter to the program (through use of a joystick, trackball, TTY, lightpen, etc.).

- 3) The computer Fourier transforms the image, multiplies it by the input filter and displays the results in about 10 seconds.

- 4) The user studies the result and instructs the computer whether to save this image or discard it or return to step 2 for further processing.

A system such as this may be realized for < \$15K not including the host computer. The host computer need be nothing more than a small minicomputer (e.g. PDP-11/10) or even a microprocessor. Of course, the faster the host computer the faster the turnaround from image to image. Almost all of the processing time will be the I/O time to and from the UFTPP, disk and display. By todays technology standards, only such superminis as the VAX-11/780 will be able to keep pace with the UFTPP.

XBL7912-3926

#### CHAPTER 2

#### FFT DERIVATION AND MODIFICATION

#### 2.1. Cooley-Tukey FFT Derivation

The continuous Fourier Transform, H(f), of a function h(t) is given by

$$H(f) = \int_{-\infty}^{\infty} h(t)e^{-j2\pi ft}dt$$

(1)

The discrete Fourier Transform is derived from the above by introduction of a real space sampling function, a real space window and a frequency space sampling function. The resulting expression for the discrete transform is

$$H(f/NT) = \sum_{g=0}^{N-1} h(gT) e^{-j2\pi fg/N}$$

$$= \sum_{g=0}^{N-1} h(gT)W^{fg}$$

(2)

where

The FFT algorithm for computing (2) when  $N=r_1 r_2 r_2 r_m$  is

$$H(n_0, n_1, \dots, n_{m-1}) =$$

$$\sum_{k_0=0}^{r_m-1} \sum_{k_1=0}^{r_{m-1}-1} \sum_{k_{m-1}=0}^{r_1-1} h(k_{m-1}, k_{m-2}, \dots, k_0) W^{nk}$$

(3)

where

$$n = n_{m-1}(r_1r_2 \cdots r_{m-1}) + n_{m-2}(r_1r_2 \cdots r_{m-2}) + \cdots + n_1r_1 + n_0$$

$$k = k_{m-1}(r_2r_3 \cdots r_{m-1}) + k_{m-2}(r_3r_4 \cdots r_m) + \cdots + k_1r_m + k_0$$

When N=r<sup>m</sup>, then (3) simplifies to

where

$$n=n_{m-1}r^{m-1}+n_{m-2}r^{m-2}+\cdots+n_0$$

$k=k_{m-1}r^{m-1}+k_{m-2}r^{m-2}+\cdots+k_0$

and

$$n_i = 0, 1, 2, \dots, r-1.$$

Implementation on a binary digital computer is most simply done when  $N=2^{m}$  and (4) becomes

$$H(n_0, n_1, \dots, n_{m-1}) =$$

$$\sum_{k_0=0}^{1} \sum_{k_1=0}^{1} \dots \sum_{k_{m-1}=0}^{1} h(k_{m-1}, k_{m-2}, \dots, k_0) W^{nk}$$

(5)

where

$$n = n_{m-1} 2^{m-1} + n_{m-2} 2^{m-2} + \dots + n_0$$

$k = k_{m-1} 2^{m-1} + k_{m-2} 2^{m-2} + \dots + k_0$

and

$$n_{i} = 0, 1.$$

It is easy to see that computation of (5) requires m iterations where the  $i^{th}$  iteration involves the intermediate results from the previous iteration. The intermediate results,  $H_i(t)$ , for the  $i^{th}$  iteration may be expressed as

$$H_{i}(n_{0}, n_{1}, \dots, n_{i-1}, k_{m-2}, k_{m-3}, \dots, k_{0})$$

$$= \left[ \sum_{k_{m-i}=0}^{r-1} h_{i-1}(n_{0}, n_{1}, \dots, n_{i-2}, k_{m-i}, k_{m-i-1}, \dots, k_{0}) \cdot W^{i-1}^{k_{m-i}N/r} \right]$$

$$\cdot W^{(n_{i-1}r^{i-1} + n_{i-2}r^{i-2} + \dots + n_{0})}_{k_{m-i-1}r} (m-i-1)$$

$$i = 1, 2, \dots, m$$

$$(6)$$

The expression inside the [] is the expression for a radix-r "butterfly" operation and the outside portion is known as the "twiddle factor" (after Gentleman & Sande [32]). This expression effectively says that each iteration in the calculation is an r-point "butterfly" applied to N/r sets of points appropriately chosen from the intermediate results of the previous iteration. The results of this calculation are then individually "twiddled" according to the outer expression. The radix, r, of the transform is chosen according to the type of computing power available. (This will be discussed in detail in chapter 3.) In the case of radix-2, the "butterfly" results in a simple addition and subtraction of the two complex numbers followed by multiplication of the difference by a twiddle factor. The twiddle factor for the sum is always one.

It is important to notice that the  $m^{th}$  iteration produces the set  $F_m(n_0,n_1,n_2,\dots,n_{m-1})$  as a result, but the frequency coefficients in their correct order are  $F_m(n_{m-1},n_{m-2},\dots,n_0)$ . In other words, the FFT algorithm produces its results in digit reversed order which must be compensated for. (This will be taken up in chapter 5.)

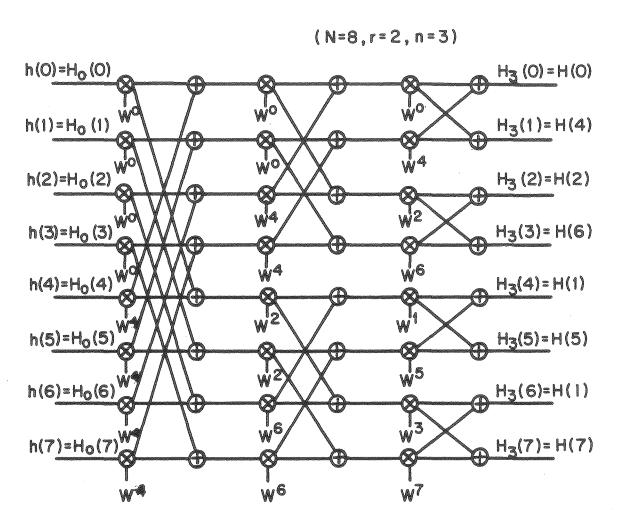

A graphic representation of the FFT algorithm for radix-2 is shown in Figure 2. This is known as the signal flow graph. Figure 3 shows the signal flow graph for the "twiddle factor" modification.

### 2.2. FFT Modification for Parallel Processing

Pease [48] describes the DFT as a matrix operation and proceeds to derive the Cooley-Tukey FFT algorithm as follows. Let the DFT be expressed as:

XBL784-3030

$$g_{r} = \sum_{s=0}^{N-1} e^{-j2\pi r s/N} \cdot f_{s} \qquad r = 0, 1, ..., N-1$$

(7)

If we allow the matrix  $T_{rs} = e^{-j2wrs/N}$  and the sets  $\{g_r\}$  and  $\{f_s\}$  to be  $\overline{g}$  and  $\overline{f}$ , respectively, then (7) can be expressed as

$$\overline{g} = T_N^{\circ} \overline{T}$$

(8)

Since the FFT produces its output in scrambled order (digit-reversed) we must introduce an operator to reflect this:

$$T'_{N} = Q_{N} T_{N}$$

(9)

where  $\boldsymbol{Q}_{N}$  is the digit reversal matrix (operator) for size  $\boldsymbol{N}_{\bullet}$

Pease shows that the key to the FFT lies in the factorization of T' as follows:

$$T'_{N} = \begin{bmatrix} T'_{N/2} & T_{N/2}' \\ T'_{N/2}K & -T'_{N/2}K \end{bmatrix}$$

$$= \begin{bmatrix} T'_{N/2} & 0 \\ 0 & T'_{N/2} \end{bmatrix} \cdot \begin{bmatrix} I & I \\ K_{N/2} & -K_{N/2} \end{bmatrix}$$

$$= \begin{bmatrix} T'_{N/2} & 0 \\ 0 & T'_{N/2} \end{bmatrix} \cdot \begin{bmatrix} I & 0 \\ 0 & K_{N/2} \end{bmatrix} \cdot \begin{bmatrix} I & I \\ I & -I \end{bmatrix}$$

(10)

where I is the identity matrix and  $\textbf{K}_{\underline{\textbf{L}}}$  the diagonal matrix

$$\operatorname{diag}(W^{0}, W^{1}, W^{2}, \dots, W^{L-1}) \quad (\operatorname{again} W = e^{-j2\pi/N})$$

It is obvious that this process may be continued to any degree as long as N/2 is an integer. When the factorization is halted the subscript on the T' matrices of the left side of (10) is the radix of the transform referred to above.

At this point the Kronecker or direct product of matrices is used. The Kronecker product for two matrices  $A=a_{\mbox{ij}}$  and  $B=b_{\mbox{kh}}$  is defined as

$$A \times B = \begin{bmatrix} a_{00}^{B} & a_{10}^{B} & \cdots & a_{i0}^{B} \\ a_{01}^{B} & \cdots & \cdots & \cdots \\ \vdots & \vdots & \ddots & \vdots \\ a_{0j}^{B} & \cdots & \cdots & a_{ij}^{B} \end{bmatrix}$$

The result has dimensions i\*k by j\*h. Thus, (10) may be expressed as

$$T'_{N} = (T'_{N/2} \times I_{2})D_{N}(I_{N/2} \times T'_{2})$$

(11)

where  $\boldsymbol{D}_{\!\!N}$  is the matrix quasi-diag (IK) and

$$\mathbf{T'}_{2} = \begin{bmatrix} \mathbf{W}^{0} & \mathbf{W}^{0} \\ \mathbf{W}^{0} & \mathbf{W}^{N}/2 \end{bmatrix} = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}$$

When the factorization is carried all the way down to a radix-2 transform (11) becomes, for  $N = 2^n$ ,

$$T'_{N} = (T'_{2} \times I_{2} \times \cdots \times I_{2}) \cdot Q_{1} \cdot (I_{2} \times T'_{2} \times \cdots \times I_{2}) \cdot Q_{2} \cdot \cdots \cdot (I_{2} \times \cdots \times I_{2} \times T'_{2})$$

$$\cdots \cdot (I_{2} \times \cdots \times I_{2} \times T'_{2})$$

where  $Q_{i} = D_{r}(i+1) \times I_{r}(n-i-1) \cdot \cdots$

As with regular matrix multiplication, the Kronecker product is not commutative. So, another operator is introduced which allows commutation of matrices under the Kronecker product. This operator, called the perfect shuffle operator, is defined as  $P_{\rm N}$  such that

$P_N$  °  $col(x_0, x_1, \dots, x_{N-1}) = col(x_0, x_{N/2}, x_1, x_{N/2} + 1, \dots, x_{N-1})$  Using  $P_N$ , it can be shown that

$$I_2 \times I_2 \times I_{N/4} = P_N (I_2 \times I_{N/2}) P_N^{-1}$$

(13)

or

$$I_4 \times I_2 \times I_{N/8} = P_N^2 (I_2 \times I_{N/2}) P_N^{-2}$$

And, (12) can be rewritten as

$$T'_{N} = (T'_{2} \times I_{N/2}) \cdot Q_{1} \cdot P(T'_{2} \times I_{N/2}) P^{-1} \cdot Q_{2} \cdot \cdot \cdot$$

$$\cdot P^{(N-1)} (T'_{2} \times I_{N/2}) P^{-(N-1)}$$

(14)

If we define  $C = (T'_2 \times I_{N/2})$  and  $Q_i = P^{(i-1)} E_i P^{-(i-1)}$  and notice that  $P_N^n = P_N$  and  $P_N^{-(n-1)} = P_N$  for  $N = 2^n$ , then we may write (14) as

$$T'_{N} = C P^{0} E_{1} P^{-0} P^{1} C P^{-1} P^{1} E_{2} P^{-1} P^{2} \cdots CP^{(n-1)} E_{n} P^{-(n-1)}$$

$$= C E_{1} P C E_{2} P \cdots C E_{n} P$$

(15)

And, finally

$$T'_{n=2^n} = \prod_{i=1}^n C E_i P$$

(16)

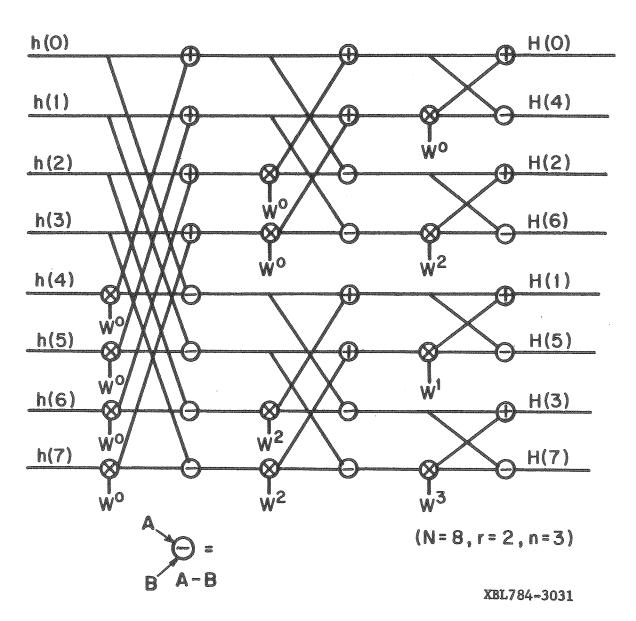

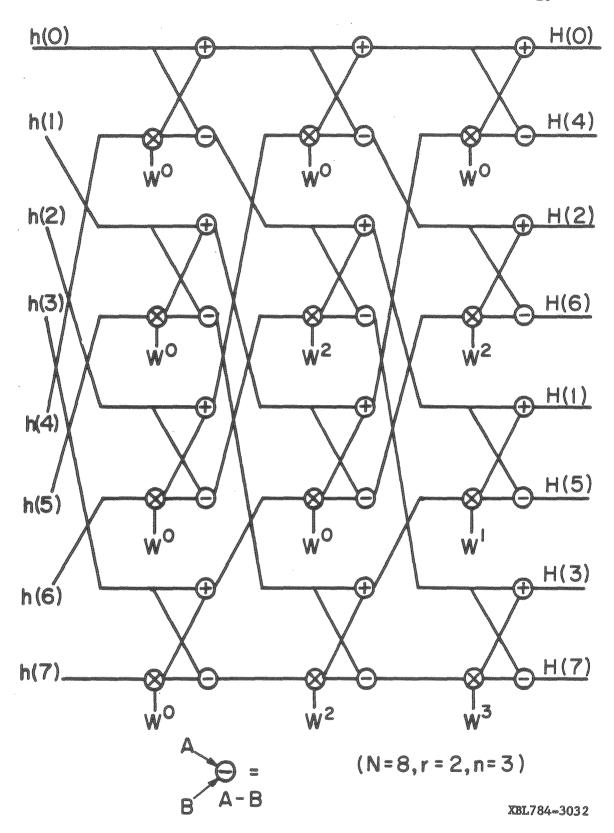

Thus, the FFT may be computed employing only the C operator (the butterfly operator), the E<sub>i</sub> operator (the twiddle factor operator) and the shuffle operator P. The importance of this representation is that the data routing is accomplished using the identical operator at each iteration. The new signal flow graph for this operation is shown in Figure 4. One will notice that this arrangement allows for the completely parallel computation of the FFT with data routing accomplished by hardwired paths as shown in Figure 5. This effectively reduces the computation time to the order of log<sub>2</sub>N since all N/2 2-point butterflies are accomplished in parallel. However, if a hardware implementation were designed, it would require N/2 complex multipliers and N complex adders. At the present state of the art, this is clearly too expensive.

#### 2.3. The Perfect Shuffle Generating Function

Examination of Figure 5 shows that the parallel arithmetic units are identical and that a single one working successively on each pair of inputs could produce the results for that iteration. If it is possible to implement the perfect shuffle in a serial fashion, then an FFT processor with flexible parallel processing architecture and simplified control logic may be realized.

Close inspection of the perfect shuffle operator reveals that there is a perfect shuffle generating function, p(i), (i.e. a function which generates the index in the output vector of a given index from the input vector) given by

Figure 4

XBL784-3033

Figure 5

$$j = p(i) = i^*r - ((i^*r)/N^*N) + (i^*r)/N$$

(17)

when r is the radix of the shuffle (and the transform) and N is the length of the vector being shuffled (i.e. the length of the transform). All operations are truncated integer arithmetic. In words, the input address i is multiplied by r modulo N to yield the output address j, which amounts to a left circular shift of i by r-l bits.

By use of the perfect shuffle generating function, the results of the  $i^{th}$  iteration,  $H_i$ , may be determined serially from the results of the previous iteration,  $H_{i-1}$  (see Eq. 6). Figure 6 shows a diagram of a serial FFT processor which uses the perfect shuffle for data routing. Since the data routing does not change from iteration to iteration as in the Cooley-Tukey algorithm, this machine has very little control logic and a low parts count. And, as will be developed in the next chapter, lends itself very well to techniques for increasing execution speed such as pipelining and parallel processing.

#### CHAPTER 3

#### ARCHITECTURE

# 3.1. Arithmetic Unit Implementation For Different Radices

A major factor which impacts the architecture of a Fourier transform processor is the radix of the transform. Eq. 4 in chapter 2 gives the general expression for a radix-r transform (figure 3 shows the butterfly operations for an 8-point, radix-2 transform). In this section we will examine what the implications of that expression are in terms of hardware. The discussion will be limited to radices which are a power of two since the Cooley-Tukey algorithm is most easily implemented under that condition.

As noted in Chapter 2, there are r complex points involved in the computation of one "butterfly" at each node of the signal flow diagram for a radix-r transform. For maximum speed, this means that there must be r parallel data paths in the butterfly computation unit. Each datum must be correctly weighted and combined with the other weighted inputs to correctly compute the r-point transform dictated by  $T_r$  (Eq. 11).

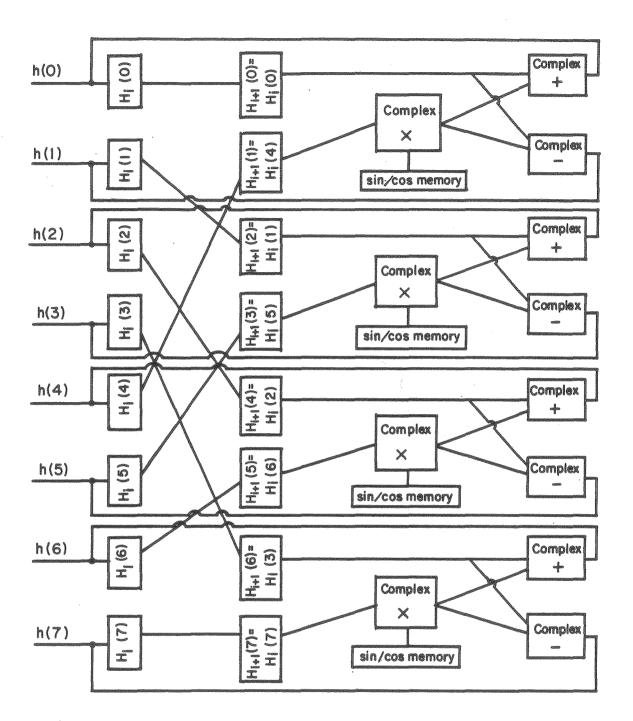

In order to compare hardware costs of various radix transforms, it is valuable to notice that any radix transform,  $T_r$ , may be further factored until it is expressed in terms of a radix-2 transform, assuming that  $r=2^{z}$ . In the same manner as Eq. 12, we can see that recursive application of Eq. 11 eventually will express the radix-r transform in terms of radix-2. Further, consider Eq. 13 and its application to the resulting expression. The final result is an expression which may be realized exactly as in the signal flow diagram shown in Figure 3. In fact, Figure 3 may be interpreted as either the signal flow diagram for a radix-2, 8-point transform of as the inside of a "butterfly" computation element for a radix-8 The only difference is that the eight inputs to the radix-8 computation element are weighted according to the "twiddle factor" formula given in Eq. 6.

There are three important implications of this analysis. First, we note that a radix-r transformer may be implemented with r  $\log_2 r$  complex adder/subtracter combinations (one complex adder and one complex subtracter is necessary to implement one radix-2 "butterfly" operation.) An equally fast radix r/2 processor would require four parallel arithemetic units due to the N/r  $\log_r N$  execution speed of the Cooley-Tukey algorithm. In general, moving from radix-r to radix  $s = q \times r$ , the speed increase is

$$\frac{N}{r} \log_{s} N \circ X = \frac{N}{s} \cdot \log_{s} N$$

$$=>$$

$X = q^{\circ}log_{S}q$

It can be seen that the number of adders/subtracters stays constant for equally fast machines of different radices.

Secondly, we see a difference in the number of complex multipliers necessary to implement different radix proocessors. Again, referring to Eq. 6, we first consider the number of multipliers necessary within the radix-r transform computer. The recursive nature of the FFT allows us to see that implementation of a radix-r  $(r=2^q)$  transform using radix-2 "butterflys" requires q steps. At the ith step,  $2^{(i-1)}$  transforms of radix- $2^{(q-i+1)}$  are performed on the outputs from the i-1 step. At each step i, the weights used in the transform are given by

$$W^{x} = e^{(-j2\pi x/i)}$$

where  $x = 0, 1, 2, ..., i-1$ .

This would indicate i different weights for an i-point transform. However, recalling that  $W^{(i-y)} = -W^y$ , this is reduced to i/2. Further, we notice that  $W^{(i/4)} = j$  and  $W^0 = l$ . Multiplication by j simply requires interchanging the real and imaginary parts of the complex number. Thus for radices  $\geq 4$ , there is another savings of two complex multipliers. For radix-2, there is only one.

The values input to the radix-r transform must be weighted appropriately before the computation. Eq. 6 shows that the weights are dependent on the position of the input value in the input vector. However, there is always one weight which is unity. Therefore, another (r-1) multipliers are necessary to complete the entire transform step calculation.

In summary, the number of multipliers necessary to implement a radix-r  $(r=2^q)$  transform arithmetic unit is given by

$$M = \left[\sum_{i=1}^{q-1} 2^{i-1} \left(\frac{r}{2^{i-1} \cdot 2} - 2\right)\right] + (r-1) + 1$$

$$= \left[\sum_{i=1}^{q-1} r/2 - 2^{i}\right] + (r-1)$$

$$= (q-1) \cdot r/2 - (2^{q} - 2) + (r-1)$$

$$= (q-1) \cdot r/2 + 1$$

$$= \frac{r}{2} \log_2 r - 1$$

(18)

The expression in [] is the number of multipliers within the arithmetic unit. The (r-1) is the number of multipliers used for initial weighting. Table I shows some examples of the number of complex multipliers necessary for radix-r arithmetic units (M) compared with an equally fast version of a radix-2 machine (N).

|                         | TABLE                 |                         |                          |

|-------------------------|-----------------------|-------------------------|--------------------------|

| ľ                       | <u>q</u>              | M                       | N                        |

| 2<br>4<br>8<br>16<br>32 | 1<br>2<br>3<br>4<br>5 | 1<br>3<br>9<br>25<br>65 | 1<br>4<br>12<br>32<br>90 |

A third consideration for the radix-r processor is the amount of coefficient storage necessary. Eq. 6 shows that the "twiddle factor" at step i uses the (i-l) most significant digits (base r) of the data address, digit reversed and masked as the base value to which W must be raised. This value is then multiplied by  $k_{(m-i-1)}$  which can take on the values  $0,1,2,\ldots,(r-1)$ . When i=m, m-l digits are used to compute the base value. During this iteration N/r different values will be used indicating that the minimum number of coefficients that must be stored for a radix-r transform is N/r. (It is assumed that all coefficients will be stored at the address equal to the value to which W must be raised to obtain that coefficient. For example, W would be stored at location 8.)

The  $k_{(m-i-1)}$  modifier of the base value has considerable hardware implication. Arithmetically, the final "twiddle factor"

value may be determined from the base "twiddle factor" by squaring, cubing, etc. (The highest power being r-1.) This requires  $\log_2 r$  stages of complex multipliers for a total of r-2. Alternatively, all of the weighting factors may be stored directly raising the quantity of storage necessary to (r-1)/r x N coefficients. In general, the lower price of ROM storage would argue in favor of use of the extra storage. However, parallel access of all r-1 coefficients is not possible since the  $k_{(m-i-1)}$  parameter takes on all integral values less than r and the base values vary with iteration. Thus, multiple read cycles would be necessary to find all coefficients; or, multiple copies of the coefficients may be stored to allow parallel access. Even storage of multiple copies of the coefficients would be cheaper than the multiplier implementation (by today's standards).

# 3.2. Perfect Shuffle Data Handling

"butterfly". When a pipelined architecture is employed (as will be discussed in the next section), it is desirable to access all r in parallel as this provides the shortest pipe cycle time. It is in the memory organization that the full impact of the perfect shuffle data routing algorithm is found. While the Cooley-Tukey algorithm changes the separation of the data points to be accessed at each iteration of the transform, the perfect shuffle maintains a constant separation between points. The Cooley-Tukey (decimation in time) algorithm begins with a separation of data points of 2 (m-1) (Eq. 6) for input during the first iteration and ends with a separation of 1 at the m iteration. It is exactly the opposite for decimation in frequency. Output at each iteration is sequential for both algorithms. The perfect shuffle algorithm always accesses the data sequentially and at a separation of r on output.

No memory architecture is possible that allows direct parallel access of all input data values during all iterations of the Cooley-Tukey algorithm. Some form of variable length buffer must be interposed between the memory and arithmetic unit to match the correct values. However, using RAM and an interleaved architecture guarantees that all data values may be accessed in parallel when the

perfect shuffle is employed.

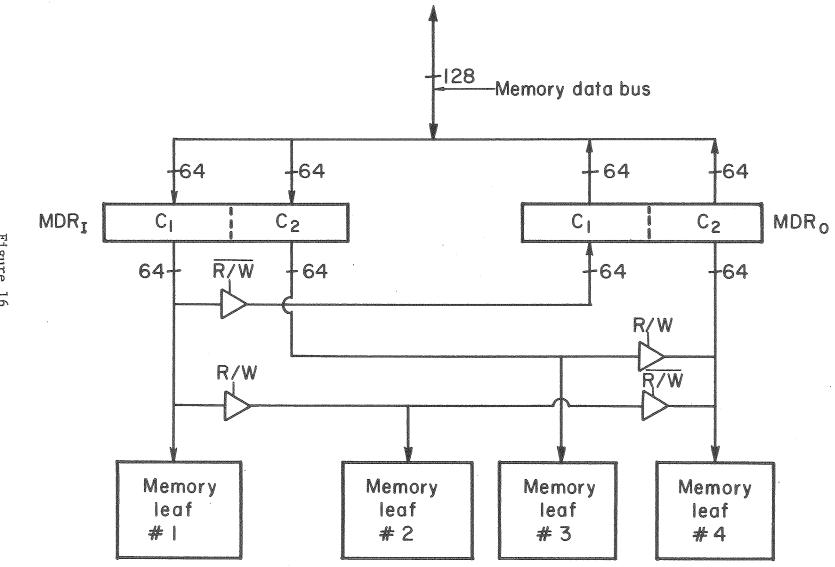

Close examination of the expression for the perfect shuffle reveals that a physical memory cannot function as both input and output simultaneously, as some input values will be destroyed by output before they are read out. However, a memory may function in both capacities at different times. When used as an input memory, access is sequential, r values per cycle. This would require r-way interleaving with addresses 0,r,2r,... in the first memory 1,r+1,2r+1,... in the second and so on. When functioning as an output memory, r complex values must also be accessed in parallel. This time however, at intervals of r. This demands that addresses separated by r be stored in different memory leaves. Notice this is exactly contrary to the sequential interleaving needed for input. The result is a requirement for  $r^2$ -way interleaving in general in order to accomplish both sequential access and a radix-r shuffle. Thus, addresses  $0, r^2, 2r^2, \dots$  occupy a leaf;  $1, r^2+1, 2r^2+1, \dots$  occupy the next and so on. Which leaves are written into during a given memory cycle is a function of whether the memory is reading or writing (input or output mode) as well as what the address is.

If multiple memory accesses can be accomplished during a machine cycle, then the interleaving may be reduced to  $r^2/C$  where C is the number of memory cycles that may be executed during one processor execution cycle.

Shift register type memories may also be employed in a similar flexible architecture [22]; however, I/O considerations argue in favor of RAM (see Section 5.6.7).

## 3.3. Pipeline Architecture For The UFTPP (Horizontal Parallel Processing)

Pipelining is a familiar architectural technique for achieving a form of parallel processing in computers. The basic idea is to break a complex operation into a series of simpler steps. Between steps the intermediate results are stored in registers. The operation is begun on a new set of input data at the beginning of each clock period as the results from the first step proceed to the second and so on. After a fixed delay, the entire pipeline will be filled and

results will begin to emerge from the end of the pipe, one per clock period. Since the simple operations require less time to complete than the entire complex operation, the clock frequency may be increased. Parallel processing is occurring since there are several data sets at various stages of completion during each execution cycle.

If the original operation would have taken time T to complete and it has now been divided into a pipeline of S steps each of duration t, then the following expressions hold (assume M data sets are to be processed)

If S  $\times$  t $\approx$ T (i.e. each step in the pipeline requires almost the whole pipe cycle to complete it, in other words, the choice of operations to be performed in each pipe cycle is time efficient), then the speed-up factor is

$$\frac{X}{W} = \frac{M^{\circ}T}{(S+M)^{\circ}t}$$

$$\approx \frac{M^{\circ}T}{(M^{\circ}t)+T}$$

$$= \frac{M^{\circ}n}{M+n}$$

≈ n for M>>n.

and n = T/t.

In the case of the FFT, the number of operations to be performed is

$$M = \frac{N}{r} \cdot \log_r N$$

where N is the size of the transform and r is the radix. This substituted into Eq. 19 gives

$$Z = \frac{N}{r} \cdot \log_r N \cdot t \tag{20}$$

for the total processing time if t is the processor cycle time.

The question then becomes "Can a radix-r Fourier Transform be implemented in a pipelined machine?" It is clear that the  $\log_2 N$

iterations of transform can be pipelined from the several processors that implement it in a cascade architecture [6]. In each iteration the following steps must be performed N/r times:

- Read the next set of r data from the input memory; read the next set of r coefficients (sine-cosine values).

- 2) Perform complex multiplication of r input data pairs with the sine-cosine sets.

- 3) Perform the radix-r butterfly operation.

- 4) Write the set of r results into the output memory.

It has already been shown that determination of the addresses for the data in steps 1 & 4 is possible and straightforward. In section 3.1 it was shown that a radix-r butterfly may be recursively broken down into several radix-2 "butterfly" operations. A radix-2 "butterfly" is simply a complex multiplication followed by a complex addition and subtraction. So, steps 2 and 3 rely on performing a complex multiplication.

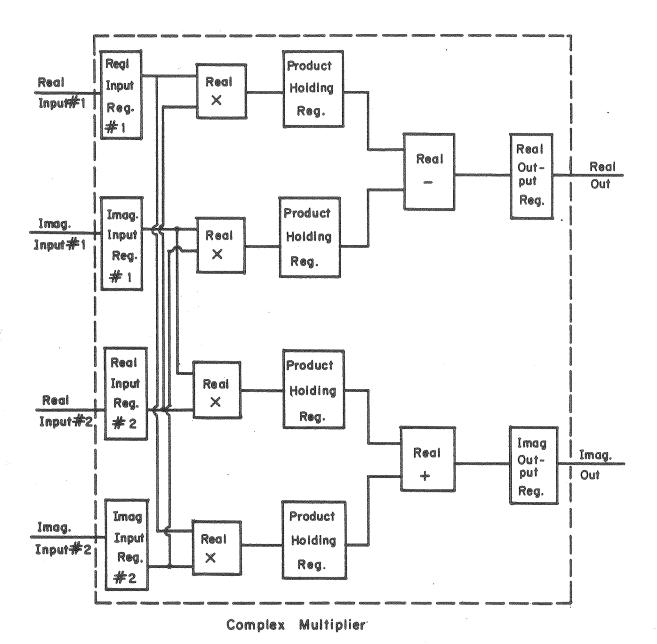

Complex multiplication may be expressed thus:

$$e + jf = (a + jb) \times (c + jd)$$

(21)

=  $(ac - bd) + j(bc + ad)$

=>  $e = ac - bd$  and  $f = bc + ad$

It is easily seen that it requires 4 independent real multiplications and an addition and subtraction. A pipelined complex multiplier is shown in Figure 7.

# 3.4. Multiple Arithmetic Units (Vertical Parallel Processing)

Section 2.3 showed that the perfect shuffle data routing algorithm used by Pease could also be applied to a sequential processor to simplify the hardware and section 3.3 showed that the technique of pipelining could be applied to the simplified processor to achieve horizontal parallel processing. Vertical parallel processing (i.e. use of multiple arithmetic units working simultaneously) is also possible with this architecture.

XBL784-3035

Figure 7

Equation 6 in section 2.1 shows that the results of the i<sup>th</sup> iteration depends only upon the results from the i-1<sup>st</sup> iteration. Further, it shows that pairs of data from that iteration are inputs to only one butterfly operation in the subsequent iteration. Thus, since the output address of any input pair may be determined from its input address (section 2.3), it is clear that there are no conflicts that would prevent several processors from working simultaneously on the same transform. (For example, two radix-2 arithmetic units working together would process 4 complex pairs at each pipeline step. Unit 1 would process pairs 0,1,4,5,8,9,... from the input and unit 2 would process 2,3,6,7,... Their corresponding output addresses would be 0,2,8,10,16,18,... and 4,6,12,14,..., respectively.)

From equation 19, it can be seen that processing time with P processors is

$$\frac{N^{\circ} \log_{r} N}{r^{\circ} P} \tag{22}$$

cycles. As noted in section 3.1 a factor of 4 is gained in processing speed for each factor of 2 increase in radix. Also, Table I showed that fewer multipliers are necessary for the higher radix processors as opposed to equally fast radix-2 units. However, there may be cases where multiple copies of a less complex, smaller radix unit may be more desirable from an implementation standpoint. One further consideration concerns the application of the processor. If flexibility in transform size is necessary, then the smaller the radix, the more sizes of transforms may be computed. (Recall that given radix r, only transforms of  $N = r^m$  where m is an integer may be computed.)

It should be noted that certain values of P (Eq. 22) are more convenient than others. When P is an integral power of 2, then the only modification to the architecture is interleaving the memories further. A parallel machine will process r°P data sets per cycle and thus the memory must be interleaved r²°P ways (see section 3.2). It is possible to implement a processor that does not contain an integral power of two arithmetic units. However, in order to guarantee that all r°P data sets can be accessed in parallel at all

addresses, the memories must be interleaved  $r^2 \cdot P'$  ways where P' is the smallest integral power of two larger than  $P \cdot P'$  in addition, the addressing hardware must be alterred to translate the logical addresses to physical ones.

Both increasing the number of parallel arithmetic units and increasing the radix cause memory fragmentation at the same quadratic rate due to the  ${\bf r}^2$  P memory interleaving requirement.

The modularity of this design allows expansion of the machine architecture to meet a wide range of speed and budget requirements subject only to the constraints discussed above.

# 3.5. Comparison of the UFTPP architecture with other architectures

The basic classes of Fourier transform processor architectures are the sequential, cascade, parallel and array types [5]. The parallel and array architectures are, as yet, paper designs since their implementation is not economically feasible. The parallel architecture is depicted in Figure 5. The speed of the parallel architecture is achieved when N/r arithmetic modules are used in the UFTPP architecture. The array architecture is simply an extension of the parallel and may be implemented in several ways (e.g. Figure 4, Figure 3 or see [4]). The UFTPP cannot attain the speed of an array architecture. The sequential architecture contains only 1 arithmetic unit and has the speed of a 1 arithmetic unit UFTPP.

The most interesting architectures for comparison with the UFTPP architecture is the cascade type (described in detail by Groginsky & Works [37] and Bergland [5] ). The cascade architecture computes a fixed length transform using  $m=\log_r N$  arithmetic units arranged in series. Each of the m radix-r units computes the results for a given iteration (i.e. the results of butterfly operations between complex points seperated by  $r^{-1}N$  where i is the position of the arithmetic unit in the series starting with 1) from the output of the previous unit. Each unit has associated with it a digital delay line (i.e. shift register) of length  $(r-1)r^{-1}N$  which pairs the correct data points for the butterfly computation for that iteration. The latency of this architecture is N cycles (i.e. the time from entrance of the

first data sample to the emergence of the first frequency coefficient) and the amount of intermediate storage necessary is N complex words. The results are output in digit reversed order and requires another N cycles.

The UFTPP architecture with  $m=\log_r N$  arithmetic units has a computation time of  $N/r + \log_r N$  S cycles (from Eq. 19). This is slightly different than the latency as the entire transform is complete at that time. However without modification to the architecture this is when the output is ready to be unloaded. Unloading also requires N cycles. The UFTPP architecture requires 2N complex words of storage.

If we set the expressions for the latency of the two architectures equal to one another we see that

$$\frac{N}{r} + \log_r N S = N(r-1) \sum_{i=1}^m r^{-i}$$

or,

$$S = \frac{N}{\log_r N}$$

When S=15 (i.e. there are 15 pipeline segments in the UFTPP), compute times (assuming identical clock speeds) for both architectures will be equal when N=256, r=2; N=64, r=4; N=8, r=8. For N larger at the given radix , the UFTPP will be faster.

The cascade architecture has the advantage that loading of new input, unloading results and computation all take place simultaneously. This can only be accomplished with the UFTPP when another 2N complex words of storage are used as input and output buffers. These buffers are filled while transform computation is taking place on data from two other memories.

The cascade architecture relies on the assumption that computation, loading and unloading speeds are approximately equal in order to obtain its hardware efficiency. However, when higher clock speeds are possible within the processor than are possible for I/O, then the cascade loses its advantage. If T is the clock period for I/O data transfers and t the processor clock period, then for T/t values in

the range of 2-5 the UFTPP architecture shows considerable savings in hardware. Table II shows the number of arithmetic modules necessary to perform a transform (P) in the same time as the m modules needed for a cascade implementation for various radices (R), transform sizes (N) and speed-up ratios T/t. It is clear that for values of T/t > 5 and radices > 4 the UFTPP advantage will increase.

| TABLE II                                                         |                                                |                                                |           |                                           |                                                          |                                                |

|------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|-----------|-------------------------------------------|----------------------------------------------------------|------------------------------------------------|

| N                                                                | · Yes                                          | m<br>m                                         | t= 2<br>P | 3<br>P                                    | 4<br>P                                                   | 5<br><u>P</u>                                  |

| 64<br>128<br>256<br>512<br>1024<br>2048<br>4096<br>8192<br>16384 | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | 633333444 | 2<br>2<br>2<br>2<br>2<br>2<br>3<br>3<br>3 | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | 1<br>1<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |

| 64<br>256<br>1024<br>4096<br>16384                               | 4<br>4<br>4<br>4                               | 3<br>4<br>5<br>6<br>7                          | 1 1 1 1   | 1<br>1<br>1<br>1<br>1                     | 1 . 1                                                    | 1 1 1 1                                        |

It has been shown that the cascade architecture is more hardware efficient when no buffer memories are used and the I/O clock speed and processor clock speeds are the same. However, if the I/O clock speed is slower than possible for the processor (which is generally the case when the Fouier transform processor is a peripheral device to a central processor), then considerable hardware savings may be realized in the arithmetic units when arranged in the UFTPP architecture rather than the cascade. The UFTPP architecture requires 4N complex memory words as opposed to N for the cascade; however, this is offset by the savings in the arithmetic units as shown by Table II.

#### CHAPTER 4

#### NUMBER REPRESENTATION & ARITHMETIC

# 4.1. Fixed Point vs. Floating Point Representation

The establishment of machine word size, number representation and arithmetic required an analysis of the errors to be expected with each of the various choices. This analysis was carried out via software simulation of the entire Fourier transform computation on a CDC 7600 computer.

The advantages and disadvantages of fixed point arithmetic vs. floating point arithmetic have been extensively discussed in the computer science literature [e.g. 31,65]. The facts which bear directly on the implementation of a Fourier Transform processor are:

- 1) Fixed point arithmetic offers a constant absolute error dependent on the number of bits used. Floating point exhibits a constant relative error; that is, the error associated with a number is a fixed fraction of its value with the value of the fraction dependent on the number of bits used.

- 2) Floating point offers a larger dynamic range (i.e. the range of numbers that can be represented with a given number of bits) than does fixed point.

- 3) Floating point arithmetic requires more hardware than does fixed point.

A fixed point number is simply a group of n bits whose values are agreed upon by convention. Regardless of these conventions there are only  $2^n$  different combinations possible. If the least significant bit represents the value X, then the precision of that number is  $\pm$  X/2. A floating point number consists of two parts, the mantissa and the exponent. The mantissa is a fixed point number and the exponent is an exponential modifier whose base is agreed upon by convention. For example, scientific notation is a form of floating point notation. The number 3.1415 x  $10^8$  has a mantissa equal to 3.1415 and an exponent of 8. The base of the exponent is 10. The

precision of the floating point number is a function of both parts. In the above example, the precision of the mantissa is  $\pm$  .00005, but the error is multiplied by  $10^8$  to give a final error of  $\pm$  5000. It can be seen that floating point representations exhibit a constant relative error.

It is also easy to see from the above example that floating point offers a much larger dynamic range than fixed point. The range of floating point is determined by the base used and the number of bits in the exponent. The number of finite values that can be represented (using binary) is  $2^m \cdot 2^n = 2^{m+n}$  where m is the number of bits in the mantissa and n the number of bits in the exponent. Thus, it is seen that for a constant number of bits the same number of numbers may be represented in either a floating or fixed-point system but their precision and spacing are different.

When performing floating point arithmetic there are two operations which must be accomplished that are not necessary in fixed point. The first, binary point alignment, concerns addition and subtraction only. Before two numbers of differing exponents can be added or subtracted their exponents must be made equal and mantissas adjusted accordingly. The second operation is normalization of the result following addition, subtraction or multiplication. In floating point representation, the minimum error is achieved when the most significant bit has value (i.e. is not a place holder). After the above operations, this may not be the case. The operation of shifting the result until its most significant bit occupies the most significant position and adjusting the exponent is called normalization. Both of these operations are easily implemented; however, they do represent an increase in necessary hardware.

Error propogation in computing Fourier Transforms has been given considerable attention in the literature for both the fixed-point [15,54,67,69,72] and floating-point cases [15,41,44]. Because of the complexity of the Fourier transform, only upper and lower bound analyses have been performed. The most useful result for the purpose of this thesis is that of Welch [72] which shows for an array of N values

This result for the one-dimensional case will be shown to extend to two-dimensional transforms performed as a series of one-dimensional transforms which are of interest here.

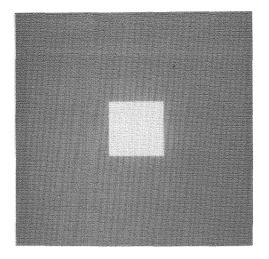

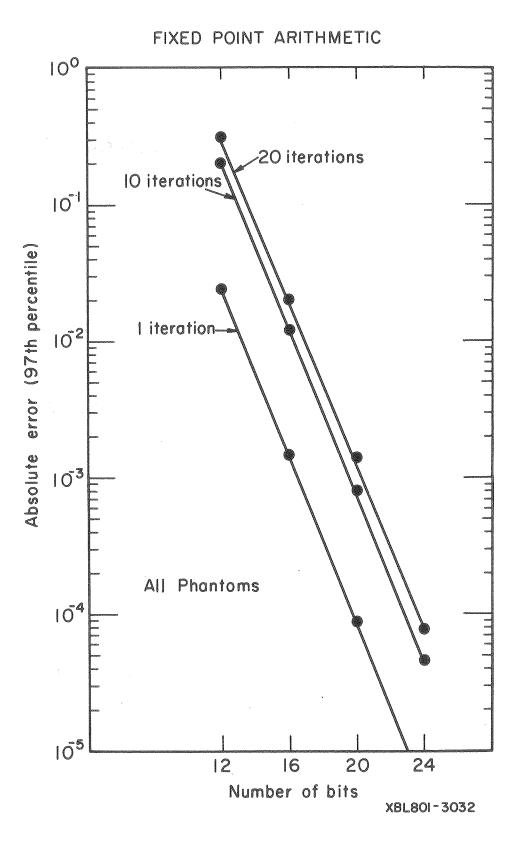

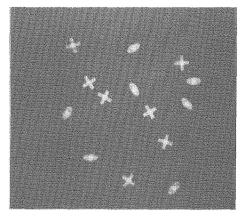

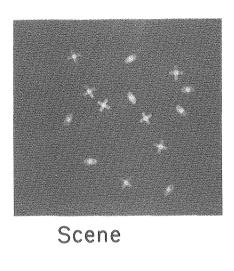

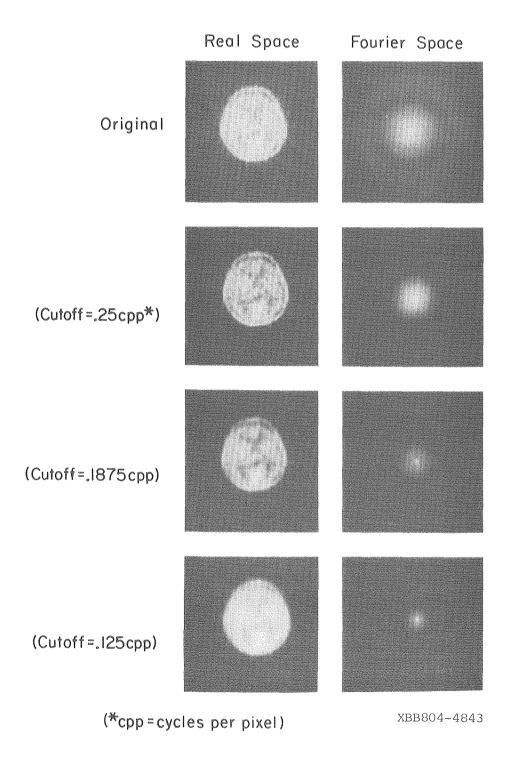

In order to make decisions as to word size, fixed or floating point representation and, in the case of fixed-point, the number of precision bits to be used, computer simulations were performed using several different phantoms (Figure 8). Computer subroutines were written which performed both fixed and floating point arithmetic using different word sizes and different numbers of precision bits. (Precision bits are the bits to the right of the binary point.) each simulation the input array (phantom) was forward transformed and inverse transformed several times. Each forward-inverse computation is referred to as an iteration. At several points, absolute errors were computed by subtracting the original image from the current The absolute values of the errors were histogrammed. metric used was the 97th percentile of the absolute value of Figure 9 shows the behavior of fixed-point arithmetic when the number of precision bits is varied. Data were taken after 1, 10 20 iterations. It can be seen that the error varies as the log of the number of bits used and propogates linearly with the number of Several different word lengths were used. The bits not used for precision allowed different ranges of values in the input arrays. (For example, if a 24 bit word was being used with 16 precision bits, 8 bits are available for range.) Assuming twos complement representation, input values could vary from  $-2^{\prime}$  to  $+2^{\prime}$ . Regardless of word length, input values or range, all results were the same within statistical variation supporting the premise that fixed-point representation exhibits constant absolute error behavior.

For the case of floating-point representation, it was observed that for a given input array the relative behavior was the same as fixed-point although the values of the errors were different. Figure 10 shows the behavior of phantom #1 whose range was 10. Table III shows the error for various phantoms of various ranges after 10 iterations using 24-bit floating point. This is an excellent illus-

Phantom No. 1

Phantom No. 2

Phantom No. 3

Figure 8

XBB804-4842

Figure 9

# FLOATING POINT ARITHMETIC IO 1 20 iterations 10 iterations IÕ2 1 iteration Absolute error (97th percentile) $\overline{O_i}$ Phantom No. 1 105 106 12 20 16 24 Number of bits XBL801-3033

Figure 10

tration of the data dependent behavior of errors under floating-point representation.

TABLE III

| Phantom                                              |                                      |      |                |                               | Ei                       | Error                      |  |  |

|------------------------------------------------------|--------------------------------------|------|----------------|-------------------------------|--------------------------|----------------------------|--|--|

| Phantom #2<br>Phantom #2<br>Phantom #3<br>Phantom #3 | (range<br>(range<br>(range<br>(range | 0000 | to<br>to<br>to | 50)<br>2000)<br>250)<br>1000) | 1.7<br>8.5<br>1.1<br>1.2 | x 10_3<br>x 10_4<br>x 10_3 |  |  |

Considering the image processing applications of the UFTPP, it was decided that it was desirable to keep errors in the 1% range. The simulations indicated that this would require approximately 16 precision bits in the fixed point case and 20-24 in floating point. The fixed point would require additional bits to provide adequate range as well. Even though floating-point representation might allow a slightly shorter word length, the simplicity of fixed-point arithmetic hardware argued in favor of its use in the first version of this machine. In subsequent versions, however, it might be advantageous to use floating point.

The last consideration with respect to error propogation concerns handling of normalization in the fixed point case. The choice is to shift right one bit after each iteration or to divide by N after the entire transform. If one shifts after each iteration one prevents the possibility of overflow but sacrifices some precision. Waiting to divide by N after the entire transform requires m=log\_N more bits to be added to all words which represents a very significant addition in hardware. Simulations were performed to observe just how much additional error would be introduced by dividing by 2 after each iteration. Table IV shows the differences in error under the same conditions as in Figure 9. It can be seen from this table that the difference in error is only about 10%. The amount of

TABLE IV

|                        |                                                                                                                     | Iterat:                                                                                      | ions                                                                                               |

|------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Bits<br>12<br>16<br>20 | $ \begin{array}{c}     \frac{1}{-3} \\ 3.0 \times 10^{-4} \\ 3.0 \times 10^{-5} \\ 1.5 \times 10^{-5} \end{array} $ | $ \begin{array}{c} 10 \\ 6.0 \times 10 \\ -2 \\ 4.0 \times 10 \\ 3.5 \times 10 \end{array} $ | $\begin{array}{c}     20 \\ 1.3 \times 10^{-1} \\ 4.0 \times 10^{-4} \\ 3.0 \times 10 \end{array}$ |

hardware saved by performing the normalization at each iteration is worth the tradeoff of a 10% larger error.

In summary, it has been shown that for the purposes of the UFTPP and its applications fixed-point arithmetic using 16 precision bits should result in about 1% accuracy even when several iterations of transforms are performed. Since the two-dimensional transforms are to be accomplished with a series of one-dimensional transforms, it seems reasonable that the error growth should continue to follow the square root of N dependence demonstrated by Welch.

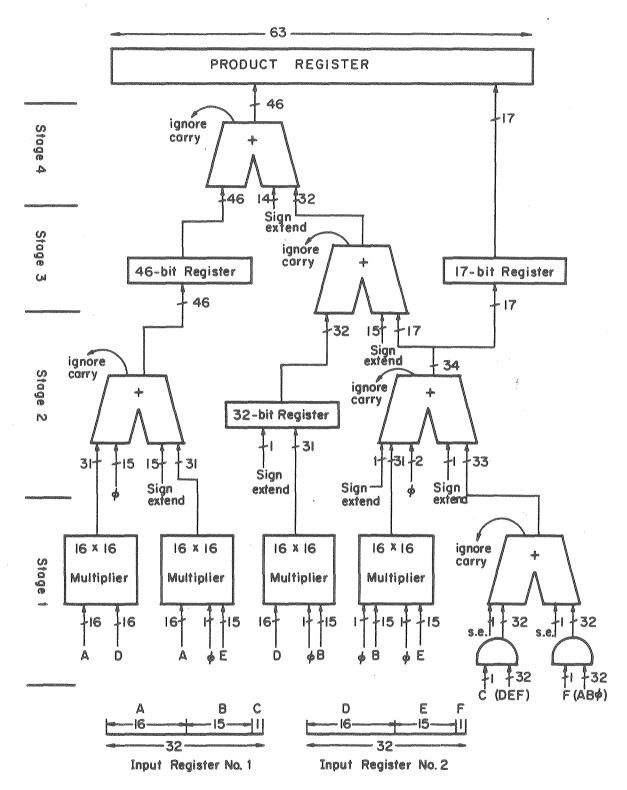

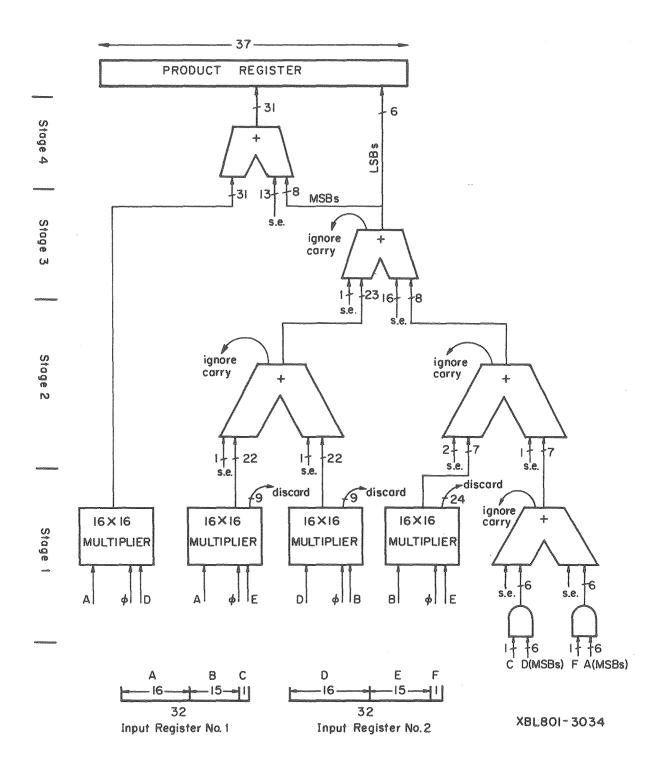

The overall word length to be used is largely determined by the cost that can be tolerated for the implementation of the real multipliers. As mentioned in Chapter 1, LSI multiplier chips have become available that perform 8-, 12-, or 16-bit multiplications. It is relatively straightforward to implement a double precision multiplication using four of these chips. The choice is then whether 24- or 32-bit words are more desirable. When 16 bits are used for precision, the available input ranges would be  $\frac{1}{2}$  128 or  $\frac{1}{2}$  32,768 for the 24- or 32-bit cases, respectively. It is clear that 24 bits simply does not allow a reasonable range and, thus, 32-bit words were chosen. Figure 11 shows the hardware configuration for performing a 32 x 32-bit multiplication yielding a 63-bit product.

XBL792-3212

Figure 11

#### CHAPTER 5

#### PROCESSOR IMPLEMENTATION

# 5.1. Overall System Description

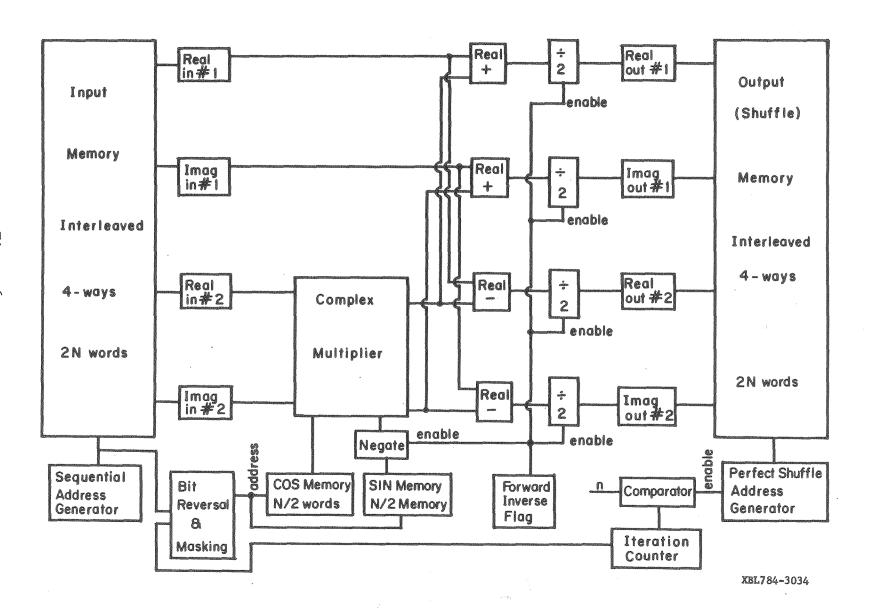

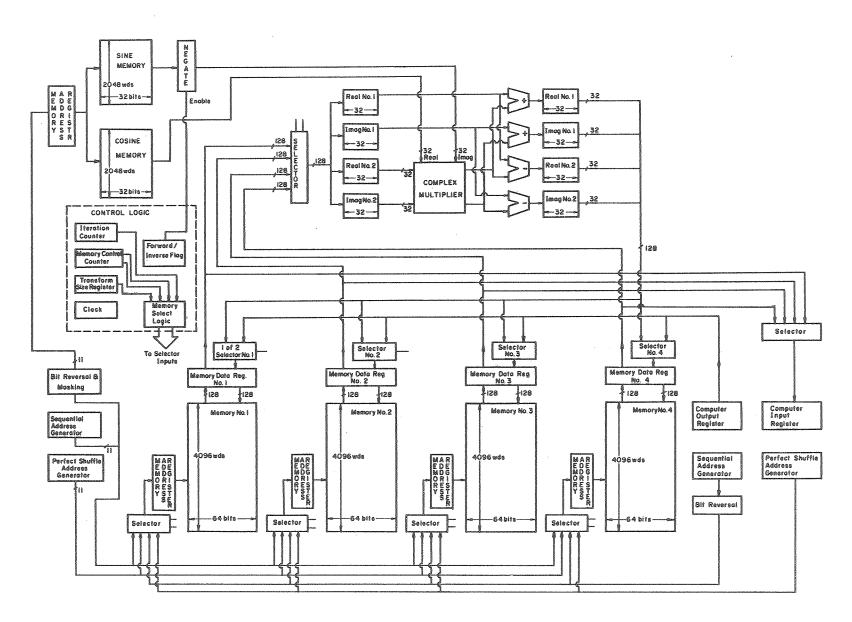

Demonstration and implementation of the architectural design put forth in this thesis was achieved by construction of a radix-2, one arithmetic unit prototype system for transformation of arrays up to 4096 complex values. As outlined in previous chapters larger and faster systems are easily designed. The system consists of an arithmetic unit, a memory system, a multiplexer system, an interface (for the host computer) and overall control logic. Figure 12 shows a schematic diagram of these constituents and their interconnections. The arithmetic unit houses the complex multiplier, cosine and sine read-only-memories, the butterfly computation module, and normalization circuitry. The memory system consists of four independent physical memories that may serve as processor input memory, processor output memory, computer input buffer or computer output buffer. multiplexer system consists of all the selectors shown in Figure 12. It performs a routing function that brings the data from/to the appropriate memories to/from their destinations/sources. The interface allows the loading of data from the computer into the computer output buffer (in the UFTPP), unloading results from the computer input buffer to the computer and control of the UFTPP by the host computer. The control logic section initializes the processor, monitors progress of transform computation, buffer loading/unloading and communicates information concerning the status of the processor to the computer via the interface.

The processor is implemented on a total of 8 boards each measuring 24" x 18.5". Each board has 400 edge-connectors along one of the 24" edges. Of these, 80 are reserved for power and ground connections leaving 320 available for general use. A power and ground plane was laid down (one on each side of each board) using printed circuit technology to allow for low resistance power and ground distribution and to minimize ground loops. All other connections were

wirewrapped. The eight circuit boards communicate with each other via a wirewrapped backplane.

## 5.2. The Arithmetic Unit

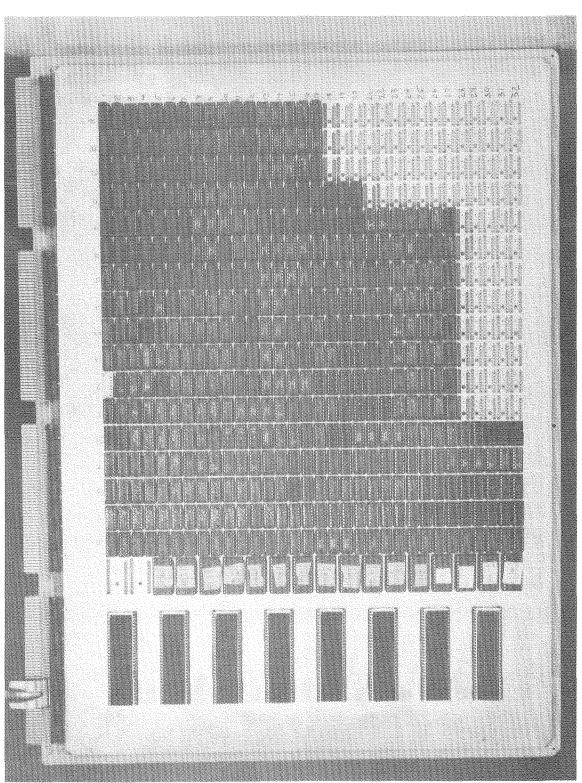

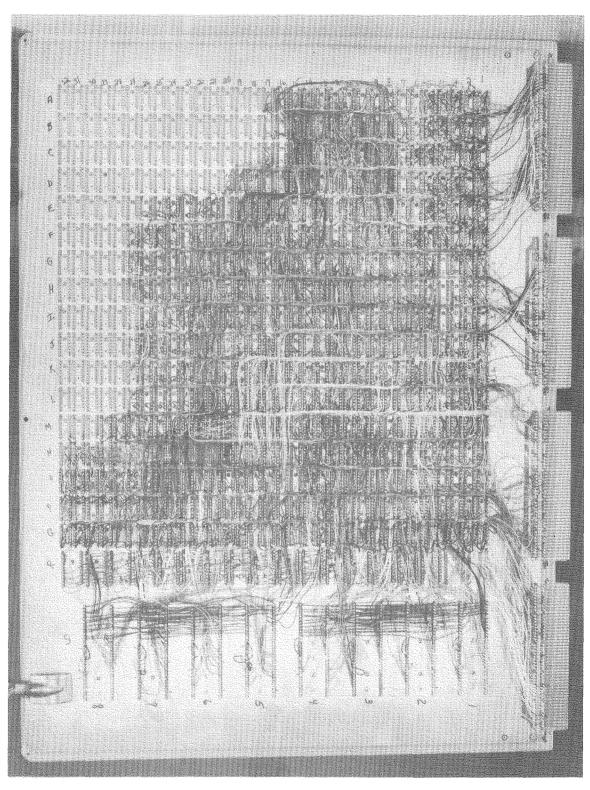

The arithmetic unit is implemented on two boards. Together they house a complex multiplier, the butterfly module, the sine/cosine memories, and the normalization circuitry. Each arithmetic board houses 8 LSI multiplier chips, 16 PROM chips and approximately 325 other MSI integrated circuits (e.g. 4-bit adders, 6-bit registers, etc.). Each board draws about 20 amps. Figure 13 shows the component side of one of the arithmetic boards and Figure 14 shows the wiring side of the same board.

In order to minimize the number of connectors necessary on each board, a technique similar to bit-slicing but applied to words has been employed. The output of the entire arithmetic unit is two complex values. Rather than having one board compute the first complex value and the other board the second one, a more efficient usuage of the connectors is made if one board compures the real parts of both complex values and the second board computes the imaginary parts. Thus, each board houses two real multipliers, a sine or cosine memory and half of a butterfly module. If we further divide the two complex inputs into their real and imaginary halves  $(C_1 = (R_1, I_1))$  and  $C_2 = (R_1, I_1)$  $(R_2, I_2)$ ), then the two real multipliers on the first board, Al, compute the values:  $R_1$  cos and  $I_2$  sin. The difference between these two values is the real part of the complex product,  $R_3$ , as indicated by Eq. 21 (Chapter 3). The multipliers on the second board, A2, compute the values  $\mathbf{R}_2$  sin and  $\mathbf{I}_2$  cos. The sum of these two is the imaginary part of the complex product, I2.

The basic algorithm for implementation of the real multiplier is as shown in Figure 11 (Chapter 4). However, since the 63-bit product is to be combined with a 32-bit value in the butterfly module, it is not necessary to compute all 63 bits. Only 32-bit accuracy is necessary at the output of the complex multiplier and it can be shown that only 37-bits need to be computed at the outputs of the real multipliers. Figure 15 shows the hardware configuration necessary to

Figure 13 CBB790-16710

Figure 14 CBB790-16712

Figure 15

implement a real multiplier of this nature. Simulations have shown that results obtained from this implementation do not differ from the 63-bit result by more than  $3 \times 10^{-6}$ . Since the numbers used in the UFTPP have 16 precision bits, their accuracy is  $\pm 2^{-17} = 7.6 \times 10^{-6}$ . Thus, the results in the 63-bit product are indistinguishable from the results in the 37-bit version. This represents a 50% reduction in hardware for each of the four real multipliers.

The real multipliers are pipelined as described in Chapter 3. Figure 15 indicates the 4 stages each contains. Between each of the stages are registers which capture the results from the previous stage at each clock interval.

The inputs to the multipliers are either data values from a memory or a sine/cosine value. The sine and cosines are stored in ROM. The sine ROM is on one board and the cosine on the other. Each board makes its value available to the other one. The addresses for the ROMs are generated through a bit reversal and masking function described by Pease [48].

In all of the simulations cited in Chapter 4, it was assumed that the sine and cosine values are represented with N-2 bits of precision. The two remaining bits allow for a range of  $\pm$  2 (actually  $-2 + 2^{-(N-2)}$  to  $+2 - 2^{-(N-2)}$ ). The sine/cosine memories are 32 bits wide using 30 bits of precision.

The data inputs to the arithmetic unit are pairs of complex values as indicated by the signal flow graph (Figure 4) in Chapter 2. If we label them  $\mathbf{C}_1$  and  $\mathbf{C}_2$ , then  $\mathbf{C}_2$  is the value to be "twiddled" (i.e. multiplied by the sine/cosine values) and  $\mathbf{C}_1$  is saved until the butterfly operation is ready to be performed.

The butterfly module consists of two adders and two subtractors. "Word-slicing" each results in half containing one adder and one subtractor (and produces either the real parts or the imaginary parts of the two complex pairs. The result from the half complex multiplier is added to and subtracted from the corresponding half of the other input value to yield the result. The first board, Al, computes  $R_1 + R_3 = R_4$  and  $R_1 - R_3 = R_5$  and the second board computes  $I_1 + I_3 = I_4$

and  $I_1 - I_3 = I_5$ . Depending upon the direction of the transform, this result may be divided by two (i.e. shifted right one bit with sign extension) to incorporate the 1/N normalization necessary for the forward transform. This result is then the output of the arithmetic module.

The forward transform computation is

$$H(f) = \frac{1}{N} \sum_{i=1}^{n} h(t) e^{-j2\pi f t/N}$$

and the inverse is

$$h(t) = \sum_{i=0}^{n} H(f) e^{j2\pi ft/N}$$