## **UC Santa Barbara**

## **UC Santa Barbara Electronic Theses and Dissertations**

## **Title**

On Design and Machine Learning Resiliency of Memristor- and eFlash-Memory-Based Strong Physical Unclonable Functions

## **Permalink**

https://escholarship.org/uc/item/7kv63803

### **Author**

Larimian, Shabnam

## **Publication Date**

2021

Peer reviewed|Thesis/dissertation

## University of California Santa Barbara

# On Design and Machine Learning Resiliency of Memristor- and eFlash-Memory-Based Strong Physical Unclonable Functions

A dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy} \\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Shabnam Larimian

## Committee in charge:

Professor Dmitri B. Strukov, Chair Professor Tim Sherwood Professor Li-C. Wang Professor Çetin Kaya Koç

| The Dissertation of Shabnam Larimian is approved. |

|---------------------------------------------------|

|                                                   |

|                                                   |

| Professor Tim Sherwood                            |

|                                                   |

| Professor Li-C. Wang                              |

| 1 Tolessor Li-C. Wang                             |

|                                                   |

| Professor Çetin Kaya Koç                          |

|                                                   |

| Professor Dmitri B. Strukov, Committee Chair      |

## On Design and Machine Learning Resiliency of Memristor- and eFlash-Memory-Based Strong Physical Unclonable Functions

Copyright  $\bigcirc$  2021

by

Shabnam Larimian

To my dear parents, Maryam and Javad, and my loving sister, Marjan, for their endless love, support, and encouragement.

To my beloved husband, Mahdi, who has been a constant source of love, help, support, and encouragement in my life and studies.

This journey would not be possible without them.

## Acknowledgements

First, I would like to express my sincere gratitude to my advisor Professor Dmitri B. Strukov for his continuous support, enthusiasm, immense knowledge, and patience. This dissertation and all the research work I have conducted during my PhD journey would not have been possible without him. I am thankful to have such the great mentor and advisor during my graduate life.

I would like to express my gratitude to the members of my examination committee, Professor Tim Sherwood, Professor Li-C. Wang, and Professor Çetin Kaya Koç for their valuable and constructive comments and suggestions.

I would like to thank my colleagues, Dr. Mohammad Reza Mahmoodi, Dr. Farnood Merikh-Bayat, Dr. Michael Klachko, Dr. Hussein Nili, Dr. Adrien Vincent, and Dr. Ping-Lin Yang for sharing their knowledge and work. The conversations with you were always helpful to enrich my research. I should thank my colleague, Dr. Itir Akgun, and my friend, Sogol Khanof, for being great and caring friends during my PhD journey.

I would like to express my deepest gratitude to my dearest family: my parents, my husband, and my younger sister. They are my strongest support and always there for me giving me the strength to reach for the stars and chase my dreams.

At the end, I would like to thank the Department of Electrical and Computer Engineering at the University of California, Santa Barbara, for all of the teaching assistant opportunities, administrative work, and IT infrastructure. I would also like to thank computing resource support from the Center for Scientific Computing from the California NanoSystems Institute (CNSI) at the University of California, Santa Barbara.

## Curriculum Vitæ Shabnam Larimian

## Education

| 2021 | Ph.D. in Computer Engineering, University of California, Santa         |

|------|------------------------------------------------------------------------|

|      | Barbara                                                                |

| 2015 | M.Sc. in Computer Engineering, University of California, Santa Barbara |

| 2014 | B.Sc. in Electrical Engineering, University of Tehran, Iran            |

## **Employment**

| 2015 - 2021 | Teaching Assistant, Department of Electrical and Computer Engineering, University of California, Santa Barbara |

|-------------|----------------------------------------------------------------------------------------------------------------|

| 2019        | Software Engineer Intern, Google                                                                               |

| 2018        | Software Engineer Intern, Google                                                                               |

| 2017        | Data Analyst Graduate Intern, Cadence Design Systems                                                           |

| 2016        | R&D Software Engineering Intern, Cadence Design Systems                                                        |

## Skills

- Python, Java, C/C++, SQLite, HTML, JavaScript, PHP, MySQL, Tcl, Perl, Verilog HDL, System Verilog

- MATLAB, Android, HSPICE, PSPICE, Cadence Virtuoso, XcitePI, ModelSim, NI Multisim, Xilinx Vivado, CodeVision AVR, Altera Quartus, Proteus, Arduino, Analog Discovery, Raphael, Filter Solution

## Awards

| 2021        | Outstanding teaching assistant award at University of California, Santa Barbara                        |

|-------------|--------------------------------------------------------------------------------------------------------|

| 2020        | ECE dissertation fellowship award at University of California, Santa Barbara                           |

| 2016 - 2020 | Outstanding teaching assistant award of ECE department at University of California, Santa Barbara      |

| 2019        | Grace Hopper Celebration scholarship award                                                             |

| 2017        | Nominee of UCSB outstanding teaching assistant award at University of California, Santa Barbara        |

| 2012        | Certificate of appreciation for teaching in applied electronics workshop at University of Tehran, Iran |

| 2008 | Ranked $71^{st}$ among 300,000 participants in the national university |

|------|------------------------------------------------------------------------|

|      | entrance exam in physics and mathematics, Iran                         |

| 2007 | Accepted in first step of mathematical Olympiad, Iran                  |

| 2007 | Accepted in first step of chemistry Olympiad, Iran                     |

| 2007 | First place of physics articles in student competition at University   |

|      | of Tehran Iran                                                         |

#### **Publications**

- S. Larimian, M. R. Mahmoodi, and D. B. Strukov, *Improving machine learning attack resiliency via conductance balancing in memristive strong PUFs*, in: SRC Techcon, Austin, TX, Sept. 2020, pp. 1-4.

- S. Larimian, M. R. Mahmoodi, and D. B. Strukov, Lightweight integrated design of PUF and TRNG security primitives based on eFlash memory in 55-nm CMOS, IEEE Transactions on Electron Devices, vol. 67 (4), pp. 1586-1592, 2020.

- M. R. Mahmoodi, Z. Fahimi, **S. Larimian**, H. Nili, H. Kim, and D. B. Strukov, A strong physically unclonable function with > 2<sup>80</sup> CRPs and < 1.4% BER using passive ReRAM technology, IEEE Solid-State Circuits Letters, vol. 3, pp. 182-185, 2020.

- M. R. Mahmoodi, H. Nili, Z. Fahimi, **S. Larimian**, H. Kim, D. B. Strukov, *Ultra-low power physical unclonable function with nonlinear fixed-resistance crossbar circuits*, in: Proc. IEDM'19, San Francisco, CA, Dec. 2019, pp. 30.1.1-30.1.4.

- M. R. Mahmoodi, H. Nili, **S. Larimian**, X. Guo, D. B. Strukov, *ChipSecure: A reconfigurable analog eFlash-based PUF with machine learning attack resiliency in 55nm CMOS*, in: Design Automation Conference (DAC), Las Vegas, NV, Jun. 2019, pp. 1-6.

#### Abstract

On Design and Machine Learning Resiliency of Memristor- and eFlash-Memory-Based Strong Physical Unclonable Functions

by

#### Shabnam Larimian

The emergence of the Internet of Things (IoT) has enabled an unprecedented expansion of interconnected networks and devices over which a huge amount of personal and/or sensitive data is carried. As a result, privacy and security issues are among the most significant challenges in designing IoT devices. These challenges can hardly be addressed using conventional cryptographic approaches because they rely on storing secret keys in memories, which not only are vulnerable to physical and side-channel attacks but also consume huge area and vast amounts of power.

Hardware-based security approaches such as physical unclonable functions (PUFs) have attracted considerable attention as replacements for conventional methods. PUFs are well suited to a wide spectrum of security applications including key generation and authentication because they generate secure keys on the fly (rather than explicitly storing any security-critical information). This is achieved by utilizing electronic devices that entail inherent sources of randomness, which in turn help create unique keys for different physical entities.

Recently, a variety of emerging nano-scale non-volatile memories are being explored for use in the design of PUFs including memristors and embedded flash (eFlash) memories. The highly non-linear current-voltage characteristics and the inherent process variations of these memory devices make them promising candidates for designing PUFs. Additionally, the ultra-low power consumption and low computation time of these de-

vices enable their use in applications with stringent requirements on energy efficiency and throughput.

This dissertation presents memristor- and eFash-memory-based PUF designs that show promising security characteristics such as near-to-ideal uniformity, diffuseness, robustness, and reliability. The robustness is verified by demonstrating the high output randomness with the test suits of the National Institute of Standards and Technology and by studying various machine learning attacks.

The specific contributions of this dissertation is that investigates several unexplored areas in crossbar-memory-design PUFs, e.g., finding optimal design for maximizing robustness characteristics, studying the impact of the capacity of machine learning models on robustness, and the impact of environmental change and thermal noise on reliability.

# Contents

| $\mathbf{C}_{1}$ | furriculum Vitae                                                 | vi   |

|------------------|------------------------------------------------------------------|------|

| $\mathbf{A}$     | bstract                                                          | viii |

| 1                | Introduction                                                     | 1    |

| 2                | Preliminaries and Prior Work                                     | 4    |

|                  | 2.1 Physically Unclonable Functions (PUF)                        | 4    |

|                  | 2.2 True Random Number Generator (TRNG)                          | 12   |

|                  | 2.3 Prior Work                                                   | 14   |

|                  | 2.4 Summary                                                      | 17   |

| 3                | Improving Machine Learning Attack Resiliency via Conductance Bal | _    |

|                  | ancing in Memristive Strong PUFs                                 | 21   |

|                  | 3.1 Background: Memristive Strong PUF                            | 22   |

|                  | 3.2 Modeling Approach                                            | 24   |

|                  | 3.3 Evaluation Metrics                                           | 27   |

|                  | 3.4 PUF Optimization                                             | 28   |

|                  | 3.5 Hardware Imperfection                                        | 39   |

|                  | 3.6 Discussion and Summary                                       | 40   |

| 4                | Lightweight Integrated Design of PUF and TRNG Security Primitive | s    |

|                  | Based on eFlash Memory in 55nm CMOS                              | 43   |

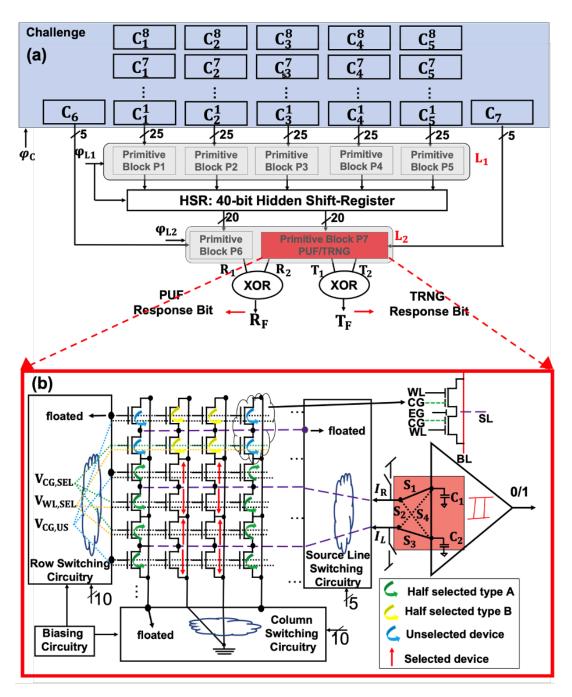

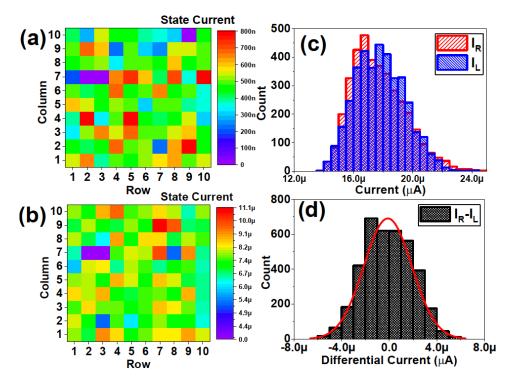

|                  | 4.1 Unified Entropy Generator                                    | 45   |

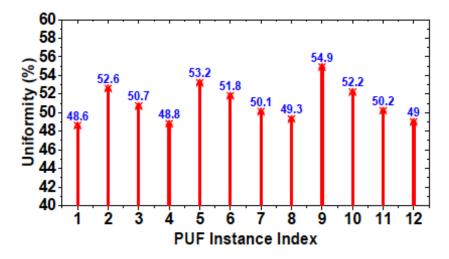

|                  | 4.2 Experimental Results                                         | 50   |

|                  | 4.3 Discussion and Summary                                       | 64   |

| 5                | Conclusion and Future Opportunities                              | 66   |

| A                | Simulation Setup                                                 | 70   |

| Ri               | ibliography                                                      | 72   |

# Chapter 1

# Introduction

With the fast and continuing development of Internet of Things, smart devices and interconnected networks have become ubiquitous for everyday tasks. In many of those tasks,

significant volume of personal and/or sensitive information is carried which raises security and privacy issues. The conventional cryptographic approaches can hardly address

those challenges because they rely on storing secret keys in memories and assume that

the keys are unknown to adversary. However, it is difficult to uphold this assumption

because the memories are vulnerable to physical and side-channel attacks. Moreover, to

store the secret keys, the memories consume huge area and power. As a result, securing

a resource-constraint, integrated system is an ongoing challenging problem [1, 2, 3, 4].

As a replacement for conventional cryptographic approaches, hardware-based security approaches such as physical unclonable functions (PUFs) have attracted substantial attentions. PUFs utilize the inherent randomness in electronic devices to generate keys on the fly rather than storing them in non-volatile memories which makes PUFs well suited to variety of security applications such as key generation and authentication.

The conventional PUFs utilize uncontrollable process variation in conventional Complementary-Metal-Oxide-Semiconductor (CMOS) fabrication technology. Process variations in purely Introduction Chapter 1

CMOS analog circuits often limit computation accuracy and result in large performance overheads due to over-designing and calibration techniques. As a result of scaling down to nano region, the next generation of PUFs will be implemented using nano-electronic devices ([5]) such as memristors ([6]) and flash memories ([7]) whose highly non-linear current-voltage characteristics and the inherent process variations make them promising candidates for designing PUFs. Moreover, the mentioned nano-electronic devices are CMOS compatible and have ultra-low power consumption and low computation time [8, 9].

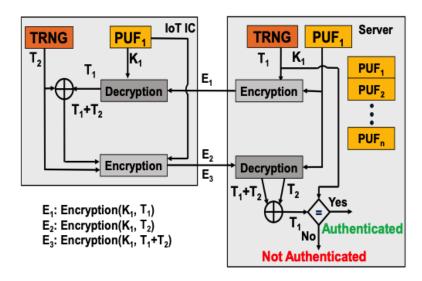

This thesis contains several contributions to the field of PUFs. We have proposed two techniques to boost memristor-based strong PUFs robustness against machine learning. Furthermore, we present a lightweight, integrated flash-memory-based design of PUF and true random number generator (TRNG) on a shared silicon which can be effectively used in mutual authentication applications. Below are the summary of the chapters.

Chapter 2. In this chapter, after defining PUF, we discuss its main types, applications, and cryptographic metrics. Then, we briefly discuss how TRNGs are associated with PUFs. Finally, we summarize the prior work on PUFs.

Chapter 3. Previous works have shown excellent prospects for implementing strong PUFs with memristive crossbar circuits. In this chapter, we propose two techniques for boosting the robustness of such PUFs to machine learning attacks. The general idea behind both proposals is to maximize the contribution of each crosspoint device to the PUF output to make the response less predictable. Specifically, we present results for choosing an optimal ratio of selected rows and columns and investigate in detail the improvements in robustness due to the balancing of device conductances in the crossbar array. The effectiveness of the proposed algorithm for conductance balancing is confirmed by modeling the response of two-sided PUF based on a 20×20 crossbar memristive circuit with a multilayer perceptron network. Then, we explore some open questions which

Introduction Chapter 1

require in-depth analysis. Specifically, we quantify the effect of device nonlinearity and device analog-tunability. We show that nonlinear, analog memristive PUFs outperform the PUFs that have either linear or digital devices. Finally, we explore the effect of stuck-at fault devices (non-ideal yield) on PUFs uniformity. Indeed, by modeling this hardware imperfection, we show that the proposed algorithm results in a more-robust PUF.

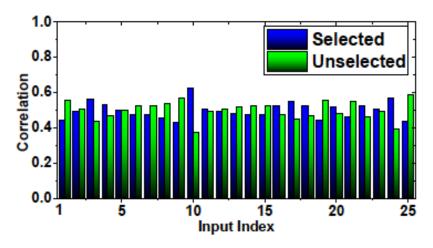

Chapter 4. In chis chapter, we present a lightweight, integrated design of flash-memory-based PUF and TRNG on a shared silicon. Specifically, the randomness in nonlinear I-V characteristics and temporal current fluctuations of embedded flash memories are exploited to generate static entropy (for PUF functionality) and dynamic entropy (for TRNG functionality). A time-multiplexed architecture is designed to enhance the security and expand the challenge-response pair space to  $10^{211}$ . Experimental results demonstrate 50.3% average uniformity, 49.99% average diffuseness, and native  $\leq 5\%$  bit error rate. Moreover, accelerated aging measurements is done for the designed PUF. The measurements indicate stable PUF response after 900 minutes of baking at 85°C. The analysis of the measured data also shows strong resilience against machine learning attacks and possibility for extremely energy efficient, 0.56 pJ/b operation.

# Chapter 2

# Preliminaries and Prior Work

Physically unclonable functions and true random number generators are two main cryptography primitives. The former is used to implement secure secret key generation and low-cost device authentication whereas the latter generate random numbers from a physical process.

This chapter presents a concise background on physically unclonable functions. After defining physically unclonable function, its main types, applications, and cryptographic metrics are discussed. Then, it is discussed how true random number generators are associated with physically unclonable functions. Finally, the prior work on physically unclonable functions are summarized.

## 2.1 Physically Unclonable Functions (PUF)

Nowadays, cryptographic keys are the foundation of secure cryptographic protocols in electronic systems and are typically stored in non-volatile memories (NVMs). Because the key is assigned by an outside source and stored in a NVM, it is vulnerable to be copied and it is not trivial to maintain its security without dedicated protection.

Physical unclonable function, or PUF, is a cost-effective alternative approach that does not have the mentioned issues. Indeed, PUF is a class of hardware security primitives that generates cryptographic keys by exploiting the inherent random variations introduced during manufacturing process. Because the generated key is internal and is not assigned by an outside source, it is infeasible to clone it and create an identical physical copy. This form of randomness is inexpensive to access and does not affect the original functionality of the devices [10, 11]. Additionally, by leveraging intrinsic or extrinsic randomness sources, PUF works as a one-way function that maps an input (challenge) to an output (response). The set of generated challenge-response pairs (CRPs) are then used in different applications. Below, PUF types (based on number of CRPs), applications, and metrics are discussed.

## 2.1.1 Types

PUFs are typically classified as weak and strong based on the size of CRPs. This usually corresponds to how the number of CRPs increases when device size increases (scaling rate). Weak PUF has a small access-restricted CRPs (due to linear or polynomial scaling rate) which means that the full set of CRPs can be read if an attacker holds physical possession of the device. While it is not possible to reproduce the physical PUF itself, the attacker can deduce the mapping function with the knowledge of observed CRPs. Strong PUF, on the other hand, has huge number of CRPs (due to exponential scaling rate) that prevents a full read-out of CRPs even if the attacker gains physical access for a considerable time. This makes PUF mapping function resilient to learn or reproduce [8, 12, 2].

## 2.1.2 Applications

The most fundamental security applications of Internet of Things are key generation and authentication. Key generation (and key storage) requires a random source to generate unique keys (and a protected memory to hide them from an attacker). Comparatively, authentication requires validity of the identifying information. Depending on the application, either one-way or mutual authentication should be implemented. A common authentication approach relies on the challenge-response protocols where the verifier provides a challenge and the prover provides the response to be authenticated. In this section, some of the PUF security requirements for each of the mentioned applications are reviewed.

## **Key Generation**

Secure keys are typically generated by seeding pre-stored keys to pseudorandom number generators [13]. However, by using PUFs, the unique keys can be generated on the fly which eliminates the need for key storage. Because this application typically needs a limited capacity and CRP space, weak PUF is a promising candidate for it. Additionally, in this application, the generated keys should be reliable. Indeed, the PUF response should be reproducible across process, voltage, and temperature (PVT) variations. Because no error is tolerable in key generation applications, error correction codes and algorithms are often applied to improve the PUF reliability. Furthermore, the weak PUFs being considered in key generation application should have high throughput and low power and area overhead [8].

#### Authentication

For authentication applications, it is crucial for PUF to be unpredictable. Indeed, the PUF should be both physically and mathematically unclonable. For this purpose, the CRP space should be large enough to avoid man-in-the-middle attack by changing the challenge after each run. Additionally, the PUF circuit should be complex enough that it cannot be modeled or deduced even if an attacker has physical access to it and observe a certain number of CRPs. As a result of the mentioned requirements, strong PUFs are the best candidates for the authentication applications [8].

## 2.1.3 Quality Metrics

Assessing if a physical PUF behaves as a theoretically ideal PUF is not trivial. To assist the evaluation process, several metrics are suggested over the years [14, 15, 16, 1, 17, 18]. Here, the main and common metrics are discussed.

#### Fractional Hamming Weight or Uniformity

The Hamming weight (HW) of a vector is the number of non-zero elements in the vector. For a binary vector, HW is equal to the number of '1's in the string. Because the length of vector may vary, HW is normalized by dividing its value by the vector length. This is called fractional Hamming weight (FHW) or uniformity (UF) and is calculated as

$$FHW(R) = UF(R) = \frac{1}{|R|}HW(R) = \frac{1}{|R|}\sum_{i=0}^{|R|-1} (R_i)$$

where |R| is the length of response vector. This metric is used to assess the PUF randomness by measuring the balance of its response vector and is usually reported in percentage. The ideal value for UF is 50% indicating a perfect balance between possible responses

(same number of '0's and '1's in a response vector). UF value that is either much below or much above 50% can indicate that PUF responses are biased, and thus PUF might have non-ideal behavior.

## Fractional Hamming Distance or Diffuseness

The Hamming distance (HD) between two equal-length vectors is defined as the number of positions at which the corresponding elements are different. Because the length of vector may vary, HD is normalized by dividing its value by the vector length. This is called fractional Hamming distance (FHD) or diffuseness (DF) and is calculated as

$$FHD(R_i, R_j) = DF(R_i, R_j) = \frac{1}{|R|} HD(R_i, R_j) = \frac{1}{|R|} \sum_{i=0}^{|R|-1} (R_i - R_j)$$

where  $R_i$  and  $R_j$  are two equal-length vectors of the same PUF under different challenges. This metric is used to assess PUF randomness by measuring dissimilarity among response vectors of the same PUF under different challenges and is usually reported in percentage. The ideal value of diffuseness is 50% which shows the complete dissimilarity between PUF response when different challenges are applied. This metric that represents self-dissimilarity has little meaning in certain cases such as a weak SRAM PUF which has a single CRP.

#### Uniqueness

Uniqueness (UQ) is another metric that assess PUF randomness. It measures the dissimilarity of responses of different PUFs to the same challenge. Uniqueness is defined as

$$UQ(R,\bar{R}) = \frac{1}{|R|} HD(R,\bar{R}) = \frac{1}{|R|} \sum_{i=0}^{|R|-1} (R - \bar{R})$$

where R and  $\bar{R}$  are two equal-length response vectors of different PUF under the same challenge and HD is the Hamming distance of the two vectors. This metric is used to assess how different PUFs respond uniquely to the same challenge. UQ is usually reported in percentage and its ideal value is 50%. Any large deviations from this ideal value demonstrate correlation between different PUF instances.

## Bit Error Rate

Bit error rate (BER) is used to measure PUF reliability and reproducibility. BER shows the difference between the same PUF response under the same challenge but different situations caused by variation in temperature, variation in voltage, or noise. BER is usually reported in percentage and its ideal value is 0% meaning that PUF always produce the same response for a given challenge. When BER is not close to 0%, excessive error correction is needed to reduce it, which is costly in terms of computation time, energy consumption, and memory usage.

#### Entropy

In information theory, entropy, a basic quantity associated to any random variable, is interpreted as the average level of information or uncertainty inherent in the variable's possible outcomes. Based on Shannon equation, entropy (H(X)) is defined as

$$H(X) = -\sum_{i=1}^{n} p_i log_2(p_i)$$

where  $p_i = P(X = x_i)$  is a probability of a random variable X that can take on values  $x_1, x_2, \ldots, x_n, p_i \ge 0$ , and  $\sum_{i=1}^n p_i = 1$ . The entropy is expressed in the number of bits that carry information. For example, in a truly random binary process  $(p_i = 0.5)$ , the entropy is calculated as

$$H(X) = -(0.5log_2(0.5) + 0.5log_2(0.5)) = 1$$

The maximum entropy (1 in a binary process) indicates the maximum uncertainty of next response bit that is not observed yet [9, 19].

#### Correlation

Correlation is a metric that shows if the PUF output has any bias towards any of its inputs. Although many of the above metrics indirectly represents correlation, it can be directly calculated by the percentage of '0's or '1's in the output when one specific input changes and the other inputs stay the same. The ideal correlation value if 50% which means the output is 0 or 1 with equal probability regardless of the specific bit in challenge.

## National Institute of Standards and Technology (NIST) Test Suite

Various statistical tests can be applied to a sequence to evaluate its randomness by assessing the presence or absence of a pattern which if detected would indicate that the sequence is not random. The National Institute of Standards and Technology (NIST) test suite ([19]) is one of the online public statistical packages consisting of sixteen tests that is developed to test the randomness of binary sequences by calculating P-value. P-value is the probability that a sequence less random than the tested sequence can be generated. The P-value of 1 indicates that the sequence is perfectly random while the P-value of 0 means that the sequence is completely non-random. A significance level can be chosen as a threshold for P-value so that any value higher/lower than that indicates that the sequence is random/non-random. Typically, the significance level is chosen in the range of [0.001, 0.01]. The significance level that is used in NIST test suite in this

thesis is 0.01. This means that if the P-value of a sequence is greater/less than 0.01, the sequence passes/fails that test.

## Predictability (Machine Learning Test)

An ideal PUF should be unpredictable to attackers. To perform predictability analyses, machine learning (ML) models are considered as they are currently the most effective attack form for strong PUFs [13]. The machine learning models would be trained on a subset of CRPs and then would be tested on a mutually exclusive subset of CRPs. The input and output of the machine learning models would be connected to the challenge and response of PUF, respectively. For a single-output PUF, different binary classifiers such as logistic regression (LR), support vector machine (SVM), and multilayer perceptron (MLP) can be used. In an ideal PUF, the accuracy of the ML test should be 50% which means that the attacker cannot model the PUF by accessing a subset of CRPs.

The LR algorithm uses logistic (sigmoid) function to find the relationship between input and output. The sigmoid function is an S-shaped curve that can take any real-valued number and map it to a value between 0 and 1. LR is mostly used for a linear-separable data. Therefore, it might not be the best ML algorithm for strong PUFs where the output is a nonlinear function of the inputs.

The SVM algorithm creates a hyperplane or line (decision boundary) which separates data into classes. It uses the kernel trick to find the best line separator (decision boundary that has same distance from the boundary point of both classes). In other words, SVM tries to reduce the error by finding the best margin (distance between the line and the support vectors) that separates the classes. Although SVM is a more powerful way of learning complex nonlinear functions (comparing to LR), it runs very slow on huge amount of data. As a result, for a PUF with huge exponential CRP space, SVM is not the most efficient ML algorithm.

The MLP algorithm is a class of feedforward neural network consists of at least three layers: an input layer, a hidden layer, and an output layer. Except from the input nodes, each node is a neuron that uses a nonlinear activation function (e.g. sigmoid). MLP uses backpropagation technique for training. Because MLP has multiple layers and utilizes nonlinear activation function, it can be used to distinguish data that is not linearly separable. That is why, MLP is a good ML algorithm candidate to asses the predictability of strong PUFs.

Based on the PUF design, the attacker can choose any ML algorithm to model PUF behaviour. An ideal PUF should be resilient to any type of ML algorithms. In other words, the trained ML model should ideally has 50% accuracy on the unseen data meaning that the attacker cannot model the relationship between the input and the output of PUF using ML algorithms.

## 2.2 True Random Number Generator (TRNG)

It is important to mention that the process variation explained in Section 2.1 can be a source of randomness for true random number generators (TRNG) as well. Indeed, process variation leads to two types of random behavior namely static and dynamic. While the static response behavior is used in PUF applications, the dynamic response behavior (which is mostly due to the very small differences in operating conditions and circuit noise) is used in TRNG applications. These two randomness sources can be combined in a circuit and provides both PUF and TRNG functionalities for cryptography applications. The unified design will be very efficient in terms of area, power, and energy [16].

In order to evaluate the statistical properties of TRNG output, different metrics need to be calculated and measured. In this section, three of well-known quality metrics are reviewed and defined which ensure the presence of cryptography quality randomness.

The first metric to evaluate the TRNG output sequence is NIST test suite that is explained in detail in Section 2.1.3. NIST test suite consists of sixteen tests to evaluate randomness of a binary sequence. The generated TRNG sequence should pass all of the designed test with a sufficient significance level, so that we can use it in cryptographic applications.

The second metric to evaluate the predictability of TRNG output sequence is ML algorithms. In TRNG applications, we want to make sure the output is not predictable given the previous part of the output sequence. Due to the importance of past output bits, history-based ML algorithms such as long short-term memory could be used. In these algorithms, the output sequence of TRNG sequence would be used for both input and output [20]. Specifically, N adjacent bits within response sequence are used as one input, whereas the immediate bit after the input bit sequence is used as the output. Ideally, the ML accuracy should be 50% for the TRNG output sequence meaning that the output is not predictable even if the past N bits are given.

The third metric that is used to evaluate TRNG output sequence is auto-correlation. Auto-correlation is a mathematical metric that identifies randomness of a sequence as well as independence of each bit of the sequence with respect to the previous bits. Auto-correlation  $(R_{XX}[k])$  is calculated by the expectation between two sub-sequences of TRNG output sequence (x) that are separated by k-lag. Auto-correlation can be rewritten as

$$R_{XX}[k] = \frac{E[x_i - \mu, x_{i+k} - \mu]}{\sigma^2}$$

where  $k \in [1 - N, N - 1]$  is the lagged interval, N is the length of sequence x,  $\mu$  and  $\sigma$  are the mean and the standard deviation of x. In an ideal case, the auto-correlation of

a random sequence has a zero auto-correlation for  $k \neq 0$  and has maximum value of 1 when k = 0. This means that each sub-sequence has no correlation with the other lagged sub-sequences, resulting in a totally random sequence.

## 2.3 Prior Work

Pappu et al. [21] introduced an optical PUF where the output (response) is a function of the input laser location/polarization (challenge). The optical PUF requires large external measurement devices and is difficult to be integrated on resource-constrained hardware device. Additionally, its reliability is highly dependent on the accurate calibration of the input location.

Gassend et al. [22] then proposed the Arbiter PUF (APUF) which generates response based on the time difference between the two signal paths. The APUF consists of serially connected individual stages, where the path through each stage is determined by the input bit vector. Because the APUF is based on linear additive blocks, it is vulnerable to modeling attacks if an adversary gain access to the CRPs [23, 24]. To increase the complexity of such modeling attacks, some variants of the APUFs such as the XOR-APUFs ([23, 25]) and feed forward APUFs ([23, 26]) are proposed. To implement APUFs, latches are used which can cause meta-stable state, leading to poor reliability. To overcome the meta-stability issues, another type of delay-based PUFs, namely Ring Oscillator PUF (ROPUF) is proposed in [22, 25]. The ROPUF contains ring oscillators which are connected to two counters through two multiplexers. The select lines of the multiplexers become the challenge input to the PUF design. The counters count the number of oscillations. The comparison between the two counted number generate the output (either 0 or 1). Due to the manufacturing variations in the fabrication phase, the oscillation frequencies will not be the same for all ring oscillators, so the output bit will

change each time that two ring oscillators are selected through the multiplexers. The proposed ROPUF design is then improved in [27] and [28]. [29] includes an overview of different ROPUFs.

In addition to the delay-based PUFs, there are other types of PUFs such as traditional memory-based PUFs (e.g. SRAM). As explained in [30, 31], a SRAM cell consists of six transistors whose initial random states determine the PUF output when power is applied to the SRAM cell. The overview of other conventional PUF architectures is studied in [1] and [14]. The mentioned conventional PUFs exploit uncontrollable process variation in conventional Complementary-Metal-Oxide-Semiconductor (CMOS) fabrication technology.

Although the conventional CMOS-based PUFs are well established in industry, the technological developments are particularly important for building PUFs. As a result, the next generation of PUFs will be implemented using emerging nano-electronic devises [5]. Nano-technologies such as memristors ([6]) and flash memories ([7]) provide new opportunities due to severe inherent randomness (as a result of scaling down to nano region), low-energy consumption, simple fabrication, and CMOS compatibility [8, 9].

The memristor- and flash-memory-based weak PUFs operate based on the intrinsic statistical (mostly in switching characteristics) properties of a single memory cell in an array of devices (Figure 2.1). Therefore, the CRP space is a linear function of the array size which makes the output predictable after observing a subset of the CRPs. As shown in Figure 2.1, with each CRP, a challenge is used as the address to select rows and columns. The response is then generated by comparing the resistance of two selected devices or by comparing the current of the selected device with a reference current [32, 33, 34, 35, 36, 37, 38, 39, 40, 41, 42, 43]. Table 2.1 provides the comparison between the experimental features of memristor- and flash-memory-based weak PUFs [8].

The memristor- and flash-memory- based strong PUFs operate based on the intrinsic

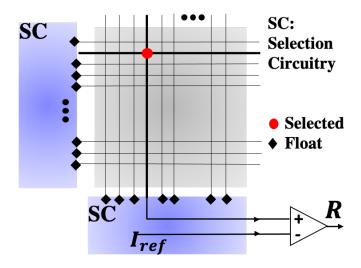

Figure 2.1: Basic architecture of NVM-based weak PUF.

statistical properties (mainly device-to-device variations) of multiple memory cells in an array or layers of arrays of devices. The basic idea is shown in Figure 2.2 where the current of two paths (which includes the sneak-path currents) are compared with each other to ensure that all the devices (selected, half-selected, and non-selected) are contributing to the response.

Figure 2.2: Basic architecture of NVM-based strong PUF.

The first demonstration of the NVM-based strong PUF is proposed in [20, 44] which

utilizes the variations in the nonlinear, analog tunable I–V characteristics of passive memristors. The basic building block of the proposed PUF is a CMOS-compatible two-level stack of 10x10 memristor arrays. In each CRP, 5 rows and 2 columns are selected. Thus, the CRP space is  $\binom{20}{5} \times \binom{10}{2} \approx 7 \times 10^7$ . The experimental data for about  $4 \times 10^7$  collected CRPs show 50% uniformity, 50% uniqueness, 50% diffuseness, and 1.5% reliability. Moreover, the responses pass NIST tests and show resiliency against a 30 ×  $250 \times 250 \times 1$  MLP classifier.

The proposed PUF ([20, 44]) has been then extended in [45] using the same source of randomness. [45] consists of a  $20 \times 20$  memristors whose conductance values are chosen from a Gaussian distribution. It is shown that the devices which have the tail values of the distribution could result in a week bias in the output. To overcome this issue, two auxiliary lines in the array are used to generate the response in two cycles. In the first cycle, the currents sensed at the auxiliary columns are compared, and then, it is XORed by the result of the generated bit in the next cycle to produce the final bit. This procedure is introduced as resistive-XOR PUF (RX-PUF). RX-PUF show 50.04% uniqueness, 50% diffuseness, and 4.1% reliability. In addition, the responses pass NIST tests. Moreover, the results show that RX-PUF has high resiliency against a  $40 \times 500 \times 500 \times 1$  MLP classifier which is trained on a subset of observed CRPs ( $\approx 120 \times 10^3$ ) and then tested on a mutually exclusive observed set  $(5 \times 10^3)$ . Table 2.2 provides the comparison the experimental features of memristor-based strong PUFs [8].

## 2.4 Summary

We started this chapter with a description of PUF, its main types, and applications. Next, we discussed the most important metrics by which the quality of PUFs is assessed. Then, we discussed the description of TRNG followed by the main metrics by which the randomness of TRNGs are evaluated. Finally, we provided a summary of prior work on PUFs.

| NIST Test         | 1                                    | ı                                    | PASS                                | 1                                 | PASS                              | ı                                                       | PASS                             | ı                     | PASS                                             | ı                                 | 1                                           |                                                                                                                                                                                                                                                                                                                   |

|-------------------|--------------------------------------|--------------------------------------|-------------------------------------|-----------------------------------|-----------------------------------|---------------------------------------------------------|----------------------------------|-----------------------|--------------------------------------------------|-----------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DF<br>(μ, σ)      | -                                    |                                      | -                                   | -                                 | 50, 2                             | -                                                       | -                                |                       | -                                                |                                   |                                             | ntages. **                                                                                                                                                                                                                                                                                                        |

| UQ<br>(μ, σ)      | -                                    | 50, 4                                | 49.8, -                             | 49.8, 4.9                         | -                                 | -                                                       | 29.9, 4.3                        | 30, -                 | 50, 3                                            | -                                 |                                             | ns of percer                                                                                                                                                                                                                                                                                                      |

| UF<br>(μ, σ)      | 50, 5                                | 51, 6                                | -                                   | - '09                             | 50, 4                             | -                                                       | 50, 2.8                          | ,                     | 50, 2                                            | -                                 | ,                                           | ented in terr                                                                                                                                                                                                                                                                                                     |

| REL               | 3.5**                                | 2                                    | 0.49                                | 0                                 |                                   | ı                                                       | 9-99>                            | 0.35                  | 0~                                               | ı                                 |                                             | ind are pres<br>fully switche                                                                                                                                                                                                                                                                                     |

| Randomness Source | Small signal*** stochastic switching | Large signal*** stochastic switching | Small signal stochastic programming | Small signal stochastic switching | Small signal stochastic switching | Large signal stochasticswitching in competitive 2R cell | Small signal stochasticswitching | Write speed variation | Oxide rupture in 55nm commercial Flash supercell | Small signal stochastic switching | Small signal stochastic switching variation | * REL, UF, UQ, and DF stand for reliability (at ~80°C unless specified), uniformity, uniqueness, and diffuseness and are presented in terms of percentages. ** Average BER at 25°C *** Small signal means the devices are operated in low-disturbance regime and large signal means that they are fully switched. |

| Capacity          | 2000                                 | 1                                    |                                     | 128                               | 256                               | ı                                                       | 8Kb                              | 256Kb                 | 64Kb                                             | ı                                 | ,                                           | 0°C unless<br>in low-distu                                                                                                                                                                                                                                                                                        |

| Demo Size         | 128x8                                | -                                    | -                                   | 128x8                             | 1Kb                               | -                                                       | 128×128                          | 256Kb                 | 64Kb                                             | 384Kb                             | ,                                           | ability (at ~8                                                                                                                                                                                                                                                                                                    |

| Cell Size<br>(F²) | -                                    | -                                    | 42                                  | -                                 | •                                 |                                                         | 340                              |                       | 218                                              | -                                 |                                             | stand for relia                                                                                                                                                                                                                                                                                                   |

| NVM               | 1T1R RRAM                            | OT1R RRAM                            | 1T1R RRAM                           | 1T1R RRAM                         | 1T1R RRAM                         | OT2R RRAM                                               | 1T1R RRAM                        | 1T1R RRAM             | 1.5Tr Flash                                      | Flash                             | SONOS<br>Flash                              | * REL, UF, UQ, and DF stand for re<br>Average BER at 25°C<br>*** Small signal means the devices                                                                                                                                                                                                                   |

| Ref.              | 2017                                 | 2019                                 | 2016                                | 2016                              | 2017                              | 2019                                                    | 2019                             | 2018                  | 2018                                             | 2012                              | 2015                                        | * REL, UF, UQ, and D<br>Average BER at 25°C<br>*** Small signal mean                                                                                                                                                                                                                                              |

Table 2.1: Comparison of experimentally demonstrated memristor- and Flash-memory-based weak PUFs.  $\,$

| Ref.      | NVM                                                                      | Cell Size<br>(F²)              | Demo Size Capacity            | Capacity            | Randomness Source                                                                                                                                                                              | REL*         | UF*<br>(μ, σ) | υQ*<br>(μ, σ) | DF*<br>(μ, σ) | ML** Test |

|-----------|--------------------------------------------------------------------------|--------------------------------|-------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|---------------|---------------|-----------|

| 2016      | OT1R RRAM                                                                | 4                              | 12x12 ~1000                   | ~1000               | Switching threshold variations                                                                                                                                                                 | -            | -             | 46, 3         | -             | YES       |

| 2018      | OT1R RRAM                                                                | 4                              | 3D 2x10x10 ~7x10 <sup>6</sup> | ~7x10 <sup>6</sup>  | Variations in nonlinearity and tunability                                                                                                                                                      | 1.5          | 50,-          | 50, 0.9       | - '09         | YES       |

| 2018      | OT1R RRAM 4                                                              | 4                              | 20x20 ~40x10 <sup>6</sup>     | ~40x10 <sup>6</sup> | Variations in nonlinearity and tunability                                                                                                                                                      | 4.1          | 4.1 50.04, -  | -             | 50,6          | YES       |

| * REL, UF | * REL, UF, UQ, and DF stand for re<br>** ML stands for machine learning. | stand for reli-<br>e learning. | ability (at ~80               | %C unless           | * MEL, UF, UQ, and DF stand for reliability (at ~80°C unless specified), uniformity, uniqueness, and diffuseness and are presented in terms of percentages. ** ML stands for machine learning. | ind are pres | ented in terr | ns of perce   | ntages.       |           |

Table 2.2: Comparison of experimentally demonstrated memristor-based strong PUFs.

# Chapter 3

# Improving Machine Learning Attack Resiliency via Conductance Balancing in Memristive Strong PUFs

As thoroughly explained in Chapter 2, among various emerging technology PUFs [8, 10], the implementations based on memristive crossbar circuits are especially promising due to their simple and low-cost fabrication process, small footprint, and CMOS integration compatibility [20]. Indeed, prior work has shown memristive strong PUFs with superior resiliency against most powerful modeling attacks as compared to CMOS PUFs [8]. Memristive PUFs utilize spatial device-to-device variations, e.g., in I-V nonlinearity [20, 34, 45], in an array of memory cells to generate random responses. Promising results were also reported for reliability and statistical properties of generated keys, as well as physical performance. The main goal of this study is to further improve the robustness of the memristive strong PUFs based on an architecture presented in [20], [45], [13].

In addition to the PUF robustness improvement, some of the open questions in designing the memristive strong PUFs are explored in this study. For example, the effect of device nonlinearity and leakage current are quantified. Additionally, the impacts of device analog-tunability, crossbar uniformity, and selection scheme are explored.

The rest of the word is organized as follows: Section 3.1 provides a brief overview of the memristive strong PUF circuits. Section 3.2 and 3.3 describe the memristors modeling approach and the evaluation metrics used in this study, respectively. Section 3.4 introduces PUF optimization methods and their results. Section 3.5 explores the hardware imperfection. Finally, Section 3.6 is dedicated to the discussion and summary of the work.

## 3.1 Background: Memristive Strong PUF

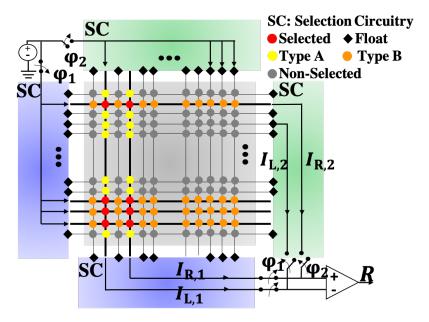

The focus of this study is on the strong PUF circuit (Figure 3.1), consisting of an  $M\times M$  array of 0T1R memristive crossbar array and its peripheral circuitry (SCs) used for biasing specific rows and columns according to the applied challenge. The memristive PUF circuit can operate in either one-sided [20, 35] or two-sided [46] approaches. The one-sided scheme requires only half of the peripheral circuitry, e.g. left and bottom SCs shown with blue color. Specifically, one bit of the output (i.e. response) is generated when applying 2M bit input (challenge). The '1's in the first M bits of the input encode the positions of "selected" rows (out of M total). Similarly, the remaining M bits specify the position of "selected" columns. All selected rows are biased with a read voltage  $V_{read}$ , all selected columns are grounded, while all the remaining lines (rows or columns) are kept floating. The output bit is computed by comparing the total current flowing in the left half of the selected columns  $I_L$  to that of the right half  $I_R$ , i.e. output is 1 if  $I_R > I_L$  and 0 otherwise.

With such a selection scheme, the devices can be classified according to the type of rows/columns they are connected to. The device is called "selected" when both its row and column are selected. The device is called "half-selected" when either its row (type B) or its column (type A) are selected, while the other electrode is floating. The device is called "non-selected" when both of its row and column are floating. Assuming that n rows and m columns are selected in the M x M crossbar array, the total number of the district CRPs is  $\binom{M}{m} \times \binom{M}{n}$ , which is a very large number even fore moderate M, n, and m values.

In the two-sided scheme, an output bit is generated in two phases. In the first phase, one intermediate output bit is generated as discussed for the one-sided approach. In the second phase, the input biases are applied to the columns, while currents are read from rows to generate another intermediate bit, i.e. effectively using the same single-sided design but with a rotated crossbar array by 90 degrees with respect to the peripheral circuitry. The output bit is then generated by XORing these two intermediate, independent bits. The two-sided PUF features a more uniform response, and hence more robust to the machine learning attacks [13], though at the cost of halved throughput and doubled the energy consumption.

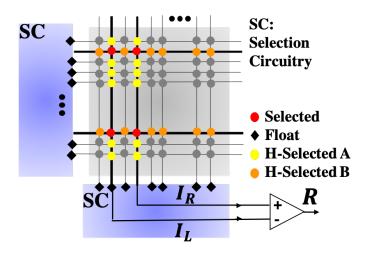

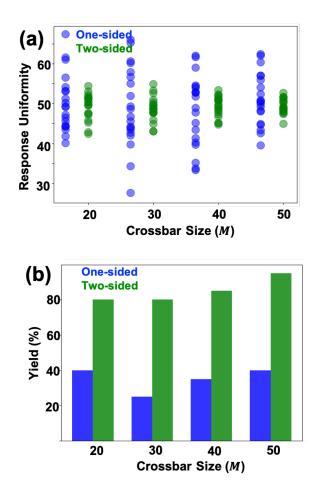

To demonstrate the benefits of the two-sided approach over a one-sided one, the response uniformity and yield of 2K CRPs of 25 instances for a variety of PUF sizes are considered. The realistic values of target conductance distribution (mean of 8.3  $\mu$ S and standard deviation of 2%) are considered for all cases. The simulation results are plotted in Figure 3.2. As shown in Figure 3.2a, the response uniformity of most of the two-sided PUFs are near-to-ideal (50%) whereas the response uniformity of most of the one-sided PUFs deviates from the ideal value. Additionally, Figure 3.2a shows that response uniformity improves when the size of the PUF crossbar increases. Furthermore, as shown in Figure 3.2b, the yield of the two-sided approach is more than two times

Figure 3.1: The top level architecture of the two-sided PUF design based on passive-ly-integrated (0T1R) memristive crossbar circuit. The crosspoint devices are colored according to the types of crossbar electrodes that they are connected to.

higher than the yield of a one-sided one. The yield is calculated based on the number of cases that pass the NIST frequency tests. Additionally, Figure 3.2b shows that yield of the two-sided approach improves when the crossbar size increases. This trend is not clear for the one-sided approach which may be due to the lack of the number of tested instances.

Based on the results of this study, two-sided PUFs are considered for the rest of this study.

## 3.2 Modeling Approach

In this study, the PUF metrics were estimated by assuming ideal peripheral circuits and modeling the output currents of the crossbar circuit with the help of the SPICE tool (the simulation setup is briefly explained in Appendix A). To model the memristor static I-V characteristics, the nonlinear current via crosspoint device was approximated with a

Figure 3.2: The effect of one-sided and two-sided approaches on (a) response uniformity and (b) yield. In both approaches, the response uniformity improves and the yield increases when PUF size increases.

generic expression

$$I = a \sinh(bV)$$

where a and b are constants that capture nonlinearity and device-to-device variations. These constants were randomly indirectly initialized for each device of the crossbar circuit. Specifically, to make the choice of the nonlinearity and variations more intuitive and representative of the real circuits, each device is characterized by the device current at "tuning" voltage V = 0.25 V, and the nonlinearity NL, which is defined as

$$NL = I(0.25V)/I(0.1V) \times 0.1V/0.25V$$

.

Unless otherwise specified, in all simulations in this study, NL is sampled from Gaussian distribution with an average of 1.5 and a specific standard deviation. Additionally, the device current at the tuning voltage is sampled from a Gaussian distribution with an average of 33.3  $\mu$ A and a specific standard deviation  $\sigma$ . After a unique NL and current at 0.25 V has been assigned for each device, the constants a and b (and hence complete unique static I-V characteristics) are derived. Note that the described approach for choosing currents crudely corresponds to the uncertainty in the tuning process for configurable PUFs [20, 45] as well as representative of the variations in the crosspoint device conductances in the fixed-resistance PUFs based on the as-fabricated devices [46]. Also, note that the absolute values for the tuning currents are not important for this particular study due to the focus on the functional characteristics of the PUFs and the assumption of the ideal peripheral circuits.

### 3.3 Evaluation Metrics

To assess the performance of the PUF, we consider three main metrics e.g. uniformity (UF), NIST and predictability which are widely discussed in the literature [20, 17, 47]. Note that it is not feasible to measure bit error rate (BER) in this study because the temperature variation and conductance drift models are not available. Additionally, note that uniqueness is more relevant in evaluating experimental data. Furthermore note that diffuseness is a weaker PUF metric as it stays near to ideal value (50%) even if other metrics show low performance.

To perform predictability analyses, machine learning models are considered as they are currently the most effective attack form for strong PUFs [13]. Memristive cross-bar PUF has a nonlinear input-output relationship, a huge CRP space, and a time-independent output response. As a result, multilayer perceptron (MLP) is chosen as an attack over logistic regression (used for linear-separable data), support vector machine (runs very slow for huge data), and recurrent neural network and long short-term memory (both use history of data). The studied MLP network consists of 2M inputs so that the challenge can be directly applied to the MLP input, and one output, corresponding to the PUF output, while the number of layers/neurons in the hidden layer(s) were varied in the simulations. A rectified linear (sigmoid) activation function was used for the hidden (output) layer neurons. The MLP classifier was trained and validated using the conventional backpropagation method on 80% of the simulated CRPs. The trained network is then used to predict PUF response on the remaining, mutually exclusive 20% of the CRPs.

# 3.4 PUF Optimization

This section first describes two proposed techniques for improving robustness against machine learning attacks. The common rationale for both techniques is that PUF robustness is increased when all crosspoint devices in the crossbar equally contribute to the output currents. The PUF response, in this case, would be a nontrivial function of the input, which depends on the unique I-V characteristics of all devices in the crossbar array. Furthermore, this section explores how the unique features of memristors namely device nonlinearity and analog tunability excel PUF security metrics. Moreover, this section studies the effect of crossbar size on PUF predictability.

### 3.4.1 Optimal Selection Ratio

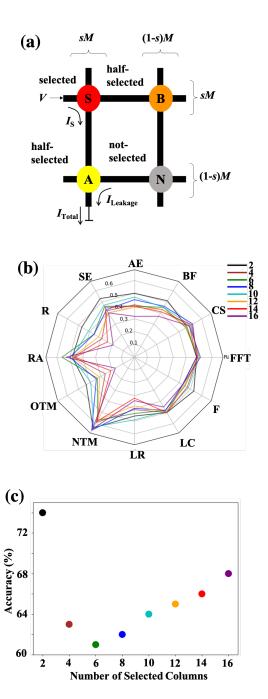

This section proposes a technique to improve PUF robustness against machine learning attacks by maximizing the contribution of the current of all devices in  $I_L$  and  $I_R$ . The requirement for the balanced contribution can be simplified to having currents via selected devices similar to those via (type A) half-selected devices, given that the output current is the sum of these two parts. The circuit parameters for having similar currents can be found from the approximate equivalent circuit of the crossbar array (Figure 3.3a), which is derived assuming negligible line resistance and similar static I-V characteristics of all crosspoint devices. Using the approximate equivalent circuit, the selected current and the leakage current can be written as  $s^2M^2a\sinh(bV_S)$  and  $s(1-s)M^2a\sinh(bV_{HSA})$ , respectively.

Our preliminary analysis for the considered average NL shows that selection ratios n/M = 0.25 and m/M = 0.2, i.e. n = 8 and m = 6 for M = 32, are close to the optimal values. To see if these selection ratios actually lead to the maximum contribution of all devices, a  $32 \times 32$  crossbar with a fixed row selection ratio (0.25) and different column

selection ratios (changes from 0.0625 to 0.5) are considered and 200K CRPs are collected for each of the PUFs. Then, the NIST test suite is conducted (Figure 3.3b) and MLP is applied to verify the predictability of the PUF output (Figure 3.3c). Although all column selection ratios pass the NIST test suite (P-values are greater than 0.01), the MLP accuracy is optimal when the column selection ratio is 0.2. In fact, with this selection ratio, the contribution of all devices is maximized resulting in more complex and less predictable PUF behavior. These optimum selection ratios are considered for the rest of the work.

### 3.4.2 Balancing Crossbar Array Conductances

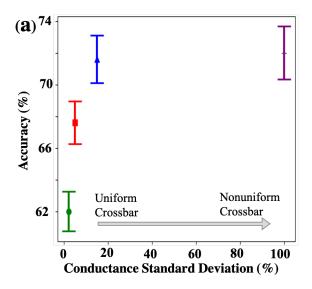

The main focus of the work is on the technique of balancing the crossbar array conductances, which allows improving PUF robustness by optimizing crosspoint device conductances resulting in a uniform crossbar. Figure 3.4a presents a motivation for this technique. It shows that PUF becomes more predictable as the dispersion in the device conductances grow. This is explained by the fact that for larger  $\sigma$ , the output current is more likely dominated by only a few devices with larger conductance – a feature that apparently makes such PUF easy to model with MLP network.

Given the challenges in the accurate tuning of the memristors, especially in the passive crossbar circuits, the natural goal is to achieve better robustness for larger  $\sigma$ . The specific objective of this study is to find such optimal mapping of the devices with predetermined (fixed) I-V characteristics to the locations in the crossbar array circuit that would maximize the PUF robustness. A balancing heuristic algorithm is introduced to address this goal (Figure 3.5). The algorithm tries to balance the total device conductances (at tuning voltage 0.25 V) across rows and columns. The intuitive idea behind such an approach is that in the crossbar array with matched conductances along the rows and columns, the

Figure 3.3: (a) simplified equivalent model of M x M crossbar circuit when read voltage  $V_{read}$  is applied to sM selected rows, the output currents are read from sM virtually grounded columns, while all the remaining lines are floated. (b) Effect of different column selection ratio in  $32 \times 32$  crossbars (b) on NIST test suite and (c) on MLP prediction accuracy.

devices with larger conductances along the current path will be compensated with those with the smaller conductances, which would in turn help in making the output currents close to each other and ultimately reduce the bias in the PUF response.

Specifically, starting with random mapping, the algorithm tries to iteratively swap the locations of two randomly chosen memristors to minimize the cost function

$$\Gamma = \sum_{i} (\sum_{j} G_{ij} - MG_{a})^{2} + \sum_{j} (\sum_{i} G_{ij} - MG_{a})^{2}$$

where  $G_{ij}$  is a conductance at 0.25V via device located in the i-th row and j-th column and  $G_a = \sum_i \sum_j G_{ij} - (0.25V)/M^2$  is an average conductance of all devices in the simulated instance of the crossbar array. The first/second term in the cost function is a sum of squared differences between the conductance of the row/column and the global average value. The cost function optimizes PUF for both one-sided and two-sided architectures and is independent of the number of selected columns.

A simulated annealing approach was implemented so that a move is always accepted if the cost function is reduced, while it is accepted with a certain probability, determined by the change in the cost and the current annealing temperature, even if the cost is increased. The annealing parameters are chosen such that most of the memristors are swapped multiple times.

Figure 3.6a-c shows an example of applying an algorithm for a  $10 \times 10$  crossbar array. The sum of the conductances across rows and columns has significant dispersion for the initial, random distribution of conductances (Figure 3.6a), while these sums become very close to each other after applying the algorithm (Figure 3.6b). Figure 3.6c shows how the value of the cost function reduces after each iteration. The algorithm effectiveness is investigated for different scenarios of the machine learning attacks (Figure 3.7). In the first study, the prediction accuracy of the MLP network was studied as a function of the

Figure 3.4: Prediction accuracy of two-sided PUF response modeled by 40-100-1 MLP network as a function of the (a) the crosspoint device conductance variations  $\sigma$  and (b) device nonlinearity mean value. The error bars represent standard deviation for the 5 simulated PUF instances, each with different device I-V characteristics. For all cases,  $M=20,\ n=5,\ m=4,\ {\rm and}\ V_{bias}=0.3{\rm V}.$  MLP accuracy decreases when the device nonlinearity mean value increases or when the conductance standard deviation decreases.

```

Balancing Heuristic

Input:

Output:

conductance matrix (mat)

balanced conductance matrix

1: T_i/T_f: initial/final temperature

2: \eta: annealing rate

3: M: number of iterations per temperature

4: £: cost

5: repeat

for each iteration in M do

7:

mat \leftarrow swap two devices randomly

8:

new_L: cost of updated mat

9:

if new_{\mathcal{L}} < \mathcal{L}

\mathcal{L} \leftarrow new_{\mathcal{L}}

10:

11:

else

rnd: generate a random number from uniform distribution

12:

prob: e^{\frac{-\Delta E}{T_i}}, where \Delta E: \mathcal{L} - new_{\mathcal{L}}

13:

if rnd < prob

14:

15:

\mathcal{L} \leftarrow new_{\mathcal{L}}

16:

else

17:

swap back the two devices

cool down: T_i \leftarrow \eta. T_i

19: until \mathcal{L} = 0 or T_i \leq T_f

```

Figure 3.5: Pseudo-code of the proposed heuristic algorithm for balancing conductances in the crossbar. The typical values for initial / final temperatures, annealing rate, and the number of iterations per temperature are  $2 / 1e^{-9}$ , 0.95, and 5000, respectively.

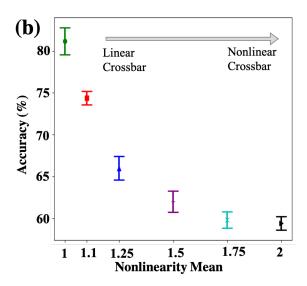

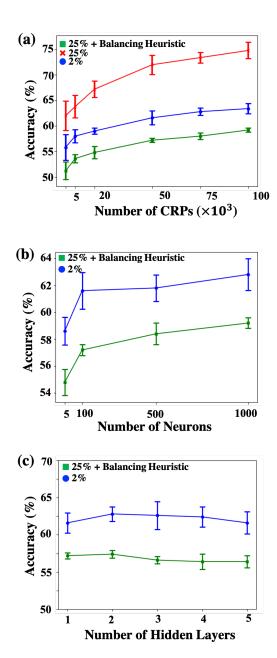

number of CRPs used in training for three cases of the crossbar conductances (Figure 3.7a). For a smaller number of CRPs, the accuracy is close to the ideal 50% when the device conductance distribution in the crossbar array is very tight. The accuracy is more than 60%, on average, for the naive (random) mapping with  $\sigma = 25\%$ , though the application of the algorithm allows reducing it to the ideal value. As expected, increasing the number of CRPs makes machine learning attacks more effective, though the prediction accuracy seems to saturate, which might be related to the limited capacity of the used MLP network.

The impact of the MLP capacity is further investigated by increasing the number of hidden layer neurons for the two-layer network (Figure 3.7b) and increasing the number of hidden layers while fixing the number of hidden layer neurons (Figure 3.7c). The accuracy first rapidly improves and then saturates in the former study case, which is likely due to the limited number of CRPs. Surprisingly, the accuracy is almost independent of the number of hidden layers for the latter. Finally, just like for the first experiment, the algorithm allows reducing prediction accuracy for the PUFs with  $\sigma = 25\%$  device conductance distribution to that of naive one with  $\sigma = 2\%$ , which confirms the effectiveness of the algorithm.

It should be noted that the crossbar (either naive or balanced one) is secure against side-channel attacks because generating  $I_R/I_L$  does not reveal any extra information compared to  $I_R/I_L$  [47, 48, 49, 50, 51]. To study this claim, the power profile of 5K CRPs of 10 20 × 20 PUF instances are collected. Statistics show that 50% of the time response = 1 consumes more power than response = 0. This is because measuring none of the  $I_L$  and  $I_R$  has any power dominance comparing to the other one.

Figure 3.6: The example of applying balancing algorithm for a  $10 \times 10$  crossbar circuit with  $\sigma = 25\%$ : (a) conductance heat-map before and (b) after applying the algorithm. The color bars at the edges of the arrays show the total conductances summed along the corresponding rows and columns. (c) The corresponding evolution of the cost function. All conductance maps are specified at 0.25V.

Figure 3.7: MLP prediction accuracy of the two-sided PUF (M = 20, n = 5, m = 4) response as a function of (a) the number of CRPs used in training 40-100-1 network, (b) the number of hidden layer neurons in two-layer network, and (c) the number of hidden layers in 40-100-...-100-1 network. There different scenarios for crossbar conductances scenarios were simulated: sigma = 2% (blue circle symbols), sigma = 25% without applying algorithm (red cross symbols), sigma = 25% with applying algorithm (green square symbols). In panel b and c studies, 50K CRPs were used for training MLP network. The error bars represent standard deviation for the 5 simulated PUF instances, each with different device I-V characteristics.

### 3.4.3 Device Nonlinearity and Analog Tunability

The memristive PUFs have been widely studied in different literature [4, 8, 9], but they lack detailed studies on the effect of memristor nonlinearity and analog tunability on PUF security metrics. The former device feature leads to nonlinear PUF operation which makes the modeling attacks almost impossible. The latter device feature leads to tunable PUF which means the devices can be custom-tuned for a specific goal in the configuration phase. The analog-tunability of memristors results in a uniform crossbar which makes output random and independent of the input.

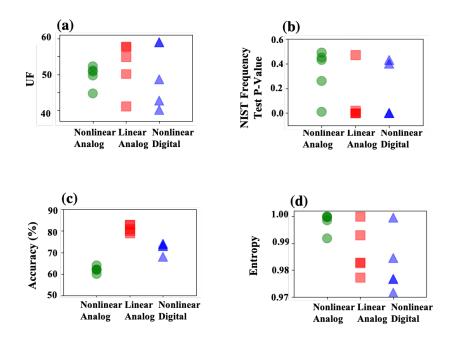

To study the effect of the device nonlinearity, 50K CRPs of 5 nonlinear and linear  $20 \times 20$  PUF instances (one-sided approach) are simulated. Furthermore, to study the effect of device analog tunability, 50K CRPs of 5 analog and digital  $20 \times 20$  PUF instances (one-sided approach) are simulated. Specifically, in analog crossbars, the target conductances are chosen as explained in Section 3.2 whereas in digital crossbars, the target conductances are chosen from two Gaussian distributions that are centered on ON- and OFF- conductance values (mean value of 8.3  $\mu$ S and 1  $\mu$ S, respectively). Based on the simulation results (Figure 3.8), nonlinear, analog-tunable, memristive crossbars outperform resistive crossbars and digital crossbars in UF (Figure 3.8a), NIST frequency test (Figure 3.8b), ML (Figure 3.8c), and entropy (Figure 3.8d).

Moreover, to evaluate the PUF robustness as a function of device nonlinearities, NL is swept from 1 to 2. As results are demonstrated in Figure 3.4b, when device nonlinearity increases, the PUF output will be a more complex function of all devices resulting in a less predictable PUF behavior.

Figure 3.8: Effect of device nonlinearity and analog tunability on (a) UF, (b) NIST frequency test P-value, (c) MLP prediction accuracy, and (d) Entropy. Nonlinear analog crossbar outperforms linear and digital crossbars in all four mentioned metrics.

#### 3.4.4 Crossbar Size

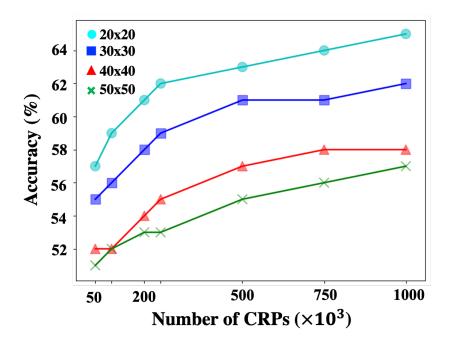

Another design variable that affects PUF predictability is crossbar size. In fact, when the crossbar size increases, the PUF complexity increases which results in a less predictable PUF behaviour. To study this claim, 1M CRPs for  $20 \times 20$ ,  $30 \times 30$ ,  $40 \times 40$ , and  $50 \times 50$  PUF instances are collected. The realistic values of  $\mu_G = 8.3$   $\mu$ S with 25% variations in the target conductance distribution as well as balancing algorithm are considered for all cases. As shown in Figure 3.9, when the size increases, the MLP accuracy reduces. This is because when the crossbar size increases, the number of ML features increases quadratically and the number of CRPs increases exponentially.

Figure 3.9: Effect of crossbar size on ML accuracy for different sizes of CRPs. When the crossbar size increases, the PUF complexity increases which results in a less lower ML accuracy.

# 3.5 Hardware Imperfection

Previous studies explored how IR-drop ([4]) affect PUF robustness. As explained in [4], when the wire resistance of interconnects are non-zero ideal, it causes IR drop along interconnects. In fact, the devices that are closer/further than the voltage source will have a lower/higher IR drop along the interconnects which results in insufficient voltage over crosspoint devices. As a result, some of the devices will have greater current reduction resulting in an undesired bias which reduces PUF reliability.

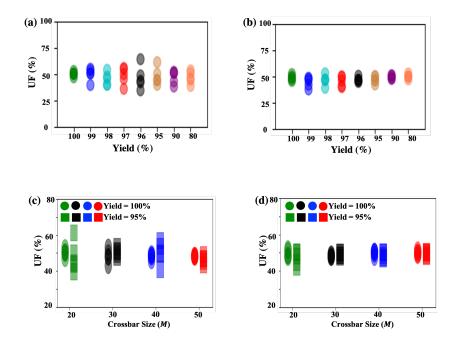

This study studies the effect of another hardware imperfection on PUF, namely non-ideal yield. When the yield is not 100%, some faulty devices exist that are stuck- at either ON or OFF state. When a device is stuck-at ON/OFF, its current is much higher/smaller than other devices. In this case, the column that consists of the stuck-at fault device becomes dominant resulting in a bias in the output which makes PUF unreliable. To

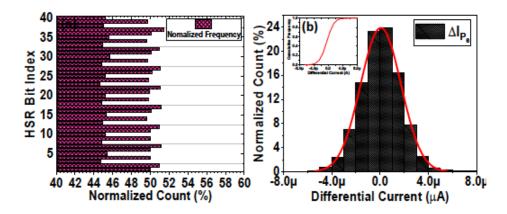

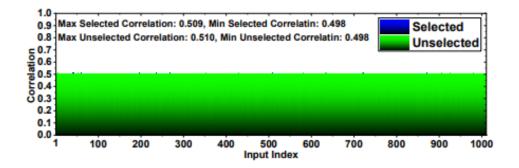

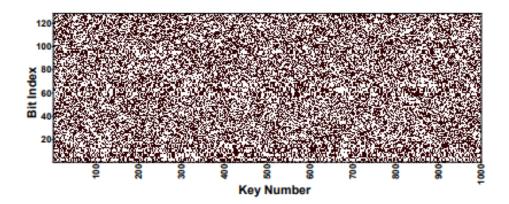

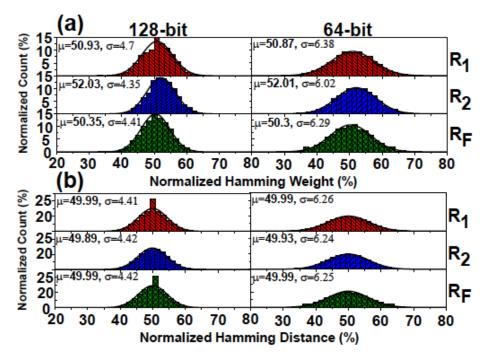

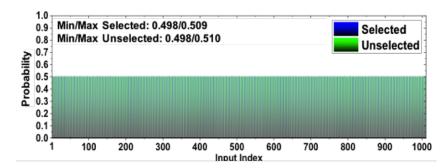

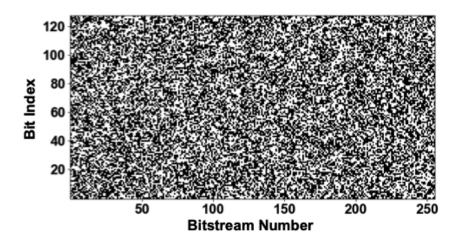

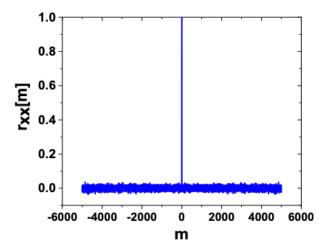

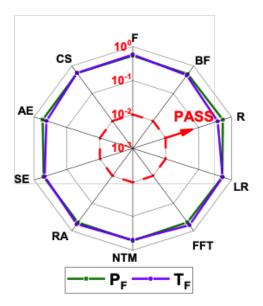

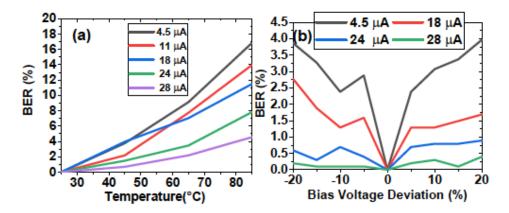

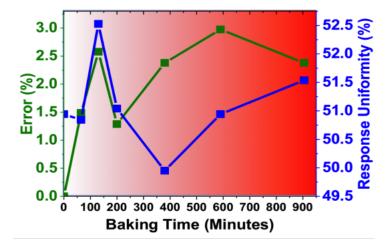

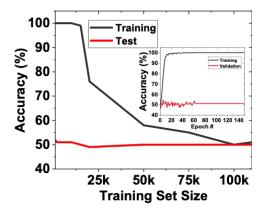

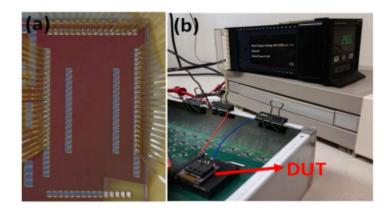

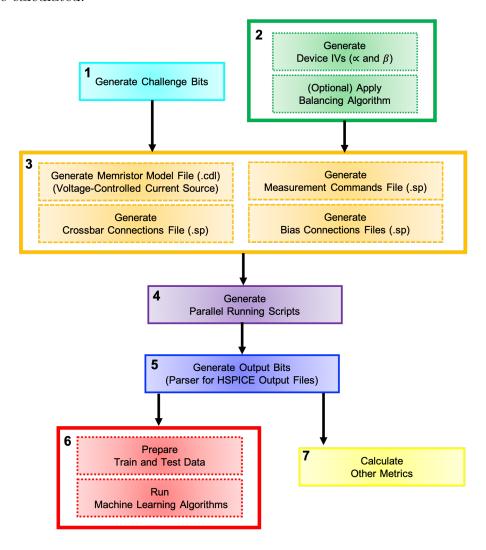

simulate the effect of yield on PUF reliability, we collected 5K CRPs of 5 PUF instances for a variety of ReRAM-based PUF sizes which have different percentages of stuck-at ON (without loss of generality) devices. The realistic values of  $\mu_G = 8.3 \ \mu\text{S}$  with 2% (without balancing algorithm) and 25% (with balancing algorithm) variations in the target conductance distribution are considered for all cases.