#### University of California Santa Barbara

## Energy-Efficient Intra-Data Center Coherent Links with High Link Budget

A dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy} \\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Aaron Maharry

#### Committee in charge:

Professor Clint Schow, Chair Professor James Buckwalter Professor Larry Coldren Professor Adel Saleh

| The Dissertation of Aaron Maharry is approved. |

|------------------------------------------------|

|                                                |

|                                                |

| Professor James Buckwalter                     |

|                                                |

| Professor Larry Coldren                        |

|                                                |

| Professor Adel Saleh                           |

|                                                |

| Professor Clint Schow, Committee Chair         |

March 2023

Energy-Efficient Intra-Data Center Coherent Links with High Link Budget

Copyright © 2023

by

Aaron Maharry

For my family

#### Acknowledgements

I would first like to thank my advisor, Professor Clint Schow, for welcoming me into his research group and providing steadfast support over the years. I came to UCSB with, in retrospect, only a vague idea of the work that I would do, and I consider myself extremely fortunate to have had the opportunity to work with and learn from him, in both technical and non-technical contexts.

I'd also like to thank my other committee members, Professors Jim Buckwalter, Larry Coldren, and Adel Saleh, for providing wonderful guidance and feedback as our research has progressed. The cross-disciplinary nature of our work has been truly rewarding, and I'm grateful to have learned from their expertise in electronics, opto-electronics, and network architecture.

This dissertation would not have been possible without the rest of the Schow group. Thanks in particular to Hector Andrade, Stephen Misak, Junqian Liu, Evan Chansky, Aaron Wissing, Viviana Arrunategui Norvick, Xinhong Du, Takahiro Tomiyasu, Amalu Shimamura, Gil Marc Sia, Yujie Xia, Steven Estrella, and Takako Hirokawa. Thanks as well to others at UCSB who I have had the pleasure of collaborating with: Luis Valenzuela, Ghazal Movaghar, James Dalton, and Navid Hosseinzadeh.

Thanks as well to the people I learned from and worked with during and after my internship at Intel, in particular Giovanni Gilardi, David Patel, Kejia Li, Ansheng Liu, and Yuliya Akulova.

I'd also like to thank all of the people at the UCSB Bridge Club for their support over the years.

Finally, I would like to express my heartfelt gratitude to my family — Mom, Dad, Sophie, Anyó, Apó, Nana, Papa, and all the Maharry's and Szökes — for their unwavering love, encouragement, and support throughout this journey.

### Curriculum Vitæ

#### Aaron Maharry

#### Education

| 2023 | Ph.D. in Electrical and Computer Engineering (Expected), Univer-    |

|------|---------------------------------------------------------------------|

|      | sity of California, Santa Barbara.                                  |

| 2019 | M.S. in Electrical and Computer Engineering, University of Cali-    |

|      | fornia, Santa Barbara.                                              |

| 2017 | B.S. in Electrical and Computer Engineering, Ohio State University. |

|      |                                                                     |

#### **Publications**

- 1. **A. Maharry** et al., "First Demonstration of an O-Band Coherent Link for Intra-Data Center Applications," Journal of Lightwave Technology, 2023 (to be published).

- 2. **A. Maharry** et al., "Integrated SOAs Enable Energy-Efficient Intra-Data Center Coherent Links," Optics Express, 2023 (to be published).

- 3. **A. Maharry** et al., "A 224 Gbps/λ O-Band Coherent Link for Intra-Data Center Applications," in 2023 Optical Fiber Communications Conference (OFC), paper M1E.5, Mar. 2023.

- 4. **A. Maharry** et al., "First Demonstration of an O-Band Coherent Link for Intra-Data Center Applications," in 2022 European Conference on Optical Communication (ECOC), Sep. 2022, pp. 1–4.

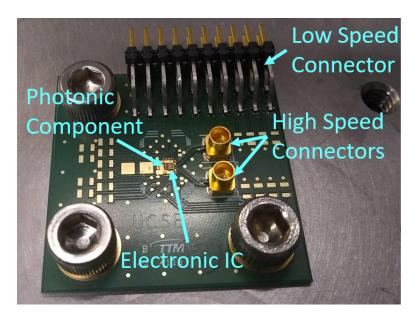

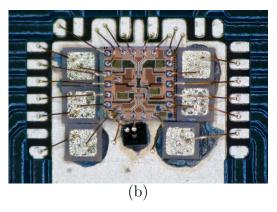

- 5. **A. Maharry**, L. A. Valenzuela, J. F. Buckwalter, and C. L. Schow, "A PCB Packaging Platform Enabling 100+ Gbaud Optoelectronic Device Testing," in 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), Jun. 2021, pp. 1323–1328. doi: 10.1109/ECTC32696.2021.00214.

- A. Maharry, L. A. Valenzuela, H. Andrade, I. Kalifa, I. Cestier, M. Galanty, B. Atias, A. Sandomirsky, E. Mentovich, L. Coldren, J. F. Buckwalter, and C. L. Schow, "A 50 Gbps 9.5 pJ/bit VCSEL-based Optical Link," in 2021 IEEE Photonics Conference (IPC), Oct. 2021, pp. 1–2. doi: 10.1109/IPC48725.2021.9592905.

- 7. **A. Maharry**, H. Andrade, T. Hirokawa, J. F. Buckwalter, and C. L. Schow, "A Novel Architecture for a Two-Tap Feed-Forward Optical or Electrical Domain Equalizer using a Differential Element," in 2019 IEEE Photonics Conference (IPC), Sep. 2019, pp. 1–2. doi: 10.1109/IPCon.2019.8908499.

- 8. J. Liu et al., "First O-band silicon coherent transmitter with integrated hybrid tunable laser and SOAs," Photonics West 2023, paper 12426-49, 2023.

- 9. H. Andrade et al., "Optical Transmitter Equalization With Tunable Mismatched Terminations in a Silicon Modulator," IEEE Photonics Technology Letters, vol. 34, no. 15, pp. 775–778, Aug. 2022, doi: 10.1109/LPT.2022.3186237.

- L. A. Valenzuela et al., "An Energy-Efficient, 60-Gbps Variable Transimpedance Optical Receiver in a 90-nm SiGe HBT Technology," in 2022 IEEE/MTT-S International Microwave Symposium - IMS 2022, Jun. 2022, pp. 279–282. doi: 10.1109/IMS37962.2022.9865274.

- 11. E. Chansky et al., "High-Speed SiGe EAMs at Cryogenic Temperatures," in 2022 IEEE Photonics Conference (IPC), Nov. 2022, pp. 1–2.

- 12. G. Movaghar, L. A. Valenzuela, J. Liu, A. Maharry, C. L. Schow, and J. F. Buckwalter, "An 88-Gbps, 3.3-pJ/Bit I/Q Receiver With Current-Mode Phase-Frequency Detection in a 130-nm SiGe HBT Technology," IEEE Solid-State Circuits Letters, vol. 5, pp. 308–311, 2022, doi: 10.1109/LSSC.2022.3231238.

- 13. G. Movaghar, V. Arrunategui, E. Chansky, A. Maharry, C. L. Schow, and J. F. Buckwalter, "A 40-Gb/s, 900-fJ/bit Dual-Channel Receiver in a 45-nm Monolithic RF/Photonic Integrated Circuit Process," IEEE Solid-State Circuits Letters, vol. 5, pp. 313–316, 2022, doi: 10.1109/LSSC.2022.3232340.

- 14. L. A. Valenzuela, Y. Xia, A. Maharry, H. Andrade, C. L. Schow, and J. F. Buckwalter, "A 50-GBaud QPSK Optical Receiver with a Phase/Frequency Detector for Energy-Efficient Intra-data Center Interconnects," IEEE Open Journal of the Solid-State Circuits Society, pp. 1–1, 2022, doi: 10.1109/OJSSCS.2022.3150291.

- 15. L. A. Valenzuela et al., "An 80-Gbps Distributed Driver with Two-Tap Feedforward Equalization in 45-nm CMOS SOI," in 2022 IEEE 22nd Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Jan. 2022, pp. 49–51. doi: 10.1109/SiRF53094.2022.9720041.

- 16. S. Misak et al., "Heterogeneously Integrated O-band SG-DBR Lasers for Short Reach Analog Coherent Links," in OSA Advanced Photonics Congress 2021 (2021), paper JTh3A.1, Jul. 2021, p. JTh3A.1. doi: 10.1364/IPRSN.2021.JTh3A.1.

- 17. H. Andrade, A. Maharry, L. Valenzuela, N. Hosseinzadeh, C. Schow, and J. Buckwalter, "An 8.2-pJ/bit, 56 Gb/s Traveling-wave Modulator Driver with Large Reverse Terminations," in 2021 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Dec. 2021, pp. 1–4. doi: 10.1109/BCICTS50416.2021.9682462.

- 18. L. A. Valenzuela, **A. Maharry**, H. Andrade, C. L. Schow, and J. F. Buckwalter, "Energy Optimization for Optical Receivers Based on a Cherry-Hooper Emitter Follower Transimpedance Amplifier Front-end in 130-nm SiGe HBT Technology," Journal of Lightwave Technology, vol. 39, no. 23, pp. 7393–7405, Dec. 2021, doi: 10.1109/JLT.2021.3115403.

- 19. Y. Xia et al., "A Fully Integrated O-band Coherent Optical Receiver Operating up to 80 Gb/s," in 2021 IEEE Photonics Conference (IPC), Oct. 2021, pp. 1–2. doi: 10.1109/IPC48725.2021.9592881.

- 20. H. Andrade, Y. Xia, A. Maharry, L. Valenzuela, J. F. Buckwalter, and C. L. Schow, "50 GBaud QPSK 0.98 pJ/bit Receiver in 45 nm CMOS and 90 nm Silicon

- Photonics," in 2021 European Conference on Optical Communication (ECOC), Sep. 2021, pp. 1–4. doi: 10.1109/ECOC52684.2021.9606026.

- 21. T. Hirokawa et al., "Analog Coherent Detection for Energy Efficient Intra-Data Center Links at 200 Gbps Per Wavelength," Journal of Lightwave Technology, vol. 39, no. 2, pp. 520–531, Jan. 2021, doi: 10.1109/JLT.2020.3029788.

- 22. L. A. Valenzuela, **A. Maharry**, H. Andrade, C. L. Schow, and J. F. Buckwalter, "A 108-Gbps, 162-mW Cherry-Hooper Transimpedance Amplifier," in 2020 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Nov. 2020, pp. 1–4. doi: 10.1109/BCICTS48439.2020.9392928.

- 23. H. Andrade et al., "Analysis and Monolithic Implementation of Differential Transimpedance Amplifiers," J. Lightwave Technol., JLT, vol. 38, no. 16, pp. 4409–4418, Aug. 2020, doi: 10.1364/JLT.38.004409.

- 24. H. Andrade et al., "Comparison of three monolithically integrated TIA topologies for 50 Gb/s OOK and PAM4," in Optical Interconnects XX, Feb. 2020, vol. 11286, pp. 194–201. doi: 10.1117/12.2548762.

- 25. L. A. Valenzuela, H. Andrade, N. Hosseinzadeh, A. Maharry, C. L. Schow, and J. F. Buckwalter, "A 2.85 pJ/bit, 52-Gbps NRZ VCSEL Driver with Two-Tap Feedforward Equalization," in 2020 IEEE/MTT-S International Microwave Symposium (IMS), Aug. 2020, pp. 209–212. doi: 10.1109/IMS30576.2020.9223818.

- 26. S. B. Estrella, T. Hirokawa, A. Maharry, D. S. Renner, and C. L. Schow, "Highspeed silicon photonic optical interconnects for cryogenic readout (Conference Presentation)," in Optical Interconnects XX, Mar. 2020, vol. 11286, p. 112860B. doi: 10.1117/12.2546635.

- 27. T. Hirokawa et al., "A Spectrally-Partitioned Crossbar Switch with Three Drops Per Cross-Point Controlled with a Driver," in 2019 IEEE Photonics Conference (IPC), Sep. 2019, pp. 1–2. doi: 10.1109/IPCon.2019.8908418.

- 28. T. Hirokawa, A. Maharry, R. Helkey, J. E. Bowers, A. A. M. Saleh, and C. L. Schow, "Demonstration of a Spectrally-Partitioned 4x4 Crossbar Switch with 3 Drops per Cross-point," in 2019 24th OptoElectronics and Communications Conference (OECC) and 2019 International Conference on Photonics in Switching and Computing (PSC), Jul. 2019, pp. 1–3. doi: 10.23919/PS.2019.8817842.

- 29. S. Estrella, D. Renner, T. Hirokawa, A. Maharry, M. Dumont, and C. Schow, "High-Speed Optical Interconnect for Cryogenically Cooled Focal Plane Arrays," Freedom Photonics LLC Santa Barbara United States, Mar. 2019. Accessed: Aug. 24, 2021. [Online]. Available: https://apps.dtic.mil/sti/citations/AD1075373

- 30. H. Andrade, T. Hirokawa, A. Maharry, A. Rylyakov, C. L. Schow, and J. F. Buckwalter, "Monolithically-Integrated 50 Gbps 2pJ/bit Photoreceiver with Cherry-Hooper TIA in 250nm BiCMOS Technology," in Optical Fiber Communication Conference (OFC) 2019, paper M3A.5, Mar. 2019.

#### Abstract

Energy-Efficient Intra-Data Center Coherent Links with High Link Budget

by

#### Aaron Maharry

As demand for internet applications, cloud computation, and AI continue to grow, data center networks must scale to support increased traffic flow. While current intensity modulation links are an economical solution today, coherent links are an increasingly attractive option to improve performance. Conventional coherent link technologies that are used today in >40 km transmission are based on power-hungry and expensive digital signal processing, and cannot be easily scaled to the high volumes required for data centers. Coherent links must be optimized for low power consumption and cost for reaches <2 km to make them viable for intra-data center networks. The enlarged link loss budgets from such links will also enable optical switching networks, which can dynamically reconfigure the network for improved server utilization, leading to vast improvements in overall data center energy efficiency.

The focus of this work is to develop energy-efficient coherent links with large link budgets for intra-data center networks. Design methodologies and architectural trade-offs for short-reach coherent link optimization will be presented. Using these techniques, custom electronic and photonic integrated circuits for coherent transmitters and receivers were designed, fabricated, assembled, and characterized. The first-ever full coherent link operating in the O-band was demonstrated with 56 Gbaud QPSK transmission. An O-band coherent link with custom packaged integrated circuits for both the transmitter and receiver was also demonstrated with 224 Gbps DP-QPSK transmission below the HD-FEC threshold with <10 pJ/bit power consumption expected for circuits including

integrated optical gain. These results shows that optimized O-band coherent links can support high data rates and link budgets with attractive energy efficiency for future intra-data center networks.

## Contents

| Cı | ırriculum Vitae                                                        | vi                                     |

|----|------------------------------------------------------------------------|----------------------------------------|

| Al | ostract                                                                | ix                                     |

| 1  | Introduction  1.1 Background and Motivation                            | 1<br>1<br>2<br>5                       |

| 2  | Low-Power Optical Links  2.1 Intensity Modulation and Direct Detection | 6<br>6<br>9<br>12                      |

| 3  | Short-Reach Coherent Link Optimization  3.1 Introduction               | 16<br>16<br>19<br>20<br>24<br>32<br>35 |

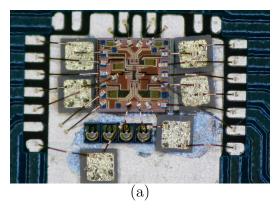

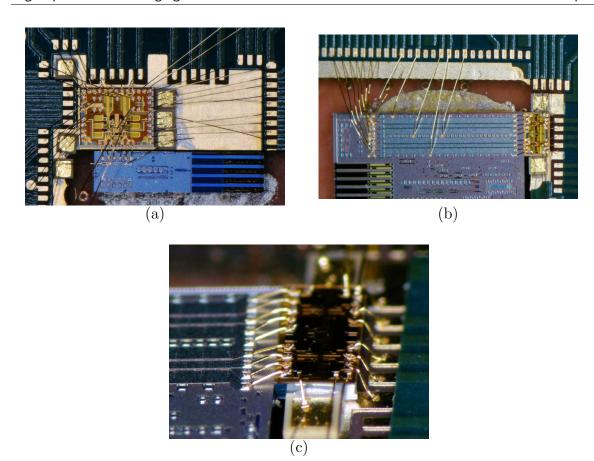

| 4  | High-Speed PCB Packaging Platform  4.1 Introduction                    | 37<br>37<br>38<br>43<br>46<br>50       |

| 5  | Low-Power Travelling Wave Modulators and Drivers5.1 Introduction       | <b>51</b> 51 52                        |

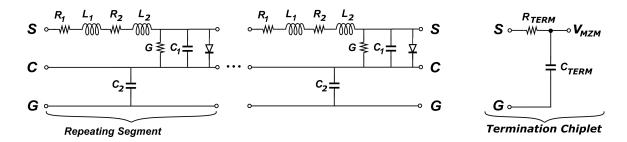

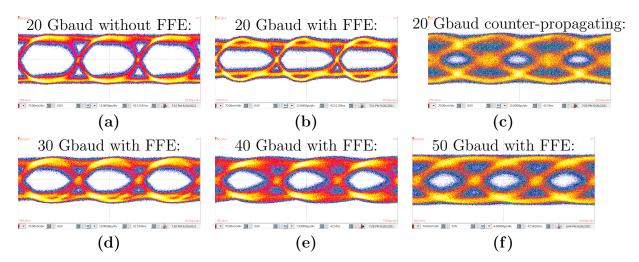

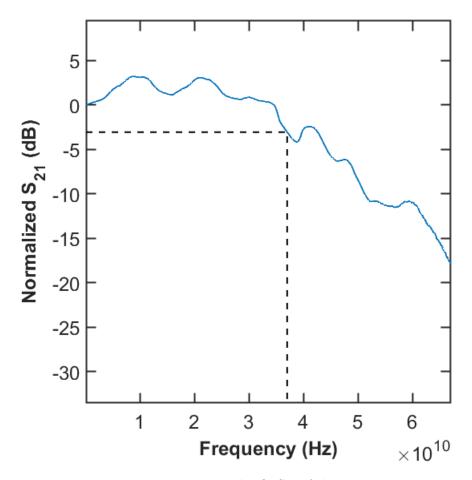

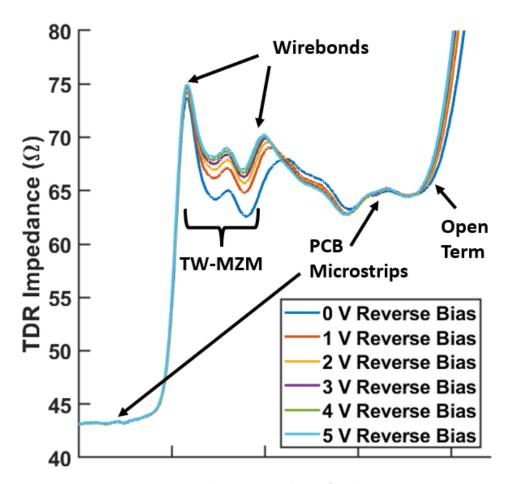

| 5.3 Silicon Photonic Travelling Wave Modulators                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56                                                                                                   |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 5.4 Design of a Optoelectronic Transmitter based on Artificial Transm | nission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                      |

| Lines                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                                                                                    |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                      |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                                                                                    |

| O-Band Coherent Links                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70                                                                                                   |

| 6.1 Introduction                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                    |

| 6.2 Design of first O-band Coherent Link for Data Center Applications | s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                                                                                    |

| 6.3 Results of first O-band Coherent Link for Data Center Application | ıs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                                                                                                    |

| 6.4 Design of 224 Gbps/ $\lambda$ O-band Coherent Link                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                    |

| 6.5 Results of 224 Gbps/ $\lambda$ O-band Coherent Link               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                    |

| 6.6 Conclusion                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                    |

| Conclusion                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                    |

| 7.1 Summary of Findings                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                    |

| 7.2 Future Work                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                                    |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                                    |

| Simulation Methods                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                                    |

| A.1 HFSS Simulation for TW-MZMs                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | J                                                                                                    |

|                                                                       | <ul> <li>5.4 Design of a Optoelectronic Transmitter based on Artificial Transmitters.</li> <li>5.5 Experimental Results for a Optoelectronic Transmitter based on Art Transmission Lines.</li> <li>O-Band Coherent Links</li> <li>6.1 Introduction.</li> <li>6.2 Design of first O-band Coherent Link for Data Center Applications</li> <li>6.3 Results of first O-band Coherent Link for Data Center Applications</li> <li>6.4 Design of 224 Gbps/λ O-band Coherent Link.</li> <li>6.5 Results of 224 Gbps/λ O-band Coherent Link.</li> <li>6.6 Conclusion.</li> <li>Conclusion</li> <li>7.1 Summary of Findings.</li> <li>7.2 Future Work.</li> </ul> | <ul> <li>5.4 Design of a Optoelectronic Transmitter based on Artificial Transmission Lines</li></ul> |

## Chapter 1

## Introduction

#### 1.1 Background and Motivation

Perhaps the defining feature of the times we live in is the impact of the computing and communications revolutions of recent decades. The astoundingly rapid development of these technologies has profoundly changed how people live their lives, and will continue to do so in times to come. A large part of the global computing infrastructure is concentrated in data centers, which house compute servers and associated infrastructure at massive scale. These data centers support the internet cloud infrastructure, and increasingly host dedicated hardware for artificial intelligence and machine learning (AI/ML) computation. Data center electricity consumption accounts for 2% of total US consumption, and new installations are continually deployed and upgraded to meet rising computation and communications demands, so efficiently scaling data center hardware is of paramount importance.

The intra-data center communications network has evolved over the years from copper interconnects to fiber optic interconnects for any link longer than a few meters. This has been due to the excellent loss and signal integrity characteristics of optical fibers,

and also due to advances in design and manufacturing of integrated photonic transmitter and receiver components. Optical links that transmit 400 Gbps over 2 km on a single fiber are being deployed in data centers today, and fiber parallelism enables large aggregate network throughput. However, even as overall internet traffic demand is growing, demand for low-latency and high bandwidth machine-to-machine communication within data centers is growing faster. Next-generation data centers will need to support 800 Gbps links within the decade, and 1.6 Tbps, 3.2 Tbps, and 6.4 Tbps ones not long thereafter. The current paradigm of widely-deployed optical link technologies won't be able to scale to meet this demand in a cost-effective and energy-efficient way, or maybe not at all. Therefore, the optics industry will need to innovate on the fundamental link technology to deploy data center optical interconnects that can power the computing and communications revolutions for years to come.

The aim of this dissertation is to outline the foundation for such a technology. Coherent optical links, which are widely deployed for longer-reach are an attractive option because of their high data rates, but as we will see, face significant challenges in reducing power consumption and cost. This work will describe novel coherent link architectures that are redesigned from the perspective of optimized energy efficiency for short-reach intra-data center links. It will be shown that competitive power consumption is achievable for these links, and that a departures from the design regimes of both short- and long-reach conventional link technologies are required to optimize performance.

#### 1.2 Optical Switching Networks

One of the most promising technologies for improving data centers is optical switching. Conventional data center networks are based on folded-Clos, or fat tree topologies, where servers connected to each other and to the outside world by optical links to multiple layers

of electronic packet switches. Switches with 51.2 Tbps of total data throughput are being deployed today, and subsequent generations supporting 102.4 Tbps and 204.8 Tbps are planned in the coming years. These switches can route vast quantities of data through the data center and facilitate server communication, but because they have to convert optical signals to electrical ones, process and route the packets, and convert the electrical signals back to optical ones, they add significant energy consumption, cost, and latency. In contrast, optical switches do no signal conversion, but simply route input optical signals to desired outputs. Various optical switching technologies are possible, with different benefits and different amounts of technical difficulty.

The most promising technologies are based on optical circuit switching (OCS), in which optical connections are reconfigured slowly and left in place for a period of time. The optical signals can either be routed by a wavelength-selective switch, or by a broadband switch. The former option enables more fine-grained adjustment of server connectivity, but is challenging to implement and has not been demonstrated with low losses for high port counts [1]. Broadband switches based on rotating MEMS mirrors, on the other hand, have already been widely deployed in data center networks by Google [2]. They were able to replace an entire layer of electronic packet switches in their network with optical circuit switches, which resulted in significant improvements of 41% power consumption and 30% cost in the network. In addition, these optical switches provided improvements in overall network throughput and the ability to incrementally deploy hardware during data center upgrades. This is because a dynamically reconfigurable optical switch-based network enables intelligent and low-latency resource interconnection that can improve computation run times and server utilization. Even though the optical circuit switches are not able to reroute every single packet of data, a simple reconfiguration to allocate network bandwidth to the resources that need it for a particular compute job can significantly improve the performance of that job. The OCSs can then recon-

figure to support the next job, where each network configuration can be maintained for timescales of a few seconds or minutes. There is still work to be done on full-system resource optimization with reconfigurable OCS-based networks, but a >2X energy efficiency improvement for the entire system (not just the network) has been projected [3].

A more comprehensive vision for optical switching, known as optical packet switching, involves reading and interpreting header information in the optical domain, and performing fast optical routing on each incoming packet. This technology is still nascent, however, and it is clear that most of the advantages of optical switching can be reaped with circuit switches, which already have mature and robust implementations.

Besides the development of the optical switches themselves, and their associated controls and algorithmic schemes, the intra-data center optical interconnects need to support the additional losses they introduce into the link. These losses can vary depending on the optical switch technology, from 2 dB for MEMs mirror switches to >10 dB for high port count or wavelength selective switches based on integrated optics. Additional impairments such as signal crosstalk and polarization dependent loss must also be accommodated. A key feature of coherent links inside data centers is that they have much larger link loss budgets and therefore allow the inclusion of optical switches in the network.

Although a large portion of this dissertation focuses on improving the energy efficiency of these intra-data center coherent links, it is important to note the power savings that could be achieved be making the link transmitters and receivers themselves infinitely efficient would be dwarfed by the potential power savings the could be achieved by replacing a layer of power hungry electrical switches with optical ones, or by increasing server utilization and computation efficiency across the whole data center. It will be shown below that short-reach coherent links can be made to operate at low power, but even if they couldn't, their enlarged link loss budgets that support optical switching would still improve overall data center energy-efficiency.

#### 1.3 Preview of Dissertation

The remainder of this dissertation will cover the design, implementation, and future prospects of energy-efficient intra-data center coherent optical links. Design methodologies and architectures for conventional intra-data center links and longer-reach coherent links will be described in Chapter 2, as well as the newly proposed low-power coherent architecture. Chapter 3 will outline an analysis and optimization framework for short reach coherent performance and power consumption. A high-speed packaging platform implementation will be presented in Chapter 4, showing characterization capabilities above 100 Gbaud. Design and measurement of high-speed and low-power travelling wave modulators and drivers will be discussed in Chapter 5. The first O-band coherent full-link measurement results, including the first  $>200 \text{ Gbps/}\lambda$  O-band link of any kind, will be reported in Chapter 6. Finally, Chapter 7 will conclude with a discussion of future work.

## Chapter 2

## Low-Power Optical Links

#### 2.1 Intensity Modulation and Direct Detection

This chapter will give an overview of the current state-of-the-art optical link technologies, and describe their relative tradeoffs, advantages, and future development challenges. Short-reach intra-data center optical links deployed today are all based on intensity modulation and direct detection technology (IMDD). This is a simple and robust link architecture in which data is encoded by modulating the intensity of the transmitted light.

IMDD links can be implemented with multiple photonic and electronic technologies. At the receiver, either vertically incident or waveguide coupled photodiodes (PDs) absorb light and generate a photocurrent signal that is amplified and detected. More advanced devices like avalanche photodiodes (APDs) can be used to trade off gain and bandwidth for improved performance. For the transmitter, directly modulated lasers (DML), or externally modulated lasers (EML) are possible. In the former, the laser diode itself it directly modulated to change the intensity of the emitted light. This category includes both waveguide-coupled lasers as well as vertical-cavity surface-emitting lasers (VCSELs). EMLs, on the other hand, integrate a laser with a separate modulation de-

vice. While adding complexity, this approach allows more degrees of freedom in designing laser performance as well as modulation efficiency and bandwidth.

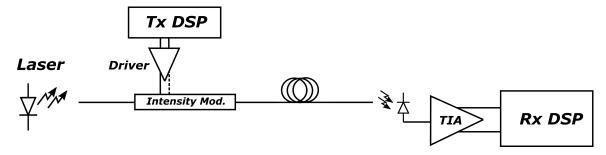

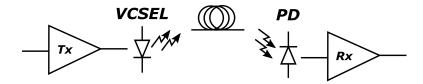

A typical architecture for a single-wavelength IMDD link based on an EML is shown in Fig. 2.1, and a similar schematic for a VCSEL-based link is shown in Fig. 2.2 Several material systems and modulation technologies can be used for these photonic integrated circuits (PICs). In InP, electro-absorption modulators (EAMs) can modulate the band edge of the device, and thus absorption of incoming light, through the quantum confined stark effect, or through the Franz-Keldysh effect. The electro-optic effect in InP, or other material systems like LiNbO<sub>3</sub>, can modulate the phase of the incoming light. When such a phase shifter modulator is placed within a Mach-Zehnder interferometer biased at quadrature, this phase modulation can be converted to an intensity modulation. High-speed phase shifters and Mach-Zehnder modulators (MZMs) can also be implemented on a silicon photonic (SiPh) material platform, using the free carrier plasma dispersion effect. While SiPh platforms offer low-loss waveguides and components with immense potential for integration, the modulation efficiency of SiPh-based pn-junction phase shifters is inferior to that of the electro-optic modulators that can be fabricated in InP or LiNbO<sub>3</sub>. Heterogeneous integration platforms that can cost-effectively combine the passive component performance and integration of SiPh with the optical gain and efficient high-speed modulation capabilities of InP, LiNbO<sub>3</sub>, or other materials may provide the best-of-both-worlds PIC fabrication platform for optical communications.

For each of these cases, an electrical driver circuit must be integrated to drive the desired modulator, and a receiver amplifier chain based on a low-noise transimpedance amplifier (TIA) at the input are required. Driver and TIA implementations include complimentary metal-oxide semiconductor (CMOS) inverters and bipolar SiGe differential pairs, and can be designed to integrate with either lumped capacitive loads or distributed ones.

Figure 2.1: Schematic of a standard IMDD link with DSP and an externally modulated transmitter.

Figure 2.2: Schematic of a standard IMDD link with a VCSEL or DML transmitter.

Due to the high bandwidth of optical fibers, these interconnects can make excellent use of parallel transmission on multiple wavelength channels co-propagating on a single fiber. This enhances a link's cost effectiveness, as a single transceiver can multiply its data throughput given the same fiber plant infrastructure. Four or even eight wavelengths ( $\lambda$ s) can be combined in a wavelength multiplexer (MUX) at the transmitter, and separated by a wavelength demultiplexer (DEMUX) at the receiver. These devices can be integrated with a PIC or purchased as a separate glass planar lightwave circuit (PLC) component, and can achieve low losses and crosstalk. In addition, devices such as ring resonators can perform wavelength-selective modulation combining or extracting optical signals from multiple laser wavelengths directly. Such highly parallel ring resonator circuits are promising, but have yet to be deployed widely.

Simple IMDD links can use two-level non-return-to-zero signalling (NRZ) to encode one bit of information per symbol, while in recent years, widespread deployment of links with higher order modulation has begun. Data center links operating over 25 Gbps/ $\lambda$ . IMDD links employing 4-level pulse amplitude modulation (4-PAM), which encodes 2

bits of data per symbol have begun to be deployed, and there are proposals for 6- or 8-level PAM to support higher data rates in future generations.

The transition to 4-PAM has marked a turning point in IMDD optical link development. NRZ links can be implemented with extremely low power consumption by utilizing limiting electronic circuits for the driver and receiver. 4-PAM links, on the other hand, require more complex and high-power linear electronics. The greater signalto-noise ratio (SNR) requirements for 4-level signalling mean that laser output power and link loss specifications also become more constrained. New digital signal processing (DSP) application-specific integrated circuits (ASICs) need to be incorporated in the link to equalize linear inter-symbol interference (ISI) in the link, as well as to interface with host-side serializer/deserializer (SerDes). These DSP chips account to for large fractions of the cost and power consumption of modern 4-PAM links. Moreover, while NRZ links were able to achieve error-free operation, corresponding to a bit error rate  $(BER) < 10^{-12}$ , 4-PAM links must rely on forward error correction (FEC) in the DSP to make links effectively error free. FEC adds latency on the order of 100 ns for the 400G generation [4], and contributes significantly to DSP power and cost. Despite this, 4-PAM IMDD solutions are being widely deployed and further developed to scale data rates for intra-data center optical links [5].

#### 2.2 Coherent Modulation and Detection

In contrast to IMDD links, which modulate and detect the intensity of the optical signal, coherent links modulate and detect both the amplitude and phase of the optical signal. The signal is often decomposed into orthogonal in-phase (I) and quadrature (Q) channels, effectively doubling the data rate relative to a link with a single intensity channel. Furthermore, coherent links can incorporate polarization-multiplexed signals,

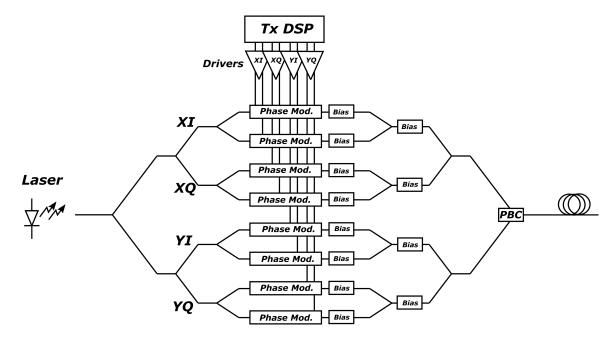

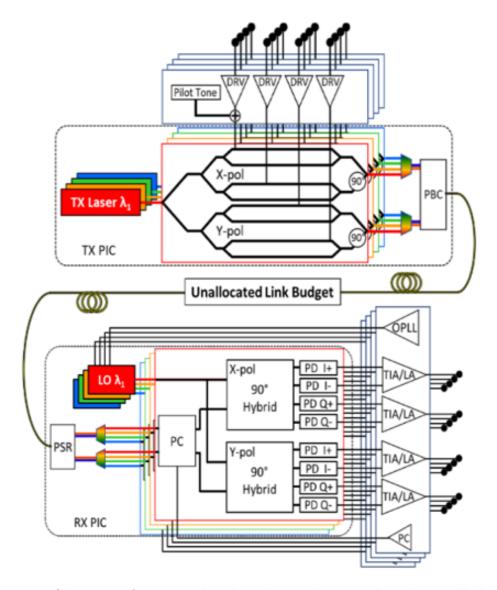

Figure 2.3: Schematic of a standard coherent transmitter. PBC: polarization beam combiner.

increasing the effective channel count to 4 per wavelength (two orthogonal polarizations, X and Y, each with I and Q channels).

In order to recover the phase information for coherent detection, the incoming signal is mixed with a local oscillator (LO) signal at the receiver. As the LO can come directly from a high-power continuous wave laser, this has the added benefit of introducing coherent gain and improving the sensitivity of the receiver. Whereas for IMDD the received photocurrent is directly proportional to the optical signal intensity, for coherent detection we have

$$I_{pd} \propto \sqrt{P_{sig}P_{LO}}.$$

(2.1)

The data rate and sensitivity benefits of coherent come at the cost of higher power consumption, cost, and complexity. Fig. 2.3 shows a schematic of a standard coher-

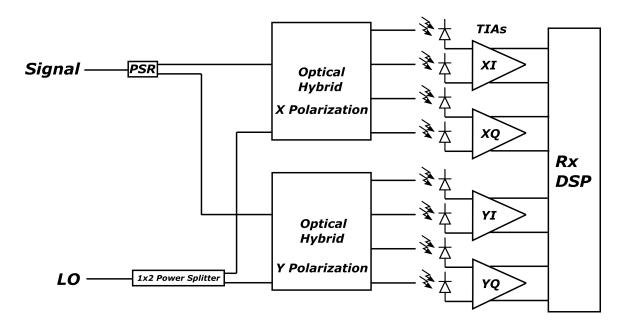

Figure 2.4: Schematic of a standard coherent receiver. PSR: polarization splitter rotator.

ent transmitter (Tx), and Fig. 2.4 shows a corresponding receiver schematic. At the transmitter, 4 MZMs are nested to form a dual-polarization (DP) IQ modulator, and at the receiver, the signal and LO must be mixed in an optical hybrid for each polarization channel. Furthermore, conventional coherent links require more complex DSP to perform carrier recovery and polarization recovery, since the signal polarization may have rotated randomly on the fiber and since the Tx and LO laser phases may drift apart. Current DSP-based coherent links consume  $\sim 40$  pJ/bit, of which roughly half comes from the DSP ASIC [6]. Increased FEC complexity, too, adds latency on the order of 10  $\mu$ s [6].

As digital CMOS electronics technology scales to shorter nodes, coherent DSP and power consumption becomes more attractive for higher volume markets. Coherent links are widely used today for long-haul transmission, and are beginning to be deployed for shorter reaches >40 km [7]. The trend of coherent link penetration into shorter and shorter reach applications will continue, with 10 km links in development and 2 km intra-data center links soon to follow.

Figure 2.5: Schematic of a proposed analog coherent detection-based optical link. PC: polarization controller. OPLL: optical phase locked loop.

#### 2.3 Analog Coherent Detection

An alternative approach to short-reach coherent optical links is analog coherent detection (ACD) [10]. The core principle of an ACD-based link is to offload functions from the DSP ASIC and perform them efficiently in the analog domain. This saves power and cost, and we have shown through link energy-efficiency analysis that power consumption

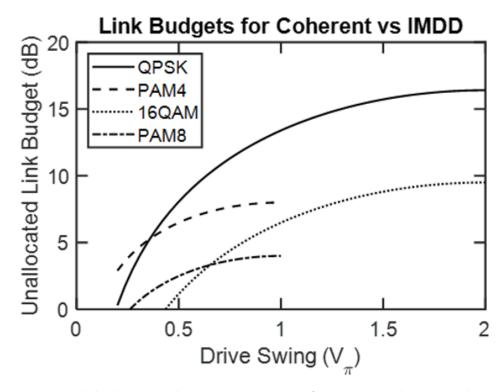

Figure 2.6: Link budgets vs driver voltage swing for various coherent and IMDD modulation formats.

on the order of 5-10 pJ/bit is possible with this architecture, which is shown in Fig. 2.5 [8].

The first such DSP function that can be transferred to the analog domain is carrier recovery. Conventional coherent links require the wavelengths of the Tx and LO lasers to be aligned within a few GHz, and then rely on a DSP-based carrier recovery algorithm to accommodate frequency and phase offsets between the lasers that arise from laser phase noise and thermal drift. Alternatively, an ACD-based link employs an optical phase locked loop (OPLL) to lock the frequency and phase of the LO to that of the incoming signal. This OPLL is formed from the coherent receiver components on the PIC, the receiver chain and phase frequency detector (PFD) circuit in the Rx EIC, and an off chip loop filter. Integrated OPLLs have been demonstrated, and shown to support error-free link operation for up to 35 Gbps binary phase shift keying (BPSK), in [9].

One critical requirement for such an OPLL is that the loop delay — the total time

it takes for the LO output light to mix with the incoming Tx signal, get absorbed in the PDs, get amplified in the Rx EIC, pass through the PFD and loop filter, and return to tune the LO frequency to correct for any offsets — must be short. The loop delay is critical for the stability of a loop that must track laser frequency and phase variations up to 100s of MHz or even GHz. Thus, a key technological requirement for the realization of an OPLL (and thus an ACD-based link) is that the LO must be integrated with the Rx PIC. This enables loop delays on the order of 100-200 ps, which would not be possible with a fiber-coupled LO.

The second DSP function that can be transferred to the analog domain is the polarization controller. This circuit serves to demultiplex the received polarization channels, even if the signal underwent an arbitrary polarization state rotation on the fiber. An optical polarization controller circuit can be realized by a set of cascaded phase shifters and 2x2 couplers, and reset-free operation has been demonstrated [11].

Finally, while conventional coherent links operate in the C-band, near the 1550 nm minimum-loss point in standard fibers, ACD links are designed to operate in the O-band, near the 1310 nm zero-dispersion point instead. This is a fundamental tradeoff for short-reach coherent links. The difference in transmission loss — 0.1 dB/km at 1550 nm, compared to 0.2 dB/km at 1310 nm — is critical for long-haul links, but becomes a minor inconvenience for links <2 km. And because of the short link length, if the link is operated at or near the zero dispersion wavelength, the chromatic dispersion penalty becomes negligible [10]. This enables the elimination of the dedicated chromatic dispersion (CD) compensation function in the coherent DSP, further improving energy efficiency.

The the ACD architecture discussed here is based on quadrature phase shift keying (QPSK), which uses simple NRZ signalling for each individual channel. When a polarization controller is combined with an OPLL for carrier recovery, these functions ensure that the photocurrent signals at the Rx PDs simply contain the demultiplexed data for each individual channel (XI, XQ, YI, and YQ). Thus, ACD-based links can use low-power and robust limiting NRZ-based electronic circuits for the driver and Rx EICs. Furthermore, as linear operation is no longer required in the DSP either, power-hungry analog-to-digital converters (ADCs) can be omitted from the ASIC.

A further benefit of using QPSK modulation is that reduced SNR requirements at the receiver improve the link loss budget of the link. As shown in [12], while coherent links benefit from coherent gain from the local oscillator, increased optical losses in the transmitter can negate this benefit. For conventional coherent link architectures that use 16QAM, this can result in the same, or even worse available link budget than a comparable IMDD link. QPSK, however, can surpass the performance of all of these alternatives and tolerate additional losses in the link. Fig. 2.6 shows the available link budget for various modulation formats vs the driver output swing used at the transmitter [8]. The link parameters used to calculate the link budgets were based on those reported in [12], with the addition of a curve for QPSK, which shows significant improvements over PAM4 and 16QAM above  $0.5 V_{\pi}$  of voltage swing.

While certain functions, such as FEC, differential decoding, and SerDes interfaces, may need to remain to successfully integrate an ACD-based link into a data center system, the techniques described above can significantly reduce the power consumption of a coherent link. This holistic optimization of the entire link architecture is required to adapt coherent links for short-reach applications inside the data center.

## Chapter 3

# Short-Reach Coherent Link Optimization

#### 3.1 Introduction

Fiber optic intra-data center network bandwidth has grown rapidly in recent years, and is projected to continue to do so, driving the need for continued optical transceiver performance scaling. As transceiver datarates surpass 1 Tb/s, scaling current pulse amplitude modulation (PAM) intensity modulation direct detection (IMDD) links requires increasing some combination of the baudrate, the number of PAM modulation levels, or the number of parallel fibers/wavelengths. Each of these strategies have significant challenges, and while IMDD may be able to support transceiver datarates above 1 Tb/s, it will soon become preferable to use coherent modulation and detection for high-bandwidth intra-data center links [12].

Coherent links, which can provide 4X increased datarate per wavelength relative to a comparable IMDD system due to polarization multiplexing and in-phase and quadrature (IQ) modulation, have been widely used in long haul and metro network applications, and

more recently for inter-data center links below 120 km using the 400ZR standard [7]. Advances in photonic integrated circuit (PIC) technologies and continued scaling of coherent digital signal processing (DSP) application-specific integrated circuits (ASICs) implementation nodes are improving the form factor, cost, and power consumption of coherent links to rival IMDD links for short-reach intra-data center applications. In addition, our recent work has investigated the possibility of using an analog coherent detection (ACD) architecture to perform the DSP functions of carrier recovery and polarization recovery in the optical domain, removing the need for power-hungry analog-to-digital converters (ADCs) and further improve coherent link power efficiency [8].

Developing coherent links for short-reach applications requires new design tradeoffs to meet the stringent power efficiency, size, cost, and interoperability requirements for intradata center links, as opposed to the fiber capacity maximization requirements typical of longer reach coherent link implementations. Already in the 400ZR architecture, module power consumption is reduced by driving the Mach-Zehnder modulator (MZM) with an input swing well below 1  $V_{\pi}$ . There have been several proposals for modified DSP implementations targeted for power savings in short-reach coherent links [13, 14]. Most notably, chromatic dispersion (CD) is negligible for 50 Gbaud links under 2 km, and thus CD compensation can be bypassed or omitted in the DSP [10]. Higher baudrate links may become more sensitive to CD, limiting their application to shorter reaches, or requiring the re-introduction of CD compensation. Short-reach coherent architectures using analog signal processing [15] or self-homodyne [16, 17] techniques to reduce DSP power consumption have also been proposed. The trend of optimization for shorter reach applications will have to continue and be applied to other aspects of the link to enable viable intra-data center coherent links.

The power efficiency of an optical transceiver is not, however, a complete picture of its effect on overall data center power consumption. Advances in the field of optical

switching have brought forward the possibility of including passive arrayed waveguide grating routers (AWGRs) or actively controlled optical switches into data center network architectures. There are proposals to replace a layer of electrical switches in current data center architectures with a layer of AWGRs or optical switches, achieving great power savings [1,18]. Additionally, data center network requirements are rapidly morphing with the rise of diverse artificial intelligence and machine learning workloads. This makes realtime network reconfiguration though optical switching especially attractive, as it has the potential to not just save power by replacing electrical switches, but also by increasing server utilization across the data center [19–21]. The potential power savings from this approach is not limited to the portion of overall data center power that is consumed by the network, but by the possible overall improvements in server utilization across the data center. Overall data center efficiency improvement of > 2X was projected in [3]. Thus, a critical consideration for supporting future data center growth is not just the power efficiency of the optical links themselves, but also their ability to support the inclusion of optical switches or AWGRs in the network. The available link budget of future intra-data center links is therefore crucial, since optical switches and AWGRs introduce additional losses that need to be accommodated. Coherent receivers have improved sensitivity over IMDD, and coherent links that use QPSK modulation can support greater overall link budgets than comparable IMDD links, making them attractive for optical switching applications [8].

Optical amplification is commonly used in conventional coherent links in the form of erbium doped fiber amplifiers (EDFAs) to extend link reach, and integrated semiconductor optical amplifiers (SOAs) to boost the optical power output of the transmitter (Tx), or to preamplify the signal at the receiver (Rx) [22,23]. In this paper, we present an analysis of optical amplification, namely SOAs integrated with the coherent PICs, as applied to short-reach coherent links. Design tradeoffs between Rx sensitivity, total link

budget, compatibility with optical switching, inter-symbol interference (ISI), and link power consumption will be examined, with the goal of outlining short-reach coherent link architectures with optimized power efficiency and viability for implementation in data centers. Optimization for link power consumption gives rise to new design spaces for short-reach coherent links in which shot, thermal, and amplified spontaneous emission (ASE) noise can all contribute substantially to overall noise at the receiver. This hybrid regime contrasts sharply with both conventional coherent links dominated by ASE noise and IMDD links dominated by thermal noise, and thus careful design is required to optimize coherent links for short-reach applications.

Section 3.2 will describe the various link architectures that will be examined. Section 3.3 will examine the link performance penalties associated with the addition of optical amplification under various architectures. Section 3.4 will present an analysis of link power efficiency incorporating optical amplification. These results will be compared to other coherent link architectures in Section 3.5. Concluding remarks will be made in Section 3.6.

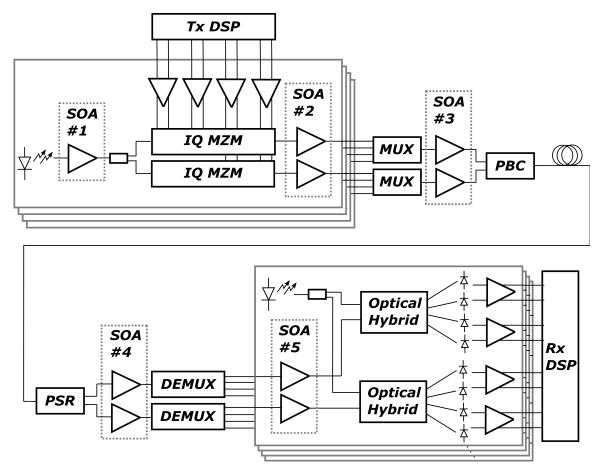

#### 3.2 Link Architecture

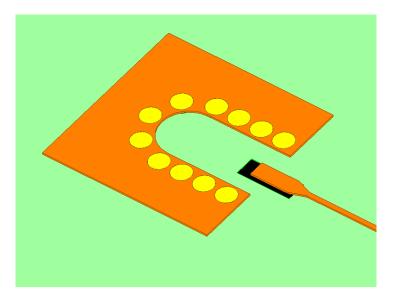

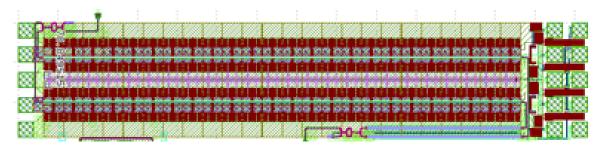

The generalized coherent link architecture that will be considered in this paper is shown in Fig. 3.1, where 5 possible locations for SOAs have been highlighted. The optical components in this diagram can be integrated into a Tx, Rx, or combined PIC using a photonic integration platform such as [24] or [25]. The SOA in position #1 serves to directly boost the Tx laser output power with minimal impairment to the link, since a constant input power will not induce an SOA pattern effect. The principle drawback of using an SOA in this position is that the high input optical power will saturate the SOA gain. In positions #2 and #3, which come after the MZM, the attenuated input

signal allows higher SOA gain, but the SOA pattern effect will introduce ISI. In these positions, the SOAs each amplify one of the two polarization channels, since SOAs are typically implemented as single-polarization devices. If wavelength division multiplexing (WDM) is used, as in the ACD-based architecture described in [8], a single pair of SOAs in position #3 can amplify all the wavelengths simultaneously after the multiplexer (MUX). Compared to position #2, this has the potential to greatly reduce power consumption in the SOAs, but will suffer from additional gain saturation, ISI, and crosstalk impairments. Similarly, SOAs in positions #4 and #5, before and after the demultiplexer (DEMUX), respectively, would act as Rx pre-amplifiers. SOAs in either of these positions would benefit from reduced nonlinear effects due to a further attenuated input signal, but would also contribute higher ASE noise at the Rx.

In-line fiber amplifiers are commonly included in longer reach coherent links, but are not considered in this analysis, as power and size requirements for intra-data center applications would be prohibitive compared with SOAs that can be readily integrated with transceiver PICs or packages. Moreover, as will be shown, additional in-line amplifiers are not needed to close short reach coherent links that have < 1 dB of fiber losses, even for demanding link budgets that include optical switches.

#### 3.3 SOA Noise and Gain Saturation

In the architectures proposed here, the ASE noise in the SOAs introduces a current noise at the photodiodes (PDs) dominated by the beating of the LO signal with the SOA ASE noise. The ASE-induced current noise variance when detected at a PD can be expressed as

Figure 3.1: General coherent link architecture. Boxes labeled SOA #1-5 indicate potential SOA insertion points throughout the link.

$$\sigma_{ASE}^2 = 4\mathbb{R}^2 |E_{LO}|^2 S_{ASE} \Delta f \tag{3.1}$$

where  $\mathbb{R}$  is the PD responsivity,  $E_{LO}$  is the normalized field from the LO,  $S_{ASE}$  is the optical power spectral density of the SOA ASE noise, and  $\Delta f$  is the receiver bandwidth. The ASE noise spectral density at the SOA output is calculated from

$$S_{ASE} = n_{sp} \frac{hc}{\lambda} (G - 1) \tag{3.2}$$

where  $n_{sp}$  is the population inversion factor of the SOA,  $hc/\lambda$  is the photon energy, and G is the SOA gain [26]. Due to the mixing in the optical hybrid, the ASE-induced noise currents at each differential PD pair are correlated, and the total ASE-induced RMS current noise is  $\sigma_{ASE,I} = \sigma_{ASE,Q} = \sqrt{2}\sigma_{ASE}$ .

In addition, SOA gain saturates with increasing input optical power, and can be written as

$$G = G_0 e^{-(G-1)P_{in}/P_{sat}} (3.3)$$

where G is the saturated gain of the SOA,  $G_0$  is the unsaturated or low input power gain of the SOA,  $P_{in}$  is the input optical power, and  $P_{sat}$  is the saturation power parameter [27].  $P_{sat}$  is an internal parameter that does not correspond directly to either the input or output 3 dB gain saturation points. Static gain saturation would have the largest effect on SOA #1 in Fig. 3.1, since the optical input power will be the highest directly after the Tx laser.

For SOAs in positions #2-5, instantaneous changes in the power of the modulated signal at the SOA input will cause the saturated gain to fluctuate, inducing nonlinear signal distortions known as the pattern effect and nonlinear phase noise (NLPN). The pattern effect and NLPN have been well studied for IMDD applications [28, 29], as well as coherent 16QAM [30, 31] and RZ-QPSK [32, 33]. There has not however been an experimental investigation of SOA nonlinear effects on QPSK. A QPSK-modulated signal, which is used in the ACD architecture, has a quasi-constant power envelope where the only SOA input power fluctuations occur during bit transitions. Thus, it is inherently more robust to SOA nonlinearities than IMDD or higher order QAM modulation formats. To investigate the performance of SOA-amplified QPSK, a time-domain simulation was

used. The optical field at the SOA output is described by

$$E_{out}(t) = E_{in}(t)e^{h(t)(1+j\alpha)/2}$$

(3.4)

where  $E_{in}(t)$  is the modulated field at the SOA input, h(t) is the instantaneous SOA gain parameter, and  $\alpha$  is the SOA linewidth enhancement factor, which describes the relationship between gain fluctuation and the induced NLPN. The instantaneous SOA gain is described by

$$\frac{d}{dt}h(t) = \frac{h_0}{\tau_c} - \frac{h(t)}{\tau_c} - (e^{h(t)} - 1)\frac{|E_{in}(t)|^2}{\tau_c P_{sat}}$$

(3.5)

where  $h_0$  is the unsaturated SOA gain parameter and  $\tau_c$  is the SOA carrier lifetime [27]. The SOA gain parameter h(t) is related to the total SOA gain by  $G = e^{h(t)}$ .

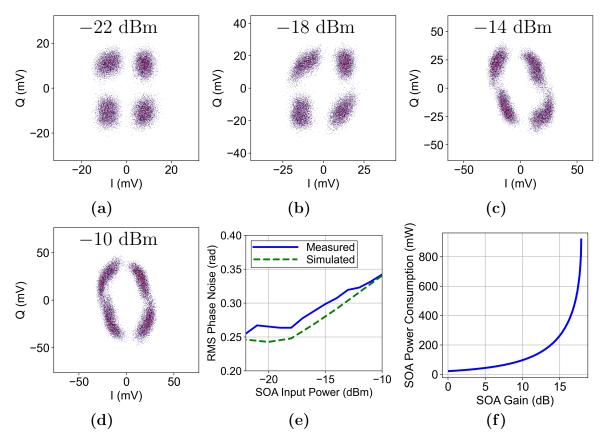

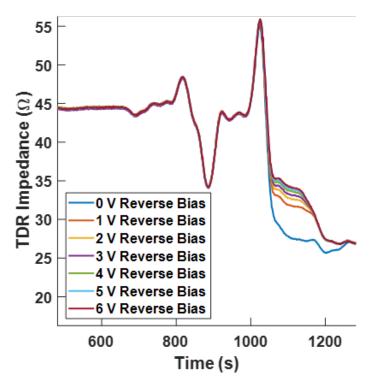

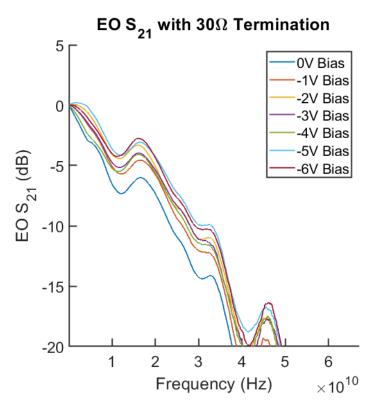

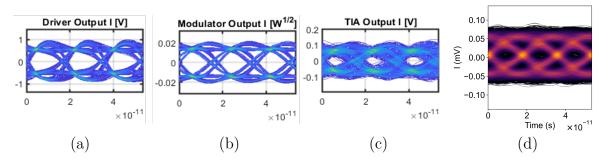

In order to confirm this model for QPSK modulation, a coherent link was tested with an SOA (Thorlabs S9FC1132P) biased at 300 mA. The measured  $G_0$  was 23 dB and the  $P_{sat}$  was 5 dBm. Measured output constellations for a reference link operating at 10 Gbaud QPSK are shown in Fig. 3.2 for SOA input power levels between -10 dBm and -22 dBm. For higher SOA input power levels, the SOA NLPN contributes substantial additional phase noise. The measured link results in Fig. 3.2 were replicated in a simulation that modelled the SOA using the above measured parameters as well as link component bandwidths and shot, thermal, and ASE noise contributions. The SOA carrier lifetime of  $\tau_c = 200$  ps and linewidth enhancement factor of  $\alpha = 5$  were estimated from the literature [27]. The measured and simulated root-mean-square (RMS) phase noise characteristics are compared in Fig. 3.2(e), showing good agreement across SOA

Figure 3.2: Measured sampled QPSK constellations depicting the SOA pattern effect and NLPN for SOA input power levels of -22 dBm (a), -18 dBm (b), -14 dBm (c), and -10 dBm (d). (e) Measured vs modeled RMS phase error for various SOA input power levels. (f) Simulated SOA power consumption  $P_{soa}$  vs saturated gain G.

input power levels and validating the above SOA analytical model for application to NLPN effects on quasi-constant power envelope QPSK modulation.

#### 3.4 Power Efficiency Optimization

#### 3.4.1 Simulation Model

The performance and power efficiency of the links considered here will now be modelled and compared in simulation. The simulation model incorporates static optical losses of various components, modulation efficiency of the Tx MZM, SOA gain, time-domain simulation of BW effects and SOA nonlinearities, and various noise sources to compute the bit error rate (BER) at the receiver. All the simulations used a full PRBS15 sequence. One of the conclusions of our previous work analyzing short reach coherent links [8] was that for typical ACD links, optimal power consumption was achieved when the Tx and LO lasers were operating at high power, which is limited by laser reliability considerations. Therefore, a constant, realizable integrated laser power of 13 dBm is assumed in this work for both the Tx and LO lasers in ACD-based coherent links. For DSP-based coherent links, a 16 dBm ITLA is assumed, with equal Tx/LO splitting. All BW impairments are assumed to be single-pole low-pass filters. CD and polarization mode dispersion (PMD) are neglected. Nonlinear WDM crosstalk in each SOA is simulated in time-domain with uncorrelated aggressor signals. All of the parameters used in the simulations are shown in Table 3.1, for both ACD- and DSP-based coherent link configurations.

The power consumption of the link is optimized by trading off driver output voltage swing and SOA gain in simulation. All other link components are assumed to have a static contribution to the overall link power consumption, which will be considered in Section 3.5. The driver power consumption is calculated from

$$P_{driver} = c_0 + c_1 \frac{V_{driver}}{Z_0} + c_2 \frac{V_{driver}^2}{Z_0}$$

(3.6)

where  $V_{driver}$  is the desired output swing,  $Z_0$  is the MZM impedance, and  $c_{1,2,3}$  are coefficients that depend on the driver design and process. In this work, we define the output swing of the drivers in an ACD-based link by the rail-to-rail differential voltage, since limiting electronics may be used in concert with driver output stage peaking circuits. We define the output swing of the linear drivers required for DSP-based links by the peak-to-peak differential voltage, including any peaking from linear equalization. The SOA

| Simulation Parameter                 | Value for ACD       | Value for DSP        | Notes                                 |  |

|--------------------------------------|---------------------|----------------------|---------------------------------------|--|

| Modulation Format                    | QPSK                | 16QAM                |                                       |  |

| Baudrate                             | 56 Gbaud            | 60 GBaud             |                                       |  |

| Target BER                           | $3.8 \cdot 10^{-3}$ | $1.25 \cdot 10^{-2}$ | HD-FEC and CFEC thresholds            |  |

| Rx Adaptive Equalizer Taps           | 1 31                |                      | No DSP equalization in ACD link       |  |

| Laser Power on PIC                   | 13 dBm              | 16 dBm               | Integrated for ACD, ITLA for DSP      |  |

| Laser Splitting                      | N/A                 | 50:50                |                                       |  |

| Driver Power Coefficient $c_0$       | 0.075 W             | 0.1 W                | Linear driver power fit to commercial |  |

| Driver Power Coefficient $c_1$       | 0.175 V             | -0.375  V            | driver performance. Limiting driver   |  |

| Driver Power Coefficient $c_2$       | 1.225               | 1.25                 | power fit to performance in [34].     |  |

| Driver CTLE Peaking                  | 6 dB                |                      |                                       |  |

| Driver CTLE Frequency                | $50~\mathrm{GHz}$   |                      |                                       |  |

| Driver Bandwidth                     | 40 GHz              |                      |                                       |  |

| MZM Bandwidth                        | $30~\mathrm{GHz}$   |                      |                                       |  |

| TIA Bandwidth                        | 40 GHz              |                      |                                       |  |

| MZM Phase Efficiency $V_{\pi}$       | 6.7 V               |                      |                                       |  |

| $MZM Z_0$                            | 30 Ω                |                      |                                       |  |

| SOA Carrier Lifetime $\tau_c$        | 200 ps              |                      |                                       |  |

| SOA $P_{sat}$                        | $15~\mathrm{dBm}$   |                      | Fit to performance in [35]            |  |

| SOA $\alpha$                         | 5                   |                      |                                       |  |

| SOA $n_{sp}$                         | 3.5                 |                      |                                       |  |

| SOA $V_d$                            | 0.88                |                      |                                       |  |

| SOA $R_s$                            | 10 Ω                |                      |                                       |  |

| Operating Wavelength                 | 1310 nm             |                      |                                       |  |

| Photodiode Responsivity $\mathbb{R}$ | 1 A/W               |                      |                                       |  |

| TIA RMS Input Noise                  | $7.2~\mu\mathrm{A}$ |                      |                                       |  |

| Tx Excess Losses                     | 9 dB                |                      |                                       |  |

| Mux+Demux Excess Losses              | 2 dB                |                      |                                       |  |

| Rx Excess Losses                     | 5.5 dB              |                      |                                       |  |

| LO Excess Losses                     | 2  dB               |                      |                                       |  |

| Fiber Loss                           | 1 dB                |                      |                                       |  |

Table 3.1: Link simulation parameters.

power consumption is calculated from

$$P_{SOA} = V_d I_{SOA} + R_s I_{SOA}^2 (3.7)$$

where  $V_d$  is the diode voltage drop and  $R_s$  is the SOA series resistance. The modeled SOA power consumption vs. saturated gain is shown in Fig. 3.2(f) for -11 dBm of input

power.

#### 3.4.2 Simulation Results

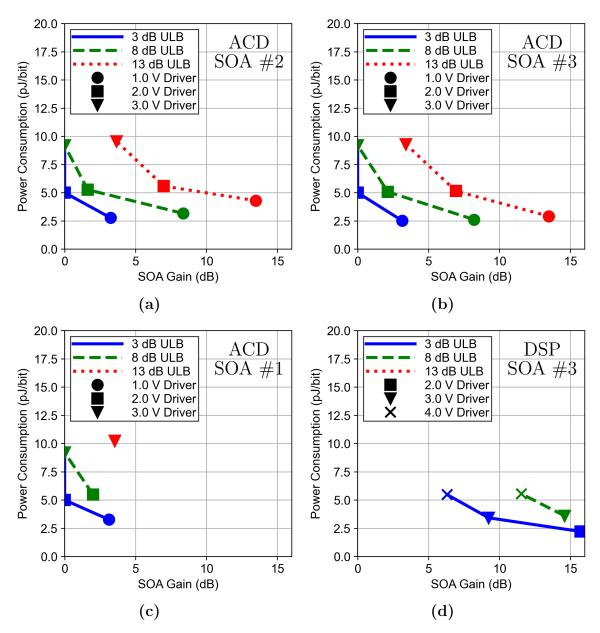

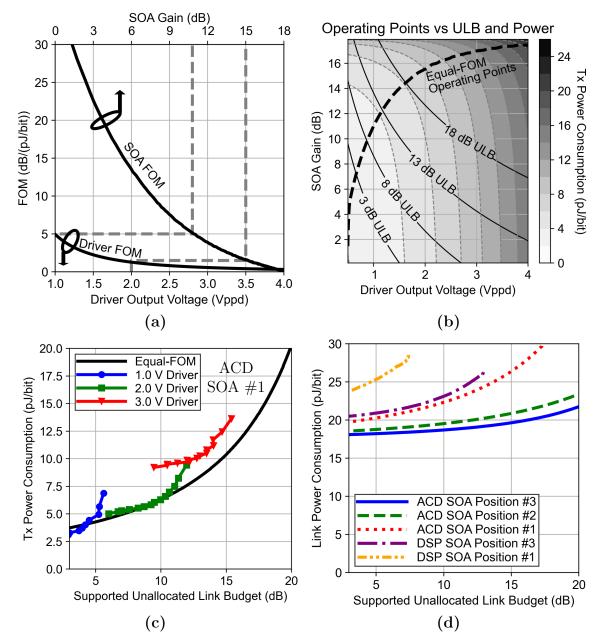

The link simulation was carried out for each of the coherent architectures outlined in Section 3.2. For each configuration of driver output voltage and SOA gain, the link was simulated multiple times to determine the acheivable unallocated link budget (ULB), modelled as additional insertion loss on the fiber, while meeting the target BER. The simulation results for various architectures are shown in Fig. 3.3, where Fig. 3.3(a-d) show the combined driver and SOA power consumption vs. the saturated SOA gain G. ACD-based and DSP-based link power consumption are normalized to 200 and 400 Gbps/ $\lambda$ , respectively, ignoring forward error correction (FEC) overhead bits.

Across the simulations, power consumption is generally improved by operating at lower driver swings and higher SOA gains. Fig. 3.3(a) shows the link design space for an ACD-based link with an SOA in position #2, where compensating for reducing driver output voltage by increasing SOA gain results in lower overall power consumption for all ULBs plotted. Further modest improvements in power consumption are achieved by moving from SOAs in position #2 to WDM amplification with SOAs in position #3, as shown in Fig. 3.3(b) and (d), despite increased input power and crosstalk at the SOA from three other simulated WDM channels. WDM amplification improved power efficiency by a larger amount for the ACD-based architecture than for the DSP-based architecture due to QPSK's increased tolerance to SOA NLPN.

The expected drawback of an architecture with an SOA in position #1 was that the high input power from the laser would saturate the SOA. Indeed, Fig. 3.3(c), shows that large SOA gains were not attainable, as they were in Fig. 3.3(a), (b) and (d). This limits the power efficiency of this architecture compared to one with SOAs in position #2 or

Figure 3.3: Driver and SOA Power consumption vs. SOA gain for an ACD-based link with SOA in position #2 (a), #3 (b), and #1 (c), and for a DSP-based link with SOA in position #3 (d), where each curve corresponds to a particular supported ULB, and the differential peak-to-peak driver output voltages are marked.

#3, where the minimally saturated SOA gain enables 6 pJ/bit better power efficiency for link operation at 13 dB ULB. Links with SOAs in positions #4 or #5 were dominated by ASE noise at the receiver that was unattenuated by link losses, and did not see improved

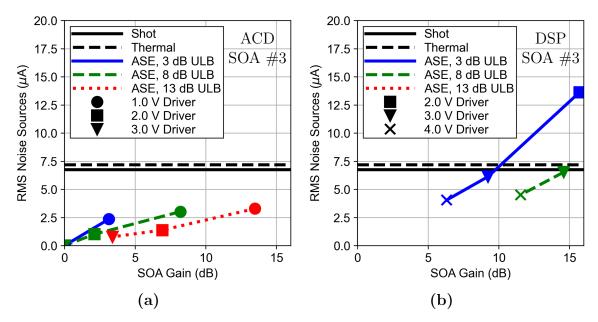

Figure 3.4: RMS noise currents at the receiver vs position #3 SOA Gain for an ACD-based link (e) and a DSP-based link (f).

performance for the link parameters assumed here.

The shot, thermal, and ASE noise components, referred to the input of the receiver and corresponding to the plotted results in Fig. 3.3(b) and (d), are shown in Fig. 3.4(a) and (b), respectively. While the shot and thermal noise levels remain constant, the ASE noise varies strongly with SOA gain. The ASE noise in the DSP-based link simulations was comparable to the receiver shot and thermal noise levels, and the ACD-based link simulations had lower, although non-negligible ASE noise contributions. The power consumption vs SOA gain curves in Fig. 3.3(c-f) do not reach an optimized minimum, however, because they were limited by the 16 dB maximum gain determined by the SOA model parameters that were chosen for this analysis. A higher-gain SOA design could enable power efficiency improvement with increased ASE noise contribution at the optimal operating point. These results suggest that short-reach coherent links optimized for power efficiency will operate in a hybrid regime in which the shot, thermal, and ASE noise contributions are all appreciable. This is a notable departure from current

conventional links, where long-reach coherent links are dominated by ASE noise and short-reach IMDD links are dominated by receiver thermal noise. In describing the links that operate in this hybrid noise regime, receiver BER sensitivity can no longer be characterized solely with respect to either received optical power or OSNR, but now requires a combination of both optical power and ASE noise information.

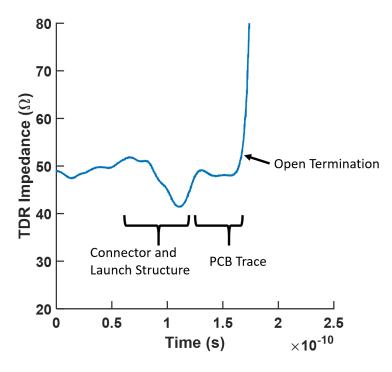

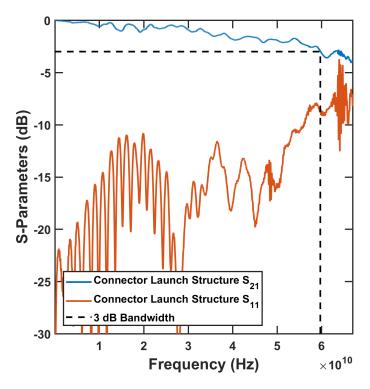

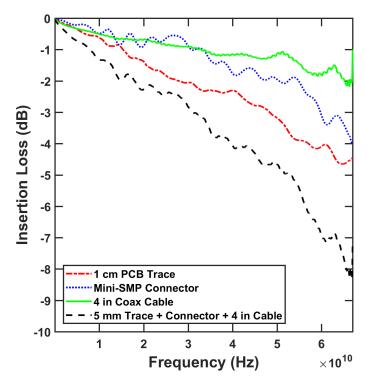

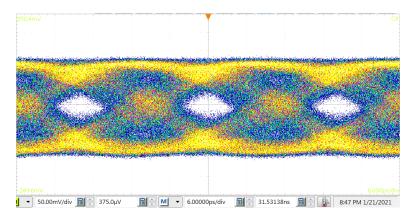

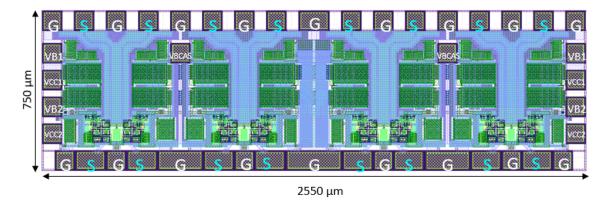

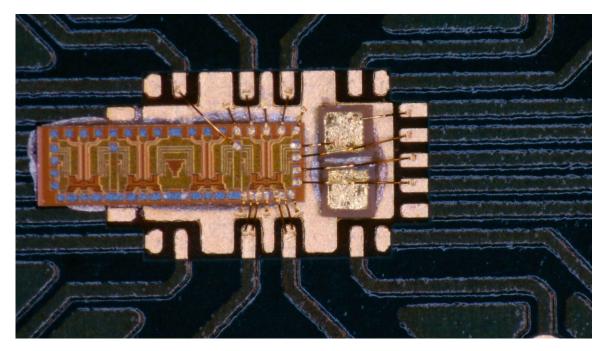

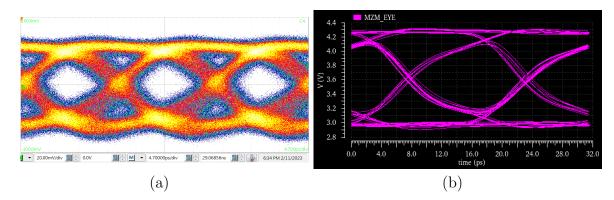

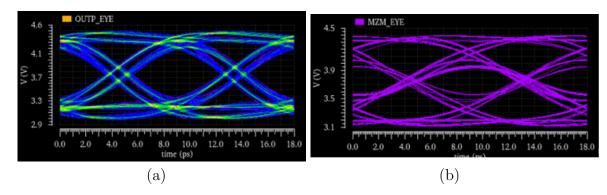

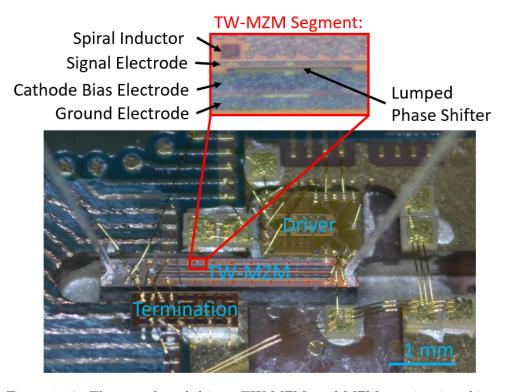

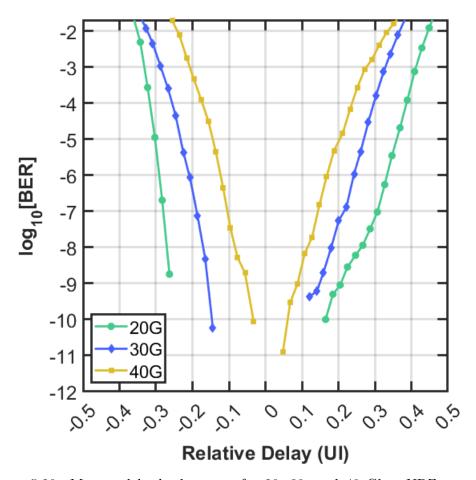

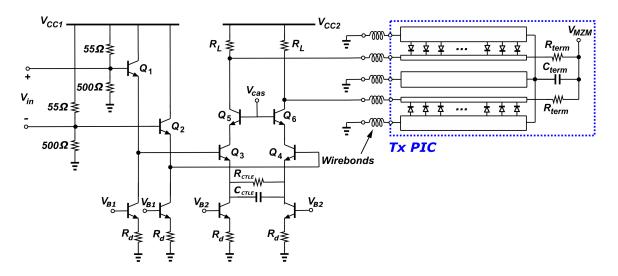

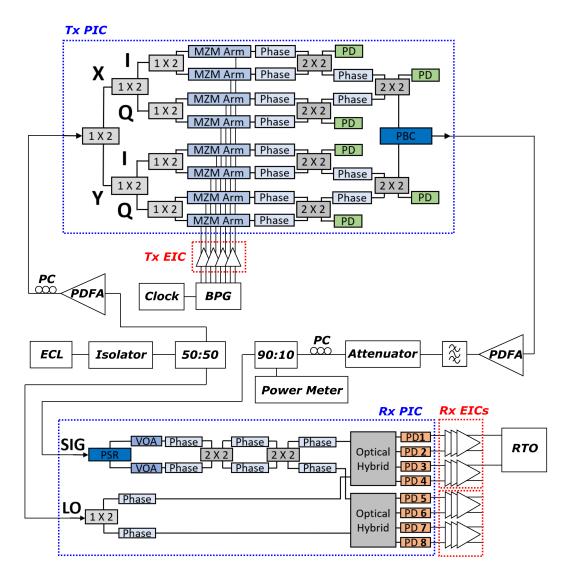

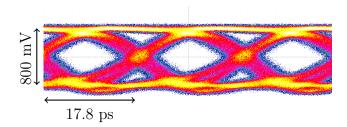

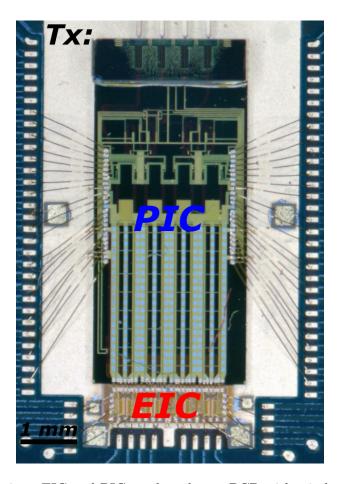

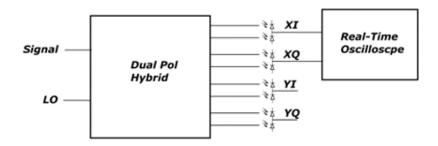

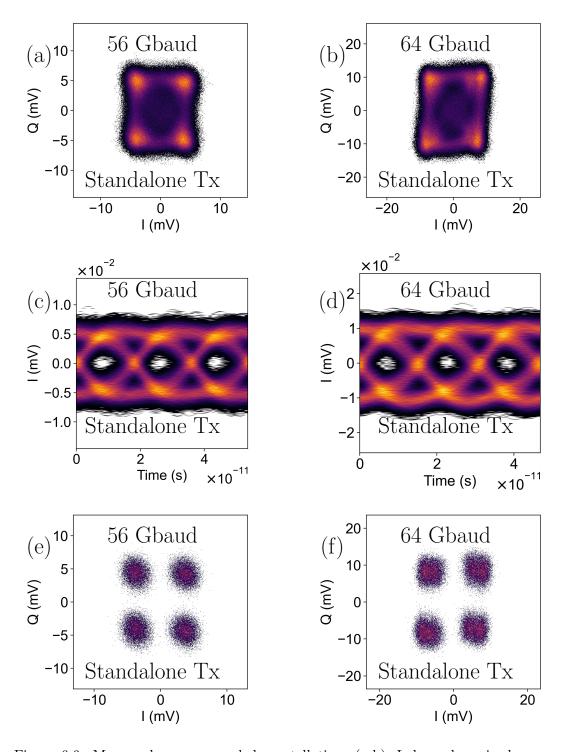

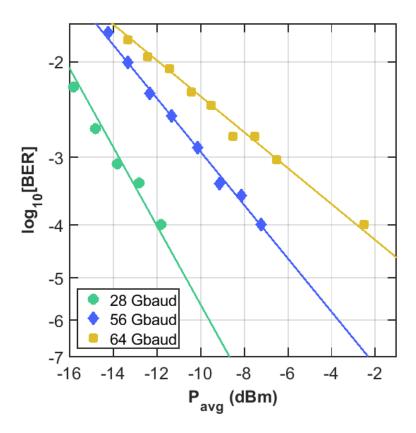

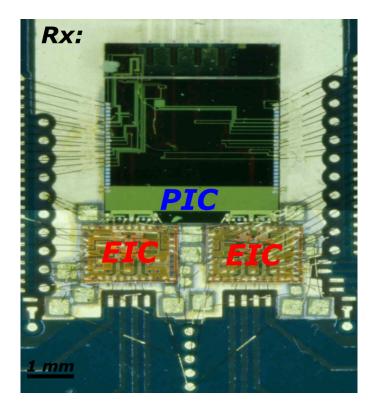

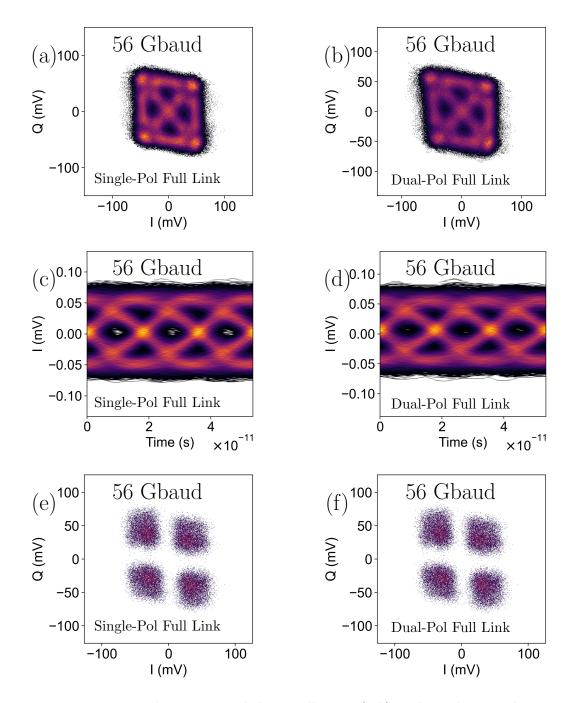

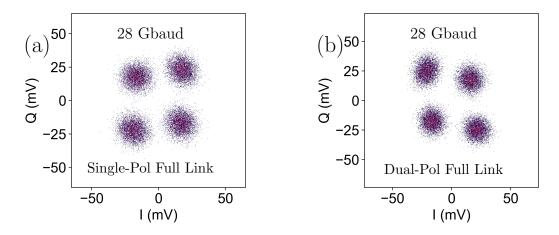

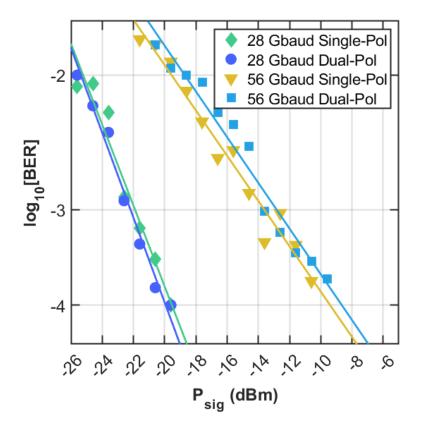

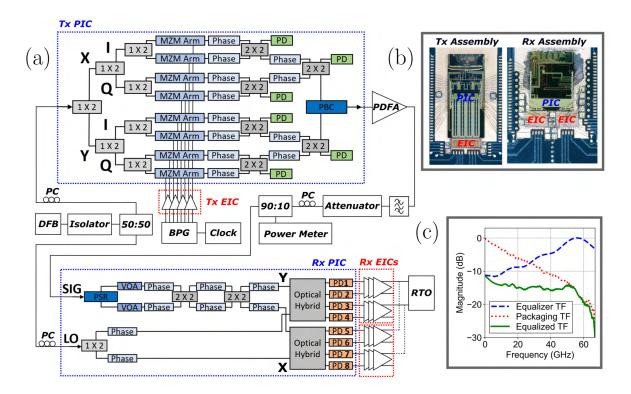

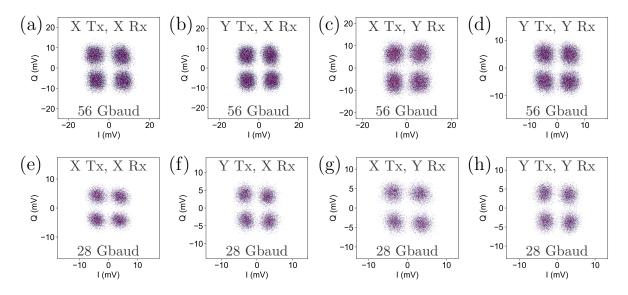

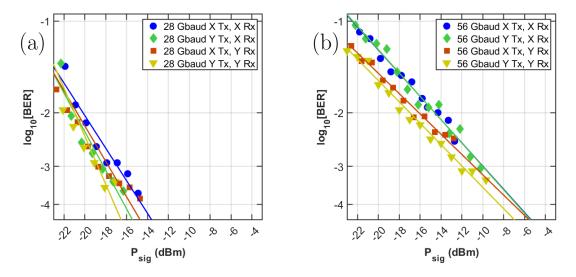

### 3.4.3 Optimization Theory