## Lawrence Berkeley National Laboratory

**Bldg Technology Urban Systems**

### Title

An Integrated Multilevel Converter with Sigma Delta Control for LED Lighting

## Permalink

https://escholarship.org/uc/item/7s54j2d9

## Authors

Gerber, Daniel L Kline, Mitchell Sanders, Seth R <u>et al.</u>

## **Publication Date**

2017-03-01

## DOI

10.1109/apec.2017.7931035

Peer reviewed

# An Integrated Multilevel Converter with Sigma-Delta Control for LED Lighting

Daniel L. Gerber, *Member, IEEE*, Chengrui Le, *Member, IEEE*, Mitchell Kline, *Member, IEEE*, Peter R. Kinget, *Fellow, IEEE*, and Seth R. Sanders, *Fellow, IEEE*

Abstract—LEDs have finally emerged as the dominant lighting technology. As such, the lighting industry values power converters that have high efficiency, unity power factor, minimal flicker, dimming, low cost, and a small form factor. This paper presents an integrated circuit (IC) LED driver that is designed to achieve these goals. It introduces multilevel converters with sigma-delta modulation to the power IC space. The driver features a pair of sigma-delta controlled multilevel converters. The first is a multilevel rectifier responsible for power-factor correction (PFC) and dimming. The second is a bidirectional multilevel inverter used to cancel AC power ripple from the DC bus. The system also contains an output stage that powers the LEDs with DC and provides for galvanic isolation. The IC LED driver has been simulated and prototyped on a silicon fabrication process. Its functional performance indicates that integrated multilevel converters are a viable topology for lighting or other similar applications.

#### I. INTRODUCTION AND BACKGROUND

#### A. The Challenge of Driving LEDs

Solid-state lighting is recognized for its efficiency, reliability, and environmental benefits. The combination of efficiency and life span makes LEDs the most economic choice for lighting. As such, it is important that the LED driver be equally inexpensive, efficient, and reliable.

There are several technical challenges in driving LEDs [1]. First, LEDs have an exponential current-voltage relationship. For this reason, LED drivers must employ precise current control in order to regulate the luminous output of the LEDs. Second, LEDs have a fast luminous response to power. The driver's AC input may transfer 120 Hz power ripple to the LEDs, which may in turn cause 120 Hz LED flicker [2], [3]. Flicker can have an adverse effect on human health including headaches, loss of concentration, and seizures. As such, the driver must have a means of reducing power ripple at the LEDs. Finally, LEDs fail at high temperature and require careful thermal management. For safety considerations, the LED heat sink must be galvanically isolated from the power train. Providing a means to galvanically isolate the LEDs allows the LEDs to be directly mounted on the heat sink. Thus, galvanic isolation of the LEDs is a desired circuit function.

Several circuit topologies have been industrially developed to meet these challenges. The linear LED driver uses a linear regulator to perform both current control and power-factor correction (PFC) [4], [5]. Its advantages are in size and cost, and it injects very little electromagnetic interference onto the line. Its disadvantages are that it lacks galvanic isolation, and it has a relatively low efficiency when the LED string is not perfectly matched to the input voltage. Switched-mode LED drivers such as the buck [6], [7], boost [8], [9], and buck-boost [10] utilize high-frequency switching and duty-cycle control to achieve PFC and output power regulation. They are usually more efficient than linear regulators since the conversion voltage drop primarily occurs across reactive components. However, switched-mode drivers lack galvanic isolation and require a relatively large inductor to reduce harmonic injection and avoid discontinuous conduction mode. The flyback LED driver is an isolated switched-mode converter that utilizes the magnetizing inductance in the flyback transformer [6], [11]–[15]. Because of its efficient conversion and galvanically isolated output, the flyback LED driver is currently the mainstream topology for high brightness LED lamps. Its main disadvantage is in the size and cost of the flyback transformer.

Several topologies have been proposed in research, each with the aim of removing the flyback transformer. Resonant LED drivers contain a resonant tank at the output [16]–[18]. They regulate the output LED current through adjustments to the switching frequency. Several designs even leverage the resonant tank for galvanic isolation [17], [18]. The resonant topology facilitates zero-voltage switching [19]-[21], which is hugely beneficial in improving efficiency, reducing switch stress, and allowing for smaller switches. Quasiresonant topologies improve on various switched-mode converter topologies by adding a small resonant tank near the power switch. Although the quasi-resonant tank does not regulate the output current, its presence allows for all the benefits of zero-voltage switching. Several quasi-resonant LED drivers have been proposed as soft switching variations of the flyback [22] or boost [23] drivers.

Switched capacitor converters have recently been in the research spotlight for low to moderate power conversion. As such, they have naturally been considered in lighting applications [17], [18]. The switched capacitor converter uses an array of switches and capacitors as a charge pump. Its major advantage is that no magnetics are required for fixed-ratio voltage conversion, making it very amenable to integration.

#### B. Power Ripple and Flicker

As mentioned in Section I-A, AC power ripple at the driver input can cause flicker on the LEDs. When a lamp operates with unity power factor, its input current  $Isin(\omega_0 t)$  is sinusoidal and in phase with the line voltage  $Vsin(\omega_0 t)$ . The

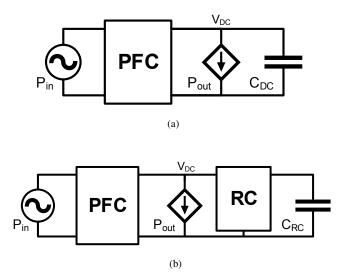

Fig. 1. Methods for reduction or cancellation of 120 Hz power ripple from the driver's power-factor correction (PFC) input module. It is desirable for the driver's output to the LEDs,  $P_{out}$ , to be constant. (a) Passive ripple cancellation involves the use of a large DC capacitor  $C_{DC}$  to filter the ripple. (b) An active ripple cancellation strategy that involves the use of a separate power converter for ripple cancellation. The ripple-cancellation (RC) module includes a storage capacitor  $C_{RC}$  that can be much smaller than  $C_{DC}$ .

resulting input power is

$$P_{in} = V sin(\omega_0 t) I sin(\omega_0 t) = \frac{VI}{2} - \frac{VI}{2} cos(2\omega_0 t)$$

$$= P_{out} + P_{RC}$$

(1)

where  $\omega_0$  is  $2\pi 60$  in the US. The average power  $P_{out}$  represents the desired DC output to the LEDs. Since the 120 Hz ripple power  $P_{RC}$  contributes directly to 120 Hz flicker, it is desirable to cancel  $P_{RC}$  from the driver's output. IEEE Standard 1789-2015 [24] suggests that 120 Hz flicker can be considered low risk below 10% flicker, and has no effect below 4% flicker.

Many LED drivers use passive ripple cancellation. As shown in Fig. 1a, passive ripple cancellation methods often require a post-rectification DC capacitor bank, which must be large enough to filter the low-frequency ripple power. For high capacitance and high voltage applications, electrolytic capacitors are considerably more cost effective than ceramic capacitors. However, electrolytics can be problematic in LED drivers due to their bulk and limited life span [6], [25]–[28]. High driver temperatures speed the evaporation of the liquid electrolyte, which can cause the capacitor to fail within five years. Since LEDs last up to twenty years, addressing or removing the electrolytic capacitor can greatly improve the life span of the lamp. Additional problems with electrolytics include high resistive loss in aging capacitors and the potential to explode when stressed by a short circuit or hydrogen buildup.

In order to eliminate the electrolytic capacitor, there has been a push toward the research and development of high quality LED drivers that employ active ripple cancellation techniques [27]–[32]. Such techniques include multiple power conversion stages, discontinuous conduction mode (DCM) [28]–[30], resonant current control [31], and the addition of a separate ripple cancellation module or energy buffer [27], [32], [33]. As shown in Fig. 1b, the LED driver in this work utilizes a separate ripple cancellation module that transfers ripple energy to a storage capacitor  $C_{RC}$ . As shown in Eq. 1, the desired constant output power  $P_{out}$  can be achieved if  $P_{RC}$  is transferred to the storage capacitor  $C_{RC}$ , the active ripple cancellation module can swing the voltage across  $C_{RC}$ , as explained in Sec. IV-B.

An active ripple cancellation module has the benefit of greatly reducing the required capacitor size. As shown in Fig. 1, the passive ripple-cancellation strategy requires a central DC capacitor  $C_{DC}$ , while the active ripple-cancellation module requires a storage capacitor  $C_{RC}$ . Driver specifications often allow for a fractional amount of ripple power F to pass to the LEDs. As such,  $P_{RC}F$  may be transferred to the LEDs, and  $P_{RC}(1-F)$  must be transferred to  $C_{DC}$  or  $C_{RC}$ . The energy on  $C_{DC}$  or  $C_{RC}$  is developed from Eq. 1 as

$$P_{cap} = (1 - F)P_{RC} = (1 - F)\frac{VI}{2}cos(2\omega_0 t)$$

$$E_{cap} = \int P_{cap} = -(1 - F)\frac{VI}{4\omega_0}sin(2\omega_0 t) + E_{cap,avg}.$$

(2)

The size of a capacitor capable of absorbing  $P_{cap}$  can be derived from the capacitor's energy swing as

$$\frac{1}{2}CV_{cap,max}^{2} - \frac{1}{2}CV_{cap,min}^{2} = 2(1-F)\frac{VI}{4\omega_{0}}$$

$$C(V_{cap,max} + V_{cap,min})(V_{cap,max} - V_{cap,min})$$

$$= (1-F)\frac{VI}{\omega_{0}}$$

$$C = (1-F)\frac{VI}{\omega_{0}(2V_{cap,avg})(V_{cap,swing})}$$

(3)

where  $V_{cap,swing}$  is the maximum allowed peak-peak voltage range the capacitor can swing, and  $V_{cap,avg}$  is the average DC voltage of the capacitor.

With passive ripple cancellation, the capacitor voltage is coupled to the output voltage, as shown in Fig. 1a. In this way,  $V_{cap,avg} = V_{DC}$  and  $V_{cap,swing} = V_{DC}F$ . The required DC capacitor size is thus

$$C_{DC} = \frac{(1-F)}{2F} \frac{VI}{\omega_0 V_{DC}^2}.$$

(4)

The active ripple-cancellation strategy in Fig. 1b has a decoupled storage capacitor whose voltage can swing between ground and  $V_{DC}$ . With  $V_{cap,avg} = V_{DC}/2$  and  $V_{cap,swing} = V_{DC}$ , the required storage capacitor size is

$$C_{RC} = (1 - F) \frac{VI}{\omega_0 V_{DC}^2} = (2F)C_{DC}.$$

(5)

The result of this analysis shows that the required size of the passive method's DC capacitor  $C_{DC}$  is much larger than the required active method's storage capacitor  $C_{RC}$ . Consider the design of a 20 W LED driver with  $V_{DC} = 180$  V and

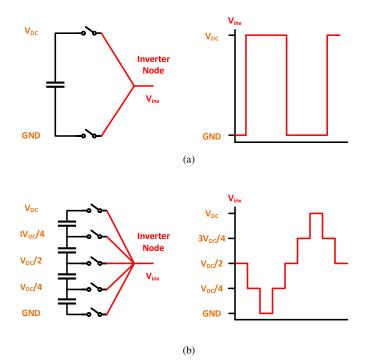

Fig. 2. Theoretical multilevel converters.  $V_{inv}$  can be connected to any of the levels of the DC capacitor bus, producing the output waveforms on the right. (a) Two-level inverter, or half-bridge. (b) Five-level inverter.

a fractional output ripple of F = 0.066, equivalent to an A19 incandescent bulb with 6.6% flicker [2], [3]. The driver requires  $C_{RC} = 1.5\mu F$  or  $C_{DC} = 12\mu F$ , for active or passive ripple-cancellation respectively. It can be shown that the passive driver will need a high voltage electrolytic capacitor [34]. The required  $C_{DC}$  increases very quickly with lower flicker specifications.

#### C. Integrated Multilevel Converters as LED Drivers

This work introduces multilevel circuit methods to the LED driver space as a means of addressing the challenges in driving LEDs (Section I-A) while also reducing the volumetric requirements for passive elements. Multilevel converters are a class of power converters that distribute the switching functionality and stress over an array of vertically stacked power switches. As shown in Fig. 2, multilevel converters are capable of connecting their inverter node to one of several DC levels. The DC levels are maintained on a DC bus, which is usually implemented with actively balanced capacitors.

Multilevel inverters have become popular in the last decade as a means to utilize lower voltage solid-state switches in high voltage applications [35]. They have the advantage of reducing individual switch stress by distributing high voltage over multiple switches. Multilevel inverters also have the ability to output one of several voltage levels, thus allowing for greatly reduced harmonic content compared to the standard two-level inverter. This feature ultimately allows for reduction in a converter's switching frequency or passive filtering requirements. Various multilevel inverter topologies have been proposed, such as the diode-clamped [36], capacitor-clamped [37]–[40], and cascaded topologies [41]. Several multilevel inverter topologies can be simplified to function as rectifiers, such as the Vienna rectifier [42]. Multilevel topologies can also be useful for energy buffer circuits [33], [43].

Since multilevel converters involve many active devices, integrated circuit (IC) technology is a convenient means of producing an efficient low-cost LED driver with small form factor. IC applications often revolve around integrating full systems onto a single chip. However, many silicon processes have device voltage limitations that would present a challenge for the design of fully integrated power systems. As such, it is natural to develop the driver using a multilevel topology so as to reduce voltage stress on each individual power switch. Overall performance may be evaluated with techniques developed in the switched capacitor design frameworks [44], [45].

In this work, a multilevel topology allows the IC to interface with the line voltage despite its device voltage limitations. In addition, this topology reduces the requirements on passive elements in the driver. The multilevel circuit function is used in two positions, one to provide power-factor correcting (PFC) rectification, and a second to provide bidirectional power flow for ripple cancellation. The generalized multilevel topology [46] is chosen because it addresses both of these functions and admits a fairly regular gate drive pattern. Other choices may very well be advantageous in optimizing die area.

Several control strategies exist for inverters and active rectifiers. Popular methods include sinusoidal PWM, space vector modulation [47], and selective harmonic elimination [48]. This work uses sigma-delta modulation [49] because of its simple implementation and direct mapping into the multilevel modulation function.

Sigma-delta modulation is often presented as a cost-effective strategy for analog to digital signal conversion in low bandwidth applications. It is naturally attractive in switching converters, which require converting a low-bandwidth control signal to one of the discrete conduction states present in an H-bridge or multilevel converter. Switch modulation produces quantization noise, which is modeled as a white process with uniform noise power. Sigma-delta modulation invokes closed-loop control to shape the noise power spectrum [50]– [54]. In practice, the sigma-delta loop functions to push the quantization noise to higher frequencies, after which it can easily be filtered out. Intuitively, the output of the sigma-delta modulator attempts to best approximate the input.

Previous work has detailed the construction of diode or capacitor clamped multilevel inverters [36], [37], but very few have built a generalized multilevel converter. Sigma-delta control for multilevel inverters has been simulated in other papers [49], [55]–[58] but has seldom been put to practice, especially in rectification. Most importantly, this research introduces multilevel converters to the power IC space. DC-DC circuits such as the switched capacitor (SC) circuit have had the recent spotlight in the emerging field of power ICs [17], [44], [45], [59]. However, this research is the first to build a fully integrated multilevel converter, thus introducing a number of engineering benefits and challenges to the fields

of multilevel converters and power ICs.

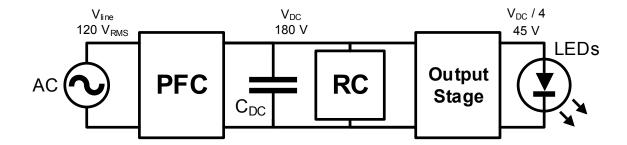

#### II. FULL SYSTEM ARCHITECTURE

The full system in Fig. 3 contains an input power-factor correction (PFC) rectifier, a ripple-cancellation (RC) circuit, a DC capacitor bus, and an output stage. The PFC rectifier converts the AC line voltage to DC with low harmonic current injection, and provides for input current regulation and dimming. The dimming level is directly controlled by the input current regulation since subsequent stages simply convert this current and feed it to the LED string. Voltage regulation is effected by the LED string voltage-current characteristic. The ripplecancellation circuit cancels ripple on the DC capacitor bus. Finally, the output stage down-converts the DC bus voltage and uses a small transformer to provide for galvanic isolation. At full power, the system is designed to operate at

At full power, the system is designed to operate at 20 W, with an input voltage and current of 120  $V_{RMS}$  and 167 mA<sub>RMS</sub>, respectively. The nominal voltages of the internal DC bus and output LED string are respectively 180 V and 45 V, but these voltages may vary by application and dimming level.

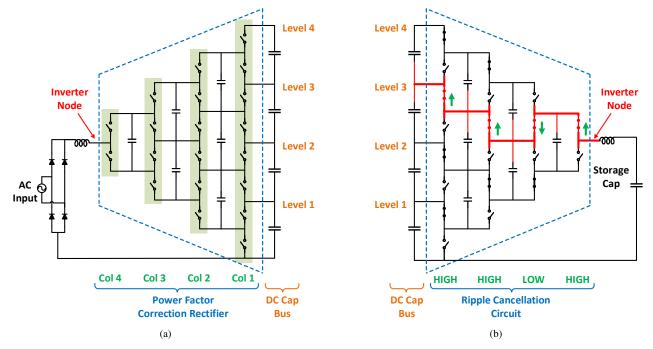

#### III. MULTILEVEL TOPOLOGY FOR PFC AND RIPPLE-CANCELLATION MODULE

The power-factor correction (PFC) rectifier and ripplecancellation modules use a generalized multilevel topology, as shown in Fig. 4. Each switching column contains transistors that switch synchronously and alternate in complementary pairs. By switching the various columns high or low, the inverter node can be connected to any of the five DC levels. Each column connects to a set of smaller integrated flying capacitors, which assist in rapidly stabilizing the column voltages and serve as a supply for the gate drivers. This topology is bidirectional, allowing the circuit to be configured as a rectifier or inverter, for PFC and ripple cancellation, respectively. It can also self-balance the DC capacitor bus such that the voltages across the DC capacitors are equal [46].

The power-factor correction (PFC) rectifier functions to enforce unity power factor and control the input power. As shown in Fig. 4a, the PFC rectifier can control the voltage at the inverter node. In this way, the PFC rectifier can set the voltage across the input inductor, and thus control the input current. Fine control over the input current enables harmonic reduction and allows for dimming via current control.

As mentioned in Section I-B, 120 Hz input power ripple can cause LED flicker. The ripple-cancellation module functions to actively cancel ripple from the DC capacitor bus. As shown in Fig. 4b, the ripple-cancellation circuit is able to transfer ripple energy from the DC capacitor bus to the storage capacitor by precisely swinging the storage capacitor voltage. This allows for a huge reduction in the required DC capacitor size, and obviates the need for electrolytics.

#### IV. SIGMA-DELTA CONTROL

The multilevel converters in the power-factor correction (PFC) and ripple-cancellation modules are controlled via sigma-delta modulation. In this context, the multilevel converter behaves like a quantizer since it can only set the inverter

node to one of several quantized levels. Like any quantizer, the multilevel converter produces quantization noise. Sigmadelta modulation invokes closed loop control to push the quantization noise to higher frequencies, after which it can easily be filtered out [50]. Intuitively, the output of the sigmadelta modulator will attempt to best approximate the input.

As a control scheme, sigma-delta modulation has the distinct advantage of simplicity. Fig. 5b suggests that a simple firstorder sigma-delta control loop could be implemented with a single integrating op-amp. Sigma-delta modulation also has the advantages of closed-loop robustness and stability, assuming that the loop is properly designed. Finally, the quantization behavior of the multilevel converter causes sigma-delta modulation to simply be a very convenient control scheme. PWM is rather difficult and complicated for multilevel converters because a triangle wave must be generated between each level. Techniques such as space vector modulation, and selective harmonic elimination all require complicated control.

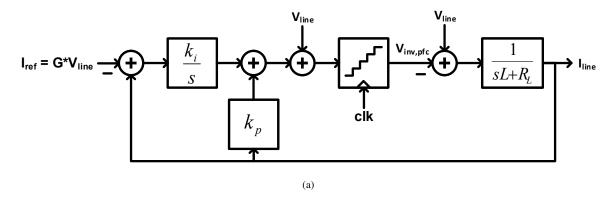

#### A. Control for the PFC Rectifier

The power-factor correction (PFC) rectifier uses a second order sigma-delta loop to set the line current to best approximate a reference current waveform. As shown in Fig. 5a, the reference current waveform  $I_{ref}$  is nominally sinusoidal and in-phase with the line voltage. Sigma-delta control is especially useful because its ability to shape quantization noise is necessary for meeting the line current harmonic specs. The variable current control factor G can modulate the amplitude of  $I_{ref}$ , which ultimately controls the input power. In this way, LED dimming is achieved by decreasing G, and thus choking the driver's input power.

The control loop design in Fig. 5a allows for the adjustment of the integral gain  $k_i$  and the proportional gain  $k_p$ . It is often reasonable to set

$$K = (k_i/f_s)(\Delta/\delta) = 1 \tag{6}$$

where the quantizer is clocked at frequency  $f_s$ , and its quantization levels step by  $\Delta$  at the output and  $\delta$  at the input [56], [57]. If K >> 1, the quantizer may attempt to switch by more than one level at a time. If K << 1, the quantizer output may experience dead zones in which it does not switch when it should. After  $f_s$  and  $k_i$  are selected,  $k_p$  can be chosen to help shape the quantization noise curve. In this work, L = 10 mH,  $R_L = 2 \Omega$ ,  $k_i = 1e7$ , and  $k_p = 25$ . The PFC rectifier samples at  $f_s = 400$  kHz.

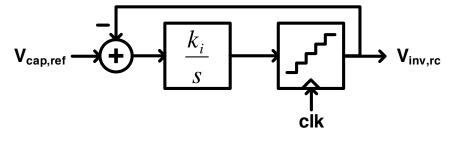

#### B. Control for the Ripple-Cancellation Module

The ripple-cancellation module uses sigma-delta modulation to swing the storage capacitor voltage such that the 120 Hz power ripple is cancelled from the DC bus. The 120 Hz ripple power  $P_{RC}$  is previously developed in Eq. 1, and does not account for internal driver losses. An ideal active ripple-cancellation module transfers all of  $P_{RC}$  to the storage capacitor. As such, the ideal voltage waveform  $v_{cap,ref}$  on the

Fig. 3. Block diagram of the LED driver with power-factor correction (PFC), ripple cancellation (RC), and output stage. C<sub>DC</sub> indicates the DC capacitor bus.

Fig. 4. Generalized multilevel schematic for the PFC rectifier and ripple-cancellation module. The DC capacitor bus helps define the DC levels, buffers power flow, and connects to the output stage (not shown here). (a) PFC with switching columns highlighted in green. (b) Ripple-cancellation module with an example switch configuration for connecting the inverter node to level 3. Note that the DC capacitor bus is shared between (a), (b), and the output stage in Fig. 6.

storage capacitor is derived from its energy  $E_{RC}$  as:

$$E_{RC}(t) = \frac{1}{2}C_{RC}v_{cap,ref}^{2}(t) = \int_{-\infty}^{t} P_{RC}(t)$$

(7)

$$\sqrt{VI} + V_{max}^{2} + V_{min}^{2}(t)$$

(7)

$$v_{cap,ref}(t) = \sqrt{-\frac{VI}{2\omega_0 C_{RC}}}\sin(2\omega_0 t) + \frac{V_{max}^2 + V_{min}^2}{2}$$

for storage capacitance  $C_{RC}$ .  $V_{max}$  and  $V_{min}$  are the maximum and minimum levels that the storage capacitor voltage should be constrained to.

In this work, the ripple-cancellation module relies on openloop control with a look-up table parameterized by dimming level command, eg. power level. Each  $v_{cap,ref}$  waveform stored in the look-up table corresponds to one half-period of data. The data is actually the modulation waveform, generated with a system as indicated in Fig. 5b. In practice, the waveform is triggered by the line voltage zero crossing.

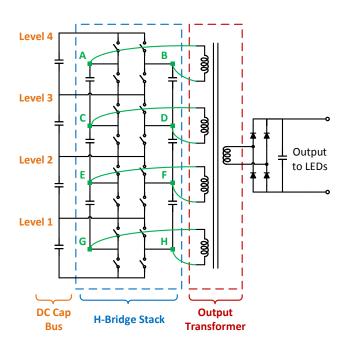

#### V. OUTPUT STAGE

As shown in Fig. 6, power is provided to the LEDs through the output stage, which consists of an array of stacked Hbridges and an output transformer. The output stage functions as a fixed-ratio 4:1 series-parallel step-down circuit, which serves to step the 180 V DC capacitor bus voltage down to the 45 V LED output. Another function of the output stage is to facilitate in balancing the voltage levels on the DC capacitor bus, which is crucial for correct operation of the power-factor correction (PFC) and ripple-cancellation modules.

Each of the inverter nodes in the H-bridge stack is connected to a small isolation transformer. This transformer has four primary windings and one secondary, all of which have the same number of turns. The transformer is useful in galvanically

(b)

Fig. 5. The sigma-delta control loops for the PFC rectifier and ripple-cancellation module. Each loop has an integrator and a quantizer clocked at 400 kHz. (a) A second order sigma-delta loop is used for the PFC rectifier. The first pole is obtained from the input inductor with inductance L and series resistance  $R_L$ . The voltage across the inductor is the difference between the line voltage  $V_{line}$  and the inverter node of the PFC rectifier  $V_{inv,pfc}$ . The second pole is obtained from the control blocks with integral gain  $k_i$  and proportional gain  $k_p$ . Negative feedback causes the input current  $I_{line}$  to closely track a reference current  $I_{ref}$ . Dimming is adjusted via the input gain G, which scales the line voltage waveform to the intended input current level. (b) A first order sigma-delta loop is used for the ripple-cancellation module. This module uses the sigma-delta loop to set the inverter node of the ripple-cancellation circuit  $V_{inv,rc}$  to approximate a preprogrammed waveform  $V_{cap,ref}$ .

isolating the LEDs from the high voltage circuits, and in facilitating the series-parallel connection of this stage. In addition, it provides soft switching to the H-bridge stack via its leakage and magnetizing inductance. This transformer is not designed to store energy, and so it can be substantially smaller than that of an equivalent flyback converter. Its size is determined by the desired switching frequency of the H-bridge stack. Even with a small toroid, the H-bridge stack can be clocked at 50 kHz or lower.

An alternative output stage topology, the hybrid resonant switched capacitor (HRSC) converter, is discussed in [17]. In the HRSC topology, the H-bridge stack does not require an output transformer, but instead achieves galvanic isolation via capacitive coupling to a resonant tank. Adjusting the switching frequency of the H-bridge stack adjusts the driving frequency of the resonant tank, thereby providing a secondary means of current control to the LEDs. The main disadvantage of the HRSC are that it must switch in the MHz range in order to leverage a reasonably sized resonant tank for current control. In addition, the coupling capacitors have to withstand the relatively high resonant tank voltage. Although [17] demonstrates the HRSC as a viable alternative, the LED driver in this work uses the transformer output topology (Fig. 6) because the power-factor correction rectifier already provides for current regulation.

#### VI. EXPERIMENTAL RESULTS

#### A. Integration and Testing

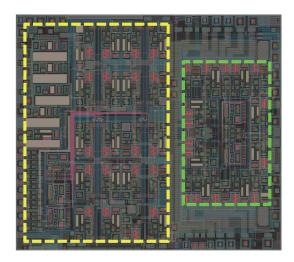

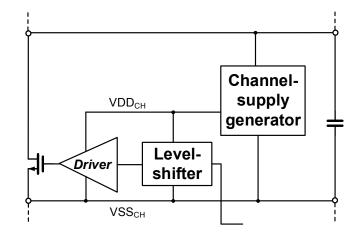

The full system from Fig. 3 has been simulated, experimentally tested, and verified. A prototype IC, shown in Fig. 7, was designed and fabricated on an Analog-Bipolar-CMOS-DMOS (ABCD) high voltage process. The IC contains the circuitry for a multilevel converter and a H-bridge stack. Both circuits use 100 V N-type LDMOS transistors as their power switches, and every power switch requires an integrated gate driver.

The architecture for the chip's gate driver is shown in Fig. 8. Each gate driver consists of a floating channel supply generator, a level shifter, and a driver. The channel supply uses power from a DC or flying capacitor to create a floating 5 V supply. Its function is to provide power to the level shifter and the driver. The level shifter is responsible for shifting a low voltage digital signal up to the floating voltage domain. Finally, the driver is an inverter that amplifies the floating digital signal with enough power to drive the gate capacitance of the power switch. Additional details about the design of the gate driving channel are discussed in [17].

The test board in Fig. 9 is implemented on a 2-layer PCB and the system is controlled via off-chip components and

Fig. 6. The output stage is comprised of an integrated H-bridge stack and an output transformer. The H-bridge stack is clocked at 50 kHz. Note that the DC capacitor bus is shared with the circuits in Fig. 4.

Fig. 7. The prototype IC layout with dimensions of 7.08mm X 6.28mm. The multilevel converter is on the left (yellow). The H-bridge stack is on the right (green).

a Xilinx Spartan-3 FPGA. These off-chip functions can be readily integrated on a subsequent design turn, and require very small die area. Table I shows a full list of required external components (not including the pair of multilevel converter chips).

Fig. 8. An LDMOS power switch and its gate driving channel. Each channel consists of a floating channel supply, a level shifter, and a driver (inverter). The channel supply bootstraps off a flying capacitor and generates the VDD<sub>CH</sub> voltage at 5 V above VSS<sub>CH</sub>.

Fig. 9. Board and lab setup. The power board (lower left of the LEDs) contains two ICs, one for the PFC rectifier and one for the ripple-cancellation module. The FPGA board (left) attaches to the control board (top center). All of the control logic can be integrated in CMOS on the IC.

#### B. Data and Results

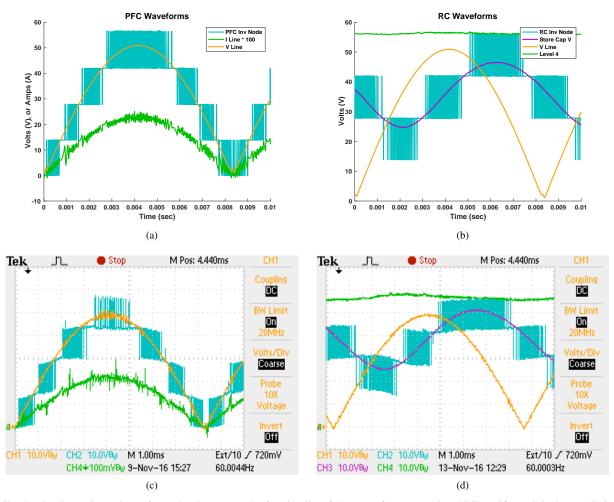

The waveforms in Fig. 10 demonstrate functionality. The PLECS simulation waveforms shown in Figs. 10a and 10b can be compared to the experimental scope waveforms, shown in Figs. 10c and 10d. Figs. 10a and 10c show that the powerfactor correction (PFC) rectifier can limit harmonics on line current (green) and ensure that it is in phase with the line voltage (yellow). The PFC inverter node (blue) of the PFC is shown to utilize all four levels. Figs. 10b and 10d show that the ripple-cancellation module can cancel AC ripple from the DC capacitor bus. Swinging the storage capacitor voltage (purple) allows the DC voltage at level 4 (green) to be almost entirely devoid of ripple.

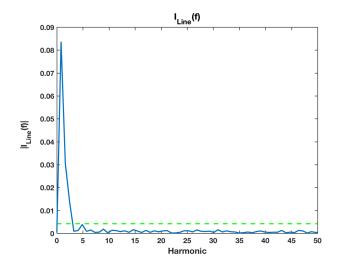

Fig. 11 shows an FFT of the line current input. Standards such as IEC 61000-3-2 (US) and EN 61000-3-2 (Europe) specify the acceptable limitations on specific line-current harmon-

Fig. 10. Simulated and experimental waveforms that demonstrate the functionality of the power-factor correction (PFC) rectifier and ripple-cancellation module. (a) Simulated PFC waveforms with the line voltage (yellow), line current (green), and the PFC rectifier inverter node of Fig. 4a (blue). The line current is scaled by 100 for visibility. (b) Simulated ripple-cancellation module waveforms. Waveforms include the line voltage (yellow), the voltage at level 4 of the DC capacitor bus (green), the voltage across the storage capacitor (purple), and the ripple-cancellation module inverter node from Fig. 4b (blue). (c) Experimental PFC rectifier waveforms from oscilloscope; waveforms correspond to Fig. 10a. The line current (green) is measured as the voltage across a 1 ohm current sense resistor, and the amperage is directly equal to the measured voltage. Horizontal divisions are 1 ms. Vertical divisions are 10 V for the line voltage (yellow) and PFC rectifier inverter node (blue), and are 100 mV for the line current (green). (d) Experimental ripple-cancellation module waveforms; waveforms correspond to Fig. 10b. Horizontal divisions are 1 ms and vertical divisions are all 10 V.

ics [60]. For lighting applications, these standards specify that the fifth harmonic must be less than 10% of the fundamental. In this work, the fifth harmonic is 4.6% of the fundamental. Higher harmonics are required to be less than 3% of the fundamental, and these specifications are also met.

The test part did not function at full rated voltage, but was testable to approximately half of rated voltage. This was due to an unfixable process error with the metal finger capacitors in the channel supply generator (Fig. 8). High voltage swings would cause VDD<sub>CH</sub> to latch below VSS<sub>CH</sub>. The leakage current due to this defect would drain the flying bootstrap capacitor and lead to catastrophic failure at higher voltage. As such, data is only reported for operation at input voltages up to 45 V<sub>RMS</sub>.

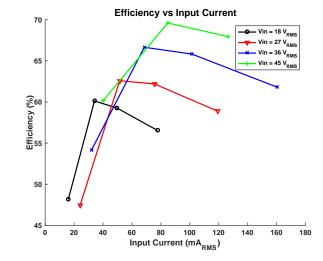

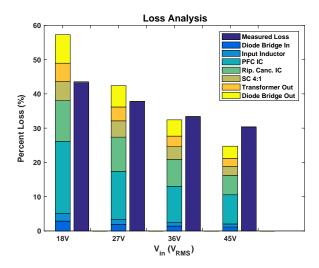

Fig. 12 shows how the efficiency varies over input voltage and current. A comparative analysis with modeled performance is given in Fig. 13 to inform understanding of the results. For the lower input voltages, the modeled loss (multicolored bar) can be compared with the actual measured loss (dark blue bar). The measured losses were well modeled, though slightly higher than predicted in modeling.

#### C. Applicability of an Integrated Multilevel LED Driver

The prototype LED driver is functional in dimming, regulating the line current harmonics, and cancelling the input ripple power without an electrolytic capacitor. However, it fails to meet the desired specifications of input voltage range and efficiency. As mentioned above, the input voltage is limited because of a process error. The ABCD process nominally supports up to 220 V on die, which would have otherwise allowed up to 120 V<sub>RMS</sub> input. Most conduction losses decrease with

TABLE I.

POWER COMPONENTS USED IN THE PROTOTYPE LED DRIVER.

| Component                   | Part Number             | Desc.            | Dim. (mm)     | Qty. |

|-----------------------------|-------------------------|------------------|---------------|------|

| PFC Inductor                | RFS1317-825KL           | 8.2 mH<br>0.25 A | 13.3x13.3x16  | 1    |

| Ripple Canc.<br>Inductor    | RFB0810-102L            | 1 mH<br>0.35 A   | 9.5x9.5x11.5  | 1    |

| Transformer<br>Toroid       | C055379A2               |                  | 18.1x18.1x7.1 | 1    |

| DC Bus Caps                 | C3216X7R2A<br>105K160AA | 1 uF<br>100 V    | 3.2x1.6x1.3   | 4    |

| Ripple Canc.<br>Storage Cap | SK052E475ZAR            | 4.7 uF<br>200 V  | 12.7x5.1x14.2 | 1-2  |

| Input Bridge                | DF02S-E3/45             | 200 V            | 8.5x6.5x3.3   | 1    |

| Output Bridge               | PD3S160-7               | 60 V             | 1.9x1.3x0.7   | 4    |

Fig. 11. FFT of the line current input  $I_{Line}$ . Line-current harmonics are all less than 5% of the fundamental (indicated by green dashed line). Data is obtained at an AC input voltage of 36 V<sub>RMS</sub> and an AC input current of 68.5 mA<sub>RMS</sub>.

the square of the voltage  $(P = V^2/R)$ , and the loss model in [61], [62] predicts the efficiency to approach 90% with a 120 V<sub>RMS</sub> input.

Despite these shortcomings, industrially developed integrated multilevel LED drivers could have the potential to greatly improve on cost and size compared to the industry standard flyback driver. First, the multilevel nature of the PFC rectifier allows the input inductor to be smaller than the inductor in a flyback driver's EMI filter. In addition, the toroidal isolation transformer at the output stage is not designed to store energy, and thus can be much smaller than a flyback transformer. In theory, the total switch die area in an integrated multilevel converter should be less than the single

Fig. 12. Efficiency versus input current. The output voltage was set at the optimal value using an electronic load. In general, the output voltage and current is determined by the total voltage drop of the series LED string.

Fig. 13. Loss versus input voltage at 80 mA input current. The lower voltages each compare a loss model (left bar) to the actual measured loss (right dark blue bar). The loss model can provide an indicative projection of how the driver would perform at higher input voltage.

switch in the flyback converter [44], [45]. However, the gate drive circuitry became unexpectedly large due to the isolation requirements in supporting floating gate drivers. Finally, it is important to reiterate that the active ripple cancellation module is crucial in obviating the electrolytic capacitor and increasing the driver's life span.

Integrated multilevel circuits have many potential benefits, and further research in the area is recommended. The authors suggest two main ways to improve this work, and a more detailed discussion is presented in [62]. First, a capacitorclamped multilevel topology should be used instead of the generalized multilevel topology. The capacitor-clamped topology has fewer switches, and the power density demonstrated in [38]–[40] suggests the potential for a die area reduction (although larger flying capacitors would be required). In addition, this topology alleviates many of the robustness issues present in the generalized topology that arise because of the floating gate drivers in columns 2, 3, and 4. Second, the authors recommend substituting every other NMOS power switch for an equivalent PMOS. PMOS switches, in conjunction with a capacitor-clamped topology, have the potential to eliminate the need for floating gate drivers altogether. Fixed gate drivers are far more robust and require less die area.

#### VII. CONCLUSION

This paper documents the design, fabrication, and testing of an IC LED driver based on a multilevel topology. The multilevel power-factor correction rectifier converts AC to DC, cancels line-current harmonics, and controls the input power. The multilevel ripple-cancellation module swings the voltage on a storage capacitor in order to cancel ripple from the DC capacitor bus. Both modules are controlled via sigma-delta modulation.

While multilevel converters have proven to be practical for high voltage electronics, this work demonstrates their potential to be practical in the IC space. The multilevel topology was shown to be particularly useful for expanding the capabilities of any IC process that has devices with a relatively low drainsource breakdown voltage ( $V_{DS,max}$ ). With careful and robust design, integrated multilevel converters show great promise for lighting and household electronics.

#### ACKNOWLEDGMENT

The authors would like to thank Texas Instruments for their technical support. Financial support was provided by the DOE under the ARPA-E ADEPT program, contract Metacapacitors DE-AR0000114.

#### REFERENCES

- C. Branas, F. J. Azcondo, and J. M. Alonso, "Solid-state lighting: A system review," *IEEE Industrial Electronics Magazine*, vol. 7, pp. 6–14, Dec 2013.

- [2] A. Wilkins, J. Veitch, and B. Lehman, "LED lighting flicker and potential health concerns: IEEE standard PAR1789 update," in 2010 IEEE Energy Conversion Congress and Exposition, pp. 171–178, Sept 2010.

- [3] B. Lehman, A. Wilkins, S. Berman, M. Poplawski, and N. J. Miller, "Proposing measures of flicker in the low frequencies for lighting applications," in *Energy Conversion Congress and Exposition (ECCE)*, 2011 IEEE, pp. 2865–2872, IEEE, 2011.

- [4] Y. Hu and M. M. Jovanovic, "A novel led driver with adaptive drive voltage," in *Applied Power Electronics Conference and Exposition*, 2008. APEC 2008. Twenty-Third Annual IEEE, pp. 565–571, IEEE, 2008.

- [5] S. Cha, D. Park, Y. Lee, C. Lee, J. Choi, J. Lee, and H. Lee, "Ac/dc converter free led driver for lightings," in *Consumer Electronics (ICCE)*, 2012 IEEE International Conference on, pp. 706–708, IEEE, 2012.

- [6] H. Van der Broeck, G. Sauerlander, and M. Wendt, "Power driver topologies and control schemes for leds," in *Applied Power Electronics Conference, APEC 2007-Twenty Second Annual IEEE*, pp. 1319–1325, IEEE, 2007.

- [7] J. T. Hwang, K. Cho, D. Kim, M. Jung, G. Cho, and S. Yang, "A simple led lamp driver ic with intelligent power-factor correction," in *Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*, 2011 IEEE International, pp. 236–238, IEEE, 2011.

- [8] X. Xu and X. Wu, "High dimming ratio led driver with fast transient boost converter," in *Power Electronics Specialists Conference*, 2008. *PESC 2008. IEEE*, pp. 4192–4195, IEEE, 2008.

- [9] R.-L. Lin, Y.-C. Chang, and C.-C. Lee, "Optimal design of led array for single-loop ccm buck–boost led driver," *IEEE Transactions on Industry Applications*, vol. 49, no. 2, pp. 761–768, 2013.

- [10] J. M. Alonso, J. Viña, D. G. Vaquero, G. Martínez, and R. Osorio, "Analysis and design of the integrated double buck-boost converter as a high-power-factor driver for power-led lamps," *IEEE Transactions on Industrial Electronics*, vol. 59, no. 4, pp. 1689–1697, 2012.

- [11] J. T. Hwang, M. S. Jung, D. H. Kim, J. H. Lee, M. H. Jung, and J. H. Shin, "Off-the-line primary side regulation led lamp driver with singlestage pfc and triac dimming using led forward voltage and duty variation tracking control," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 12, pp. 3081–3094, 2012.

- [12] Y. Hu, L. Huber, and M. M. Jovanovic, "Single-stage flyback powerfactor-correction front-end for hb led application," in *Industry Applications Society Annual Meeting*, 2009. IAS 2009. IEEE, pp. 1–8, IEEE, 2009.

- [13] M. Rico-Secades, A. Calleja, J. Cardesin, J. Ribas, E. Corominas, J. Alonso, and J. Garcia, "Driver for high efficiency led based on flyback stage with current mode control for emergency lighting system," in *Industry Applications Conference, 2004. 39th IAS Annual Meeting. Conference Record of the 2004 IEEE*, vol. 3, pp. 1655–1659, IEEE, 2004.

- [14] X. Xie, J. Wang, C. Zhao, Q. Lu, and S. Liu, "A novel output current estimation and regulation circuit for primary side controlled high power factor single-stage flyback led driver," *IEEE Transactions on Power Electronics*, vol. 27, no. 11, pp. 4602–4612, 2012.

- [15] Y. Hu, L. Huber, and M. M. Jovanović, "Single-stage, universal-input ac/dc led driver with current-controlled variable pfc boost inductor," *IEEE Transactions on power Electronics*, vol. 27, no. 3, pp. 1579–1588, 2012.

- [16] A. Prodic and M. Peretz, "Merged-stage high efficiency high power factor hb-led driver without electrolytic capacitor," May 15 2013. US Patent App. 13/894,725.

- [17] C. Le, M. Kline, D. L. Gerber, S. R. Sanders, and P. R. Kinget, "A stackable switched-capacitor DC/DC converter IC for LED drivers with 90% efficiency," in *Proceedings of the IEEE 2013 Custom Integrated Circuits Conference*, pp. 1–4, Sept 2013.

- [18] M. Kline, I. Izyumin, B. Boser, and S. Sanders, "A transformerless galvanically isolated switched capacitor led driver," in *Applied Power Electronics Conference and Exposition (APEC), 2012 Twenty-Seventh Annual IEEE*, pp. 2357–2360, IEEE, 2012.

- [19] B. Andreycak, "Zero voltage switching resonant power conversion," in UNITRODE Power Supply Design Seminar SEM-700, Citeseer, 1990.

- [20] G. Hua and F. C. Lee, "Soft-switching techniques in pwm converters," *IEEE Transactions on Industrial Electronics*, vol. 42, no. 6, pp. 595–603, 1995.

- [21] R. Redl, N. O. Sokal, and L. Balogh, "A novel soft-switching full-bridge dc/dc converter: Analysis, design considerations, and experimental results at 1.5 kw, 100 khz," *IEEE Transactions on Power Electronics*, vol. 6, no. 3, pp. 408–418, 1991.

- [22] X. Wu, Z. Wang, and J. Zhang, "Design considerations for dual-output quasi-resonant flyback led driver with current-sharing transformer," *IEEE Transactions on Power Electronics*, vol. 28, no. 10, pp. 4820– 4830, 2013.

- [23] D. Shmilovitz, A. Abramovitz, and I. Reichman, "Quasi-resonant led driver with capacitive isolation and high pf," *IEEE Journal of Emerging* and Selected Topics in Power Electronics, vol. 3, no. 3, pp. 633–641, 2015.

- [24] B. Lehman, "Recommended practices of modulating current in high brightness leds for mitigating health risk to viewers," in *Flicker and IEEE PAR1789, IEEE ECCE paper*, 2010.

- [25] P. S. Almeida, D. Camponogara, M. Dalla Costa, H. Braga, and J. M. Alonso, "Matching led and driver life spans: a review of different techniques," *IEEE Industrial Electronics Magazine*, vol. 9, no. 2, pp. 36–47, 2015.

- [26] L. Gu, X. Ruan, M. Xu, and K. Yao, "Means of eliminating electrolytic capacitor in ac/dc power supplies for led lightings," *IEEE Transactions* on *Power Electronics*, vol. 24, no. 5, pp. 1399–1408, 2009.

- [27] S. Wang, X. Ruan, K. Yao, S.-C. Tan, Y. Yang, and Z. Ye, "A flickerfree electrolytic capacitor-less AC–DC LED driver," *IEEE Transactions* on *Power Electronics*, vol. 27, no. 11, pp. 4540–4548, 2012.

- [28] W. Chen and S. R. Hui, "Elimination of an electrolytic capacitor in ac/dc light-emitting diode (led) driver with high input power factor and constant output current," *IEEE Transactions on Power Electronics*, vol. 27, no. 3, pp. 1598–1607, 2012.

- [29] J. M. Alonso, A. J. Calleja, D. Gacio, J. Cardesín, E. Lopez, M. A. Dalla Costa, M. F. Da Silva, and R. N. Do Prado, "High-power-factor light-emitting diode lamp power supply without electrolytic capacitors for high-pressure-sodium lamp retrofit applications," *IET Power Electronics*, vol. 6, no. 8, pp. 1502–1515, 2013.

- [30] J. M. Alonso, D. Gacio, A. J. Calleja, F. Sichirollo, M. F. da Silva, M. A. Dalla Costa, and R. N. do Prado, "Reducing storage capacitance in off-line led power supplies by using integrated converters," in *Industry Applications Society Annual Meeting (IAS), 2012 IEEE*, pp. 1–8, IEEE, 2012.

- [31] P. S. Almeida, M. A. Dalla Costa, J. Alonso, and H. A. C. Braga, "Application of series resonant converters to reduce ripple transmission to led arrays in offline drivers," *Electronics Letters*, vol. 49, no. 6, pp. 414–415, 2013.

- [32] M. Chen, Y. Ni, C. Serrano, B. Montgomery, D. Perreault, and K. Afridi, "An electrolytic-free offline led driver with a ceramic-capacitor-based compact ssc energy buffer," in *Energy Conversion Congress and Exposition (ECCE)*, 2014 IEEE, pp. 2713–2718, IEEE, 2014.

- [33] Y. Tang, M. Chen, and L. Ran, "A compact mmc submodule structure with reduced capacitor size using the stacked switched capacitor architecture," *IEEE Transactions on Power Electronics*, vol. 31, no. 10, pp. 6920–6936, 2016.

- [34] D. L. Gerber, An Integrated Multilevel Converter with Sigma Delta Control for LED Lighting. PhD thesis, University of California Berkeley, 2017.

- [35] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Transactions on Industrial Electronics*, vol. 49, pp. 724–738, Aug 2002.

- [36] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Transactions on Industry Applications*, vol. IA-17, pp. 518–523, Sept 1981.

- [37] T. A. Meynard and H. Foch, "Multi-level conversion: high voltage choppers and voltage-source inverters," in *Power Electronics Specialists Conference, 1992. PESC '92 Record., 23rd Annual IEEE*, pp. 397–403 vol.1, Jun 1992.

- [38] T. Modeer, C. Barth, Y. Lei, and R. Pilawa-Podgurski, "An analytical method for evaluating the power density of multilevel converters," in *Control and Modeling for Power Electronics (COMPEL), 2016 IEEE* 17th Workshop on, pp. 1–5, IEEE, 2016.

- [39] C. B. Barth, T. Foulkes, W. H. Chung, T. Modeer, P. Assem, Y. Lei, and R. C. Pilawa-Podgurski, "Design and control of a gan-based, 13-level, flying capacitor multilevel inverter," in *Control and Modeling for Power Electronics (COMPEL), 2016 IEEE 17th Workshop on*, pp. 1–6, IEEE, 2016.

- [40] Z. Ye and R. C. Pilawa-Podgurski, "A power supply circuit for gate driver of gan-based flying capacitor multi-level converters," in *Wide Bandgap Power Devices and Applications (WiPDA)*, 2016 IEEE 4th Workshop on, pp. 53–58, IEEE, 2016.

- [41] P. W. Hammond, "A new approach to enhance power quality for medium voltage AC drives," *IEEE Transactions on Industry Applications*, vol. 33, pp. 202–208, Jan 1997.

- [42] J. W. Kolar, U. Drofenik, and F. C. Zach, "Current handling capability of the neutral point of a three-phase/switch/level boost-type PWM (VIENNA) rectifier," in *Power Electronics Specialists Conference*, 1996. *PESC '96 Record., 27th Annual IEEE*, vol. 2, pp. 1329–1336 vol.2, Jun 1996.

- [43] M. Chen, K. K. Afridi, and D. J. Perreault, "A multilevel energy buffer and voltage modulator for grid-interfaced microinverters," *IEEE Transactions on Power Electronics*, vol. 30, no. 3, pp. 1203–1219, 2015.

- [44] M. D. Seeman and S. R. Sanders, "Analysis and optimization of switched-capacitor DC-DC converters," *IEEE Transactions on Power Electronics*, vol. 23, pp. 841–851, March 2008.

- [45] S. R. Sanders, E. Alon, H. P. Le, M. D. Seeman, M. John, and V. W. Ng, "The road to fully integrated DC-DC conversion via the switchedcapacitor approach," *IEEE Transactions on Power Electronics*, vol. 28, pp. 4146–4155, Sept 2013.

- [46] F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing," *IEEE Transactions on Industry Applications*, vol. 37, pp. 611–618, Mar 2001.

- [47] J. Rodriguez, L. Moran, P. Correa, and C. Silva, "A vector control technique for medium-voltage multilevel inverters," *IEEE Transactions* on *Industrial Electronics*, vol. 49, pp. 882–888, Aug 2002.

- [48] L. Li, D. Czarkowski, Y. Liu, and P. Pillay, "Multilevel selective harmonic elimination PWM technique in series-connected voltage inverters," in *Industry Applications Conference*, 1998. Thirty-Third IAS Annual Meeting. The 1998 IEEE, vol. 2, pp. 1454–1461 vol.2, Oct 1998.

- [49] C. S. Diaz, F. I. Escobar, G. C. Diotaiuti, and V. M. G. Arguis, "Adaptive sigma-delta modulator applied to control a five level multilevel inverter," in *Devices, Circuits and Systems, 2004. Proceedings of the Fifth IEEE International Caracas Conference on*, vol. 1, pp. 219–224, Nov 2004.

- [50] H. Inose and Y. Yasuda, "A unity bit coding method by negative feedback," *Proceedings of the IEEE*, vol. 51, pp. 1524–1535, Nov 1963.

- [51] D. A. Johns and K. Martin, Analog integrated circuit design. John Wiley & Sons, 2008.

- [52] S. R. Norsworthy, R. Schreier, and G. C. Temes, *Delta-sigma data converters: theory, design, and simulation.* Wiley-IEEE Press, 1996.

- [53] S. Park, Principles of Sigma-Delta Modulation for Anlog-To-Digital Converters. Motorola, 1990.

- [54] W. Kester, "Adc architectures iii: Sigma-delta adc basics," Analog Devices, MT022, 2008.

- [55] I. Colak, E. Kabalci, and R. Bayindir, "Review of multilevel voltage source inverter topologies and control schemes," *Energy Conversion and Management*, vol. 52, no. 2, pp. 1114 – 1128, 2011.

- [56] M. Manjrekar and G. Venkataramanan, "Advanced topologies and modulation strategies for multilevel inverters," in *Power Electronics Specialists Conference*, 1996. PESC '96 Record., 27th Annual IEEE, vol. 2, pp. 1013–1018 vol.2, Jun 1996.

- [57] J. Liao and M. Ferdowsi, "An improved cascaded H-bridge multilevel inverter controlled by an unbalanced voltage level sigma-delta modulator," in 2008 IEEE Vehicle Power and Propulsion Conference, pp. 1–5, Sept 2008.

- [58] G. Ceglia, V. Guzman, C. Sanchez, F. Ibanez, J. Walter, and M. I. Gimenez, "A new simplified multilevel inverter topology for DC-AC conversion," *IEEE Transactions on Power Electronics*, vol. 21, pp. 1311–1319, Sept 2006.

- [59] M. D. Seeman, A Design Methodology for Switched-Capacitor DC-DC Converters. PhD thesis, EECS Department, University of California, Berkeley, May 2009.

- [60] M. N. Z. Abidin, "IEC 61000-3-2 harmonics standards overview," Schaffner EMC Inc., Edsion, NJ, USA, 2006.

- [61] D. L. Gerber, M. Kline, S. R. Sanders, C. Le, and P. R. Kinget, "An integrated multilevel converter with sigma delta control for led lighting," in *Applied Power Electronics Conference and Exposition (APEC)*, 2017 *IEEE*, pp. 2398–2403, IEEE, 2017.

- [62] D. Gerber, An Integrated Multilevel Converter with Sigma Delta Control for LED Lighting. PhD thesis, EECS Department, University of California, Berkeley, May 2017.

**Peter R. Kinget** received an engineering degree in electrical and mechanical engineering and the Ph.D. in electrical engineering from the Katholieke Universiteit Leuven, Belgium. He has worked in industrial research and development at Bell Laboratories, Broadcom, Celight and Multilink before joining the faculty of the Department of Electrical Engineering, Columbia University, NY in 2002, where he currently is the Department Chair and Bernard J. Lechner Professor in Electrical Engineering. He is also a consulting expert on patent litigation and a

technical consultant to industry. His research interests are in analog, RF and power integrated circuits and the applications they enable in communications, sensing, and power management.

Peter is widely published and received several awards. He is a Fellow of the IEEE. He has been a "Distinguished Lecturer" for the IEEE Solid-State Circuits Society (SSCS), and an Associate Editor of the IEEE Journal of Solid State Circuits (2003-2007) and the IEEE Transactions on Circuits and Systems II (2008-2009). He has served on the program committees of many of the major solid-state circuits conferences and has been an elected member of the IEEE SSCS Adcom (2011-2013 & 2014-2016).

**Daniel L. Gerber** received the B.S. and M.S. degrees in electrical engineering from MIT, Cambridge, MA, USA, and the Ph.D degree in electrical engineering at UC Berkeley, Berkeley, CA, USA, in 2010, 2011, and 2017, respectively. His doctoral research was in circuits and controls for LED drivers and other power electronics. Daniel is currently working as a postdoctoral fellow at Lawrence Berkeley Labs, Berkeley, CA, USA. His current research interests are in electronics for building efficiency; specifically in modeling and experimental validation

of DC power distribution for zero net energy buildings.

Chengrui Le received the M.S. degree in electrical engineering from Columbia University, New York, NY, USA, and the B.S. degree from the Department of Microelectronics and Nano electronics, Tsinghua University, Haidian, Beijing, China. He is currently working toward the Ph.D. degree at Columbia University. His research interests include analog IC design and he has experience inorganic circuit design/fabrication. He worked on the circuit development, integration, and testing of the Metacapacitor LED driver.

Seth R. Sanders received the S.B. degree in electrical engineering and physics and the S.M. and Ph.D. degrees in electrical engineering from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1981, 1985, and 1989, respectively. He was a Design Engineer at the Honeywell Test Instruments Division, Denver, CO, USA. Since 1989, he has been on the Faculty of the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, USA, where he is currently a Professor. His research interests include

high-frequency power conversion circuits and components, in design and control of electric machine systems, and in nonlinear circuit and system theory as related to the power electronics field.

Mitchell Kline received the B.S. degree in computer engineering from Texas A&M University, College Station, TX, USA, in 2008, and the M.S. degree in electrical engineering on the topic of capacitive power transfer from University of California at Berkeley in 2010. He is a Post-Doctoral Researcher with the Bernhard Bosers Group, Berkeley Sensor and Actuator Center, Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA, USA. His research interests include low power high precision integrated

circuit design, MEMS, and inertial sensors.