# UCLA UCLA Electronic Theses and Dissertations

### Title

Schottky-Diode-Based Wake-Up Receiver and Power Management Systems for IoT Applications

**Permalink** https://escholarship.org/uc/item/7wv541cb

Author Elhebeary, Mahmoud

Publication Date 2020

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Schottky-Diode-Based Wake-Up Receiver and Power Management Systems for IoT Applications

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Mahmoud M Rashad Ibrahim Elhebeary

2020

© Copyright by Mahmoud M Rashad Ibrahim Elhebeary 2020

### ABSTRACT OF THE DISSERTATION

Schottky-Diode-Based Wake-Up Receiver and Power Management Systems for IoT Applications

by

Mahmoud M Rashad Ibrahim Elhebeary Doctor of Philosophy in Electrical and Computer Engineering University of California, Los Angeles, 2020 Professor Chih-Kong Ken Yang, Chair

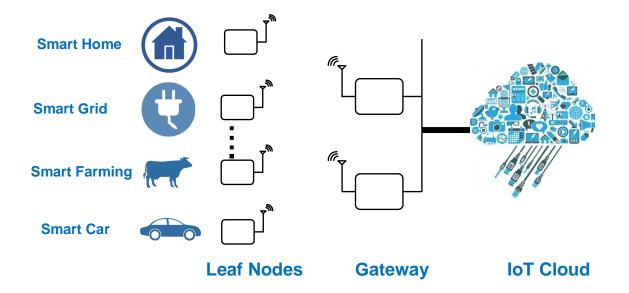

Internet of Things (IoT) has recently become a crucial technology in our daily lives that has applications ranging from managing airports' passenger flow to taking care of the elder. It aims at connecting all appliances and products to create a vast network of applications. An IoT system is composed of leaf nodes that collect data from different applications which then transmit the data to a gateway or hub and eventually for storage and processing in the cloud. Battery life is a key bottleneck for leaf nodes that are either mobile or distributed without a fixed power connection. In order to communicate with a very low power budget, wake-up receivers (WuRx) that are part of a power management unit are needed in order to extend a device's service period.

While several approaches to wake-up a leaf node is possible such as using a watchdog timer that periodically and systematically wakes up the device, this work, we target leaf nodes with high throughputs and accessed in an asynchronous manner by a centralized hub. Such a WuRx imposes specific challenges including low wake-up latency, high data rate, good sensitivity, and ultra-low power budget targeting a battery life >10 years. Existing designs do not satisfy all challenges for the WuRx system or the battery power management efficiencies at such low power. Hence, we propose a new WuRx technique with the submicrowatt power management unit that significantly bridges the gap between the required and achievable performance. New integrated circuit techniques are implemented in CMOS chip such as building Schottky diode on CMOS, a novel data-locking oscillator technique, and a digital correlation unit to identify signatures from the hub.

Existing solutions for low voltage regulation suffer from low power efficiency especially with load currents that transitions from nano-watts to milli-watts. In this dissertation, we first propose a two-stage hybrid power management unit (PMU) that employs a highlyefficient novel ON-OFF LDO as the second stage and uses a switched-capacitor dc-dc divider as the first stage. This design is then enhanced to operate across a wide range of loads from sub-microwatt to 100's of microwatts by using selectable sizing of its switches to improve efficiency to >95% across the target range of load current. The output voltage that is divided from the first stage is then regulated using the proposed ON-OFF LDO with a dropout voltage of <30mV. The hybrid architecture regulates battery voltage to 0.4V and achieves a power efficiency of >85% for the wake-up receiver as the load.

Lastly, when the main transceiver receives the wake-up signal, it requires a short time for settling so that it communicates the necessary information to the gateway quickly. The main transceivers consume in order of 10s of milli-Watts which is regulated through an LDO. Existing solutions could not provide short settling with small overshoot for a fast start-up. We propose a novel LDO that uses a new Coarsely-Quantized Class-D control that enables wide loop bandwidth using a multi-level and pulse-width modulated (MLPWM) gate control of the output device. The flipped voltage follower (FVF) output stage is adopted with a feedforward derivative path to limit overshoot/undershoot. The proposed LDO settles within 280ns when the load is stepped in 7ns from 0 to 300mA with no observed overshoot or undershoot. The dissertation of Mahmoud M Rashad Ibrahim Elhebeary is approved.

Gregory Pottie

Danijela Cabric

Sudhakar Pamarti

Chih-Kong Ken Yang, Committee Chair

University of California, Los Angeles

2020

To my family

### TABLE OF CONTENTS

| 1 | Intr              | oducti                                                                | on                                  | 1                                      |

|---|-------------------|-----------------------------------------------------------------------|-------------------------------------|----------------------------------------|

|   | 1.1               | Motiva                                                                | ation                               | 2                                      |

|   | 1.2               | Thesis                                                                | Organization                        | 7                                      |

| 2 | Bac               | kgrour                                                                | nd                                  | 9                                      |

|   | 2.1               | Wake-                                                                 | up Receiver                         | 10                                     |

|   |                   | 2.1.1                                                                 | Low-power radios                    | 10                                     |

|   |                   | 2.1.2                                                                 | Always-on wake-up receiver          | 14                                     |

|   | 2.2               | Power                                                                 | Management Unit for IoT Application | 16                                     |

|   |                   | 2.2.1                                                                 | Wide range hybrid DC-DC converter   | 16                                     |

|   |                   | 2.2.2                                                                 | Coarsely Quantized Class-D LDO      | 18                                     |

|   | 2.3               | Summ                                                                  | ary                                 | 21                                     |

|   |                   |                                                                       |                                     |                                        |

| 3 | Wal               | ke-Up                                                                 | Receiver for IoT Applications       | 22                                     |

| 3 | <b>Wal</b><br>3.1 |                                                                       | Receiver for IoT Applications       | <b>22</b><br>23                        |

| 3 |                   |                                                                       |                                     |                                        |

| 3 |                   | Wake-                                                                 | up Receiver Model                   | 23<br>24                               |

| 3 |                   | Wake-<br>3.1.1                                                        | up Receiver Model                   | 23<br>24                               |

| 3 |                   | Wake-<br>3.1.1<br>3.1.2                                               | up Receiver Model                   | 23<br>24<br>27                         |

| 3 |                   | Wake-<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                             | up Receiver Model                   | 23<br>24<br>27<br>29                   |

| 3 | 3.1               | Wake-<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                             | up Receiver Model                   | 23<br>24<br>27<br>29<br>30             |

| 3 | 3.1               | Wake-<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>System                   | up Receiver Model                   | 23<br>24<br>27<br>29<br>30<br>33       |

| 3 | 3.1               | Wake-<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>System<br>3.2.1<br>3.2.2 | up Receiver Model                   | 23<br>24<br>27<br>29<br>30<br>33<br>35 |

|          |                | 3.3.2   | Variable gain amplifier with variable threshold voltage . |      | <br>•          | • | • | 40  |

|----------|----------------|---------|-----------------------------------------------------------|------|----------------|---|---|-----|

|          |                | 3.3.3   | Data-locked startable oscillator                          |      | <br>•          | • | • | 43  |

|          |                | 3.3.4   | Digital correlation unit                                  |      | <br>•          |   | • | 44  |

|          | 3.4            | Summa   | ary                                                       |      | <br>•          | • | • | 46  |

| 4        | Pow            | ver Ma  | nagement for IoT Applications                             |      | <br>           |   |   | 47  |

|          | 4.1            | Hybrid  | l-Converter System Architecture                           |      | <br>           |   |   | 48  |

|          |                | 4.1.1   | Switched-Capacitor DC-DC Converter                        |      | <br>. <b>.</b> |   |   | 48  |

|          |                | 4.1.2   | ON-OFF LDO                                                |      | <br>•          |   |   | 52  |

|          |                | 4.1.3   | Ranges Switching                                          |      | <br>           |   | • | 56  |

|          | 4.2            | Hybrid  | l-Converter Implementation                                |      | <br>•          |   |   | 58  |

|          | 4.3            | Summa   | ary                                                       |      | <br>           | • | · | 63  |

| <b>5</b> | Coa            | rsely-Q | Quantized Class-D LDO                                     |      | <br>           |   |   | 65  |

|          | 5.1            | System  | n Design Considerations                                   |      | <br>           |   | • | 65  |

|          |                | 5.1.1   | Coarsely-Quantized Class-D Control with FVF Output S      | tage | <br>           |   | • | 66  |

|          |                | 5.1.2   | Feed Forward Control for Power Transistor                 |      | <br>•          | • | • | 70  |

|          |                | 5.1.3   | Stability Analysis                                        |      | <br>           |   |   | 72  |

|          | 5.2            | Coarse  | ly-Quantized Class-D Implementation                       |      | <br>           | • |   | 75  |

|          | 5.3            | Summa   | ary                                                       |      | <br>•          | • | • | 80  |

| 6        | $\mathbf{Exp}$ | erimer  | ntal Results                                              |      | <br>           |   |   | 82  |

|          | 6.1            | Measu   | rement Results of Wake-up receiver                        |      | <br>           | • | • | 82  |

|          | 6.2            | Measu   | rement Results of PMU Chip                                |      | <br>           | • | • | 92  |

|          | 6.3            | Measu   | rement Results of Class-D LDO                             |      | <br>           |   | • | 97  |

|          | 6.4            | Summa   | ary                                                       |      | <br>           |   |   | 104 |

| 7  | Conclusion and | Future Wor | k | <br> | <br> | <br> | <br>• | <br> | 105 |

|----|----------------|------------|---|------|------|------|-------|------|-----|

| Re | eferences      |            |   | <br> | <br> | <br> | <br>  | <br> | 108 |

### LIST OF FIGURES

| 1.1 | IoT nodes top-level structure                                                       | 2  |

|-----|-------------------------------------------------------------------------------------|----|

| 1.2 | Leaf nodes architecture and Thesis work focus                                       | 3  |

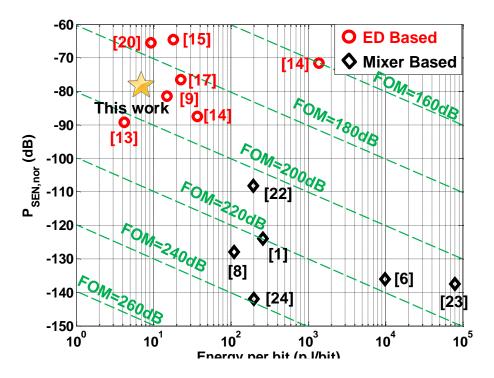

| 1.3 | Wake-up receiver normalized sensitivity versus FOM for prior publications $\ . \ .$ | 4  |

| 1.4 | Power efficiency versus load current of prior work                                  | 5  |

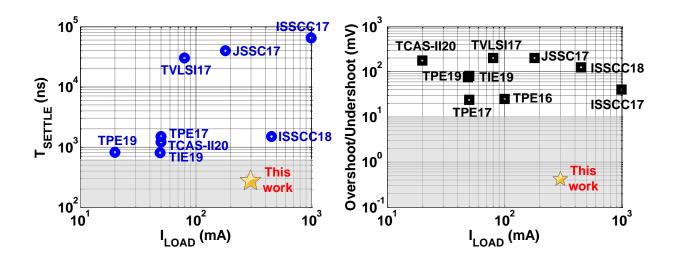

| 1.5 | Settling time and overshoot/undershoot versus load current of prior work            | 6  |

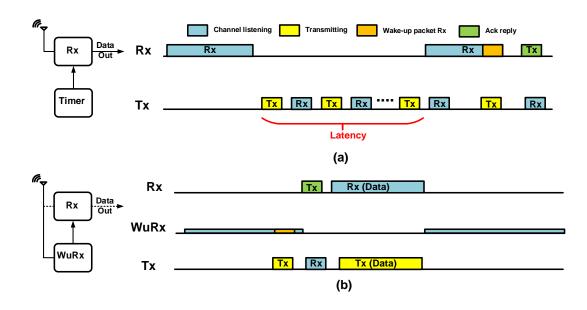

| 2.1 | (a)Periodically wake-up receiver (b)Always-on wake-up receiver                      | 11 |

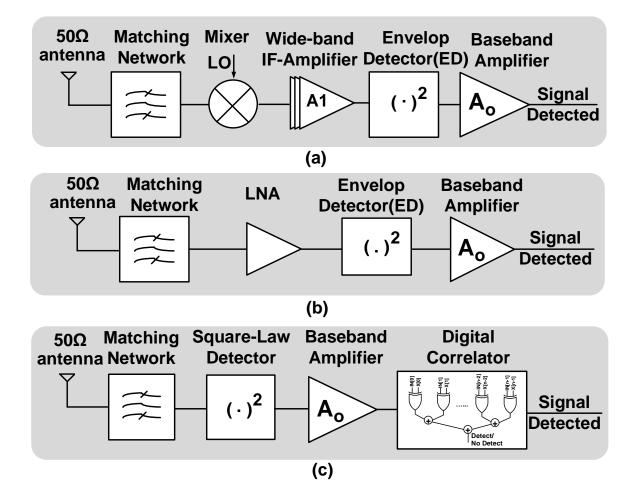

| 2.2 | (a) Conventional IF/Uncertain-IF Superhetrodyen WuRx (b) Conventional tuned         |    |

|     | RF WuRx (c) square-law detector based WuRx                                          | 15 |

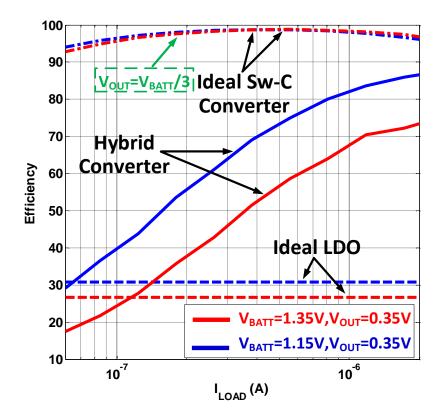

| 2.3 | Efficiency for ideal switched-C, ideal LDO and proposed hybrid converter at dif-    |    |

|     | ferent supply voltages.                                                             | 17 |

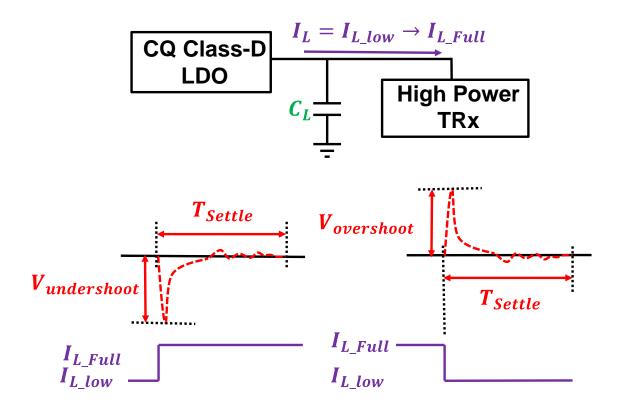

| 2.4 | Transient response for load change for leaf node radio.                             | 19 |

| 2.5 | Conventional (a) analog and (b) digital control versus, (c) proposed MLPWM          |    |

|     | control                                                                             | 21 |

| 3.1 | ROC curves of ED, MF, and Corr at $SNR=6dB$                                         | 26 |

| 3.2 | ROC curves of ED, MF, and Corr at SNR=15dB                                          | 26 |

| 3.3 | System model for noise analysis                                                     | 29 |

| 3.4 | The effect of the correlator length (L) on the WuRx performance measured using      |    |

|     | AUC at different SNRs                                                               | 30 |

| 3.5 | Probability of false alarm and detection as a function of the threshold of an 8 bit |    |

|     | correlator for different number of bits allowed to be wrong while still declaring a |    |

|     | match $l$                                                                           | 31 |

| 3.6 | Probability of false alarm and detection as a function of the threshold of an 8 bit |    |

|     | correlator for different SNRs.                                                      | 32 |

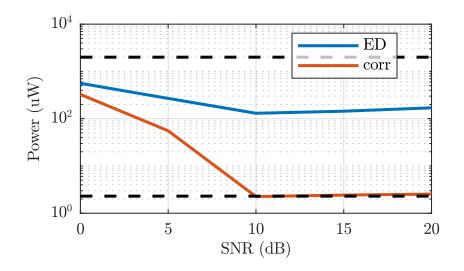

| 3.7  | The expected energy consumption of ED and Corr when parameters are optimized $\label{eq:expected}$        |    |

|------|-----------------------------------------------------------------------------------------------------------|----|

|      | as a function of SNR                                                                                      | 33 |

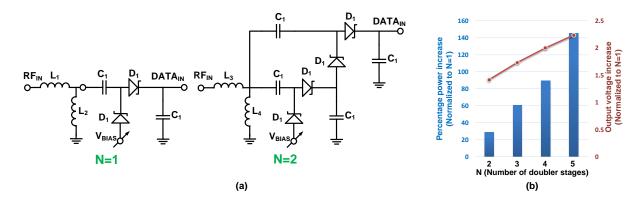

| 3.8  | Proposed wake-up receiver architecture                                                                    | 34 |

| 3.9  | (a)voltage doubler configuration for N=1 and N=2, (b) percentage increase in                              |    |

|      | power and voltage gain of having multiple double stages normalized to N=1 $$ .                            | 36 |

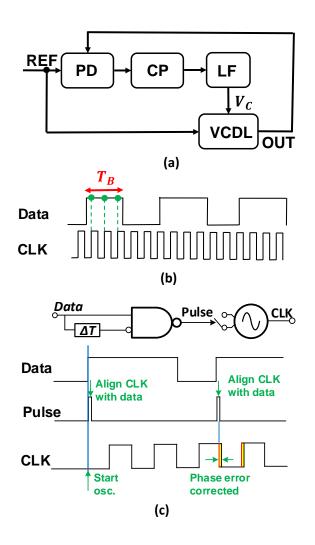

| 3.10 | $(a) DLL\ conceptual\ design,\ (b)\ oversampling\ oscillator,\ and\ (c) conceptual\ diagram$              |    |

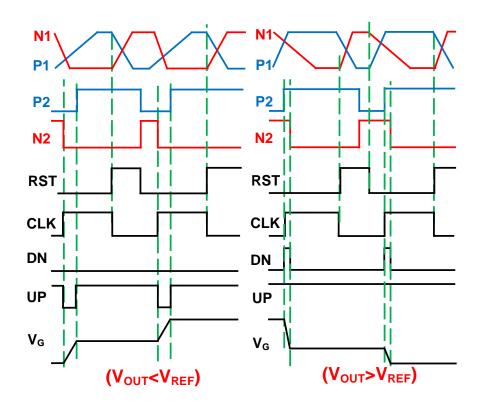

|      | for data-locked startable oscillator operation                                                            | 38 |

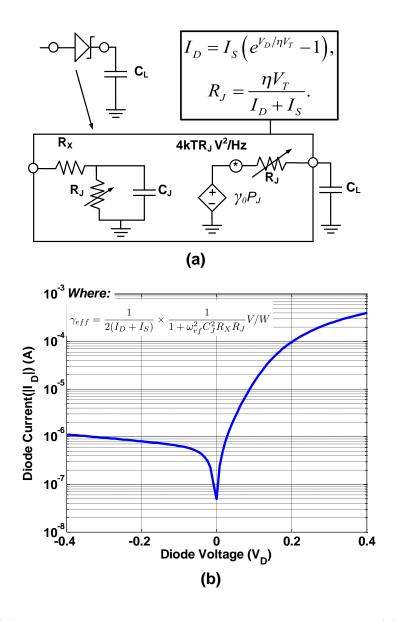

| 3.11 | (a) Schottky diode small-signal model and equations, (b) Schottky diode mea-<br>sured I-V characteristics | 40 |

| 3.12 | (a) Amplifier chain circuit implementation, (b) different threshold voltage config-                       |    |

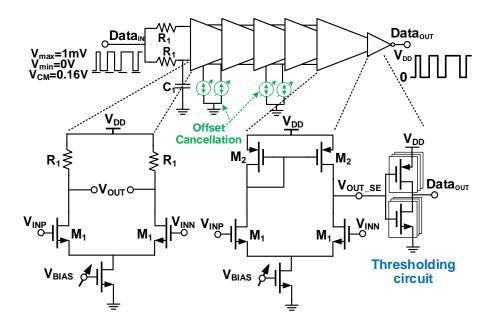

|      | uration,(c) amplifier gain configuration for different input power levels                                 | 41 |

| 3.13 | (a)Thresholding at different configurations, (b)amplifier gain configuration for                          |    |

|      | different input power levels                                                                              | 42 |

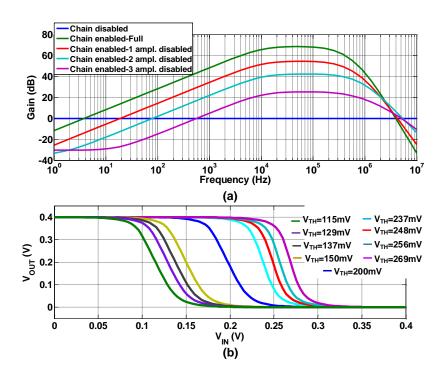

| 3.14 | (a)Relaxation oscillator architecture with data locking technique (b) pulse gener-                        |    |

|      | ator for data locking technique and SR latch with set dominant to avoid delayed                           |    |

|      | startup (c) comparator design for the oscillator (d)zero-order temperature com-                           |    |

|      | pensation using Npoly and Ppoly                                                                           | 43 |

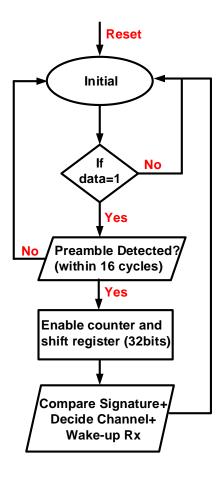

| 3.15 | Digital correlation unit flow-chart operation                                                             | 45 |

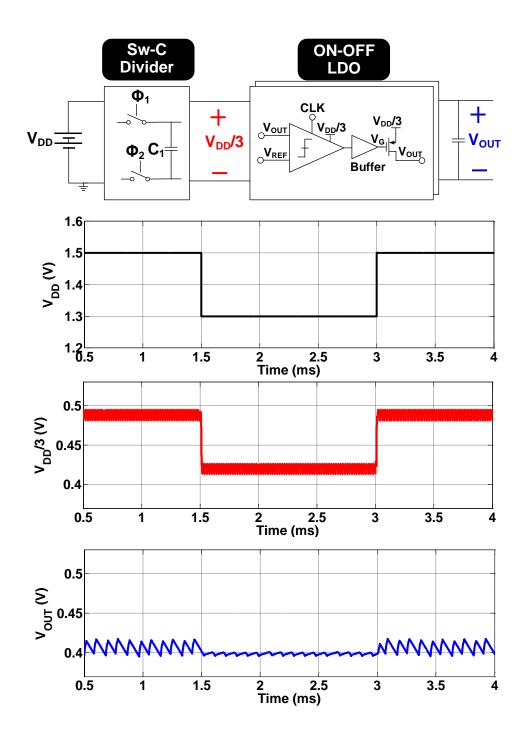

| 4.1  | Proposed hybrid converter top-level and supply changing impact on the first stage                         |    |

|      | of switched capacitor divider and the output voltage regulated at 0.4V                                    | 49 |

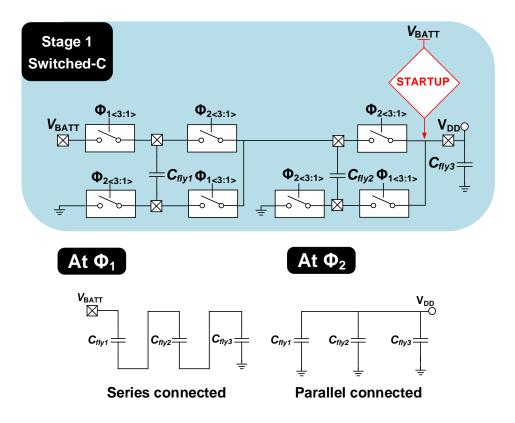

| 4.2  | Switched-capacitor divider architecture and series-parallel operation at $2 \ clock$                      |    |

|      | phases                                                                                                    | 50 |

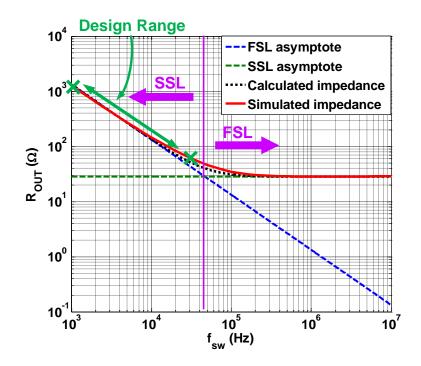

| 4.3  | Output impedance for Series-Parallel configuration versus frequency                                       | 52 |

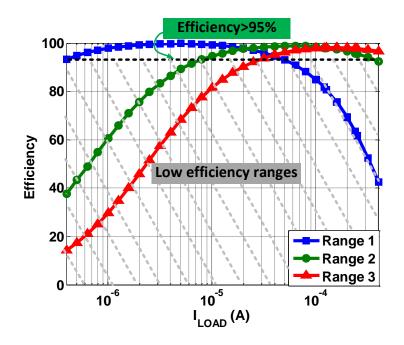

| 4.4  | Efficiency of switched capacitor divider across load currents.                                            | 53 |

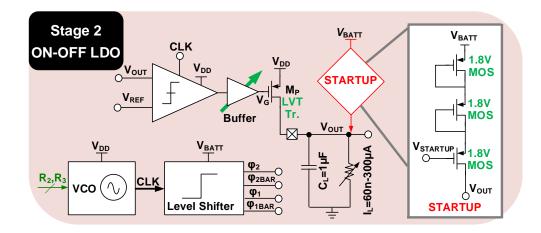

| 4.5  | Proposed ON-OFF LDO implementation with startup circuit implementation.                                   | 54 |

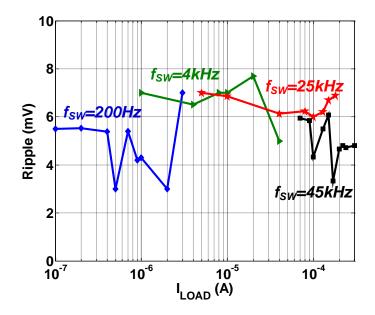

| 4.6  | Output ripple across different load currents at different ranges of operation                             | 54 |

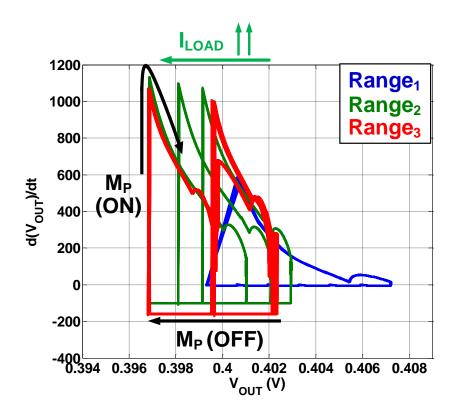

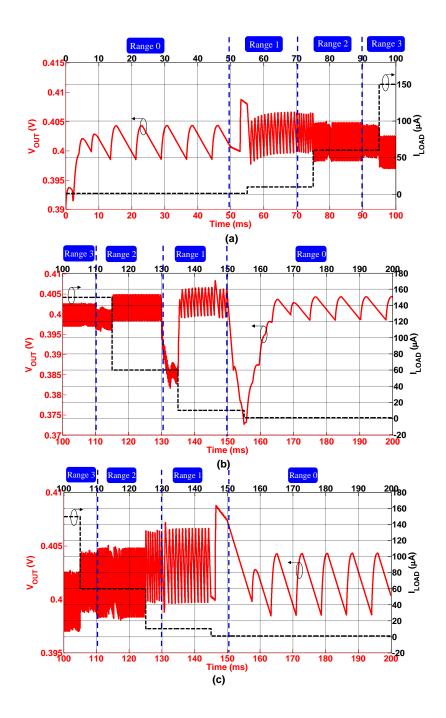

| 4.7  | Limit cycle for the ON-OFF LDO at different ranges as load changes from $10\mu$ A-<br>$60\mu$ A- $180\mu$ A | 55 |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 4.8  | (a) Ranges switching prior to load change across all ranges while load increases,                           |    |

|      | (b) range switching prior to load change across all ranges while load decreases,                            |    |

|      | and (c) ranges switching post load change across all ranges while load decreases.                           | 57 |

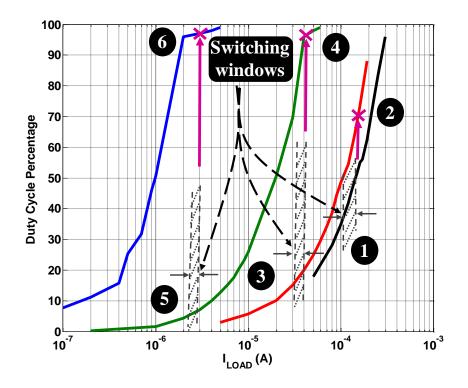

| 4.9  | Duty cycle of voltage controlling LDO power PMOS $(V_G)$ across different ranges                            |    |

|      | and switching points between different ranges.                                                              | 59 |

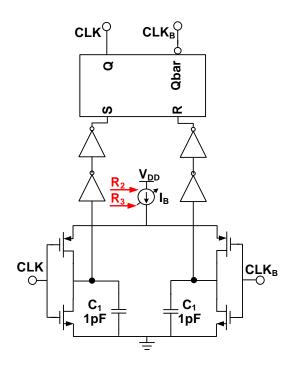

| 4.10 | Relaxation oscillator with variable frequency control                                                       | 60 |

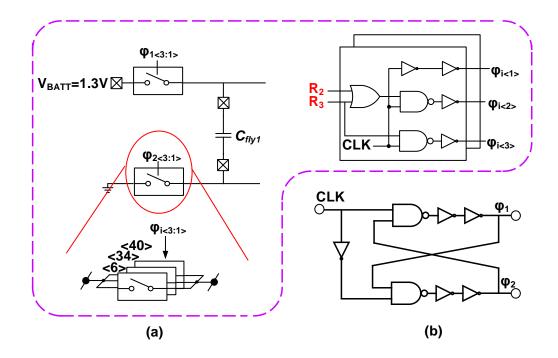

| 4.11 | (a) Variable switch size for optimizing the overall efficiency, (b) non-overlapping                         |    |

|      | clock generator.                                                                                            | 61 |

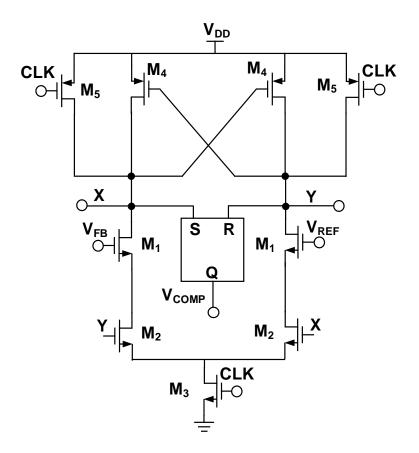

| 4.12 | Double tail latched comparator circuit implementation                                                       | 62 |

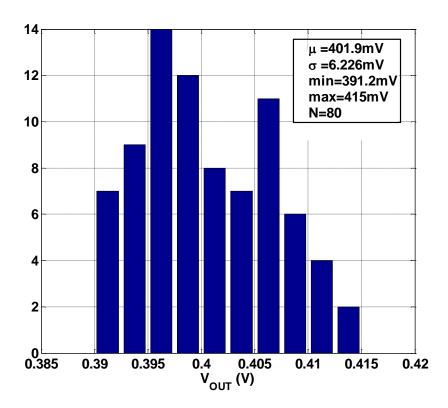

| 4.13 | Output voltage offset of the overall converter across 80 runs                                               | 63 |

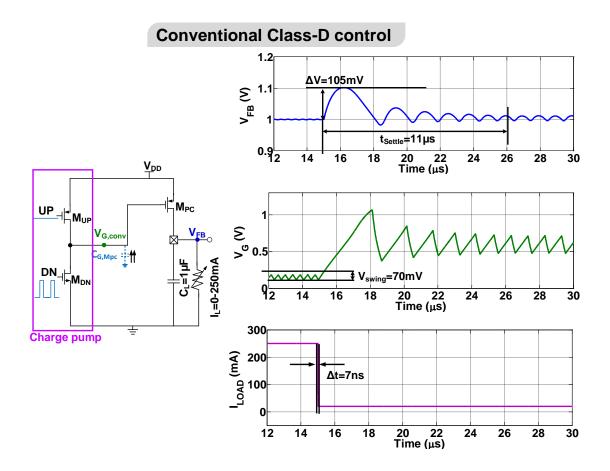

| 5.1  | Conventional class-D control charge pump and output stage and simulation wave-                              |    |

|      | forms                                                                                                       | 67 |

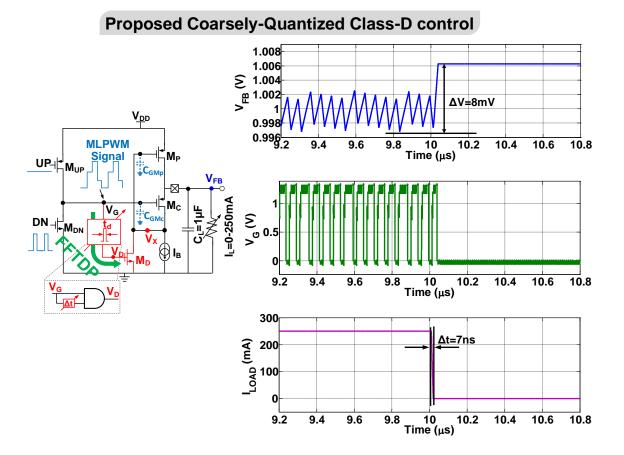

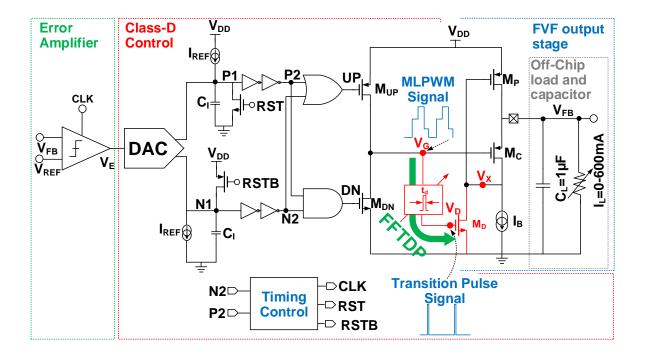

| 5.2  | Proposed Coarsely-Quantized Class-D control with FVF output stage and simu-                                 |    |

|      | lation waveform                                                                                             | 68 |

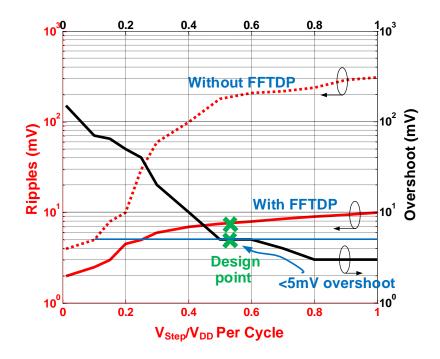

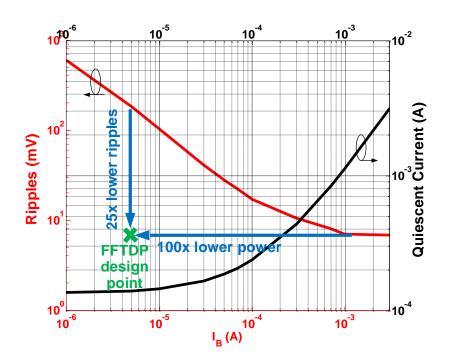

| 5.3  | Impact of $V_{Step}$ on transient behavior with and without FFTDP                                           | 69 |

| 5.4  | ${\cal I}_B$ impact on transient behavior without FFTDP and improvement due to FFTDP.                       | 71 |

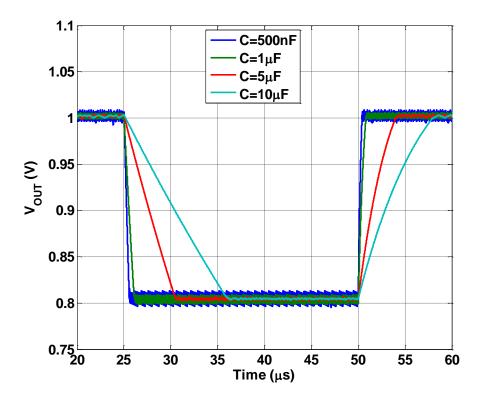

| 5.5  | Simulated line transient response at different load capacitance                                             | 72 |

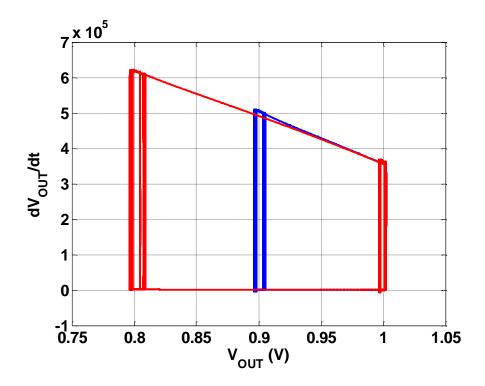

| 5.6  | Limit cycle simulation results at different reference voltage changes $\ldots$                              | 73 |

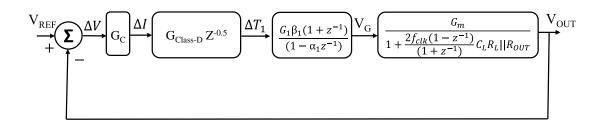

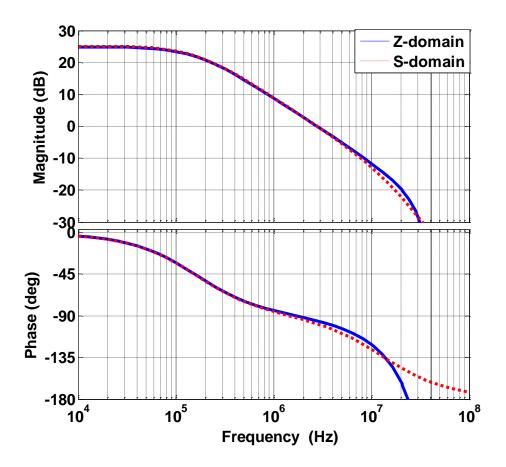

| 5.7  | Class-D FVF system modeling.                                                                                | 74 |

| 5.8  | System open-loop gain and phase margin in Z-domain and S-domain pole approx-                                |    |

|      | imation.                                                                                                    | 75 |

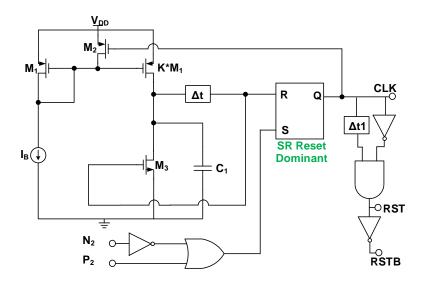

| 5.9  | System architecture for the proposed Coarsely-Quantized Class-D FVF LDO                                     | 76 |

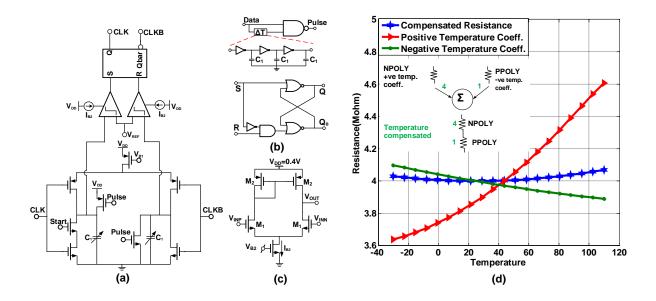

| 5.10 | Timing control circuit implementation                                                                       | 77 |

| 5.11 | Timing diagram for Coarsely-Quantized Class-D control operation.                                            | 78 |

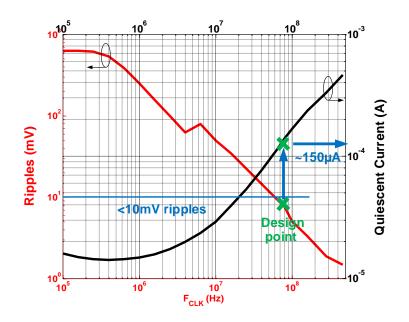

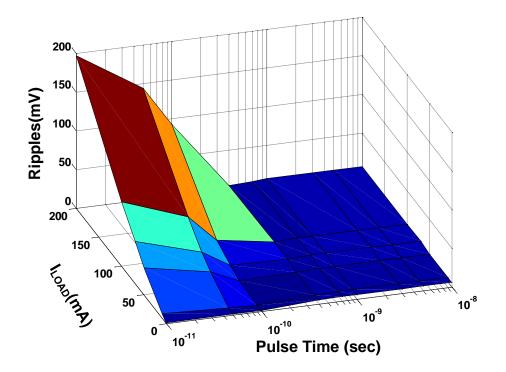

| 5.12 | Clock frequency impact on the transient behavior of ripples and quiescent current.          | 79 |

|------|---------------------------------------------------------------------------------------------|----|

| 5.13 | Pulse width variation across different loads and the output ripples results at $f_{sw}$     |    |

|      | of 83MHz                                                                                    | 80 |

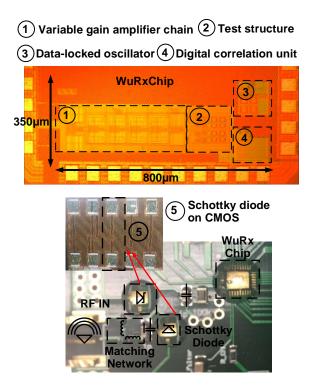

| 6.1  | WuRx chip and Schottky diode chip Micrographs and PCB for the overall system.               | 83 |

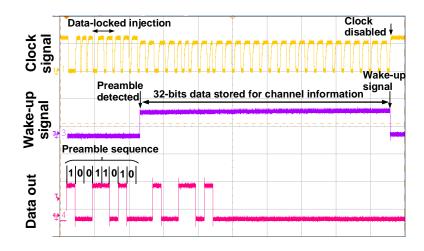

| 6.2  | Measured wake-up system preamble detection and wake-up signal at $P_{IN}$ =-50dBm           |    |

|      | and data rate of 200kbps.                                                                   | 83 |

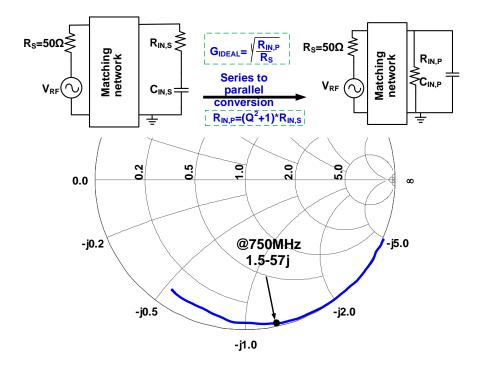

| 6.3  | Measured input impedance for Schottky diode doubler structure at the operating              |    |

|      | biasing conditions                                                                          | 84 |

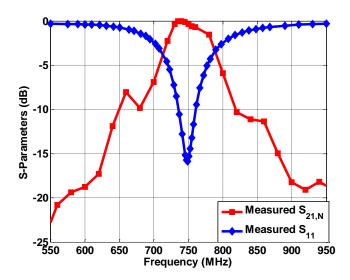

| 6.4  | $S_{11}$ and $S_{21,N}$ measurement                                                         | 84 |

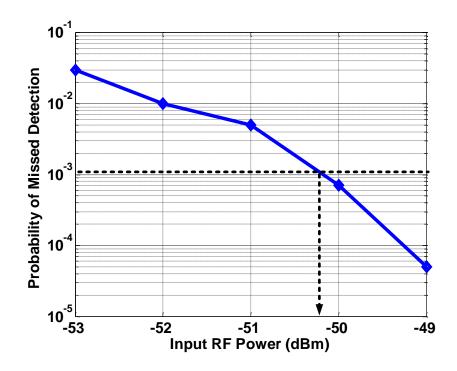

| 6.5  | Measured missed detection versus input power of the wake-up receiver $\ldots$ .             | 85 |

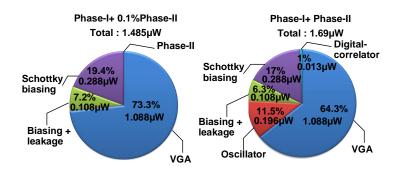

| 6.6  | Power breakdown of proposed wake-up receiver                                                | 86 |

| 6.7  | Measured signal-to-interferer ratio (SIR) at different offset frequencies from car-         |    |

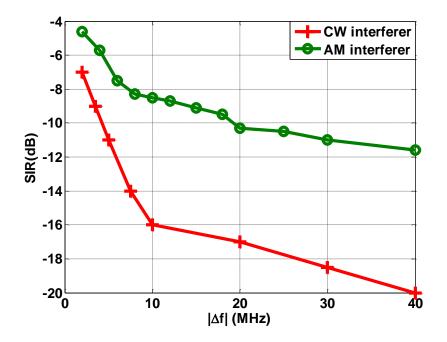

|      | rier with CW and AM interferer                                                              | 86 |

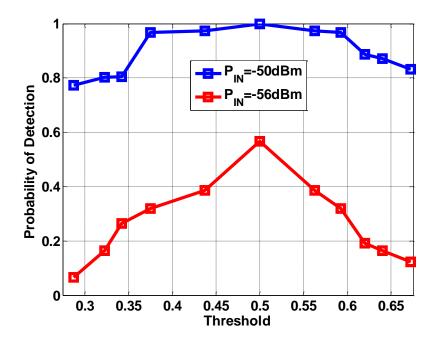

| 6.8  | Measured Probability of detection at $P_{IN}$ =-50dBm and $P_{IN}$ =-56dBm                  | 87 |

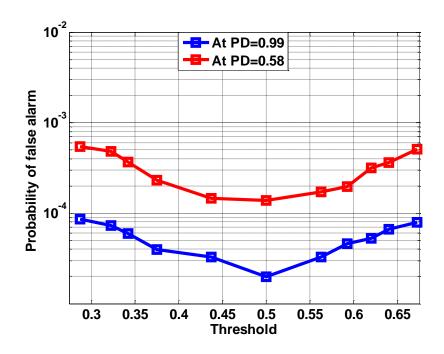

| 6.9  | Measured Probability of false alarm at PD=0.99 and PD=0.58                                  | 88 |

| 6.10 | Normalized sensitivity versus energy per bit and proposed FOM for WuRx system               |    |

|      | comparison for prior publications                                                           | 89 |

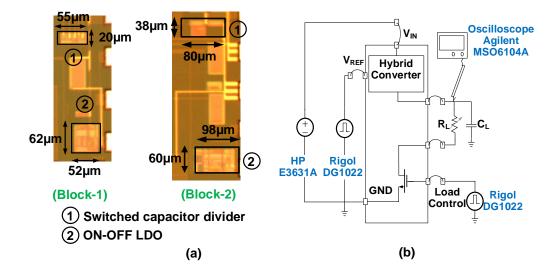

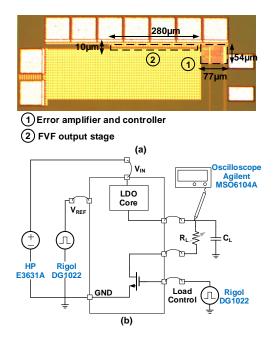

| 6.11 | (a) Chip Micrograph for Block-1 and Block-2, and (b) test setup                             | 92 |

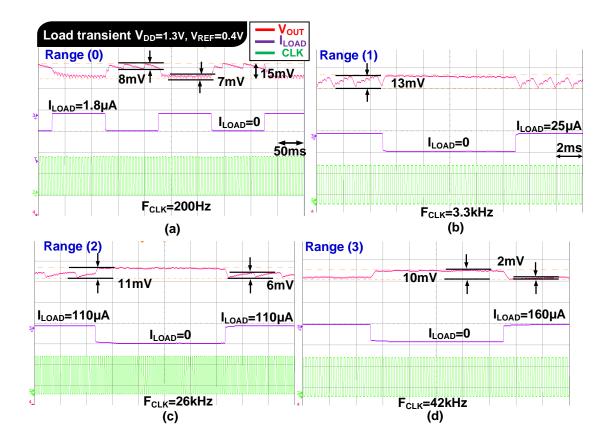

| 6.12 | Measured load transient from no-load condition to (a) $1.8\mu A$ for the sub-microwatt      |    |

|      | block (Range-0), (b) $25\mu A$ for higher ranges block (Range-1), (c) $110\mu A$ for higher |    |

|      | ranges block (Range-2), and (d) 160 $\mu A$ for higher ranges block (Range-3)               | 93 |

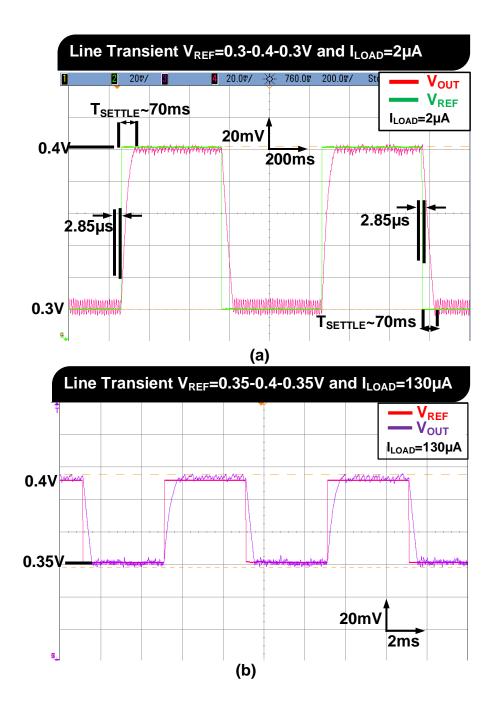

| 6.13 | (a)Measured line transient for sub-microwatt block-1 when reference voltage change          |    |

|      | from 0.3V-0.4V, and (b) measured line transient for block-2 at a load current of            |    |

|      | $130\mu$ A and reference voltage change from 0.35-0.4V                                      | 94 |

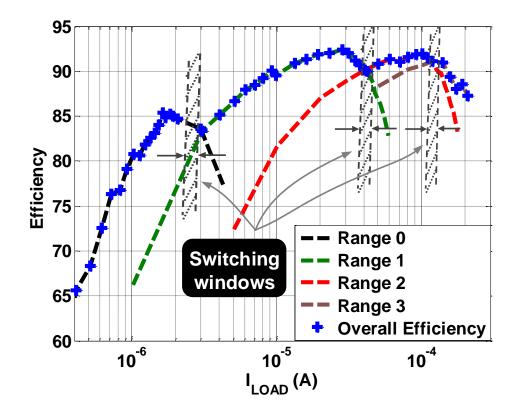

| 6.14 | Measured overall efficiency across 4 operating ranges                                       | 95 |

| 6.15 | (a) Chip micrograph, (b) measurement setup of the proposed Class-D LDO                      | 97 |

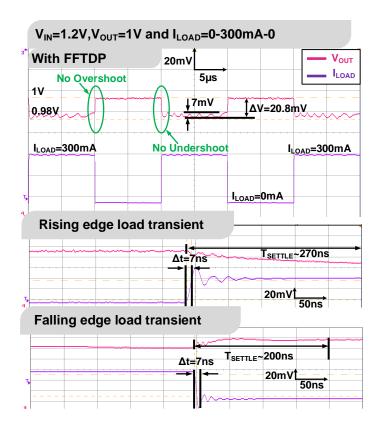

| 6.16 | Measured load transient at load change from 0-300mA in 7ns at $V_{DD}$ =1.2V and           |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | $V_{OUT}$ =1V with FFTDP and zoomed-in rising and falling edges                            | 98  |

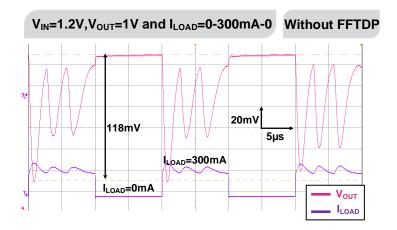

| 6.17 | Measured load transient at load change from 0-300mA in 7ns at $V_{DD}$ =1.2V and           |     |

|      | $V_{OUT} = 1$ Without FFTDP                                                                | 98  |

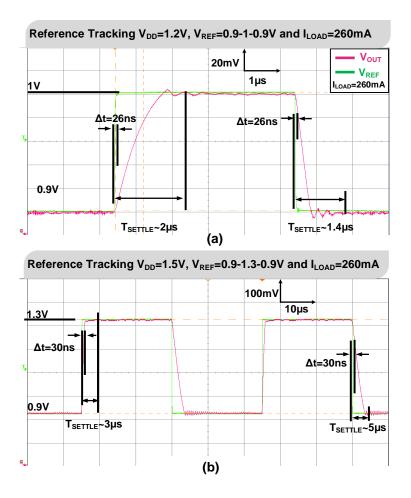

| 6.18 | (a) Measured line transient at supply voltage of 1.2V and edge time of 26ns, (b)           |     |

|      | measured line transient at supply voltage of $1.5V$ and wider reference voltage            |     |

|      | change 0.9V-1.3V                                                                           | 99  |

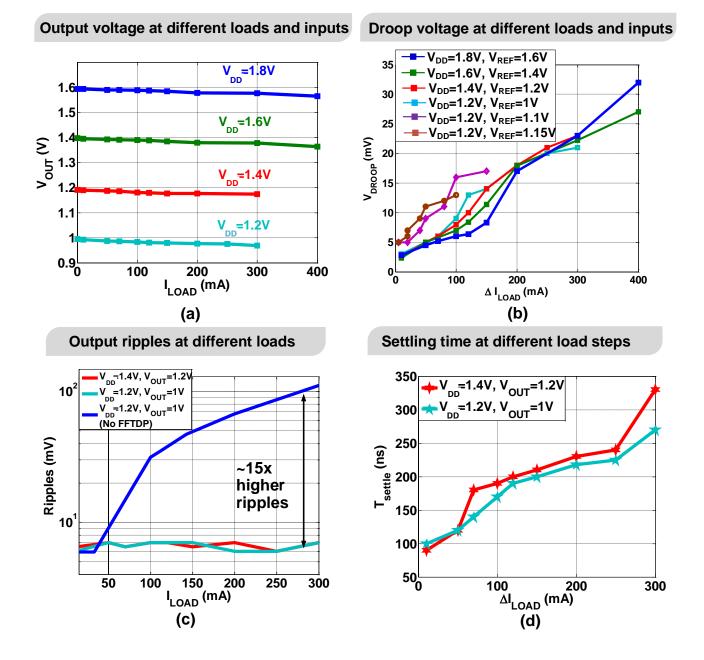

| 6.19 | (a) Various measured performance of proposed LDO at 200mV of dropout voltage:              |     |

|      | (a) load regulation, (b) Vdroop, (c) ripple, and (d) settling time. $\ldots \ldots \ldots$ | 100 |

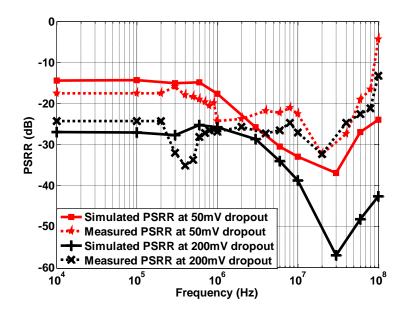

| 6.20 | Measured and simulated PSRR at 50-mV and 200-mV dropout voltage at 30-mA $$                |     |

|      | and 60-mA load respectively                                                                | 101 |

## LIST OF TABLES

| 6.1 | Comparison of the proposed WuRx with state-of-the-art designs | 91  |

|-----|---------------------------------------------------------------|-----|

| 6.2 | Comparison with prior publications                            | 96  |

| 6.3 | Performance summary and comparison with prior art             | 103 |

#### ACKNOWLEDGMENTS

Foremost, I want to express my sincere appreciation and gratitude to my mentor and academic advisor, Prof. Ken Yang. His advice, guidance, and relentless support during my doctoral program were invaluable to my successful completion. During my Ph.D., I enjoyed our meetings, which I benefited from both technically and personally. I find it hard to express my gratitude for him always being ready with advice and the right feedback even under his busiest time.

I would also like to thank my committee members Prof. Gregory Pottie, Prof. Sudhakar Pamarti, and Prof. Danijela Cabric for their dedicated service on my thesis supervisory committee and all their guidance and constructive feedback. Special thanks to Prof. Sudhakar Pamarti for his continuous support with the fabrication of my chips and his helpful ideas and comments. I am also grateful to Prof. Danijela Cabric and Samer Hanna for their collaboration in the wake-up receiver architecture and for providing support.

I am much obliged to the Department's Office of Graduate Student Affairs whose staff members are always there to answer questions, give advice, and process paperwork promptly. They play a key, behind-the-seen, role in advancing research at UCLA. Deeona Columbia, Ryo Arreola, and Kyle Jung thank you.

Throughout my Ph.D., I had the chance to do three industry-related internships that provided me with a lot of valuable experience. The first was with the Audio Codec group at Qualcomm, Irvine, for which, I would like to thank Sherif Galal and Khaled Abdelfattah who mentored and guided me throughout the internship. The second internship was with the touch team at Qualcomm, San Diego, for which, I would like to thank Sameer Wadhwa for his guidance and for filing my first patent with Qualcomm. The third internship was with the PLL team at Qualcomm, San Diego, for which I would like to thank Sangwook Park for his support.

I would like to thank my lab-mates especially my dear friend, Li-Yang Chen, for great discussion and friendship. Also, I would like to thank Ryan Stark, Ashutosh Shiledar, Liangxiao Tang, and Jiazhang Song. During my stay at UCLA, I was blessed to be among a group of wonderful people who made my stay in Los Angeles a wonderful memory and who were always there for me, helping me get over every technical and non-technical obstacle I have met. Thanks are due to my dear friends, Atharav Gupta, Hossien Razavi, Shi Bu, Jiyue Yang, Albert Hung, Uneeb Rathore, Sumeet Singh, Usama Anwar, Star Li, Navjot Singh, Abdelaziz Elshaya, Ahmed Elzohair, Kejian Shi, and Ghaith Hattab.

Also, I would like to express my gratitude to my Egyptian friends in Los Angeles Moustafa Alzantout, Yahya Ezzeldin, Mohamed Karmoose, Ahmed Alaa, Osama Hanna, Antonious Girgis, Samer Hanna, and Amir Nabil.

I would like to thank my friends in other states in the U.S for all the phone calls we had that kept me sane during tough times: Mostafa Kishk, Mahmoud Ayman, Omar Bakry, and Karim Megawer. I would also like to thank my friends in Egypt for being my second family and always having my back without a second thought: Mohamed Abdelkhalek and Hany Helmy.

Finally, I want to thank my parents for their love, infinite patience, and endless support. I also want to express my gratitude to my sister Nesma for being always kind and giving. I want to thank my brother, Mohamed, for supporting me during hard times. I would like to express my deepest gratitude to my uncle, Prof. Mohamed Asaad, for always inspiring me. I want to thank my aunt Magda Asaad for her continuous giving.

### VITA

- 1991 Born, Giza, Egypt.

- 2013 B.Sc., Electrical Engineering, Cairo University, Egypt.

- 2013-2015 M.Sc., Electrical Engineering, Cairo University, Egypt.

- 2015-2020 Research Assistant, Electrical and Computer Engineering Department, University of California, Los Angeles (UCLA).

### PUBLICATIONS

**M. Elhebeary** and C. K. Yang, "A Class-D FVF LDO with Multi-Level PWM Gate Control, 280-ns Settling Time, and No Overshoot/Undershoot," in IEEE Transactions on Circuits and Systems I: Regular Papers, (In press).

**M. Elhebeary** and C. K. Yang, "A 92%-Efficiency Battery Powered Hybrid DC-DC Converter for IoT Applications," in IEEE Transactions on Circuits and Systems I: Regular Papers, (In press).

M. Elhebeary, L. Chen, S. Pamarti, and C. KenYang, "An 8.5pJ/bit Ultra-Low Power Wake-Up Receiver Using Schottky Diodes for IoT Applications," ESSCIRC 2019 - IEEE 45th European Solid-State Circuits Conference (ESSCIRC), Cracow, Poland, 2019, pp. 205-208.

M. Elhebeary and C. K. Yang, "An 85%-Efficiency Hybrid DC-DC Converter for Sub-Microwatt IoT Applications," 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), Dallas, TX, USA, 2019, pp. 9-12.

## CHAPTER 1

## Introduction

Internet of Things (IoT) aims at connecting appliances and products embedded within our environment that would then gather a broad scope of information to be used to enhance our ability to respond to the environment or for our environment to respond to us. In addition to any individual's normal daily life, the applications include numerous specific fields such as agricultural, medical, manufacturing, automotive, etc. Fig. 1.1 shows the basic hierarchy of how leaf nodes are connected in a system. Leaf nodes collect data and transmit the data to a gateway through a handshaking protocol, where it only transmits the data to a gateway that may have limited availability. The gateway may be mobile such as a quadcopter that only passes once in a while over the group of sensors in a remote location or a fixed transmission unit that sends the broadcast signal to collect data from nearby leaf nodes. The data collected then is uploaded to an IoT cloud where it's analyzed and processed to forecast and analyze different phenomena.

IoT leaf nodes are extremely sensitive to energy dissipation as it directly corresponds to their deployment lifetime. Not only do they need a low-power means to monitor the environment for an activation signal, but they also need to draw little total energy from an energy source such as a battery or supercapacitor while reacting to activation. This dissertation demonstrates both with a wake-up receiver that draws less than  $4.2\mu$ A of current from a 0.4V source and a power management unit that achieves 85% efficiency at such low currents while achieving a fast transition to higher current load and maintaining efficiency.

### 1.1 Motivation

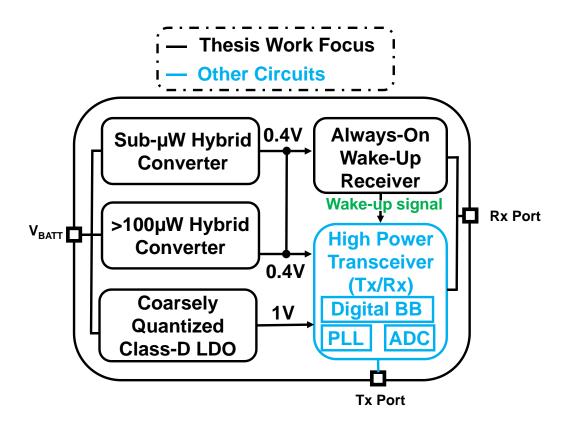

In this work, we focus on the design of leaf nodes with a limited source of energy, i.e. battery-powered and limited energy harvesting. The leaf node structure is shown in Fig. 1.2 composed of the following: a wake-up receiver to sense the channel and wake-up the high power radio when the predefined signature is being asserted, a high-sensitivity transceiver which is always sleeping and only wakes up when the wake-up receiver sends a signal. A power management unit that regulates the battery voltage to multiple voltage levels for the ultra-low-power wake-up receiver and high-power blocks on the chip. The leaf node is battery powered and should have a lifetime of >10 years. Thus minimizing average power consumption from the battery is the main concern for the system specifications.

Due to the limited power budget, a wireless data transceiver of the leaf node cannot be always on. Instead, a very low-power wake-up receiver that is always on and monitoring a specific frequency spectrum awakens the primary data transceiver should a signature be detected. For targeted real-time applications, low latency is critical specification as the gateway will be available only for a short time, this leads to high data rates required for the primary data transceiver and fast power management unit chip for fast wake-up <1ms. A highly effi-

Figure 1.1: IoT nodes top-level structure

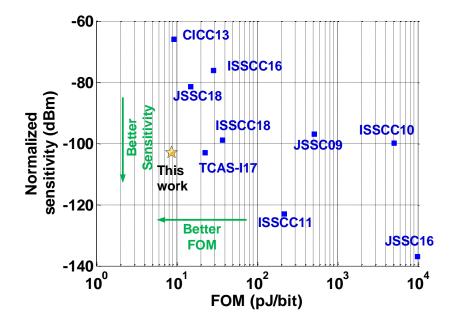

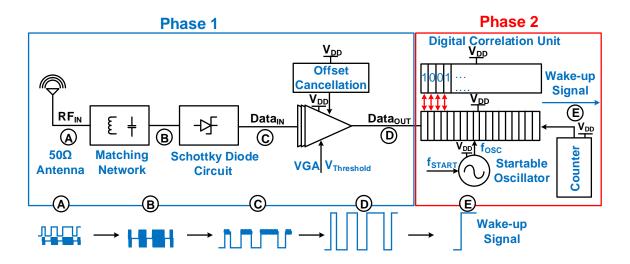

cient wake-up receiver is achieved by combining two techniques: a Schottky diode front end that is optimally biased for low energy/bit, and a two-phase wake-up technique which further lowers the quiescent operating power when no data is sensed on the channel by turning off the second phase. Therefore, the energy efficiency of the WuRx is optimized on both the circuit level and the architectural level. On the circuit level, we propose a low-power CMOS Schottky diode as a power detector consuming only 18% of total power, while providing sufficient bandwidth, compared to >35% in prior publications. On the architectural level, the proposed two-phase architecture reduces the average power consumption further by 12% by activating the second phase only in case of detection of the data stream in the channel. For the given latency specification along with the battery capacity of 800mAh, this would limit the wake-up receiver power budget to <2 $\mu$ W. Thus allowing the battery-operated leaf node to operate for >10 years. This work consumes low power of 1.69 $\mu$ W at 200kbps resulting in sub 9pJ/bit with normalized sensitivity of -103dB which compares favorably with prior

Figure 1.2: Leaf nodes architecture and Thesis work focus

publications as shown in Fig. 1.3. To operate with such strict power consumption, the low supply voltage is adopted for sub-threshold operation.

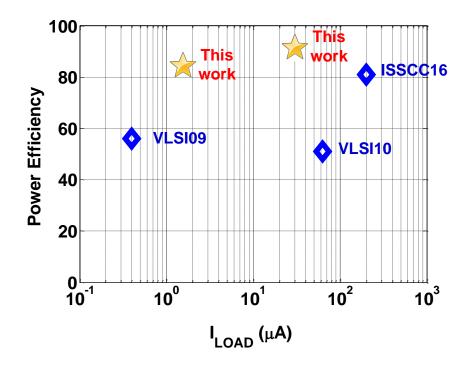

An efficient power management unit is a critical component of the leaf nodes. First, the wake-up receiver circuit requires a high power-efficiency regulator. The regulation overhead for such low loads is often poor and degrades the overall life-time of the leaf node. The power management unit (PMU) furthermore needs to achieve high power efficiency at low output ripple levels. Since subsequent stages are turned on after wakeup, the PMU must handle a wide range of load current and continuous output voltage levels, not just discrete predefined levels. Multiple power management solutions are explored including low dropout regulators and switched capacitor dividers. LDO achieves continuous output level and low ripple levels, however, it has low power efficiency. For switched capacitor divider, it can achieve high power efficiency, however, it can not provide continuous output voltage levels. We combine the merits of both approaches and implemented a hybrid converter for low voltage supply generation. The hybrid converter achieves high power efficiency exceeding 80% at low power loads and across wide load range while regulating output voltage at

Figure 1.3: Wake-up receiver normalized sensitivity versus FOM for prior publications

Figure 1.4: Power efficiency versus load current of prior work

0.4V. The first stage is a switched-C divider with a fixed 3:1 divide ratio and achieves an efficiency of 97%. Similar to prior literature, a larger input voltage range can be supported by selecting different division ratios. This work introduces an LDO second stage that uses an all-digital ON-OFF controller that uses small quiescent current to maintain an overall efficiency of >85%. The LDO provides a regulated output voltage with a dropout voltage of 30mV and leverages the output capacitance to suppress the ripple to less than 10mV. To maximize efficiency, we jointly optimize both stages so that they share the same clock signal. Also, a system-level switching between different configuration is proposed to increase the range of load currents that the at which efficiency is optimized to supply the required power for additional blocks that are turned on. Figure 1.4 shows the power efficiency of the hybrid power management unit compared to prior work. One final challenge in the power management of leaf nodes is the high power radio regulation. When different load ranges switch to the high power mode, it requires fast settling, low overshoot supply regulation since it wakes up for a short period.

Figure 1.5: Settling time and overshoot/undershoot versus load current of prior work

For the fast transient response regulation unit, we present a novel Coarsely-Quantized Class-D LDO that provides a regulated output voltage at 1V for the main-radio. The main motivation behind this work is to achieve fast transient response in case of fast load change along with short settling time. To achieve these system specifications, we introduced a novel gate control scheme for the output stage. In this control scheme, we decoupled the control path from the power path, hence allowing fast loop control over sudden changes at the load. Also to sense these sudden load changes and to stabilize the output ripples within a small time, we introduced a feed-forward path that acts as a derivative path for the control signal. These techniques helped in achieving fast settling time(i.e. 10x lower compared to same load changes in the prior art) and no overshoot or undershoot(i.e. only static load regulation due to load increase) as compared to prior work as shown in Fig. 1.5. The proposed LDO achieves settling of 280ns for load change of 300mA with an edge time of 7ns. The LDO shows no-overshoot or undershoots at fast transient load changes that resemble digital core switching, hence it can be of benefit to operating digital core circuits.

### 1.2 Thesis Organization

The dissertation is composed of seven chapters. In Chapter 2, we begin with background information on the thesis two main contributions. First, we cover the different ways of implementing wake-up receivers and also covers different approaches for always-on wake-up receivers and power, sensitivity trade-offs. Second, we highlight the different approaches to implementing power management for leaf nodes. Also, we provide the system specifications requirements for ultra-low-power generation along with different load range-switching resulting in the need of fast transient regulator.

The main contributions of this dissertation can be split into two parts. The first part discusses the wake-up receiver of power limited leaf node, whereas the second part discusses the power management solutions for the leaf node. In Chapter 3, we present the implementation of an ultra-low-power wake-up receiver for high throughput applications with asynchronous communications. We propose a CMOS Schottky diode used as an energy detector for better detection with low power cost. For reducing the overall power consumed of the wake-up, we divided the system into 2 phase which saves 12% on average. Also, we propose a data-locked oscillator as the second phase of the wake-up system to avoid the usage of bulky crystal oscillators. We also show circuit implementation and system analysis of the system.

The second part is discussed in Chapters 4 and 5, where we discuss power management unit implementation which comprises of the hybrid DC-DC converter and Coarsely-Quantized class-D LDO. In Chapter 4, we discuss the power management solution to operate the WuRx at the low supply of 0.4V while achieving power efficiency exceeding 80% for low load below  $2\mu$ W. We show the system implementation of a wide load  $(0.8\mu$ W- $100\mu$ W) of the hybrid DC-DC converter. The wide load coverage is achieved through system-level switching to improve power efficiency across the whole range. In Chapter 5, we present a novel class-D flipped voltage follower (FVF) low-dropout (LDO) regulator. The system is enabled after the wake-up system asserts the wake-up signal to the main transceiver. This binds the system startup and settling time to provide a high load in a short time. The system implementation and system analysis are presented in the chapter along with stability analysis. The proposed LDO is modeled as and provided a linearized stability model to show different system parameters. The implementation responds to load changes from 0-300mA in 7ns with no observed overshoot/undershoot and can operate down to 10mV dropout voltage.

Multiple test-chips were built as part of this dissertation to validate the various design approaches. Chapter 6 shows the experimental measurement results for each of these experiments as follows. First, we present the wake-up receiver chip fabricated in CMOS 65nm. Second, we present PMU chips fabricated in CMOS 28nm (2 chips for different load ranges). Third, we present the Class-D LDO chip fabricated in 28nm. Chapter 7 concludes the work, lists the contributions, and offers some ideas for future work.

## CHAPTER 2

## Background

This chapter provides a brief overview of the different issues of limited power leaf node design. We focus on the background of the thesis main contributions in the wake-up receiver and the power management for the leaf node. First, we review the different implementations of the wake-up receiver which are the duty-cycled or the always-on. Then we will discuss in detail the always-on wake-up receiver architecture which is compatible with our targeted application. We show different trade-offs of sensitivity, latency, and energy per bit cost for each of the different approaches. Then we discuss the trade-offs of the envelope detector based wake-up receiver and the power management challenges at low voltage and power levels. Also, we discuss the challenges of operating the wake-up receiver at low voltage, and quiescent current would require high power efficiency regulation which is challenging at these levels.

Second, we review different approaches for voltage regulation and the trade-offs at low power levels. The Wake-up receiver system consumes low power is a challenging problem to achieve high power efficiency. After the wake-up signal is asserted, the high power radio wake-up with low latency which requires stable supply. We discuss the different topologies of LDOs to supply the high power radio and the trade-offs between analog, digital, and the proposed class-D LDO. This discussion is important to understand the challenges in limited power leaf node implementation.

### 2.1 Wake-up Receiver

### 2.1.1 Low-power radios

Low power radio becomes a critical component in leaf nodes since it forms a large portion of the power used. Since the power consumption of the receiver chain used in the unlicensed band is relatively high. Different approaches have been implemented to reduce the average power consumption in these sensor nodes which are divided mainly into two approaches. The first approach is suitable for sensor nodes that are characterized by long idle periods and burst mode reception and transmission of data. Figure 2.1(a) shows a duty-cycled receiver approach which is a common way in 4G transceivers [1], [2]. In the sleep mode, lower power consumption for the sensor node is required since it is almost >90% of the time. The following equation shows the average power consumed for the wake-up receiver.

$$P_{avg} = \frac{P_{slp}t_{slp} + P_{on}t_{on}}{t_{slp} + t_{on}}$$

(2.1)

So the on time will decide the average power consumed by the wake-up receiver. Also, the system is required to wake-up at low power cost and allow higher power circuit components to operate through the transmission and reception phase. This approach requires a precise clock and fast startup oscillator to minimize its on-time detection phase. This approach trades-off power with the periodicity which can lead to slow response and long latency.

The second approach is to use a low-power wake-up receiver system that is always on and constantly listen to the channel. In this approach, the high power receiver is on sleep mode unless a wake-up signal is received from the always-on wake-up module. The wakeup system consumes low power and sacrifices high sensitivity compared with a high power receiver. The wake-up system detects certain data sequence and enables the high power receiver to allow higher data rate transmission and higher sensitivity. Figure 2.1(b) shows the data sequence which starts with the transmitter sends a preamble sequence, so the wakeup receiver receives this preamble and enables the operation of the high power receiver. Then the high power receiver sends an acknowledgment reply to establish a communication channel with the transmitter. Finally, the transmitter sends data to the receiver and the

Figure 2.1: (a)Periodically wake-up receiver (b)Always-on wake-up receiver.

receiver goes back to sleep again. The challenge is maintaining minimal energy per bit of the always-on receiver with the required data rate for different applications. In this thesis, we will emphasize the implementation of the second approach with more details about different architectures and design details.

Different parameters are used to define the figure of merit for wake-up receivers. In the next section, we will show the main parameters used for different approaches and their impact on the overall power consumption and the overall latency of the system.

### 2.1.1.1 Battery life

Battery life elongation is the motivation for this work. For billions of sensor nodes required to sense physical phenomenons and provide reliable data for the life-time of more than 10 years. For a given data-rate requirement, the power consumption of the receiver is optimized to elongate the battery life. This is done by having duty cycling of the receiver system with small on-time to lower the average power consumption. Other approaches use an alwayson wake-up receiver to put the main receiver always on sleep and have an ultra-low-power wake-up receiver to always listens to the channel. Another way of elongating the battery life is to integrate it with energy harvesting as auxiliary power source [25]-[26].

### 2.1.1.2 Wake-up latency

The wakeup latency is an important factor for the wake-up receiver design. Since the gateway can be only available for a few minutes per data collection as well the power limitation over the gateway which requires a short time to accommodate the data transmission. Different applications have different wake-up latency requirements ranges  $250\mu$ s to 10ms [24]. To achieve the lower end of the wake-up latency, the system is required to run at a data rate of >50kbps [9]-[17]. Thus imposing high quiescent current used in baseband amplification circuits compared to low data rate <1kbps. From which we can see that energy per bit is considered the main parameter to compare different wake-up receivers with different data rates.

### 2.1.1.3 Probability of false alarm

The probability of false alarm is defined as the false wake-up for the main receiver given that the correct signature is not detected. This can happen due to the noise in one of the following two scenarios. First, the noise is high enough to invert "0" to "1" and it coincides with the predefined pattern. Second, another pattern sent and the noise changed it to the correct pattern. This will result in unwanted wake-up of the main transceiver which consumes in the order f few milli-watts, hence, resulting in battery life degradation. Typically, the probability of false alarm is required to be sufficiently low i.e.  $< 10^{-4}$  so that the power consumption of the overall leaf node kept within the power consumption of the always-on wake-up receiver.

### 2.1.1.4 Probability of detection

The probability of detection is defined as the detection rate when the correct signatures are sent over the channel. The missed detection rate is the complement of the probability of detection and it is set at  $10^{-3}$ , which puts the probability of detection at 99.9%. The gateway can further relax the specification over the probability of detection by having multiple transmissions (i.e. example 5 times) which put the requirement over the probability of detection for the system to be 66.5%. This would further relax the design of an energy detector minimum signal to noise ratio.

#### 2.1.1.5 Energy per bit

The basic figure-of-merit for the wake-up receiver is the energy per bit cost, which is calculated by dividing the average power over the data rate. Wake-up latency plays an important rule in the choice of the data-rate thus affecting average power consumption. However, for base-band circuits the bandwidth is directly proportional to the current consumption (i.e Bandwidth  $BW=g_m/C_L$ , where  $g_m \propto I_{SS}$ ), where  $I_{SS}$  is the bias current. Thus more power is required as data rate increases. Which is also applicable for digital circuits in the system and base-band clock generation. Since the power is  $P=Cf_{clk}V_{DD}^2$ , which shows higher power levels at higher data rates. Different wake-up receiver architectures target improving the energy per bit cost along with maximizing the system sensitivity.

### 2.1.1.6 Sensitivity

Sensitivity is defined as the minimum detectable signal which the radio can sense. It sets the distance range of detection as well as the transmitted power to accommodate the medium losses. For a receiver, the sensitivity is the goal of improvement for a given data rate. For receivers, the sensitivity improvement comes at the expense of power consumption by using high power low noise amplifiers (LNA) to amplify the signal at pass-band. Other approaches use a mixer as a front-end to lower the power consumed on the expenses of the receiver sensitivity. Also, the bandwidth in RF and the filtering lowers the total integrated noise and improves the overall sensitivity. For a receiver, the sensitivity can be expressed as:

$$P_{sen} = NF_{Rx} + 10logBW - 174 + SNR_{min} \tag{2.2}$$

### 2.1.2 Always-on wake-up receiver

Always-on wake-up receivers can be categorized into 3 main architectures as shown in Fig. 2.2. The first architecture is a superheterodyne mixer which is first introduced in [3]. This architecture is a mixer based architecture that achieves a  $52\mu$ W power. It operates from a 0.5V supply and achieves high sensitivity of -72dBm. The power consumption in this approach is a function of the frequency of operation since the oscillator consumes the largest power portion. This approach achieves good interference rejection which is required in many applications. However, the high power consumed in the local oscillator and mixer power sometimes limits its usage for long-life battery-based applications. Different implementations followed that one and achieved higher sensitivity and different bands of operation as in [4]-[7]or even used different modulation schemes as FSK as in [8].

The second architecture is a conventional tuned RF. This architecture uses LNA in the front-end to achieve high sensitivity. This architecture amplifies the low power input signal and then passes it over the envelop detector to decode the data sent. The signal after the envelop detector is in baseband and can be amplified using a low power baseband amplifier. This approach is used [9]-[10]. In [10], the power dissipated in LNA forms 66% of the total power dissipated in the circuit of  $23\mu$ W. This power consumption for LNA at 900MHz frequency would be much higher if the 4G band was targeted or Wi-Fi bandwidth. This architecture achieves -78.5dBm due to the use of LNA at the front-end. In [8], the LNA also forms 55% of the total power. Even without the LNA and having the detector circuit in the front-end, this architecture would still consume relatively high power >20 $\mu$ W resulting in high Joule per-bit cost.

The third architecture used the square-law detector as the front-end. The square-law detector can be in the form of NMOS in the sub-threshold region with bias current as in [12]. Using NMOS in sub-threshold as in [11], achieved sensitivity up to -69dBm with a data rate of 300bps but in the expenses of bandwidth and start-up latency exceeding 100ms. The power consumption is 4.2nW in the expenses of the data rate which consequently reflects on the energy per bit cost at 15pJ/bit. Other architectures used voltage rectifiers using diode-

**Figure 2.2:** (a) Conventional IF/Uncertain-IF Superhetrodyen WuRx (b) Conventional tuned RF WuRx (c) square-law detector based WuRx.

connected transistors as in [13], [14]. These architectures trade-off the bandwidth (data rate) and power consumption. Other approaches uses off-chip components for the wake-up operation as in [15], [16]. In these approaches, the wake-up receiver can work at a maximum frequency of 1GHz with high power consumption and low data rate transmission of 1kbps.

The proposed always-on wake-up receiver is presented in Chapter 3. Also, we discuss the evaluation of the architecture through the different figures of merits (FOM). Published techniques have used sensitivity, power, data-rate, latency, and carrier frequency as ways of comparison. Wake-up receivers are used mainly in two kinds of applications, (1) high latency with high sensitivity requirement [12] (2)low-latency with moderate sensitivity required[17]. An example of low-latency and moderate sensitivity is the health care devices that use wireless body area network (WBAN) are located at short distances from the body requires data rate ranges of 100's of kbps and low sensitivity of -40 dBm. The power constraints for such devices are high since battery replacement is extremely difficult, so it must operate under  $2\mu$ W to achieve reasonable battery life.

### 2.2 Power Management Unit for IoT Application

Power management of leaf nodes consumes large power overhead. In this thesis, we will focus on two main design challenges for supply regulation. First the voltage regulation of the low power-low voltage loads as in wake-up receivers. Second, the fast settling regulators for the main receiver when it starts-up. There are different design parameters for power management systems. We will focus mainly on power efficiency, load transient, voltage overshoot and undershoot, and settling time.

### 2.2.1 Wide range hybrid DC-DC converter

Battery-powered systems have used several options to down-convert and regulate supply voltages at low power levels. Buck converters are a common architecture in step-down voltage converters for high power regulations that target 100s of milliwatts. Due to the large overhead associated with its control [32] along with the inductor size, buck converters are not good candidates for low power applications. Low dropout (LDO) regulators [33], [34] provide high supply rejection and regulated output voltage. However, this approach results in poor power efficiency. For example, a regulated voltage at 0.4V from a battery output at 1.3V would have a maximum efficiency of  $\eta$ =30% under the assumption of no quiescent current as per Eq. 2.3

$$PE = \frac{V_{OUT}}{V_{IN}} * \frac{I_{OUT}}{I_{IN}}$$

(2.3)

Where  $V_{OUT}$  is the output voltage,  $I_{OUT}$  is the load current,  $V_{IN}$  is the input voltage,

and  $I_{IN}$  is the current drawn from the input voltage.

Another approach is to use a switched-capacitor dc-dc converter which has power efficiency up to 97% [35]. However, switched capacitor designs typically only divide the input voltage and does not provide any supply rejection or regulation. A hybrid architecture [36] has been shown where the first stage divides the battery voltage by five using a switchedcapacitor dc-dc converter. The design then uses an LDO in the second stage for output voltage regulation. This system provides an efficiency of up to 56% at low loads. However, the work suffers from a high voltage ripple of up to 50mV at the output and can only operate across a narrow range of load. Other two-stage approaches include using multiple switchedcapacitor dividers with feedback to sense the output voltage and control the divider's ONtime to deliver achieve regulation. The approach has been shown to achieve maximum

**Figure 2.3:** Efficiency for ideal switched-C, ideal LDO and proposed hybrid converter at different supply voltages.

efficiency of 70.4% [37]. Hybrid step-up converters are also used for energy-harvesting applications as in [38],[39], [40], and [41] in which the first stage is a boost converter or switched capacitor charge pump to boost the low input voltage, and the second stage is an LDO for output voltage regulation.

For the low voltage-low power regulation challenge, we propose a two-stage hybrid power management unit that can cover a wide load range through multiple phases of activation. Fig. 2.3 shows the efficiency comparison between the 2 approaches discussed in the literature and the proposed approach at low load which resembles the wake-up receiver circuit. The wake-up receiver is continuously ON and monitors the environment at power consumption. When a triggering event is detected, a higher power component is activated such as a radio to establish a communications channel. Ahead of this activation, the PMU activates another portion of the converter to provide efficiently the necessary power. The system then has additional tiers of activation which will require high power which can be fulfilled using class-D LDO proposed in Chapter 5. A battery's discharge characteristics [42] for such a system shows that over 90% of battery charge being utilized within the range of 1.4-1.15V [43]. The output voltage during the first two phases of operation of IoT application targets the range of 0.35-0.4V to power the always-ON wake-up circuit with up to a few  $\mu$ A of load current and power the low power radio with up to a few hundreds of  $\mu$ A of load current. Chapter 4 describes the proposed two-stage architecture in detail.

### 2.2.2 Coarsely Quantized Class-D LDO

After the startup signal is asserted by the wake-up receiver, the main transceiver is required to startup and perform the handshaking technique. The system activates then the LDO required for powering up the main transceiver unit. This restricts the startup time and the settling time for the regulated supply. The settling time of the regulated supply is defined by the time in which the output voltage is within a small range from the predefined reference. The sudden load increase change causes supply voltage to undershoot and long settling time. However, achieving low overshoot at fast load changes is challenging, as it requires wide loop bandwidth often at the expenses of high quiescent current of 10mA as in [56].

For digital circuits of the main radio, another important specification for the supply voltage is ripple and overshoot/undershoot. The voltage overshoot/undershoot can not exceed 10% of the regulated voltage, otherwise, this will cause setup time and hold time violation for the system. An illustration is shown in Fig. 2.1 to show the overshoot/undershoot of the regulated voltage as well as the settling time of the output voltage to have a stable supply.

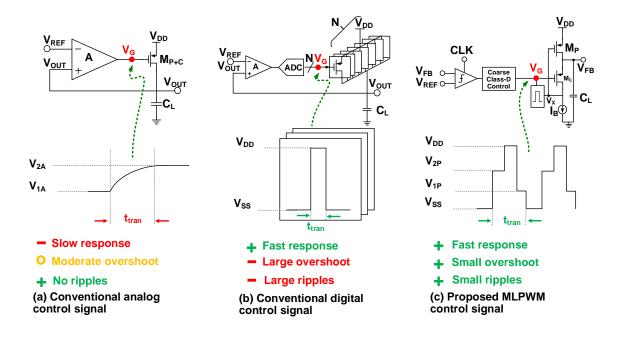

Several approaches have commonly been used in implementing LDO regulators. The most common is by an analog control loop as shown in Fig. 2.5(a). Such an analog LDO is chosen for high supply rejection and can achieve moderate overshoot and undershoot in transient load changes as in [57]-[61]. However, achieving wide loop bandwidth for fast settling affects the stability of the control loop across a wide range of loads and requires complex compensation of multiple loops. Improving the loop gain and achieving wider loop bandwidth improves transient response for the LDO as conceptually demonstrated in [62]

Figure 2.4: Transient response for load change for leaf node radio.

but is at the cost of the quiescent power of the controller and voltage headroom.

Digital LDOs [63]-[66], has more recently been shown to effectively regulate low output voltages and occupy a smaller layout area. However, it requires a minimum load current for proper operation and commonly exhibits large overshoots and long settling times with sharp load changes as shown in Fig. 2.5 (b). Variants of the digital LDO addresses some of these drawbacks by incorporating hybrid techniques of analog-assisted digital LDOs [67], [68] in which analog loops are added to digital LDOs to enhance transient response. However large overshoots/undershoots can still occur.

A conventional class-D control LDO has been proposed [69] in which the control loop comprises an analog amplifier which compares the reference voltage to the output voltage and accordingly controls a charge pump at the gate of the output stage with the corresponding pumping pulse width. In [69], the control loop's bandwidth is limited by the equivalent time constant at the gate of the output stage. Similar to an analog LDO, due to the bandwidth limitations, the work reports small ripple but has large overshoots (>40mV) and long settling times (>6 $\mu$ s).

For the fast start-up and setting challenge, we proposed a Coarsely-Quantized Class-D LDO as shown in Fig. 2.5 (c). We introduced a new method to control the gate voltage of the output stage using a multi-level pulse width modulated (MLPWM) signal and reduce the output stage's gate capacitance with the use of a flipped-voltage follower (FVF) output stage. This approach extends the loop bandwidth by pushing the dominant open-loop pole to the output node at the cost of voltage ripple at the output. We trade-off the number of quantization steps at the gate voltage with the desired ripple. A feed-forward transition detection path (FFTDP) is also introduced at the FVF output stage to substantially reduce the quiescent current. This design achieves no noticeable undershoot at 300mA/7ns load change and 280ns to settle at the required voltage. Chapter 5 discusses the proposed architecture for the novel LDO.

Figure 2.5: Conventional (a) analog and (b) digital control versus, (c) proposed MLPWM control

# 2.3 Summary

In this chapter, we showed the background of different approaches to building a low-power radio. We discussed different architectures of the always-on wake-up receiver and the trade-offs for different applications. We discussed the main parameters for wake-up receiver performance which will be further discussed in Chapter 3. Also, we gave a background for the power management challenges in leaf nodes. We discussed the hybrid converter challenges in achieving high power efficiency and the alternatives for low power regulation. Also, we highlighted the challenges in achieving fast startup regulation and the different architectures used in literature.

In the next chapter, we will discuss the system and circuit implementation of the proposed Schottky diode-based wake-up receiver system. We will show the analysis of using digital correlator and how it improves the probability of false alarm which improves the overall power consumption of the leaf node. Also, we will show the proposed architecture and circuit-level implementation of the wake-up receiver and the different design challenges.

# CHAPTER 3

# Wake-Up Receiver for IoT Applications

In this chapter, we propose a two-phase wake-up receiver that can be used in different bands and provides lower operating average power by 12% at low channel activity. We target high throughput applications with asynchronous communications where the wake-up system is primarily used to avoid the use of watchdog timers that performs synchronization and need low-latency in the startup of the main receiver. For energy detector, we propose a Schottky diode that is fabricated using CMOS technology, i.e. not part of the technology design-kit, to minimize parasitic capacitance allowing operation at high frequency ranges [23]. The second phase based on the novel data-locked startable oscillator allows correct data correlation at no need for an external clock or expensive external crystal oscillator. Digital correlator compares the received data to the preset signature to avoid interferer false wake-up for the main receiver. Digital correlator compares the received data to the preset signature to avoid interferer false wake-up for the power-hungry main receiver, which can dominate the system-level energy consumption. By optimizing the correlator length and the energy detector thresholds, we show that the two-phase wake-up receiver can reduce the system-level energy consumption by up to 60x compared to the single-stage energy detector equivalent. Wide bandwidth front-end design is adopted in the design to satisfy wake-up latency of  $200\mu s$  corresponding to 40-bits signature comparison at 200kbps data rate. This work consumes low power of  $1.69\mu$ W resulting in energy per bit of 8.45 pJ/bit.

The chapter is organized as follows, in Section 3.1 we discuss the wake-up receiver model and the noise analysis for envelope detector based receivers. We also show a performance comparison between the matched filter and correlator based wake-up receivers. In Section 3.2 we show the proposed 2-phase architecture and the CMOS Schottky diode used as energy detector. The circuits implementation is shown in Section 3.3, showing the implementation challenges. The measurement results are presented in Section 6.1 with the chip micrograph built using 65nm CMOS technology.

## 3.1 Wake-up Receiver Model

From the point of view of a wake-up receiver, the ground truth can be described as one of two; either the <u>s</u> was transmitted or no. In the absence of <u>s</u>, there are two possible scenario; a signal <u>s'</u> was transmitted or no signal at all was transmitted. This can be described using the following hypotheses

- $H_0$ : The sequence <u>s</u> was not transmitted.

- $H_{0A}$ : No signal was transmitted

- $H_{0B}$ : A sequence  $\underline{s}' \neq \underline{s}$  was transmitted.

- $H_1$ : The sequence <u>s</u> was transmitted.

where  $H_0 = H_{0A} \cup H_{0B}$ . The probability of detection is defined as the probability of declaring  $H_0$  when the truth is  $H_1 P_{FA} = Pr(declareH_0|H_1)$ , and the probability of detection is defined as  $P_D = Pr(declareH_1|H_1)$  The prior distributions of the different events are given by  $P(H_0)$ , and  $P(H_1)$ , where  $P(H_0) = P(H_{0A}) + P(H_{0B})$ . Given our definitions of the possible event, the transmitted signal x is signal given by

$$\boldsymbol{x} = \begin{cases} \boldsymbol{0} & H_{0A} \\ \boldsymbol{s}' & H_{0B} \\ \boldsymbol{s} & H_1 \end{cases}$$

(3.1)

Since we are using OOK modulation, s is a binary sequence of length L having d ones. As for s', it is any sequence of the same length not equal to  $\underline{s}$ . To trigger the WuRx, we constraint the first element of both  $\underline{s}$  and  $\underline{s'}$  to have the first bit equal to one. The received signal is modeled as z whose k-th element z[k] is given by

$$\underline{z} = \underline{x} + \underline{n} \tag{3.2}$$

where <u>n</u> is the additive white Gaussian noise (AWGN) vector with zero mean and covariance matrix variance  $\sigma^2 \underline{I}$ , where <u>I</u> is the identity matrix. Since in our analysis we assume that the received signal was normalized to have magnitude one, the signal to noise ratio (SNR) is equal to  $1/\sigma^2$ .

### 3.1.1 Comparison of WuRx Architectures

After describing the signal model and the possible events, we consider how different wake-up receiver architectures decide whether to fire the receiver. We consider three architectures, the energy detector, the correlator, and the matched filter and compare their performance.

**Energy Detector (ED)** The energy detector decides as follows

ED declares

$$\begin{cases} H_0 & z[1] \le \lambda \\ H_1 & z[1] \ge \lambda \end{cases}$$

(3.3)

where  $\lambda$  is a threshold and z[1] is the first element of the vector  $\underline{z}$ . Due to the simplicity of the energy detector, it is unable to differentiate between  $H_{0A}$  and  $H_{0B}$ .

**Correlator (Corr)** Instead of waking up the receiver for every signal that crosses the energy threshold, the correlator compares to the sequence  $\underline{s}$ . The system consists of two stages. In the first, the always-on energy detector compares the input energy with a threshold of  $\lambda$ . When the first element of the received vector z[1] crosses the threshold, the correlator is activated. The binary vector  $\overline{z}$  is obtained using the ED threshold  $\lambda$ . Once,  $\overline{z}$  is obtained it is compared to the sequence s. The system declares  $H_1$  if the received sequence  $\overline{z}$  differs by at most l bits from the reference sequence  $\underline{s}$ . This can be expressed as follows

$$\bar{z}[k] = \begin{cases} 0 & z[k] \le \lambda \\ 1 & z[k] > \lambda \end{cases}$$

(3.4)

WuRx declares

$$\begin{cases} H_{0A} \quad \bar{z}[1] = 0 \\ H_{0B} \quad \bar{z}[1] = 1, \ \sum_{i=2}^{L} \bar{z}[i] \oplus s[i] > l \\ H_{1} \quad \bar{z}[1] = 1, \ \sum_{i=2}^{L} \bar{z}[i] \oplus s[i] \le l \end{cases}$$

(3.5)

where  $\oplus$  is the binary xor operator. Since the correlator uses the entire sequence for comparison, it is expected to have a probability of false alarm lower than the ED. However, at low SNR, if we consider the exact match only (l = 0), any mistakes in the bits would lead to a misdetection.

Matched Filter (MF) The matched filter compares the analog values of z with the signature  $\underline{s}$ . The MF operation can be written as  $\eta = z^T s$

MF declares

$$\begin{cases} H_0 & \eta \le \lambda \\ H_1 & \eta > \lambda \end{cases}$$

(3.6)

Since, s is a binary sequence,  $\eta$  can be rewritten as the sum of the elements of z at the location where s[i] is equal one

$$\eta = \sum_{\{i:s[i]=1\}} z[i] \tag{3.7}$$

Since  $\eta$  is the sum of multiple values of z, it is expected to be more robust to false alarm compared to ED, which only considers the first value of z. However, the MF does not take into consideration the values of z where s is equal to zero. Hence, many different values of z will map to the same value of  $\eta$  even at high SNR leading to more false alarms than the correlator.

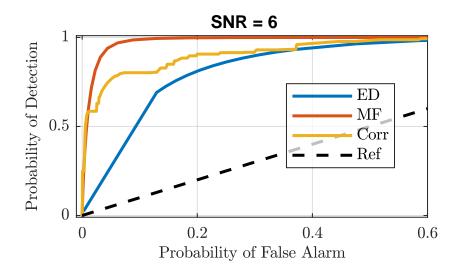

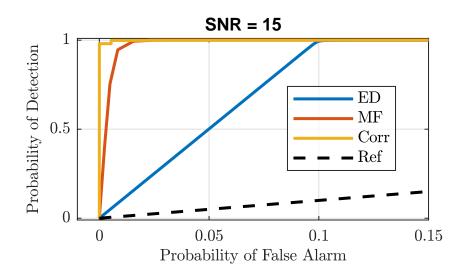

We compare the performance of the three architectures. Since, there is a trade-off between the probability of false alarm and the probability of detection, we use the receiver operation characteristics curves (ROC) to show this tradeoff [79]. Both the correlator, and a Matched filter used as sequence have L = 8 and d = 4. The ROC curve was obtained for ED and MF by scanning the values of  $\lambda$  in the range [-2, 2] and [-L, L] respectively. For the correlator, lwas sweeped from 0 to L and for each value of l, the threshold was sweeped between [-2, 2]. The prior probabilities were chosen as  $P(H_{0A}) = 0.9$ , and  $P(H_{0A}) = 256P(H_{0B})$ . This equivalent to 10% utilization with 256 equiprobable 8 bit sequences.

Figure 3.1: ROC curves of ED, MF, and Corr at SNR=6dB.

Figure 3.2: ROC curves of ED, MF, and Corr at SNR=15dB.

The ROC curves at SNR of 6 dB and 15 dB are shown in Fig. 3.1. We can see at 15dB, Correlator outperforms both the MF and ED. Since Corr checks the entire sequence, it can achieve lower PFA compared to ED. MF is unable to distinguish sequences matching s at its ones while differing at its zeros, and hence, has a lower  $P_{FA}$ , even at this high SNR. As the SNR drops, MF starts to outperform the correlator. Since the correlator will suffer from a misdetection if the first bit of the sequence was not correctly detected. Unlike the matched filter which uses all the energy of the sequence to perform the detection. From these results, we see that the correlator parameters l and  $\lambda$  can be optimized to outperform the energy detector. Due to its low power requirement compared to the matched filter, we decided to build a correlator. In our design, we pick L to trade off the wakeup latency with the performance as measured by  $P_{FA}$  and  $P_D$ .

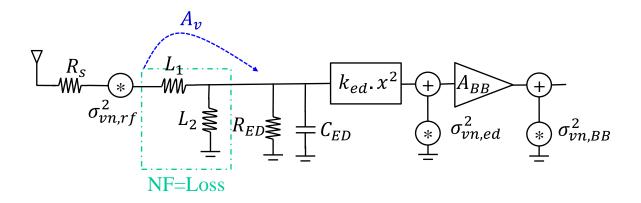

### 3.1.2 Noise Analysis

In this subsection, we analyze the noise contribution of envelop detector based wake-up receiver based on [22]. The system model is shown in Fig. 3.3. The model consists of the following: the noise due to the antenna  $(\sigma_{n,rf})$  and with passive gain with  $(A_v)$  at center frequency of  $(f_{rf})$ . The square law detector with input impedance of  $(R_{ED})$  and  $(C_{ED})$  and gain of  $(k_{ed})$ . The input RF signal  $(v_{in}(t))$  is amplified by the passive gain provided by the matching network. The input signal can be presented as:

$$v_{in}(t) = A_t \cos(2\pi f_{rf}t + \phi_{rf}) \tag{3.8}$$

The signal power at the antenna can be written as  $v_{in,rms}^2 = P_{in}R_S$ . The input noise from the antenna passed through a band-pass filter of the matching network which results in input referred noise of  $\sigma_{n,rf}^2 = KTR_s BW_{RF}$  where K is Boltzmann's constant, T is absolute temperature,  $R_s$  is antenna 50 ohm resistance, and  $BW_{RF}$  is the RF bandwidth.

This signal is amplified by the passive gain provided by the impedance transformation. The output voltage at the matching network is given by

$$v_{ed,in}(t) = A_v v_{in}(t) \tag{3.9}$$

The output noise at the envelop detector output is calculated as function of the input noise as follows

$$\sigma_{n,ed,in}^2 = \sigma_{n,rf}^2 A_v^2 N F \tag{3.10}$$

where the noise contribution of the matching network is given by (NF) which is the losses of this network.

The input signal and the input referred noise are added together and inserted at the

square law detector

$$v_{ed,out}(t) = k_{ed}(v_{ed,in}(t) + v_{n,ed,in}(t))^2$$

(3.11)

where  $v_{n,ed,in}$  is the voltage noise at the input of the square-law device with variance of  $\sigma_{n,ed,in}^2$ . By calculating the rms output voltage signal

$$v_{ed,out,rms} = k_{ed}^2 v_{ed,in,rms}^4 = A_v^4 k_{ed}^2 P_{in}^2 R_s^2$$

(3.12)

Then by calculating the noise at the output of the square law-detector from equation 3.11, we see that we have 2 main components. The first one is the noise due to the multiplication of the signal and the noise which is negligible. The second term due to the matching network and envelop detector noise and is presented as

$$\sigma_{n,ed,out}^2 = 4kTR_{ED}BW_{BB} \tag{3.13}$$

Where  $R_{ED}$  is the input resistance at  $f_{rf}$  and it's tied to the antenna source resistance at the matched condition as follows

$$R_{ED} = A_v^2 R_s \tag{3.14}$$

So the signal to noise ratio  $(SNR_{out})$  at the output of the envelop detector can be expressed as

$$SNR_{out} = \frac{A_v^4 k_{ed}^2 P_{in}^2 R_s^2}{4kTR_{ED}BW_{BB}}$$

(3.15)

The sensitivity equation can be expressed according to the  $SNR_{out}$  equation as follows

$$P_{sens}^{2} = \frac{4kTR_{ED}BW_{BB}SNR_{min}}{A_{v}^{4}k_{ed}^{2}P_{in}^{2}R_{s}^{2}}$$

(3.16)

where  $SNR_{min}$  is the minimum SNR at which the signal can be detected at the input of the WuRx. To simplify the equation, we can substitute using eq. 3.14, then the expression can be expressed as

$$P_{sens}^2 = \frac{4kTBW_{BB}}{A_v^2 k_{ed}^2 R_s}$$

(3.17)

From the resulted equation, we find out that the system sensitivity is directly proportional to the base-band bandwidth of the system (data rate). Also it's inversely proportional to the envelop detector gain and the passive gain which both needs to be maximized in order

Figure 3.3: System model for noise analysis.

to achieve the maximum sensitivity for a given data rate. As we will show in Section 3.2, the Schottky diode maximizes the conversion gain as well as the passive gain through matching network for the data rate of 200kbps.

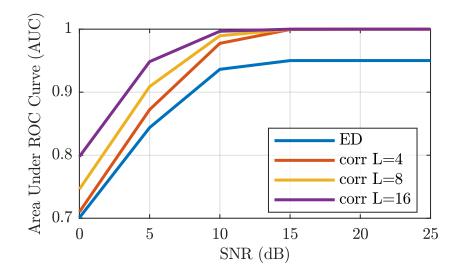

### 3.1.3 Correlator Design Analysis

To determine the effect of our choice of the correlator length L on the performance of the wake-up receiver, we generate a ROC curve for the candidate values of L at different SNRs. The area under the ROC curve (AUC) was used as a comparison metric. An ideal detector would have an AUC value equal to one. The ROC curves were generated using the same parameters as in Section 3.1.1. The results are shown in Fig. 3.4, from which we see that by increasing L, we can find the values of l and  $\lambda$  that improve the performance of the detector. However, increasing L increases wake-up latency. Hence, we decided to use L = 8.

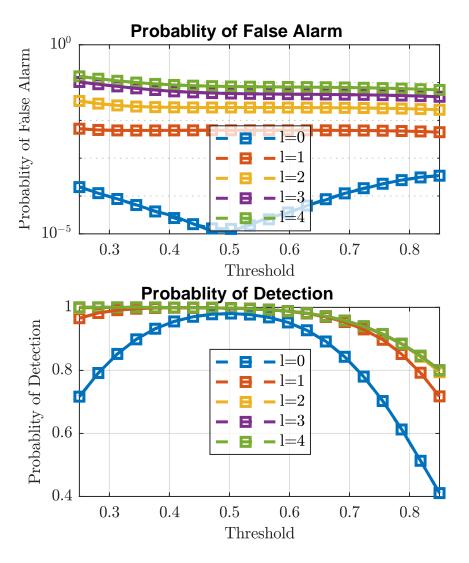

After choosing L = 8, we aim to determine the values of the parameters l and  $\lambda$ , which optimize the system performance. The effect of changing the threshold for different l at SNR=15dB is shown in Fig. 3.5. As we increase l, the probability of detection increases but, the  $P_{FA}$  increases at least by up to 100 folds. To avoid erroneous wake-ups of the receiver, we decided to choose l = 0.

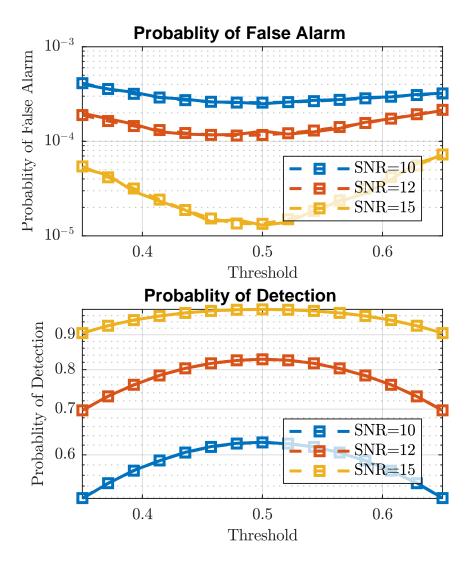

After choosing l = 0, we plot the effect of the choice of the threshold on the system

Figure 3.4: The effect of the correlator length (L) on the WuRx performance measured using AUC at different SNRs.