## UC Berkeley Green Manufacturing and Sustainable Manufacturing Partnership

## Title

Using a Hybrid Approach to Evaluate Semiconductor Life Cycle Environmental Issues: A Case Study in Interconnect Module Impacts

### Permalink

https://escholarship.org/uc/item/7x99h868

### **Authors**

Krishnan, N. Boyd, S. Rosales, J. <u>et al.</u>

# Publication Date 2004

## Using a Hybrid Approach to Evaluate Semiconductor Life Cycle Environmental Issues

A Case Study in Interconnect Module Impacts

Krishnan, N., Boyd S., Rosales J., Dornfeld D. Mechanical Engineering University of California, Berkeley Berkeley, CA, USA nkrishna@newton.berkeley.edu

*Abstract*— A methodology to perform a hybrid approach to evaluate semiconductor life cycle impacts is developed. This methodology uses (i) bottom-up process models and data to develop inventories for semiconductor manufacturing, and for specialty semiconductor chemicals items and (ii) an economic input-output method for generic inventory items. The approach attempts to overcome several semiconductor LCA challenges and is illustrated through a case study in life cycle environmental impacts of an interconnect module in a logic device.

Keywords-Hybrid Life Cycle Assessment; Design for Environment, Semiconductor Manufacturing

#### I. INTRODUCTION (HEADING 1)

With rapid growth in the electronics and computer sectors, environmental and health issues associated with semiconductor manufacturing are growing in importance. In addition to environmental impacts during the actual manufacturing process itself, semiconductor manufacturing also mobilizes materials and energy in other industries throughout the economy, potentially leading to a wide range of upstream environmental impacts. To evaluate total environmental impacts associated with semiconductor manufacturing, it is therefore necessary to evaluate impacts associated with the entire supply chain.

Environmental analysis in semiconductors has therefore been progressing towards Life Cycle Assessment (LCA). Given the complexity of semiconductor processes and the rapid rate of change, it is essential to develop LCA tools and studies that can be adapted rapidly with changes in technology, and that can account for absent or inconsistent data. Currently, a generic LCA tool to support semiconductor manufacturing does not exist. However, a few LCA and inventory studies have been conducted that demonstrate the importance of considering upstream life cycle impacts [1,2].

However, detailed life cycle studies may also require significant time to complete. And it is challenging to ensure that the boundary of the assessment is comprehensive, and that most significant contributions to the life cycle inventory have been accounted for.

Other studies have also developed manufacturing inventory data for typical wafer fabrication operations [3] and for an EPROM device [4]. For all these studies, it is difficult to apply Raoux S., Smati, R. Environmental Solutions Products Division Applied Materials Santa Clara, CA, USA

the results to understand the impacts of newer technologies or different families of devices.

Smati et. al. have developed studies that are parameterized, and can be altered based on certain technology parameters but that specifically focus on gaseous emissions from semiconductor manufacturing. [5]. Murphy [6, 7] has also developed a module-based parametric analysis of semiconductor environmental impacts to provide the flexibility needed to develop predictive life cycle inventories within fabs.

We adopt a similar approach in this work, but we base the analysis directly on individual equipment sets [8]. We also seek to develop methodologies for the collection of life cycle data throughout the semiconductor supply chain.

To summarize, several obstacles to effective semiconductor life cycle assessments (LCA) exist, including: (i) significant effort and time required to perform detailed life cycle inventory analyses; (ii) boundary problems related to inclusion of all pertinent industries and secondary flows; (iii) updating studies as equipment, processes and chemicals change; and (iv) tracking environmental impact data (resource and waste) throughout the supply chain and quantifying uncertainty in results.

This paper outlines a framework to address some of these life cycle assessment challenges through the use of a hybrid approach, incorporating Society for Environmental Toxicology and Chemistry (SETAC) and economic input-output strategies. The hybrid LCA approach is illustrated through a case study that applied the methodology to assess the life cycle environmental impacts of an interconnect process module in a logic device.

#### II. METHODOLOGY

#### A. Within-Fab Inventory

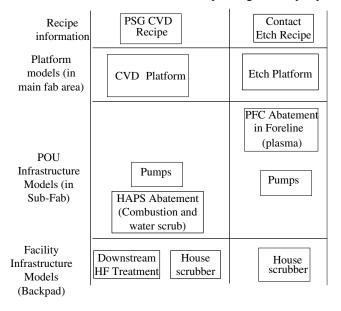

An equipment centric approach offers a convenient way to build "bottom-up" environmental analyses for the entire manufacturing facility. For the purposes of this work, four key modules are identified, each consisting of a string of process steps – Shallow Trench Isolation (STI), gate stack, via and interconnect following a methodology developed by Smati [5]. To enable this analysis, a library of equipment centric environmental process models must be constructed, with four components. These are (i) a library of recipes for individual process steps; (ii) a process tool library; (iii) a library of point of use infrastructure requirements in the subfab, such as pumps, abatement devices, monitoring equipment, gas panels, etc. and (iv) a library of facilities infrastructure.

Each equipment-based model can be instanced using different recipe data, emissions data and facility infrastructure options (pumps, abatement devices, HVAC systems, etc.) allowing a mix and match approach to develop different "bottom-up" case studies, analysis for different manufacturing operations, product types, etc (Fig 1). For individual users of this tool, such an organization offers two advantages: (i) It allows a separation of proprietary information (from recipes, for instance) from non-proprietary, generic process tools (such as facilities infrastructure), or shared information among companies and (ii) It separates databases that change rapidly (such as recipe databases or platform models) from facility infrastructure data and models that may change less rapidly.

Figure 1. Hierarchy of equipment models

Previous work in this area has involved the development of the Environmental Value Systems Analysis (EnV-S) methodology to simultaneously assess environmental cost of ownership (COO) and environmental impacts of semiconductor processing equipment [9]. The equipment and process libraries developed as a part of this work will build on the EnV-S and will be able to simultaneously assess COO and environmental inventory in semiconductor manufacturing.

#### B. Upstream Life-Cycle Inventories

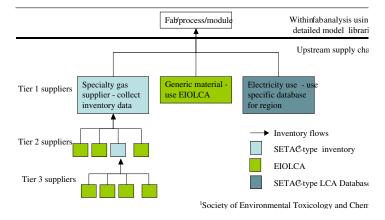

A hybrid LCA approach is then used to evaluate upstream effects (Fig 1). Such an approach involves developing detailed inventories and process models for specific items, and using a input-output LCA method for other inventory items. In this work we use an economic input-output LCA (EIO-LCA) approach developed at Carnegie Mellon [10].

In a hybrid approach, data collection efforts are streamlined because data are only collected to generate detailed life cycle inventory and impact assessments for specialty and high cost chemicals and materials used. The EIO-LCA approach is used for generic chemicals and sectors (especially generic sectors with slow process changes). Advantages of using an inputoutput approach are speed of analysis (and significantly reduced costs), circumvention of the boundary problem and availability of a wide range of environmental endpoints. Other currently available SETAC LCA databases may also be used for generic chemicals or for generic industries not adequately represented in the EIO-LCA sector divisions.

Figure 2. Hybrid LCA Approach for Semiconductor Manufacturing

#### C. General Criteria For Applying EIO-LCA Assessment

Determining the extent of detailed inventory assessment required before applying the generic EIO methodology is one of the key decisions in a hybrid LCA. Some general guidelines for performing a detailed inventory analysis, for a hybrid semiconductor LCA are below. A detailed inventory analysis could be performed for:

- i. Complex molecules

- ii. High purity materials (~>99.9%)

- iii. Materials that are not a part of the EIO-LCA mix

- iv. Materials with impacts per \$ that are significantly different from the EIO-LCA sector aggregate.

Item (v) would imply the collection of inventory data for the manufacturing of this material. If the manufacturing inventory data (normalized per \$ of output) are similar to that from the EIO-LCA assessment, then the EIO methodology could be applicable to the manufacturing of this material and to its upstream inputs.

#### III. CASE STUDY IN INTERCONNECT IMPACTS

To illustrate the methodology and some of the challenges with this hybrid LCA approach for semiconductor manufacturing, we apply this to a case study in interconnect fabrication. Interconnect refers to the metal lines that connect the transistors on a semiconductor device. In this assessment, we base our assessment on a typical state of the art microprocessor at the 130 nm node with 8 layers of copper wiring, manufactured on a 300 mm wafer.

The interconnect module is chosen for this study because (i) Significant gaseous environmental impacts, stem from etch and CVD processes [5] which occur frequently in the interconnect module; (ii) Chemical Mechanical Planarization (CMP) processes, which account for significant facility water use and liquid waste are a part of the interconnect module [11] and (iii) Each additional layer of interconnect involves a repeating of the process sequence in the previous layer. Inventory assessment can therefore be performed for a single layer and extrapolated to describe the entire module. The interconnect module could represent a sizeable fraction of overall facility impacts with a reduced analytical burden.

A bottom-up, process model approach is used to generate a life cycle inventory for the interconnect module, including the processes in Table 1. In this work, we develop inventory data for all processes except for lithography. Lithography is excluded from this assessment at this point because of scarcity of input data available to the authors.

| Step | Process                                                                       | Considered in<br>Analysis |  |

|------|-------------------------------------------------------------------------------|---------------------------|--|

| 1    | Barrier Low ktm dep                                                           | Yes                       |  |

| 2    | Dielectric Deposition                                                         | Yes                       |  |

| 3    | Trench Lithography                                                            | No                        |  |

| 4    | Trench Etch                                                                   | Yes                       |  |

| 5    | Wet Clean                                                                     | Yes                       |  |

| 6    | Via Lithography                                                               | No                        |  |

| 7    | Via Etch                                                                      | Yes                       |  |

| 8    | Wet Clean                                                                     | No                        |  |

| 9    | Deposit Titanium Liner                                                        | Yes                       |  |

| 10   | Deposit Titanium Nitride<br>Barrier                                           | Yes                       |  |

| 11   | Copper Seed Layer<br>Deposition                                               | Yes                       |  |

| 12   | Copper Electro-Chemical<br>Plating                                            | Yes                       |  |

| 13   | Copper Chemical<br>Mechanical Planarization<br>(CMP) and Post-CMP<br>cleaning | Yes                       |  |

TABLE I. PROCESS FLOW FOR COPPER INTERCONNECTS

In this work, energy used is tracked through the life cycle and is employed as the metric for interconnect impacts. Energy is often chosen as a LCA metric, because several life cycle impacts are associated with energy generation. The purpose of this work is to illustrate a methodology to perform a hybrid LCA for semiconductor fabrication. Therefore including additional metrics is beyond the scope of the current work and will be a part of future study.

A list of chemical and material inputs considered, appears in Table 2.

| GWG      | Hazardo<br>-us | Other          | VOC                    | Flamm<br>-able   | Specialty     | Generic         |

|----------|----------------|----------------|------------------------|------------------|---------------|-----------------|

| $C_2F_6$ | F <sub>2</sub> | O <sub>2</sub> | TDM<br>AT <sup>1</sup> | SiH <sub>4</sub> | CMP<br>Slurry | Electric<br>ity |

|                                               |                  |                 |                  |                | $AI_2O_3$        |         |  |

|-----------------------------------------------|------------------|-----------------|------------------|----------------|------------------|---------|--|

|                                               |                  |                 |                  |                | CMP              | Ultra   |  |

| $CH_4$                                        | HF               | Ar              | TMS <sup>2</sup> | H <sub>2</sub> | Slurry           | Pure    |  |

|                                               |                  |                 |                  |                | SiO <sub>2</sub> | Water   |  |

| NF₃                                           | SiF <sub>4</sub> | $N_2$           |                  |                | Benzotri         | City    |  |

|                                               |                  |                 |                  |                | -azole           | Water   |  |

|                                               | $C_4F_8$         | He              |                  |                | Pad              | Cooling |  |

|                                               |                  |                 |                  |                | primer           | Water   |  |

|                                               |                  | NH <sub>3</sub> |                  |                |                  |         |  |

| <sup>1</sup> tetrakis-(dimethylamido)titanium |                  |                 |                  |                |                  |         |  |

<sup>2</sup>Trimethylsilane

#### TABLE II. Key Interconnect Fabrication Inventory Items

Data for semiconductor inventory modules were gathered from three different sources - (i) estimates based on average or 'typical' recipe parameters, (ii) estimates based on averages from equipment datasheets, and (iii) other published data.

Data on chemical costs were primarily based on the price of chemicals sold to the microfabrication laboratory at the University of California at Berkeley. Utility costs were collated from data published by SEMATECH [13].

The upstream energy inventory is based on models derived from patents on record and industrial chemistry literature. Energy use is estimated from the power supplied in agitation as well as heat used in the activation of a given conversion. The best case yield is assumed, using the most preferable (efficient) method of preparation.

#### IV. SUMMARY OF CURRENT FINDINGS

We estimate the overall manufacturing-phase electricity use of the processes modeled to consume  $\sim$ 92 Kwhr/wafer, for a wafer with 8 interconnect layers. This figure is expected to be low since this work has currently not accounted for all interconnect processes (such as lithography) and associated facility infrastructure (such as HVAC systems). The overall energy consumption for semiconductor processing (excluding infrastructure) is estimated in other work to be 406 Kwhr/wafer for an 8 layer device [6].

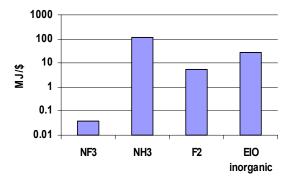

The EIO-LCA is however, not directly applicable to all semiconductor inputs. According to the criteria described in Section II C, detailed life cycle inventories must be developed for several of the chemical and materials inputs to the interconnect module. The error associated with not developing detailed inventories for specialty chemicals is illustrated through an example with  $NF_3$ .

NF<sub>3</sub> is used as a chamber cleaning gas during following the deposition of dielectric materials in interconnect. It is a specialty semiconductor chemical and is expensive, with a price range of 60-120 \$/lb based on the quantity purchased (132-264 \$/kg). In this work we use a high volume price of \$132/kg NF<sub>3</sub>. A simplified inventory assessment of the manufacturing of NF<sub>3</sub> indicates that the manufacturing of NF<sub>3</sub> uses 4.65 MJ/kg (36.6 kJ/\$) to manufacture, or 141.7 kJ/\$ along with inputs of NH<sub>3</sub> and F<sub>2</sub>. This is quite different from the EIO-LCA average number of 36.9 MJ/\$ for the manufacturing of inorganic chemicals. If inventory results for the manufacturing of NH<sub>3</sub> and F<sub>2</sub> are examined, it can be seen that they use 112.0 MJ/\$ (28 MJ/kg) and 5.2 MJ/\$ (8 MJ/kg)

respectively, which are closer to the EIO-LCA sector value of 26.2 MJ/\$ (Fig 3).

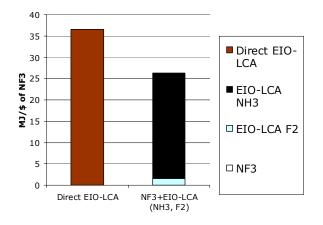

It therefore follows that it is necessary to use the data on the inventory for NF<sub>3</sub>, since its energy intensity per dollar is very different from the EIO-LCA number. This is to be expected, since NF<sub>3</sub> is a high value semiconductor chemical and has a high cost. A direct EIO-LCA analysis considering NF<sub>3</sub> as a generic inorganic chemical would therefore be expected to overestimate energy. The variation in the overall life cycle energy impacts is considered for two cases - (i) NF3 is directly input into the EIO-LCA method and (ii) first-tier inventory data for NF<sub>3</sub> is collected, and F2 and NH3 are input into the EIO-LCA method. The use of the generic EIO-LCA method for F2 and NH3 is justified because they have closer manufacturing energy intensity per dollar to the EIO sector average (Figure 3). It can be seen that, in this case, increasing inventory detail to include the manufacturing of NF<sub>3</sub> has a considerable effect on overall environmental impacts, and that the direct application of the EIO method would result in an increased life cycle energy estimate of 11.9 MJ/\$.

Figure 3. Comparison of Manufacturing Energy per Dollar for  $NF_3$ ,  $NH_3$ ,  $F_2$  and the EIO sector aggregate

Figure 4. Comparing Upstream Life Cycle Energy Consumption for NF<sub>3</sub> Using Direct EIO-LCA and a First-Tier Hybrid Approach

#### V. SUMMARY

A methodology to perform a hybrid LCA for semiconductor devices is presented. The approach involves developing detailed life cycle inventories for semiconductor processing steps, based on equipment centric models and data Life cycle inventories are also developed for specialty chemical and materials inputs to the industry. Detailed inventory results with generic chemical and material inputs are connected to an economic input-output LCA tool to evaluate overall life cycle impacts.

This approach can be used to perform a quick LCA for semiconductor manufacturing that can keep pace with the rapid rate of technology change in the industry. The approach also allows the LCA to be as comprehensive as possible, and helps avoid boundary problems.

The approach is highlighted with application in evaluating life cycle impacts of the interconnect module. Energy consumption is the metric used in this example. Results highlight the need to develop and adhere to guidelines that specify the stage at which it is acceptable to apply the EIO-LCA tool.

#### REFERENCES

- Williams E. D., Ayres R. U., Heller M., "The 1.7 Kilogram Microchip: Energy and Material Use in the Production of Semiconductor Devices," Environmental Science and Technology, Vol.36 (24), pp. 5504-5510, Dec 15, 2002.

- [2] S. Hermanns, "Using the LCA Method for Identifying Resource Conservation Priorities at AMD Saxony," NSF/SRC Center for Environmentally Benign Semiconductor Manufacturing Tele-Seminar, November 2002.

- [3] K. Schischke, M. Stutz, J. P. Ruelle, H. Griese, H. Reichl, "Life Cycle Inventory Analysis and Identification of Environmentally Significant Aspects in Semiconductor Manufacturing," IEEE Symposium on Electronics and the Environment, pp. 145-150, 2001.

- [4] F. Taiariol, P. Fea, C. Papuzza, R. Casalino, E. Galbiati, S. Zappa, "Life Cycle Assessment of an Integrated Circuit Product," IEEE Symposium on Electronics and the Environment, pp. 128-133, 2001.

- [5] Smati, R., Raoux, S., Ho, D., Woolston, M. 2002, "Measuring and modeling gas consumption and emis-sions from semiconductor manufacturing processes," EHS Assessment Techniques, SEMICON West.

- [6] Murphy C. F., Kenig G. A., Allen D. T., Laurent J-P., Dyer D. E., "Development of Parametric Material, Energy, and Emission Inventories for Wafer Fabrication in the Semiconductor Industry," Environmental Science & Technology, Vol. 37 (23), pp. 5373-5382, 2003.

- [7] Murphy C. F., Laurent J-P, Allen D. T., "Life Cycle Inventory Development for Wafer Fabrication in Semiconductor Manufacturing," Proceedings IEEE Electronics and the Environment, pp. 276-281, 2003.

- [8] N. Krishnan, S. Thurwachter, T. Francis, P. Sheng, "A Modular Environmental Design and Decision-Support Tool (EDDT) for Semiconductor Manufacturing," Proceedings From SEMICON West Improving Environmental Performance of Wafer Manufacturing Processes, 2000.

- [9] Krishnan N., Design for Environment in Semiconductor Manufacturing, Ph.D. Dissertation, University of California, Berkeley, 2003.

- [10] Hendrickson C., Horvath A., Joshi S., Lave L., "Economic Input-Output Models For Environmental Life-Cycle Assessment," Environmental Science & Technology. 32(7):A 184-A 191, 1998 Apr 1.

- [11] International Technology Roadmap for Semiconductors (ITRS), Interconnect, 2001 Edition.

- [12] Maag, B., Boning, D., Voelker, B., "Assessing the Environmental Impact of Copper CMP," Semiconductor International. October 2000.

[13] "Fab Utility Cost Values for Cost of Ownership (COO) Calculations,"

0-7803-8250-1/04/\$20.00 © 2004 IEEE.

90