## UC San Diego UC San Diego Electronic Theses and Dissertations

### Title

Towards A Private New World: Algorithm, Protocol, and Hardware Co-Design for Large-Scale Secure Computation

**Permalink** https://escholarship.org/uc/item/81j8r6zh

Author Riazi, Mohammad Sadegh

Publication Date 2020

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

#### Towards A Private New World: Algorithm, Protocol, and Hardware Co-Design for Large-Scale Secure Computation

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Computer Engineering)

by

M. Sadegh Riazi

Committee in charge:

Professor Farinaz Koushanfar, Chair Professor Tara Javidi Professor Andrew B. Kahng Professor Ryan Kastner Professor Truong Nguyen

2020

Copyright M. Sadegh Riazi, 2020 All rights reserved. The dissertation of M. Sadegh Riazi is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California San Diego

2020

## DEDICATION

To my beloved wife, my lovely sister, and my dear parents.

### EPIGRAPH

"Any sufficiently advanced technology is indistinguishable from magic." —Arthur C. Clarke

### TABLE OF CONTENTS

| Signature Pa  | ige .                      | iii                                                                                                                                                                                                                                      |

|---------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication .  |                            | iv                                                                                                                                                                                                                                       |

| Epigraph      |                            |                                                                                                                                                                                                                                          |

| Table of Cor  | ntents                     | vi                                                                                                                                                                                                                                       |

| List of Figur | res                        | xi                                                                                                                                                                                                                                       |

| List of Table | es                         | xiii                                                                                                                                                                                                                                     |

| Acknowledg    | gements                    | xv                                                                                                                                                                                                                                       |

| Vita          |                            | xviii                                                                                                                                                                                                                                    |

| Abstract of t | he Diss                    | sertation                                                                                                                                                                                                                                |

| Chapter 1     | Intro<br>1.1<br>1.2<br>1.3 | oduction       1         Mixed-Protocol Secure Computation Framework for Machine Learning       2         Neural Network Transforming for Secure Computation       3         High-Performance Hardware Architecture for Computing on En- |

|               |                            | crypted Data                                                                                                                                                                                                                             |

|               | 1.4<br>1.5                 | Compact Circuit Representation for Secure Computation7Efficient Search on Private Data8                                                                                                                                                  |

|               | 1.5                        | Secure Content-Addressable Memory                                                                                                                                                                                                        |

|               | 1.0                        | Synthetic Human Fingerprints    10                                                                                                                                                                                                       |

|               | 1.7                        | Impact         12                                                                                                                                                                                                                        |

|               | 1.9                        | Acknowledgements    12                                                                                                                                                                                                                   |

| Chapter 2     | Bacl                       | kground                                                                                                                                                                                                                                  |

|               | 2.1                        | Cryptographic Protocols                                                                                                                                                                                                                  |

|               |                            | 2.1.1 Oblivious Transfer Protocol                                                                                                                                                                                                        |

|               |                            | 2.1.2 Garbled Circuit Protocol                                                                                                                                                                                                           |

|               |                            | 2.1.3 GMW Protocol                                                                                                                                                                                                                       |

|               |                            | 2.1.4 BMR Protocol                                                                                                                                                                                                                       |

|               |                            | 2.1.5 Additive Secret Sharing                                                                                                                                                                                                            |

|               | 2.2                        | CKKS Fully Homomorphic Encryption Scheme                                                                                                                                                                                                 |

|               | 2.3                        | Deep Neural Networks                                                                                                                                                                                                                     |

|               | <b>a</b> 4                 | 2.3.1 Generative Adversarial Networks                                                                                                                                                                                                    |

|               | 2.4                        | Human Fingerprints   25                                                                                                                                                                                                                  |

|               | 2.5                        | Sub-String Search Algorithms                                                                                                                                                                                                             |

|           | 2.6 | Content-Addressable Memory                                         | 26       |

|-----------|-----|--------------------------------------------------------------------|----------|

|           | 2.7 | Approximate Search                                                 | 27       |

|           | 2.8 | Acknowledgements                                                   | 30       |

|           |     |                                                                    |          |

| Chapter 3 |     | meleon: Mixed-Protocol Secure Computation Framework for Machine    |          |

|           |     | ning                                                               | 32       |

|           | 3.1 | Introduction                                                       | 33       |

|           | 3.2 | Related Work                                                       | 37       |

|           | 3.3 | The Chameleon Framework                                            | 40       |

|           |     | 3.3.1 Chameleon Online Execution Flow                              | 41       |

|           |     | 3.3.2 Security Model                                               | 43       |

|           |     | 3.3.3 Semi-honest Third Party (STP)                                | 43       |

|           | 3.4 | Chameleon Design and Implementation                                | 44       |

|           |     | 3.4.1 GC and GMW Engines                                           | 44       |

|           |     | 3.4.2 A-SS Engine                                                  | 45       |

|           |     | 3.4.3 Supporting Signed Fixed-point Numbers                        | 48       |

|           |     | 3.4.4 Generating Multiplication Triples                            | 51       |

|           |     | 3.4.5 Fast STP-aided Oblivious Transfer                            | 52       |

|           |     | 3.4.6 Security                                                     | 53       |

|           | 3.5 | Experimental Results                                               | 53       |

|           | 3.6 | Summary                                                            | 54       |

|           | 3.7 | Acknowledgements                                                   | 55       |

|           | 5.7 |                                                                    | 00       |

| Chapter 4 | XON | N: Efficient Neural Network Transformation for Oblivious Inference | 56       |

| -         | 4.1 | Introduction                                                       | 57       |

|           | 4.2 | Related Work                                                       | 60       |

|           | 4.3 | Circuit Privacy                                                    | 63       |

|           | 4.4 | The XONN Framework                                                 | 65       |

|           |     | 4.4.1 Customized Network Binarization                              | 65       |

|           |     | 4.4.2 Oblivious Inference                                          | 68       |

|           |     | 4.4.3 Oblivious Conditional Addition Protocol                      | 72       |

|           |     | 4.4.4 Security of XONN                                             | 75       |

|           | 4.5 | The XONN Implementation                                            | 77       |

|           | 1.0 | 4.5.1 Modular Circuit Synthesis and Garbling                       | 80       |

|           |     | 4.5.2 Application Programming Interface (API)                      | 81       |

|           | 4.6 | Attacks on Deep Neural Networks                                    | 82       |

|           | 4.7 | Experimental Results                                               | 84       |

|           | 4.7 | 4.7.1 Evaluation on MNIST                                          | 84       |

|           |     | 4.7.1 Evaluation on VIVIST                                         | 87       |

|           |     |                                                                    | 87<br>89 |

|           |     |                                                                    |          |

|           |     | 4.7.4 Network Trimming Examples                                    | 90<br>01 |

|           | 4.0 | 4.7.5 Accuracy, Runtime, and Communication                         | 91<br>02 |

|           | 4.8 | Summary                                                            | 92       |

|           | 4.9 | Acknowledgements                                                                                |

|-----------|-----|-------------------------------------------------------------------------------------------------|

| Chapter 5 | HEA | X: High-Performance Hardware Architecture for Computing on En-                                  |

| 1         |     | ted Data                                                                                        |

|           | 5.1 | Introduction                                                                                    |

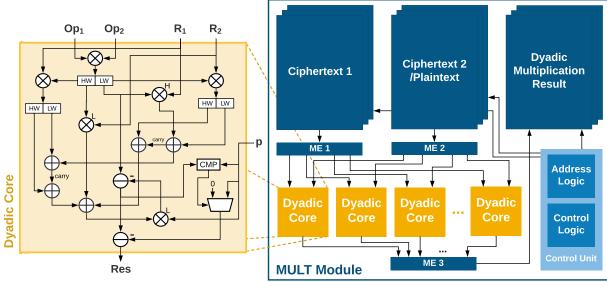

|           | 5.2 | MULT Module                                                                                     |

|           |     | 5.2.1 Homomorphic Multiplication Algorithm                                                      |

|           |     | 5.2.2 HEAX Word Size and Native Operations                                                      |

|           |     | 5.2.3 MULT Architecture                                                                         |

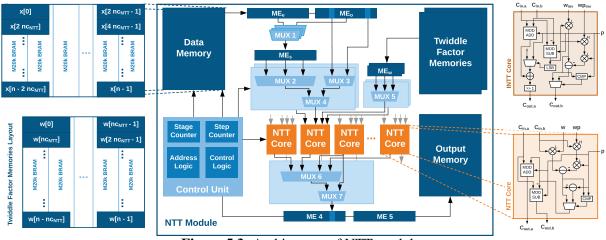

|           | 5.3 | NTT Module                                                                                      |

|           |     | 5.3.1 Algorithms                                                                                |

|           |     | 5.3.2 NTT Architecture                                                                          |

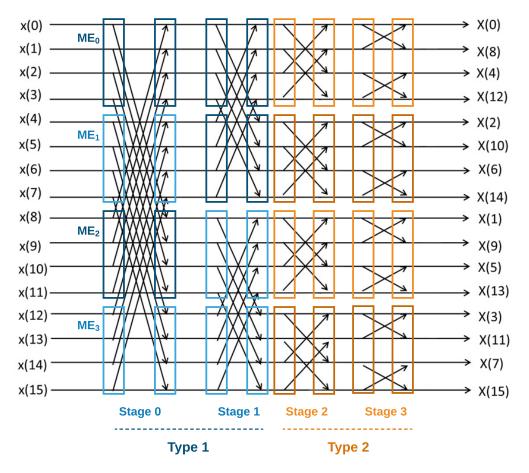

|           |     | 5.3.3 Access Pattern                                                                            |

|           |     | 5.3.4 Reordering Coefficients and Optimal MUXs 105                                              |

|           |     | 5.3.5 NTT High-Level Pipeline                                                                   |

|           |     | 5.3.6 Memory Utilization and Word-Packing                                                       |

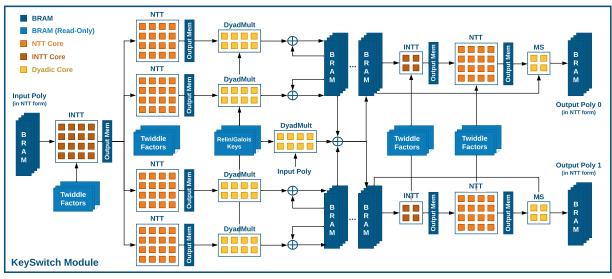

|           | 5.4 | KeySwitch Module                                                                                |

|           |     | 5.4.1 Algorithm                                                                                 |

|           |     | 5.4.2 KeySwitch Architecture                                                                    |

|           |     | 5.4.3 Balancing Throughput                                                                      |

|           |     | 5.4.4 KeySwitch Ops. and Synchronization                                                        |

|           | 5.5 | System View and Data Flow                                                                       |

|           |     | 5.5.1 On-Chip vs. Off-Chip Memory Accesses                                                      |

|           |     | 5.5.2 Data Transfer on PCIe                                                                     |

|           | 5.6 | Implementation and Experiments                                                                  |

|           |     | 5.6.1 Experimental Setup                                                                        |

|           |     | 5.6.2 FHE Parameters and Security Guarantees                                                    |

|           |     | 5.6.3 Resource Consumption                                                                      |

|           |     | 5.6.4 Performance                                                                               |

|           | 5.7 | Related Work                                                                                    |

|           | 5.8 | Summary                                                                                         |

|           | 5.9 | Acknowledgements                                                                                |

|           |     |                                                                                                 |

| Chapter 6 |     | Circuits: Compact Boolean Circuits for Secure Multiparty Computation 127                        |

|           | 6.1 | Introduction                                                                                    |

|           | 6.2 | Automated Circuit Generation                                                                    |

|           | 6.3 | Methodology                                                                                     |

|           | 6.4 | Auction                                                                                         |

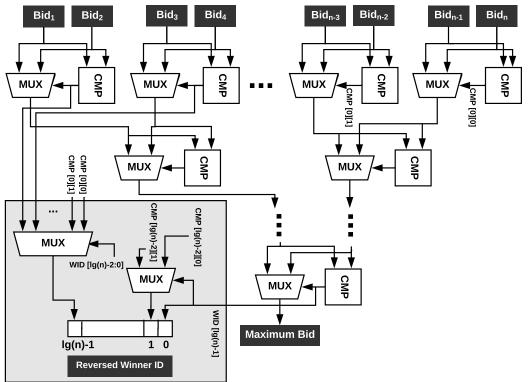

|           | (5  | $6.4.1  \text{Circuit Design}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

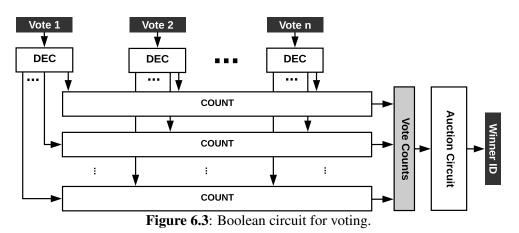

|           | 6.5 | Voting         136           (51)         Cinquit Design                                        |

|           | 6.6 | 6.5.1 Circuit Design                                                                            |

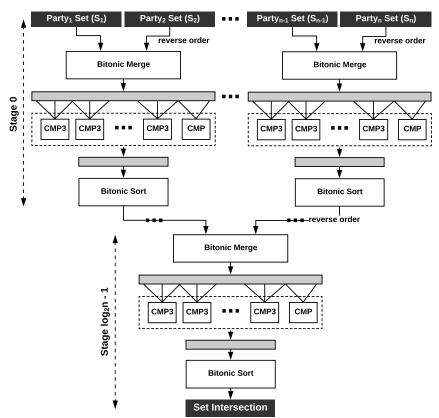

|           | 6.6 | Set Intersection                                                                                |

|           |     | 6.6.1 Circuit Design                                                                            |

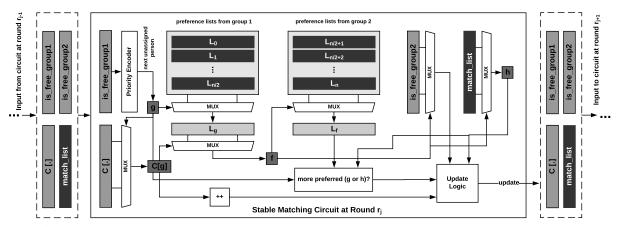

|           | 6.7   | Stable Matching                                                                   |

|-----------|-------|-----------------------------------------------------------------------------------|

|           |       | 6.7.1 Circuit Design                                                              |

|           | 6.8   | Nearest-Neighbor Search (NNS)                                                     |

|           |       | 6.8.1 Circuit Design                                                              |

|           | 6.9   | Experimental Results and Related Work                                             |

|           |       | 6.9.1 Experimental Setup                                                          |

|           |       | 6.9.2 Auction                                                                     |

|           |       | 6.9.3 Voting                                                                      |

|           |       | 6.9.4 Private Set Intersection                                                    |

|           |       | 6.9.5 Stable Matching 151                                                         |

|           |       | 6.9.6 Nearest-Neighbor Search                                                     |

|           |       | 6.9.7 Scaling Up Circuit Generation                                               |

|           | 6.10  | Summary                                                                           |

|           | 6.11  | Acknowledgements                                                                  |

|           |       |                                                                                   |

| Chapter 7 | PriSe | earch: Privacy-Preserving Text Search                                             |

|           | 7.1   | Introduction                                                                      |

|           | 7.2   | PriSearch                                                                         |

|           |       | 7.2.1 String Search Algorithms                                                    |

|           |       | 7.2.2 String Search in GC                                                         |

|           |       | 7.2.3 PriSearch Algorithm                                                         |

|           |       | 7.2.4 Different Variants of PriSearch                                             |

|           |       | 7.2.5 Security of PriSearch                                                       |

|           | 7.3   | Results 166                                                                       |

|           | 7.4   | Related Work and Comparison                                                       |

|           | 7.5   | Summary 169                                                                       |

|           | 7.6   | Acknowledgements                                                                  |

| Chanton 9 | CAN   | Asura, Saaura Contant, Addressable Mamary 170                                     |

| Chapter 8 | 8.1   | Isure: Secure Content-Addressable Memory       170         Introduction       171 |

|           | 8.2   |                                                                                   |

|           | 0.2   | Methodology1738.2.1Scenario and Privacy Concerns173                               |

|           |       | •                                                                                 |

|           |       |                                                                                   |

|           |       | 6 6                                                                               |

|           |       | 0                                                                                 |

|           |       |                                                                                   |

|           | 0.2   | 8.2.6 Approximate Search in CAMs                                                  |

|           | 8.3   | Analyses         182           8.2.1         Delemend Frames Analysis             |

|           |       | 8.3.1 Delay and Energy Analysis                                                   |

|           |       | 8.3.2 Delay Analysis                                                              |

|           |       | 8.3.3 Energy Analysis                                                             |

|           |       | 8.3.4 Accuracy Analysis                                                           |

|           |       | 8.3.5 Security Analysis                                                           |

|              |      | 8.3.6 Compressed Sensing                                       | ) |

|--------------|------|----------------------------------------------------------------|---|

|              |      | 8.3.7 Brute-force Attack                                       | ) |

|              |      | 8.3.8 Validating the LSH Transformation                        | ) |

|              |      | 8.3.9 Triangulation Attack                                     | 1 |

|              | 8.4  | Related Work                                                   | 2 |

|              | 8.5  | Summary                                                        | 5 |

|              | 8.6  | Acknowledgements                                               | 5 |

| Chapter 9    | Synł | Fi: Synthetic Human Fingerprints                               | 5 |

|              | 9.1  | Introduction                                                   | 5 |

|              | 9.2  | Prior Art                                                      | ) |

|              | 9.3  | Methodology                                                    | ) |

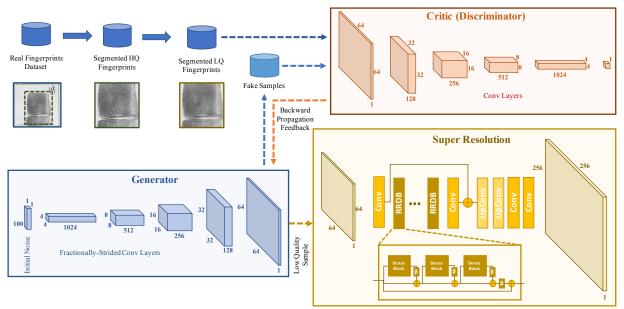

|              |      | 9.3.1 Pre-processing Phase: Fingerprint Segmentation 201       | 1 |

|              |      | 9.3.2 Phase 1: Generating Synthetic Fingerprints using GAN 202 | 2 |

|              |      | 9.3.3 Phase 2: Generalization to High-Quality Images 204       | 4 |

|              | 9.4  | Experimental Results                                           | 5 |

|              |      | 9.4.1 Computational Environment                                | 5 |

|              |      | 9.4.2 Pre-processing Dataset                                   | 7 |

|              |      | 9.4.3 Architectures                                            | 7 |

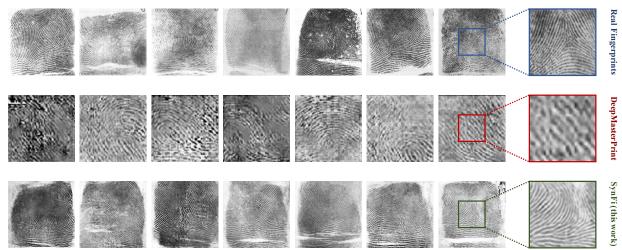

|              |      | 9.4.4 Synthetic Samples and Qualitative Comparison 207         | 7 |

|              |      | 9.4.5 Indistinguishability and Quantitative Comparison 208     | 3 |

|              | 9.5  | Summary                                                        | ) |

|              | 9.6  | Acknowledgements                                               | 1 |

| Chapter 10   | Futu | re Research Directions                                         | 2 |

| Appendix A   | Netv | work Network Architectures in XONN                             | 4 |

| - *          | A.1  | Acknowledgements                                               | 5 |

| Bibliography |      |                                                                | 2 |

### LIST OF FIGURES

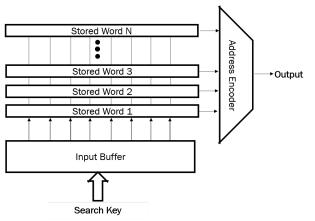

| Figure 2.1:  | Schematic view of Content Addressable Memory (CAM)                                                | 27  |

|--------------|---------------------------------------------------------------------------------------------------|-----|

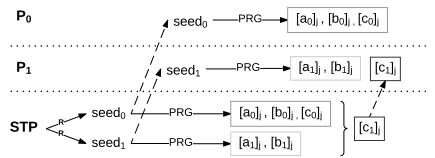

| Figure 3.1:  | Seed expansion process to precompute A-MTs/B-MTs with low communica-                              |     |

|              | tion                                                                                              | 52  |

| Figure 3.2:  | Beaver's OT precomputation protocol [Bea95]                                                       | 52  |

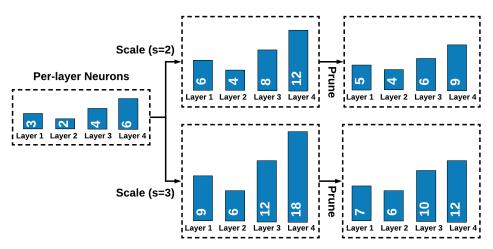

| Figure 4.1:  | Illustration of BNN customization. The bars represent the number of neurons in each hidden layer. | 66  |

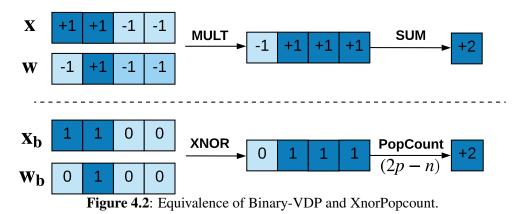

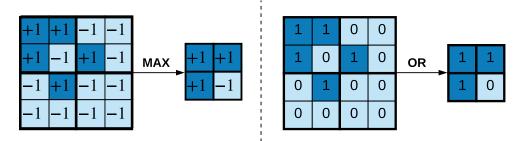

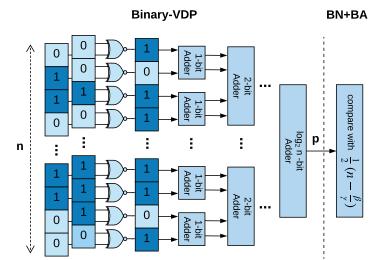

| Figure 4.2:  | Equivalence of Binary-VDP and XnorPopcount.                                                       | 70  |

| Figure 4.3:  | The equivalence between Max-Pooling and Boolean-OR operations in BNNs.                            | 71  |

| Figure 4.4:  | Circuit for binary-VDP followed by comparison for batch normalization (BN)                        |     |

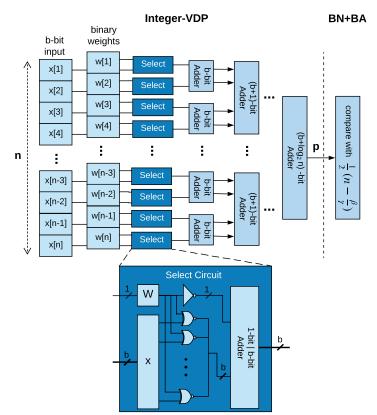

|              | and binary activation (BA).                                                                       | 71  |

| Figure 4.5:  | Circuit for Integer-VDP followed by comparison for batch normalization                            |     |

|              | (BN) and binary activation (BN)                                                                   | 72  |

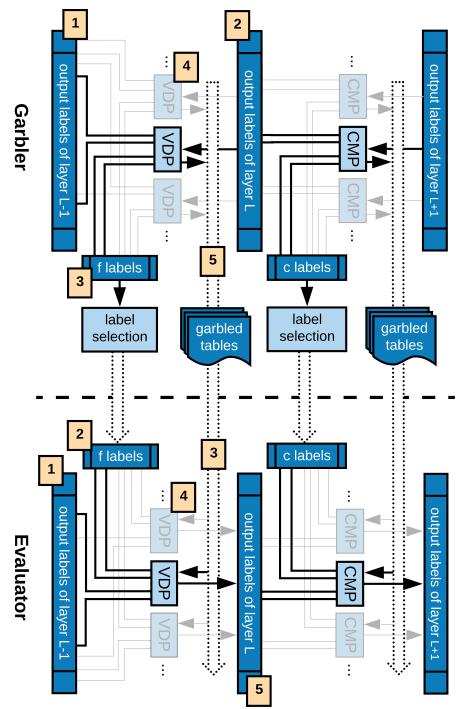

| Figure 4.6:  | Oblivious Conditional Addition (OCA) protocol.                                                    | 73  |

| Figure 4.7:  | XONN modular and pipelined garbling engine.                                                       | 79  |

| Figure 4.8:  | Sample snippet code in XONN                                                                       | 81  |

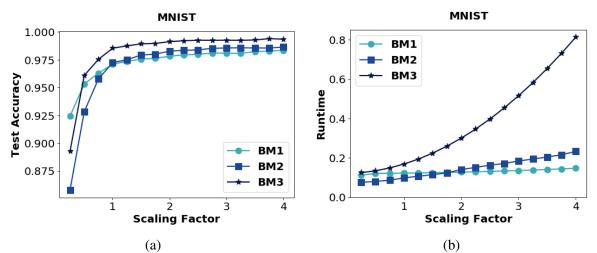

| Figure 4.9:  | Effect of scaling factor on (a) accuracy and (b) inference runtime of MNIST                       |     |

|              | networks. No pruning was applied in this evaluation.                                              | 85  |

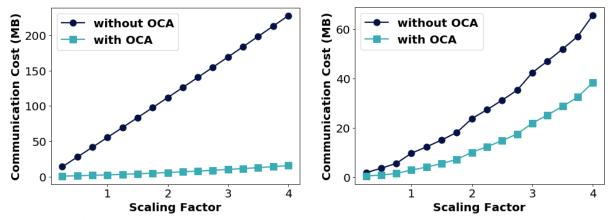

| Figure 4.10: | Effect of OCA on the communication of the BM1 (left) and BM2 (right) net-                         |     |

|              | works for different scaling factors. No pruning was applied in this evaluation.                   | 86  |

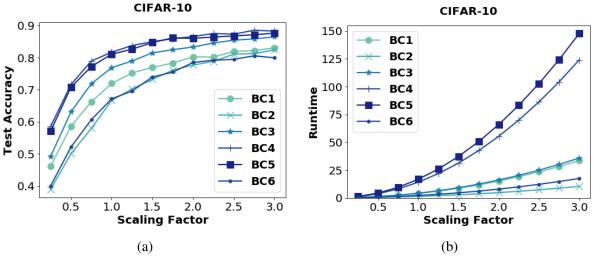

| Figure 4.11: | (a) Effect of scaling factor on accuracy for CIFAR-10 networks. (b) Effect of                     |     |

|              | scaling factor on runtime. No pruning was applied in this evaluation                              | 88  |

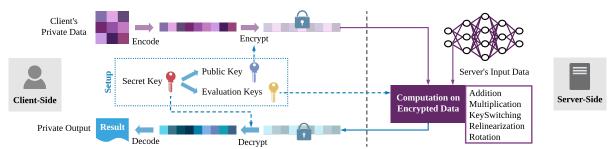

| Figure 5.1:  | The data flow of an end-to-end encrypted computation based on homomor-                            |     |

|              | phic encryption.                                                                                  | 95  |

| Figure 5.2:  | Architecture of MULT module.                                                                      | 100 |

| Figure 5.3:  | Architecture of NTT module.                                                                       | 104 |

| Figure 5.4:  | Access pattern of Type 1 and Type 2 stages in NTT                                                 | 106 |

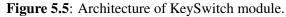

| Figure 5.5:  | Architecture of KeySwitch module.                                                                 | 110 |

| Figure 5.6:  |                                                                                                   | 114 |

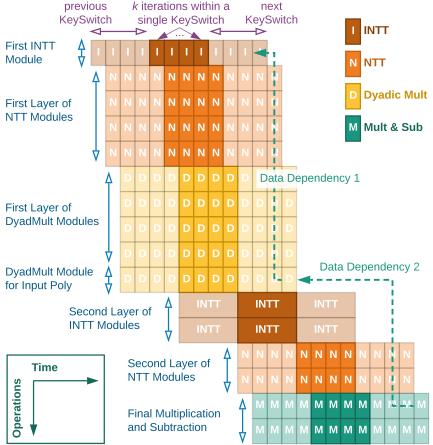

| Figure 5.7:  | System-view of HEAX.                                                                              | 115 |

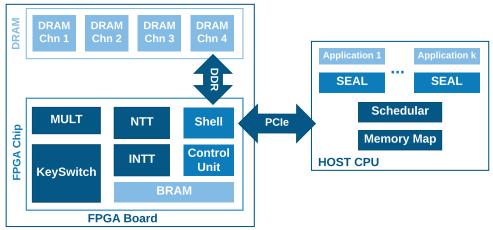

| Figure 6.1:  | Global flow of MPCircuits circuit generation.                                                     | 131 |

| Figure 6.2:  | Boolean circuit for auction.                                                                      | 136 |

| Figure 6.3:  | Boolean circuit for voting.                                                                       | 137 |

| Figure 6.4:  | High-level circuit description of the Sort-Merge-Compare-Shuffle for Private                      |     |

|              | Set Intersection. Three operations are performed at each stage: merge,                            |     |

|              | compare, and sort.                                                                                | 139 |

| Figure 6.5:  | The circuit for stable matching unrolled for round $r_j$ . The circuit takes as                   |     |

|              | input the intermediate values from previous round $r_{j-1}$ , processes the current               |     |

|              | round based on the preference lists, and outputs the updated values                               | 143 |

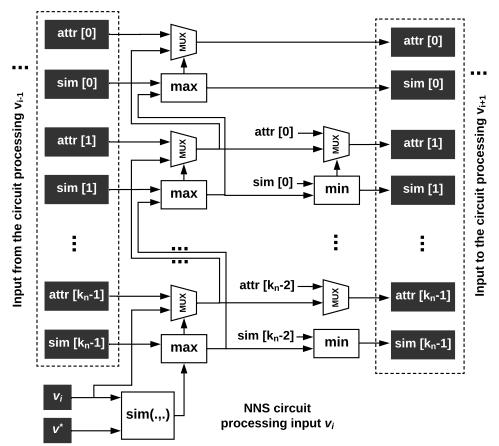

| Figure 6.6:   | The circuit of the Nearest-Neighbors Search (NNS) that finds the $k_n$ most similar attributes to $v^*$ . In the experimental results, the circuit is unrolled for                                                                                   |       |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|               | <i>n</i> times                                                                                                                                                                                                                                       | 147   |

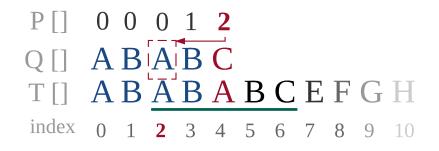

| Figure 7.1:   | Illustration of steps in PriSearch algorithm.                                                                                                                                                                                                        | 164   |

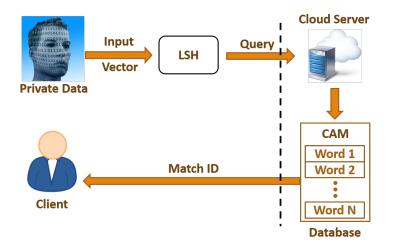

| Figure 8.1:   | Overview of the secure approximate search scenario using CAMsure                                                                                                                                                                                     | 175   |

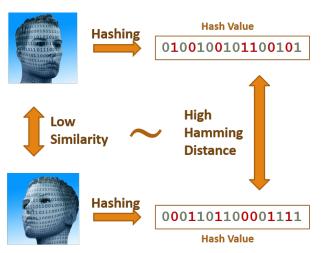

| Figure 8.2:   | Relationship between the data and hash domains. The hashing scheme preserves the proximity of inputs only for similar data.                                                                                                                          | 177   |

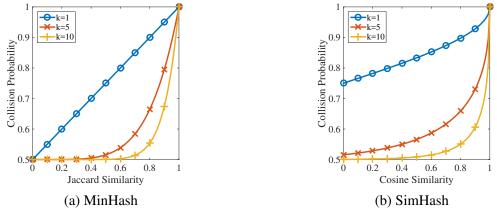

| Figure 8.3:   | Collision probability vs. similarity for MinHash and SimHash functions for three different security parameters $k \in \{1, 5, 10\}$ . $k = 1$ represents traditional                                                                                 |       |

|               | LSH methods. $\ldots$                                                                                                                                                                                                                                | 180   |

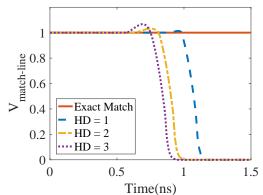

| Figure 8.4:   | CAM match-line transient output voltage for exact and approximate matching                                                                                                                                                                           | g.183 |

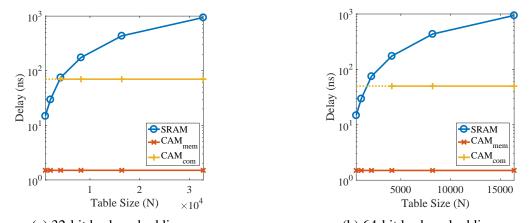

| Figure 8.5:   | Delay analysis for hash embeddings of size 32 and 64-bit. $CAM_{mem}$ and $CAM_{mem}$ denote memorial CMOS based CAMe respectively.                                                                                                                  |       |

|               | $CAM_{com}$ denote memristive and commercial CMOS-based CAMs, respectively. The dotted line for $CAM_{com}$ shows interpolated data.                                                                                                                 | 185   |

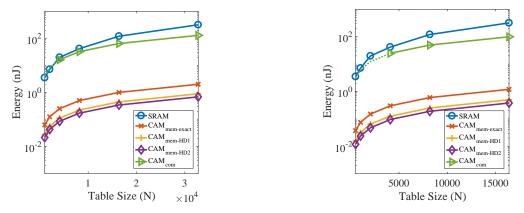

| Figure 8.6:   | Energy consumption analysis for hash embeddings of size 32 and 64-bit and                                                                                                                                                                            | 100   |

| -             | different Hamming distances. $CAM_{mem}$ and $CAM_{com}$ denote memristive and                                                                                                                                                                       |       |

|               | commercial CMOS-based CAMs, respectively. The dotted line for $CAM_{com}$                                                                                                                                                                            | 106   |

| Eigung 97.    | shows interpolated data.                                                                                                                                                                                                                             | 186   |

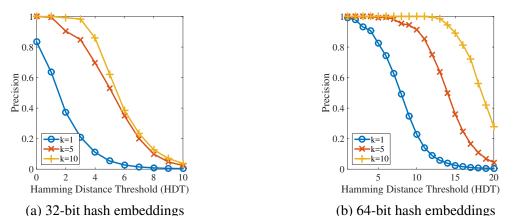

| Figure 8.7:   | Precision analysis for hash embeddings of size 32 and 64-bit for different security parameters $(k)$ .                                                                                                                                               | 187   |

| Figure 8.8:   | Recall analysis for hash embeddings of size 32 and 64-bit for different                                                                                                                                                                              | 107   |

| -             | security parameters $(k)$                                                                                                                                                                                                                            | 188   |

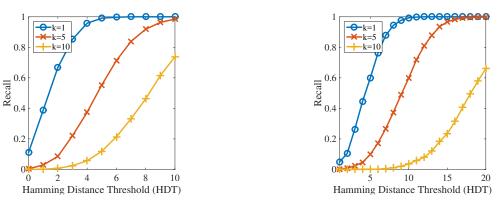

| Figure 8.9:   | Precision vs. Recall analysis of 32 and 64-bit hash embeddings for different                                                                                                                                                                         | 100   |

| E. aura 9 10. | security parameters (k).                                                                                                                                                                                                                             | 189   |

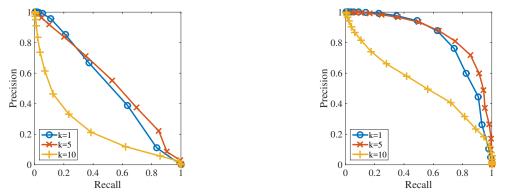

| Figure 8.10:  | Validating LSH transformation in practice on Speed-Dating dataset for security parameter $k = 5$ .                                                                                                                                                   | 191   |

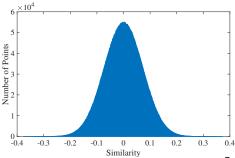

| Figure 8.11:  | Histogram of pairwise similarities between $p$ and $10^7$ randomly selected                                                                                                                                                                          | 171   |

| U             | points in 190-dimensional space.                                                                                                                                                                                                                     | 192   |

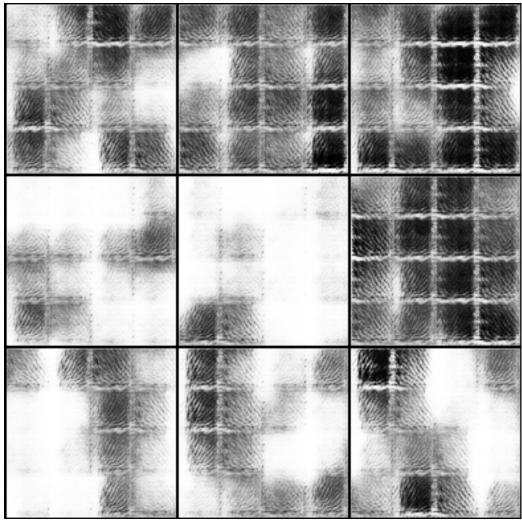

| Figure 9.1:   | The result of generating $256 \times 256$ pixel images using GAN                                                                                                                                                                                     | 201   |

| Figure 9.2:   | Overall design of SynFi for training (building the system) and execution                                                                                                                                                                             |       |

| <b>D'</b> 0.2 | (generating synthetic samples).                                                                                                                                                                                                                      | 202   |

| Figure 9.3:   | Quality comparison between real and synthetic fingerprint samples. <i>Top row:</i> NIST dataset real fingerprint samples. <i>Middle row:</i> Synthetic fingerprints generated by DeepMasterPrint [BRT <sup>+</sup> 18]. <i>Bottom row:</i> Synthetic |       |

|               | fingerprints generated by SynFi (this work)                                                                                                                                                                                                          | 206   |

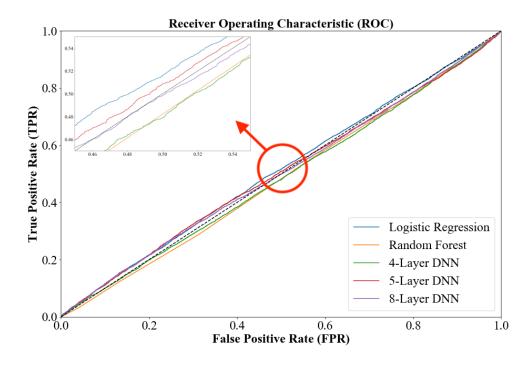

| Figure 9.4:   | The ROC curve of five different machine learning models in distinguishing                                                                                                                                                                            | _00   |

|               | real fingerprints from synthetic ones generated by SynFi                                                                                                                                                                                             | 210   |

#### LIST OF TABLES

| Table 3.1:  | Summary of properties of the Du-Atallah multiplication protocol and the protocol based on Multiplication Triples.                                                                                                          | 47  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.1:  | High-Level Comparison of oblivious inference frameworks. "C"onstant round complexity. "D"eep learning/secure computation co-design. "I"ndependence of secondary server. "U"pgradeable to malicious security using standard |     |

|             | solutions. "S"upporting any non-linear layer.                                                                                                                                                                              | 63  |

| Table 4.2:  | Computation and communication cost of OCA.                                                                                                                                                                                 | 75  |

| Table 4.3:  | Summary of the trained binary network architectures evaluated on the MNIST                                                                                                                                                 |     |

|             | dataset. Detailed descriptions are available in Appendix A, Table A.1.                                                                                                                                                     | 85  |

| Table 4.4:  | Comparison of XONN with the state-of-the-art for the MNIST network archi-                                                                                                                                                  |     |

|             | tectures.                                                                                                                                                                                                                  | 87  |

| Table 4.5:  | Summary of the trained binary network architectures evaluated on the CIFAR-                                                                                                                                                |     |

|             | 10 dataset                                                                                                                                                                                                                 | 88  |

| Table 4.6:  | Comparison of XONN with prior art on CIFAR-10                                                                                                                                                                              | 89  |

| Table 4.7:  | Summary of medical application benchmarks.                                                                                                                                                                                 | 90  |

| Table 4.8:  | Runtime, communication cost (Comm.), and accuracy (Acc.) for medical                                                                                                                                                       |     |

|             | benchmarks                                                                                                                                                                                                                 | 90  |

| Table 4.9:  | Trimming MNIST architectures.                                                                                                                                                                                              | 90  |

| Table 4.10: | Trimming the BC2 network for CIFAR-10                                                                                                                                                                                      | 91  |

| Table 4.11: | Accuracy (Acc.), communication (Comm.), and latency (Lat.) for MNIST                                                                                                                                                       |     |

|             | dataset. Channel/neuron trimming is not applied                                                                                                                                                                            | 91  |

| Table 4.12: | Accuracy (Acc.), communication (Comm.), and latency (Lat.) for CIFAR-10                                                                                                                                                    |     |

|             | dataset. Channel/neuron trimming is not applied                                                                                                                                                                            | 92  |

| Table 5.1:  | Summary of FPGA boards' specifications.                                                                                                                                                                                    | 118 |

| Table 5.2:  | The HE parameter sets used in this work. $n$ is the ciphertext polynomial size,                                                                                                                                            |     |

|             | qp is the ciphertext modulus, and k is the number of RNS components of q.                                                                                                                                                  | 119 |

| Table 5.3:  | Resource consumption of each computation core                                                                                                                                                                              | 119 |

| Table 5.5:  | KeySwitch architecture for different HE parameter sets                                                                                                                                                                     | 120 |

| Table 5.6:  | Resource consumption of HEAX for different HE parameter sets                                                                                                                                                               | 120 |

| Table 5.7:  | Performance comparison of HEAX with CPU. Number of operations per                                                                                                                                                          |     |

|             | second for CKKS <i>low-level</i> operations                                                                                                                                                                                | 120 |

| Table 5.4:  | Resource consumption of basic modules                                                                                                                                                                                      | 120 |

| Table 5.8:  | Performance comparison of HEAX with CPU. Number of operations per                                                                                                                                                          |     |

|             | second for CKKS <i>high-level</i> operations.                                                                                                                                                                              | 121 |

| Table 5.9:  | Performance comparison (operations per second) of HEAX with NVIDIA GPUs for NTT computation.                                                                                                                               | 122 |

| Table 6.1:  | Secure Auction.                                                                                                                                                                                                            | 149 |

| Table 6.2:  | Secure Voting.                                                                                                                                                                                                             | 150 |

| Table 6.3:        | Private set intersection (Bitwise-AND variant).                                                         | 151 |

|-------------------|---------------------------------------------------------------------------------------------------------|-----|

| Table 6.4:        | Private set intersection (SMCS variant).                                                                | 151 |

| Table 6.5:        | Secure stable matching                                                                                  | 152 |

| Table 6.6:        | Secure k-nearest neighbor search.                                                                       | 153 |

| Table 6.7:        | Circuit generation for higher number of participants in secure auction                                  | 153 |

| Table 6.8:        | Circuit generation for higher number of participants in the secure $k_n$ -NNS                           |     |

|                   | search when $b = 32$ .                                                                                  | 154 |

| Table 7.1:        | Summary of characteristics for different string search algorithms                                       | 160 |

| Table 7.2:        | Summary of different algorithms for string search and their complexity; $R =  \Sigma $                  |     |

|                   | $ \Sigma $ , <i>n</i> is the number of characters in the text, and <i>m</i> is the number of characters |     |

|                   | in the query. The missing complexities in the fifth column means utilizing                              | 171 |

| $T_{a}$ h la 7 2. | ORAM does not improve the performance                                                                   | 161 |

| Table 7.3:        | Timing and communication results for different benchmarks                                               | 167 |

| Table 8.1:        | Cache design for the RAM baseline.                                                                      | 183 |

| Table 8.2:        | Specifications of CAM baselines.                                                                        | 184 |

| <b>T</b> 11 0 1   |                                                                                                         |     |

| Table 9.1:        | Analyzing indistinguishability of synthetic fingerprints against the real ones                          | 200 |

|                   | using various machine learning models                                                                   | 209 |

| Table A.1:        | Evaluated neural network architectures on MNIST dataset.                                                | 214 |

| Table A.2:        | Evaluated neural network architectures for CIFAR-10 dataset.                                            | 216 |

| Table A.3:        | Evaluated neural network architectures for CIFAR-10 dataset (BC3 and BC4                                |     |

|                   | networks).                                                                                              | 217 |

| Table A.4:        | Evaluated neural network architectures for CIFAR-10 dataset (BC4 network).                              | 218 |

| Table A.5:        | Evaluated neural network architectures for CIFAR-10 dataset (BC5 network).                              | 219 |

| Table A.6:        | Evaluated neural network architectures for CIFAR-10 dataset (BC6 network).                              | 220 |

| Table A.7:        | Evaluated neural network architectures for medical datasets.                                            | 221 |

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank my Ph.D. advisor, Professor Farinaz Koushanfar, for her genuine support, unconditional care, and invaluable guidance and help.

I would like to thank my committee members, Professor Tara Javidi, Professor Truong Nguyen, Professor Andrew B. Kahng, and Professor Ryan Kastner for their valuable suggestions and advice during my doctoral study. I want to express my gratitude to my mentors at Microsoft Research, Dr. Kristin Lauter and Dr. Kim Laine for their unequivocal support and guidance which enabled me to work on the cutting-edge technologies. I was fortunate to work with and learn from Professor Ahmad-Reza Sadeghi, Professor Ari Juels, Professor Thomas Schneider, Professor Tajana Rosing.

I am grateful to have worked with several brilliant researchers. In particular, I would like to thank Dr. Azalia Mirhoseini, Dr. Ebrahim Songhori, Dr. Ilya Razenshteyn, Dr. Hao Chen, Dr. Oxana Poburinnaya, Dr. Ilaria Chillotti, Dr. Rahul Chatterjee, Mohammad Samragh, Siam Hussain, Mojan Javaheripi, Mohsen Imani, Yeseong Kim, Yihe Dong, Dr. Wei Dai, and Blake Pelton.

Last but not least, I would also like to express my most sincere appreciation of my wife, my sister, my parents, and my dear friends for their emotional support. I would not be the same person without them.

The material in this dissertation is, in part, based on the following papers that are published or are under review.

Chapter 1 and 2, in part, has been published at (i) the Proceedings of 2018 ACM ASIA Conference on Computer and Communications Security (AsiaCCS) and appeared as: M. Sadegh Riazi, Christian Weinert, Oleksandr Tkachenko, Ebrahim M Songhori, Thomas Schneider, Farinaz Koushanfar, "Chameleon: A Hybrid Secure Computation Framework for Machine Learning Applications", and (ii) the Proceedings of 2019 USENIX Security Symposium and appeared as M. Sadegh Riazi, Mohammad Samragh, Hao Chen, Kim Laine, Kristin Lauter, Farinaz

XV

Koushanfar, "XONN: XNOR-based Oblivious Deep Neural Network Inference", and (iii) the Proceedings of 2019 IEEE Hardware Oriented Security and Trust (HOST) and appeared as: M. Sadegh Riazi, Mojan Javaheripi, Siam U Hussain, Farinaz Koushanfar, "MPCircuits: Optimized Circuit Generation for Secure Multi-Party Computation", and (iv) the Proceedings of 2020 ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS) and appears as: M. Sadegh Riazi, Kim Laine, Blake Pelton, Wei Dai, "HEAX: An Architecture for Computing on Encrypted Data", and (v) the Proceedings of 2017 Design Automation Conference (DAC) and appeared as: M. Sadegh Riazi, Ebrahim M. Songhori, Farinaz Koushanfar, "PriSearch: Efficient Search on Private Data", and (vi) the 2017 ACM Transactions on Embedded Computing Systems (TECS) and appeared as: M. Sadegh Riazi, Mohammad Samragh, Farinaz Koushanfar, "CAMsure: Secure ContentAddressable Memory for Approximate Search", and a paper that has been submitted to the 2020 Design Automation Conference (DAC) as: M. Sadegh Riazi, Seyed Mohammad Chavoshian, Farinaz Koushanfar, "SynFi: Automatic Synthetic Fingerprint Generation". The dissertation author was the primary author of this material.

Chapter 3, in part, has been published at the Proceedings of 2018 ACM ASIA Conference on Computer and Communications Security (AsiaCCS) and appeared as: M. Sadegh Riazi, Christian Weinert, Oleksandr Tkachenko, Ebrahim M Songhori, Thomas Schneider, Farinaz Koushanfar, "Chameleon: A Hybrid Secure Computation Framework for Machine Learning Applications". The dissertation author was the primary author of this material.

Chapter 4 and Appendix A, in part, has been published at the Proceedings of 2019 USENIX Security Symposium and appeared as M. Sadegh Riazi, Mohammad Samragh, Hao Chen, Kim Laine, Kristin Lauter, Farinaz Koushanfar, "XONN: XNOR-based Oblivious Deep Neural Network Inference". The dissertation author was the primary author of this material.

Chapter 5, in part, has been published at the Proceedings of 2020 ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS) and appears as: M. Sadegh Riazi, Kim Laine, Blake Pelton, Wei Dai, "HEAX: An Architecture for Computing on Encrypted Data". The dissertation author was the primary author of this material.

Chapter 6, in part, has been published at the Proceedings of 2019 IEEE Hardware Oriented Security and Trust (HOST) and appeared as: M. Sadegh Riazi, Mojan Javaheripi, Siam U Hussain, Farinaz Koushanfar, "MPCircuits: Optimized Circuit Generation for Secure Multi-Party Computation". The dissertation author was the primary author of this material.

Chapter 7, in part, has been published at the Proceedings of 2017 Design Automation Conference (DAC) and appeared as: M. Sadegh Riazi, Ebrahim M. Songhori, Farinaz Koushanfar, "PriSearch: Efficient Search on Private Data". The dissertation author was the primary author of this material.

Chapter 8, in part, has been published at the 2017 ACM Transactions on Embedded Computing Systems (TECS) and appeared as: M. Sadegh Riazi, Mohammad Samragh, Farinaz Koushanfar, "CAMsure: Secure ContentAddressable Memory for Approximate Search". The dissertation author was the primary author of this material.

Chapter 9, in part, has been submitted to the 2020 Design Automation Conference (DAC) as: M. Sadegh Riazi, Seyed Mohammad Chavoshian, Farinaz Koushanfar, "SynFi: Automatic Synthetic Fingerprint Generation". The dissertation author was the primary author of this material.

This dissertation was supported, in parts, by the Office of Naval Research (ONR) N00014-17-1-2500, National Science Foundation (NSF)/Semiconductor Research Coporation (SRC) (1619261/2016-TS-2690), MURI (FA9550-14-1-0351), NSF GC@Scale CNS-1619261, and NSF Trust-Hub grant (CNS-1649423) grants.

#### VITA

| 2014      | Bachelor of Science in Electrical Engineering, Sharif University of Technology, Tehran, Iran                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|

| 2016      | Master of Science in Computer Engineering, Rice University, Houston, Texas                                                         |

| 2016-2020 | Graduate Research Assistant, University of California San Diego, La Jolla, California                                              |

| 2020      | Doctor of Philosophy in Electrical Engineering (Computer Engineering),<br>University of California San Diego, La Jolla, California |

#### PUBLICATIONS

**M. Sadegh Riazi**, Seyed Mohammad Chavoshian, Farinaz Koushanfar, "SynFi: Automatic Synthetic Fingerprint Generation", *ArXiv Preprint*, 2020.

**M. Sadegh Riazi**, Kim Laine, Blake Pelton, Wei Dai, "HEAX: An Architecture for Computing on Encrypted Data", *ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS)*, 2020.

Siam U. Hussain, **M. Sadegh Riazi**, Farinaz Koushanfar, "The Fusion of Secure Function Evaluation and Logic Synthesis", *IEEE Security and Privacy (S&P) Magazine*, 2020.

Rahul Chatterjee, **M. Sadegh Riazi**, Tanmoy Chowdhury, Emanuela Marasco, Farinaz Koushanfar, Ari Juels, "Multisketches: Practical Secure Sketches Using Off-the-Shelf Biometric Matching Algorithms", *ACM Conference on Computer and Communications Security CCS*, 2019.

**M. Sadegh Riazi**, Mohammad Samragh, Hao Chen, Kim Laine, Kristin Lauter, Farinaz Koushanfar, "XONN: XNOR-based Oblivious Deep Neural Network Inference", *USENIX Security*, 2019.

Mohsen Imani, Yeseong Kim, **M. Sadegh Riazi**, John Messerly, Patric Liu, Farinaz Koushanfar, Tajana Rosing, "A Framework for Collaborative Learning in Secure High-Dimensional Space", *IEEE Cloud Computing (CLOUD), 2019.*

**M. Sadegh Riazi**, Mojan Javaheripi, Siam U Hussain, Farinaz Koushanfar, "MPCircuits: Optimized Circuit Generation for Secure Multi-Party Computation", *IEEE Hardware Oriented Security and Trust (HOST), 2019.*

Ebrahim M Songhori, **M. Sadegh Riazi**, Siam U Hussain, Ahmad-Reza Sadeghi, Farinaz Koushanfar, "ARM2GC: Succinct Garbled Processor for Secure Computation", *In Proceedings of Design Automation Conference (DAC)*, 2019.

**M. Sadegh Riazi**, Bita Darvish Rouhani, Farinaz Koushanfar, "Deep Learning on Private Data", *IEEE Security and Privacy (S&P) Magazine, 2019.*

Hao Chen, Ilaria Chillotti, Oxana Poburinnaya, Ilya Razenshteyn, **M. Sadegh Riazi**, "SANNS: Scaling Up Secure Approximate k-Nearest Neighbors Search", *ArXiv Preprint arXiv:1904.02033*, 2019.

**M. Sadegh Riazi**, Christian Weinert, Oleksandr Tkachenko, Ebrahim M Songhori, Thomas Schneider, Farinaz Koushanfar, "Chameleon: A Hybrid Secure Computation Framework for Machine Learning Applications", *ACM ASIA Conference on Computer and Communications Security (AsiaCCS)*, 2018.

**M. Sadegh Riazi** and Farinaz Koushanfar, "Privacy-Preserving Deep Learning and Inference", *International Conference On Computer Aided Design (ICCAD)*, 2018.

Hao Chen, Ilaria Chillotti, Oxana Poburinnaya, Ilya Razenshteyn, M. Sadegh Riazi, "Scaling Up Secure Nearest Neighbor Search", *Neural Information Processing Systems (NeurIPS) Workshop on Privacy-Preserving Machine Learning, 2018.*

Bita Darvish Rouhani, **M. Sadegh Riazi**, Farinaz Koushanfar, "DeepSecure: Scalable Provably-Secure Deep Learning", *In Proceedings of Design Automation Conference (DAC), 2018.*

Siam U. Hussain, **M. Sadegh Riazi**, Farinaz Koushanfar, "SHAIP: Secure Hamming Distance for Authentication of Intrinsic PUFs", *ACM Transactions on Design Automation of Electronic Systems (TODAES)*, 2018.

**M. Sadegh Riazi**, Mohammad Samragh, Farinaz Koushanfar, "CAMsure: Secure Content-Addressable Memory for Approximate Search", *ACM Transactions on Embedded Computing Systems (TECS)*, 2017.

**M. Sadegh Riazi**, Ebrahim M. Songhori, Farinaz Koushanfar, "PriSearch: Efficient Search on Private Data", *In Proceedings of Design Automation Conference (DAC)*, 2017.

**M. Sadegh Riazi**, Ebrahim M Songhori, Ahmad-Reza Sadeghi, Thomas Schneider, Farinaz Koushanfar, "Toward Practical Secure Stable Matching", *In Proceedings of Privacy Enhancing Technologies (PoPETs), 2017.*

**M. Sadegh Riazi**, Beidi Chen, Anshumali Shrivastava, Dan Wallach, Farinaz Koushanfar, "Sub-Linear Privacy-Preserving Near-Neighbor Search", *ArXiv Preprint arXiv:1612.01835, 2016.*

**M. Sadegh Riazi**, Neeraj K. R. Dantu, L. N. Vinay Gattu, Farinaz Koushanfar, "GenMatch: Secure DNA Compatibility Testing", *IEEE Hardware Oriented Security and Trust (HOST), 2016.*

#### ABSTRACT OF THE DISSERTATION

#### Towards A Private New World: Algorithm, Protocol, and Hardware Co-Design for Large-Scale Secure Computation

by

#### M. Sadegh Riazi

Doctor of Philosophy in Electrical Engineering (Computer Engineering)

University of California San Diego, 2020

Professor Farinaz Koushanfar, Chair

Data privacy and security are among the grand challenges in the emerging era of massive data and collective intelligence. On the one hand, the rapid advances of several technologies, including artificial intelligence, are directly dependent on harnessing the full potential of data. On the other hand, such colossal collections of data inherently have sensitive information about individuals; explicit access to the data violates the privacy of content owners. While a number of elegant cryptographic solutions have been suggested for secure storage as well as secure transmission of data, the ability to compute on encrypted data at scale has remained a standing challenge. Secure computation is a set of developing technologies that enable processing on the unintelligible version of the data. Secure computation can create a zero-trust platform where two or more individuals or organizations collaboratively compute on their shares of data without compromising data confidentiality. Computing on encrypted data removes several critical obstacles that prohibit scientific advances in which collaboration between distrusting parties is needed. Nevertheless, secure computation comes at the cost of significant computational overhead and higher communication between the pertinent parties. Currently, the high computational complexity prevents secure computation to be adopted in compute-intensive systems. This dissertation introduces several holistic algorithm-level, protocol-level, as well as hardware-level methodologies to enable the large-scale realization of the emerging secure computing and privacy technologies.

The key contributions of this dissertation are as follows:

- Introducing a novel secure computation framework in which several secure function evaluation protocols are integrated. The integration allows to choose a specific protocol to execute each unique operation based on the underlying mathematical characteristics of the protocol. The proposed methodology enables the secure execution of machine learning models 4-133× faster than the prior art.

- Designing a neural network transformation and a customized secure computation protocol for secure inference on deep neural networks. The transformation translates the contemporary neural network operations into several Boolean operations that can more efficiently be executed in secure computation protocols. The proposed transformation in conjunction with the customized protocol enable privacy-preserving medical diagnosis on four medical datasets for the first time.

- Design and end-to-end implementation of a new high-performance hardware architecture for computing on encrypted data. The proposed architecture outperforms high-end GPUs by more than 30× and modern CPUs by more than two orders of magnitude.

- Creating an efficient methodology based on hardware synthesis tools to produce compact Boolean circuit representation of a given function. The Boolean representation is optimized according to the cost function of secure computation protocols. The methodology reduces the computation and communication costs by up to  $4\times$ .

- Designing a new substring search algorithm customized for secure computation that does not require random access to the text. The proposed algorithm outperforms all state-of-the-art substring search algorithms when run within the secure computation protocol.

- Introducing the first secure content-addressable memory for approximate search. The design enables high-accuracy similarity-based approximate search while keeping the underlying data private without relying on a trusted server. The construction is the first to provide post-breach data confidentiality.

- Proposing a new methodology to create large-volume synthetic human fingerprints that are computationally indistinguishable from real fingerprints. The methodology enhances the security of any fingerprint-based authentication system.

## Chapter 1

## Introduction

Rapid advances in computing capabilities, together with exponential growth in the number of sensors, have led to the generation of an unprecedented volume of data. In addition, faster Internet connections have paved the way for ubiquitous use of online services. Thus, several privacy and security issues are emerging as a result of poor data management and insufficient security mechanisms. Data centers are increasingly prone to both internal and external hacks, and preserving consumers' data privacy is becoming more challenging every day. To this end, novel cryptographic solutions are needed to enhance the security of large-scale systems and the privacy of consumers.

Secure computation is a new set of technologies that enables *computation on the encrypted data*. In contrast to traditional encryption mechanisms that protect data in storage or transit, secure computation protects data during computation: closing the loop for data confidentiality. The security guarantees, however, come at the cost of several orders of magnitude computation and communication overhead, limiting the real-world deployment of this technology.

This thesis addresses several standing challenges related to secure computation. In particular, several algorithmic, protocol-level, and hardware-level methodologies are proposed that enable computing on encrypted data to become ubiquitous. In this section, I will review the challenges as well as my proposed methodologies to address such problems.

## 1.1 Mixed-Protocol Secure Computation Framework for Machine Learning

Secure Function Evaluation (SFE) is one of the most influential achievements of modern cryptography. It allows two or more parties to evaluate a function on their inputs without disclosing the inputs to each other; that is, all inputs are kept private by the respective owners. In fact, SFE emulates a *trusted* third party which collects inputs from different parties and returns the result of the function to all (or a specific set of) parties. SFE has many applications in privacy-preserving biometric authentication [EFG<sup>+</sup>09], secure auctions [FPRSJ04], secure search [RSK17b], privacy-preserving machine learning [DGBL<sup>+</sup>16a], and data mining [LP00]. SFE was initially introduced in 1982 by Andrew Yao [Yao82] as the millionaires' problem in which two millionaires are interested to know which one has more money without disclosing their amount of wealth. Later on, the problem was formalized as a general question for any function. The two most prominent SFE protocols are Yao's Garbled Circuits (GC) [Yao86b] and the Goldreich-Micali-Wigderson (GMW) protocol [GMW87].

In theory, any function that can be represented as a Boolean circuit can be evaluated securely using GC or GMW protocols. For certain frequent operations such as multiplication, the Boolean circuit description can result in a substantial overhead. The number of Boolean gates in the circuit grows quadratically with respect to the bit-width of the operands. As a result, GC and GMW can often be too slow and hence are of limited practical value. In addition to generic secure computation protocols, i.e., GC and GMW, there exist solutions that enable a subset of operations while imposing less computational overhead. For instance, secret sharing based methodologies allow one to perform linear operations such as multiplication and addition on the encrypted data. Non-linear operations, however, are not supported by these methodologies.

I introduce Chameleon, a fast, modular, and hybrid (mixed-protocol) secure computation framework for machine learning tasks that utilizes GC, GMW, and additive secret sharing protocols and achieves unprecedented performance both in terms of runtime and communication between parties. The proposed methodology securely executes linear operations, such as multiplication and addition, on encrypted values using additive secret sharing. The computation on the additive shares takes place in the ring  $\mathbb{Z}_{2^l}$ , integers modulo a power-of-two number. As such, linear operations can be computed significantly faster than generic SFE protocols due to the inherent properties of the ring  $\mathbb{Z}_{2^l}$ .

Non-linear operations on the encrypted values will be computed using either of the generic protocols, i.e., GC or GMW. To switch the underlying protocol, one needs to change the secret types from additive shares to Yao and Boolean shares, and vice versa. Chameleon provides efficient mechanisms to realize this requirement and enable execution of different protocols interchangeably. In addition, Chameleon introduces a new secure Vector Dot Product (VDP) protocol that requires less computation and communication, both asymptotically and concretely, compared to prior standard protocols for VDP. Since VDP is usually the computational bottleneck of almost all machine learning models, Chameleon substantially reduces the secure evaluation of various machine learning models. To further reduce the communication between parties, certain compression and seed expansion techniques are incorporated. In a nutshell, Chameleon provides a new approach to securely execute any type of machine learning application with 4-133× faster runtime.

## **1.2** Neural Network Transforming for Secure Computation

The advent of big data and striking recent progress in artificial intelligence are fueling the impending industrial automation revolution. In particular, Deep Learning (DL) —a method based on learning Deep Neural Networks (DNNs) —is demonstrating a breakthrough in accuracy. DL models outperform human cognition in a number of critical tasks such as speech and visual recognition, natural language processing, and medical data analysis. Given DL's superior performance, several technology companies are now developing or already providing DL as a service. They train their DL models on a large amount of (often) proprietary data on their own servers; then, an inference API is provided to the users who can send their data to the server and receive the analysis results on their queries. The notable shortcoming of this remote inference service is that the inputs are revealed to the cloud server, breaching the privacy of sensitive user data.

*Oblivious inference* is the task of running the DL model on the client's input without disclosing the input or the result to the server itself. Several solutions for oblivious inference have been proposed that utilize one or more cryptographic tools such as Homomorphic Encryption (HE) [BV14, BGV14], Garbled Circuits, GMW protocol [GMW87], and Secret Sharing (SS). Each of these cryptographic tools offer their own characteristics and trade-offs.

I introduce XONN, a novel end-to-end framework which provides a paradigm shift in the conceptual and practical realization of privacy-preserving interference on deep neural networks. The existing work has largely focused on the development of customized security protocols while using conventional fixed-point deep learning algorithms. XONN, for the first time, suggests leveraging the concept of the Binary Neural Networks (BNNs) in conjunction with the GC protocol. In BNNs, the weights and activations are restricted to binary (i.e,  $\pm 1$ ) values, substituting the costly multiplications with simple XNOR operations during the inference phase. The XNOR operation is known to be *free* in the GC protocol [KS08a]; therefore, performing oblivious inference on BNNs using GC results in the removal of costly multiplications. Using my approach, I show that oblivious inference on the standard DL benchmarks can be performed with minimal, if any, decrease in the prediction accuracy.

State-of-the-art approaches for oblivious inference require at least one round of interaction between client the server. This requirement, in turn, can substantially increase the runtime of oblivious inference in real-world settings where the network latency is high and unstable. One of XONN's design principles is to have a *constant* rounds of interaction between client and the server regardless of the number of layers in the neural network. The removal of many interaction rounds paves the way to run very deep neural networks. For instance, XONN enables secure medical diagnosis on four medical datasets for the first time, i.e., breast cancer, diabetes, liver disease, and Malaria. Leveraging XONN, medical agencies can obtain AI-based medical diagnosis through third parties without disclosing patients's data: the private data remains encrypted at all times, even during the computation by the third party. Thus, medical agencies can enhance their diagnosis without violating patients' privacy.

# **1.3 High-Performance Hardware Architecture for Computing on Encrypted Data**

Cloud computing has, in a short time, fundamentally changed the economics of computing. It allows businesses to quickly and efficiently scale to almost arbitrary-sized workloads; small organizations no longer need to own, secure, and maintain their own servers. However, cloud computing comes with significant risks that have been analyzed in the literature over the last decade (see [DWC10,HN08,SK11]). Specifically, many of these risks revolve around data security and privacy. For example, data in cloud storage might be exposed to both outsider and insider threats, and be prone to both intentional and unintentional misuse by the cloud provider. Recently, the European Union and the State of California have passed strong data privacy regulations. In this light, companies and organizations that possess highly private data are hesitant to migrate to the cloud, and cloud providers are facing increasing liability concerns.

Fully Homomorphic Encryption (FHE) provides provable security guarantees without any trust assumptions on the cloud provider, and it can be used to enable several secure and privacy-preserving cloud-based solutions. For instance, in the context of Machine Learning as a Service (MLaaS), FHE can be used to perform oblivious neural network inference [DGBL<sup>+</sup>16b,DSC<sup>+</sup>18]:

clients send the encrypted version of their data, the cloud server runs ML models on the encrypted queries, and returns the result to the clients. All intermediate and final results are encrypted and can only be decrypted by the clients. Perhaps, the most critical obstacle today to deploy FHE at large-scale is the enormous computation overhead compared to a plaintext counterpart in which data is not kept confidential.

The *ciphertext* in FHE schemes is a set (usually a pair) of polynomials with degree n - 1 (vectors of *n* integers) modulo a big integer. One of the main challenges of designing an architecture for FHE is that homomorphic operations on ciphertexts involve computationally intensive modular arithmetic on big integers (with several hundred bits). These operations have convoluted data dependency among different parts of the computation, making it challenging to design a high-throughput architecture. Moreover, the degree of the underlying polynomials is enormous (in the order of several thousand). Storing the entire intermediate results on FPGA chip is prohibitive.