# UCLA UCLA Electronic Theses and Dissertations

# Title

Selective Area Doping of GaN by Epitaxial Layer Overgrowth and Its Power Electronic Applications

**Permalink** https://escholarship.org/uc/item/81p6k52w

# Author

Wang, Jia

Publication Date

2021

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA

Los Angeles

Selective Area Doping of GaN by Epitaxial Layer Overgrowth

and Its Power Electronic Applications

A dissertation submitted in partial satisfaction of the

requirements for the degree Doctor of Philosophy

in Materials Science and Engineering

by

Jia Wang

2021

© Copyright by

Jia Wang

2021

# ABSTRACT OF THE DISSERTATION

# Selective Area Doping of GaN by Epitaxial Layer Overgrowth and Its Power Electronic Applications

by

Jia Wang

Doctor of Philosophy in Materials Science and Engineering University of California, Los Angeles, 2021 Professor Ya-Hong Xie, Chair

GaN has wide bandgap, high critical electric field, and high electron saturation velocity, making it an ideal candidate for power switching electronics. However, the development of GaNbased power electronics is still hampered by the high cost of GaN substrate and selective area doping capabilities (especially for *p*-type) to produce laterally patterned *p*-*n* junctions. Epitaxial lateral overgrowth (ELO) is known to render low-dislocation-density GaN in the overgrown regions (wings) on inexpensive foreign substrates. Furthermore, the combination of ELO (prior to the coalescence stage) and *in-situ* doping process produces the half-core-shell doping profile which has been used in the optoelectronics such as microrod LEDs. However, the application of ELO-GaN has not been explored in the power applications mostly because such doping profile is not configured to withstand high reverse blocking voltage unless the modified structures and methods could be adopted. In this dissertation, a holistic approach was employed to study the innovative measures either in the material growth or device processing stage to tailor the half-core-shell doping profile produced by the ELO of GaN into the desired selective-area doping profiles for power switching electronics featuring the building block of laterally patterned p-n junctions.

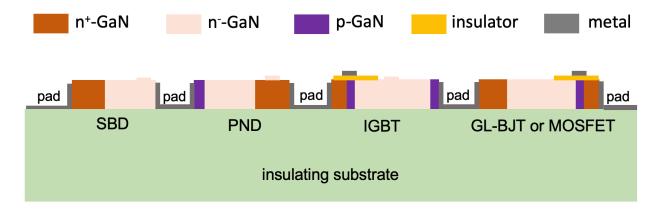

For the device processing innovation, the concept of true-lateral device architecture was proposed which consists of fully lateral aligned p-n junctions. The general advantages of such device architecture were comprehensively discussed from various aspects. In addition, the low-dislocation density GaN in the wing regions of ELO was fully utilized as an ideal drift layer of a power device. As a result, both power diodes (SBD and PND) and power bipolar transistors (GL-BJT and IGBT) with the true-lateral device architecture were experimentally demonstrated either with superior performance or for the first time, highlighted by the record high critical electric field in a GaN p-n junction and the record high current gain of a power bipolar transistor.

Alternatively, for the material growth innovation, the hybrid epitaxy-enabled substrate transfer approach was demonstrated to produce the GaN substrate with repeating laterally patterned *p*-*n* junctions suitable for a number of advanced electronic devices such as a planar-gate vertical MOSFET. In addition, the selective area doping profiles of the GaN substrate product also rendered a number of state-of-the-art characterization techniques which provided valuable information to study the incorporation and diffusion of dopants (especially for acceptors) in GaN.

With these innovative measures and a deeper understanding of selective area doping of GaN, the potential of epitaxial lateral overgrowth to simultaneously realize the low threading dislocation density and the selective-area doping profile (lateral patterned p-n junctions) was initially and finally unleashed, which may spawn a revival of interest into ELO-GaN to yield unprecedented opportunities in power electronic applications. The dissertation of Jia Wang is approved.

Hiroshi Amano

Dwight Christopher Streit

Jaime Marian

Kang Lung Wang

Ya-Hong Xie, Committee Chair

University of California, Los Angeles

2021

Dedicated to my parents

for their boundless love and support

# TABLE OF CONTENTS

| Chapter 1 Introduction1                                     |

|-------------------------------------------------------------|

| 1.1 Background1                                             |

| 1.1.1 Power Switching Electronics 1                         |

| 1.1.2 Critical Electric Field in a WBG Semiconductor        |

| 1.1.3 Material of Choice                                    |

| 1.2 Improvement for GaN as Power Switching Electronics7     |

| 1.2.1 GaN with Low Dislocation Density7                     |

| 1.2.2 Selective-area Doping Capabilities10                  |

| 1.3 Epitaxial Lateral Overgrowth of GaN14                   |

| 1.3.1 Dislocation Reduction by ELO14                        |

| 1.3.2 Towards Selective-area <i>p</i> -type Doping by ELO15 |

| 1.4 Aim of the Study and Outline of the Dissertation16      |

| 1.5 References                                              |

| Chapter 2 ELO-GaN with Half-Core-Shell Doping Structure     |

| 2.1 ELO with Serpentine-Channeled Masks 22                  |

| 2.1.1 Overview                                              |

| 2.1.2 MOVPE Growth                                          |

| 2.2 Characterization of the ELO-GaN Stripes                 |

| 2.2.1 Optical Microscopy                                    |

| 2.2.2 Scanning Electron Microscopy                          |

| 2.2.3 Fluorescence Microscopy                              |    |

|------------------------------------------------------------|----|

| 2.2.4 Cathodoluminescence Microscopy                       |    |

| 2.3 Stacking Faults in the ELO-GaN Stripes                 |    |

| 2.4 Summary                                                | 44 |

| 2.5 References                                             | 44 |

| Chapter 3 True-lateral Diodes on ELO-GaN                   |    |

| 3.1 Rational                                               | 47 |

| 3.1.1 True-vertical and Quasi-vertical Device Architecture |    |

| 3.1.2 CPE-induced Stress and Reliability Issue             |    |

| 3.1.3 True-lateral Device Architecture                     |    |

| 3.2 Device Fabrication of the True-Lateral Diodes          | 59 |

| 3.2.1 Process Flow                                         | 59 |

| 3.2.2 Edge Termination                                     |    |

| 3.3 Device Characterization                                | 65 |

| 3.3.1 TLM Measurement                                      | 65 |

| 3.3.2 Capacitance Profiling Measurement                    |    |

| 3.3.3 Forward <i>I-V</i> Characteristics                   | 71 |

| 3.3.4 Reverse <i>I-V</i> Characteristics                   | 76 |

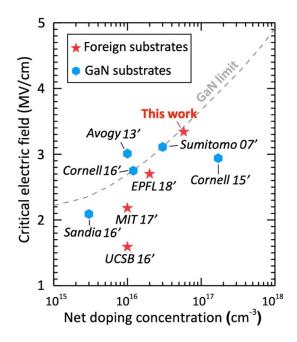

| 3.4 Critical Electric Field                                | 78 |

| 3.4.1 Impact Ionization Modeling                           |    |

| 3.4.2 Critical Electric Field Benchmarking                 |    |

| 3.5 Summary                                                |    |

| 3.6 References                                             |    |

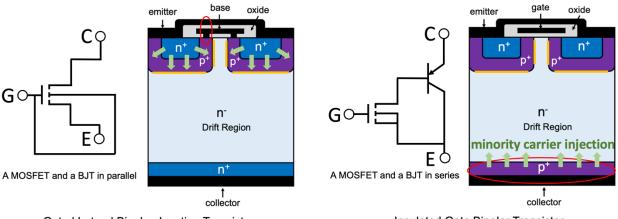

| Chapter 4 True-lateral Bipolar Transistors on ELO-GaN             |                 |

|-------------------------------------------------------------------|-----------------|

| 4.1 Introduction                                                  |                 |

| 4.2 Concept of Gated Lateral Power BJT                            |                 |

| 4.2.1 Tradeoff between Current Gain and Breakdown Voltage         |                 |

| 4.2.2 Device Structure                                            | 90              |

| 4.2.3 Device Simulation                                           | 94              |

| 4.3 Fabrication of Gated Lateral Power BJT                        | 97              |

| 4.4 Performance of Gated Lateral Power BJT                        | 101             |

| 4.5 Insulated-Gate Bipolar Transistor                             | 107             |

| 4.6 Summary                                                       | 115             |

| 4.7 References                                                    | 116             |

| Chapter 5 GaN Substrate with Repeating Laterally Patterned p-n    | Junctions . 120 |

| 5.1 Overview                                                      | 120             |

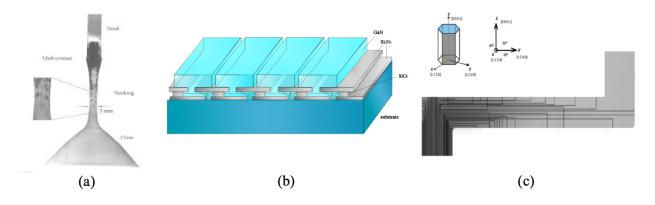

| 5.2 Hybrid Epitaxy-enabled Substrate Transfer                     | 121             |

| 5.2.1 General Methodology                                         |                 |

| 5.2.2 Growth and Transfer Experiment                              |                 |

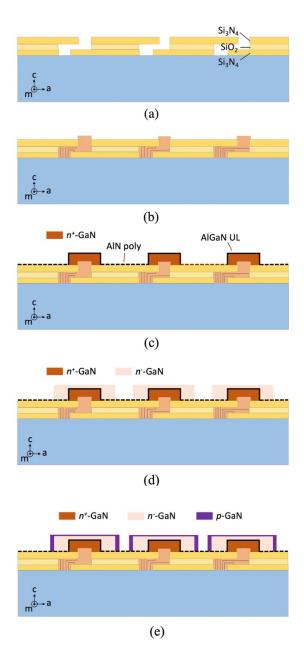

| 5.2.3 Repeating Laterally Patterned <i>p</i> - <i>n</i> Junctions |                 |

| 5.3 Normally-off Vertical MOSFETs                                 |                 |

| 5.3.1 Overview                                                    |                 |

| 5.3.2 Device Fabrication                                          |                 |

| 5.3.3 Electrical Characterization                                 |                 |

| 5.4 Summary                                                       | 140             |

| 5.5 References                                                    | 141             |

| Chapter 6 Selective-area Doping by Anisotropic Diffusion of Mg             | 143 |

|----------------------------------------------------------------------------|-----|

| 6.1 Quantitative Mapping of Elements, Dopants and Carriers                 |     |

| 6.1.1 Challenge for Quantitative Characterization of Selective-area Doping |     |

| 6.1.2 Cross-sectional Elemental, Dopant, and Carrier Mappings              | 144 |

| 6.2 Modeling of Anisotropic Diffusion of Mg in ELO-GaN                     | 154 |

| 6.3 Delta-doping of Mg for Ohmic Contact to <i>p</i> -type GaN             | 160 |

| 6.3.1 Rational                                                             | 160 |

| 6.3.2 Experiments                                                          | 161 |

| 6.3.3 <i>I-V</i> Measurement Results                                       | 163 |

| 6.4 Summary                                                                | 168 |

| 6.5 References                                                             | 168 |

| Chapter 7 Conclusion and Future Outlook                                    | 171 |

| 7.1 Concluding Remarks                                                     | 171 |

| 7.2 Future Outlook                                                         |     |

| 7.2.1 Improvement of $V_{BR}$                                              |     |

| 7.2.2 Reduction of R <sub>on,sp</sub>                                      | 174 |

| 7.2.3 Substrate Transfer and Monolithic Integration Platform               | 175 |

| 7.3 References                                                             |     |

# LIST OF FIGURES

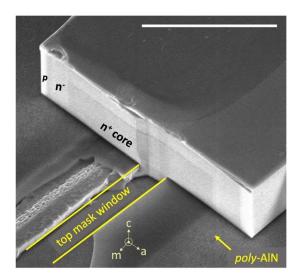

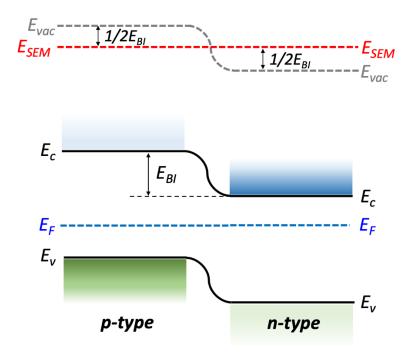

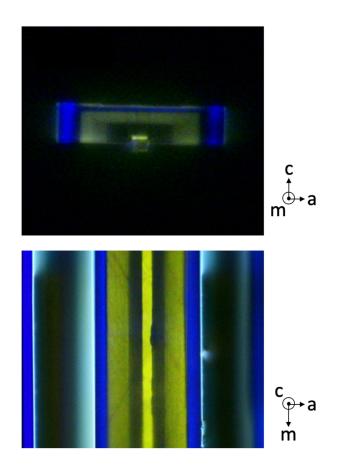

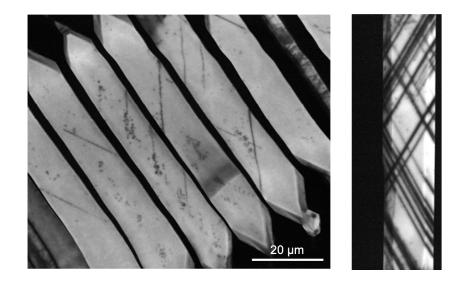

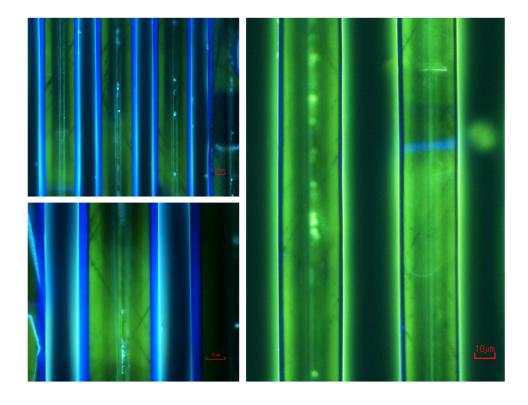

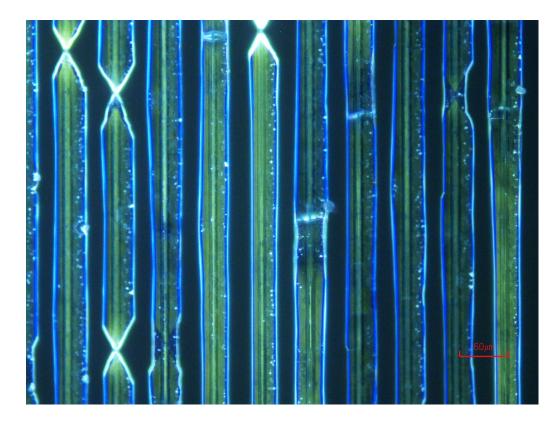

**Figure 1.1** Applications of power switching electronics sorted by the rated voltage and current..2 Figure 1.4 R<sub>on.sp</sub> versus V<sub>BR</sub> for all the common types of power switches (Si, SiC and GaN)...... 6 Figure 1.8 Ion implantation and etch-and-regrowth to create the selective-area p-type region. 13 Figure 2.1 Comparison between conventional ELO and with serpentine-channeled masks...... 22 Figure 2.3 Veeco K465i GaN MOCVD system used for growing the ELO-GaN samples....... 25 Figure 2.4 Schematic of the growth process of GaN island with half-core-shell doping profile.27 Figure 2.5 Schematics of ELO-GaN with different types of half-core-shell doping profiles...... 28 Figure 2.9 The SEM image showing the half-core-shell doping profile of the GaN island....... 33 Figure 2.10 The band diagram of the SEM detector and vacuum with respect to a *p*-*n* junction.33 Figure 2.11 Fluorescence microscopic images showing the half-core-shell doping profile....... 35

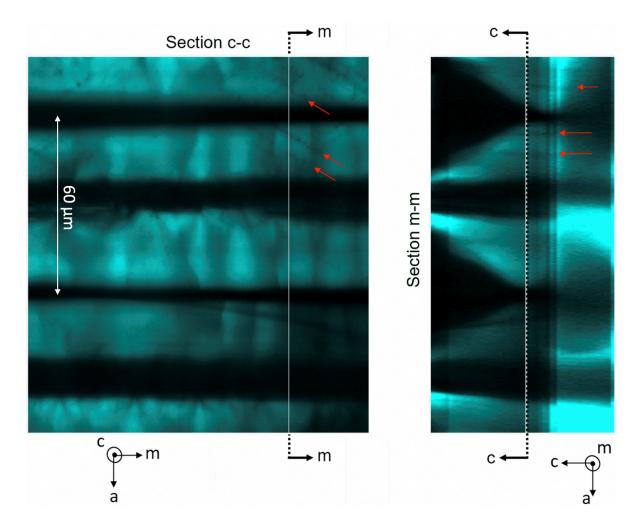

| Figure 2.13 CL images showing the typical defect of "inclined dark line" across the stripes 38            |

|-----------------------------------------------------------------------------------------------------------|

| Figure 2.14 The depth-scanning multiple-photon luminescence images (near-band emission) 39                |

| Figure 2.15 Low-temperature PL spectra of the non-doped ELO-GaN island                                    |

| Figure 2.16 The PSFs in the ELO-GaN stripes without the insertion of AlGaN underlayer 42                  |

| Figure 2.17 The suppression of PSFs with the insertion of AlGaN underlayer                                |

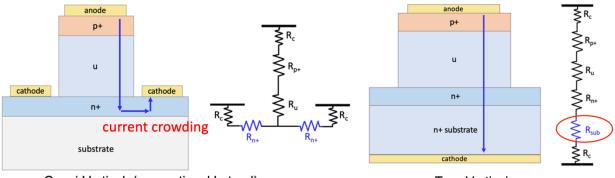

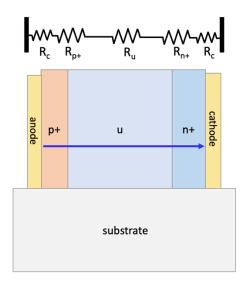

| Figure 3.1 Schematics of quasi-vertical and fully vertical PNDs and equivalent resistance 47              |

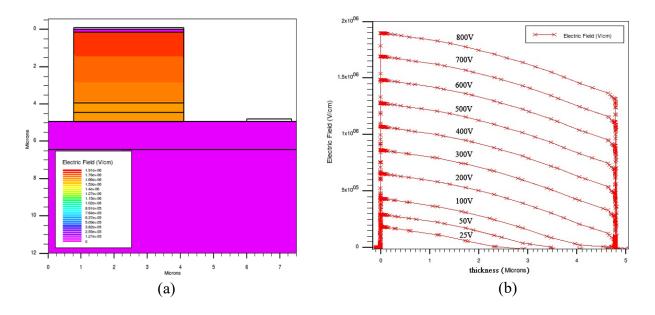

| Figure 3.2 Simulated field distribution in the drift layer under various reverse bias                     |

| Figure 3.3 The schematics of high-field induced stress in the fully-depleted drift layer                  |

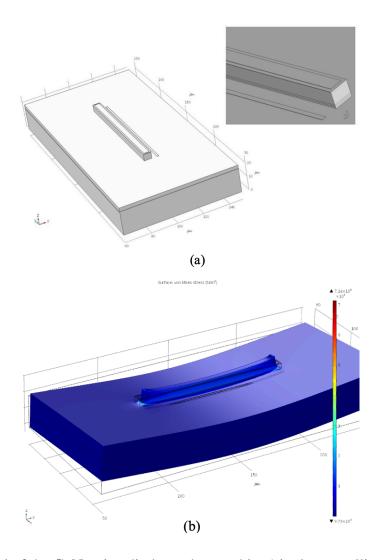

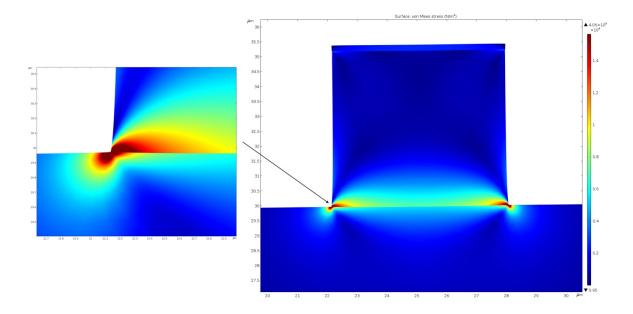

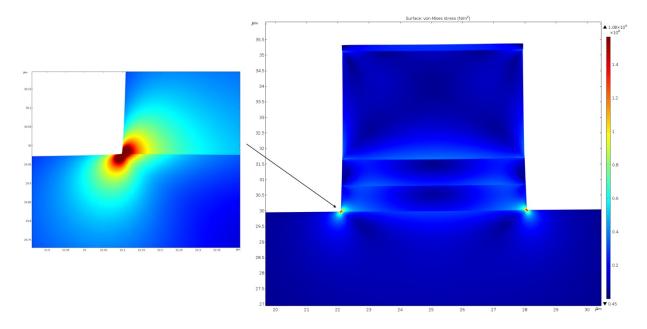

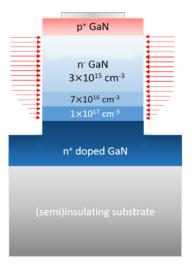

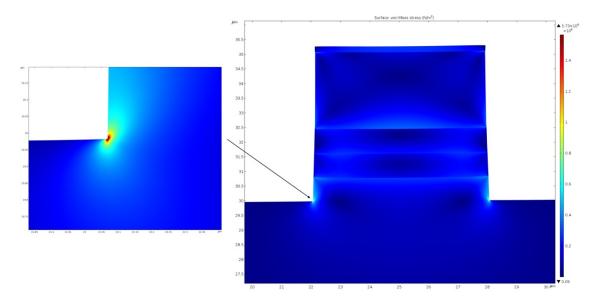

| Figure 3.4 The stripe-like diode model and the simulated stress distribution in the structure53           |

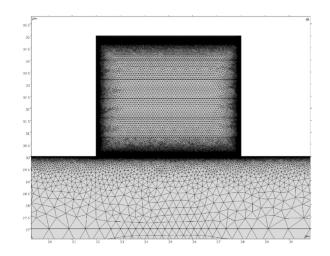

| Figure 3.5 The meshing profile of the enlarged diode structure                                            |

| Figure 3.6 Stress distribution in the <i>p</i> - <i>n</i> diode without step-graded doping buffer layers  |

| <b>Figure 3.7</b> Stress distribution in the $p$ - $n$ diode with step-graded doping buffer layers        |

| <b>Figure 3.8</b> Schematic of the CPE induced stress with 1- $\mu$ m-deep mesa-etch of $n^+$ layer       |

| Figure 3.9 Reduced stress distribution with step-graded doping layers and deep mesa etching. 56           |

| Figure 3.10 Schematic illustration of true-lateral diode architecture and equivalent resistance. 57       |

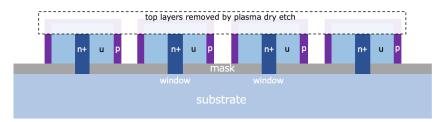

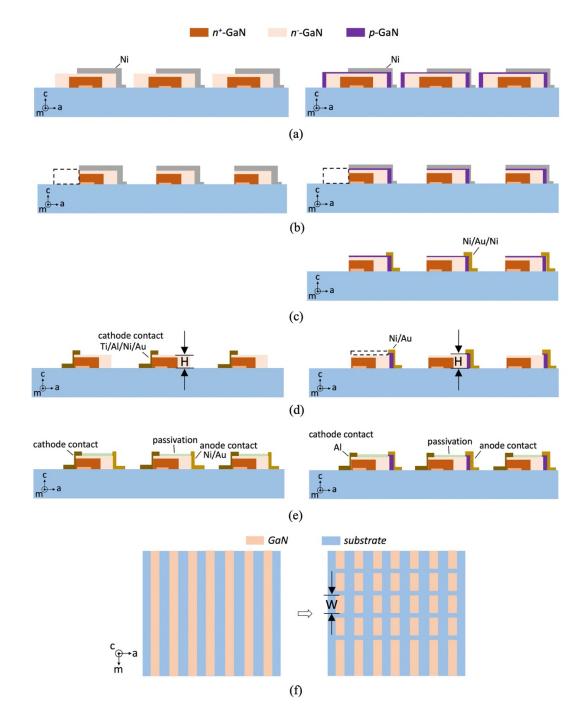

| Figure 3.11 The schematic showing dry etch to remove the top layers of <i>p</i> -GaN and <i>u</i> -GaN 59 |

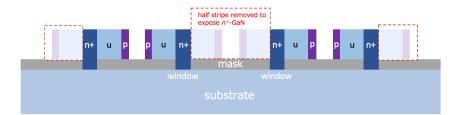

| <b>Figure 3.12</b> The schematic showing second dry etch to expose $n^+$ -GaN                             |

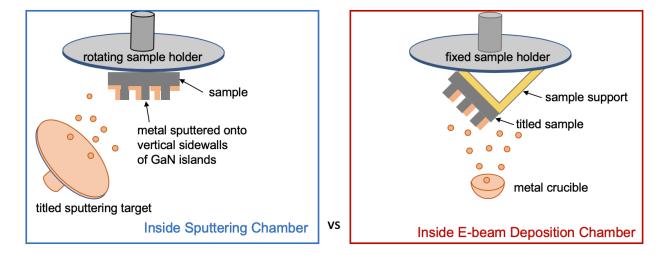

| Figure 3.13 Metal contacts deposited onto the island sidewalls and onto the mask                          |

| Figure 3.14 Schematic comparison of sputtering vs. e-beam evaporation                                     |

| Figure 3.15 Cross-sectional schematics of the processing of true-lateral SBD and PND                      |

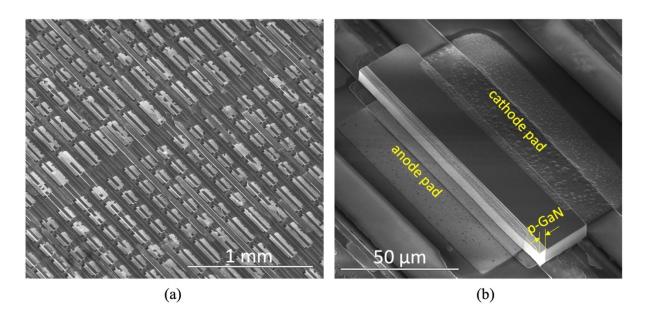

| Figure 3.16 The angled-viewed SEM images of the fabricated PND arrays and a single PND 64                 |

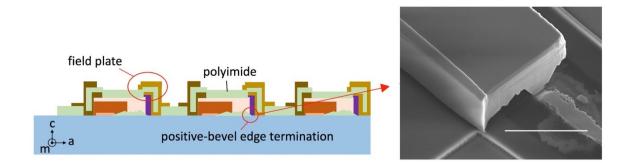

| Figure 3.17 Schematic of the edge termination schemes and SEM image of the GaN island 64                  |

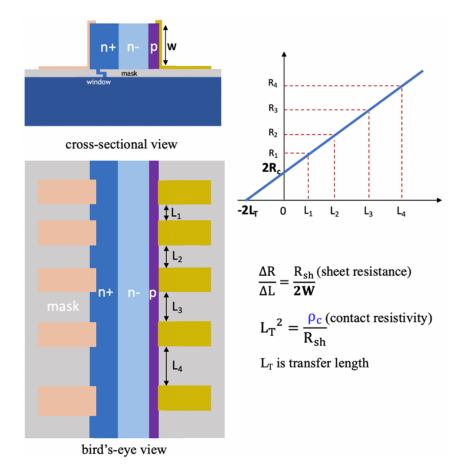

| Figure 3.18 Schematic illustrations of modified TLM measurement setup and pattern design66                |

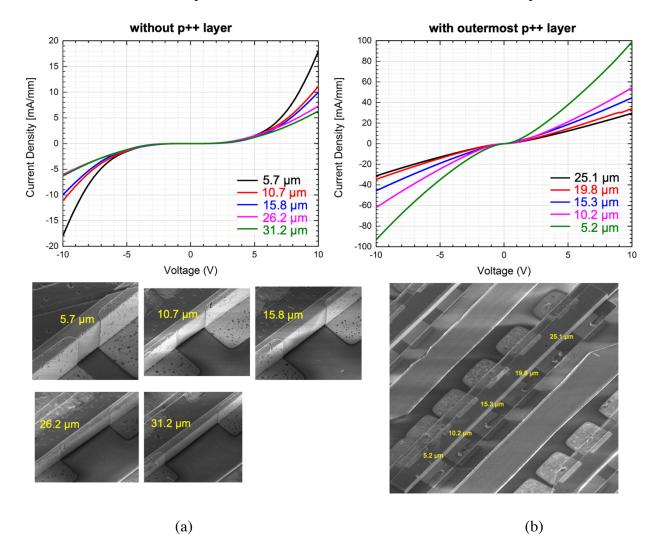

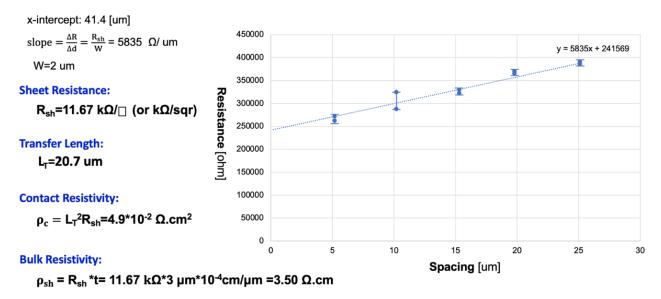

| Figure 3.19 Angled-view SEM images of the TLM test structure for the true-lateral PND67                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

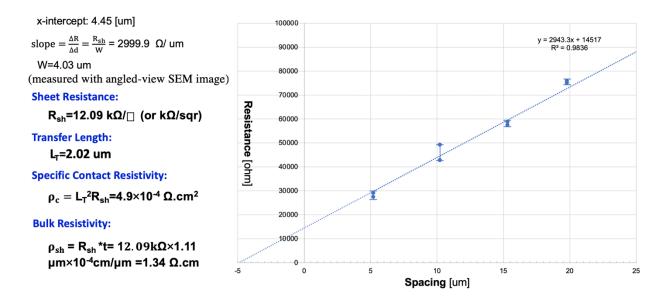

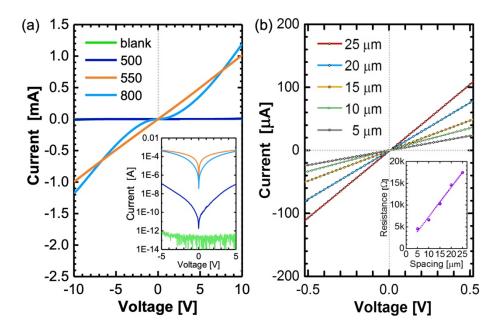

| Figure 3.20 The TLM measurement results for Ohmic contact to <i>p</i> -GaN side                                                                           |

| Figure 3.21 The TLM measurement results for Ohmic contact to $n^+$ -GaN side                                                                              |

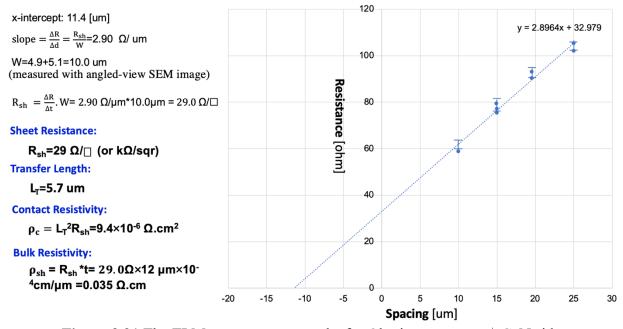

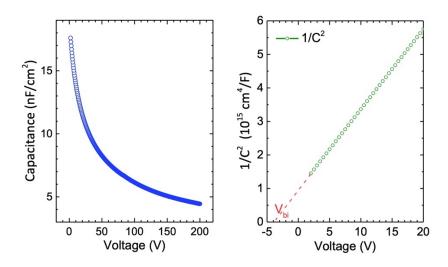

| Figure 3.22 The modified setup for capacitance-voltage profiling in the fully lateral PND 69                                                              |

| Figure 3.23 The variation of E-field versus depletion region depth in the fully lateral PND 69                                                            |

| <b>Figure 3.24</b> (left) <i>C</i> - <i>V</i> characteristics and (right) $1/C^2$ vs. <i>V</i> plot of the <i>a</i> -plane GaN PND 70                     |

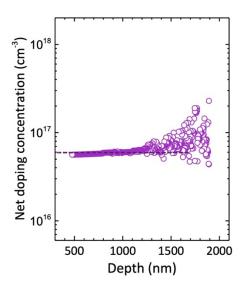

| Figure 3.25 Net doping concentration versus depletion depth of the ELO-GaN PND                                                                            |

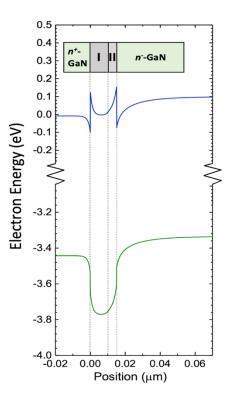

| Figure 3.26 The simulated band diagram of n <sup>+</sup> -GaN/n <sup>+</sup> -Al <sub>0.2</sub> Ga <sub>0.8</sub> N/n <sup>-</sup> -GaN heterostructure72 |

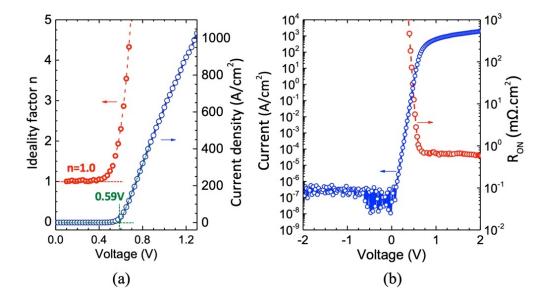

| Figure 3.27 Forward <i>I-V</i> characteristics of the ELO-GaN SBD                                                                                         |

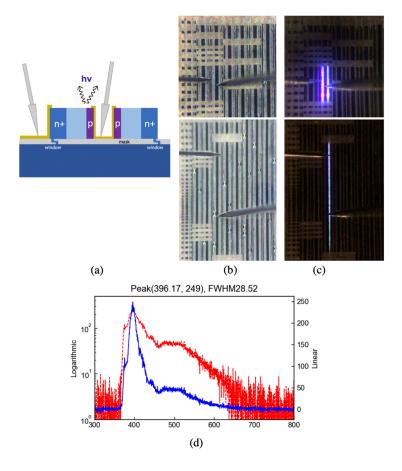

| Figure 3.28 Electroluminescence of the ELO-GaN PND samples                                                                                                |

| Figure 3.29 Forward <i>I-V</i> characteristics of the ELO-GaN PND with edge termination75                                                                 |

| Figure 3.30 Reverse <i>I-V</i> characteristics of the ELO-GaN SBD                                                                                         |

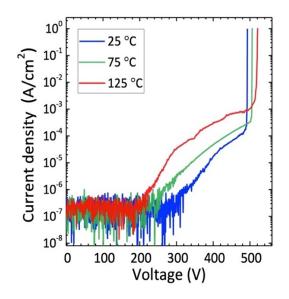

| Figure 3.31 Reverse <i>I-V</i> characteristics of the ELO-GaN PND with varying temperatures                                                               |

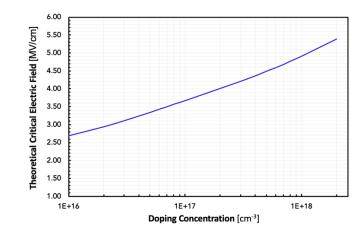

| Figure 3.32 Calculated theoretical critical filed versus net doping concentration                                                                         |

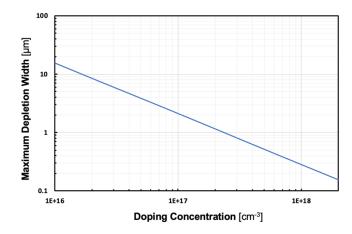

| Figure 3.33 Calculated maximum depletion width versus net doping concentration                                                                            |

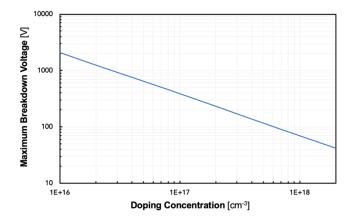

| Figure 3.34 Calculated maximum breakdown voltage versus net doping concentration                                                                          |

| Figure 3.35 Benchmark of the non-polar true-lateral PND with other PNDs in the literature83                                                               |

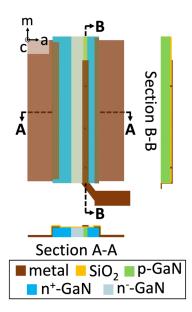

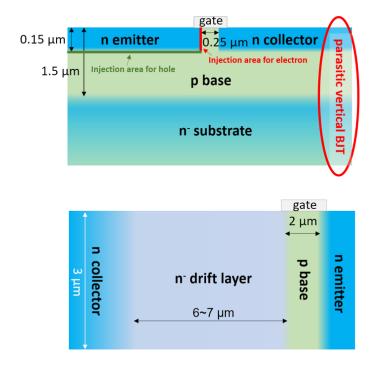

| Figure 4.1 Schematic comparison of the structure of GL-BJT and IGBT                                                                                       |

| Figure 4.2 Schematic illustrations of the structure of the GaN GLP-BJT                                                                                    |

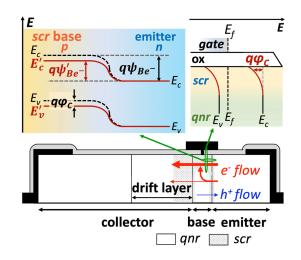

| Figure 4.3 The band diagrams across the two key junctions of the GLP-BJT91                                                                                |

| Figure 4.4 Band diagrams among conventional lateral BJT, Gated-Lateral BJT and MOSFET. 93                                                                 |

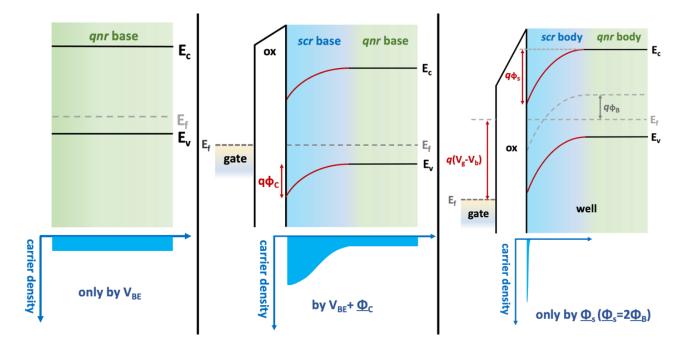

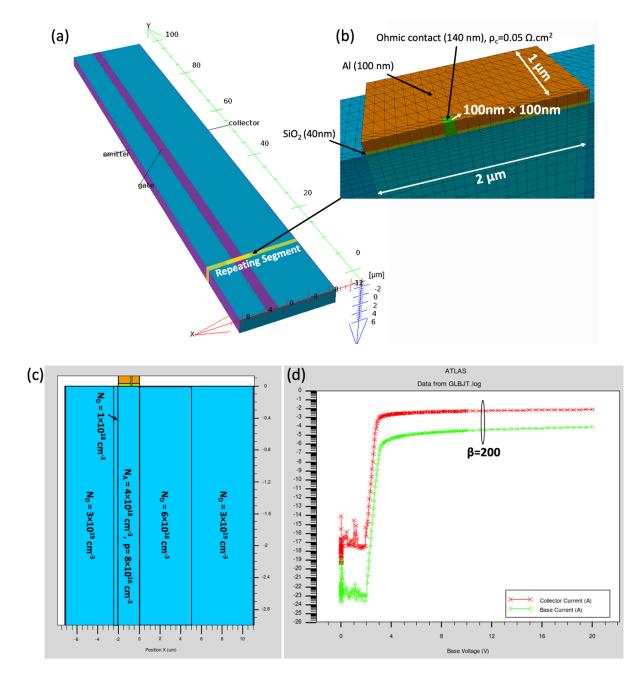

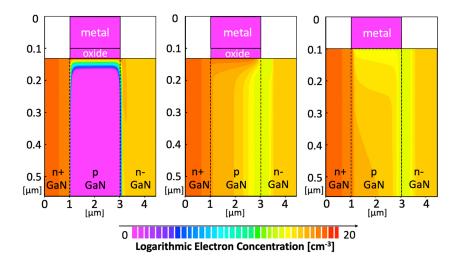

| Figure 4.5 TCAD simulation results with regard to the GaN GLP-BJT                                                                                         |

| Figure 4.6 Electron concentration distribution in MOSFET, GLP-BJT and conventional BJT 96                                                                 |

| Figure 4.7 The structures of a conventional GL-BJT and the GLP-BJT in this dissertation97                                         |

|-----------------------------------------------------------------------------------------------------------------------------------|

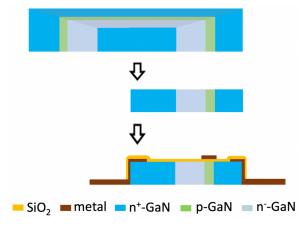

| Figure 4.8 Schematics of the key steps of fabricating the GLP-BJT on the ELO-GaN island 98                                        |

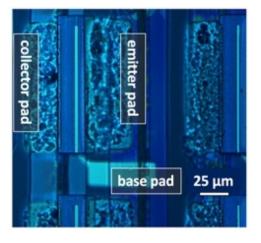

| Figure 4.9 Bright-field optical microscopic image of the as-processed GaN GLP-BJT                                                 |

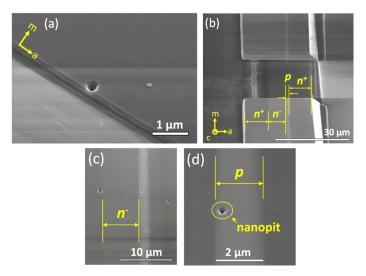

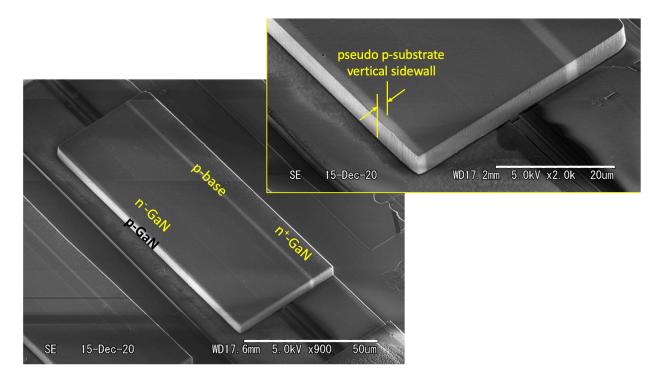

| Figure 4.10 Angled-view SEM images of the GaN islands with lateral n <sup>+</sup> -n <sup>-</sup> -p-n <sup>+</sup> junctions 100 |

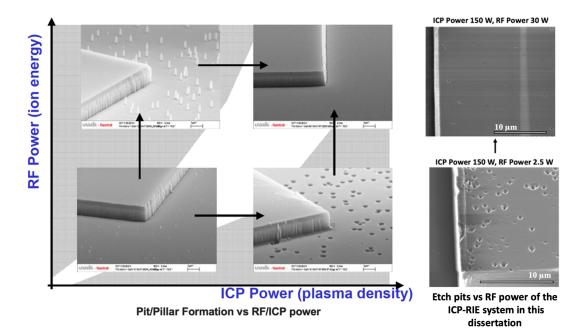

| Figure 4.11 The etch pits modulatable by RF power and ICP power of the ICP-RIE system100                                          |

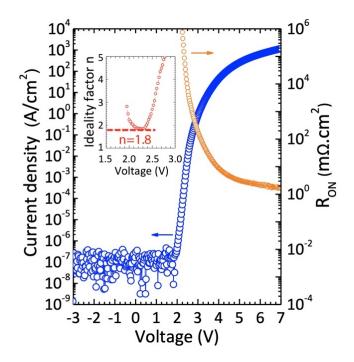

| Figure 4.12 Open-collector <i>I-V</i> characteristics of the GaN GLP-BJT                                                          |

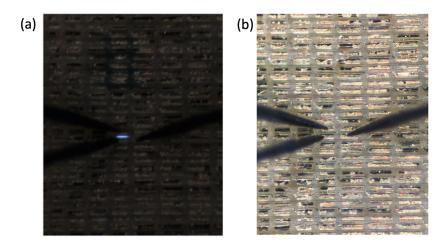

| Figure 4.13 Blue electroluminescence during the measurement under dark condition                                                  |

| Figure 4.14 TLM results of the Ohmic contact to <i>p</i> -base                                                                    |

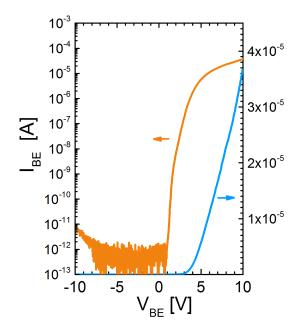

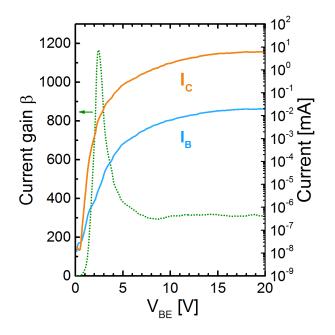

| Figure 4.15 The Gummel plot of the GaN GLP-BJT 104                                                                                |

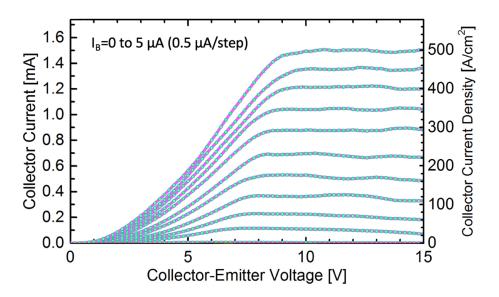

| Figure 4.16 Common-emitter output characteristics of the GLP-BJT 105                                                              |

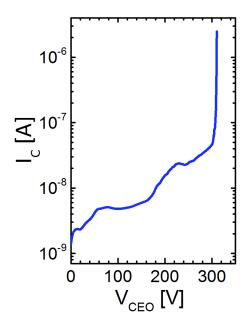

| Figure 4.17 Open base blocking <i>I-V</i> characteristics of the GLP-BJT 105                                                      |

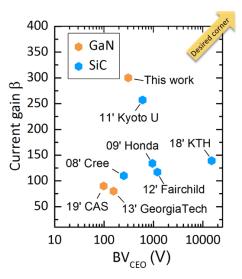

| Figure 4.18 Benchmark of common-emitter current gain vs open base breakdown voltage 107                                           |

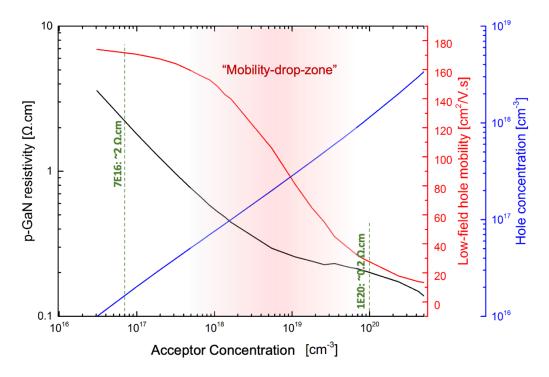

| Figure 4.19 Calculated hole concentration and <i>p</i> -resistivity against acceptor concentration 109                            |

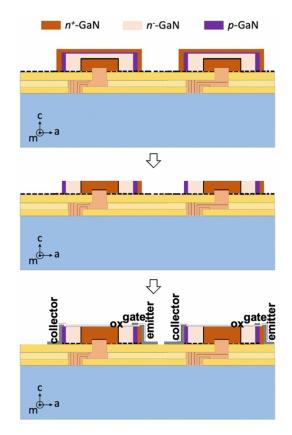

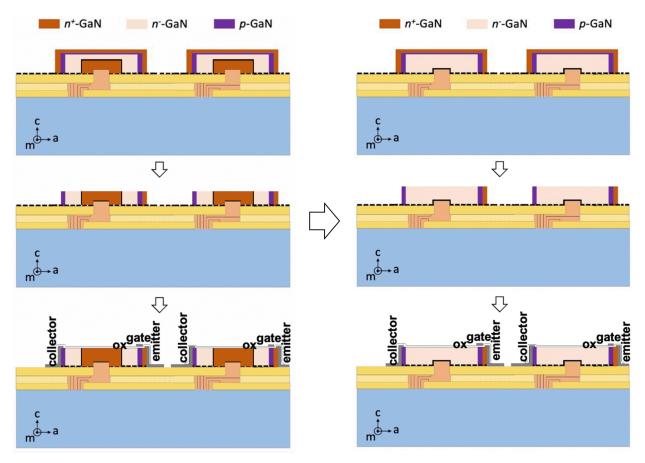

| Figure 4.20 Schematics of the key steps of the fabrication of IGBT on the ELO-GaN                                                 |

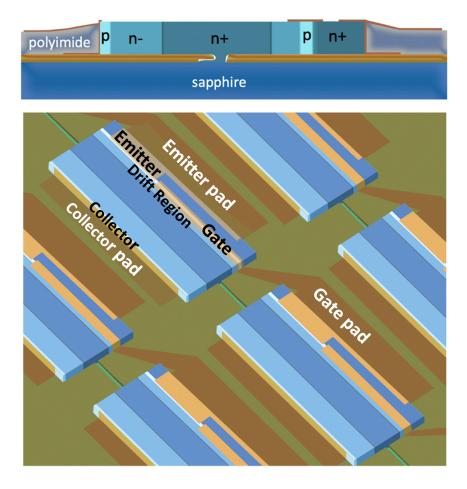

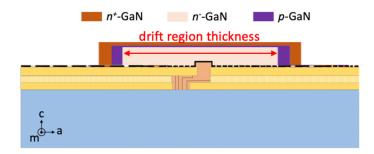

| Figure 4.21 Cross-sectional and stereographic illustrations of the IGBT 111                                                       |

| Figure 4.22 SEM image of the ELO-GaN island with fully lateral <i>p-n-p-n</i> homojunctions 112                                   |

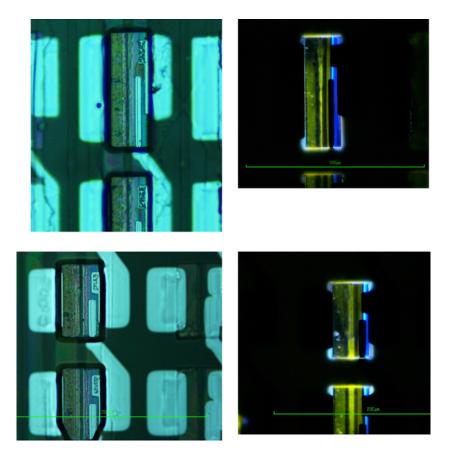

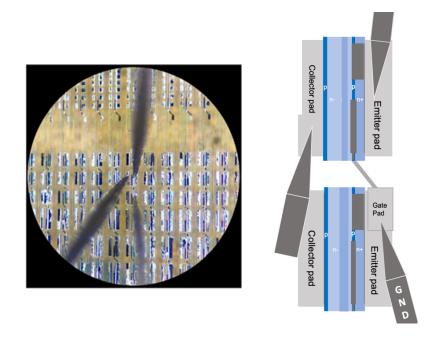

| Figure 4.23 The as-processed IGBTs on the ELO-GaN islands with varying lengths                                                    |

| Figure 4.24 The schematic of the IGBT being measured and images showing the real test114                                          |

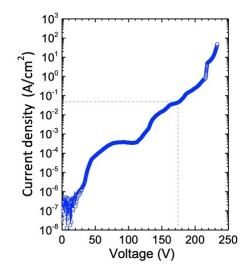

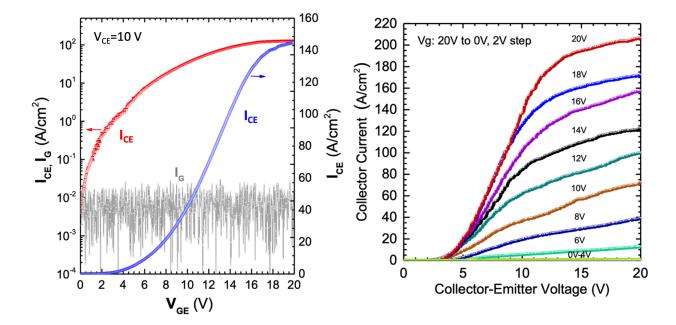

| Figure 4.25 The transfer and the output characteristics of the prototype GaN IGBT 115                                             |

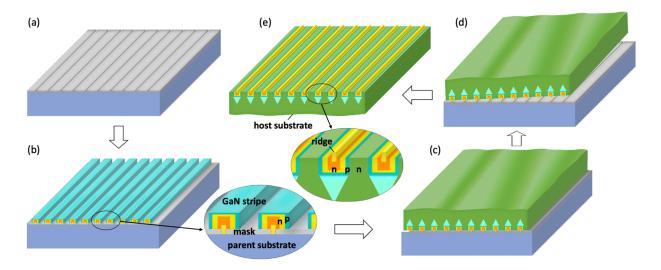

| Figure 5.1 Schematics of the bottom-up epitaxial layer transfer process and the product 122                                       |

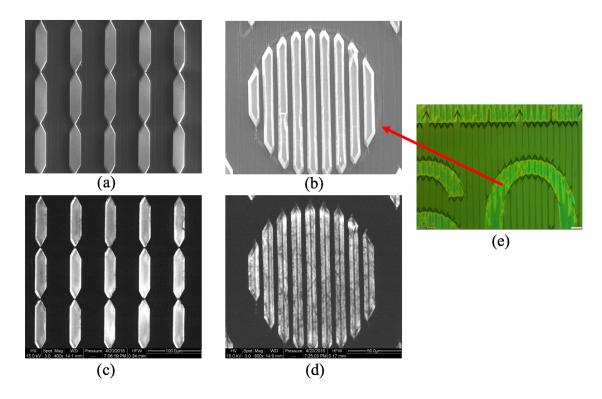

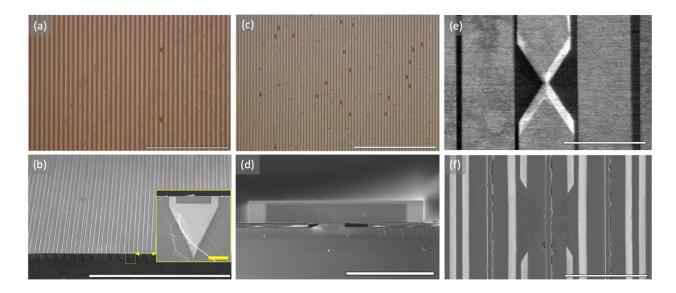

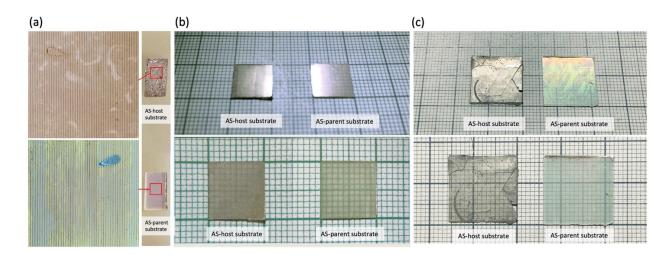

| Figure 5.2 OM and SEM images of the GaN samples after the 1st and 2nd epitaxial growths. 125                                      |

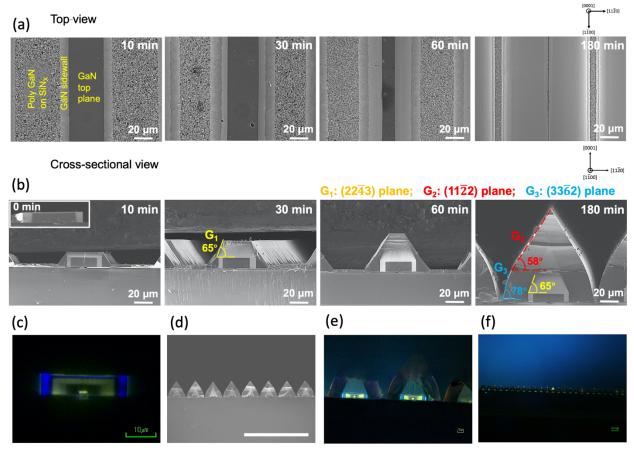

| Figure 5.3 Crystallographic and morphological evolution of the GaN stripe array at several growth                                 |

| times during the HVPE process prior to coalescence                                                                                |

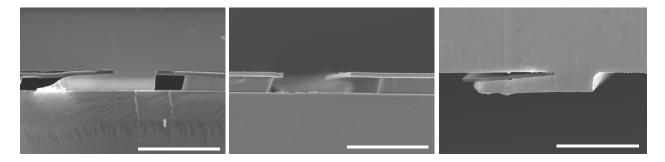

| Figure 5.4 Cross-sectional SEM images showing the details of the adjoining part between the GaN               |

|---------------------------------------------------------------------------------------------------------------|

| active layer and the mask-patterned parent substrate                                                          |

| Figure 5.5 A set of real photos showing varying-size GaN substrates with integrated active layer              |

| that were fully released from the equal sized diced mask-patterned sapphire substrates                        |

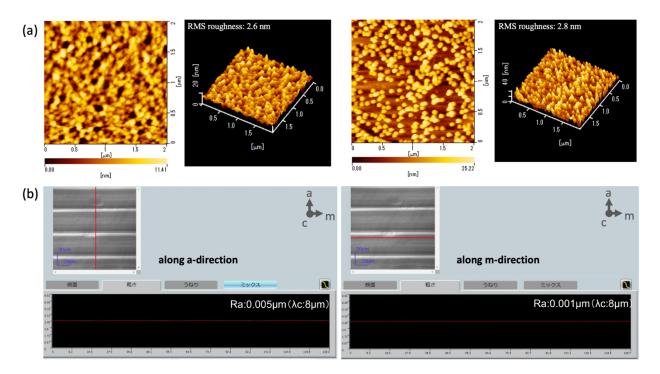

| Figure 5.6 (a) The plan-view and 3D-view atomic force microscopic images of the as-separated                  |

| (0001) GaN surface. (b) As-chemical mechanical polished (0001) GaN surface along <i>a</i> -direction          |

| and m-direction measured by confocal laser scanning microscopy                                                |

| Figure 5.7 The backside of substrate before and after the mechanical polish process                           |

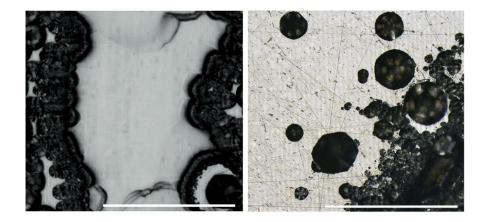

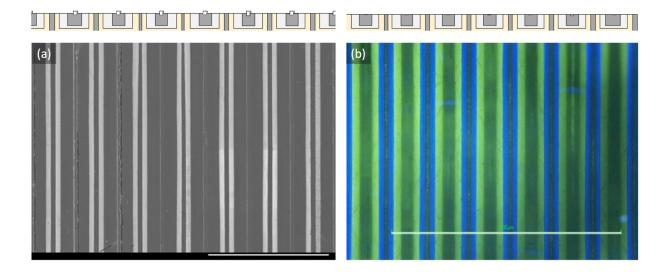

| Figure 5.8 Top-view scanning electron microscopic image of the $(000\overline{1})$ AS-GaN substrate and       |

| top-view fluorescence microscopic image of the $(000\overline{1})$ as-polished GaN substrate                  |

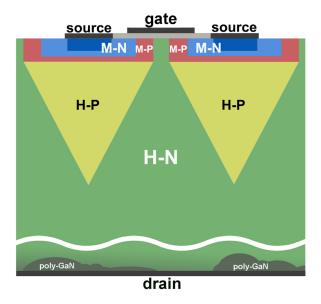

| Figure 5.9 Cross-sectional schematic illustration of the structure of a normally-off planar-gate              |

| vertical MOSFET fabricated on the GaN substrate134                                                            |

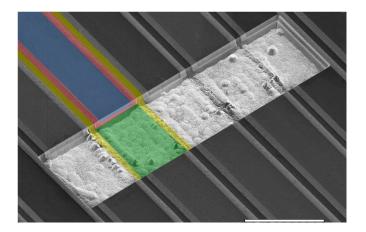

| Figure 5.10 The angled-view SEM image showing the doping regions and the trench used for                      |

| device isolation and pad support before deposition of oxide, metal, and polyimide filling 134                 |

| Figure 5.11 Fluorescence microscopic image of MOSFETs fabricated on the GaN substrate. 136                    |

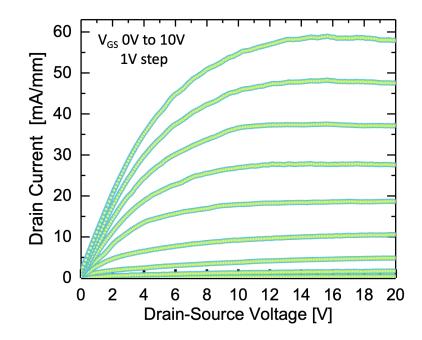

| Figure 5.12 The $I_{DS}$ - $V_{DS}$ characteristics of the MOSFET where $V_G$ ranged from 0V to 10V 137       |

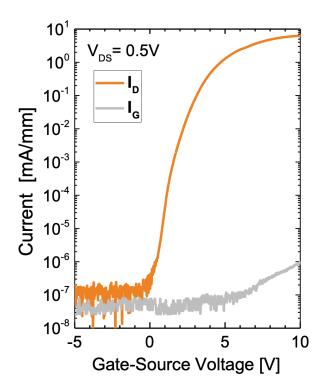

| Figure 5.13 The $I_{DS}$ - $V_{GS}$ characteristics of the MOSFET where $V_{DS}$ was 0.5 V                    |

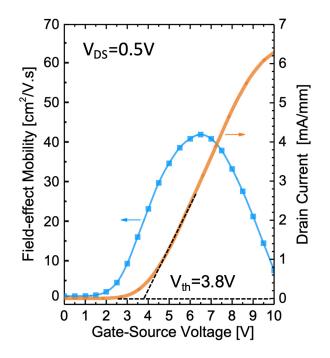

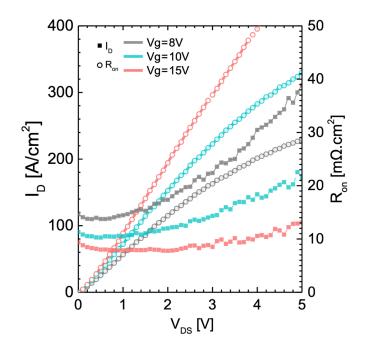

| Figure 5.14 The $I_{DS}$ - $V_{GS}$ characteristics and the field-effect mobility $\mu_{FE}$ - $V_{GS}$ curve |

| Figure 5.15 The $I_{DS}$ - $V_{DS}$ and $R_{ON}$ - $V_{DS}$ curves under various $V_{GS}$                     |

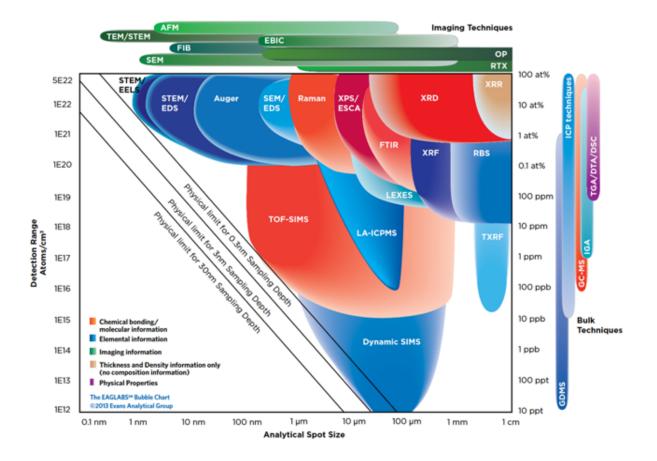

| Figure 6.1 Schematics showing the tradeoff between detection range and analytical spot size.144               |

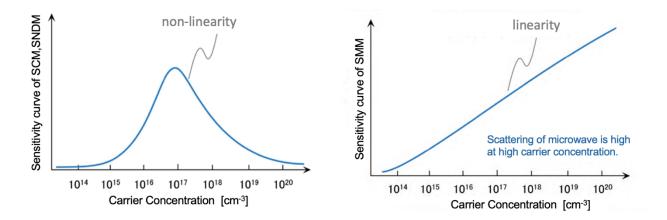

| Figure 6.2 The comparison of SNDM (or SCM) and SMM in their sensitivity                                       |

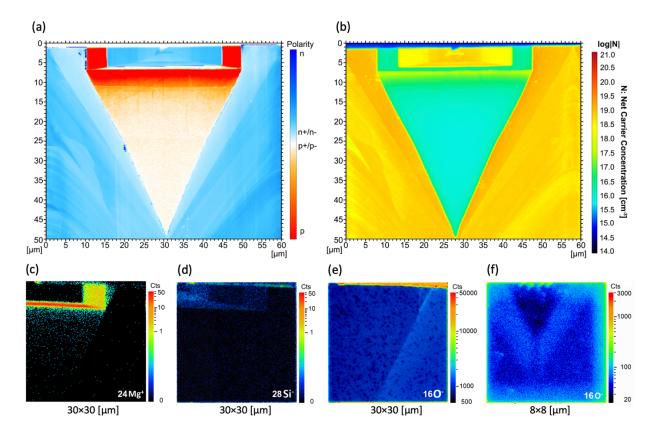

| Figure 6.3 Cross-section dopant, carrier, and elemental mappings of a repeating doping unit. 146              |

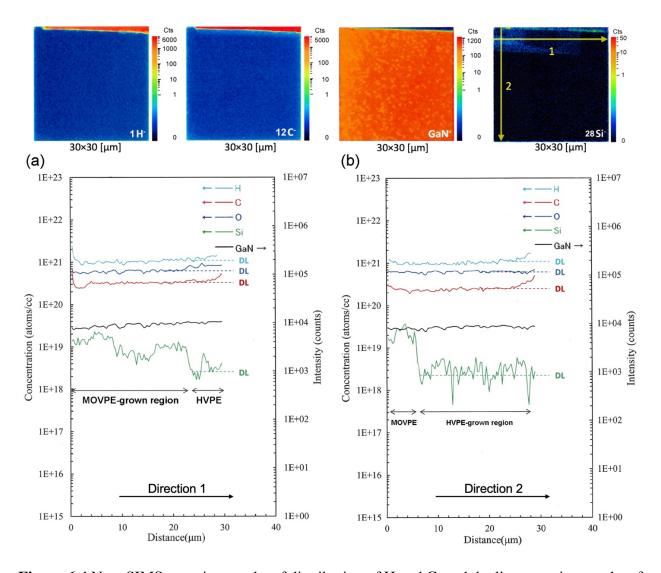

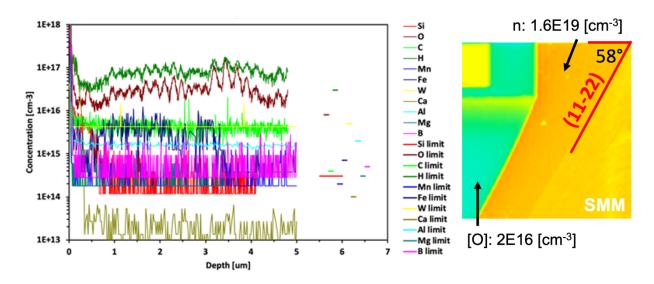

| Figure 6.4 NanoSIMS mapping results of H, C and line scanning results of H, C, O and Si 149                   |

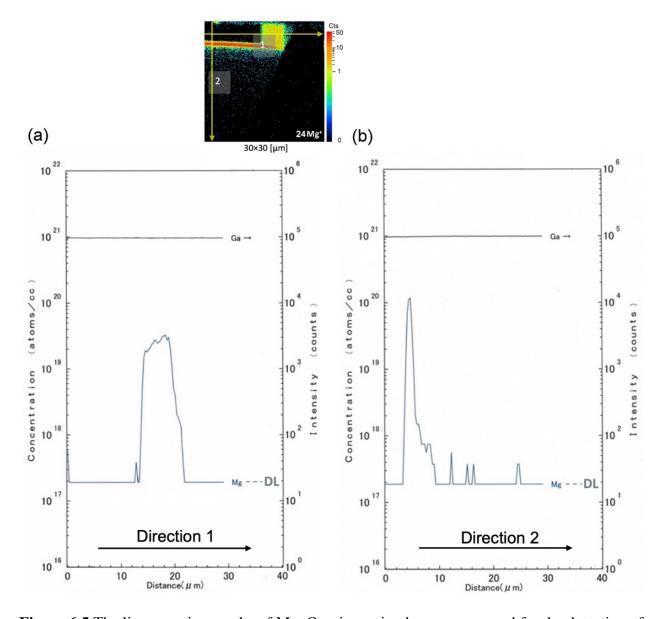

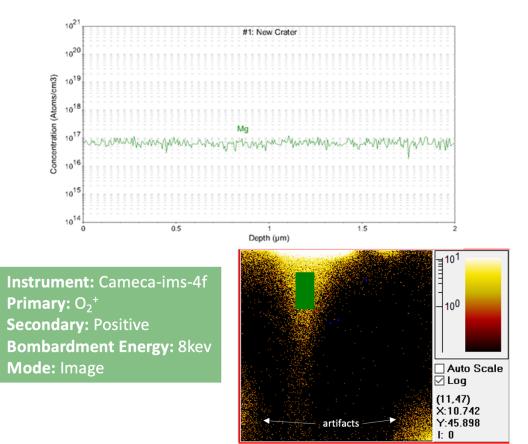

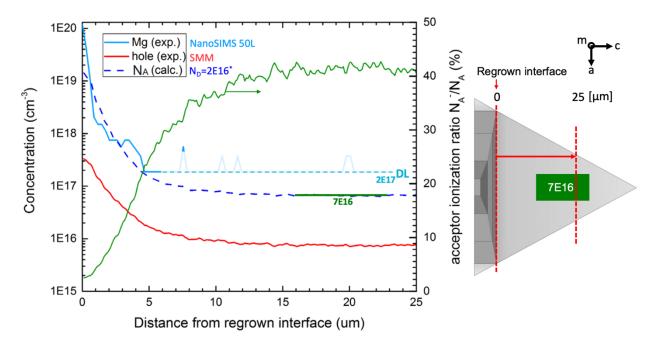

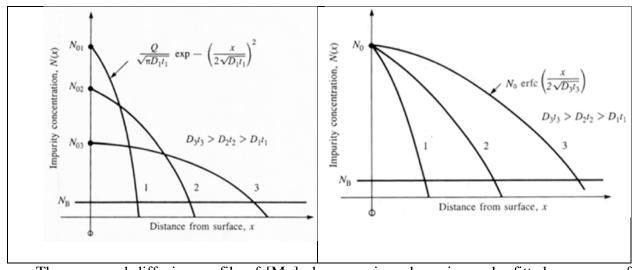

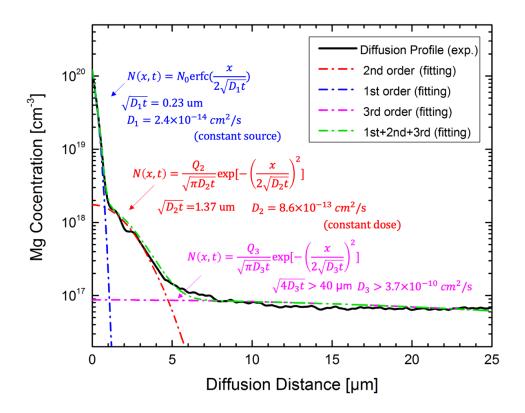

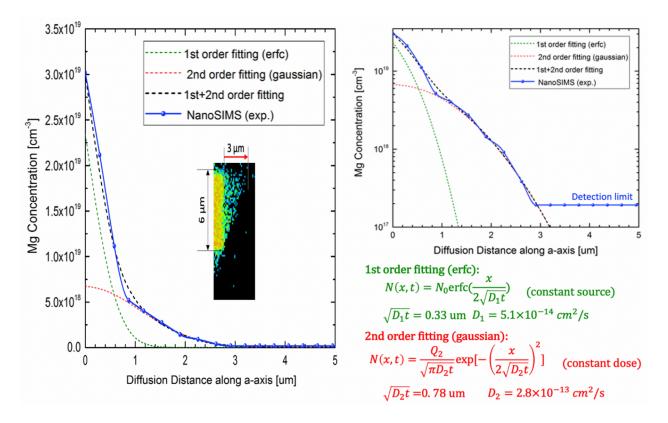

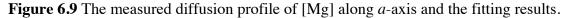

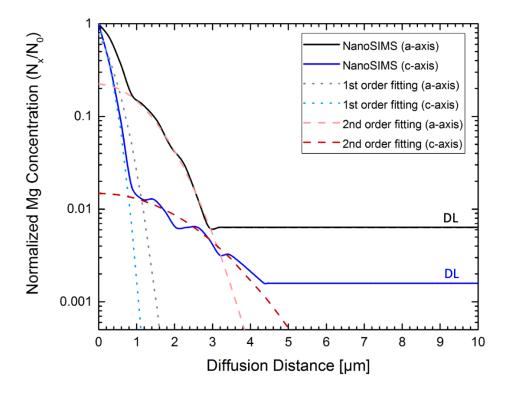

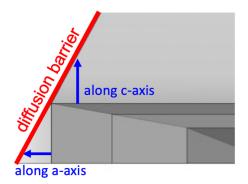

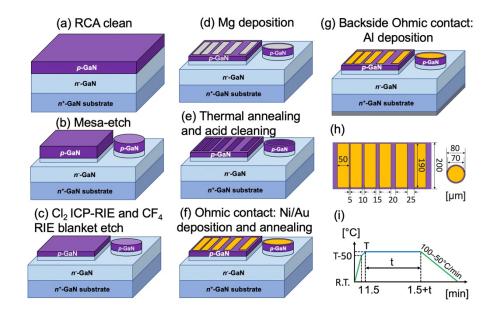

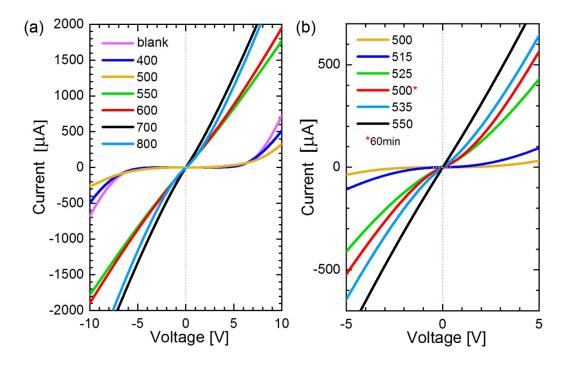

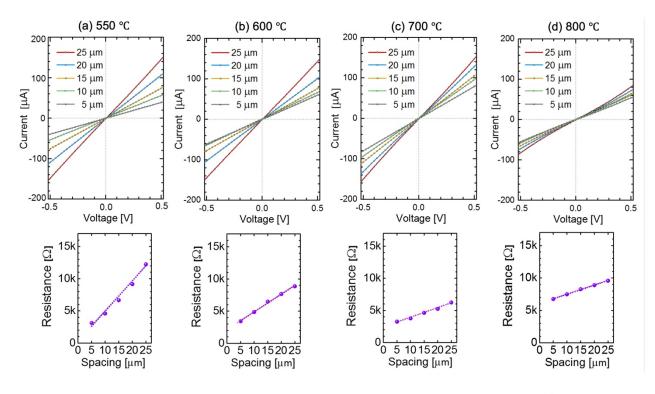

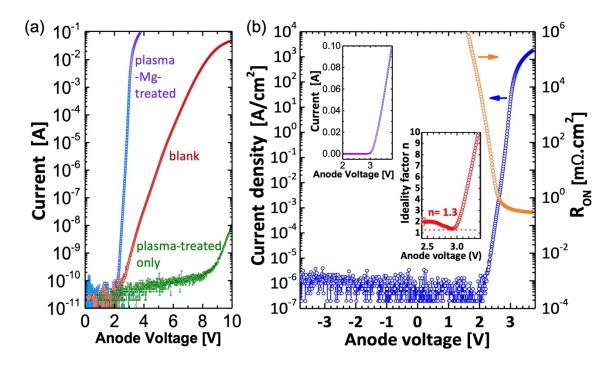

**Figure 6.6** TOF-SIMS depth scan revealing the [Mg] in the upper triangular *p*-GaN region... 152 Figure 6.7 The correlation among the distribution of [Mg] from the regrown interface measured by NanoSIMS 50L, the distribution of hole concentration measured by SMM and the distribution Figure 6.8 The measured diffusion profile of [Mg] along c-axis and the fitting results...... 155 Figure 6.10 The normalized diffusion profiles of [Mg] along c- and a-axis and fitting curves. 157 Figure 6.11 The presumed diffusion barrier at the boundary of the triangle which limited the Figure 6.13 The dynamic SIMS result of a reference GaN sample grown on c-plane GaN substrate Figure 6.14 Schematic illustrations of the key steps of the fabrication flow for the p-GaN TLM Figure 6.15 The *I-V* characteristics of the blank sample and path II-samples with varying T. 164 Figure 6.17 (a) The I-V characteristics of the plasma-treated samples with and without Mgtreatment (blank sample). (b) TLM result of the plasma-treated sample with Mg-treatment. ... 166 Figure 6.18 Forward I-V characteristics of the PNDs with dual plasma-Mg-treatment...... 167

| Figure 7.3 The <i>p</i> -GaN sidewall exposed by dry etch and the associated plasma damages recovered |

|-------------------------------------------------------------------------------------------------------|

| by deposition of Mg and thermal annealing174                                                          |

| Figure 7.4 Monolithic integration of different GaN devices after ELO-GaN island transfer 176          |

# LIST OF TABLES

## ACKNOWLEDGMENTS

First and foremost, I would like to express my sincere gratitude to my Ph.D. advisor Professor Ya-Hong Xie for his mentorship over all these years. Not only is he a knowledgeable scientist in multiple academic domains, but he also possesses immensely analytical and deduction talents who is good at rigorous brainstorming with students. Under his subtle influence, I learnt to weigh a deep understanding of fundamentals by repeated reading classics equally important to doing experiments. Constantly aware of his teachings and the emphasis to construct a clear physical picture in mind when faced with all kinds of complex issues in the real conditions, I greatly benefited from it as it helps me to effectively examine the killer factor leading to the various experimental failures and also to unravel countless mysteries in the experiments especially when we venture deep into the unexplored domains such as trying to taking innovative measures in material growth and device processing aspects to solve the issues of ELO-GaN.

I would also like to express my deep thanks to Professor Hiroshi Amano for his utmost kindness and generosity in being my host researcher at Nagoya University during the last three years, when I was fortunate enough to conduct research in a world's leading lab in nitrides semiconductor with access to unlimited research resources. If it weren't for his kind financial support, the experiments in this dissertation would not have existed. Moreover, I was greatly impressed and touched by his personality of humility, optimism, and spirit of dedication. Being a diligent and self-disciplined researcher, he keeps himself in the office from morning to night and only takes one day off every year. I really enjoyed those numerous weekends when we discussed the exciting progress together in his office, as I can always benefit from his rich insight into my research field as well as his warm encouragement.

I am also grateful to the other honorable committee members whom I have known very well from different courses long before they joined the thesis committee. I would like to offer my very special thanks to Professor Dwight C. Streit who actually introduced GaN to me and inspired my interest in this amazing direct wide bandgap semiconductor material when I was taking the graduate course MAT-SCI 222 taught by him. Under his guidance, I made a term project on the GaN and was highly appraised by Prof. Streit at the end. Without this fortunate opportunity, I may never have determined my mind to choose GaN as the topic of my research career.

I would also like to sincerely thank Professor Jaime Marian who greatly helped me improve the understanding regarding mechanical properties of materials which is usually the weak point for many electrical engineers and semiconductor device researchers. Being a great instructor, he effectively imparted the fundamental knowledge to me in an easily understandable language and I finally scored A+ in his course of MAT-SCI 143A with hard efforts. These sets of knowledge, as well as those acquired from his course of MAT-SCI 243C, concretely helped me later in dealing with multidisciplinary issues in GaN such as long-range stress fields of dislocations, converse piezoelectric stress-induced cracks, thermal stress-enabled void-assisted substrate separation which contributed significantly to my dissertation.

I am also very grateful to Professor Kang L. Wang who kindly accepted the invitation to serve on my committee from the department of Electrical Engineering. Professor Wang is one of my idols who represented the perfect image of a researcher and advisor, due to which reason I also audited his course EE 224 on solid state electronics which expanded my horizon by offering fundamentals from a deeper solid state physics level and the angle of carrier transport slightly different from many other popular textbooks on semiconductor physics. I feel really honored to later have his acceptance to join my Ph.D. thesis committee.

In addition to the committee members, I would also like to offer my heartfelt thanks to the professors and colleagues whom I have been fortunate to work with and friends who aided my Ph.D. research. I am deeply grateful to our collaborators with Peking University-Professor Xiaodong Hu and some of his team members: Dr. Hua Zong, Dr. Shengxiang Jiang and Mr. Guo Yu-for carrying out the MOVPE growths according to my design. I also really enjoyed the moments when I traveled with Prof. Hu in Japan and China who is not only a professor but also a friend of mine despite age differences. I would like to appreciate the kind assistance from Professor

Yoshio Honda and Professor Shugo Nitta to the experiments carried out at Nagoya University. I am really grateful to Dr. Jian Shen for carrying out the HVPE growths for me at Akasaki Research Center in Nagoya University. I would also like to thank Dr. Yuto Ando and Mr. Yaqiang Liao for teaching me semiconductor processing skills in the cleanroom and acknowledge the helps from Dr. Guohao Yu, Dr. Qiang Liu, Dr. Ting Liu, and Mr. Wentao Cai for teaching me different kinds of characterization techniques. In addition, special thanks are offered to Dr. Weifang Lu with Meijō University (Nagoya, Japan) who provided the helpful method of inserting AlGaN underlayer in the ELO-GaN islands and to Mr. Takeru Kumabe for the helpful discussions on the BJT/HBTs and plasma etch-induced damages to *p*-type GaN.

Besides, I would like to acknowledge that Chapter 4, Section 4.2–4.4 is a modified version of "Jia Wang, Ya-Hong Xie, and Hiroshi Amano, High-Gain Gated Lateral Power Bipolar Junction Transistor, *IEEE Electron Device Letters*, 42, 9, 2021" on copyright grounds.

I want to especially acknowledge Japan-US Advanced Collaborative Education Program (JUACEP) for bridging the Engineering School of UCLA and that of Nagoya University together. It is with the help of such bridge that I finally got in touch with Prof. Amano, which later completely shifted the landscape of my Ph.D. study and research career path.

In a higher sense, the very fact that the fruitful research in this dissertation was achieved based on a close collaboration between the three universities across three different countries: United States, Japan and China allows me to deeply recognize the truth that science should really transcend the national borders.

In addition to those who helped with my Ph.D. research, I would also truly wish to say thank you to my dear friends and loved ones with whom I spent the happy time together in the United States, Japan, and China in the past years.

Last but not least, I would like to offer my utmost gratitude to my mom and dad for their limitless love and support throughout my life, words cannot express my gratitude and love to my family members.

# VITA

## Education

- 2007-2011 B. Eng. in Materials Science and Engineering Tongji University, Shanghai, China

- 2012-2015 M. S. in Materials Science and Engineering University of California, Los Angeles

#### **Academic or Professional Employment**

- 2015-2016 Senior Technical Officer Layertech Co. Ltd., Shanghai, China

- 2018-2021 Technical Assistant Staff IMaSS, Nagoya University, Japan

#### **Selected Publications**

1. **Jia Wang**, Ya-Hong Xie, and Hiroshi Amano, "High-Gain Gated Lateral Power Bipolar Junction Transistor," *IEEE Electron Device Letters*, vol. 42, no.9, pp. 1370–1373, 2021.

2. (*Editor's Pick*) Jia Wang, Guo Yu, Hua Zong, Yaqiang Liao, Weifang Lu, Wentao Cai, Xiaodong Hu, Ya-Hong Xie, and Hiroshi Amano, "Non-polar True-lateral GaN Power Diodes on Foreign Substrates," *Applied Physics Letters*, vol. 118, no.21, 212102, 2021.

3. **Jia Wang**, Shun Lu, Wentao Cai, Takeru Kumabe, Yuto Ando, Yaqiang Liao, Yoshio Honda, Ya-Hong Xie, and Hiroshi Amano, "Ohmic contact to p-type GaN enabled by post-growth diffusion of magnesium," *submitted to IEEE Electron Device Letters*, 2021.

4. **Jia Wang**, Jian Shen, Hua Zong, Shengxiang Jiang, Yuto Ando, Guohao Yu, Weifang Lu, Ting Liu, Wentao Cai, Shugo Nitta, Yoshio Honda, Xiaodong Hu, Ya-Hong Xie, and Hiroshi Amano, "Bottom-up epitaxial layer transfer enables wide bandgap semiconductor substrate with laterally patterned *p*-*n* junctions," *submitted to Nature Communications*, 2021.

# **Patent Pending**

**Jia Wang**, Ya-Hong Xie, and Hiroshi Amano, "Epitaxy-Enabled Substrate Transfer," U.S. Provisional Patent Application No. 63/113,388, 2020.

## Conferences

Jia Wang, Hiroshi Amano, Ya-Hong Xie, "3D GaN Power Switching Electronics: A Revival of Interest in ELO," In 2021 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), pp. 1-3. IEEE, 2021.

2. **Jia Wang**, Shengxiang Jiang, Hua Zong, Yaqiang Liao, Ting Liu, Jian Shen, Yuto Ando, Yoshio Honda, Xiaodong Hu, Hiroshi Amano, and Ya-Hong Xie, "Vertical PN Junction-based GaN Power Diode.", Oral presentation at: 2019 51th International Conference on Solid State Devices and Materials (SSDM); Sept., 2019; Nagoya, Japan.

# **Chapter 1**

# Introduction

#### 1.1 Background

### **1.1.1 Power Switching Electronics**

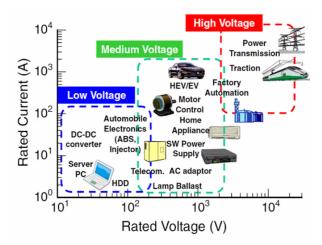

With the advent of information era characterized by revolutionary in the silicon (Si)-based computing and communication industries, energy technology is becoming more critical than ever before. The high demands for energy has pushed for increased efficiency in power conversion systems [1], [2]. For one thing, hybrid electric vehicles are becoming cost-effective and popular, and there is growing interest in the development of all-electric transportation to reach a carbon-neutral society. For another, the electricity transmission and distribution infrastructure is amid rapid transformation in its history and a flexible and robust smart electricity grid is needed. Semiconductor switches are at the heart of power conversion systems. In 2020, electricity accounts for 40% of the total energy consumption, whereas more than 30% of electricity undergoes at least one stages of transistor-based power conversion before reaching every household. It is expected that the share would reach 80% by the year of 2030 [3].

This solid-state energy conversion is widely referred to as "power switching electronics", which constitutes the backbone of electricity transmission, distribution, and processing much like signal electronics is used for constructing the information highway.

Power switching electronics are the major factor that determines the performance, reliability, and cost of the overall power conversion system, which is needed in many applications including electric/hybrid vehicles and power grids. Silicon remains today's most widely employed powerswitching semiconductor material, and some 600 V-class Si-based devices such as super-junction MOSFETs have achieved outstanding performance with the on-resistance as low as 35 m $\Omega$ .cm<sup>2</sup> [4], which is approaching the material limit of Si. In order to meet the ever-increasing demand of power conversion, the efficiency of the power switching electronics has to be improved by exploring other semiconductor materials other than Si. The semiconductors having wide-bandgap (WBG) are the ideal choice to satisfy the requirement of power switches which inherently can achieve better voltage blocking capability and current handling capability. The former is often compared by the breakdown voltage ( $V_{BR}$ ) at OFF-state and the latter one is often compared by the specific on-resistance ( $R_{on.sp}$ ), i.e., the differential resistance of the device in the ON-state multiplied by the device area.

**Figure 1.1** A schematic summary of various applications for power switching electronics sorted by the rated voltage (V) and rated current (A) [5].

#### 1.1.2 Critical Electric Field in a WBG Semiconductor

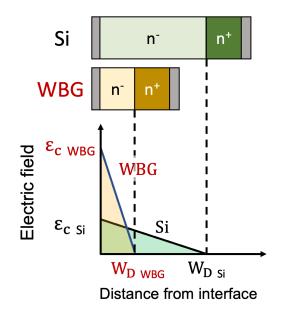

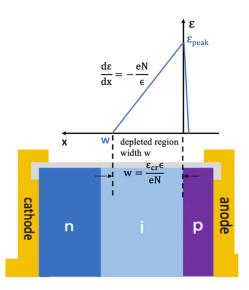

Why could a WBG semiconductor-based power device have higher breakdown voltage and lower specific on-resistance than its Si-based counterpart? The answer can be better illustrated by using the simple model of a one-sided junction, when all the depletion region is considered on the n-side of the junction. Under reverse bias, the electric field  $\varepsilon_c$  decreases along the junction distance with the slope being proportional to N<sub>d</sub>, the net doping concentration in the drift layer. When a Si

diode and a WBG semiconductor diode withstand the same reverse bias, the area of the triangles enclosed by the field ( $\epsilon$ )-distance (W) plot in Fig. 1.2 is the same.

Figure 1.2 Comparison of Si and WBG semiconductor in a one-sided junction model which highlights the merit of a high  $\varepsilon_c$ .

Because WBG semiconductor can intrinsically tolerate higher critical field  $\varepsilon_c$ , if under the same breakdown voltage, i.e., when the area of triangles is equal, then the WBG semiconductor can have shorter  $W_D$ -thinner depletion region with higher ionized net charge density, which leads to a smaller specific resistance of the drift layer during the ON state. Therefore, WBG can achieve lower specific on-resistance while preserving high breakdown voltage. By the same token, in a p<sup>+</sup>- n<sup>-</sup> junction diode, the derivation of V<sub>BR</sub> and R<sub>on.sp</sub> are as follows:

$$V_{BR} = V_{app} + V_{bi} = \int_{-x_p}^{x_n} \varepsilon \, dx = \frac{x_p^2 e N_A}{2\epsilon} + \frac{x_n^2 e N_D}{2\epsilon} \approx \frac{x_n^2 e N_D}{2\epsilon}$$

(1.1)

$$R_{on,sp} = \rho_p x_p + \rho_n x_n = \frac{x_p}{eN_A \mu_p} + \frac{x_n}{eN_D \mu_n} \approx \frac{x_n}{eN_D \mu_n}$$

(1.2)

where  $V_{app}$  is the applied reverse bias,  $V_{bi}$  is the built-in voltage,  $x_n$  and  $x_p$  are the depletion region thickness on the p-type and n-type semiconductor side.

In general, figure of merits (FOMs) which usually consist of several key material properties are defined and used as benchmark to compare the device performance. In the field of power switching electronic, Baliga's FOM is one of the most commonly used FOMs, which was initially proposed by Dr. B. Jayant Baliga who is best known for his pioneering work in power semiconductor devices [6]. The Baliga's FOM (also written as BFOM or  $FOM_{Baliga}$ ) can be expressed as follows:

$$FOM_{Baliga} = \frac{V_{BR}^2}{R_{on,sp}} = \frac{\varepsilon_c^3 \mu_n \epsilon}{4}$$

(1.3)

here  $\epsilon$  is the material's permittivity (dielectric constant),  $\mu_n$  is the electron mobility (for singlesided junction where n-side is lightly doped), and  $\epsilon_c$  is the critical electric field which is defined as the maximum field in a one-sided infinite planar junction at the onset of breakdown. Since FOM<sub>Baliga</sub> is derive from the model of single-sided junction where only the resistance of quasineutral region of the drift layer is taken into the consideration of the specific on-resistance (this is true and mostly accurate when ignoring the effects of high-level minority injection), FOM<sub>Baliga</sub> should be best understood as the performance limit of a unipolar power device [7].

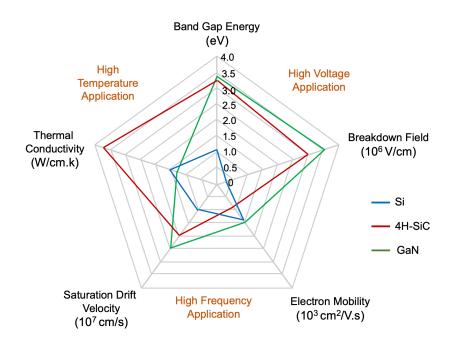

#### **1.1.3 Material of Choice**

We can tell from Baliga's FOM that the critical electric field  $\varepsilon_c$ -the term in the cubic form in the Baliga's FOM's expression-is the key property for a power semiconductor material. In general, gallium nitride (GaN) and silicon carbide (SiC) are the two most studied WBG materials. If we compare some key material properties of Si, 4H-SiC (the most common polymorph of SiC) and GaN (wurtzite) by using a radial pentagon in Fig. 1.3, we may find out that GaN possesses higher critical field than SiC and Si, making it a good choice for power switching electronics. Specifically, compared to 4H-SiC which features largest bandgap (3.26 eV at 300K) and critical breakdown electric field  $E_c=2.5-3.0$  MV/cm among all the common polymorphs of SiC [8], GaN has higher breakdown field strength with an estimated value of 3.3–3.7 MV/cm, better on-state performance under higher frequency operation [8]. In terms of avalanche breakdown, the critical field is determined by the width of bandgap. As such, the fact that GaN has wider bandgap than SiC lays the theoretical foundation for the anticipated superior performance of a GaN-based power electronic device [9].

Figure 1.3 A comparison between the key materials properties of Si, 4H-SiC and GaN.

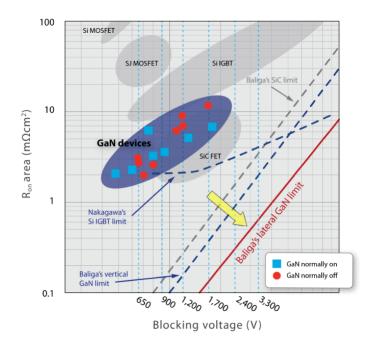

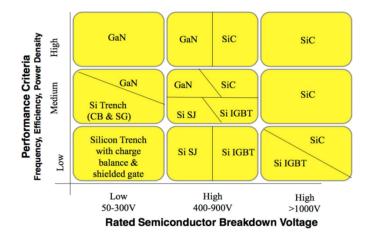

Due to these superior properties, GaN-based power electronic devices are considered to hold the promise of much better performance compared to the Si incumbents and even their SiC rivals in critical factors such as on-state loss, switching loss and the ability to block high voltage in the off-state. Fig. 1.4 summarizes the specific on-resistance and blocking voltage of all the common types of power switches. Despite the theoretical anticipation of superior power performances that GaN should possess over SiC, the de facto applications of GaN and SiC based power electronics as summarized in Fig. 1.5 presents a stark contrast. In other words, even though GaN has a higher limit than SiC, the best reported performance of GaN-based transistors remains inferior to that of SiC and is significantly below the predicted performance limit. In view of application sorted by voltage ratings, there is a separation line of ~600V in the field of median-and-high frequency power electronics, above which SiC is dominating the status quo-the material of choice for the most demanding power switching applications, i.e., in power grids, whereas GaN-based power transistors have limited market share in low and median power applications with VBR<600 V. Then what is it that causes the discrepancy between theoretical and de facto performances? The answer to this question is crucial which also underlies the motivation of this dissertation, as shall be elaborated in the subsequent section. Secondary to this, one can also observe from Fig. 1.5 that in the low-and-median frequency applications, Si is widespread used throughout the entire voltage rating range. In fact, WBG-based power devices as a whole represents still a very small fraction of power electronic market (\$160M: \$16B) today and even smaller share (~0.05%) of the total semiconductor market [10].

**Figure 1.4** The material-limit curves of Si, SiC and GaN and  $R_{on,sp}$  versus  $V_{BR}$  for all the common types of power switches (the yellow arrow indicates the desired direction) [11].

Figure 1.5 Applications of power electronics sorted by voltage and frequency [10].

## 1.2 Improvement for GaN as Power Switching Electronics

## 1.2.1 GaN with Low Dislocation Density

Fundamentally, material defects usually account for the deviation from predicted device performance that is based on the abstract physical model with perfect semiconductor material. In terms of WBG materials, if there are numerous states introduced into otherwise forbidden band, the benefits of having a wide bandgap would be seriously compromised. Therefore, it is important to investigate the effects of defects on the device performance. And these defects, shallow or deep in their relative energy level to the band-edge, generally arise from impurity atoms or vacancies (0D), dislocations (1D) or interface/surface and stacking faults (2D). Unraveling their origins is also important to evaluate their relative influences in different WBG materials at material growth or device processing stage. For example, doping is one of the main drawbacks in SiC devices, which in practice can only be achieved by means of ion implantation. However, ion implantation in SiC will heavily damage the lattice and create point defects which are hard to recover despite thermal annealing post-treatment [13]. Worse than SiC, not only is GaN difficult for effective p-type doping, but also it has greater problem in its crystal growth.

Unlike SiC and Si, the growth of bulk crystal of GaN is severely hindered by the extreme high temperature (2225 °C) and high pressure (6.5 GPa) [12] due to the high equilibrium vapor pressure of  $N_2$ , making it almost impossible endeavor trying to mass produce crystals of any significant size (e.g., 2-inch diameter) as required by the economy of manufacturing. Consequently, the production of GaN wafers relies entirely on hetero-epitaxy of GaN on foreign substrates such as Si, sapphire and SiC with progressively higher substrate cost. The most widely used growth technique is vapor phase epitaxy (VPE). Probably the most challenging aspect of GaN hetero-epitaxy is the lacking of lattice matched substrates thus the unavoidably high density of dislocations and the associated reliability challenges [13]. For example, sapphire-the widespread employed heterosubstrate today for mass production of white light LED chips, has lattice mismatch of 8% to GaN, leading to a dislocation density of  $10^8-10^9$  cm<sup>-2</sup>.

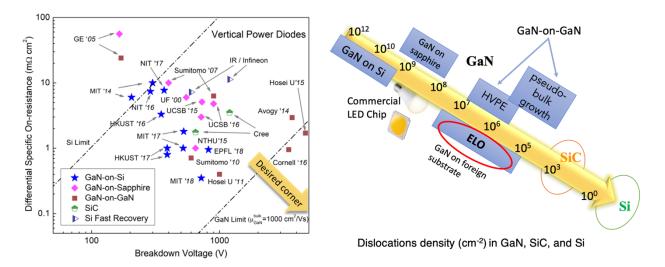

**Figure 1.6** The correlation of GaN power device performance (left image from [14]) with dislocation density in GaN material grown on different substrates (right image).

It is believed that the presence of high density of dislocation is the main reason for the degraded breakdown performance in GaN based power electronics. Such correlation might be better revealed in Fig. 1.6 which combines the performance benchmarking of GaN vertical power

diodes fabricated on different substrates with a schematic summary of GaN with varying orders of dislocation density grown on different substrates. As it appears in the right schematic, GaN has typically the highest dislocation density  $(>10^{9} \text{ cm}^{-2})$  on Si due to the largest lattice misfit, followed by the median dislocation density of down to  $\sim 10^8$  cm<sup>-2</sup> for GaN on sapphire, and the lower dislocation density GaN in the range of 106–108 cm<sup>-2</sup> for GaN-on-GaN substrate prepared by HVPE or pseudo-bulk growth techniques such as ammonothermal or sodium flux method. On the other hand, in the left figure, there is also a similar trend-from the blue stars indicating GaN diodes on Si, to the pink diamonds indicating GaN diodes on sapphire, and finally to the crimson squares indicating GaN diodes on GaN substrate. Such trend pointing to the desired lower-right corner is parallel to the direction of the golden arrow pointing to lower dislocation density. In some sense, the correlation also represents the interplay the between microscopic defects in the material science domain to the macroscopic performance in the electrical engineering domain. It was also observed experimentally that dislocation is closely associated with current leakage paths due to deep level traps [15]. The enormous build-up of leakage current causes so-called premature breakdown, which can occur when the critical field and  $V_{BR}$  are much less than the predicted values. To date, a couple of leakage mechanisms (trap-assisted space charge limited current and variable range hopping conduction along dislocations) have been invoked for explaining the behavior of GaN devices in the literature [16][17]. It is also known that dislocations tend to be decorated by points defect (vacancy and impurities) because of the interaction of the stress fields generated by the dislocation and point defect (i.e., the cancellation or reduction of stress fields provides driving force for point defects to decorate a dislocation). The trapped electrons hop between deep levels induced by the grouped point defects decorating along threading dislocation then constitute leakage paths under high field.

Therefore, there is a pressing need to minimize the dislocation density in GaN in order to enhance the performance of power devices. As shown in Fig. 1.6, localized dislocation filtering techniques such as epitaxial lateral overgrowth (ELO) or film thickening via halide vapor phase epitaxy (HVPE) have been employed to achieve threading dislocation density (TDD) as low as 10<sup>6</sup> cm<sup>-2</sup>, which is three orders of magnitude lower than that of the GaN-on-sapphire films used for light-emitting diodes (LEDs) today [13]. The detailed discussion of ELO-the main topic of this dissertation, will be arranged in the next section.

Compared to ELO, thickening has been used more in recent years due to its effectiveness in the reduction of TDD, as most of the commercially available "bulk GaN substrate" (freestanding GaN) are actually derived from thick crystal films grown by HVPE on foreign substrates and subsequently removed from the substrate. In principle, by growing thicker films, the reaction between neighboring dislocations eliminates each other due to the cancelation of stress fields of individual dislocations-a process known as dislocation annihilation. Such reaction between neighboring dislocation causes the reduction of TDD. However, such reduction has a theoretical limit since the probability of dislocation annihilation reduces with increasing film thickness until approaching zero asymptotically. This is fundamentally because the strength of the stress field of individual dislocation decays reciprocally with distance so that the thermal fluctuation will dominate over the weak attraction beyond certain separation distance.

## 1.2.2 Selective-area Doping Capabilities

In order to improve the performance of GaN-based power devices, with the gradual improvement in the material quality of GaN with low dislocation density over the past decade, doping has resurfaced as another critical bottleneck. In fact, the dislocation density of GaN has reached a low level in the GaN devices fabricated on GaN substrate so that the avalanche

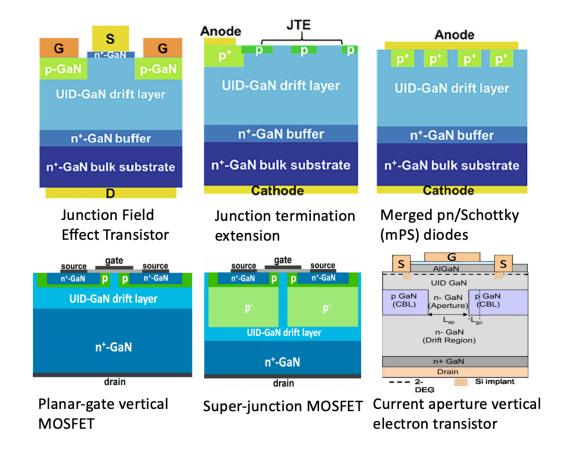

breakdown capability has been demonstrated and the critical E-field approached the material limit of GaN [18]. Nevertheless, on the other hand, the effective p-type doping of GaN still poses the issue. This is fundamentally because that magnesium (Mg) with which the first demonstration of p-type conduction in GaN was realized [19], is still the only dopant available to produce p-type GaN till today [20]. However, because of a high ionization energy (~200 meV), the hole concentration is rather limited in even heavily doped p-GaN due to the incomplete ionization of acceptors [21][22]. In addition, in-situ corporation of Mg impurity during the vapor phase epitaxy is still the dominant methodology for p-type doping of GaN, which would only produce planar and blanket p-type GaN thin film rather than selective-area p-type GaN. Specifically, the ability to obtain selective area p-type doping profile of GaN, or rather, to obtain laterally patterned p-n junctions, is the bottleneck to realize a plethora of power electronics with advanced structures and functions [23]. Figure 1.7 schematically illustrates some of these advanced electronics with laterally-patterned p-n junctions, including junction field-effect transistors (JFETs), p-GaN guard rings for junction termination extension, merged p-n/Schottky (mPS) diodes, planar-gate normally-off vertical MOSFETs [24], super-junction MOSFETs, and current aperture vertical electron transistors (CAVETs) [25].

In principle, in some of these applications, p-type region greatly assists in the edge termination by easing the field crowding at the edge, such as in the cases of guard ring or mPS diodes [26]. Alternatively, p-GaN region may also help reduce the net charge density  $|N_D-N_A|$  in the space charge region (depletion region) of the neighboring n-regions in the OFF state so that the reverse blocking voltage is increased due to the reduced slope of the E-field (proportional to  $|N_D-N_A|$ ) along the depletion region [27]. Finally, the p-region will also help decrease the specific on-resistance by high-level minority injection into n-region [6], [28]. Amongst the aforementioned three merits, the first will help to approach the infinite planar junction-the ideal unipolar model for the Baliga's FOM. And the second and third merits will help go beyond to the performance limit set by the Baliga's unipolar model by achieving the limit-breaking high  $V_{BR}$  and limit-breaking low Ron,sp, respectively.

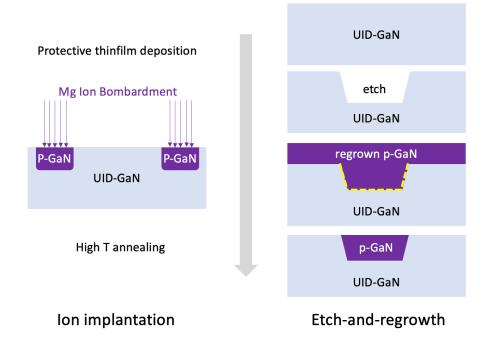

**Figure 1.7** Schematic illustrations of several advanced electronics which requires the selective area doping profile characterized by the laterally-patterned p-n junctions [23]–[25], [27]

In reality, although the desired selective-area doping profile featuring laterally-patterned p-n junctions are highly sought after, the current main methodologies, i.e., ion implantation and etchand-regrowth methods, suffer from various issues. Ion implantation is the dominant technology for doping in Si and quite a lot of research efforts have been devoted to ion implantation of Mg to create p-GaN. However, it is extremely difficult to activate implanted Mg which results in low activation ratio unless ultrahigh pressure and temperature is employed [29], restricting the yield of the technology. Furthermore, extended defects such as inversion domain with Mg segregation are also among the typical issues in the post-implanted region which are difficult to recover [30]. Alternatively, etch-and-regrowth has been another methodology [31]. As drawn in Fig. 1.8 (right), a trench area is created by dry etch followed by regrowth of p-GaN. However, the unavoidable plasma damage caused to the regrown interface is problematic. The typical issues may include the leakage pathway along the regrowth interface [32] and the notorious and omnipresent Si pile-up which leads to the  $n^+$ -GaN sheet along the regrowth interface due to a considerable incorporation of Si atoms [33]. Given that both ion implantation and etch-and-regrowth are faced with various setbacks, a new methodology is strongly desired to realize the selective-area doping capability in GaN.

**Figure 1.8** Schematic illustration of the ion implantation and etch-and-regrowth methods to create the selective-area p-type region in GaN.

#### **1.3 Epitaxial Lateral Overgrowth of GaN**

#### **1.3.1 Dislocation Reduction by ELO**

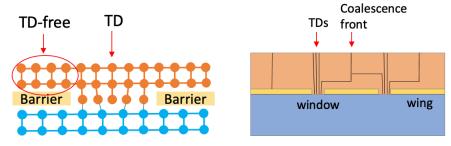

**Figure 1.9** Schematic illustrations of the epitaxial layer overgrowth of GaN to reduce the threading dislocation density.

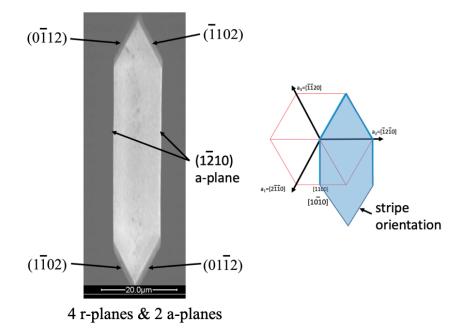

The method of epitaxial lateral overgrowth (ELO) has attracted much interest in the past two decades for obtaining GaN with reduced dislocation density or/and controlled crystallographic planes on the foreign substrate [34]. The original and main purpose of ELO is to reduce the dislocation density. The principle can be briefly illustrated in Fig. 1.9, when the single crystalline GaN indicated by the orange lattice is epitaxially grown onto the foreign substrate in blue having a different lattice constant, misfit dislocation is generated which lies on the interface to relieve the misfit strain beyond the critical thickness of GaN. Then a pair of dislocation lines will adjoin the misfit dislocation at its ends and threads up to the surface, forming two threading dislocations (TDs). Based on this, if a nucleation barrier layer (also referred to as the mask) is deposited to cover part of the foreign substrate onto which GaN cannot nucleate, the GaN directly grown onto the foreign substrate from where there is absence of nucleation barrier (referred to as the window) will then grow laterally over the mask. Such overgrown region (referred to as the wing) is mostly free of threading dislocations (TDs) and the TD-free wing region represents the desired region in the ELO-GaN. Basically, ELO samples contain three areas with different types of defects and densities: the areas grown from the window having high threading dislocation density, the precoalescence laterally overgrown areas containing few bent threading dislocations and occasionally helical dislocations, and areas where two growth fronts meet (coalescence front) having a high dislocation density at the boundary and occasionally voids [35].

### 1.3.2 Towards Selective-area p-type Doping by ELO

A key difference between the growth of pre-coalescence ELO-GaN from the growth of continuous thinfilm lies in the contrast between 2D and 3D growth mode. The in-situ doping during the 3D growth mode unlocks an additional degree of freedom perpendicular to the basal-plane and naturally leads to the selective-area doping profile in the orthogonal 2D sectional views.

In fact, many research works in the recent decade have been devoted to the creation of 3D doping profile in GaN by using ELO process for optoelectronic applications such as InGaN microrods LED [36]. Following this line of thought, the defining feature of 3D growth mode might also endow the selective-area doping of GaN for power electronics with new opportunities. However, very few research works were available in the literature to have explored the possibility of the 3D growth and doping process enabled by the pre-coalescence ELO-GaN to achieve the desired selective-area doing profile for power electronic applications [37].

The main reason lies in that the 3D growth and doping process would eventually create the half-core-shell doping profile which is not suitable for a power electronic device to withstand high reverse blocking voltage and high current density. As a result, in order to achieve the desired selective-area doping profiles configured for an ideal power switching electronic device, innovative measures need to be taken in either materials growth or device processing stage. This will serve as one of the main topics of this dissertation, therefore it will be discussed in greater detail in Chapter 2.

#### 1.4 Aim of the Study and Outline of the Dissertation

In this dissertation, the main focus was devoted to the innovative measures either in the material growth or device processing stage to tailor the half-core-shell doping profile enabled by the epitaxial lateral overgrowth of GaN into the desired selective-area doping profiles for power switching electronics featuring the building block of laterally patterned p-n junctions. In addition, the potential of the epitaxial lateral overgrowth to produce low-dislocation density GaN in the wing regions was also unleashed by virtue of the special selective-area doping structure-known as the true-lateral device architecture. Taking advantages of the true-lateral device architecture, the excellent electrical performances were demonstrated on a series of power devices from diodes to transistors, highlighted by the record high critical electric field in a GaN p-n junction and the record high current gain of a power bipolar transistor.

In Chapter 1, the background of this dissertation was introduced from a high-level perspective. The directions to improve GaN-a promising candidate for power switching electronics due to the high critical E-field-come from two aspects: reducing dislocation density and achieving selectivearea doping capability. With this aim, the purpose to revisit the epitaxial lateral overgrowth of GaN was illustrated, which has strong promise to satisfy the two goals at the same time. Given that the dislocation density reduction by ELO was well established in the past decades, the promise of ELO to achieve the desired selective area doping profile for power devices warrants greater research.

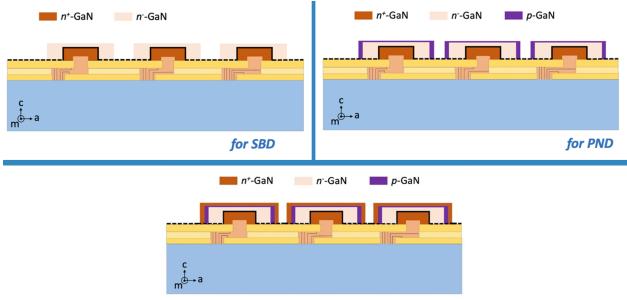

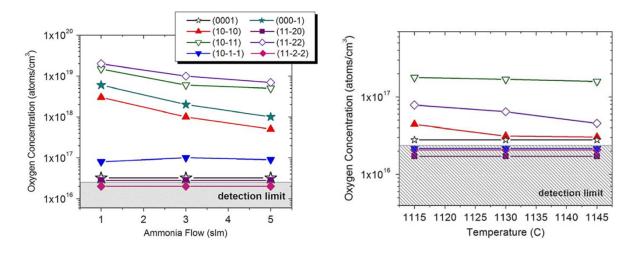

In Chapter 2, the special ELO process employed in this dissertation was introduced and the advantage over conventional ELO was discussed. Then GaN stripe arrays with various half-coreshell doping profiles were grown by a combination of ELO and in-situ doping process. A series of methods of characterization were carried out to reveal the doping structure and also to investigate the planar defects identified in the stripes. In Chapter 3, a set of device processing measures to tailor the half-core-shell doping structure into the innovative true-lateral device architecture were elaborated, preceded by the discussion of the advantages of the true-lateral device architecture over the true-vertical or quasi-vertical counterpart. Specifically, the converse-piezoelectric effect-induced stress issue associated with the true-vertical or quasi-vertical device structure was discussed. Then, the p-n junction diode (PND) and Schottky barrier diode (SBD) with the true-lateral device architecture were fabricated and characterized. The critical breakdown field was extracted and the theoretical critical field under the same condition was calculated by finite element analysis based on the impact ionization model.

In Chapter 4, a novel type of bipolar transistor known as gated lateral power bipolar junction transistor (GLP-BJT) was discussed with TCAD modeling. Then, the prototype GLP-BJT was experimentally demonstrated with the advantage of the true-lateral device architecture to further increase the current gain and breakdown voltage. On the other hand, another important bipolar transistor-insulated gate bipolar transistor (IGBT) was experimentally demonstrated on GaN by virtue of the special advantages of the true-lateral device architecture which otherwise would face formidable challenges to be fabricated.

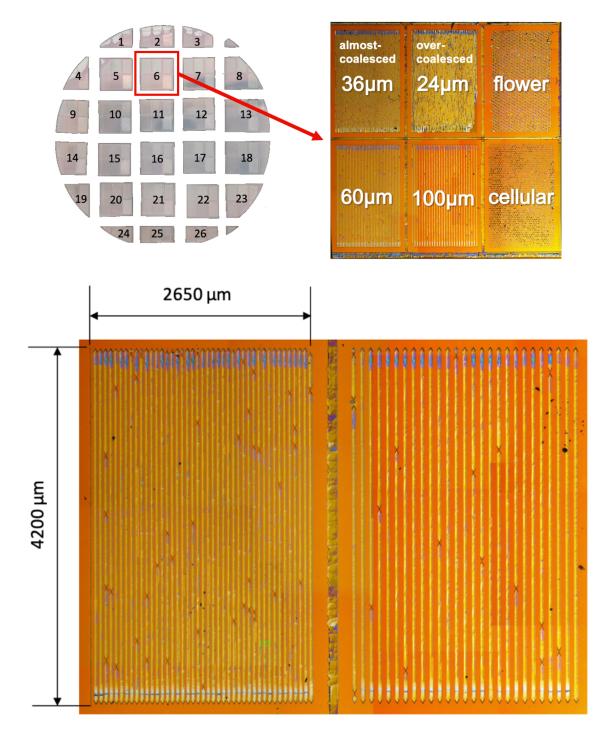

In Chapter 5, alternative measures from material growth aspect were discussed to turn the half-core-shell doping structure into the desired selective-area doping profile featuring repeating laterally patterned p-n junctions on the GaN substrate. Such measures are categorized as a new type of growth and transfer. Material characterization techniques were carried out from different angles to evaluate the special selective-area doping profile. For the device application, the planar-gate vertical MOSFETs were demonstrated on the GaN substrate.

In Chapter 6, the state-of-the-art characterization techniques featuring high spatial resolution were carried out to investigate the elemental, dopant, and carrier distribution of the ELO-GaN samples with selective-area doping profiles. Then the anisotropic diffusion model of Mg was built and the novel phenomenon associated with the diffusion behaviors of Mg in the ELO-GaN were provided with possible explanations. On the other hand, the application of delta-doping of Mg by diffusion in forming excellent Ohmic contact to p-GaN was demonstrated with success. Specifically, the capability to fully recover the Ohmic contact to plasma-damaged p-GaN shows a strong promise to address the bottleneck in this field of study, which should also lend a solid hand to greatly enhance the performance of p-n junction diode and bipolar transistors in future work.

In Chapter 7, the conclusion remarks and future outlook were presented.

### **1.5 References**

- [1] H. Amano et al., "The 2018 GaN power electronics roadmap," Journal of Physics D: Applied Physics, vol. 51, no. 16, p. 163001, 2018.

- [2] R. J. Kaplar et al., "Characterization and reliability of SiC-and GaN-based power transistors for renewable energy applications," in 2012 IEEE Energytech, 2012, pp. 1–6.

- [3] K. Shenai, "Switching megawatts with power transistors," The Electrochemical Society Interface, vol. 22, no. 1, p. 47, 2013.

- [4] G. Deboy, N. Marz, J.-P. Stengl, H. Strack, J. Tihanyi, and H. Weber, "A new generation of high voltage MOSFETs breaks the limit line of silicon," in International Electron Devices Meeting 1998. Technical Digest (Cat. No. 98CH36217), 1998, pp. 683–685.

- [5] T. Kimoto, "Material science and device physics in SiC technology for high-voltage power devices," Japanese Journal of Applied Physics, vol. 54, no. 4, p. 40103, 2015.

- [6] B. J. Baliga, Fundamentals of power semiconductor devices. Springer Science & Business Media, 2010.

- [7] J. A. Cooper and D. T. Morisette, "Performance Limits of Vertical Unipolar Power Devices in GaN and 4H-SiC," IEEE Electron Device Letters, vol. 41, no. 6, pp. 892–895, 2020.

- [8] A. Agarwal et al., "600 V, 1-40 A, Schottky diodes in SiC and their applications," in Proc. Int'l Power Electronics Technology Conf, 2002, pp. 631–639.

- [9] D. Han, A. Ogale, S. Li, Y. Li, and B. Sarlioglu, "Efficiency characterization and thermal study of GaN based 1 kW inverter," in 2014 IEEE Applied Power Electronics Conference

and Exposition-APEC 2014, 2014, pp. 2344–2350.

- [10] K. O. Armstrong, S. Das, and J. Cresko, "Wide bandgap semiconductor opportunities in power electronics," in 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2016, pp. 259–264.

- [11] G. Patterson and J. Roberts, "Gallium nitride-delivering its promise in automotive applications," in 6th Hybrid and Electric Vehicles Conference (HEVC 2016), 2016, pp. 1–6.

- [12] R. Stevenson, "The world's best gallium nitride," IEEE Spectrum, vol. 47, no. 7, pp. 40– 45, 2010.

- [13] A. Dadgar, "Sixteen years GaN on Si," physica status solidi (b), vol. 252, no. 5, pp. 1063– 1068, 2015.

- [14] Y. Zhang, A. Dadgar, and T. Palacios, "Gallium nitride vertical power devices on foreign substrates: a review and outlook," Journal of Physics D: Applied Physics, vol. 51, no. 27, p. 273001, 2018.

- [15] M. Qi et al., "High breakdown single-crystal GaN p-n diodes by molecular beam epitaxy," Applied Physics Letters, vol. 107, no. 23, 2015.

- [16] E. J. Miller, E. T. Yu, P. Waltereit, and J. S. Speck, "Analysis of reverse-bias leakage current mechanisms in GaN grown by molecular-beam epitaxy," Applied physics letters, vol. 84, no. 4, pp. 535–537, 2004.

- [17] Y. Zhang et al., "Design space and origin of off-state leakage in GaN vertical power diodes," in 2015 IEEE International Electron Devices Meeting (IEDM), 2015, pp. 31–35.

- [18] I. C. Kizilyalli, A. P. Edwards, H. Nie, D. Disney, and D. Bour, "High voltage vertical GaN p-n diodes with avalanche capability," IEEE Transactions on Electron Devices, vol. 60, no. 10, pp. 3067–3070, 2013.

- [19] H. Amano, M. Kito, K. Hiramatsu, and I. Akasaki, "P-type conduction in Mg-doped GaN treated with low-energy electron beam irradiation (LEEBI)," Japanese Journal of Applied Physics, vol. 28, no. 12 A, pp. L2112–L2114, 1989.

- [20] M. A. Reshchikov, P. Ghimire, and D. O. Demchenko, "Magnesium acceptor in gallium nitride. I. Photoluminescence from Mg-doped GaN," Physical Review B, vol. 97, no. 20, p. 205204, 2018.

- [21] W. Götz, N. M. Johnson, J. Walker, D. P. Bour, and R. A. Street, "Activation of acceptors in Mg-doped GaN grown by metalorganic chemical vapor deposition," Applied Physics Letters, vol. 68, no. 5, pp. 667–669, 1996.

- [22] S. Brochen, J. Brault, S. Chenot, A. Dussaigne, M. Leroux, and B. Damilano, "Dependence of the Mg-related acceptor ionization energy with the acceptor concentration in p-type GaN

layers grown by molecular beam epitaxy," Applied Physics Letters, vol. 103, no. 3, pp. 1–5, 2013.

- [23] H. Fu et al., "Selective area regrowth and doping for vertical gallium nitride power devices: Materials challenges and recent progress," Materials Today, 2021.

- [24] M. Yoshino et al., "Fully Ion Implanted Normally-Off GaN DMOSFETs with ALD-Al<sub>2</sub>O<sub>3</sub> Gate Dielectrics," Materials, vol. 12, no. 5, p. 689, 2019.

- [25] S. Chowdhury, M. H. Wong, B. L. Swenson, and U. K. Mishra, "CAVET on bulk GaN substrates achieved with MBE-regrown AlGaN/GaN layers to suppress dispersion," IEEE Electron Device Letters, vol. 33, no. 1, pp. 41–43, 2012.

- [26] T. Hayashida, T. Nanjo, A. Furukawa, and M. Yamamuka, "Vertical GaN merged PiN Schottky diode with a breakdown voltage of 2 kV," Applied Physics Express, vol. 10, no. 6, Jun. 2017.

- [27] D. Khachariya et al., "A Path Toward Vertical GaN Superjunction Devices," ECS Transactions, vol. 98, no. 6, p. 69, 2020.

- [28] S. Han, S. Yang, and K. Sheng, "Conductivity Modulation in Vertical GaN PiN Diode: Evidence and Impact," IEEE Electron Device Letters, vol. 42, no. 3, pp. 300–303, 2021.

- [29] H. Sakurai et al., "Acceptors activation of Mg-ion implanted GaN by ultra-high-pressure annealing," in 2019 19th International Workshop on Junction Technology (IWJT), 2019, pp. 1–2.

- [30] B. J. Pong et al., "Structural defects and microstrain in GaN induced by Mg ion implantation," Journal of applied physics, vol. 83, no. 11, pp. 5992–5996, 1998.

- [31] K. Fu et al., "Investigation of GaN-on-GaN vertical p-n diode with regrown p-GaN by metalorganic chemical vapor deposition," Applied Physics Letters, vol. 113, no. 23, p. 233502, 2018.

- [32] G. W. Pickrell et al., "Regrown Vertical GaN p-n Diodes with Low Reverse Leakage Current.," Journal of Electronic Materials, vol. 48, no. 5, 2019.

- [33] T. Liu et al., "Suppression of the regrowth interface leakage current in AlGaN/GaN HEMTs by unactivated Mg doped GaN layer," Applied Physics Letters, vol. 118, no. 7, 2021.

- [34] B. Beaumont, P. Vennéguès, and P. Gibart, "Epitaxial lateral overgrowth of GaN," Physica Status Solidi (B) Basic Research, vol. 227, no. 1, pp. 1–43, 2001.

- [35] P. Gibart, "Metal organic vapour phase epitaxy of GaN and lateral overgrowth," Reports on Progress in Physics, vol. 67, no. 5, pp. 667–715, 2004.

- [36] C. Kölper, M. Sabathil, F. Römer, M. Mandl, M. Strassburg, and B. Witzigmann, "Coreshell InGaN nanorod light emitting diodes: Electronic and optical device properties,"

Physica status solidi (a), vol. 209, no. 11, pp. 2304–2312, 2012.

[37] J. Wang, H. Amano, and Y.-H. Xie, "3D GaN Power Switching Electronics: A Revival of Interest in ELO," in 2021 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), 2021, pp. 1–3.

# **Chapter 2**

# **ELO-GaN with Half-Core-Shell Doping Structure**

#### 2.1 ELO with Serpentine-Channeled Masks

#### 2.1.1 Overview

The ELO-GaN samples that are employed in this dissertation are mainly grown on the threelayer mask patterned sapphire substrates. As briefly introduced in Chapter 1, the mask material (usually  $SiO_2$ ,  $SiN_x$ ) should function as the nucleation barrier to the epitaxial growth of GaN. In a conventional ELO mask structure, a single layer of mask is deposited onto the substrate with periodic openings (referred to as windows) [1]. Instead, the modified mask structure employed in this dissertation features staggered three-layer mask ( $Si_3N_4/SiO_2/Si_3N_4$ ) forming a "Z"-shaped or serpentine-like channel.

**Figure 2.1** Comparison of dislocation reduction in (a) conventional ELO process and (b) ELO process with serpentine-channeled mask.

In general, the guiding principle of ELO is to minimize the crystalline portion of the filmsubstrate interfacial area and use such interface only for the purpose of enabling epitaxy [2]. This is the same with serpentine-channeled mask, and both of them start by patterning mask onto which GaN cannot nucleate and only the windows between masks enable the epitaxial growth of GaN, which is also known as the selective area growth (SAG). As shown in Fig. 2.1 (a), in a conventional ELO process, after the growth of GaN from the window, the growth will be switched to the lateral mode by adjusting V/III ratio. A portion of threading dislocations (TDs) will bend due to the image force driving them to thread to the nearest surface. During the lateral growth, the TDs will meander and some may thread to the top surface, causing the remaining TDs in the lateral growth region. At the final stage of lateral growth, the growth fronts will coalesce with each other where numerous new defects are generated such as TDs (1D), stacking faults (2D) and micro-voids (3D). After the coalescence, the vertical growth resumes as the new TDs propagate along with the growth front before threading to the surface of the film. In this way, the dislocations can be reduced in the lateral overgrowth region (wing) but there are still two high-defects regions (i.e., window and coalescence front) per window [3].

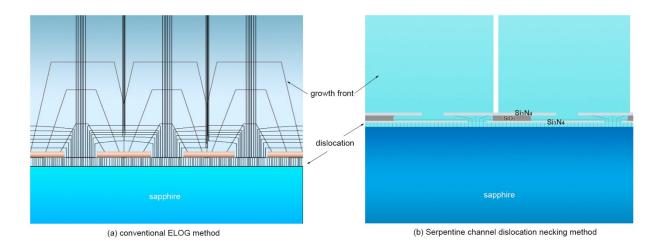

In comparison, the ELO process with serpentine-channeled mask can further overcome some of the drawbacks of conventional ELO process by making the most of mask geometry and further filtering the TDs. The benefit of building the serpentine-channel with a length of horizontal part stems from the so-called "dislocation necking" process. As shown in Fig. 2.1(b) and Fig. 2.2 (c), when the growth is switched from vertical to lateral mode in the channel, some TDs are bent in a similar manner to those in a conventional ELO process, the unbent TDs will terminate at the nearest surface of the overhanging  $Si_3N_4$ . After the lateral growth is kept for a period of time, the growth is switched from lateral back to vertical mode so that the growth front can emerge from the top window with low dislocation density (the remaining TDs experienced twice bending). The subsequent growth is just the same as a conventional ELO process [4]–[6].

Then, in order to avoid the generation of numerous new TDs and stacking faults upon the coalescence of adjacent islands, the coalescence process could better be forestalled. Fortunately, this is not difficult to achieve since the coalescence process itself, on the contrary, is more difficult to achieve. As it appears, the window region in this modified approach has low dislocation density comparable to the adjacent wing regions, then the size of low dislocation density region is doubled compared to the conventional ELO process.

**Figure 2.2** (a) An X-ray topography image describing the dislocation necking in a silicon boule (image courtesy of Wacker/Siltronic, Germany); (b) Schematic illustration of the GaN grown out of the double-layer mask; (c) Schematic drawing of the dislocation necking in the serpentine channel.

Furthermore, in addition to the dislocation bending during switches between lateral and vertical growth, it is also meaningful to discuss the filtering of dislocation within the lateral channel due to the necking process. Historically, the dislocation necking was originated from the well-known art in manufacturing large-volume dislocation-free silicon crystal (Czochralski method) [7]. As illustrated in Fig. 2.2 (a), a needle-like silicon seed is slowly pulled out of silicon melt. The condition at which the bottom of needle touches the melt is maintained very close to thermal equilibrium so that the melt will slowly solidify on the colder side away from the melt. It is important to note that dislocations glide along certain specific planes and directions in a crystal.

By carefully controlling the rate and the direction of pull-out while minimizing the probability of dislocation threading along the pull-out direction, dislocations will "shoot themselves out" by gliding out of the crystal within the narrow and long neck region. In this manner, as long as the long neck region has high aspect ratio, the final crystal will be completely free of dislocations.

Unlike the bulk growth from melt, one does not have the luxury of creating a vertical neck in the vapor phase epitaxy. Instead, as illustrated in Fig. 2.2 (b)(c), the neck would meander in parallel, rather than perpendicular, to the substrate surface. In analogy to the Czochralski method, the dislocation will be driven out of the parallel GaN neck since the TD gliding direction is out of the c-plane growth direction. As a result, it allows dislocations to be effectively filtered out. As such, the crystal, when growing out of the top mask windows, is entirely relieved of the mismatch strain while featuring low threading dislocation density [6].

#### 2.1.2 MOVPE Growth

The MOVPE growths are carried out in a Veeco K465i GaN MOCVD system, as shown in Fig. 2.3. Both sapphire and Si are used as substrates for epitaxial growths. In the case of Si, AlN buffer layer (150 nm) is deposited to prevent meltback etching of GaN, also the deposition of AlN should precede mask patterning since AlN has no growth selectivity on the  $SiO_2/Si_3N_4$  mask.

Figure 2.3 Veeco K465i GaN MOCVD system used for growing the ELO-GaN samples.

| Step                                             | H <sub>2</sub><br>(slpm) | N <sub>2</sub><br>(slpm) | NH₃<br>(slpm) | Ga<br>(sccm) | Si<br>(sccm) | Mg<br>(sccm) | V/III | Temperature<br>(°C) | Pressure<br>(torr) | Time(min) |