### UC Riverside UC Riverside Electronic Theses and Dissertations

### Title

Architectural Support for Securing Systems Against Micro-Architectural Attacks

Permalink https://escholarship.org/uc/item/8434p6kn

Author Mohammadian Koruyeh, Esmaeil

Publication Date 2022

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA RIVERSIDE

Architectural Support for Securing Systems Against Micro-Architectural Attacks

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Computer Science

by

Esmaeil Mohammadian Koruyeh

September 2023

Dissertation Committee:

Dr. Nael Abu Ghazaleh, Chairperson Dr. Rajiv Gupta Dr. Chengyu Song Dr. Mohsen Lesani

Copyright by Esmaeil Mohammadian Koruyeh 2023 The Dissertation of Esmaeil Mohammadian Koruyeh is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

My PhD journey was a transformative experience, filled with challenges but also moments of insight and growth. Throughout it all, I was fortunate to never feel alone, surrounded by those who guided and supported me.

First and foremost, I owe a deep debt of gratitude to Professor Nael Abu-Ghazaleh. Your kindness and patience have been my constant throughout this journey. In every challenge, your belief in me and your steady guidance made all the difference. Beyond the academic insights, it was your genuine care and understanding that shaped my experience most profoundly. You have been much more than an advisor to me; you've been a guiding light in both my academic and personal growth. For all of this and more, thank you from the depths of my heart.

I extend my sincere thanks to my committee members, Professors Rajive Gupta, Chengyu Song, and Mohsen Lesani, for their invaluable feedback. Your combined expertise and insights have been instrumental in refining this work to its present form.

To my lab mates: Shafiur Rahman, Fatemah Alharbi, Hoda Naghibi Jouybari, Hodjat Asghari-Esfeden, Sankha Dutta, Ahmed Abdo, Shirin Haji Amin Shirazi, Sakib Md Bin Malek, Jason Zellmer, Abdulrahman Bin Rabiah, and notably, Khaled Khaswaneh our times together, from coffee breaks to shared successes, were invaluable. Your individual insights and collective support profoundly enriched both my academic work and my personal experiences during our time together.

To my friends, Hadi Zamani, Mohammad Farajollahi, Alireza Abdoli, Sajjad Bahrami, Mehdi Kohansal, Valeh Ebrahimi, and Shahrzad Haji Amin Shirazi - each one of you holds a special place in this journey. Together, you became more than friends; you were the family I found away from home. Whether it was the unwavering support, shared laughter, or quiet moments of understanding, you all made here feel familiar and comforting.

Lastly, Being miles away in a different country has underscored the importance and value of family. To my parents, Mohammad Ali and Maryam; my siblings, Parisa, Ebrahim, and Ali; and my beloved nephew and niece, Soroush and Rosha Heidari – despite the distance, your love, guidance, and unwavering support have always made me feel close to home. Your constant encouragement and the sacrifices you've made have been the bedrock upon which my resilience was built. While I embarked on this academic journey in a foreign land, it was your unwavering faith in me that kept my compass directed towards my goals. To my family.

#### ABSTRACT OF THE DISSERTATION

Architectural Support for Securing Systems Against Micro-Architectural Attacks

by

Esmaeil Mohammadian Koruyeh

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, September 2023 Dr. Nael Abu Ghazaleh, Chairperson

Cybersecurity threats continue to grow as the number of attacks on all layers of computing systems by motivated and sophisticated attackers continues to grow over the past several years. The recent Meltdown and Spectre attacks have shown that computer architecture and hardware also offer software-exploitable attack surfaces that can be used to compromise systems. This dissertation investigates the boundary between hardware and software with respect to computer security, exploring attacks that originate in the hardware, and conversely architecture support for securing systems and software.

In this dissertation, we introduce SpectreRSB, a new Spectre attack that we developed targeting the return stack buffer used to optimize the execution of return instructions on modern CPUs. We show that both local attacks (within the same process such as Spectre 1) and attacks on SGX are possible by constructing proof of concept attacks. We also analyze additional types of the attack on the kernel or across address spaces and show that under some practical and widely used conditions they are possible. Having demonstrated the possibility of Spectre attacks, the dissertation explores general defense approaches to counter this important vulnerability class. The first defense we contribute is SPECCFI, a new CPU design principle that secures modern processors against Spectre attacks with the help of program analysis while retaining the benefits of speculative execution. SPECCFI represents a new approach to securing architecture by using techniques that protect software to enforce secure operation even during speculative execution.

We extended the idea of using program analysis during speculation, to defend against more variants of transient execution attacks. More specifically, we proposed the Speculative Execution Regulation (SER) as a general class of defense. Since speculative execution states are accessible to an attacker, SER seeks to ensure that security invariants are enforced even during speculation.

The third contribution of the dissertation is a general approach to securing processors against transient execution attacks by making speculation leakage free in a principled way, enabling CPUs to retain the performance advantages of speculation while removing the security vulnerabilities it exposes. Our defense, SafeSpec, is a design principle where speculative state is stored in temporary shadow structures, that are not accessible to committed instructions.

The final contribution of my dissertation is the possibility of side-channel attacks on new emerging memories to find potential vulnerabilities. More specifically we showed the possibility of side-channel attacks when Intel Optane persistent memory operates as the main memory in the system and DRAM is considered as the last level cache. The timing difference between accessing the DRAM and Non-Volatile RAM (NVRAM) can create a side channel.

# Contents

| List of Figures |                | xiii                                                                       |           |

|-----------------|----------------|----------------------------------------------------------------------------|-----------|

| Li              | List of Tables |                                                                            |           |

| 1               | Intr           | oduction                                                                   | 1         |

|                 | 1.1            | Contributions of the Dissertation                                          | 3         |

|                 |                | 1.1.1 Exploring vulnerabilities in computer hardware                       | 3         |

|                 |                | 1.1.2 Designing secure systems against Micro-architectural attacks         | 4         |

| 2               | Bac            | kground                                                                    | 8         |

|                 | 2.1            | Out of Order execution (OoO)                                               | 9         |

|                 |                | 2.1.1 Microarchitectural vs Architectural Effects                          | 11        |

|                 | 2.2            | Branch prediction                                                          | 11        |

|                 | 2.3            | Speculation Attacks                                                        | 13        |

|                 |                | 2.3.1 Spectre-PHT                                                          | 14        |

|                 |                | 2.3.2 Spectre-BTB                                                          | 15        |

|                 |                | 2.3.3 Spectre-STL                                                          | 16        |

|                 | 2.4            | Meltdown, LVI and MDS attacks                                              | 16        |

| 3               | Spe            | ctre Returns! Speculation Attacks using the Return Stack Buffer            | <b>21</b> |

|                 | 3.1            | Introduction                                                               | 21        |

|                 |                | 3.1.1 Defenses against Meltdown/Spectre                                    | 23        |

|                 | 3.2            | Attack Principles: Reverse Engineering the Return Stack Buffer             | 26        |

|                 |                | 3.2.1 RSB Overview                                                         | 27        |

|                 |                | 3.2.2 RSB sources of misspeculation                                        | 28        |

|                 | 3.3            | SpectreRSB: Basic attack example                                           | 31        |

|                 | 3.4            | Attacks across different threads/processes                                 | 35        |

|                 |                | 3.4.1 Attack 2a: Attack across two colluding threads                       | 35        |

|                 |                | 3.4.2 Attack 2b: Attack with two colluding threads with return from inside |           |

|                 |                | kernel                                                                     | 36        |

|                 |                | 3.4.3 Attack 2c: Attacks across Process boundary                           | 37        |

|                 | 3.5            | SpectreRSB Atack 3: Attacks on SGX                                         | 37        |

|   | 3.6                                                                                | Potential Attack 4: From user to Kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38                                                                                                                         |

|---|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|   | 3.7                                                                                | Discussion and Mitigations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41                                                                                                                         |

|   | 3.8                                                                                | Concluding Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43                                                                                                                         |

| 4 | _                                                                                  | culative Execution Regulation (SER): Leveraging Program Analysis<br>Secure Speculative Execution<br>SPECCFI: Mitigating Spectre Attacks using CFI Informed Speculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                                                                                         |

|   | 4.1                                                                                | SPECCET: Mitigating Spectre Attacks using CFT informed Speculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49                                                                                                                         |

|   |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

|   |                                                                                    | 4.1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49                                                                                                                         |

|   |                                                                                    | 4.1.2 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53                                                                                                                         |

|   |                                                                                    | 4.1.3 SPECCFI System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56                                                                                                                         |

|   |                                                                                    | 4.1.4 Threat Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56                                                                                                                         |

|   |                                                                                    | 4.1.5 Instruction Set Architecture (ISA) Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57                                                                                                                         |

|   |                                                                                    | 4.1.6 Compiler Modification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58                                                                                                                         |

|   |                                                                                    | 4.1.7 Forward-Edge Defense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59                                                                                                                         |

|   |                                                                                    | 4.1.8 Enforcing CFI for Committed Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63                                                                                                                         |

|   |                                                                                    | 4.1.9 Backward-Edge Defense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64<br>60                                                                                                                   |

|   |                                                                                    | 4.1.10 Comparison to Intel CET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69<br>70                                                                                                                   |

|   |                                                                                    | 4.1.11 Security Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70                                                                                                                         |

|   |                                                                                    | 4.1.12 Performance and Complexity Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72                                                                                                                         |

|   | 4.0                                                                                | 4.1.13 Empirical Security Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82                                                                                                                         |

|   | 4.2                                                                                | Concluding Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86                                                                                                                         |

|   |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

| 5 | Spe<br>tize                                                                        | cAsan: Protecting Data Speculation using Speculative Address Sani-<br>r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| 5 | tize                                                                               | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88                                                                                                                         |

| 5 | <b>tize</b><br>5.1                                                                 | r Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>88</b><br>88                                                                                                            |

| 5 | <b>tize</b><br>5.1<br>5.2                                                          | r<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>88</b><br>88<br>89                                                                                                      |

| 5 | <b>tize</b><br>5.1                                                                 | r Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>88</b><br>88<br>89<br>93                                                                                                |

| 5 | <b>tize</b><br>5.1<br>5.2                                                          | Introduction       Introduction         Background       Speculative Execution Regulation (SER)         5.3.1       Threat Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>88</b><br>88<br>89<br>93<br>94                                                                                          |

| 5 | <b>tize</b><br>5.1<br>5.2                                                          | Introduction       Introduction         Background       Speculative Execution Regulation (SER)         5.3.1       Threat Model         5.3.2       SPECASAN System Model, Architectural Modifications                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>88</b><br>88<br>89<br>93<br>94<br>95                                                                                    |

| 5 | <b>tize</b><br>5.1<br>5.2<br>5.3                                                   | Introduction       Introduction         Background       Background         Speculative Execution Regulation (SER)       Secure         5.3.1       Threat Model         5.3.2       SPECASAN System Model, Architectural Modifications         5.3.3       SPECASAN Implementation                                                                                                                                                                                                                                                                                                                                                                             | <b>88</b><br>88<br>93<br>93<br>94<br>95<br>101                                                                             |

| 5 | <b>tize</b><br>5.1<br>5.2                                                          | Introduction       Introduction         Background       Speculative Execution Regulation (SER)         Speculative Execution Regulation (SER)       Speculative Execution Regulation (SER)         5.3.1       Threat Model         5.3.2       SPECASAN System Model, Architectural Modifications         5.3.3       SPECASAN Implementation         Security Evaluation:       SPECASAN against Micro-architectural attacks                                                                                                                                                                                                                                 | 88<br>88<br>93<br>93<br>94<br>95<br>101<br>101                                                                             |

| 5 | <b>tize</b><br>5.1<br>5.2<br>5.3                                                   | Introduction       Introduction         Background       Speculative Execution Regulation (SER)         Speculative Execution Regulation (SER)       Speculative Execution Regulation (SER)         5.3.1       Threat Model         5.3.2       SPECASAN System Model, Architectural Modifications         5.3.3       SPECASAN Implementation         Security Evaluation:       SPECASAN against Micro-architectural attacks                                                                                                                                                                                                                                 | 88<br>88<br>93<br>93<br>94<br>95<br>101<br>101                                                                             |

| 5 | <b>tize</b><br>5.1<br>5.2<br>5.3<br>5.4                                            | Introduction       Introduction         Background       Background         Speculative Execution Regulation (SER)       Speculative Execution Regulation (SER)         5.3.1       Threat Model         5.3.2       SPECASAN System Model, Architectural Modifications         5.3.3       SPECASAN Implementation         Security Evaluation:       SPECASAN against Micro-architectural attacks         5.4.1       Performance Evaluation and Future work                                                                                                                                                                                                  | <b>88</b><br>88<br>93<br>93<br>94<br>95<br>101                                                                             |

|   | <b>tize</b><br>5.1<br>5.2<br>5.3<br>5.4                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88<br>88<br>93<br>94<br>95<br>101<br>101<br>108                                                                            |

|   | tize<br>5.1<br>5.2<br>5.3<br>5.4<br>Safe                                           | Introduction       Introduction         Background       Speculative Execution Regulation (SER)         Speculative Execution Regulation (SER)       Speculative Execution Regulation (SER)         5.3.1       Threat Model         5.3.2       SPECASAN System Model, Architectural Modifications         5.3.3       SPECASAN Implementation         Security Evaluation:       SPECASAN against Micro-architectural attacks         5.4.1       Performance Evaluation and Future work <b>Spec:</b> Leakage-Free Speculation         Introduction       Introduction                                                                                        | <ul> <li>88</li> <li>89</li> <li>93</li> <li>94</li> <li>95</li> <li>101</li> <li>101</li> <li>108</li> <li>110</li> </ul> |

|   | tize<br>5.1<br>5.2<br>5.3<br>5.4<br>Safe<br>6.1                                    | Introduction       Introduction         Background       Background         Speculative Execution Regulation (SER)       Speculative Execution Regulation (SER)         5.3.1       Threat Model         5.3.2       SPECASAN System Model, Architectural Modifications         5.3.3       SPECASAN Implementation         Security Evaluation:       SPECASAN against Micro-architectural attacks         5.4.1       Performance Evaluation and Future work         Spec:       Leakage-Free Speculation         Introduction       Introduction         Background and Threat Model       Introduction                                                      | <b>88</b><br>88<br>93<br>94<br>95<br>101<br>101<br>108<br><b>110</b>                                                       |

|   | tize<br>5.1<br>5.2<br>5.3<br>5.4<br>Safe<br>6.1<br>6.2                             | Introduction       Introduction         Background       Speculative Execution Regulation (SER)         5.3.1       Threat Model         5.3.2       SPECASAN System Model, Architectural Modifications         5.3.3       SPECASAN Implementation         Security Evaluation:       SPECASAN against Micro-architectural attacks         5.4.1       Performance Evaluation and Future work         eSpec:       Leakage-Free Speculation         Introduction       Background and Threat Model         SafeSpec:       Leakage-free Speculation                                                                                                            | <b>88</b><br>88<br>93<br>94<br>95<br>101<br>101<br>108<br><b>110</b><br>110<br>113                                         |

|   | tize<br>5.1<br>5.2<br>5.3<br>5.4<br>Safe<br>6.1<br>6.2<br>6.3                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>88</b><br>88<br>93<br>94<br>95<br>101<br>101<br>108<br><b>110</b><br>1110<br>113<br>114                                 |

|   | tize<br>5.1<br>5.2<br>5.3<br>5.4<br><b>Safe</b><br>6.1<br>6.2<br>6.3<br>6.4        | Introduction       Background         Background       Speculative Execution Regulation (SER)         5.3.1       Threat Model         5.3.2       SPECASAN System Model, Architectural Modifications         5.3.3       SPECASAN Implementation         Security Evaluation:       SPECASAN against Micro-architectural attacks         5.4.1       Performance Evaluation and Future work <b>eSpec:</b> Leakage-Free Speculation         Introduction       Background and Threat Model         SafeSpec       Leakage-free Speculation         SafeSpec       For Caches and TLBs         Transient Speculation Attacks       Transient Speculation Attacks | <b>88</b><br>88<br>93<br>94<br>95<br>101<br>101<br>108<br><b>110</b><br>113<br>114<br>118                                  |

|   | tize<br>5.1<br>5.2<br>5.3<br>5.4<br><b>Safe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>88</b><br>88<br>93<br>94<br>95<br>101<br>101<br>108<br><b>110</b><br>110<br>113<br>114<br>118<br>121                    |

|   | tize<br>5.1<br>5.2<br>5.3<br>5.4<br><b>Safe</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>88</b><br>88<br>93<br>94<br>95<br>101<br>101<br>108<br><b>110</b><br>113<br>114<br>118<br>121<br>123                    |

|    | 6.7            | Discussion, Limitations and Future Directions       | 128 |  |

|----|----------------|-----------------------------------------------------|-----|--|

|    | 6.8            | Concluding Remarks                                  | 130 |  |

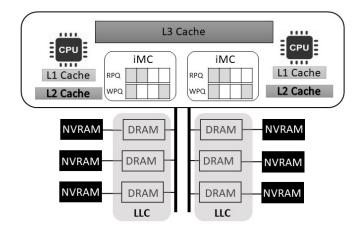

| 7  | Inte           | el Optane Side-channel Analysis                     | 132 |  |

|    | 7.1            | Introduction                                        | 132 |  |

|    | 7.2            | Background                                          | 134 |  |

|    | 7.3            | Reverse Engineering the Intel Optane in Memory-mode | 136 |  |

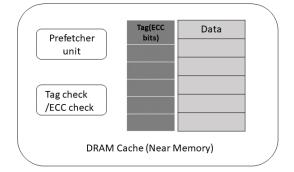

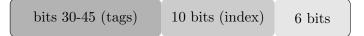

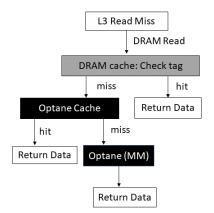

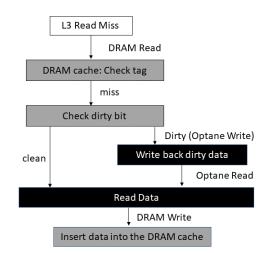

|    |                | 7.3.1 Properties of DRAM Cache (Near memory)        | 137 |  |

|    |                | 7.3.2 Optane controller                             | 140 |  |

|    | 7.4            | Timing Channels                                     | 141 |  |

|    |                | 7.4.1 Timing channel l                              | 141 |  |

|    |                | 7.4.2 Timing channel 2                              | 147 |  |

|    |                | 7.4.3 Covert channel                                | 150 |  |

|    | 7.5            | Concluding Remarks                                  | 152 |  |

| 8  | Cor            | ncluding Remarks                                    | 153 |  |

| Bi | Bibliography 1 |                                                     |     |  |

# List of Figures

| 2.1 | Out-Of-Order (O3) Execution                                                                  | 10 |

|-----|----------------------------------------------------------------------------------------------|----|

| 2.2 | Branch Predictor Unit consists of three different predictors: (1) PHT for                    |    |

|     | conditional branch direction; $(2)$ BTB for indirect branch addresses; and $(3)$             |    |

|     | RSB for return addresses.                                                                    | 12 |

| 2.3 | Spectre attack variant 1                                                                     | 14 |

| 2.4 | MeltDown and MDS attack [83]                                                                 | 19 |

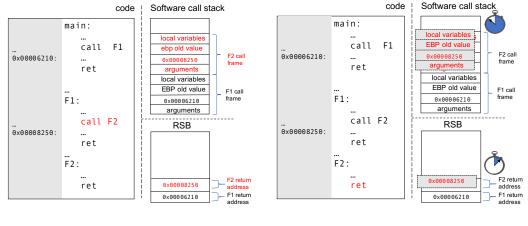

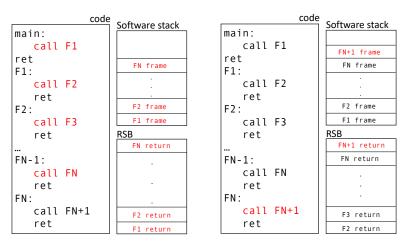

| 3.1 | Example of function call and return effect on software call stack and $\operatorname{RSB}$ . | 26 |

|     | (a) Calling a function (F2)                                                                  | 26 |

|     | (b) Return from a function (F2)                                                              | 26 |

| 3.2 | Example of overfill of RSB                                                                   | 29 |

|     | (a) Executing N nested function                                                              | 29 |

|     | (b) N+1 nested function call                                                                 | 29 |

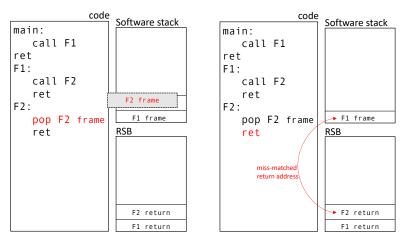

| 3.3 | Example of direct pollution of the RSB                                                       | 30 |

|     | (a) Removing the current return                                                              | 30 |

|     | (b) Mismatch between RSB, Stack                                                              | 30 |

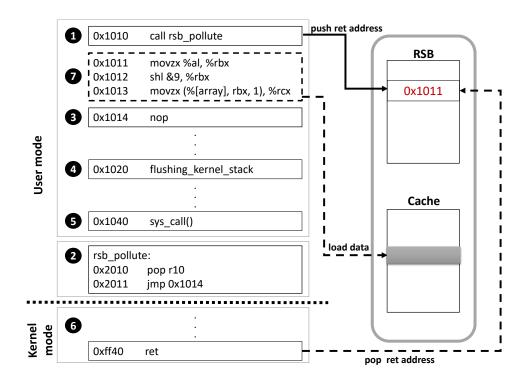

| 3.4 | SpectreRSB basic attack example                                                              | 34 |

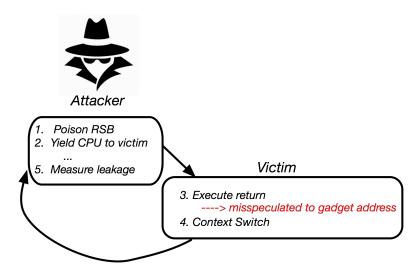

| 3.5 | Attack 2: Basic Attack Flow                                                                  | 36 |

| 3.6 | Attack 4: Basic Attack Flow                                                                  | 40 |

| 4.1 | Example attack across address spaces                                                         | 60 |

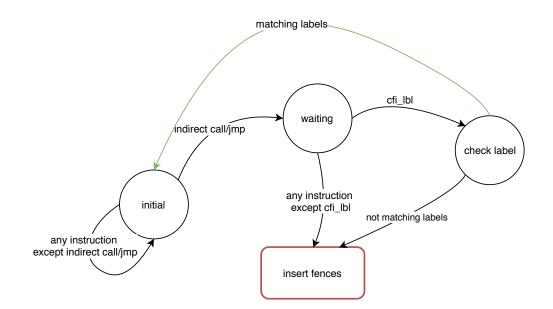

| 4.2 | State machine for forward edge protection                                                    | 61 |

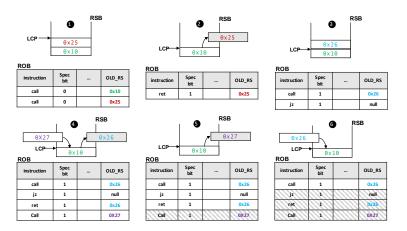

| 4.3 | Example of the operation of the combined RSB/SCS $\ldots \ldots \ldots \ldots \ldots$        | 65 |

| 4.4 | Code sample to illustrate the operation of RSB/SCS                                           | 67 |

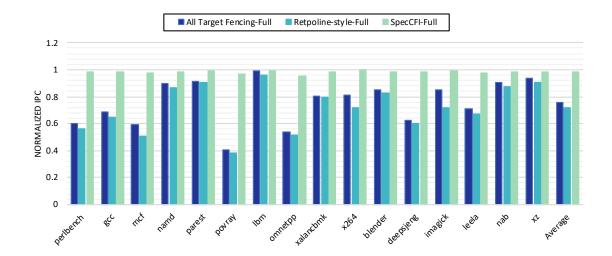

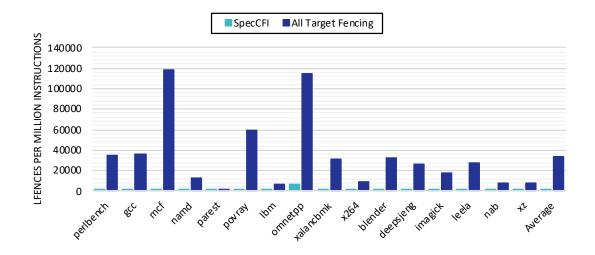

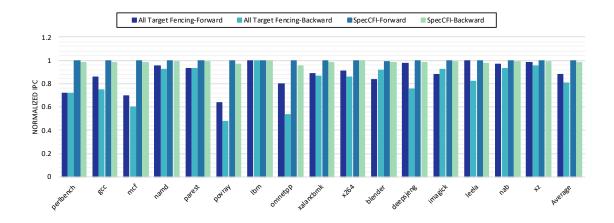

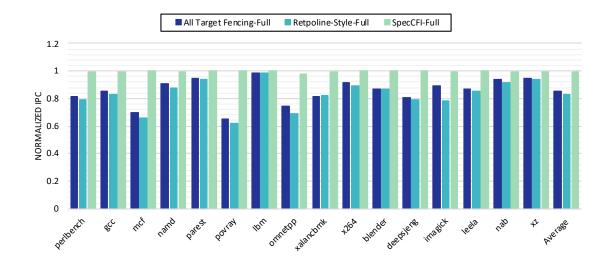

| 4.5 | Performance Impact                                                                           | 75 |

| 4.6 | Number of lfences inserted by different defenses                                             | 77 |

| 4.7 | Overhead breakdown for forward and backward edge                                             | 78 |

| 4.8 | Performance using relaxed fences                                                             | 79 |

| 4.9 | Speculative control-flow bending attack example.                                             | 85 |

| 5.1 | ARM Memory Tagging Extension (MTE)                                                           | 90 |

| 5.2 | MTE: Memory Tagging Extension                                                                | 91 |

| 5.3 | SPECASAN Architecture Overview                     | 96       |

|-----|----------------------------------------------------|----------|

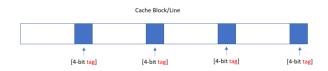

| 5.4 | Extended cache block with MTE tag                  | )7       |

| 5.5 | SPECASAN against Spectre V1                        | )3       |

| 5.6 | SPECASAN against Spectre V4                        | )5       |

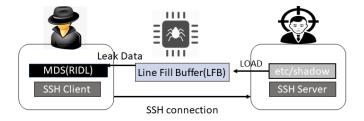

| 5.7 | MDS-LFB Attack Flow 10                             | 17       |

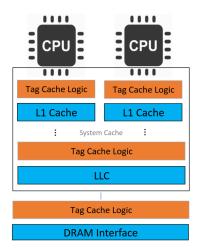

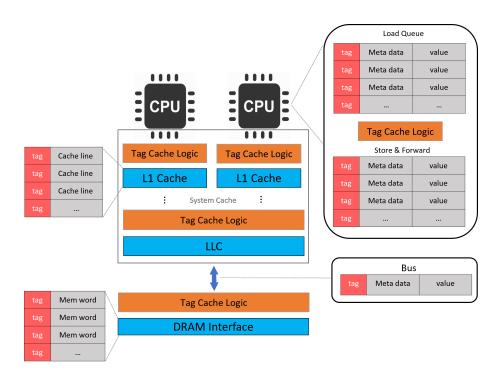

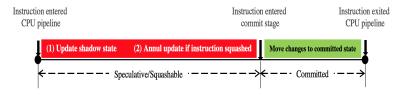

| 6.1 | SafeSpec overview                                  | 5        |

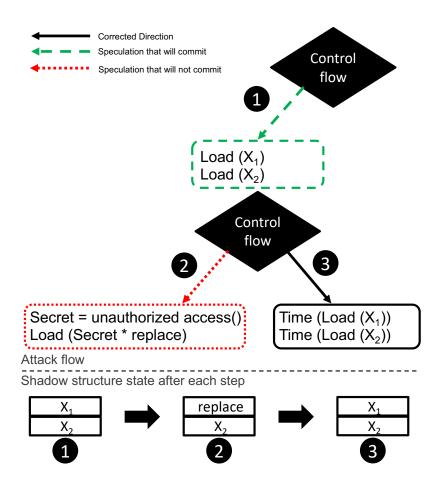

| 6.2 | Transient speculation attack (TSA)                 | 7        |

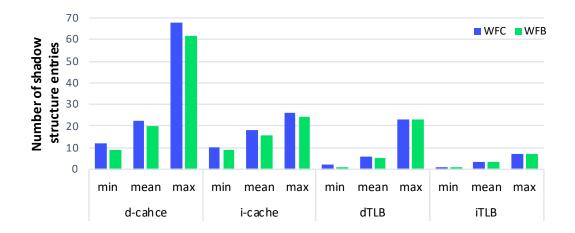

| 6.3 | Shadow structure size that fits 99.99% of accesses | 20       |

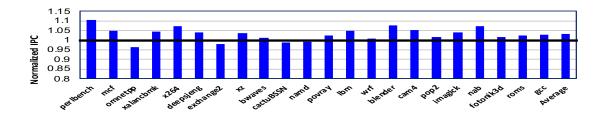

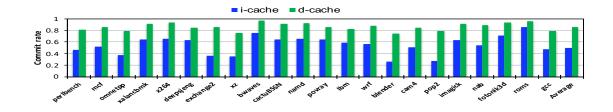

| 6.4 | Relative performance to non-secure OoO execution   | 3        |

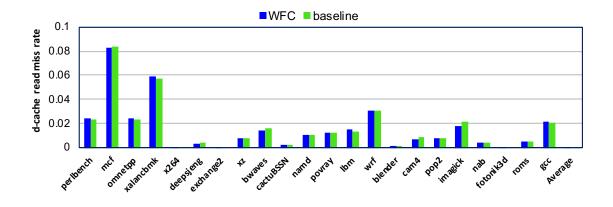

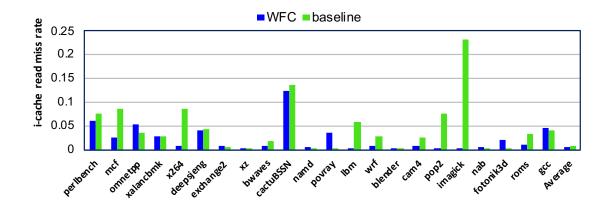

| 6.5 | d-cache read miss rates including shadow d-cache   | 24       |

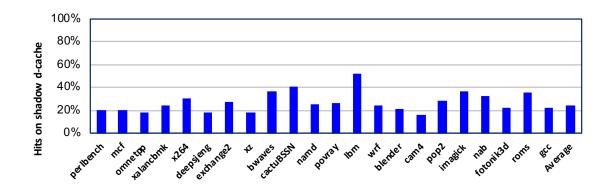

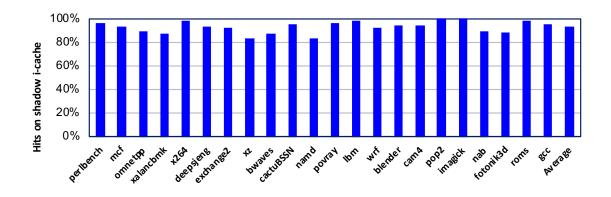

| 6.6 | Percentage of hits on shadow d-cache               | 24       |

| 6.7 | i-cache miss rate including the shadow i-cache 12  | 6        |

| 6.8 | Percentage of hits on shadow i-cache 12            | 26       |

| 6.9 | Commit rate of shadow state 12                     | 27       |

| 7.1 | Optane Memory-Mode Architecture Overview           | 5        |

| 7.2 | Optane DRAM cache                                  | <b>7</b> |

| 7.3 | Optane Memory Access 14                            | 2        |

| 7.4 | Optane DRAM cache access flow 14                   | 8        |

# List of Tables

| 3.1 | Experiment Environment                                                    | 32  |

|-----|---------------------------------------------------------------------------|-----|

| 3.2 | Attack senarios vs. defense mechanisms                                    | 41  |

| 4.1 | Spectre attack variants and their targeted branch prediction components . | 53  |

| 4.2 | ISA Extensions to support CFI                                             | 58  |

| 4.3 | Configuration of the simulated CPU                                        | 73  |

| 4.4 | SPECCFI hardware implementation overhead                                  | 81  |

| 4.5 | Empirical security evaluation of SPECCFI.                                 | 82  |

| 4.6 | Available SMother Gadgets in Standard Libraries                           | 83  |

| 5.1 | ISA Extensions to support MTE                                             | 92  |

| 6.1 | Configuration of the Simulated architecture                               | 123 |

| 6.2 | Security Analysis of Meltdown/Spectre                                     |     |

| 6.3 | SafeSpec hardware overhead at 40nm                                        |     |

| 7.1 | Properties of DRAM when acting as cache for Optane memory 1               | 138 |

# Chapter 1

# Introduction

The number of hardware vulnerabilities has increased significantly in the past few years. With the development of countermeasures against software vulnerabilities, more attention from attackers has been dedicated to finding and exploiting vulnerabilities in hardware. In modern computing systems, hardware is considered the root of trust which provides many security-critical services such as secure boot, secure computation, cryptography acceleration, key management, memory access control, and more. Exploiting hardware vulnerabilities could undermine all the security guarantees offered by the hardware. In addition, hardware designers have proposed and utilized different optimization techniques to improve performance and energy efficiency. There is a tendency, however, to overlook the security of these new optimizations in the design process.

In today's computing devices, caches are well-studied optimizations that aim at hiding memory access latency. However, researchers have shown that computer systems are vulnerable to side-channel attacks which can leak sensitive data like cryptography keys due to timing differences between cache accesses and main memory accesses. More specifically, an adversary can gain information about a system if they can measure leakage in its physical implementation, even if the implementation is otherwise fully secure; such an attack is called a side channel attack. Micro-architectural side channel attacks occur when leakage is measured through process interactions through the shared resources on a processor, including caches and other structures. These attacks are more dangerous on the cloud since tenants share resources.

The recent transient execution attacks such as Spectre and Meltdown, which target speculative execution, a computer architecture optimization technique used for performance, demonstrated how speculative execution can be exploited to enable the disclosure of secret data across both software and hardware isolation boundaries. Specifically, attackers can misguide the processor to speculatively execute a read instruction with an address under their control. Although the speculatively read values are not visible to programs through the architectural state, since the mis-speculation effects are eventually undone, they can be communicated out using a covert channel.

New computing models with combinations of processors augmented by a variety of interconnect and memory architectures lead to new attacks. Accelerators as co-processors in such systems can be either the target of attacks themselves or serve as a vector for launching or amplifying attacks that compromise the main processor or the whole system, bypassing existing mitigations already in place. Having investigated the security of processors, the secure design beyond the CPUs to include cross-processor (CPU-GPU, CPU-FPGA, MultiGPU, ...) attack scenarios and consider all types of processors, memory, and interconnect components in heterogeneous computing systems need to get more attention.

This dissertation pursues two directions:

- Exploring vulnerabilities in computer hardware that are exploitable by software.

- Designing secure systems to protect against these vulnerabilities and, where beneficial, leveraging program analysis.

### 1.1 Contributions of the Dissertation

This dissertation investigates the boundary between hardware and software with respect to computer security, exploring attacks that originate in the hardware, and conversely architecture support for securing systems and software.

#### 1.1.1 Exploring vulnerabilities in computer hardware

#### SpectreRSB

Spectre attacks rely on the attacker manipulating the branch predictors within the processor. The first exploration and disclosure of the attack identified and attacked two predictors: the direction predictor (Spectre v1) and the branch target predictor (Spectre v2). In this thesis, we identified a new Spectre class that targets the return stack buffer (RSB), a structure within modern processors used to predict the target of return instructions. Specifically, we show how an attacker can manipulate the state of the RSB to cause speculative execution of a payload attack gadget that reads and exposes sensitive information from kernel space or otherwise protected data.

#### Intel Optane Side-channel attack

The advancement in data-intensive and high-performance computing, e.g. Large scale machine learning and large-scale graph analytics workloads, has increased the demand for more efficient and scalable memory systems besides specialized accelerators. Emerging Non-Volatile Memories (NVMs) are promising candidates for bridging the bandwidth gap between processor and memory. NVMs can be integrated into different levels of memory hierarchy from caches to main memory. Due to promising aspects, emerging NVMs are already being commercialized by industries e.g Intel's 3D Xpoint and Intel's Optane. The unique characteristics of these emerging memories may lead to security and privacy issues that need to be investigated. In this dissertation, we have studied the possibility of side-channel attacks on these new memories to find the potential vulnerabilities. More specifically we showed the possibility of side-channel attacks when Intel Optane persistent memory operates as the main memory in the system and DRAM is considered as the last level cache. The timing difference between accessing the DRAM and Non-Volatile RAM (NVRAM) can create a side channel.

#### 1.1.2 Designing secure systems against Micro-architectural attacks

Over the past few years, many hardware-level security vulnerabilities such as Spectre, Meltdown, and more recently MDS have been identified which exploit speculative execution and out-of-order execution of processors. Processors are vulnerable to these attacks since they do not consider all available information from software at the time of speculation and so they have to guess program execution paths or use stale data from their internal

buffers. To mitigate these vulnerabilities, we proposed to apply program analysis (e.g static analysis) techniques at the compiler level. These techniques can provide enough information for the processor to disambiguate speculation or only forward data from its internal buffers to the correct instructions. Each class of aforementioned attacks targets different components of the microarchitecture and has unique properties. To mitigate them, the source of speculation should be identified and the proper program analysis techniques should be applied to disambiguate each speculation source. In this dissertation, we proposed SPECCFI, a lightweight solution to prevent the two most dangerous Spectre variants: Spectre-BTB (v2) and Spectre-RSB (v5). SpecCFI prevents these attacks by using control-flow integrity (CFI) principles to identify when a prediction is likely erroneous and constraints speculation if it is, making it the first software-hardware approach to protecting systems against Spectre attacks. We extended the idea of using program analysis during speculation, to defend against more variants of transient execution attacks like MDS and LVI attacks. More specifically, we proposed the Speculative Execution Regulation (SER) as a general class of defense. Since speculative execution states are accessible to an attacker, SER seeks to ensure that security invariants are enforced even during speculation.

We also introduced a new model (SafeSpec) for supporting speculation in a way that is immune to the side-channel leakage necessary for attacks such as Meltdown and Spectre. In particular, SafeSpec stores side effects of speculation in separate structures while the instructions are speculative. The speculative state is then either committed to the main CPU structures if the branch commits, or squashed if it does not, making all direct side effects of speculative code invisible. This dissertation is organized as follows:

Chapter 2 Background and Related Work: This chapter starts by providing a brief overview of cache side-channel attacks. We then describe a general overview of transient execution attacks.

Chapter 3 SpectreRSB: This chapter introduces a new variant of Spectre attack which exploits the Return Stack Buffer (RSB) in modern processor's pipeline. We will discuss the principle of the attack and then show that both local attacks (within the same process such as Spectre 1) and attacks on SGX are possible by constructing proof of concept attacks. We also analyze additional types of attacks on the kernel or across address spaces and show that under some practical and widely used conditions they are possible.

Chapter 4 - Speculative Execution Regulation (SER): This chapter deals with the utilization of program analysis against transient attacks. In this chapter, We will describe SPECCFI, which aims to restrict the control flow of the program to a predefined set of targets. We then show the effectiveness of this approach against Spectre attacks with a very low performance overhead.

Chapter 5- SPECASAN: Protecting Data Speculation using Speculative Address Sanitizer Expanding upon the concept of Speculative Execution Regulation (SER) that leverages program analysis to defend against transient attacks, this chapter presents SPECASAN. As an embodiment of SER, SPECASAN uses the Data Flow Integrity principle to mitigate a broad spectrum of transient attacks, including Meltdown, MDS, and some variants of the Spectre attacks. Chapter 6 - SafeSpec: We introduce (SafeSpec), a new model for supporting speculation in a way that is immune to side-channel leakage by storing side effects of speculative instructions in separate structures until they commit. Additionally, we address the possibility of a covert channel from speculative instructions to committed instructions before these instructions are committed. We develop a cycle-accurate model of the modified design of an x86-64 processor and show that the performance impact is negligible.

*Chapter 7* - Intel Optane side-channel attacks: We report the results of reverse engineering of Intel Optane memory when it operates in memory mode. We then show several possibilities that can lead to side-channel attacks based on reverse engineering results. In end, we discuss the side-channel attacks that we built against Intel Optane memory.

## Chapter 2

# Background

Speculative execution has been an important part of processor architecture starting from the 1950s. The IBM Stretch processor implemented a predict not-taken branch predictor to avoid stalling a processor pipeline when a branch is encountered [30]. Computer architecture advanced rapidly starting in the early 1980s leading to rapid increase in the amount of speculation that is exploited with aggressive out-of-order execution. This speculation is supported by sophisticated branch predictor designs [126, 219, 277] that are highly successful in predicting both the branch direction and its target address. In particular, the number of pipeline stages in production CPUs has continued to grow to the point where modern pipelines commonly have between 15 and 25 stages. With out-of-order execution, when a branch instruction stalls (e.g., due to a cache miss on which it depends), instructions that follow the branch are continuously being issued speculatively. Thus, the speculation window where instructions are getting executed speculatively can be large, typically limited by the size of structures such as the reorder buffer, which can hold a few hundred instructions that are being executed within the pipeline.

Speculation is designed to not affect the correctness of a program. Although branch mispredictions occur and speculative instructions can ignore execution faults (e.g., permission error for memory access) these semantics were not considered harmful as misspeculation will eventually be detected and the erroneously executed instructions will be squashed, leaving no directly visible changes to the program state held in structures such as registers and memory. Micro-architectural structures such as caches and Translation Look-aside Buffers (TLB) are affected by speculative operations, but the contents of such structures typically only affect performance, not the correctness of a program. In fact, prior work has shown that there are beneficial prefetching side-effects to speculatively executed instructions even those that are eventually squashed [179].

This section overviews some background on modern micro-architecture in modern processors: Out of order execution, branch predictor and cache structures.

### 2.1 Out of Order execution (OoO)

Modern processors implement many features designed to avoid delays in processing due to such things as data dependencies, branch/control flow resolutions, and accessing memory. One such feature is out-of-order (O3) execution, in which instructions are often executed speculatively (i.e., as a prediction/guess) in cycles that would otherwise be a stall in the execution pipeline in hopes of gaining performance by removing the stalls if

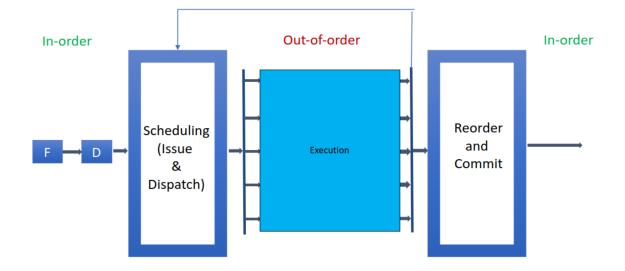

Figure 2.1: Out-Of-Order (O3) Execution

the prediction is correct, and at worst removing the speculatively executed (i.e., transient) instructions if the prediction is incorrect.

This is accomplished by issuing instructions and dispatching them to the proper functional units in program order (i.e., "in-order), allowing them to execute out of program order (i.e., "out-of-order"), and then committing them in program order again when they are finished executing.

To accomplish this, a reorder buffer (ROB) is used to keep track of program order and any dependencies, and instructions are only allowed to commit when they are at the top of the ROB.

In addition, with regard to memory instructions such as loading from or storing to memory, buffers such as load queues (LQ) and stores queues (SQ) are often utilized to keep track of in-flight memory instructions, which are often grouped into a load-store queue (LSQ) to be able to monitor instructions that alias to the same memory location in an attempt to resolve memory dependencies earlier in the pipeline.

#### 2.1.1 Microarchitectural vs Architectural Effects

Many of the optimizations involved in out-of-order execution utilize temporary storage devices that aren't directly visible during normal processing in a system. The ROB, LSQ, and SQ/LQ are examples of these, but there are many others, to include caches, line-fill buffers, return stack buffers (RSBs), as well as Branch Target Buffers (BTBs) and Pattern History Tables (PHTs). The transient instructions and their data stores in these temporary storage devices are referred to microarchitectural states as they differ from the traditionally visible architectural states (such as registers and DRAM), which are visible throughout execution.

### 2.2 Branch prediction

Branch prediction is a critical component of modern processors that support speculative out-of-order execution. When a control flow instruction (branch, call or return) is encountered, the result of the instruction (e.g., whether or not a conditional branch will be taken or what the target value is of an indirect branch or a return) is generally not known at the front end of the pipeline. As a result, to continue to fill the pipeline and utilize the available resources of the processor, branch prediction is used.

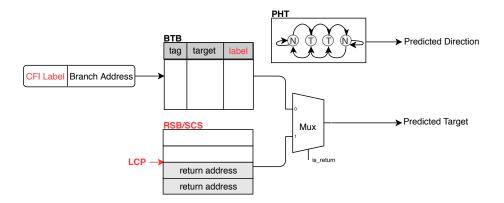

Modern processors employ sophisticated predictors (shown in Figure 2.2) which typically consist of three components:

Figure 2.2: Branch Predictor Unit consists of three different predictors: (1) PHT for conditional branch direction; (2) BTB for indirect branch addresses; and (3) RSB for return addresses.

- Direction predictor: is responsible for predicting the direction of a conditional branch. Although a number of implementations have been studied, modern predictors typically implement a two-level context sensitive predictor [68]. The first level is a simple predictor that hashes each branch address to a direction predictor (typically a 2bit saturating counter). This predictor is used either when a branch is not being successfully predicted or when the predictor has not been trained yet. When the predictor is trained, it typically uses a second prediction algorithm, often a variant of a gshare predictor [277], which uses the global history of a branch in addition to its address to hash to a direction predictor as before. The advantage is that the same branch can have different predictions based on the control flow path used to reach it.

- *Target predictor:* is used by indirect jump and indirect call instructions which jump to an address held in a register or a memory location, which is unknown at the front

end of the pipeline. This predictor typically uses the hash of the branch address to index a cache holding the branch targets called the branch target buffer (BTB). BTBs are shared across threads on a virtual core: one value used by a process could be used by another process whose branch has a matching address in the BTB [70].

• The return address stack: Since returns are not well predicted using the BTB, and often follow strict call-return semantics, their target is predicted using a return address stack of fixed size. When a call instruction executes, the return address is pushed on this hardware stack; if overflow happens, previous entries are overwritten [148]. When a return is encountered the top of the stack is popped and used as the return target.

#### 2.3 Speculation Attacks

In this section we review two main class of Speculation attacks i.e Spectre and Meltdown attacks. Modern processors use different micro-architectural elements to help with branch prediction. Researcher have recently shown that the speculation behavior of modern processors can be exploited. In general, these attacks exploit four properties:

- **P1**: branch prediction validation happens in deep in the CPU pipeline. As a result, speculative instructions near the branch can access unprivileged memory locations.

- **P2**: speculative instructions leave side-effects in micro-architectural structures such as caches, which can be inferred using well-known timing side channel attacks like Prime+Probe and Flush+Reload [274].

- P3: the branch predictor can be mistrained (Spectre 1), or directly polluted (Spectre 2). It is shared across all programs running on the same physical core [70, 95, 145], allowing code running in one privilege domain to manipulate branch prediction in another domain (e.g., kernel, VM, hypervisor, another process, or SGX enclave). SpectreRSB attacks replace this step with speculation control through the RSB.

- **P4**: permission checks are performed deep in the pipeline and execution fault is generated only if the instruction is committed, enabling speculative instructions to access data outside its privilege domain;

```

if (offset < array1_size)

y = array2[array1[offset] * 64];</pre>

```

Figure 2.3: Spectre attack variant 1

#### 2.3.1 Spectre-PHT

Spectre-PHT is presented in Figure 2.3. In this code, a victim process reads values from array1 using the offset provided by the attacker. Then, the resulting value is used to perform an access into array2. As we discussed above, accesses into the array2 can be used by the attacker to deduce the value of the index. The index, in its turn, is controlled by the attacker since attacker controls the offset. Therefore, the attacker can use a carefully selected value of offset to read arbitrary memory address which then will result in cache access observable by the attacker. However, the if statement ensures there are no out of bounds memory accesses allowed. Unfortunately, the attacker can exploit speculative execution and behavior of branch predictor to force the victim process to perform an out of bounds memory access in the following way:

- a) The attacker mistrains the branch predictor by executing the code several times with the value of the offset such that the if statement is true (branch instruction nottaken).

- b) Next, to make the speculative window larger, the attacker evicts array1\_size from the cache, so that the CPU has to load the value from memory. Since the speculation result will not be resolved until this value arrives, forcing it to come from memory expands the size of the speculation window to allow more elaborate speculative gadgets to be executed.

- c) Finally, the attacker chooses the malicious offset such that it be larger than array1\_size. The trained branch predictor unit predicts the branch not-taken, so that the CPU executes two memory accesses speculatively and discloses the secret value through the cache side channel.

#### 2.3.2 Spectre-BTB

The Spectre-BTB attack, exploits the Branch Target Buffer (BTB) in processors. The BTB's role in facilitating branch prediction within speculative execution becomes a critical point of vulnerability, as an attacker can manipulate the BTB to influence the control flow of a victim's program. By carefully selecting a vulnerable indirect branch address in the victim's program, the attacker can cause mispredictions of indirect branch targets, which forces the CPU to speculatively execute a maliciously chosen sequence of instructions, effectively steering the victim's control flow down an unintended path. Although this speculative execution is rolled back later, it leaves behind microarchitectural traces, including alterations in cache state, that can be analyzed to obtain sensitive information. Prior work [70] had shown that the branch predictor is shared among processes on the same core. So, one thread can pollute it for another across protection boundaries (including across VMs). Thus, the attacker can poison the branch target predictor for the victim and force it to speculatively execute the gadget which reveals the sensitive data within the victim. This is a dangerous attack because it allows cross process/cross VM Spectre attacks.

#### 2.3.3 Spectre-STL

This variant of the Spectre attack exploits the fact that memory disambiguation predictor may wrongly determine that a load operation doesn't depend on a preceding store operation when they share the same physical address but different virtual addresses. Due to this incorrect prediction, the load operation proceeds before the store operation is complete. Since the load operation is incorrectly scheduled before the store, it ends up reading an outdated value from the cache. An attacker can craft specific code to exploit this behavior and access data they shouldn't be able to see.

### 2.4 Meltdown, LVI and MDS attacks

The closely related Meltdown attack relies on the fact that a permission check for memory access during normal out-of-order execution of an instruction can happen late in the instruction execution due to pipelining and instruction reordering (P4) allowing the CPU to load the privileged data until the permission is later checked. Unlike Spectre variants, Meltdown does not rely on using misspeculation. Since an exception eventually will be raised, this attack requires the ability to tolerate and recover from the raised exception.

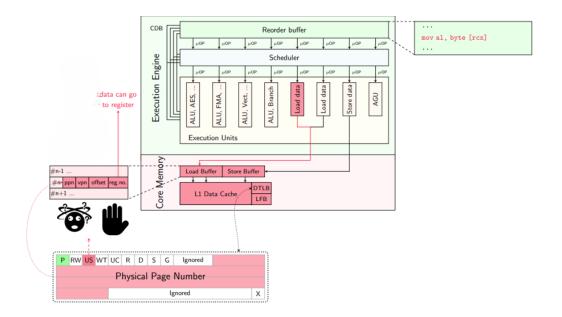

Researchers have demonstrated that several variants of Meltdown-type attacks and Micro-architectural Data Sampling (MDS) attacks exhibit shared characteristics. These common traits enable attackers to extract sensitive data from specific internal microarchitectural elements, notably the L1 Data Cache (L1D), Line Fill Buffer, Load Port, Store Buffer, and Register Files. In their comprehensive study, Gruss et al. [83] categorize these attacks based on their distinctive micro-architectural behaviors.

- Deferred Permission Check Some Meltdown-type attacks exploit the fact that permission checks occur late in the pipeline, allowing the attacker to gain access to higher-privilege data. The original Meltdown attack (Meltdown-US) enables an attacker with user privilege to access kernel data due to improper checking of the US (User Accessible bit).

- Incorrect Use of Intermediate Values In another type of Meltdown attack, attackers aim to misuse intermediate values. For example, in the Foreshadow attack [240], if the present bit is not set and the processor raises an exception, the processor will still copy the physical address(intermediate value) into the load buffer entry. By exploiting this, the attacker will be able to index into the L1 Dcache and other internal buffers, potentially leaking sensitive data.

• Use After Free More recent variations of Meltdown-type attacks seem to leverage the use-after-free type vulnerability. This flaw leads to the use of outdated values, as observed in instances such as ZombieLoad [211], RIDL [244], and Fallout [178].

We explain the meltdown and MDS general attack flow based on 2.4. When a load micro-operation is placed into the re-order buffer, an entry in the load-buffer (or more broadly, a memory-order buffer for a load memory operation) is allocated ( $\bullet$ ) to guarantee the proper sequencing of memory load visibility. When the load micro-op is scheduled for the load-data execution unit, it accesses its corresponding entry in the load buffer during step  $\bullet$ . At this stage, the load buffer entry still holds stale data: a stale register number, outdated virtual address information, and a lingering physical address. During Step  $\bullet$ , the load-buffer entry is refreshed with the register number and the virtual address details from the load micro-op, such as the virtual page number and offset.