# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Digital signal generation for wireless communication systems

#### **Permalink**

https://escholarship.org/uc/item/84s281ct

#### **Author**

Rode, Jeremy

#### **Publication Date**

2010

Peer reviewed|Thesis/dissertation

# Digital Signal Generation for Wireless Communication Systems

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electrical Circuits and Systems)

by

Jeremy Rode

#### Committee in charge:

Professor Peter M. Asbeck, Chair Professor Lawrence E. Larson Professor Ian Galton Professor Andrew B. Kahng Professor C. Fred Driscoll

©

Jeremy Rode, 2010

All rights reserved

| The dissertation of Jeremy Rode is approved, and it  |          |

|------------------------------------------------------|----------|

| is acceptable in quality and form for publication on |          |

| microfilm and electronically:                        |          |

|                                                      |          |

|                                                      | _        |

|                                                      | -        |

|                                                      | _        |

|                                                      | _        |

| Ch                                                   | _<br>air |

University of California, San Diego 2010

# **Dedication**

To my parents and Dr. Nibbles

# **Table of Contents**

| Signature Page       | e                                                                | iii  |

|----------------------|------------------------------------------------------------------|------|

| Dedication           |                                                                  | iv   |

| Table of Conto       | ents                                                             | v    |

|                      | 3                                                                |      |

| -                    |                                                                  |      |

| Acknowledge          | ments                                                            | xvii |

| Vita                 |                                                                  | xix  |

| Publications         |                                                                  | xix  |

|                      | e Dissertation                                                   |      |

| <b>CI</b> 4 <b>1</b> |                                                                  |      |

| Chapter 1            |                                                                  | 1    |

| Introduction         | W. 1 G                                                           |      |

| 1.                   | Wireless Communication Systems                                   |      |

| 2.                   | Transmitters for Wireless Communication Systems                  |      |

| 2.1.                 | Baseband Signal Generation                                       |      |

| 2.2.                 | Classical Transmitters                                           |      |

| 2.3.                 | Digital Transmitters                                             |      |

| 2.4.                 | Digital Encoding / Quantization                                  |      |

| 2.5.                 | Transmitter Figures of Merit                                     |      |

| 3.                   | Migrating from Analog to Digital                                 |      |

| 4.                   | Goals of Dissertation.                                           |      |

| 5.                   | Organization of Dissertation                                     |      |

| 5.1.                 | Communication Standards Chosen                                   |      |

| 5.2.                 | Chapter Organization                                             | 17   |

| 6.                   | References                                                       | 20   |

| Chapter 2            |                                                                  |      |

| Digital Transn       | nitter Design Issues and Metrics                                 | 21   |

| 1.                   | Introduction                                                     | 21   |

| 2.                   | Design and Measurement Challenges                                | 21   |

| 2.1.                 | Digital Amplifier Testing                                        | 22   |

| 2.2.                 | Switching Amplifiers and Aperiodic Drive                         | 23   |

| 3.                   | Figures of Merit and Metrics to Address Digital Amplifier Design | 24   |

| 3.1.                 | Drain Efficiency                                                 | 24   |

| 3.2.                 | Multistage Efficiency and Power-Added Efficiency                 |      |

| 3.3.                 | System Efficiency                                                |      |

| 3.4.                 | In-Band Power Ratio for Digital Amplifiers                       | 26   |

| 4.                   | Conclusion                                                       |      |

| 5.                   | References                                                       |      |

| Chapter 3            |                                                                  |      |

| -                    | 5.4) Transmitter Demonstration                                   | 30   |

| 1.                   | Introduction                                                     |      |

| 2.                   | ZigBee (802.15.4)                                                |      |

| 3.      | Quantization Algorithm                                     | 32 |

|---------|------------------------------------------------------------|----|

| 3.1.    | Motivation                                                 |    |

| 3.2.    | Noise Spreading Algorithm                                  | 33 |

| 3.3.    | In-Band Power Ratio.                                       |    |

| 3.4.    | Algorithmic Power Control.                                 | 34 |

| 3.5.    | Power Consumption                                          | 36 |

| 4.      | The 802.15.4 / Zigbee Transmitter                          | 37 |

| 4.1.    | Transmitter Architecture                                   |    |

| 4.2.    | Simulation Setup                                           | 38 |

| 4.3.    | Simulation Results                                         | 40 |

| 4.4.    | Transmitter Architecture Power Dissipation Simulation      | 42 |

| 4.5.    | The Voltage-Mode Class-D CMOS Amplifier                    |    |

| 5.      | Measurements                                               |    |

| 5.1.    | Measurement Setup.                                         |    |

| 5.2.    | VMCD Square Wave Measurement Results                       |    |

| 5.3.    | ZigBee Power Measurement Results                           |    |

| 5.4.    | Spectral Measurement Results                               |    |

| 6.      | Comparison with Traditional Transmitters                   |    |

| 6.1.    | System Efficiency                                          |    |

| 6.2.    | External Components                                        |    |

| 7.      | Conclusion                                                 |    |

| 8.      | Acknowledgments                                            |    |

| 9.      | Appendix A: VHDL Source Code                               |    |

| 9.1.    | Top-level VHDL Source Code                                 |    |

| 9.2.    | LFSR VHDL Source Code                                      |    |

| 10.     | References                                                 | 57 |

| Chapter | 4                                                          |    |

|         | QPSK Delta-Sigma Digital Transmitter Demonstration         | 57 |

| 1.      | Introduction                                               |    |

| 2.      | CDMA / QPSK                                                |    |

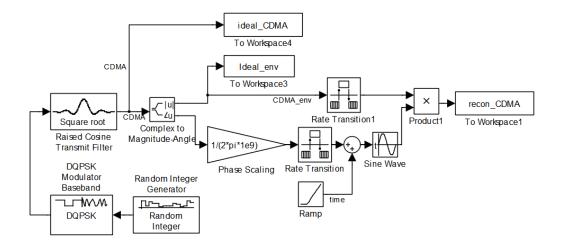

| 3.      | System Description                                         | 59 |

| 3.1.    | Baseband                                                   |    |

| 3.2.    | Upsampling                                                 |    |

| 3.3.    | Frequency Translation                                      | 61 |

| 3.4.    | Amplification                                              | 64 |

| 3.5.    | Reconstruction Filter                                      | 65 |

| 4.      | Delta-Sigma Modulator Simulations                          | 65 |

| 4.1.    | Modulator Noise Transfer Function                          | 66 |

| 4.2.    | Optimizing a Delta-Sigma Modulator for Full Duplex Receive |    |

|         | Band Noise                                                 | 68 |

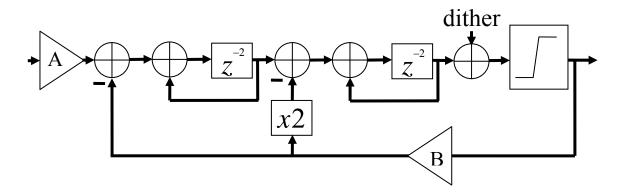

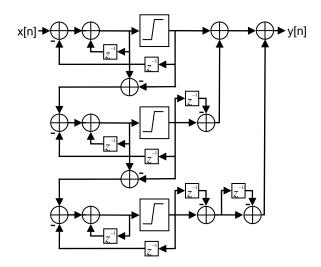

| 4.3.    | Modulator Block Diagram                                    | 69 |

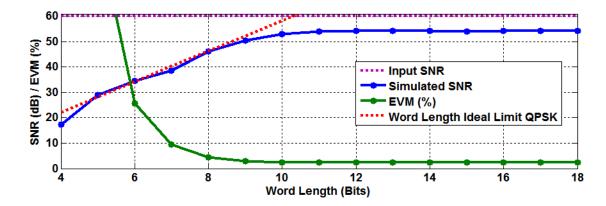

| 4.4.    | Modulator Numerical Representation                         |    |

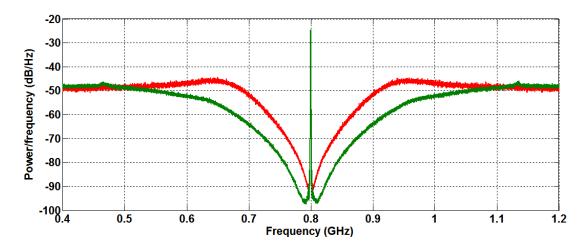

| 4.5.    | Dithering                                                  | 73 |

| 4.6.    | Digital Integrator Overflow                                |    |

| 4.7.    | Number of Quantizer States                                 |    |

| 4.8.      | In-Band Power Ratio                                      | 78  |

|-----------|----------------------------------------------------------|-----|

| 4.9.      | Gain Control                                             | 80  |

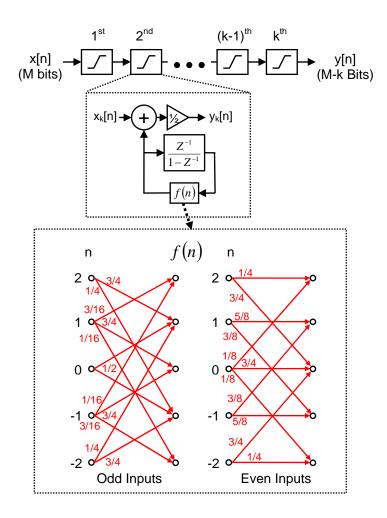

| 5.        | Delta-sigma Modulator Hardware Implementation            | 81  |

| 5.1.      | Band-pass Resonator Parallelization.                     |     |

| 5.2.      | Two's Complement Negation Optimization                   |     |

| 5.3.      | Triple Input Adders                                      |     |

| 5.4.      | FPGA Implementation                                      | 86  |

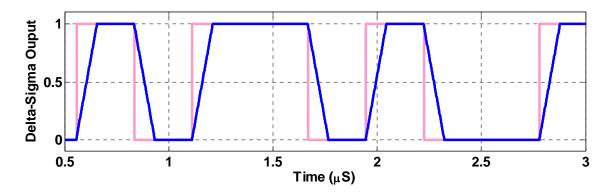

| 6.        | Hardware Measurements                                    | 88  |

| 7.        | Summary and Conclusions                                  | 91  |

| 8.        | Acknowledgments                                          | 91  |

| 9.        | References                                               | 92  |

| Chapter 5 |                                                          |     |

|           | Mode Nonlinearities and Broadband Noise                  | 94  |

| 1.        | Introduction                                             | 94  |

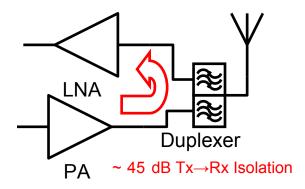

| 2.        | Frequency-Division Full-Duplex Communication             | 95  |

| 3.        | Delta-sigma NTF and Full Duplex Receive Band             | 96  |

| 4.        | Quantifying Nonlinearities in VMCD Amplifiers            |     |

| 4.1.      | Delta-Sigma Driven VMCD Amplifier Simulations            |     |

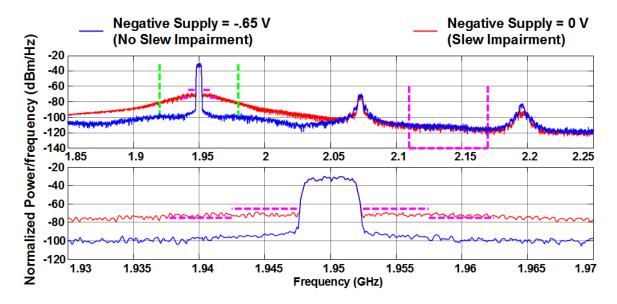

| 4.2.      | Asymmetrical Slew Rate Non-idealities                    |     |

| 4.3.      | Mismatched On Resistances                                |     |

| 4.4.      | Supply Memory                                            |     |

| 4.4.1.    | Simulation                                               |     |

| 4.4.2.    | Analysis                                                 |     |

| 5.        | VMCD Amplifier Redesign                                  |     |

| 5.1.      | Simulations and Design                                   |     |

| 5.2.      | Chip-on-Board                                            |     |

| 5.3.      | Spectral Measurements                                    |     |

| 6.        | Conclusion                                               |     |

| 7.        | Acknowledgments                                          |     |

| 8.        | References                                               |     |

| Chapter 6 |                                                          |     |

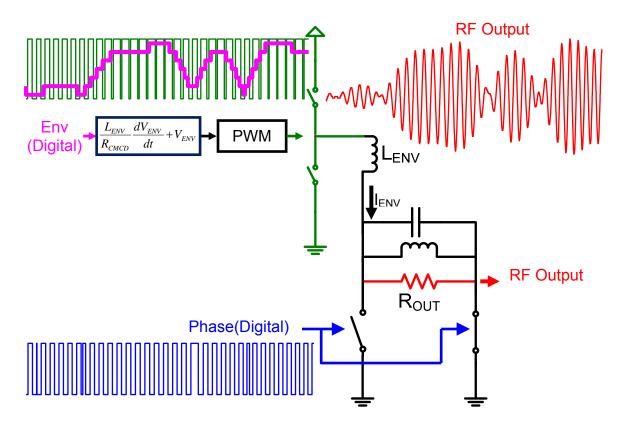

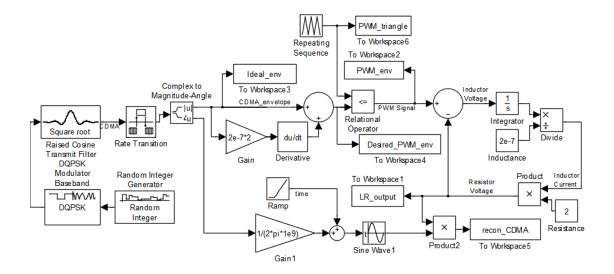

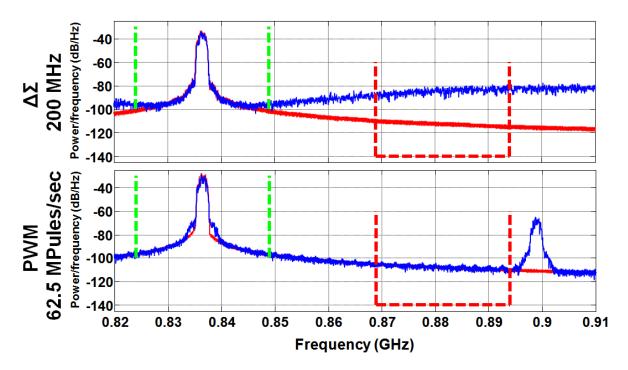

|           | Pulse Width Modulation Applied to Microwave Transmitters | 120 |

| -         | Introduction                                             |     |

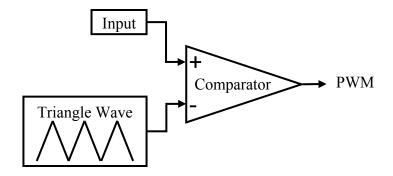

| 2.        | Pulse Width Modulation                                   |     |

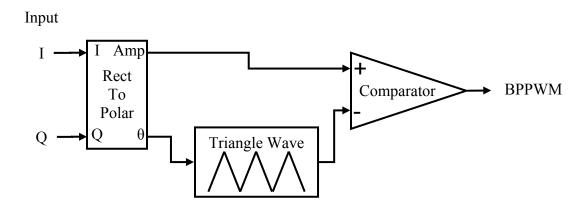

| 3.        | Band-Pass Pulse Width Modulation                         |     |

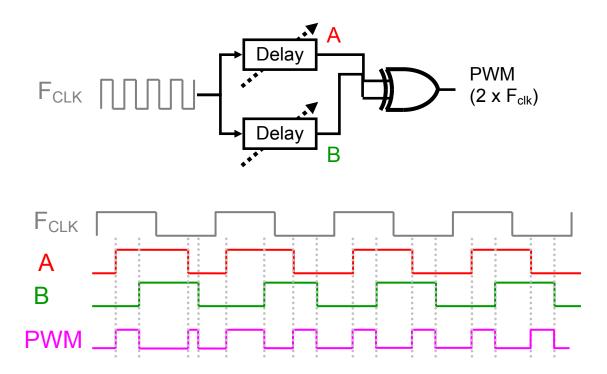

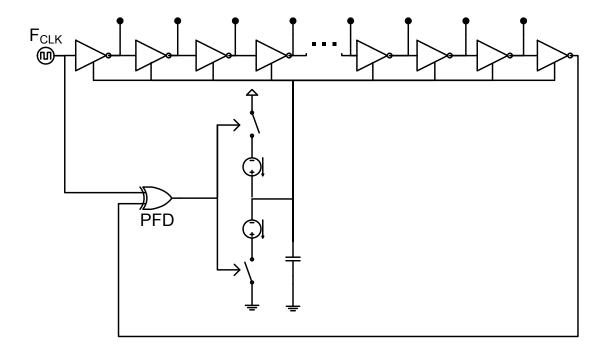

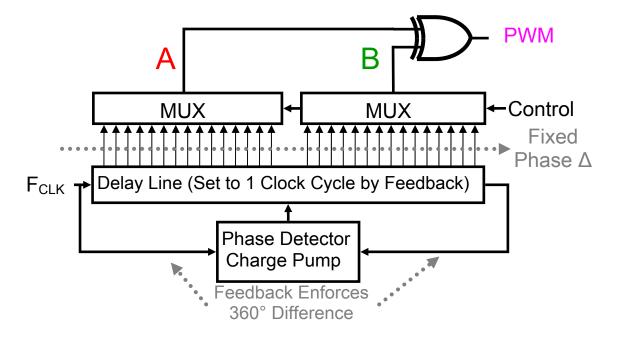

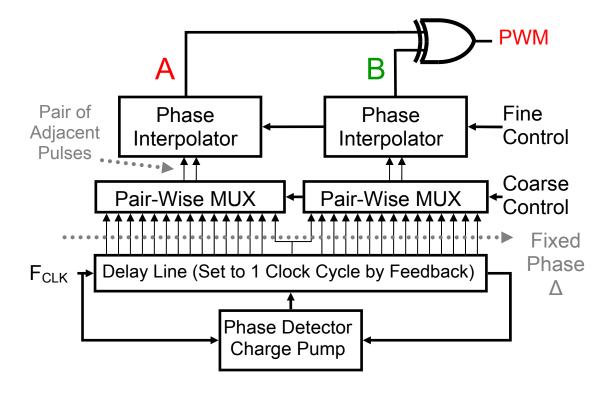

| 4.        | Generating PWM/BPPWM signals                             |     |

| 5.        | Synchronous Versus Asynchronous PWM/BPPWM                |     |

| 6.        | Traditional Digital PWM Generation                       |     |

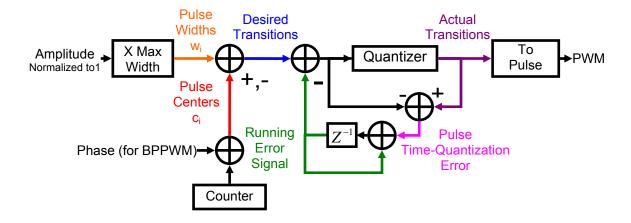

| 7.        | Shaping PWM Time Quantization Noise                      |     |

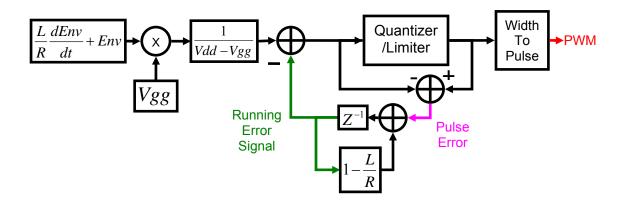

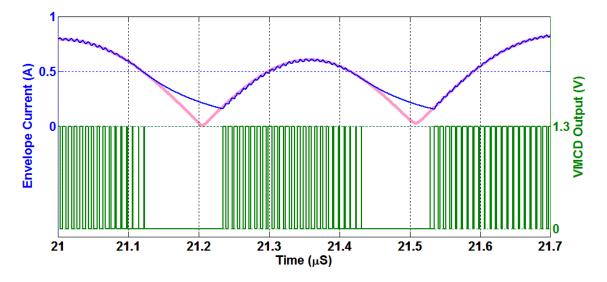

| 8.        | Generating Asynchronous PWM/BPPWM Digitally              |     |

| 9.        | Simulating Asynchronous PWM/BPPWM                        |     |

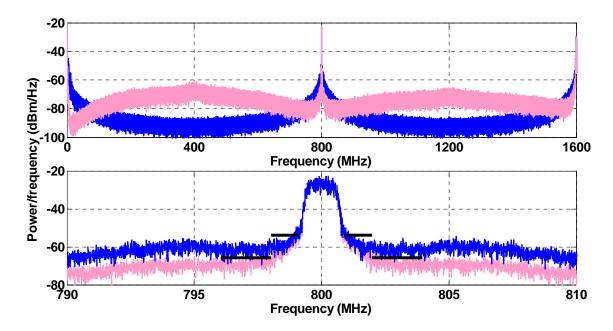

| 10.       | VMCD Broadband Noise Excited by BPPWM vs. Delta-sigma    | 138 |

| 11.       | Experimental Results                                     |     |

| 11.1.     | Time Quantization Noise in Generated Signal              |     |

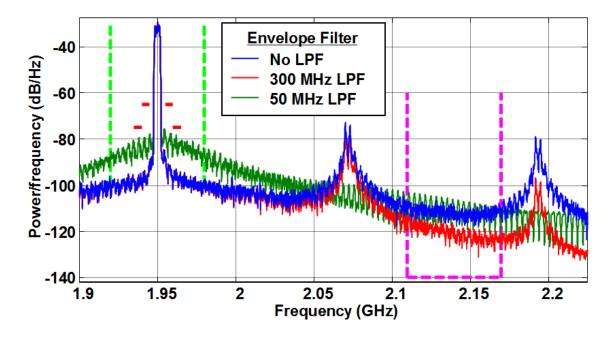

| 11.1.     | Spectral Performance                                     | 141 |

| 11.3.      | Efficiency Performance                                        | 142         |

|------------|---------------------------------------------------------------|-------------|

| 12.        | Conclusion                                                    | 143         |

| 13.        | Acknowledgments                                               | 144         |

| 14.        | References                                                    |             |

| Chapter 7  |                                                               |             |

| _          | r Amplifier                                                   | 145         |

| 1.         | Introduction                                                  |             |

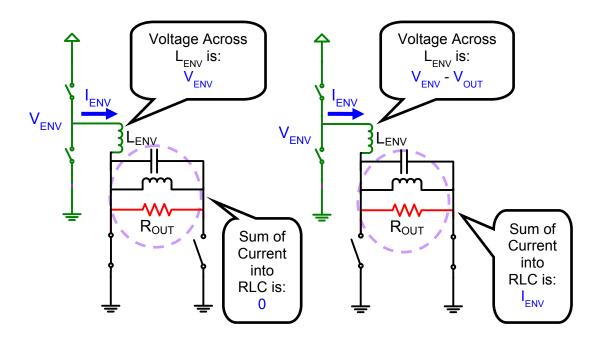

| 2.         | Polar Amplifiers                                              |             |

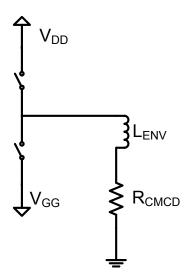

| 3.         | The VMCD/ CMCD Digital Polar Amplifier                        |             |

| 4.         | Targeted Communication Standard                               |             |

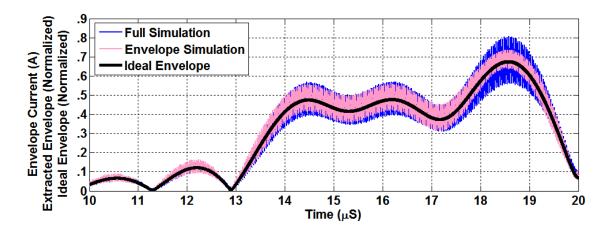

| 5.         | Simulation Methodology                                        |             |

| 6.         | Encoding Algorithm Selection                                  |             |

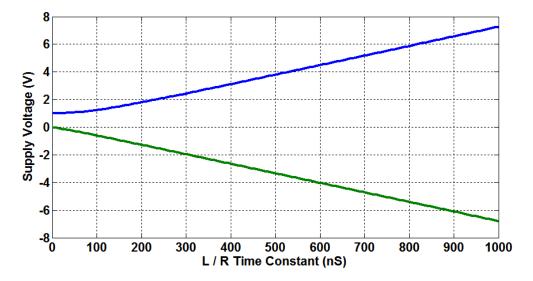

| 7.         | Inductor Sizing.                                              |             |

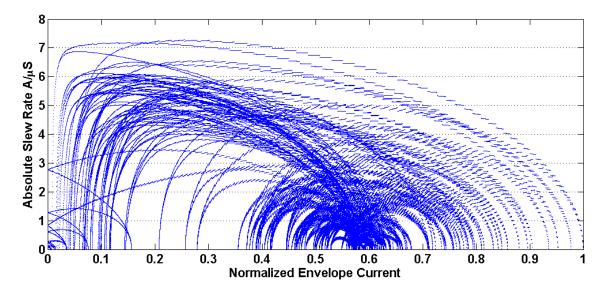

| 8.         | Envelope Inductor Current Slew Rate                           |             |

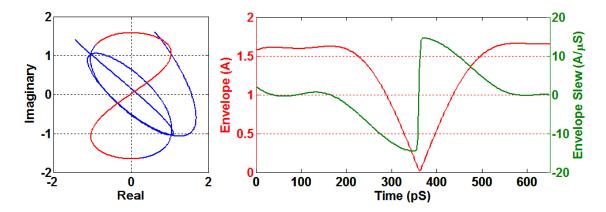

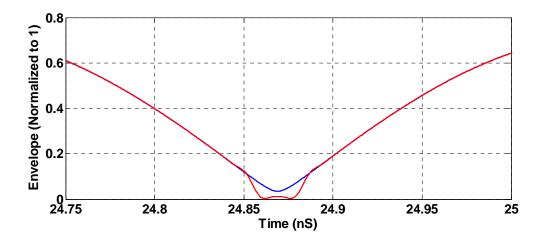

| 8.1.       | WCDMA Envelope Slew Rate and Zero-Crossings                   |             |

| 8.2.       | Polar Envelope Slew Rate Expansion                            |             |

| 9.         | Envelope Current Slew Rate Limitations for the VMCD/CMDC Pol  | 10 1<br>lar |

| <i>)</i> . | Amplifier                                                     |             |

| 9.1.       | WCDMA Peak-to-Minimum Ratio.                                  |             |

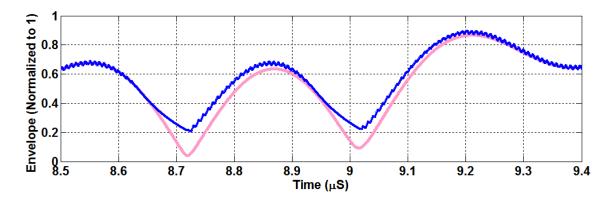

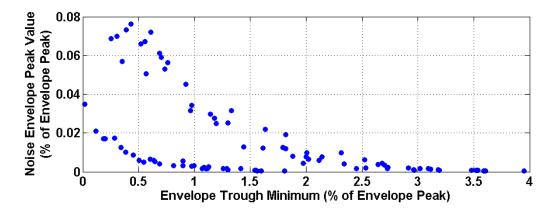

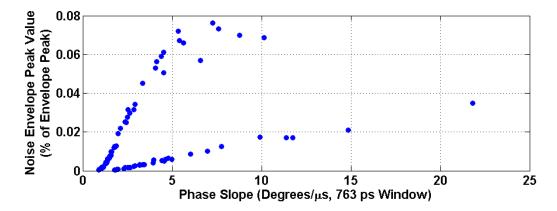

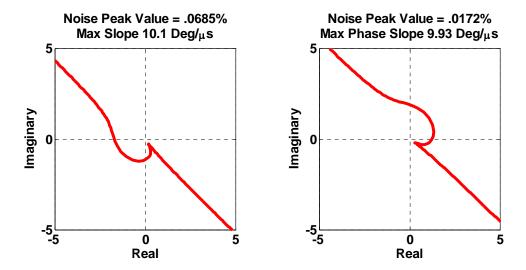

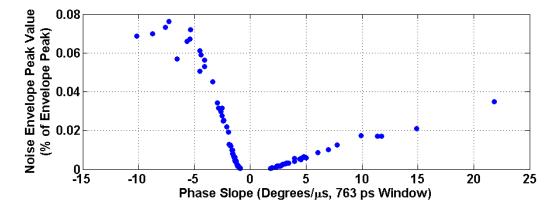

| 9.2.       | Envelope Error Memory                                         |             |

| 9.3.       | PWM Modulators and Sampled Time                               |             |

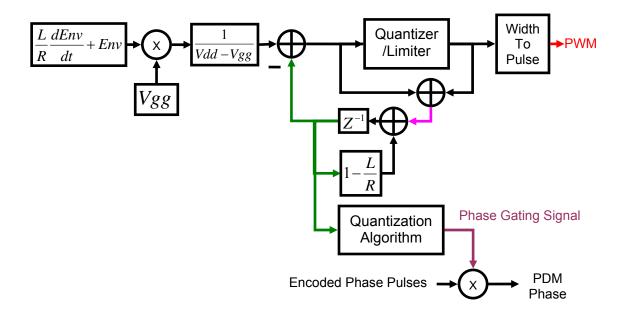

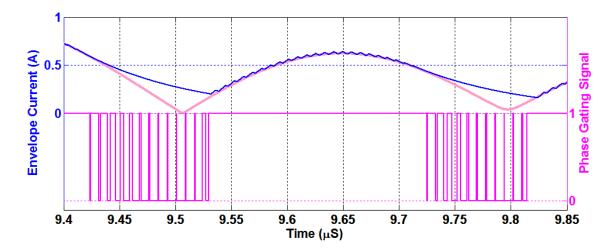

| 9.4.       | Pulse Density Modulation in the Phase Path                    |             |

| 10.        | Polar System Broadband Noise Generation                       |             |

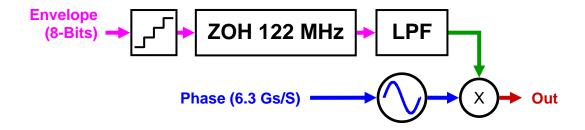

| 10.1.      | Finite Bandwidth Signals                                      |             |

| 10.1.      | Time Alignment                                                |             |

| 10.2.      | Time Misalignment Error Derivation                            |             |

| 10.2.1.    | Time Misalignment Error Trajectory                            |             |

| 10.2.2.    | Envelope Pre-distortion for Broadband Noise Suppression       |             |

| 10.2.3.    | Conclusion                                                    |             |

| 11.        | Acknowledgments                                               |             |

| 13.        | E                                                             |             |

|            | References                                                    | 192         |

| Chapter 8  | Diment Engagement Symthesis                                   | 102         |

|            | Direct Frequency Synthesis                                    |             |

| 1.         | Introduction                                                  |             |

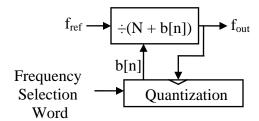

| 2.         | Frequency Synthesis                                           |             |

| 3.         | Fractional-N Direct Frequency Synthesis                       |             |

| 4.         | Delta-Sigma Based Fractional-N Direct Frequency Synthesis     |             |

| 5.         | Successive Requantization                                     | 198         |

| 6.         | Successive Requantization Based Fractional-N Direct Frequency | 200         |

| _          | Synthesizer                                                   |             |

| 7.         | Measurements                                                  |             |

| 8.         | Conclusion                                                    |             |

| 9.         | Acknowledgments                                               |             |

| 10.        | References                                                    | 204         |

| Chapter 9  |                                                               |             |

| Conclusion |                            | 205 |

|------------|----------------------------|-----|

| 1.         | Dissertation Summary       |     |

| 2.         | Conclusion and Future Work | 207 |

# **List of Figures**

| Chapter 1  |                                                                                                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

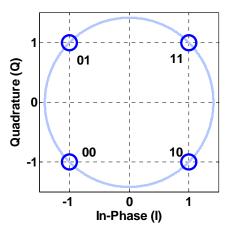

| Figure 1:  | Example QPSK constellation diagram annotated with Gray code symbol                                                                                          |

| C          | mapping and the unit circle.                                                                                                                                |

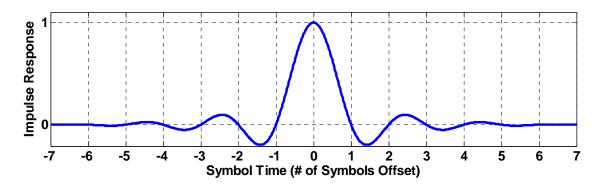

| Figure 2:  | Raised cosine filter impulse response (roll-off factor = 0.22).                                                                                             |

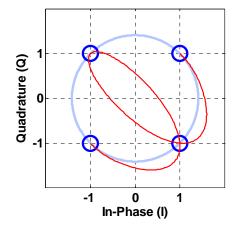

| Figure 3:  | Example I/Q signal trajectory from a 11 10 01 10 00 data stream                                                                                             |

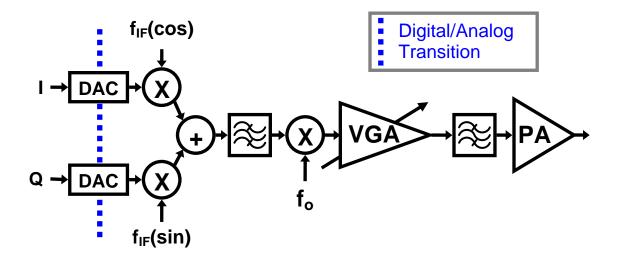

| Figure 4:  | Block diagram of a heterodyne transmitter6                                                                                                                  |

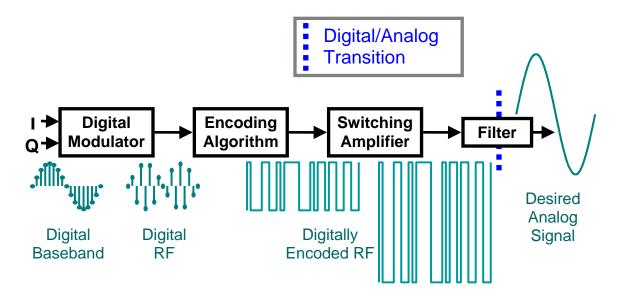

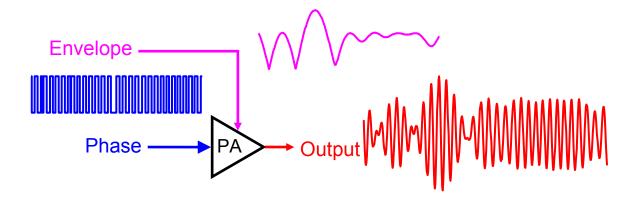

| Figure 5:  | Block diagram of a digital transmitter. Shown with exaggerated example waveforms                                                                            |

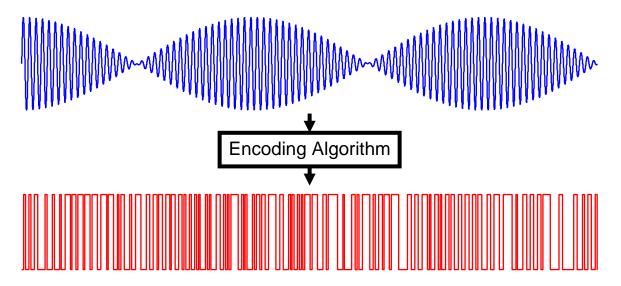

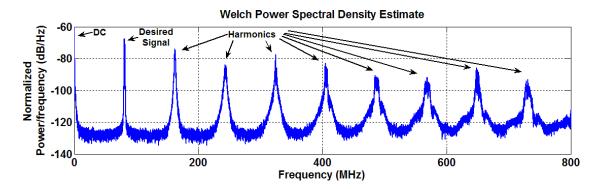

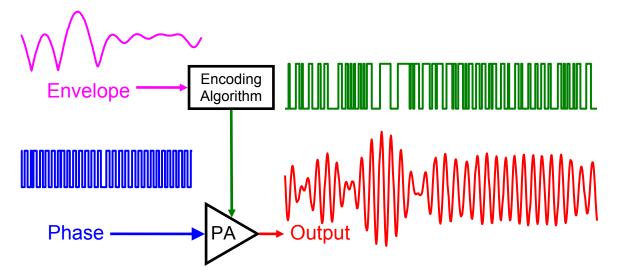

| Figure 6:  | Example waveforms of an encoding algorithm quantizing a two-tone signal Input at the top, and output at the bottom.                                         |

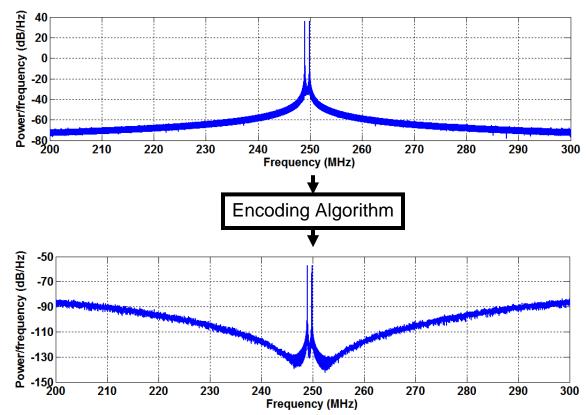

| Figure 7:  | Computed spectra of the signals from Figure 6. Input at the top, and output at the bottom                                                                   |

| Chapter 2  |                                                                                                                                                             |

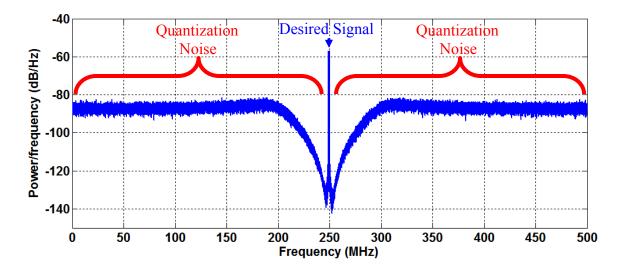

| Figure 1:  | Spectra of two-tone from chapter 1, Figure 4, zoomed out to the Nyquist frequency and marked to illustrate in-band power ratio  27                          |

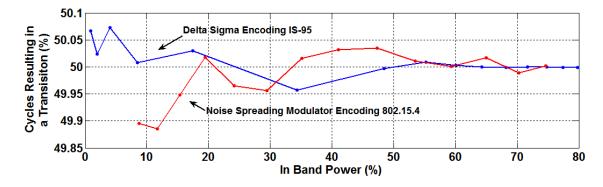

| Figure 2:  | Switching probability of different encoding algorithms encoding different communication standards to be used in this work (IS-95 CDMA and ZigBee/802.15.4). |

| Chapter 3  |                                                                                                                                                             |

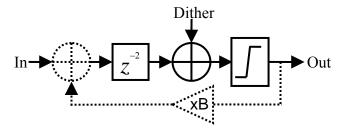

| Figure 1:  | Block diagram of the direct quantization algorithm with optional power control feedback show in dashed lines                                                |

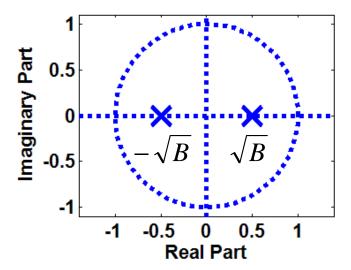

| Figure 2:  | Z-plane plot of noise transfer function of the noise spreading algorithm34                                                                                  |

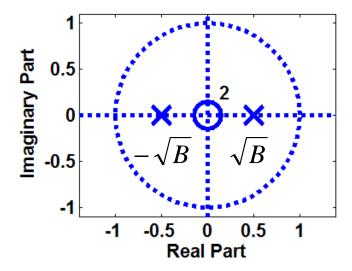

| Figure 3:  | Z-plane plot of signal transfer function of the noise spreading algorithm35                                                                                 |

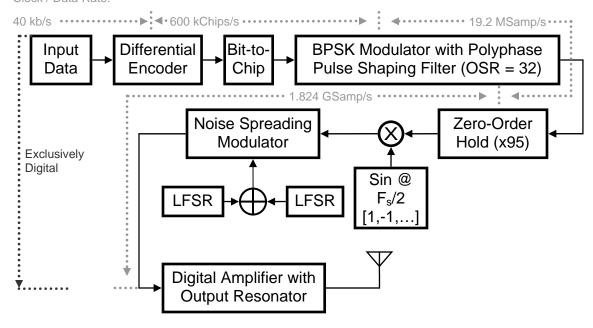

| Figure 4:  | diagram of proposed transmitter architecture                                                                                                                |

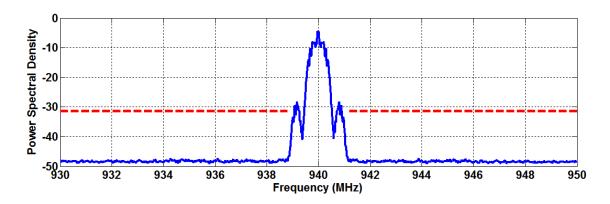

| Figure 5:  | Simulated PSD of the ZigBee signal. The spectral mask is shown in dashed red                                                                                |

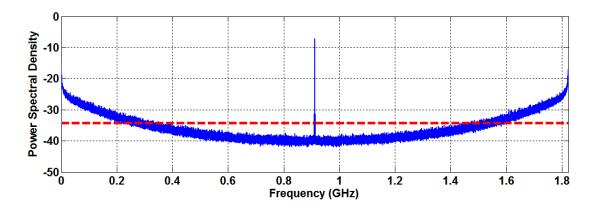

| Figure 6:  | Simulated wideband PSD of noise spreading algorithm in high algorithmic power back-off. The spectral mask is shown in dashed red40                          |

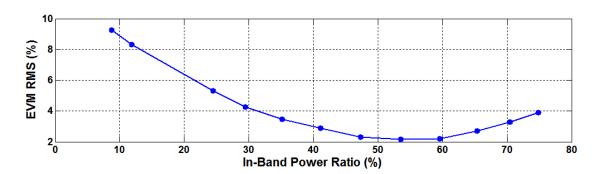

| Figure 7:  | Simulated EVM vs. algorithmic power back-off40                                                                                                              |

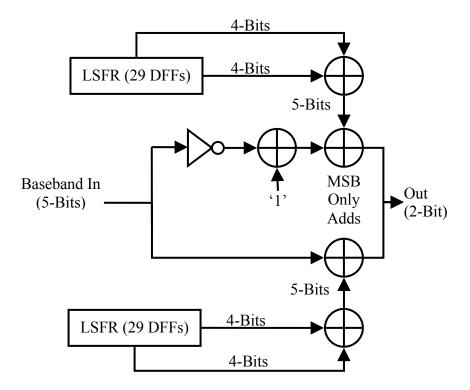

| Figure 8:  | Block diagram of the digital functionality implemented in VHDL41                                                                                            |

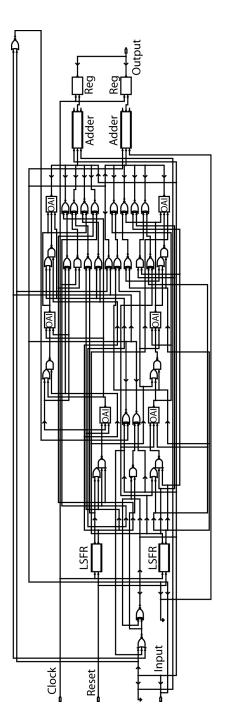

| Figure 9:  | Synthesized schematic of noise spreading modulator                                                                                                          |

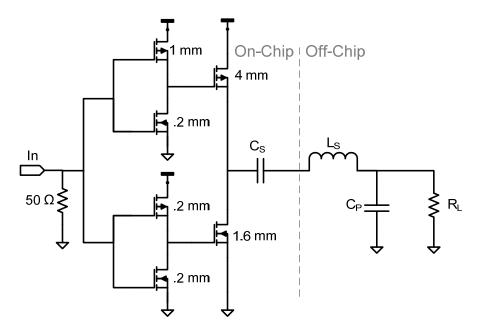

| Figure 10: | Schematic of the CMOS VMCD amplifier. Supply decoupling capacitors omitted. All transistor lengths are the 0.18 µm minimum45                                |

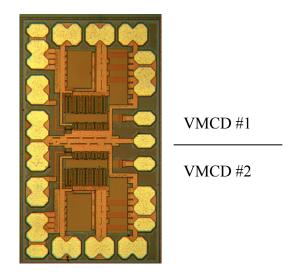

|            | Die photograph of the dual VMCD amplifier chip45                                                                                                            |

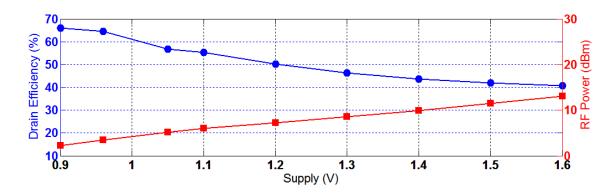

| Figure 12: | Measured square wave drain efficiency (blue with circle markers) and RF Power (red with square markers) vs. supply with a 935 MHz square wave               |

| Figure 13: | drive signal                                                                                                                                                |

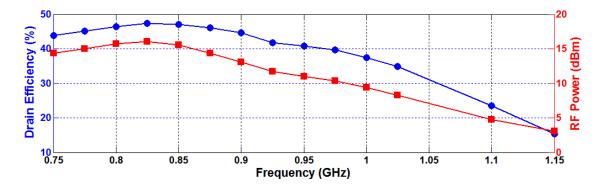

| Ei 14      | power (red with square markers) vs. Frequency with a 1.5 V supply                                                                                           |

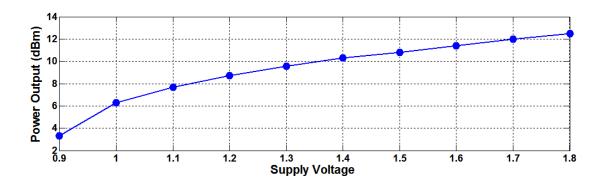

|            | Measured 802.15.4 / ZigBee power output power vs. supply                                                                                                    |

|            | , ii , , , , , , , , , , , , , , , , ,                                                                                                                      |

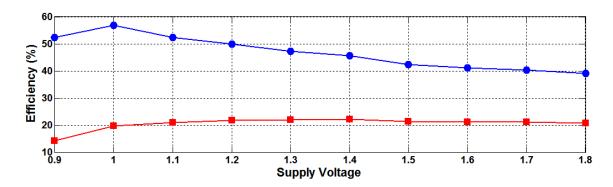

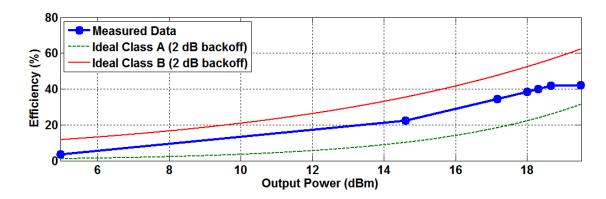

|   | Figure 16:  | Measured ZigBee drain efficiency with algorithmic power back-off               |

|---|-------------|--------------------------------------------------------------------------------|

|   |             | compared to two ideal efficiencies for classical panalog amplifiers49          |

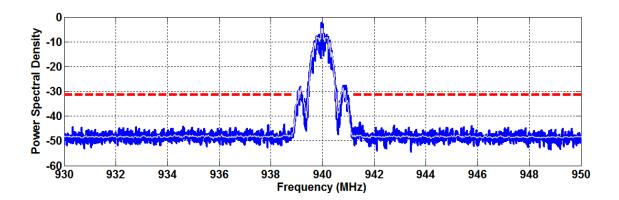

|   | Figure 17:  | In-band measured output spectrum at 1.5 V supply with 802.15.4 relative        |

|   |             | PSD mask (RBW = 10 kHz). Shown with the simulated spectrum overlaid            |

|   |             | in light gray50                                                                |

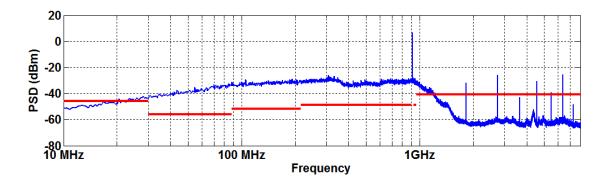

|   | Figure 18:  | Full measured output spectrum at 1.5V supply with FCC spurious emission        |

|   |             | limits. $(RBW = 100 \text{ kHz})$ 50                                           |

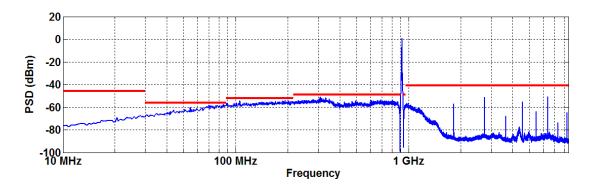

|   | Figure 19:  | Above measured spectrum with modeled second order elliptic output filter       |

|   | · ·         | applied51                                                                      |

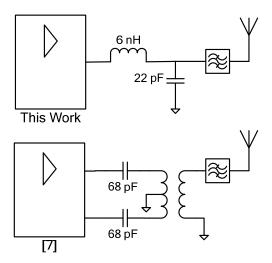

|   | Figure 20:  | Schematic of external RF components required by proposed transmitter           |

|   | Ü           | (top) versus [7] (bottom)                                                      |

| ( | Chapter 4   |                                                                                |

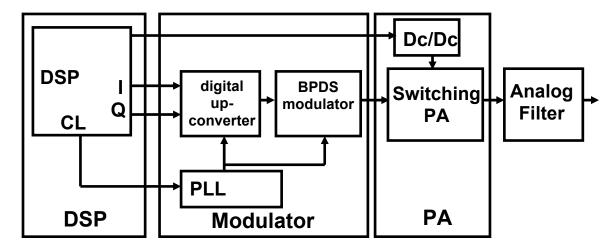

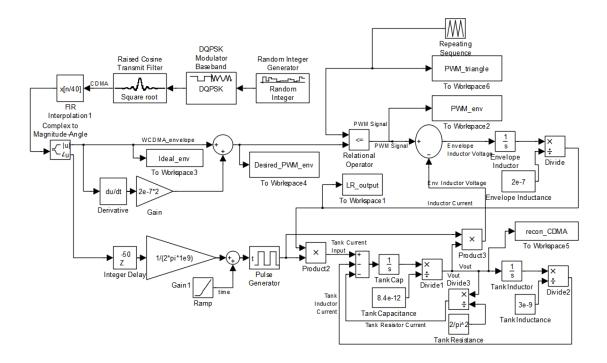

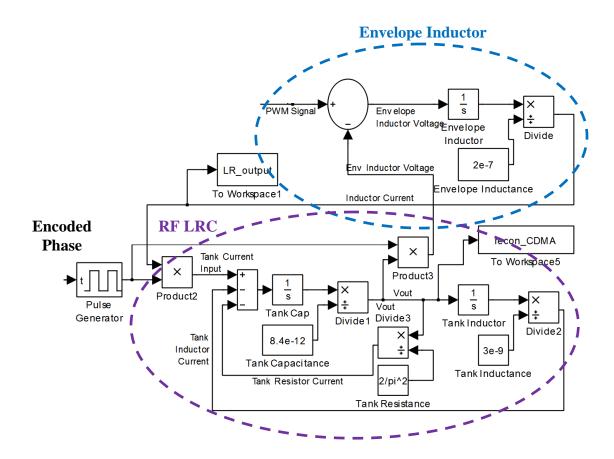

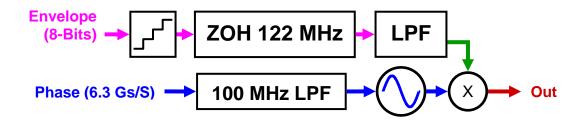

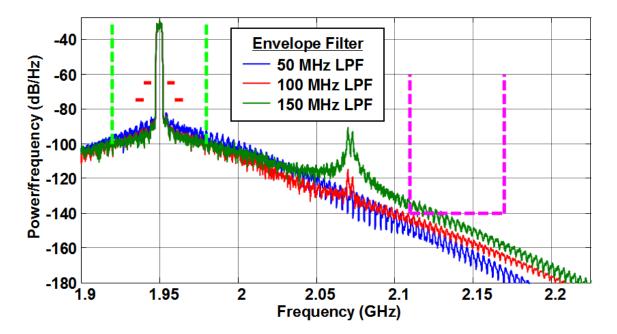

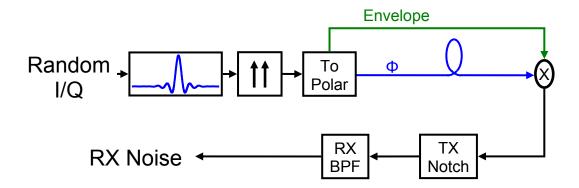

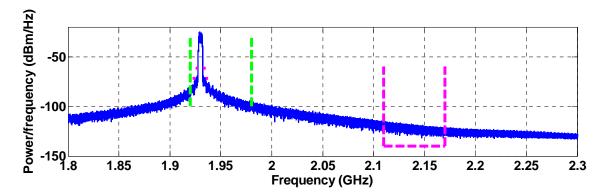

| _ | Figure 1:   | System block diagram for an all-digital transmitter                            |

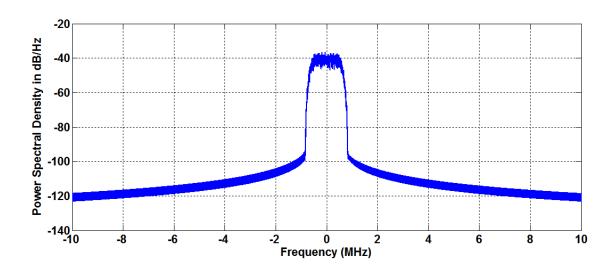

|   | Figure 2:   | Spectrum of complex baseband signal comprised of random QPSK chips             |

|   | 1 iguic 2.  | filtered with a raised cosign filter. The signal chip rate and bandwidth are   |

|   |             | 1.25 MHz and the sampling rate is 80 MHz                                       |

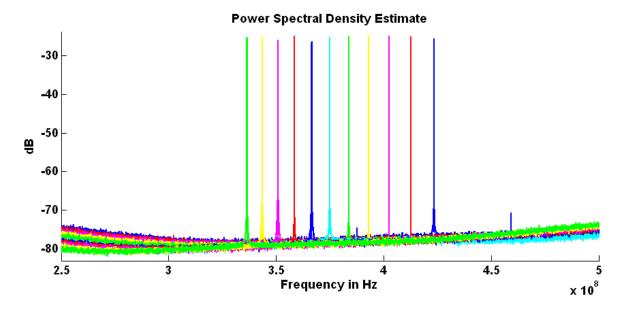

|   | Figure 3:   | Simulated spectra of the signal immediately before delta-sigma modulation.     |

|   | rigule 3.   | Sampling is at 3.2 GHz and scaled to correspond to a 33 dBm transmit           |

|   |             | 1 0                                                                            |

|   |             | power. The noise floor is due to the side lobes of the Hamming window          |

|   | E: 4.       | used 61                                                                        |

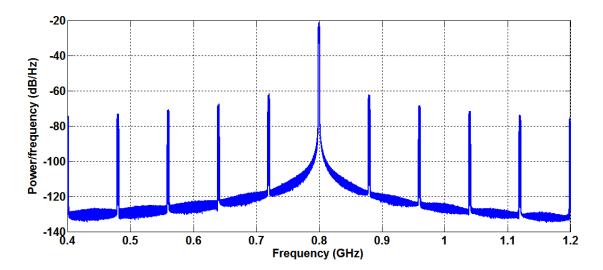

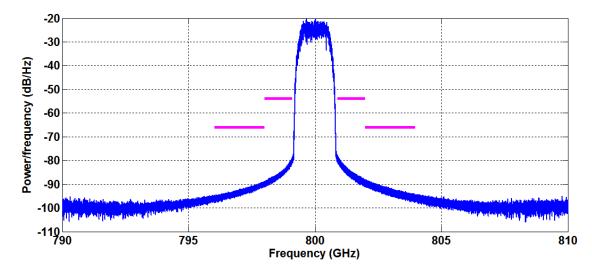

|   | Figure 4:   | Simulated wide-band spectrum of delta-sigma modulated signal at a              |

|   | г. с        | sampling rate of 3.2 GHz                                                       |

|   | Figure 5:   | Zoomed view of the output spectrum in fig. 4, with lines drawn at the          |

|   | г. с        | approximate ACPR limits shown                                                  |

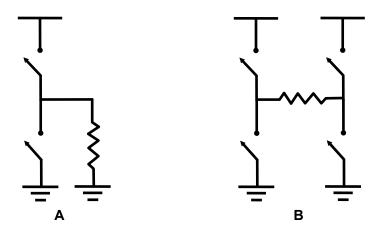

|   | Figure 6:   | Class-D switching amplifiers: A) Single-ended B) Differential (H-              |

|   | D: <b>5</b> | Bridge)64                                                                      |

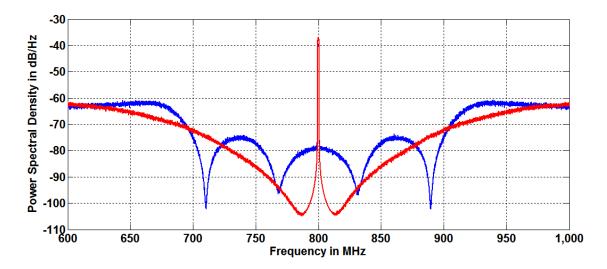

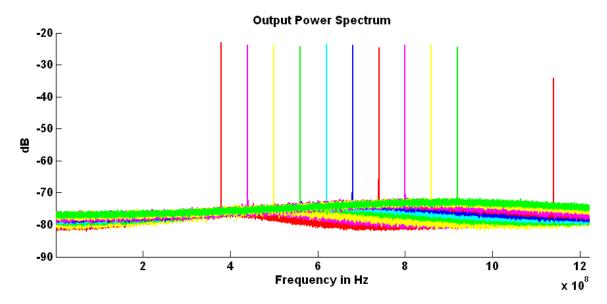

|   | Figure 7:   | Simulated output spectra of an eighth order band-pass delta-sigma with         |

|   |             | staggered NTF zeros (blue) compared to a simple fourth order modulator         |

|   |             | (red). Both modulators are running at a 3.2 GHz sampling rate, using 16-bit    |

|   |             | digital integrators                                                            |

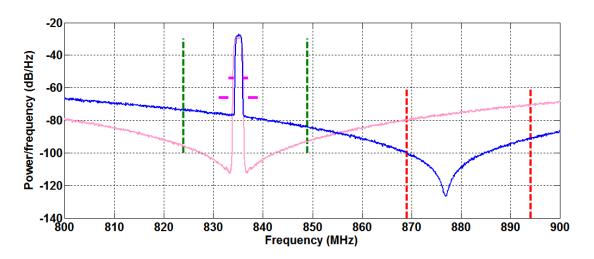

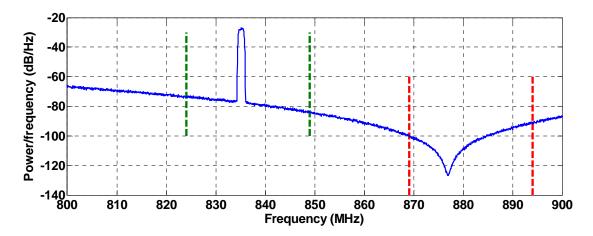

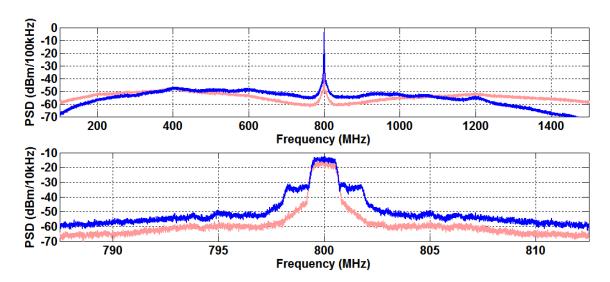

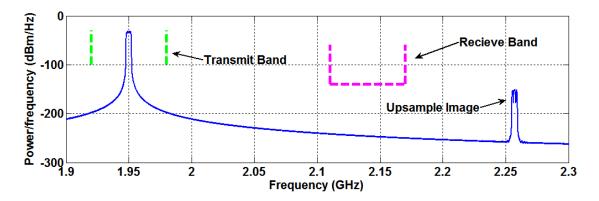

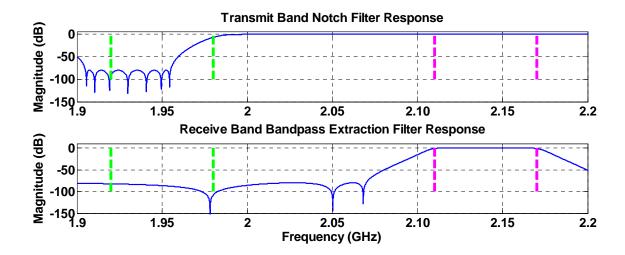

|   | Figure 8:   | Simulated spectrum of a delta-sigma system with a frequency plan               |

|   |             | optimized for receive channel noise supression (dark blue). The power level    |

|   |             | is scaled for a 33 dBm transmitter                                             |

|   | Figure 9:   | Delta-sigma modulator block diagram69                                          |

|   | Figure 10:  | Simulated signal-to-noise ratio (SNR) (solid blue with circles, top) and Error |

|   |             | Vector Magnitude (EVM) (solid green with circles, bottom) versus delta-        |

|   |             | sigma modulator word length                                                    |

|   | Figure 11:  | Simulated output of a delta-sigma modulator with no dither (green), and full   |

|   |             | scale dither (red) added in the NTF loop74                                     |

|   | Figure 12:  | Simulated output spectra for a delta-sigma modulator with wrap overflow        |

|   |             | (red)76                                                                        |

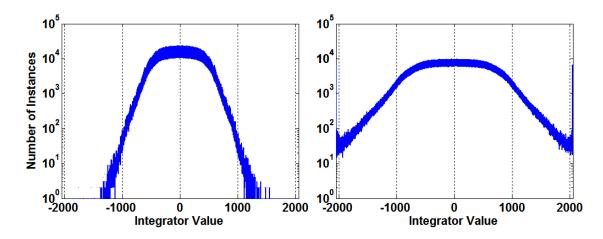

|   | Figure 13:  | Histograms of simulated final stage integrator values with wrap overflow       |

|   | -           | (left) and saturate overflow (right)77                                         |

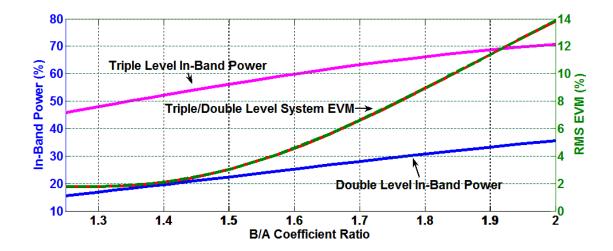

|   | Figure 14:  | Simulated EVM and in-band power ratio for two and three level based delta-     |

|   | -           | sigma systems                                                                  |

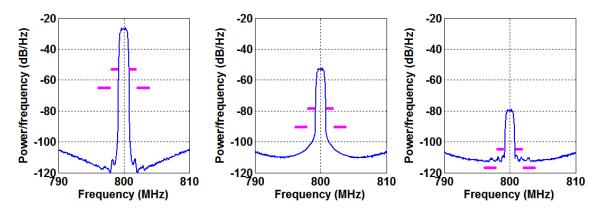

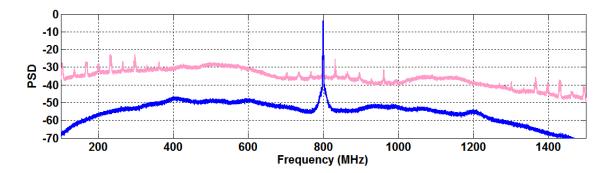

|   | Figure 15: | Output spectra CDMA waveform power scaled solely using delta-sigma             | 20                |

|---|------------|--------------------------------------------------------------------------------|-------------------|

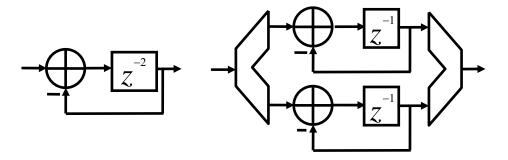

|   | Figure 16: | Band-pass double-delay resonator (left) to parallel single-delay resonator     | 50                |

|   | rigule 10. | (right) transformation                                                         | 27                |

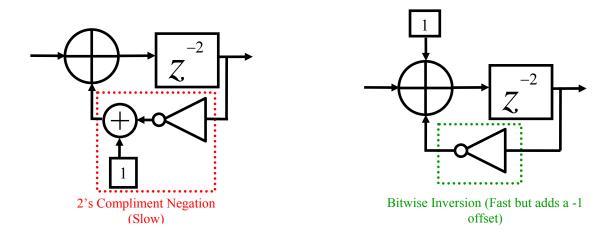

|   | Figure 17: | Two's complement negation optimization (right) shown compared with             | <i>5</i> <u>∠</u> |

|   | riguic 17. | standard negation (left)                                                       | 33                |

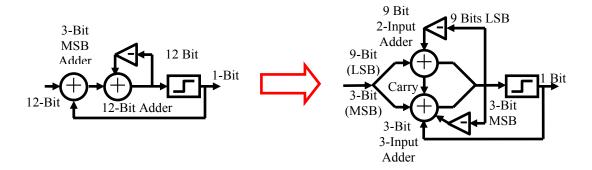

|   | Figure 18: | Block diagram for one possible method to transform a 12-bit two-input          |                   |

|   | Č          | adder cascade to a single triple-input adder                                   | 34                |

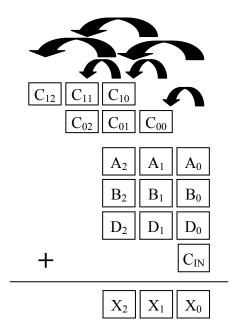

|   | Figure 19: | Graphical depiction of equations for a 3-bit 2-input binary Adder. The top     |                   |

|   |            | arrows trace the origins of the carry signals                                  |                   |

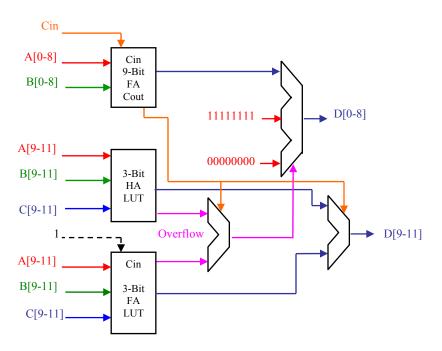

|   | Figure 20: | 12-bit 3-input adder implementation block diagram                              | 37                |

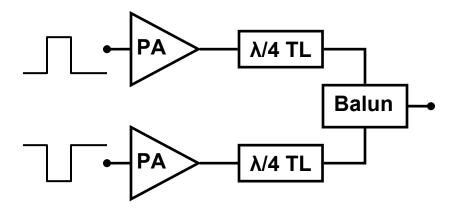

|   |            | Block diagram of H-bridge amplifier                                            |                   |

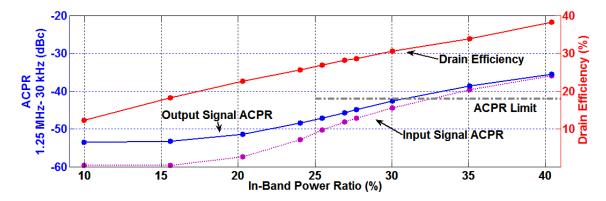

|   | Figure 22: | Drain efficiency and ACPR for the H-bridge with distributed match, at a 2      |                   |

|   |            | supply, driven with a 2-level CDMA delta-sigma signal                          |                   |

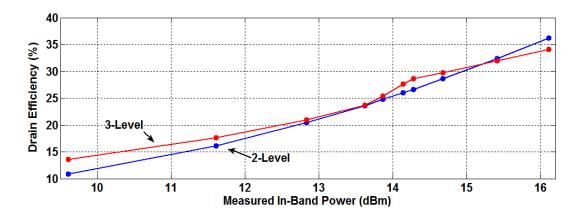

|   | Figure 23: | Drain efficiency comparison between H-bridge amplifier driven with 2-lev       |                   |

|   |            | signal and 3-level signal.                                                     |                   |

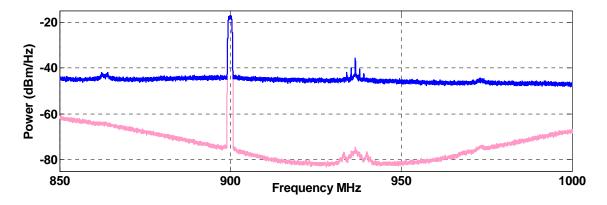

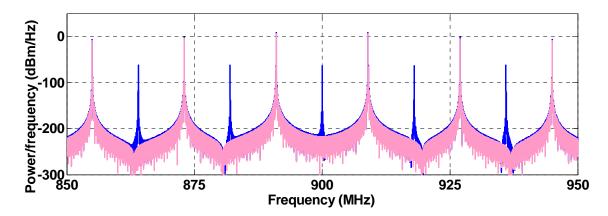

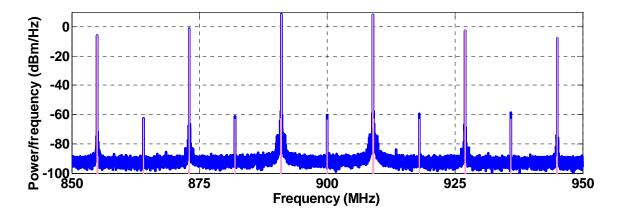

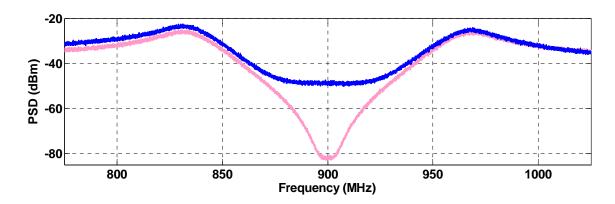

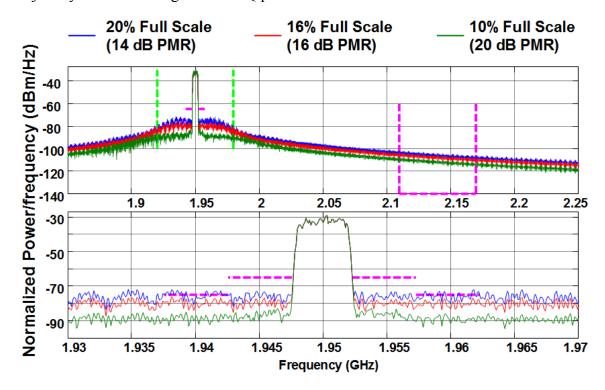

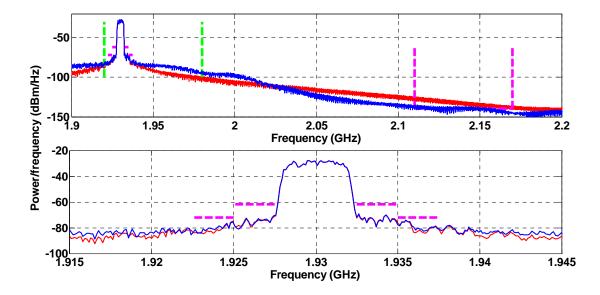

|   |            | Spectral performance of the CMOS VMCD amplifier                                | )1                |

| ( | Chapter 5  |                                                                                |                   |

|   | Figure 1:  | Full duplex communication system block diagram showing TX to RX self-          |                   |

|   |            | jamming.                                                                       |                   |

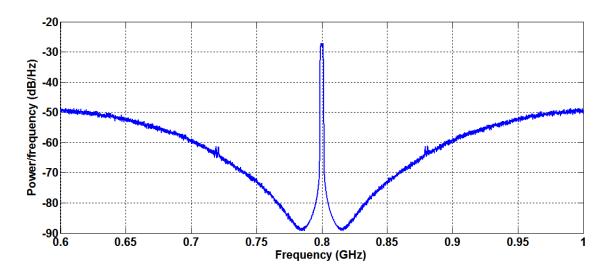

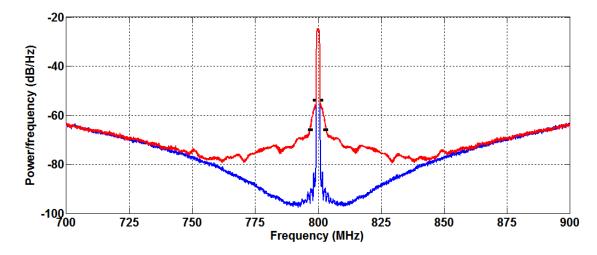

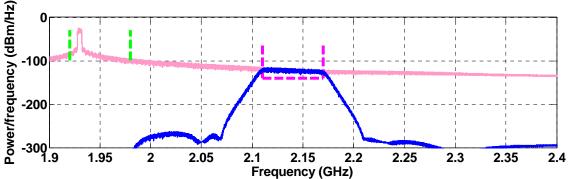

|   | Figure 2:  | Simulated delta-sigma encoded CDMA spectrum with NTF zeros optimize            |                   |

|   |            | for RX band noise performance (from chapter 4, Figure 8)                       | <b>)</b> 7        |

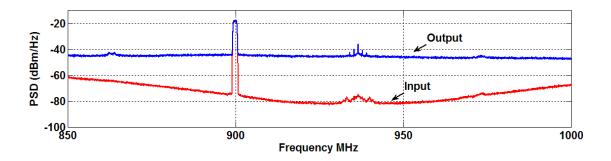

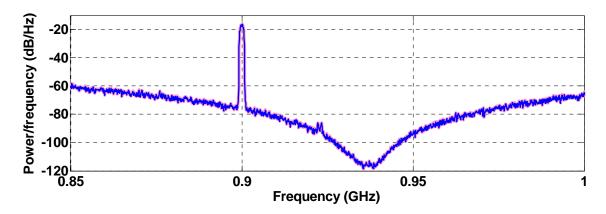

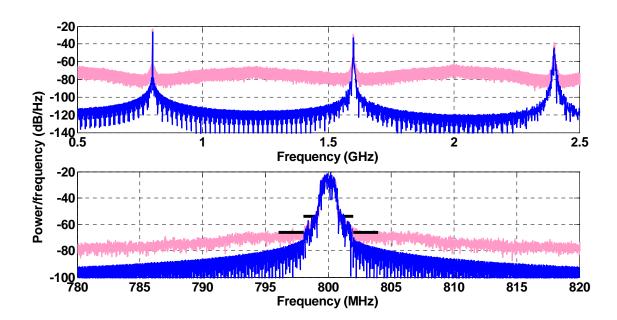

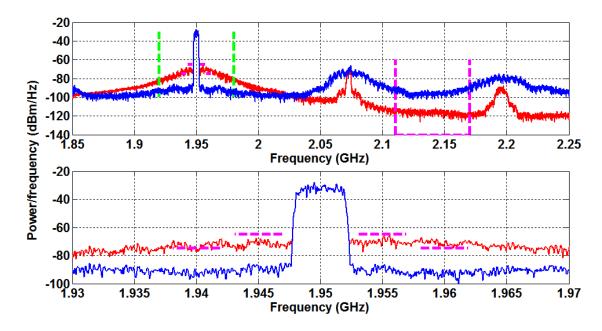

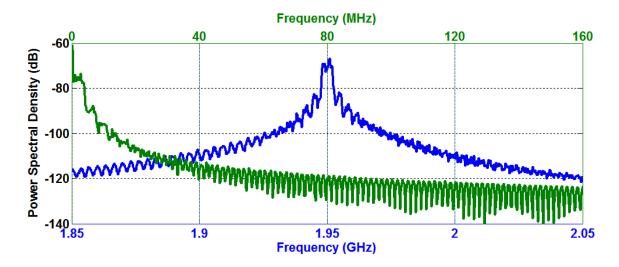

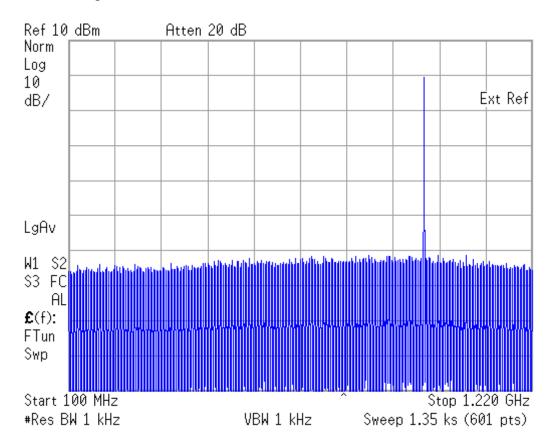

|   | Figure 3:  | Measured output from the delta-sigma signal generation system (Agilent 81134A) | 2/1               |

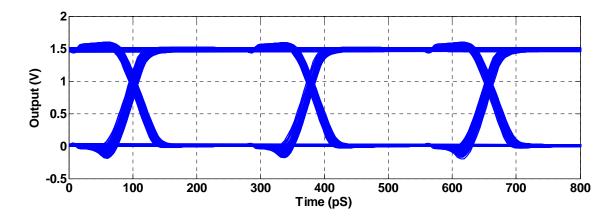

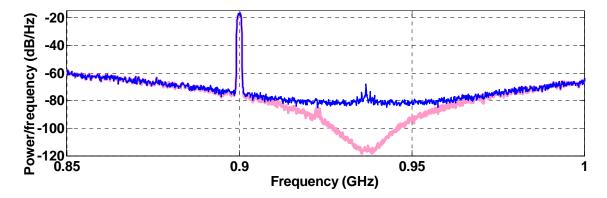

|   | Figure 4:  | Measured input (light red) and output (blue) of the VMCD amplifier driver      |                   |

|   | 1 15410 1. | with a delta-sigma signal                                                      |                   |

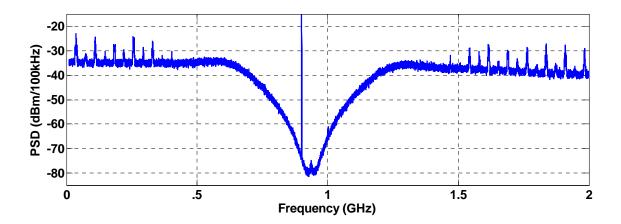

|   | Figure 5:  | Measured broadband spectra of VMCD amplier output.                             |                   |

|   | Figure 6:  | Simulated output transient response of the VMCD amplifier, over-plotted t      |                   |

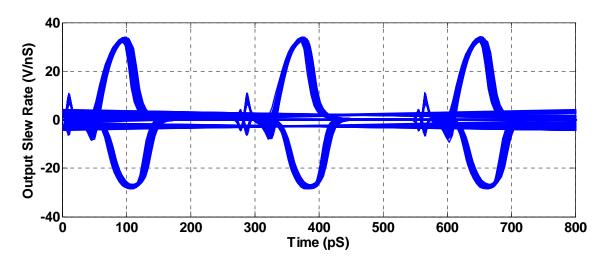

|   | U          | form an eye diagram10                                                          |                   |

|   | Figure 7:  | Slew rate eye diagram constructed by over plotting the derivatives of the      |                   |

|   |            | voltage transitions                                                            | )2                |

|   | Figure 8:  | Example of severe symmetrical slew applied to test delta-sigma signal10        | )3                |

|   | Figure 9:  | Simulated delta-sigma with symmetrical slew applied (blue) is compared         |                   |

|   |            | with an ideal, no slew signal (light red) (40 GHz sampling rate, 10 V/nS       |                   |

|   |            | rise/fall, simulated for 1 mS)                                                 | )3                |

|   | Figure 10: | Simulated delta-sigma signal with the asymmetrical slew applied (blue)         |                   |

|   |            | compared with the measured amplifier results (light red). The asymmetrical     |                   |

|   |            | slew applied is 33 V/nS rise and 27 V/nS fall time                             | )4                |

|   | Figure 11: | Simulated spectra of phase reversal signal (dark blue) with a 24V/nS rise      |                   |

|   |            | time and 28 V/nS fall time. Shown with spectrum of ideal phase reversal        |                   |

|   |            | signal with no slew impairment (light red)                                     | )5                |

|   | Figure 12: | Measured phase reversal signal output (dark blue) shown with spectrum of       |                   |

|   |            | slew simulation (light red). Spectrum of the measured output is shown in       |                   |

|   |            | thicker pen to facilitate comparison10                                         | )6                |

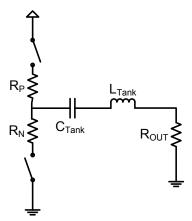

| Figure 13: | Simplified VMCD amplifier schematic diagram emphasizing mismatche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|            | on-resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

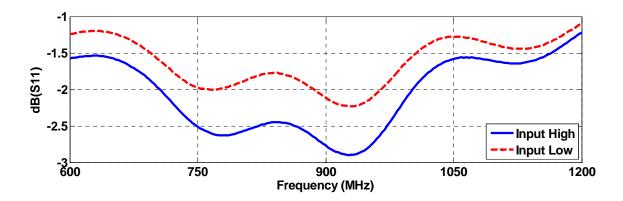

| _          | S-parameter measurements looking into the output of the amplifer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| Figure 15: | Simulation of VMCD amplifier with a mismatched on resistance amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|            | delta-sigma encoded CDMA signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Figure 16: | Simulation of VMCD amplifier with a mismatched on resistance amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|            | delta-sigma quantiaztion-noise-only signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .109 |

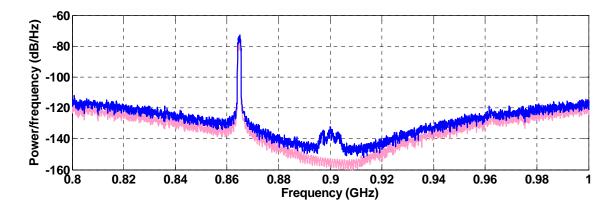

| Figure 17: | Measured amplifier input (light red) and output (dark blue) with a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|            | quantization noise only signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

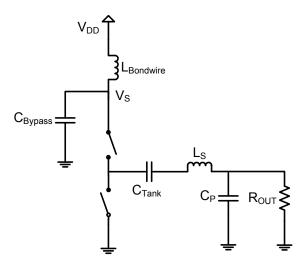

| _          | Simplified VMCD amplifier schematic with bondwire inductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

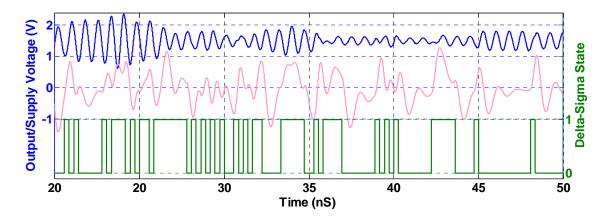

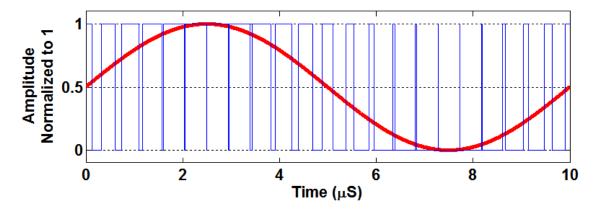

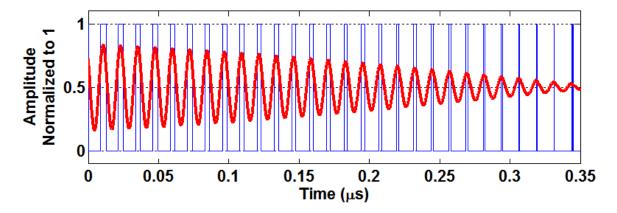

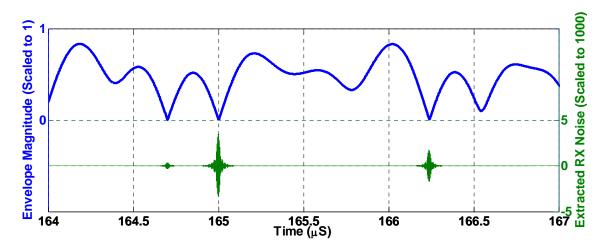

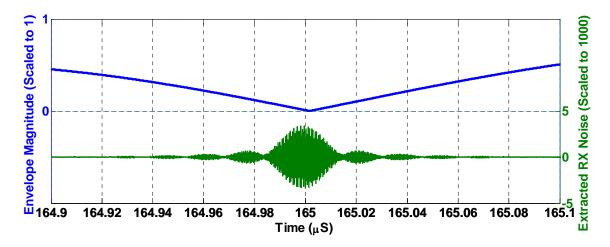

| Figure 19: | Time domain simulation of circuit in Figure 18. Bottom is delta-sigma d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| E: 20      | signal (green), middle is the output voltage (light red) and top is V <sub>S</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

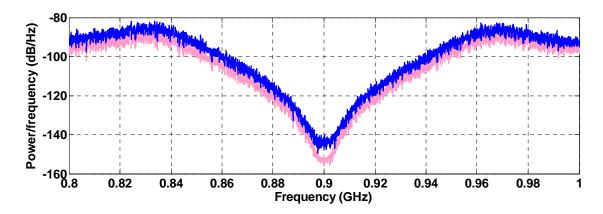

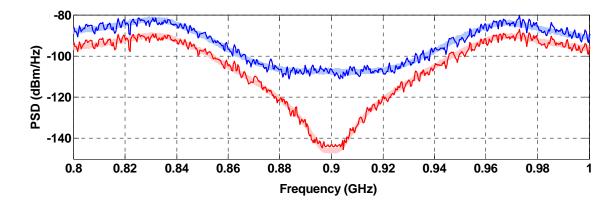

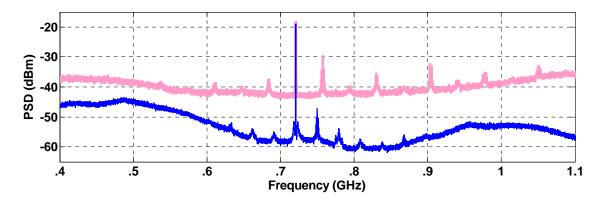

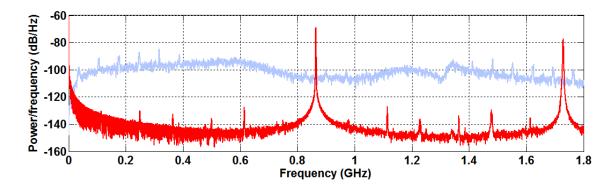

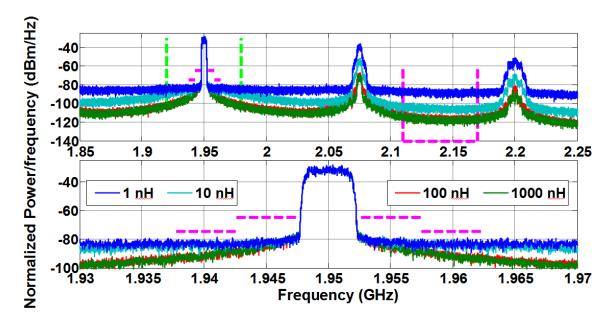

| Figure 20: | Spectra of both simulation (dark lines) and measurement (light lines) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| F: 21      | quantization-noise-only signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

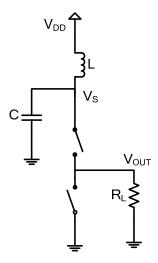

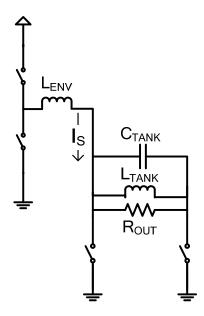

|            | VMCD circuit used in hand analysis of supply memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

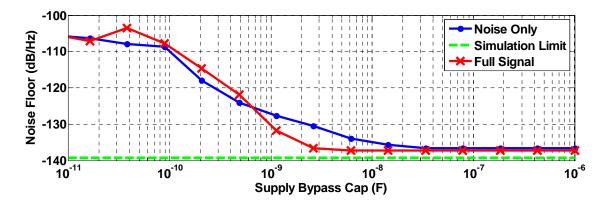

| Figure 22: | Simulation of noise floor vs bypass capacitor size. Shown with simulating simulating of the definition |      |

| Eigyma 22. | mimumum (dotted line)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .115 |

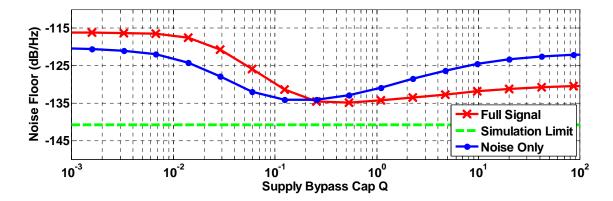

| Figure 23: | Simulation of a VMCD with 1.2 nF bypass capacitor with a supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 116  |

| Eigyma 24. | inductance is set at .5 nH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .110 |

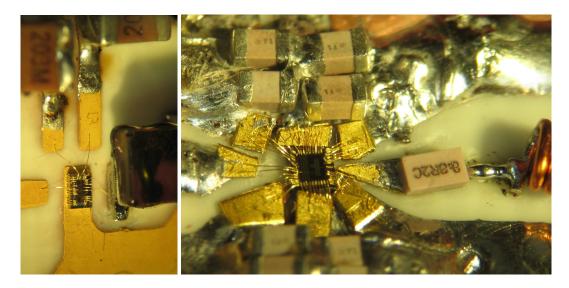

| Figure 24: | Microphotographs of old (left) and new (right) amplifier and respective chip-on-board components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 117  |

| Figure 25: | Measured output spectra of the new VMCD amplifier design (bottom dar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |