#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Learning Optimizations for Hardware Accelerated Designs

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

by

Pingfan Meng

#### Committee in charge:

Professor Ryan Kastner, Chair Professor Scott Baden Professor Andrew McCulloch Professor Steven Swanson Professor Michael Taylor

Copyright

Pingfan Meng, 2016

All rights reserved.

| The Dissertation of Pingfan Meng is approved and is acceptable in quality |

|---------------------------------------------------------------------------|

| and form for publication on microfilm and electronically:                 |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

| Chair                                                                     |

University of California, San Diego 2016

## DEDICATION

To Audrey, Fangang and Jianping.

### **EPIGRAPH**

Any sufficiently advanced technology is indistinguishable from magic.

Arthur C. Clarke

### TABLE OF CONTENTS

| Signature Page                                                           |                                                        | iii                        |

|--------------------------------------------------------------------------|--------------------------------------------------------|----------------------------|

| Dedication                                                               |                                                        | iv                         |

| Epigraph                                                                 |                                                        | v                          |

| Table of Contents                                                        |                                                        | vi                         |

| List of Figures                                                          |                                                        | ix                         |

| List of Tables                                                           |                                                        | xi                         |

| List of Algorithms                                                       |                                                        | xii                        |

| List of Listings                                                         |                                                        | xiii                       |

| Acknowledgements                                                         |                                                        | xiv                        |

| Vita                                                                     |                                                        | xvi                        |

| Abstract of the Dissertati                                               | ion                                                    | xviii                      |

| 1.1 Overview 1.1.1 Optimiz 1.1.2 Hardwa 1.1.3 Automa 1.2 Contributions . | zation of Hardware Accelerated Designs                 | 1<br>1<br>3<br>5<br>8<br>9 |

| Part I Manual Desig                                                      | gn Approaches                                          | 10                         |

| Chapter 2 Hardware A ment                                                | acceleration Approaches for Optical Labeled DNA Align- | 11                         |

| 2.1 Background an                                                        | d Motivation                                           | 11                         |

| 2.2 Related Work.                                                        |                                                        | 14                         |

| 2.3 Alignment Algo                                                       | orithm                                                 | 15                         |

|                                                                          | signs                                                  | 23                         |

| 2.4.1 Multi-c                                                            | ore CPU                                                | 24                         |

| 2.4.2 GPU                                                                |                                                        | 25                         |

| 2.4.3 FPGA.                                                              |                                                        | 29                         |

| 2.5 Results                                                              |                                                        | 38                         |

| 2.6 Hardware Com                                                         | parison                                                | 42                         |

|         | 2.6.1 Performance                                                         |

|---------|---------------------------------------------------------------------------|

|         | 2.6.2 Hardware Prices                                                     |

| 2.7     | Summary                                                                   |

| Chapter | FPGA-GPU-CPU Heterogeneous Architecture for Real-time Cardiac             |

| 1       | Physiological Optical Mapping                                             |

| 3.1     | Background and Motivation                                                 |

| 3.2     | Related Work                                                              |

| 3.3     | Optical Mapping Algorithm                                                 |

| 5.5     | 3.3.1 Normalization                                                       |

|         | 3.3.2 Phase Correction Spatial Filter                                     |

|         | 3.3.3 Phase Correction Algorithm                                          |

|         | 3.3.4 Temporal Median Filter                                              |

| 3.4     | Application Partitioning                                                  |

| 3.5     | Design and Implementation                                                 |

| 3.3     |                                                                           |

|         |                                                                           |

|         |                                                                           |

| 26      | $\boldsymbol{\varepsilon}$                                                |

| 3.6     | Results and Analysis                                                      |

|         | 1                                                                         |

|         | 3.6.2 Performance                                                         |

| 2.7     | 3.6.3 Accuracy                                                            |

| 3.7     | Summary                                                                   |

| Part II | Automatic Approaches with Machine Learning                                |

| Chapter | Re-thinking Machine Learning for OpenCL Design Space Exploration on FPGAs |

| 4.1     | Background and Motivation                                                 |

| 4.2     | Related Work                                                              |

| 4.3     | Problem Formulation                                                       |

| 4.4     | Re-thinking Machine Learning for System Level FPGA DSE                    |

| 4.4     | 4.4.1 Pitfall: attempting to learn more accurately                        |

|         |                                                                           |

| 4.5     | 8                                                                         |

| 4.5     | ATNE Algorithm                                                            |

| 4.0     |                                                                           |

|         | 4.6.1 Experimental Setup                                                  |

| 4 7     | 4.6.2 Prediction Quality                                                  |

| 4.7     | Summary                                                                   |

| Chapter |                                                                           |

|         | Exploration?                                                              |

| 5.1     | Background and Motivation                                                 |

| 5.2      | Related Work                                                          | 87  |

|----------|-----------------------------------------------------------------------|-----|

| 5.3      | Overview                                                              | 88  |

| 5.4      | Can One Use Estimation Data for FPGA Design Space Exploration?        | 90  |

|          | 5.4.1 Experimental Setup                                              | 90  |

|          | 5.4.2 Can one directly use the Pareto points from the estimated data? | 91  |

|          | 5.4.3 Can one mine the estimation data for FPGA DSE?                  | 94  |

| 5.5      | Algorithms                                                            | 99  |

| 5.6      | Analysis: Determine $N_{th}$                                          | 103 |

| 5.7      | Evaluation Results                                                    | 104 |

| 5.8      | Summary                                                               | 108 |

| Chapter  | 6 Conclusion                                                          | 109 |

| Chapter  | 7 Future Directions                                                   | 111 |

| Bibliogr | raphy                                                                 | 113 |

### LIST OF FIGURES

| Figure 2.1.  | Demonstration of the optical labeling process                                                                                                          | 12 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2.  | Comparison of the conventional and the novel <i>de novo</i> assembly methods                                                                           | 13 |

| Figure 2.3.  | Array alignment                                                                                                                                        | 16 |

| Figure 2.4.  | Overall algorithm and its hardware partitioning                                                                                                        | 17 |

| Figure 2.5.  | Visualized pair-wise alignment process                                                                                                                 | 18 |

| Figure 2.6.  | Possible parallelism in the algorithm                                                                                                                  | 23 |

| Figure 2.7.  | Multi-core CPU accelerated design.                                                                                                                     | 26 |

| Figure 2.8.  | Visualized GPU kernel for dynamic programming                                                                                                          | 28 |

| Figure 2.9.  | FPGA implementation of the three levels of parallelism                                                                                                 | 33 |

| Figure 2.10. | FPGA design space exploration using HLS                                                                                                                | 34 |

| Figure 2.11. | FPGA boundary score module                                                                                                                             | 35 |

| Figure 2.12. | FPGA dynamic programming module with three levels of concurrency                                                                                       | 37 |

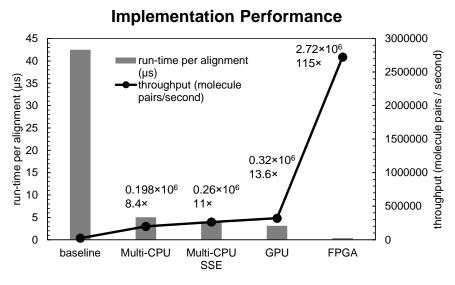

| Figure 2.13. | Performance of the accelerated designs                                                                                                                 | 38 |

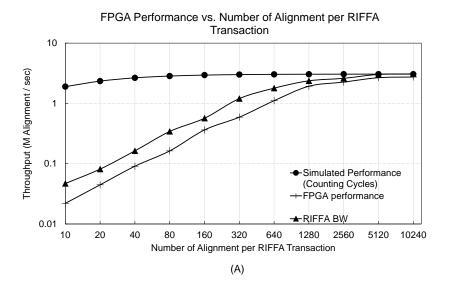

| Figure 2.14. | Performance vs. number of alignments per host - accelerator device transaction                                                                         | 40 |

| Figure 3.1.  | Image conditioning effect                                                                                                                              | 48 |

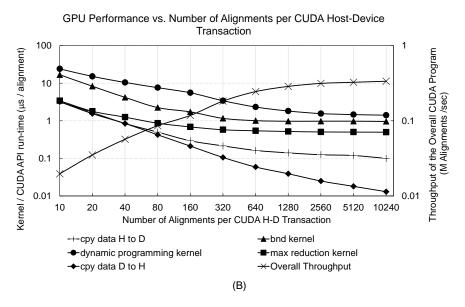

| Figure 3.2.  | Optical mapping algorithm                                                                                                                              | 52 |

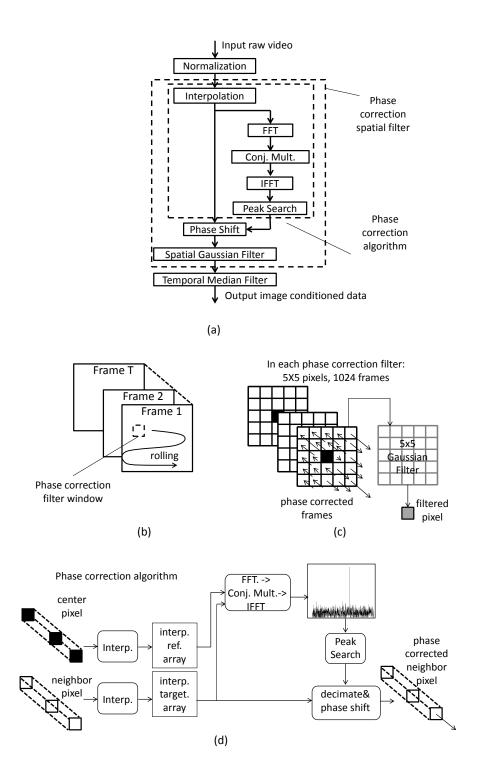

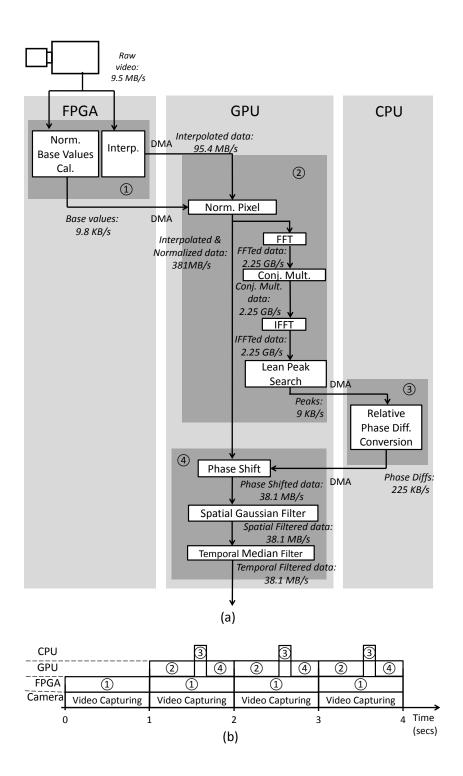

| Figure 3.3.  | FPGA-GPU heterogenous architecture                                                                                                                     | 59 |

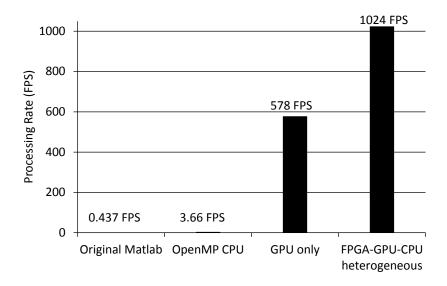

| Figure 3.4.  | The performance of the FPGA-GPU-CPU heterogenous implementation in comparison to the original Matlab, the OpenMP C++, and the GPU only implementation. | 61 |

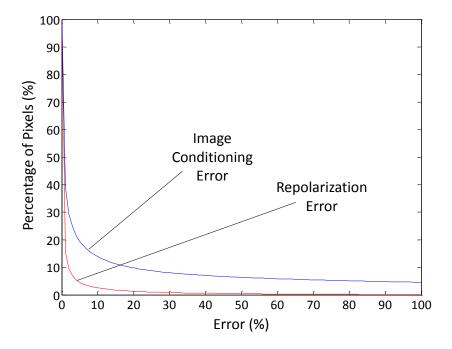

| Figure 3.5.  | Error of the output of the optical mapping image conditioning and error in repolarization analysis                                                     | 62 |

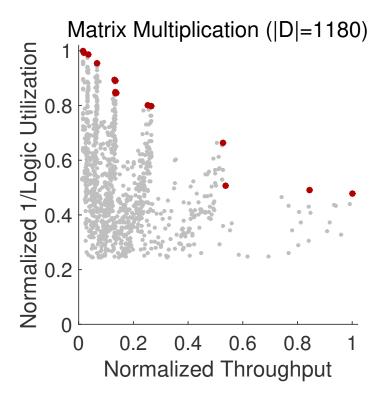

| Figure 4.1. | The visualization of the design space of the matrix multiplication application in the objective space using the OpenCL-to-FPGA tool | 69  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

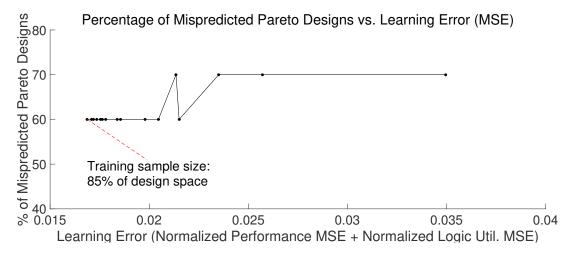

| Figure 4.2. | Demonstration of the pitfall of improving learning accuracy                                                                         | 72  |

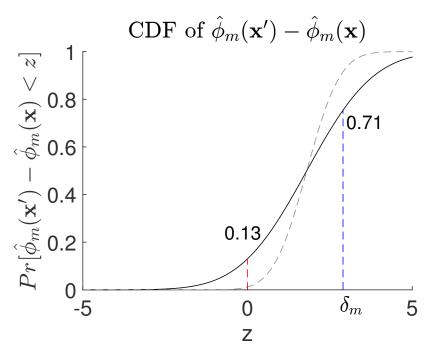

| Figure 4.3. | CDF of $\hat{\phi}_m(\mathbf{x}') - \hat{\phi}_m(\mathbf{x})$                                                                       | 74  |

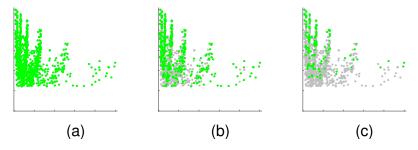

| Figure 4.4. | Transition of eliminating the predicted non-Pareto designs                                                                          | 78  |

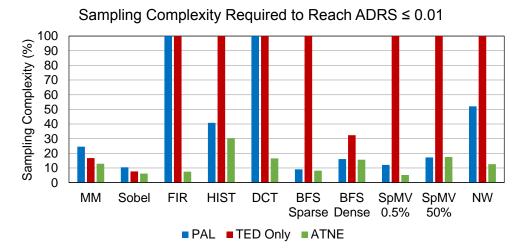

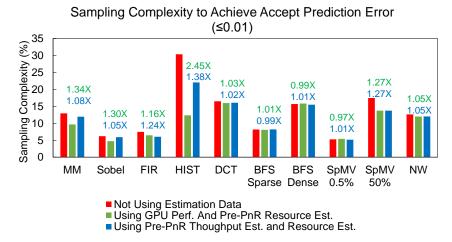

| Figure 4.5. | Sampling complexity to achieve ADRS $\leq 0.01$                                                                                     | 81  |

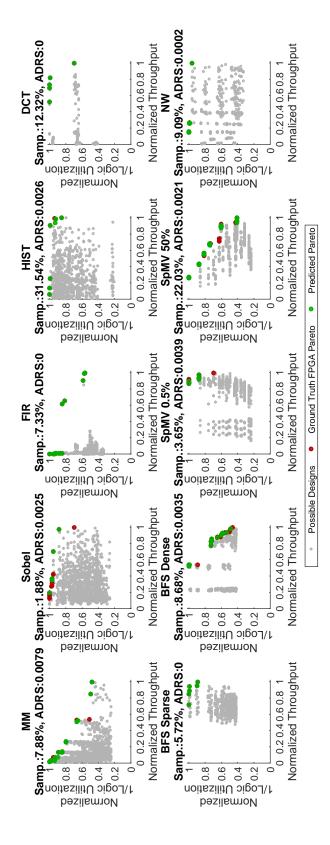

| Figure 4.6. | Demonstration of predicted Pareto Points                                                                                            | 82  |

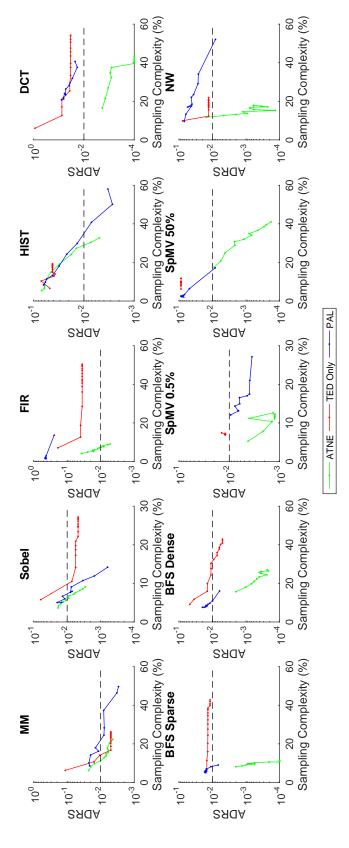

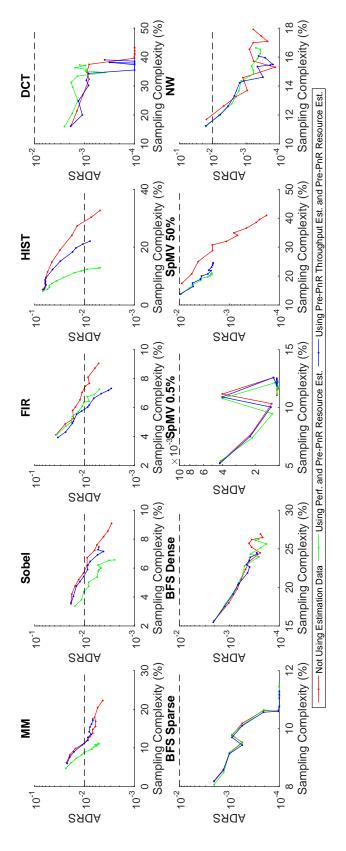

| Figure 4.7. | The comparison between prediction qualities (ADRS) of ATNE and the other state of the art approaches PAL, TED only                  | 83  |

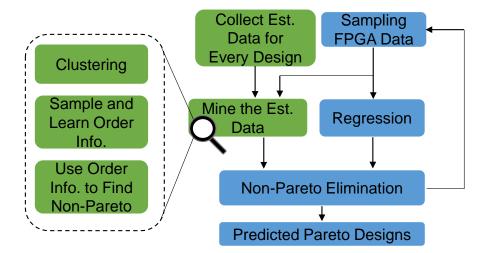

| Figure 5.1. | Flow diagram of the FPGA DSE process using estimation data                                                                          | 90  |

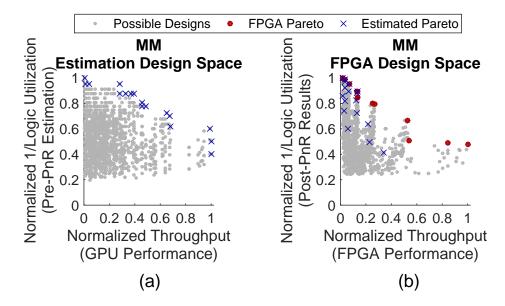

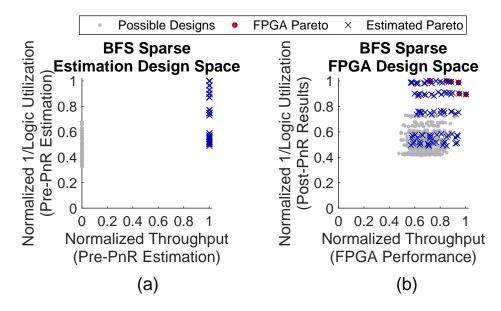

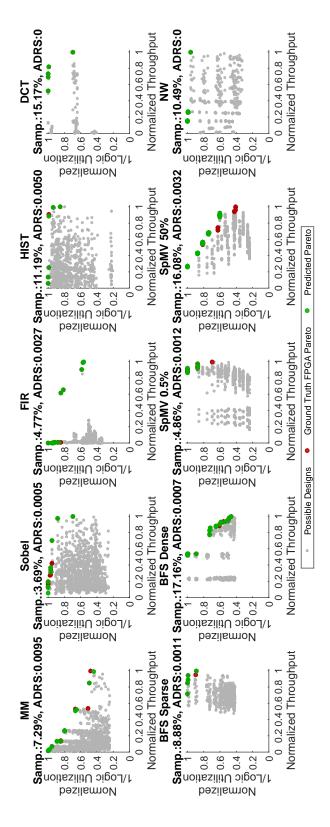

| Figure 5.2. | Example of directly using estimation data to find the Pareto frontier                                                               | 92  |

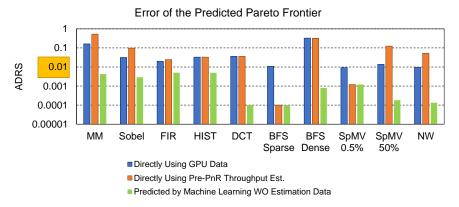

| Figure 5.3. | Prediction errors (ADRS) of 3 different approaches                                                                                  | 92  |

| Figure 5.4. | An example of extremely inaccurate estimation space                                                                                 | 94  |

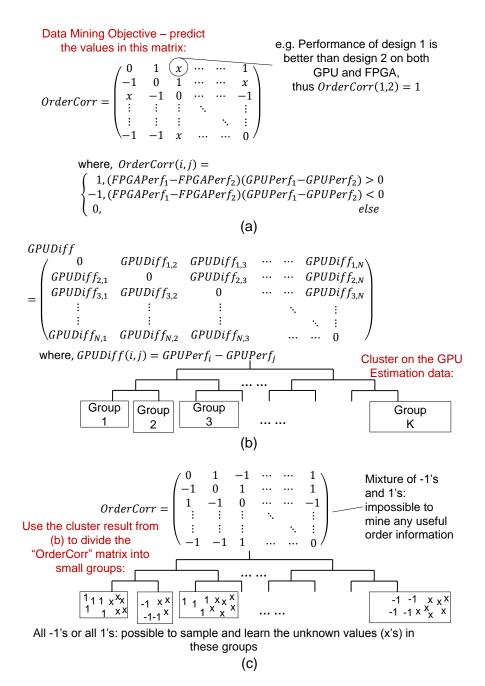

| Figure 5.5. | Our data mining approach                                                                                                            | 97  |

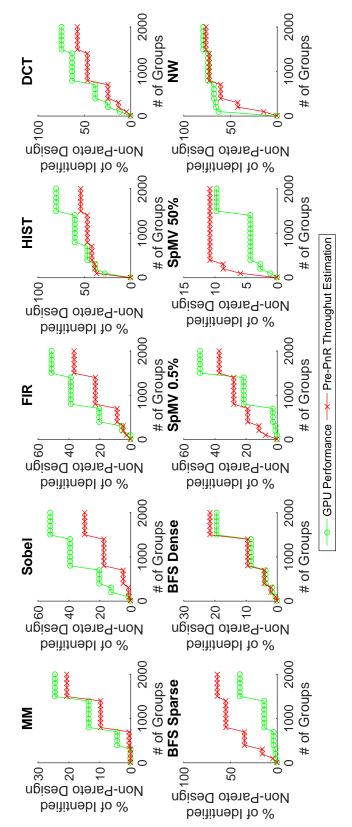

| Figure 5.6. | The effectiveness of the data mining method                                                                                         | 98  |

| Figure 5.7. | Sampling Complexities to Achieve Accept Prediction Error (ARDS leq0.01)                                                             | 105 |

| Figure 5.8. | Visualization of the run results of our approach using GPU performance data as estimation                                           | 106 |

| Figure 5.9. | The evaluation results of using the GPU performance, pre-PnR throughput estimation and the baseline machine learning method .       | 107 |

### LIST OF TABLES

| Table 2.1. | Constant values for score functions                                             | 22 |

|------------|---------------------------------------------------------------------------------|----|

| Table 2.2. | FPGA design resource utilization on VC707                                       | 41 |

| Table 2.3. | Hardware Comparison                                                             | 42 |

| Table 3.1. | Optical mapping algorithm partition decisions                                   | 55 |

| Table 4.1. | Tunable Knobs in the OpenCL Code and Their Impacts on the Hardware Architecture | 70 |

| Table 4.2. | Details of OpenCL Benchmarks                                                    | 79 |

### LIST OF ALGORITHMS

| Algorithm 2.1 | The Boundary Score Algorithm            | 21  |

|---------------|-----------------------------------------|-----|

| Algorithm 2.2 | The Dynamic Programming Score Algorithm | 22  |

| Algorithm 4.1 | The ATNE Algorithm                      | 76  |

| Algorithm 5.1 | Estimation Data Mining Algorithm        | 101 |

| Algorithm 5.2 | Recursive Clustering                    | 102 |

### LIST OF LISTINGS

| Listing 2.1. | Pseudo Code for Dynamic Programming GPU Kernel                         | 27 |

|--------------|------------------------------------------------------------------------|----|

| Listing 2.2. | Pseudo Code for local score element computation function in HLS C code | 31 |

#### **ACKNOWLEDGEMENTS**

I would like to acknowledge Professor Ryan Kastner for his guidance and support as my advisor. Due to his encouragement and support, I had the opportunity to be recognized by the international level research community at several venues. This Ph.D. program under his supervision was a very enjoyable process of exploring the unknown in the computer science world.

I would also like to acknowledge my committee members. Professor Scott Baden attended multiple talks of mine and provided some valuable input to the primary part of my research. Professor Steven Swanson and Professor Michael Taylor directed me to several useful materials during my thesis proposal, which eventually provided me major inspirations of this work. Professor Andrew McCulloch's theory provides the foundation of my very first research project and publication. I would like to thank him for this great project idea which initiated my Ph.D. research.

None of this would have been possible without many collaborators. I would like to acknowledge Dr. Matthew Jacobsen. He provided me not only technical help but also insights in my research. I would also like to acknowledge Dr. Motoki Kimura, Alric Althoff, and Quentin Gautier for their extraordinary work and help in my research projects.

The majority of the work herein appears in both academic journals and conferences. Chapter 2 contains material printed in "Hardware Accelerated Alignment Algorithm for Optical Labeled Genomes", Pingfan Meng, Matthew Jacobsen, Motoki Kimura, Vladimir Dergachev, Thomas Anantharaman, Michael Requa, and Ryan Kastner, the ACM Transactions on Reconfigurable Technology and Systems 2016 and in "Hardware Accelerated Novel Optical De Novo Assembly for Large-Scale Genomes", Pingfan Meng, Matthew Jacobsen, Motoki Kimura, Vladimir Dergachev, Thomas Anantharaman, Michael Requa, and Ryan Kastner, International Conference on Field-Programmable

Technology (FPT), December 2014. The dissertation author was the primary investigator and author of these papers.

Chapter 3 contains material printed in "FPGA-GPU-CPU Heterogeneous Architecture for Realtime Cardiac Physiological Optical Mapping", Pingfan Meng, Matthew Jacobsen, and Ryan Kastner, the International Conference on Field-Programmable Technology (FPT) 2012. The dissertation author was the primary investigator and author of this paper.

Chapter 4 contains material printed in "Adaptive Threshold Non-Pareto Elimination: Re-thinking Machine Learning for System Level Design Space Exploration on FPGAs", Pingfan Meng, Alric Althoff, Quentin Gautier, and Ryan Kastner, the Conference on Design Automation and Test in Europe (DATE) 2016. The chapter also contains material that was an improvement of the results in the conference paper. The dissertation author was the primary investigator and author of this paper.

Chapter 5 contains material printed in the submission of "Can One Use GPU Performance Data for FPGA Design Space Exploration?", Pingfan Meng, Alric Althoff, Quentin Gautier, and Ryan Kastner, to International Conference On Computer Aided Design (ICCAD), 2016. The dissertation author was the primary investigator and author of this paper.

#### VITA

| 2009 | Bachelor of Science, Shanghai Jiaotong University         |

|------|-----------------------------------------------------------|

| 2011 | Master of Science, University of California, San Diego    |

| 2016 | Doctor of Philosophy, University of California, San Diego |

#### **PUBLICATIONS**

"Can One Use GPU Performance Data for FPGA Design Space Exploration?", Pingfan Meng, Alric Althoff, Quentin Gautier, and Ryan Kastner, International Conference On Computer Aided Design (ICCAD), 2016 (under review)

"Adaptive Threshold Non-Pareto Elimination: Re-thinking Machine Learning for System Level Design Space Exploration on FPGAs", Pingfan Meng, Alric Althoff, Quentin Gautier, and Ryan Kastner, Design Automation and Test in Europe (DATE), March 2016

"Hardware Accelerated Alignment Algorithm for Optical Labeled Genomes", Pingfan Meng, Matthew Jacobsen, Motoki Kimura, Vladimir Dergachev, Thomas Anantharaman, Michael Requa, and Ryan Kastner, ACM Transactions on Reconfigurable Technology and Systems (TRETS), in press

"Real-time 3D Reconstruction for FPGAs: A Case Study for Evaluating the Performance, Area, and Programmability Trade-offs of the Altera OpenCL", Quentin Gautier, Alexandria Shearer, Janarbek Matai, Dustin Richmond, Pingfan Meng, and Ryan Kastner, International Conference on Field-Programmable Technology (FPT), December 2014

"Hardware Accelerated Novel Optical De Novo Assembly for Large-Scale Genomes", Pingfan Meng, Matthew Jacobsen, Motoki Kimura, Vladimir Dergachev, Thomas Anantharaman, Michael Requa, and Ryan Kastner, International Conference on Field Programmable Logic and Applications (FPL), September 2014

"FPGA Accelerated Online Boosting for Multi-Target Tracking", Matthew Jacobsen, Pingfan Meng, Siddarth Sampangi, Ryan Kastner, IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM), May 2014

"GPU Accelerated Post-Processing for Multifrequency Biplanar Interferometric Imaging", Pingfan Meng, George R. Cutter Jr., Ryan Kastner, David A. Demer, Oceans, September 2013

- "A Hardware Accelerated Approach for Imaging Flow Cytometry", Dajung Lee, Pingfan Meng, Matthew Jacobsen, Henry Tse, Dino Di Carlo and Ryan Kastner, International Conference on Field Programmable Logic and Applications (FPL), September 2013

- "FPGA-GPU-CPU Heterogeneous Architecture for Realtime Cardiac Physiological Optical Mapping", Pingfan Meng, Matthew Jacobsen, and Ryan Kastner, International Conference on Field-Programmable Technology (FPT), December 2012

- "A Hardware in the Loop Wireless Channel Emulator for Software Defined Radio", Janarbek Matai, Pingfan Meng, Linjuan Wu, Ryan Kastner, International Conference on Field-Programmable Technology (FPT), December 2012

- "GPU Acceleration of Optical Mapping Algorithm for Cardiac Electrophysiology", Pingfan Meng, Ali Irturk, Ryan Kastner, Andrew McCulloch, Jeffrey Omens and Adam Wright, International conference of the IEEE Engineering in Medicine & Biology Society (EMBS), August 2012

- "Strategies for Implementing Hardware-Assisted High-Throughput Cellular Image Analysis", Henry T. Tse, Pingfan Meng, Daniel R. Gossett, Ali Irturk, Ryan Kastner, and Dino Di Carlo, Journal of Laboratory Automation, December 2011 vol. 16 no. 6 422-430

#### ABSTRACT OF THE DISSERTATION

Learning Optimizations for Hardware Accelerated Designs

by

#### Pingfan Meng

Doctor of Philosophy in Computer Science

University of California, San Diego, 2016

Professor Ryan Kastner, Chair

Many emerging applications require hardware acceleration due to their growing computational intensities. These accelerated designs use heterogeneous hardware, such as GPUs, FPGAs and multi-core CPUs to process the intensive computations at a higher rate. The first part of this work provides two paradigms of hardware accelerated biomedical applications. These paradigms achieved 115X and 273X speedups respectively.

Developing these paradigms taught us that, in order to efficiently utilize the heterogeneous accelerators, the designer needs to carefully investigate which device is the most suitable accelerator for a particular computing task. In addition, the designer

needs to effectively optimize the computations to fully exploit the computing power of the selected accelerator. This process is called design space exploration (DSE). Heterogeneous DSE requires multiple programming skills for these different types of devices.

In recent years, there is a trend to use one unified programming language for multiple heterogeneous devices. The SDKs and hardware synthesis tools have enabled OpenCL as one unified language to program heterogeneous devices including GPUs, FPGAs, and multi-core CPUs. However, one major bottleneck for DSE still exists. In contrast to GPU and CPU OpenCL code compilation, which only consumes several milliseconds, implementing OpenCL designs on a FPGA requires hours of compilation time. Moreover, merely tuning a few programming parameters in the OpenCL code will result in an abundance of possible designs. Implementing all these designs requires months of compilation time. Exploring the FPGA design space with brute force is therefore impractical.

The second part of this work addresses this issue by providing a machine learning approach for automatic DSE. This machine learning approach automatically identifies the optimal designs by learning from a few training samples. In comparison with other state-of-the-art machine learning frameworks, this approach reduces the amount of hardware compilations by 3.28X, which is equivalent to hundreds of compute hours. This work also provides a data mining method that enables the machine to automatically use the estimation data to replace the time consuming end-to-end FPGA training samples for DSE. Mining these estimation data further reduces the amount of hardware compilations by 1.26X.

# Chapter 1

# Introduction

#### 1.1 Overview

#### 1.1.1 Optimization of Hardware Accelerated Designs

Numerous emerging applications from a variety of domains require computing systems that are capable of processing intensive data at a high rate. However, the general purpose Central Processing Units (CPU) are usually incapable of providing the required computing performance for these applications. Therefore, in order to meet the performance requirement, hardware acceleration is highly desirable. Several applications that used hardware acceleration are enumerated as follows: (1) many real-time detection and tracking tasks [1, 2, 3, 4, 5, 6] require accelerated computer vision systems; (2) bioinformatics applications [7, 8, 9, 10, 11, 12] require accelerated computing systems to process lengthy genetic sequences; (3) some database applications [13, 14, 15, 16, 17] require hardware accelerators to achieve higher throughput; (4) multiple cryptographic applications need hardware accelerators to reduce the compute time of those complex encryption/decryption operations [18, 19, 20, 21]; (5) many biomedical systems [22, 23, 24, 25, 26] require hardware accelerators to achieve the real-time processing rate.

These applications use heterogeneous hardware to accelerate the computationally intensive processes. Graphics Processing Units (GPU) and Field-Programmable Gate

Arrays (FPGA) are two types of typical heterogeneous hardware accelerators. Both the GPU and FPGA accelerate computations by utilizing parallelism. The GPU architecture contains many parallel cores that run in the Single Instruction, Multiple Data (SIMD) fashion. The FPGA provides a customizable architecture where the designers can implement parallelism such as pipelines and replicated computing units.

In order to achieve the high performance goal, the hardware accelerated designs need to be carefully optimized. The essence of this optimization task is to restructure and tune the code in a particular way to map the application onto those parallel hardware features efficiently. On the GPU, the programmer needs to map the original sequential software code to the SIMD architecture by assigning the computation tasks to a massive group of threads [27, 28, 29, 30]. The programmer also needs to carefully manage the memory access pattern of the code to efficiently fit the process on the memory hierarchy of the architecture. On the FPGA, the designer is responsible for customizing the architecture to fulfill the computation task. Due to the hardware design nature of the FPGA implementation, it requires the designer to optimize the architecture on a low level. For example, the designer needs to make decisions on the depth of a pipeline or the bit-width of a register [31, 32, 33, 34, 35, 36, 37].

This dissertation presents several research results on the problem of how to effectively explore the optimizations for hardware accelerated designs. In the first part, I will provide two hardware acceleration paradigms in two emerging application domains: one high throughput genetic sequencing system and one cardiac physiology image processing system. The second part of this dissertation presents a methodology using machine learning to automatically explore the optimization strategies for hardware accelerated designs.

#### 1.1.2 Hardware Accelerated Paradigms

In Chapter 2, I will present a paradigm of the hardware accelerated DNA de novo assembly. De novo assembly is a widely used methodology in bioinformatics. However, the conventional short-read de novo assembly is incapable of reliably reconstructing the large-scale structures of human genomes [38] due to the ambiguity caused by repetition of the nucleobases (i.e. "A", "T", "G" and "C"). In recent years, a novel assembly technology has been proposed. This new technology aligns the DNA strings based on the uniquely identifiable patterns of optical labels instead of the nucleobases. In contrast to the four letter nucleobases, these optical patterns are arbitrary floating point numbers. For this reason, these optical patterns are unlikely to have repetitions. Thus, this enables reliable large-scale de novo assembly. Despite its advantage in large-scale genome analysis, this new technology requires a more computationally intensive alignment algorithm than its conventional counterpart. For example, the run-time of reconstructing a human genome is on the order of 10,000 hours on a sequential CPU. Therefore, in order to practically apply this new technology in genome research, accelerated approaches are desirable. The results of this work are three different accelerated approaches, multi-core CPU, GPU and FPGA. Against the sequential software baseline, the multi-core CPU design achieved a  $8.4\times$  speedup while the GPU and FPGA designs achieved  $13.6\times$  and  $115\times$  speedups respectively. This work also provides the details of the manual design space exploration for this application on these three different devices. In addition, this work compares these devices in performance, optimization techniques, prices and design efforts.

In Chapter 3, I will present a FPGA-GPU-CPU heterogeneous hardware architecture for a biomedical image process application – real-time optical mapping. Real-time optical mapping is a technique that can be used in cardiac disease study and treatment technology development to obtain accurate and comprehensive electrical activity over the

entire heart [39, 40]. It provides a dense spatial electrophysiology. Each pixel essentially plays the role of a probe on that location of the heart. However, the high throughput nature of the computation causes significant challenges in implementing a real-time optical mapping algorithm. This is exacerbated by high frame rate video (order of 1000 fps) for many medical applications. Accelerating optical mapping technologies using multiple CPU cores yields modest improvements, but still only performs at 3.66 frames per second (fps). A highly tuned GPU implementation achieves 578 fps. A FPGA-only implementation is infeasible due to ultra-large intermediate data arrays generated by the optical mapping algorithm. The main result of this work is the real-time system accelerated by a FPGA-GPU-CPU architecture running at 1024 fps. This represents a 273× speedup over a multi-core CPU implementation.

Developing these paradigms taught us that the heterogeneous design space exploration (DSE) is extremely difficult. In many cases, each type of device requires a unique programming or design skill. Thus, in order to explore multiple acceleration devices for a given application, the designer needs to implement the application using multiple different languages. For example, in order to implement the paradigms described in Chapters 2 and 3, we used multiple programming languages such as C++, CUDA, Verilog and OpenMP. Using some of these design languages such as Verilog is especially tedious due to its low level nature. According to our firsthand development experience, it takes months of development time to implement one application on all these different devices.

In recent years, there is a trend of using one unified language to program all types of heterogeneous devices. The improvement of High Level Synthesis (HLS) tools allows the designer to use software language to program FPGAs. The state-of-the-art HLS tools are capable of automatically converting programs written in high level languages, such as C, CUDA and OpenCL [41, 42, 43, 44, 45, 46, 47, 48], to FPGA accelerated implementations. The OpenCL-to-FPGA synthesis tool is especially appealing since

OpenCL software SDKs have already been available for CPUs and GPUs. This means the designer can use one unified language to program all three heterogeneous devices. In order to achieve a high performance FPGA design, the programmer needs to tune multiple parameters and primitives in the high level code [49, 50, 51, 52, 53, 54]. Tuning these parameters and primitives creates a great number of possible designs. The HLS compilation process is time consuming due to the Place and Route (PnR) stage of the tool chain. PnR assigns the application functionalities onto the actual hardware logic and connects them physically. Multiple subproblems in this PnR task have been proven to be NP-hard [55, 56]. This process usually consumes multiple hours for a typical design. Thus, the brute force DSE method that implements and evaluates all these possible tunings may consume months of compilation time. This issue motivates the second part of this dissertation - machine learning automation.

## 1.1.3 Automatic Machine Learning Design Space Exploration

As discussed in Section 1.1.2, SDKs and hardware synthesis tools have provided a push forward to enable OpenCL as a unified language to program heterogeneous platforms such as GPUs, FPGAs, and multi-core processors. However, one major bottleneck of the system level OpenCL-to-FPGA design tools is their extremely time consuming synthesis process (including place and route). The design space for a typical OpenCL application contains thousands of possible designs even when considering a small number of design space parameters. It costs months of compute time to synthesize all these possible designs into end-to-end FPGA implementations. Thus, it is impractical to explore a large amount of possible designs by implementing and evaluating them.

One direction to address this issue is to build analytical models to describe the design objectives, e.g. performance and hardware resource utilization. Using these models, one can evaluate the designs without implementing them. There exists many

analytical models [57, 58, 59, 60, 61] for GPU architectures. However, in contrast to GPUs, the reconfigurable FPGA devices do not have fixed architectural features. Therefore, it is unlikely to build an analytical model to describe all FPGA designs. There only exist a few FPGA analytical models for particular domains of designs [62, 63]. The effectiveness of these models is moderate since the actual FPGA performance depends on many low level factors and design tool chain operations. These factors are usually nonlinear and sometimes even random (e.g. the random numbers used in the place and route stage). Therefore, it is extremely difficult to analytically describe the final output of a high level design. Moreover, these models only target several specific types of operations. They are not available for most applications on the FPGA.

Another direction is to build a machine to automatically learn the design space of each particular application by a small number of sampled training designs. However, most of the existing machine learning approaches focus on how to predict the model of the design space accurately. This is not the goal of optimization. The actual goal of optimization is to find the "good" designs. It is unnecessary to model the entire design space since it is useless to obtain the performances of those "bad" designs. Thus, the existing machine learning approaches are not suitable for FPGA DSE problems. To address this issue, in Chapter 4, we propose a novel machine learning approach - Adaptive Threshold Non-Pareto Elimination (ATNE). Instead of focusing on regression accuracy improvement, ATNE focuses on understanding and adapting to the inaccuracy. ATNE provides a Pareto identification threshold that adapts to the estimated inaccuracy of the regressor. This approach results in a more efficient DSE. For the same prediction quality, ATNE reduces the amount of required compilations by 3.28× (hundreds of compilation hours) against the other state of the art machine learning frameworks [64, 65] for FPGA DSE. In addition, ATNE is capable of identifying the Pareto designs for certain difficult design spaces which the other existing frameworks are incapable of exploring effectively. The ATNE approach uses the real FPGA implementations as the training data. Obtaining these training data still consumes a great amount of time due to the PnR stage in compilation. Is there any method to further reduce the time consumption? To answer this question, we investigated how to use pre-Place and Route (pre-PnR) estimation data for FPGA DSE in Chapter 5. We obtained one type of estimation data by running those FPGA OpenCL designs on the GPU. Although the GPU and FPGA are two different compute platforms, they are both dictated by the OpenCL programming model. The OpenCL design on the FPGA contains many GPU-like architectural features such as SIMD, compute unit parallelism, and local/global memory hierarchy. It is therefore reasonable to believe that if one uses OpenCL programming language on both devices, the GPU and FPGA design spaces will share a certain level of similarity. In contrast to implementing a design on the FPGA, it is significantly cheaper to compile a GPU program (milliseconds compilation on the GPU vs. hours of synthesis time on the FPGA). For these reasons, it is possible to use the GPU results to replace the FPGA training data for DSE.

We also obtained other types of estimation data from the pre-PnR stages of the OpenCL-to-FPGA compilation tool chain. These data contain some high level information of the application. Therefore, they can be used to roughly estimate the final FPGA implementation. Generating these estimations requires significantly less time than obtaining the real FPGA measurements does. Therefore, using these estimation data to partially replace the real FPGA training data could reduce the time consumption further. The estimations are not identical to actual FPGA measurements, i.e., there exists some level of inaccuracy (potentially substantial differences) in the estimation data. For this reason, an intelligent data mining approach is proposed in Chapter 5 to effectively extract useful information from the estimation data to improve FPGA DSE. We implemented this approach and evaluated it with 10 end-to-end FPGA benchmarks. The evaluation

results indicate that our approach effectively reduces the sampling complexity by  $1.26 \times$ , which reduces the DSE by hundreds of compute hours.

#### 1.2 Contributions

The primary contributions of this work are enumerated as follows.

A hardware accelerated optical labeled DNA sequence alignment system: This work is the first attempt to accelerate the large-scale genome assembly on hardware. The work provides an end-to-end FPGA accelerated design and a GPU accelerated implementation. In addition, this work provides a comparison and design space exploration of the multi-core CPU, GPU and FPGA. This work has been published and is described in Chapter 2.

A FPGA-GPU-CPU heterogeneous architecture for real-time optical cardioelectrophysiology: This includes a FPGA-GPU-CPU heterogeneous hardware accelerated system that provides real-time optical mapping. This also includes an analysis of how to efficiently partition and assign the application to different hardware accelerators. This work has been published and is described in Chapter 3.

A robust machine learning approach for OpenCL-to-FPGA Design Space Exploration: This includes a mathematical model to investigate how the machine learning technology should be applied in the system level FPGA DSE task. This work also provides a novel approach which reduces the synthesis complexity by 3.28× compared with other state of the art approaches. This work used 10 end-to-end OpenCL applications (real performance data from applications running on the FPGA, not just reports from the synthesis tool) to verify the effectiveness of the proposed approach. This work has been published and is described in Chapter 4.

A data mining approach that uses pre-Place and Route estimation data for OpenCL-to-FPGA Design Space Exploration: This work investigated the question of whether one can use estimation data for FPGA DSE by providing empirical studies on several possible approaches. The output of this work is a data-mining approach that effectively extracts the useful information from the estimated results for FPGA DSE.

### 1.3 Dissertation Outline

The dissertation is organized as two parts. Chapters 2 and 3 in Part I present the two manually designed hardware acceleration paradigms. Chapter 2 details the first paradigm: hardware accelerated approaches for a DNA sequence alignment algorithm. Chapter 3 focuses on the details of the second paradigm: a FPGA-GPU-CPU heterogeneous system for real-time cardiac physiological image processing.

Chapters 4 and 5 in Part II focus on the investigation of how to use machine learning to automate OpenCL-to-FPGA design space exploration. Chapter 4 describes a novel machine learning approach for the OpenCL-to-FPGA DSE. Chapter 5 discusses the question of whether one can use the pre-PnR estimation data to further improve the efficiency of the DSE.

Chapter 6 concludes this work. Chapter 7 describes several possible future directions of this topic.

# Part I

# **Manual Design Approaches**

# Chapter 2

# Hardware Acceleration Approaches for Optical Labeled DNA Alignment

## 2.1 Background and Motivation

The ability to construct *de novo* assemblies is widely pursued for medical and research purposes. These *de novo* assemblies are especially invaluable in the studies of structural variations of genomes [66]. However, the conventional short-read technology based *de novo* assemblies provide structural information only on a micro-scale (< 1,000 bases per fragment). They are not capable of reconstructing the large-scale structures of human genomes [38]. This is due to the fact that using the short-read based assembly leads to ambiguity when these large-scale (> 100,000 bases per fragment) genomes have frequent structural repetitions (typical medium to large genomes contain 40 - 85% repetitive sequences [67]).

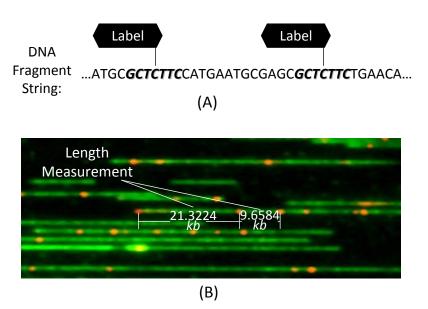

In recent years, research has shown that a novel optical label based technology is able to overcome this limitation of the short-read technology [68]. This novel technology fluorescently labels the DNA molecule strings at the locations where a specific nucleobase combination appears (e.g. label wherever the combination GCTCTTC appears, as demonstrated in Fig. 2.1(A)). Then the labeled DNA molecules are linearized by being passed through a nanochannel device. These linearized strings with labels are imaged

by a CCD camera as demonstrated in Fig. 2.1(B). In the image field, on each string, the physical distances between every two labels are measured and collected. This process results in a uniquely identifiable sequence-specific pattern of labels to be used for *de novo* assembly. As opposed to the four letters, these arbitrary physical distances are unlikely to contain structural repetitions. Therefore, this optical method enables the reconstruction of the large-scale genomes for modern bioinformatic studies. In genomic studies, *N*50 is a widely used metric to measure the ability of a technology to assemble large-scale structures. Research results show that this novel optical assembly enhances the *N*50 by two orders of magnitude compared to the short-read assembly [38].

**Figure 2.1.** Demonstration of the optical labeling process. (A) Fluorescent labels attached to "GCTCTTC". (B) The real image field of labeled DNA fragments from a microscopy CCD camera. The strings are linearized DNA fragments. The glowing dots are fluorescent labels. The numbers in kilo-bases(kb) are examples of physical distance measurement between labels.

The task of the *de novo* assembly is reconstructing the genome from a set of DNA fragments. The most computationally intensive part of this task is the algorithm that aligns every pair from the DNA fragment set. This pair-wise alignment algorithm

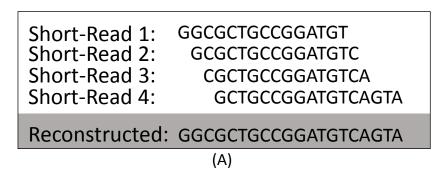

for the optical assembly is fundamentally different from the short-read alignment. In the conventional short-read based process, as depicted in Fig. 2.2 (A), the alignment algorithm is applied on the strings with "A", "C", "G" or "T" DNA nucleobase letters. As opposed to the short-read letters, the new optical method aligns the locations of the fluorescent labels on the strings shown in Fig. 2.2 (B). Aligning these arbitrary numbers obtained from a human genome takes nearly 10,000 hours on a sequential CPU. Moreover, research [69] has shown that the resolution of the optical label method can be further enhanced by adding multiple types (colors) of labels.

**Figure 2.2.** Comparison of the conventional and the novel *de novo* assembly methods. (A) Alignment process in the conventional short-read based method. (B) Alignment process in the novel optical label based method. Each dot represents a fluorescent label.

Therefore, accelerating this alignment algorithm is desired not only for the purpose of shortening the process time but also for enabling this optical based technology in genome studies that require high resolutions.

In this chapter, we present three accelerated approaches for the optical labeled

DNA fragment alignment using multi-thread CPU, GPU and FPGA. These designs are compared against a single thread sequential CPU implementation.

The rest of the chapter is organized as follows. We discuss related work in Section 2.2. We describe the alignment algorithm in Section 2.3. This is followed by descriptions of the accelerated designs in Section 2.4. Experimental performance results are provided in Section 2.5. We compare the hardware accelerators in Section 2.6. Section 2.7 summarizes this chapter.

#### 2.2 Related Work

Multiple accelerated approaches for short-read assembly have been proposed in recent years. Olson *et al.* have proposed a multi-FPGA accelerated genome assembly for short-reads in [7]. They accelerated the alignment algorithm on the FPGAs for the reference guided genome assembly with 250× and 31× speedups reported against the software implementations BFAST and Bowtie respectively. Varma *et al.* have presented a FPGA accelerated *de novo* assembly for short-reads in [8]. They chose to accelerate a preprocessing algorithm on the FPGA to reduce the short-read data for the CPU assembly algorithm. They reported a 13× speedup over the software. They also proposed an improved FPGA implementation exploiting the hard embedded blocks such as BRAMs and DSPs in [70]. Attempts have also been made to accelerate genome assembly on GPUs. Aji *et al.* have proposed a GPU accelerated approach for short-read assembly in [71]. They reported a 9.6× speedup. Liu *et al.* proposed a GPU accelerated DNA assembly tool - SOAP3 [72] which achieves 20× speedup over Bowtie.

Although these approaches have improved the performance of the short-read assembly significantly, they are limited to micro-scale genomes. There is still no high performance solution for large-scale genome structure analysis. Our implementations provide an accelerated solution for this large-scale genome task.

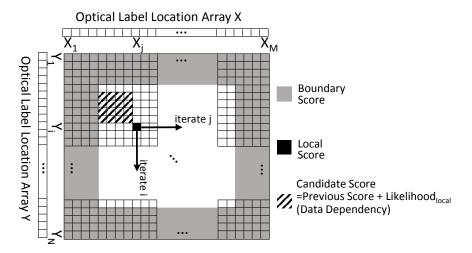

Our implementations are fundamentally different from these previous efforts because they employ the novel optical label based genome assembly. Our accelerated designs differ from the previous short-read approaches in two ways: 1) the data in the optical method requires more precision bits than conventional four letters (A,C,G,T) do; 2) the physical label locations require a different alignment algorithm [73] from the traditional Smith-Waterman. Most short-read methods employed the traditional Smith-Waterman algorithm which computes each score matrix element from its three immediately adjacent elements. The algorithm in our optical label based method computes each element from a  $4 \times 4$  area as demonstrated in Fig. 2.5. These differences not only increase the computational intensity but also require a different hardware parallel strategy from the ones proposed in these previous short-read based works. To the best of our knowledge, our implementations are the first attempt to accelerate the large-scale genome assembly using GPUs and FPGAs.

## 2.3 Alignment Algorithm

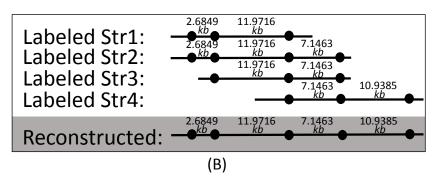

Our goal is to align every pair of floating point number arrays which represent the physical distances of the optical labels on the DNA fragments. As shown in Fig. 2.3, for arrays X and Y, we decide whether the alignment ( $X_j$  aligned to  $Y_i$ ) is valid based on three evaluations. Firstly, as shown in Fig. 2.3 (A), we need to evaluate the similarity between  $X_j$  and  $Y_i$ , which is intuitive. Secondly, as depicted in Fig. 2.3 (B), we need to evaluate the boundary offset penalty. When  $X_j$  is aligned to  $Y_i$ , the leftmost ends of  $X_j$  and  $X_j$  may create an offset. Large offsets produce unwanted gaps in the DNA assembly. A valid alignment should have minimum offset. The third evaluation is to calculate the similarities between  $X_j$ 's neighbors and  $Y_i$ 's neighbors as demonstrated in 2.3 (C). The necessity of this evaluation is also intuitive. Even if  $X_j$  is very similar to  $Y_i$ , the alignment is not valid if the other elements of the two arrays are dissimilar.

**Figure 2.3.** Array alignment: assume  $X_j$  aligned to  $Y_i$ , (A) evaluate the similarity between  $X_j$  and  $Y_i$ ; (B) evaluate the boundary offset penalty when  $X_j$  aligned to  $Y_i$ ; (C) evaluate the similarities between  $X_j$ 's neighbors and  $Y_i$ 's neighbors.

These intuitive evaluations of the alignment are realized by a dynamic programming method specifically modified for the optical DNA analysis by Valouev [73]. The overall flow diagram of the algorithm is demonstrated in Fig. 2.4. The algorithm aligns two arrays X and Y of optical label positions by computing a likelihood score matrix and finding the maximum within this matrix. Each score represents the likelihood of a possible alignment between X and Y. Assuming the sizes of the input arrays are M and N, the algorithm computes a  $M \times N$  score matrix as depicted in Fig. 2.5. The computation of each element in the matrix requires local scores. The black square in the figure shows an example of a local score. Those elements near the edges, shown as the grey regions in the figure, also require boundary scores. Thus, the alignment algorithm consists of three steps: 1) compute the boundary scores as described in Algorithm 2.1; 2) compute the local scores as described in Algorithm 2.2; 3) find the best score and its correspondent (i, j) in the score matrix as shown in lines 10 - 12 of Algorithm 2.2. If the best score passes the threshold, then we find an alignment between X and Y with  $X_i$

aligned to  $Y_i$  using a trace-back operation. In our hardware accelerated approaches, we keep the trace-back operation on the host PC. We therefore only describe the best score computation in detail as follows.

#### Accelerate the most computationally intensive stage PC Accelerator DNA Align-Boundary Local Max Score Path Frag. Score Score Search Trace ment arravs Avoid intensive device - PC data transfer

**Figure 2.4.** Overall algorithm and its hardware partitioning. We accelerate the local score stage due to its computational intensity. In our partitioning, we also assign the boundary score and max score search stages to the accelerator to avoid intensive device-PC data communication.

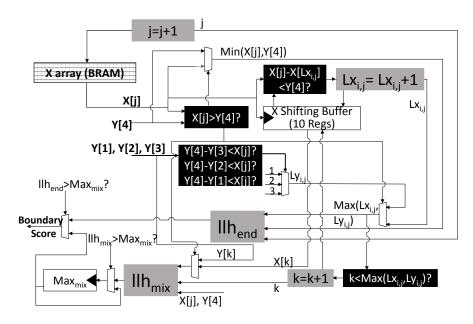

The computation of the boundary scores is described in Algorithm 2.1. In the algorithm, to compute a boundary score element located at (i, j), we firstly compute its leftmost offset  $Lx_{i,j}$  or  $Ly_{i,j}$  as shown in lines 13 - 22. Then we compute an "end" likelihood and several mixed likelihoods as shown in lines 23 - 33. We choose the maximum among these likelihoods to be the boundary score for this position. This process is iterated, as shown in lines 4 and 12, to produce the boundary scores for the top 4 rows and the leftmost 4 columns of the score matrix. An identical boundary score algorithm is also applied on the rightmost offsets of the input arrays to fill the bottom 4 rows and the rightmost 4 columns of the score matrix. These boundary score locations are visualized in Fig. 2.5.

We compute a local score to represent the similarity between  $X_j$  and  $Y_i$  as well as the similarities between  $X_j$ 's neighbors and  $Y_i$ 's neighbors. In Algorithm 2.2, to compute each local score  $score_{i,j}$ , we generate 16 score candidates correspondent to its upper-left  $4 \times 4$  neighbors (refer to Algorithm 2.2 lines 5 - 9). Each of the 16 candidates is

computed by adding a local likelihood (this represents the similarity between  $X_j$  and  $Y_i$ ) to its correspondent previous score (this represents the similarity between  $X_j$ 's neighbors and  $Y_i$ 's neighbors) from the  $4 \times 4$  area (the shaded area in Fig.2.5). The score in  $score_{i,j}$  is updated with the maximum among all these  $4 \times 4$  candidates. This process is iterated  $M \times N$  times to generate the complete score matrix as shown in lines 3 and 4. Then we find the highest score within the matrix (lines 10 - 12), which represents the best alignment for X and Y. This highest score is used in the post processes to complete the genome reconstruction.

**Figure 2.5.** Visualized pair-wise alignment process. The 2D array represents the likelihood score matrix. Each (i, j) element in the matrix is a likelihood score for aligning  $X_j$  with  $Y_i$ . The top, bottom, left and right grey regions represent the boundary score computations. The black square and the shaded area displays one iteration of the dynamic programming process. The computations for the black square have data dependencies to the shaded area. The arrows show that this computation is iterated to fill the entire matrix.

The likelihood functions in Algorithm 2.1 and 2.2 are derived from an error model proposed in [73]. The functions  $Likelihood_{local}(x, y, m, n)$  and  $Likelihood_{end}(x, m, n)$  are computed as shown in Equations 2.3 and 2.4 respectively. The  $Likelihood_{local}(x, y, m, n)$  function consists of two terms: the bias value  $B_{XY}$  (provided in Equation 2.1); the maximum between the penalty value (provided in Equation 2.2) and a constant  $P_{OutlierPenalty}$ .

The values of the constants used in Equations 2.1 - 2.4 are empirically tuned to suit the optical experiment [73]. Changing these values does not influence the computing speed of the algorithm. Therefore, without the loss of generality, in our implementations, we tuned these constants to suit our experiment input data - a synthetic human genome. These constant values are listed in Table 2.1.

Let F represent the number of DNA fragments of an assembly process. Let M be the number of labels on the fragment. The algorithm requires  $O(F^2N^2)$  times of  $Likelihood_{local}$  operations to complete an assembly process. The DNA fragment pool typically has 100,000 - 1,000,000 arrays. A typical input array length (M or N) is 15 - 100 elements. Therefore, the number of  $Likelihood_{local}$  operations, in a human genome assembly process, is on the order of  $10^{15}$ . The total amount of computations requires more than 10,000 hours on a sequential CPU.

Each element of the input arrays represents a distance, which is on the order of thousands of bases, between two neighboring optical labels on the actual DNA fragment. The synthetic data used in our implementations is designed to simulate these properties of the real-world human genomes. Since the data ranges and array lengths are similar, the computation performance tested with this synthetic data reflects the performance with the real-world genomes.

Our focus is to accelerate this pair-wise algorithm which aligns the optical labeled DNA molecule fragments to construct the contigs in the assembly process. The scaffolding process, using optical labeled contigs, is not a computationally intensive operation which can usually be performed on a sequential computer in 10-30 minutes.

$$bias_{XY} = [max(0, x - \delta) + max(0, x - \delta)] * B + B'$$

(2.1)

$$pen = C - \frac{(x-y)^2}{V*(x+y)} - P_{miss}*(m+n) - [max(0,x-\delta) + max(0,x-\delta)]*R$$

(2.2)

$$Likelihood_{local}(x, y, m, n) = bias_{XY} + max(pen, P)$$

(2.3)

$$Likelihood_{end}(x,m,n) = 2*max(0,x-\delta)*B_{end} + B'_{end} - P_{miss}*(m+n-2)$$

(2.4)

### **Algorithm 2.1:** The Boundary Score Algorithm

```

: Two arrays of optical label locations X, Y; Sizes of the input arrays 1: M,

1 Likelihood_{local}(x, y, m, n) local likelihood function

2 Likelihood<sub>end</sub>(x,m,n) end likelihood function

3 Likelihood<sub>mix</sub>(x, y, m, n) = Likelihood_{end}((x+y)/2, m, n) +

Likelihood_{local}(x, y, 1, 1) - Likelihood_{local}((x+y)/2, (x+y)/2, 1, 1) mixed local

and end likelihood function

4 for i = 1 to N do

Lx_{i,j} = 0, Ly_{i,j} = 0

5

if i \le 4 then

6

7

j_{max} = M

end

8

else

j_{max} = 4

10

end

11

12

for j = 1 to j_{max} do

if X_i < Y_i then

13

while Y_i - Y_{Ly_{i,j}} > X_j do

14

Ly_{i,j} + +

15

16

end

17

18

else

while X_i - X_{Lx_{i,i}} > Y_i do

19

20

Lx_{i,i}++

end

21

end

22

score_{i,j} =

23

Likelihood_{end}(min(X_j, Y_i), j + 1 - max(1, Lx_{i,j}), i + 1 - max(1, Ly_{i,j}))

if X_i < Y_i then

24

25

for k = Ly_{i,j} to i - 1 do

score_{i,j} = max(score_{i,j}, Likelihood_{mix}(X_j, Y_i - Y_k, j, i - k))

26

end

27

end

28

else

29

for k = Lx_{i,j} to j - 1 do

30

score_{i,j} = max(score_{i,j}, Likelihood_{mix}(X_j - X_k, Y_i, j - k, i))

31

end

32

33

end

end

34

Output: Score matrix score[1:N][1:M] filled with boundary scores in the top 4

rows and leftmost 4 columns

```

## Algorithm 2.2: The Dynamic Programming Score Algorithm

```

:Two arrays of optical label locations X, Y; Sizes of the input arrays 1: M,

1:N; Score matrix score[1:M][1:N] with boundary scores filled

1 Likelihood_{local}(x, y, m, n) local likelihood score function

2 score_{best} = -\infty

3 for i = 1 \text{ to } N \text{ do}

for j = 1 to M do

5

for g = max(1, i-4) to i-1 do

for h = max(1, j-4) to j-1 do

6

score_{i,j} =

max(score_{i,j}, A_{g,h} + Likelihood_{local}(x_j - x_h, y_i - y_g, j - h, i - g))

end

8

end

9

if score_{i,j} > score_{best} then

10

score_{best} = score_{i,j}, j_{best} = j, i_{best} = i

11

end

12

end

13

14 end

Output: Best score score_{best}; The X and Y indices of the best score j_{best} and i_{best}

```

**Table 2.1.** Constant values for score functions

| Constant          | Value   |

|-------------------|---------|

| V                 | 0.0449  |

| δ                 | 0.0010  |

| В                 | -0.0705 |

| $B^{'}$           | 0.9144  |

| P <sub>miss</sub> | 1.5083  |

| R                 | -0.0931 |

| P                 | -8.1114 |

| $B_{end}$         | 0.0226  |

| $B_{end}^{'}$     | 0.3992  |

# 2.4 Accelerated Designs

We partitioned the algorithm by accelerating some parts on the hardware and keeping some parts on the PC. This partitioning strategy is depicted in Fig. 2.4. The most computationally intensive stage of the algorithm is the local score computation. Therefore, in our partitioning, we accelerated the local score computation on the hardware. The two stages, boundary score computation and maximum score search, are not as computationally intensive as the local score stage. However, these two stages have significantly intensive data communication with the local score stage. In order to avoid this communication bottleneck between the PC and the hardware accelerator, we also assigned these two stages on the accelerator. The path trace stage consists of control intensive operations. Therefore, we kept this stage on the PC.

**Figure 2.6.** Possible parallelism in the algorithm.

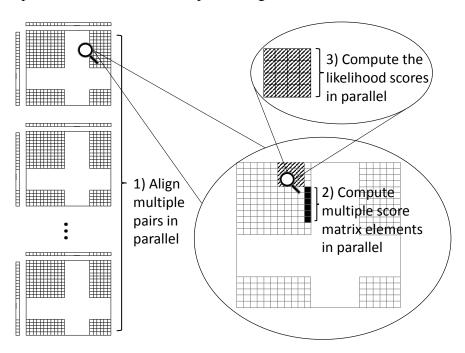

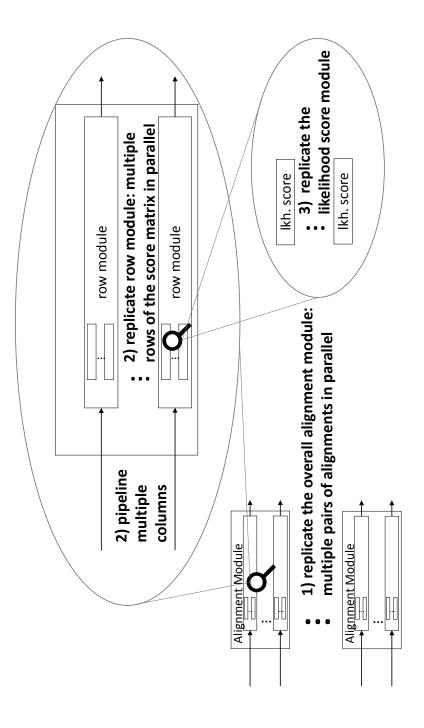

We identified three levels of possible parallelism in the algorithm (from coarse-grained to fine-grained): 1) align multiple pairs in parallel; 2) compute multiple elements

(rows or columns) in the score matrix in parallel; 3) compute the 16 likelihood scores for each score element in parallel. These three levels and their hierarchy are depicted in Fig. 2.6. Particular computation and data reuse patterns exist in each level of possible parallelism. These patterns create tradeoffs in hardware accelerated designs.

When using level 1 parallelism (processing multiple pairs in parallel), each pair is data independent. Therefore, data communications or synchronization between parallel processes do not exist. However, it requires more computing resource to manage multiple alignments concurrently as well as more storage resource for intermediate data (e.g. multiple score matrices). On the other hand, the other two levels of parallelism (levels 2 and 3) provide more opportunities to share or reuse the data between the parallel processes due to their finer granularity. However, these two fine-grained levels of parallelism may introduce performance challenges such as higher synchronization overhead on processors and placement and route complexity on FPGAs. These complex architectural tradeoffs create design space exploration problems. We explored these design spaces to determine the proper level or combination of levels of parallelism to match the architectural features on the hardware. We also applied multiple optimization techniques on each design. We applied SIMD instructions and multi-thread techniques on the CPU design. For the GPU design, we tuned the CUDA code to tackle the data dependency caused by the local score computation. We also implemented a low level FPGA design due to the inefficient resource utilization provided by the state of the art high level synthesis tools. In the following sections, we describe the design space explorations and the optimal designs in detail.

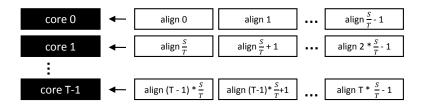

## 2.4.1 Multi-core CPU

In the CPU design, we firstly improved the locality of the program by dictating the compiler to store the highly reused variables in the CPU registers. We then parallelized

the algorithm by inserting OpenMP directives. The performance is highly correlated with the granularity of the iterations in the algorithm. We evaluated the fine-grained strategy which processes multiple rows and columns in parallel on the multiple CPU cores. The evaluation results indicated that it is expensive to synchronize and exchange fine-grained data among the cores. The multi-core CPU is more suitable for the coarse-grained parallelism. Therefore, we chose to align multiple pairs in parallel on the multi-core CPU.

We divided the total workload into several sets of alignment tasks and assigned each of the sets to a CPU core as demonstrated in Fig. 2.7. When one CPU core finishes its current alignment workload, it can start aligning another pair immediately without synchronizing with the other CPU cores. This setup does not create "dead" parallel processes or threads when the input array sizes change during the run-time. Therefore, all the CPU cores are completely occupied during this process. In addition, within each core, the process is in a sequential fashion which is suitable for control dominated operations such as the boundary score computation. We also forced functions  $Likelihood_{local}(x, y, m, n)$  and  $Likelihood_{end}(x, m, n)$  to be static and inlined in order to provide more optimization opportunities for the compiler.

The computations of the *Likelihood*<sub>local</sub> function provide us an opportunity to utilize the CPU SSE SIMD instructions. Therefore, we program the *Likelihood*<sub>local</sub> function to process 4 elements with a SIMD fashion using "\_\_m128" type of its intrinsic operands.

## 2.4.2 **GPU**

The GPU design consists of three CUDA kernels, invoked from a C++ host code. The CUDA kernels accelerate the alignment algorithm to keep the intermediate data on the GPU during the process. The C++ host program only sends the input DNA arrays to

**Figure 2.7.** Multi-core CPU accelerated design. Assume there are *S* pairs of optical arrays to be aligned and the CPU has *T* cores.

the first kernel and receives the output maximum score from the third kernel.

There are multiple options for CUDA kernel design based on different levels of granularity. We firstly evaluated the coarse-grained only strategy on the GPU. The evaluation shows that coarse-grained parallelism is significantly bounded by a low GPU occupancy. Therefore, to fully utilize the GPU parallel computing power, we added fine-grained parallelism in our design. The GPU design computes multiple rows and columns in fine-grained parallel within each GPU thread-block. The design also utilizes multiple thread-blocks to align multiple pairs in coarse-grained parallel. Computing the 16 candidates in parallel is not efficient on the GPU since it requires a 16-element reduction process which creates idle threads frequently.

We partitioned the algorithm into three CUDA kernels 1) boundary score kernel; 2) dynamic programming kernel; 3) maximum score search kernel. We chose this kernel partitioning because these parallelized computations require GPU global synchronization after 1) and 2).

In the boundary score kernel design, we fully parallelized the computations due to the data independency. The GPU thread arrangement is: assigning the boundary score computation for each element (lines 12 - 30 in Algorithm 2.1) to one GPU thread; assigning the boundary score computations of each alignment to one GPU thread-block. With this design, we maximized the GPU parallel resource occupancy. Moreover, since this design assigns all the computations of an alignment to the same thread-block, we

**Listing 2.1.** Pseudo Code for Dynamic Programming GPU Kernel

```

//gridDim.x=number of alignments

//blockDim.x=N, blockDim.y=4

3

__global__ void par_4_col_kernel(/*input/output arguments*/)

4

{

5

int align_offset=M*N*blockIdx.x;

//shared mem delecration

6

//move input X, Y arrays from global memory to shared memory

7

8

for (int col_id=0; col_id < M; col_id++)

9

10

if (threadIdx.y==0)

11

/*use feedback_score to compute the leftmost candidates and find

12

the max for col_id+3*/

13

14

else if (threadIdx.y==1)

15

/*use feedback_score to compute the 2nd left candidates and find

16

the max for col_id+2*/

17

18

else if (threadIdx.y==2)

19

20

/*use feedback_score to compute the 2nd right candidates and find

the max for col_id+l*/

21

22

else if (threadIdx.y==3)

24

/*use feedback_score to compute the rightmost candidates and find

the max for col_id*/

//output the score for col_id

26

//feedback_score[threadIdx.x]=score for col_id

27

28

_syncthreads();

29

30

}

```

were able to store the intermediate data in the shared memory to minimize the memory access delay in the computations.

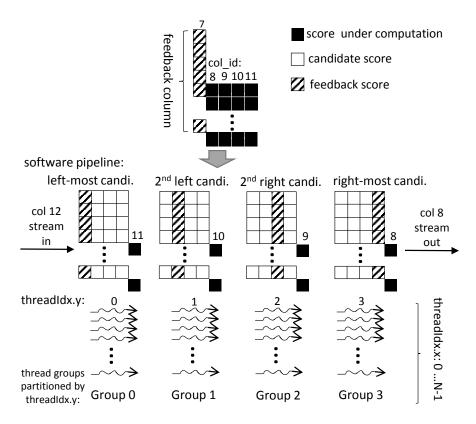

The pseudo code of the dynamic programming kernel is described in Listing 2.1. We parallelized the score element computations using  $N \times 4$  threads in each thread-block. The candidate score computation for each matrix column requires 4 previous columns as described in line 7 of Algorithm 2.2. Parallelizing this part of the algorithm is a challenging task due to this data dependency. We overcame this issue by dynamically assigning the columns of the score matrix to 4 groups of threads. As described in Listing

2.1, we used *threadIdx.y* to partition  $N \times 4$  threads into 4 groups. They form a software pipeline. Each thread group is only responsible for a specific candidate computation (leftmost, 2nd left, 2nd right or rightmost). By increasing *col\_id*, we stream the columns of the score matrix into this pipeline.

**Figure 2.8.** Visualized GPU kernel for dynamic programming, assuming the score matrix size is  $M \times N$ . N rows  $\times$  4 columns of score elements are computed concurrently. For example, columns 8,9,10 and 11 are computed concurrently. At the given state in the example, column 11 is assigned to the threads whose *threadIdx.y* = 0. Then the leftmost candidates of column 11 are computed using the previously computed data in column 7. Similarly, columns 10,9 and 8 are assigned to *threadIdx.y* = 1, *threadIdx.y* = 2 and *threadIdx.y* = 3 respectively. N is set to a multiple of 32 to ensure each warp has the threads with the same *threadIdx.y*.

The example in Fig. 2.8 shows a snapshot of this software pipeline when the GPU is processing columns 8, 9, 10 and 11. These columns are assigned to the different stages (thread groups) of the pipeline: column 11 to group threadIdx.y = 0; column 10

to threadIdx.y = 1; column 9 to threadIdx.y = 2; column 8 to threadIdx.y = 3. The computations in the pipeline stages threadIdx.y = 0 - 3 are leftmost candidates, 2nd left candidates, 2nd right candidates and rightmost candidates respectively, as shown in the shaded blocks in Fig. 2.8. In the snapshot, these computations all require the data from column 7 which has already been computed in the previous  $col_{-}id$  iteration (refer to the "for" loop in Listing 2.1). Once the computations in the snapshot are finished, the data in column 8 is then ready. With the data from column 8, the pipeline streams a new column (column 12 in the snapshot) by increasing the iteration index  $col_{-}id$ . These 4 thread groups execute different instructions to implement the 4 stages of the pipeline. In order to fit this design on the GPU SIMD architecture, we ensured the threads of each GPU warp to execute the same instruction by extending N to a multiple of 32.

Once the dynamic programming kernel finishes computing the score matrix, the third kernel searches the matrix to find  $score_{best}$ ,  $i_{best}$  and  $j_{best}$ . We implemented this maximum score search kernel using the reduction approach. We kept the reduction process of each alignment within one thread-block. Therefore, this process does not require the expensive global synchronization on the GPU. Then, we created multiple thread-blocks to concurrently process the reductions for multiple alignments. We also applied shared memory and efficient warp arrangement in the reduction.

### 2.4.3 **FPGA**

Similar to the GPU, the FPGA also accelerates the algorithm by processing the computations in a parallel fashion. The FPGA is a customizable architecture. There are usually two ways to implement the parallelism on the FPGA: 1) replicate a logic module multiple times to physically create multiple parallel data paths; 2) pipeline the architecture to process the multiple data concurrently in a streaming fashion. A high performance design requires a proper decision on which technique is used to implement

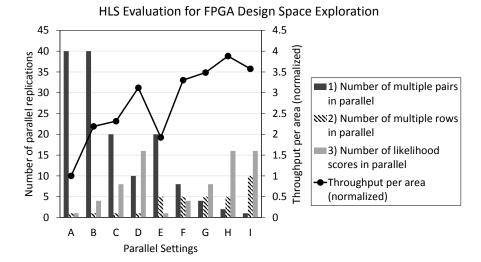

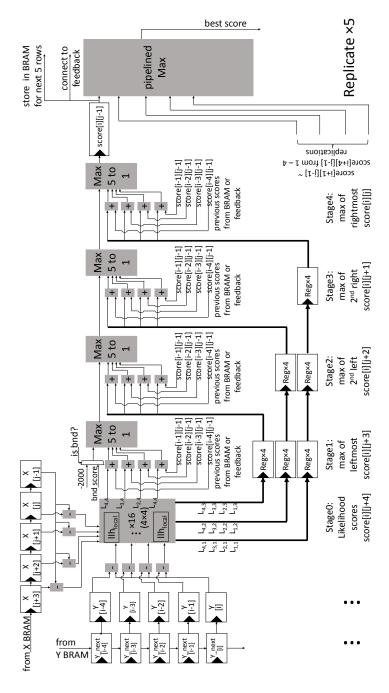

each of the three levels of the algorithmic parallelism. Moreover, due to the FPGA resource constraints, a feasible design also requires the proper number of replications in each level of parallelism. There exists many possible settings of choices of parallel techniques and numbers of replications. In order to reduce the size of the design space, we firstly constructed a reasonable structure of the FPGA design based on heuristics. Fig. 2.9 depicts this FPGA structure. Due to the algorithmic data dependency, it is impossible to replicate parallel data paths for both row and column dimensions. Therefore, we chose to only replicate the row parallel data paths (level 2 parallelism)and pipeline the column dimension (level 2 parallelism). We replicated the likelihood score units (level 3 parallelism) to sustain the throughput of this full pipeline in the column dimension. We also replicated the entire alignment module multiple times (level 1 parallelism) to maximize the overall throughput. We then permutated the numbers of parallel paths in this structure to find the optimal setting.

Implementing multiple RTL designs to measure the performances of these permutations requires a significant amount of effort. Therefore, exploring the FPGA design space using RTL designs is inefficient in terms of the development complexity. Instead of manually implementing multiple RTL designs, we propose a method using Vivado HLS which enables rapid FPGA implementations to explore different parallel structures.

We restructured the original software C code, as described in Listing 2.2, into the format that represents the parallel hardware structure. We firstly constructed a function  $lkh\_score()$  to implement the likelihood score computation in equation 2.3. To implement the full pipeline, we restructured the local score computation code into a function  $pipeline\_unit()$  with 4 pipeline stages. Lines 35 - 39 describe a line buffer used to feed the input into this pipeline. We then call  $pipeline\_unit()$  in the  $alignment\_module()$  function.

Listing 2.2. Pseudo Code for local score element computation function in HLS C code

```

void lkh_score(/*argument declaration*/)

3

//compute likelihood score as shown in equation ref{equ:s_function}

4

}

void pipeline_unit(/*argument declaration*/)

6

#pragma HLS ALLOCATION instances=1kh_score limit=16

8

//use HLS ALLOCATION directive to control the number of lkh_score

replications

11

/*declare buffering variables for the 4 stages (4 columns)*/

13

/* call lkh\_score() to compute likelihood scores for 0-3 columns*/

15

//pipeline

16

/* stage0: max for column 0*/

17

/* stage1: max for column 1*/

18

/* stage2: max for column 2*/

19

/* stage3: max for column 3*/

20

22

void alignment_module(/*argument declaration, e.g. input: DATA_TYPE x*/)

23

{

24

#pragma HLS ALLOCATION instances=pipeline_unit limit=5

25

/*use HLS ALLOCATION directive to control the number of pipeline_unit

replications */

27

/*declare x, y line buffers:

e.g. DATA_TYPE x0, x1, x2, x3, x4; */

28

30

for (/* iterate row index */)

31

{

32

for(/* iterate column index */)

33

34

//update the x line buffer

35

x4=x3;

36

x3=x2;

37

x2=x1;

38

x1=x0;

39

x0=x;

40

/* call pipeline_unit(x0, x1, x2, x3, x4, ...) */

41

}

42

43

}

void top_module(/*argument declaration*/)

45

46

{

47