# UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Power Conditioning and Stimulation for Wireless Neural Interface ICs

### Permalink

https://escholarship.org/uc/item/89w6j2k7

#### **Author** Biederman, William

# Publication Date 2014

Peer reviewed|Thesis/dissertation

#### Power Conditioning and Stimulation for Wireless Neural Interface ICs

by

William James Biederman III

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Jan M. Rabaey, Chair Associate Professor Elad Alon Professor Paul K. Wright

Fall 2014

### Power Conditioning and Stimulation for Wireless Neural Interface ICs

Copyright 2014 by William James Biederman III

#### Abstract

#### Power Conditioning and Stimulation for Wireless Neural Interface ICs

by

William James Biederman III

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Jan M. Rabaey, Chair

Brain machine interfaces have the potential to revolutionize our understanding of the brain, restore motor function, and improve the quality of life to patients with neurological conditions. In recent human trials, control of robotic prostheses has been demonstrated using micro-electrode arrays, which provide high spatio-temporal resolution and an electrical feedback path to the brain. However, after implantation, scar tissue degrades the recording signal-to-noise ratio and limits the useful lifetime of the array. This work presents two systems which utilize wireless techniques to mitigate this effect and create high-density, long-term interfaces with the human brain.

A wirelessly powered  $0.125 \text{mm}^2 65 \text{nm}$  CMOS IC integrates four  $1.5 \mu$ W amplifiers ( $6.5 \mu$ Vrms input-referred noise with 10kHz bandwidth) with power conditioning and communication circuitry. Multiple nodes free-float in the brain and communicate via backscatter to a wireless interrogator using a frequency-domain multiple access communication scheme. The full system, verified with wirelessly powered in vivo recordings, consumes  $10.5 \mu$ W and operates at 1mm range in air with 50mW transmit power.

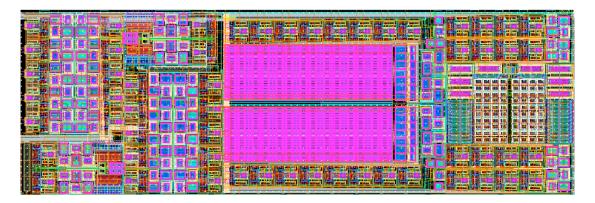

A 65nm CMOS 4.78mm<sup>2</sup> neuromodulation SoC integrates closed loop BMI functionality on a single IC which can be arrayed on a wireless sub-cranial platform. The IC consumes  $348\mu$ A from an unregulated 1.2V supply while operating 64 acquisition channels with epoch compression (at an average firing rate of 50Hz) and engaging two stimulators (with a pulse width of  $250\mu$ s/phase, differential current of  $150\mu$ A, and a pulse frequency of 100Hz). Compared to the state of the art neural SoCs, this represents the lowest area and power for the highest integration complexity achieved to date.

# Contents

| C        | onter                                   | nts                                                                                                                                                                                                                             | i                            |

|----------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Li       | st of                                   | Figures                                                                                                                                                                                                                         | iii                          |

| Li       | st of                                   | Tables                                                                                                                                                                                                                          | vii                          |

| 1        | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4 | coduction to Brain Machine Interfaces         Signals of the Brain       .         Neural Recording Techniques       .         Electrode-Tissue Interface Model       .         Biological Response of a Neural Implant       . | <b>1</b><br>2<br>5<br>8<br>9 |

| <b>2</b> |                                         | sign of A Fully-Integrated, Miniaturized $(0.125 \text{mm}^2) 10.5 \mu \text{W}$ Wireless                                                                                                                                       | 19                           |

|          |                                         | Iral Sensor                                                                                                                                                                                                                     | 13                           |

|          | 2.1                                     | System Design                                                                                                                                                                                                                   | 15                           |

|          |                                         | 2.1.1 Communication Protocol $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                              | 16                           |

|          | 0.0                                     | 2.1.2 SAR & Frequency Selection                                                                                                                                                                                                 | 16                           |

|          | 2.2                                     | Power Management                                                                                                                                                                                                                | 18                           |

|          |                                         | 2.2.1 Antenna Optimization                                                                                                                                                                                                      | 18                           |

|          |                                         | 2.2.2 Voltage Regulation                                                                                                                                                                                                        | 19                           |

|          |                                         | 2.2.3 Voltage Reference Generation                                                                                                                                                                                              | 21                           |

|          |                                         | 2.2.3.1 Architecture                                                                                                                                                                                                            | 22                           |

|          |                                         | 2.2.3.2 Error Analysis                                                                                                                                                                                                          | 25                           |

|          |                                         | 2.2.3.3 Performance                                                                                                                                                                                                             | 27                           |

|          |                                         | $2.2.3.4  \text{Conclusions}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                  | 28                           |

|          |                                         | 2.2.4 Bias Current Generation                                                                                                                                                                                                   | 29                           |

|          |                                         | 2.2.5 Power-On Reset                                                                                                                                                                                                            | 30                           |

|          | 2.3                                     | System Results                                                                                                                                                                                                                  | 31                           |

|          |                                         | 2.3.1 Wireless Operational Range                                                                                                                                                                                                | 31                           |

|          |                                         | 2.3.2 Single and Multi-Node Communication Tests                                                                                                                                                                                 | 32                           |

|          |                                         | 2.3.3 Wirelessly-Powered Full System Test                                                                                                                                                                                       | 33                           |

|          |                                         | 2.3.4 Wirelessly-Powered In Vivo Recording                                                                                                                                                                                      | 34                           |

|          | 2.4   | Conclusion                                                                                                                                    | 36 |

|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3        |       | ign of a 4.78mm <sup>2</sup> Neuromodulation SoC Combining 64 Acquisition<br>nnels with Digital Compression and Simultaneous Dual Stimulation | 41 |

|          | 3.1   | System                                                                                                                                        | 42 |

|          | 3.2   | Power Management                                                                                                                              | 44 |

|          |       | 3.2.1 Bandgap Reference                                                                                                                       | 45 |

|          |       | 3.2.2 Regulators                                                                                                                              | 47 |

|          | 3.3   | Neural Stimulation                                                                                                                            | 50 |

|          |       | 3.3.1 Stimulator Operation                                                                                                                    | 50 |

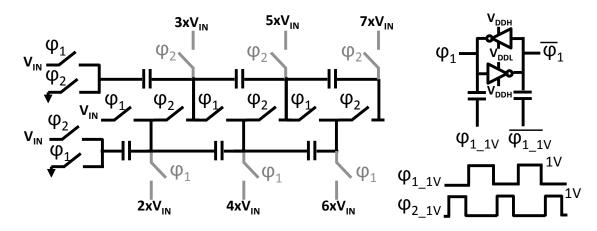

|          |       | 3.3.2 DC-DC Design                                                                                                                            | 52 |

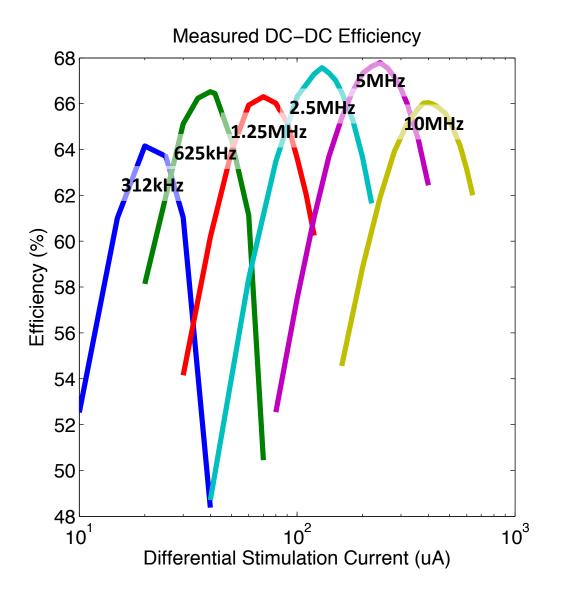

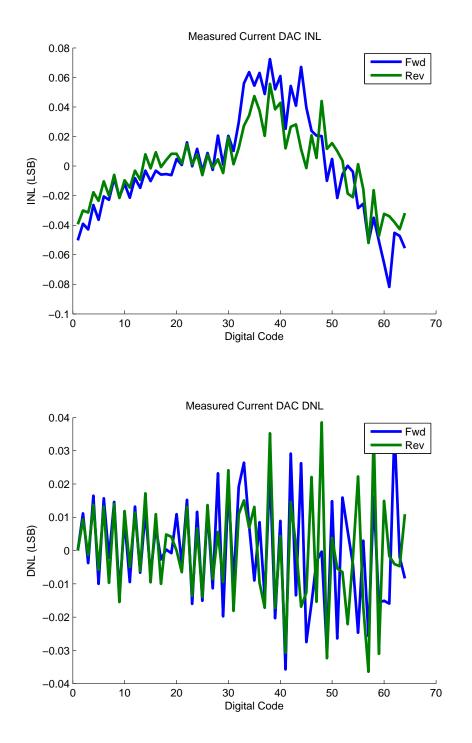

|          |       | 3.3.3 Performance                                                                                                                             | 52 |

|          | 3.4   | In Vivo System Measurements                                                                                                                   | 60 |

|          | 3.5   | Conclusion                                                                                                                                    | 62 |

| <b>4</b> | Con   | clusion                                                                                                                                       | 67 |

|          | 4.1   | Future Work                                                                                                                                   | 69 |

|          |       | 4.1.1 Integration of a Floating Recording Node IC with Electrodes for <i>In</i><br><i>Vivo</i> Studies                                        | 69 |

|          |       | 4.1.2 Design of a Wireless Stimulation Headstage                                                                                              | 69 |

|          |       | 4.1.3 Transcranial Link for a Free Floating BMI Platform                                                                                      | 72 |

|          | 4.2   | Final Thoughts                                                                                                                                | 73 |

| Bi       | bliog | graphy                                                                                                                                        | 76 |

### ii

# List of Figures

| 1.1 | A World Health Organization table of years lost to disability (YLD), summarizing     |     |

|-----|--------------------------------------------------------------------------------------|-----|

|     | the number of healthy years of life lost from various neurological disorders [1].    | 2   |

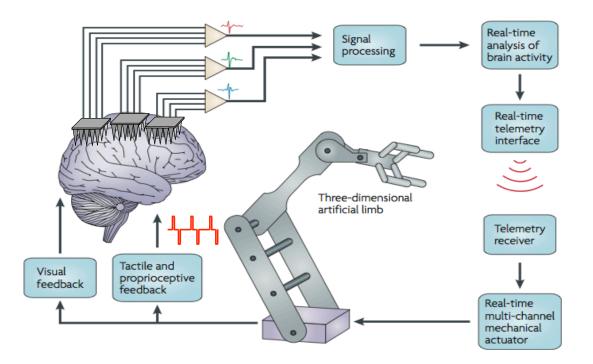

| 1.2 | Conceptual diagram of a closed loop BMI system. Image adapted from [3]               | 3   |

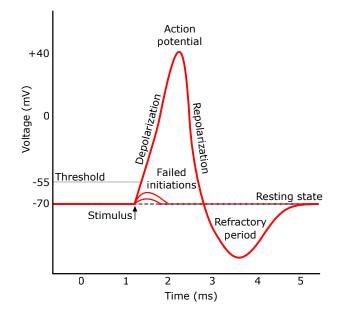

| 1.3 | A typical action potential voltage waveform measured across a neuron's cell mem-     |     |

|     | brane.                                                                               | 4   |

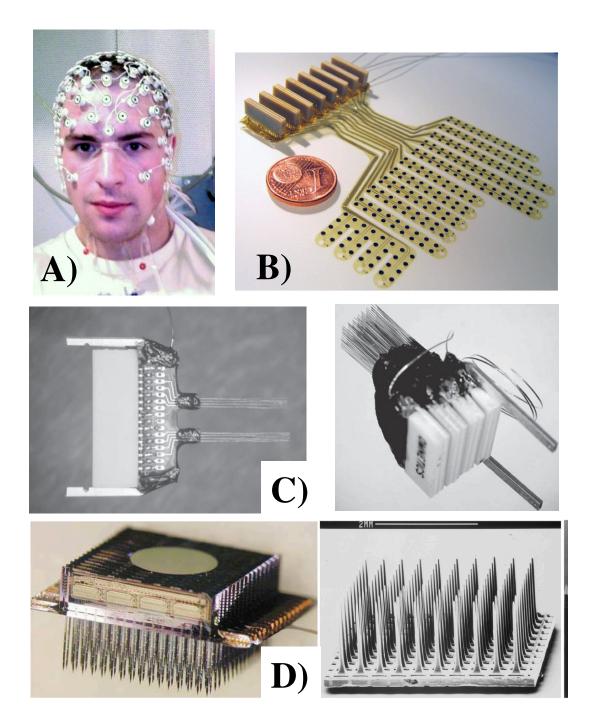

| 1.4 | Examples of various neural recording techniques. A) Shows a patient wearing          |     |

|     | an EEG array during a clinical study, B) Shows a micro machined 256 channel          |     |

|     | ECoG array [5], C) A 16 and 128 channel micro wire array [6], and D) (left) A        |     |

|     | silicon "Michigan" probe array [7] (right) A silicon "Utah" probe array [8].         | 6   |

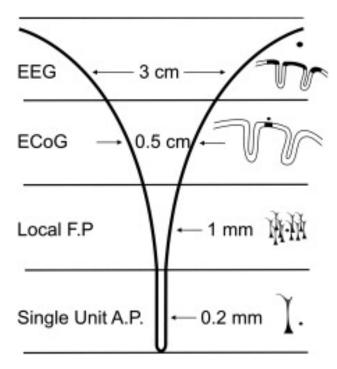

| 1.5 | A comparison of the spatial resolution for different recording modalities. EEG,      |     |

|     | located on the skull, averages neural activity from approximately 3cm of cortical    |     |

|     | area. ECoG, located directly on the cortex, averages neural activity from approx-    |     |

|     | imately 0.5cm of cortical area. While LFP and single unit APs are recorded from      |     |

|     | smaller cortical areas within the brain. [9]                                         | 7   |

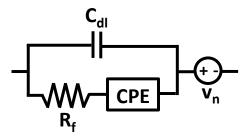

| 1.6 | A lumped element impedance model of the electrode tissue interface. $C_{dl}$ models  |     |

|     | the double layer capacitance, $R_f$ represents Faradaic currents, CPE represents a   |     |

|     | constant phase delay and $v_n$ represents a lumped noise model                       | 8   |

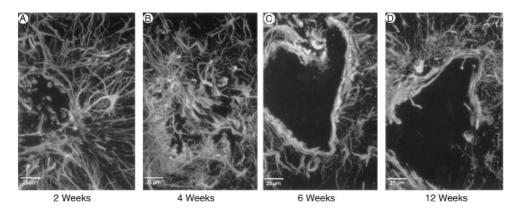

| 1.7 | Timeline for the formation of glial scar tissue around an implanted neural probe     |     |

|     | over a 12 week period, $[28]$ .                                                      | 10  |

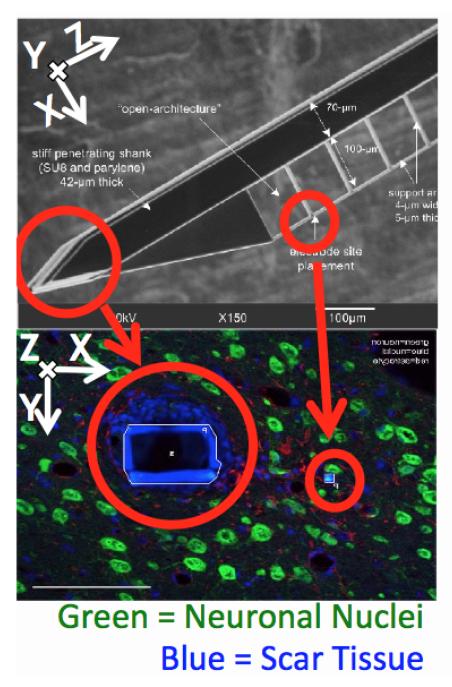

| 1.8 | A reduction in the cross section area of an implant can mitigate an acute biological |     |

|     | reaction. Image is adapted from [31]                                                 | 12  |

| 0.1 |                                                                                      |     |

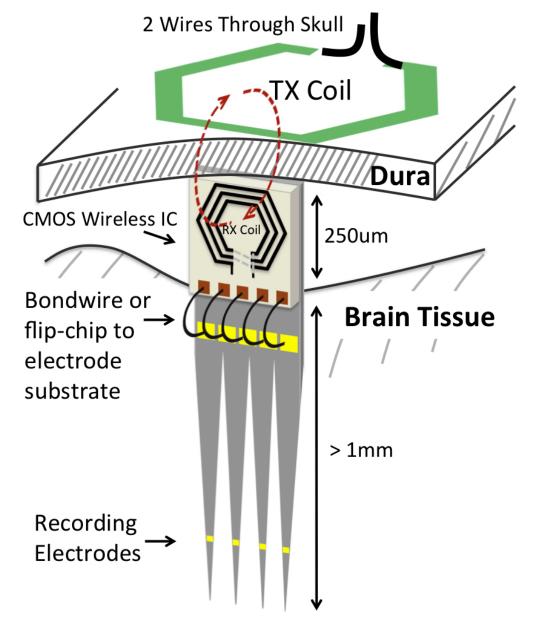

| 2.1 | A conceptual diagram of the implementation of a BMI utilizing the developed          |     |

|     | wireless neural sensor. The sensor free-floats under the dura, while receiving       | 1 / |

| 0.0 | power from and communicating to an interrogator beneath the skull.                   | 14  |

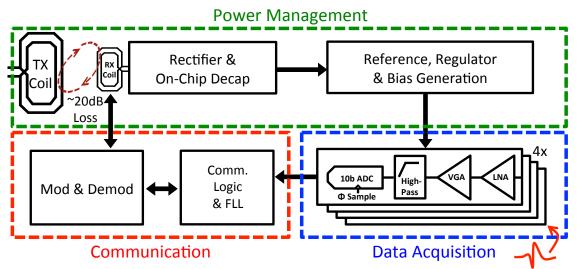

| 2.2 | System diagram, subdivided into three primary circuit blocks: Power manage-          | 15  |

| 0.0 | ment, communication circuitry, and data acquisition.                                 | 15  |

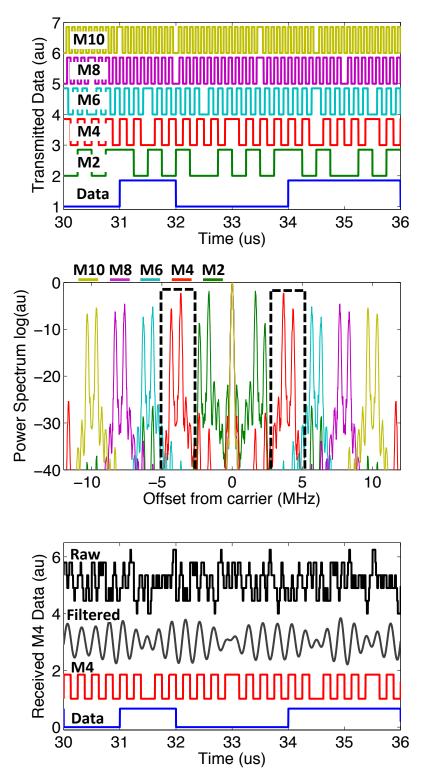

| 2.3 | Theory of a Miller encoded communication scheme for multi-node interrogation.        |     |

|     | Top: Miller encoded waveforms (2,4,6,8,10 MHz) for a data set. Middle: The           |     |

|     | resulting frequency spectrum from 5 nodes communicating simultaneously. Bot-         |     |

|     | tom: The recovered raw waveform before and after bandpass filtering, and the         | 17  |

|     | recovered original transmitted M4 signal and equivalent data                         | 17  |

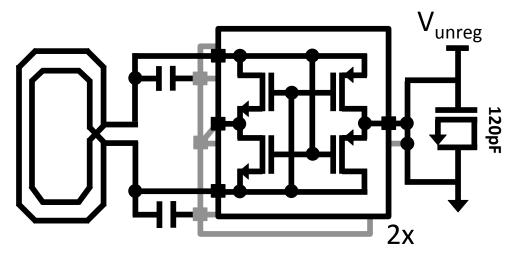

| 2.4  | A high- $R_p$ on-chip coil increases the open circuit voltage and maximizes the effi-<br>ciency of the self-synchronous rectifier. 120 pF of on-chip decoupling capacitance |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | is implemented with thick-oxide native devices.                                                                                                                             | 20 |

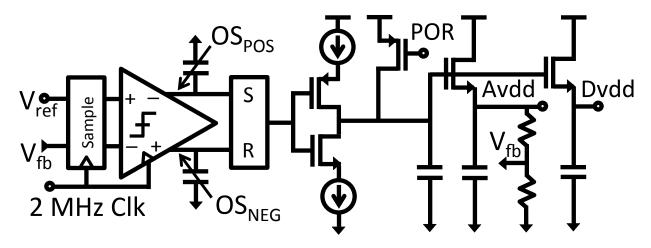

| 2.5  | Discrete-time LDO regulator schematic utilizing a comparator with capacitive                                                                                                |    |

|      | offset cancelation and a charge pump loop filter                                                                                                                            | 20 |

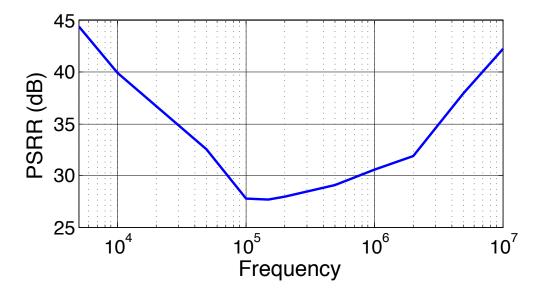

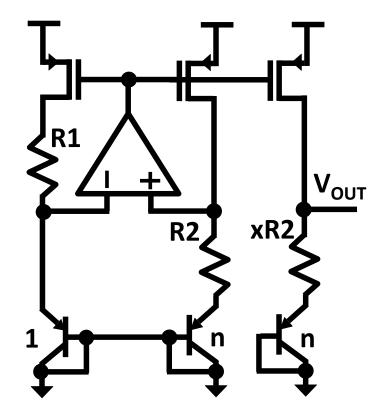

| 2.6  | The measured discrete-time LDO regulator supply rejection across frequency                                                                                                  | 21 |

| 2.7  | A typical bandgap architecture, requiring $V_{DD,min} \approx 1.4$ V                                                                                                        | 22 |

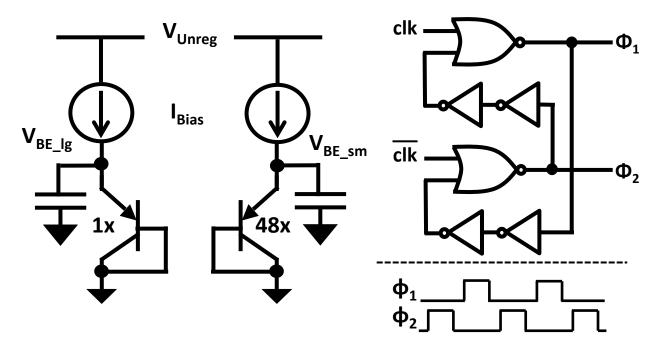

| 2.8  | Schematics for generation of $V_{BE_{lg/sm}}$ and non-overlapping clocks                                                                                                    | 23 |

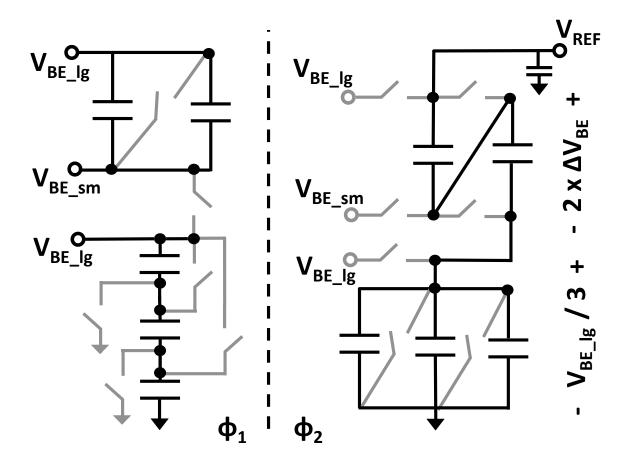

| 2.9  | Schematic of the SC network with a divide/multiply ratio of $3/2$ .                                                                                                         | 25 |

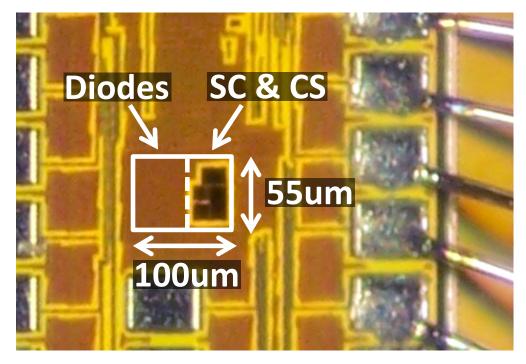

| 2.10 | Die photo of the implemented design $(0.0055 \text{mm}^2 \text{ excluding pads})$                                                                                           | 27 |

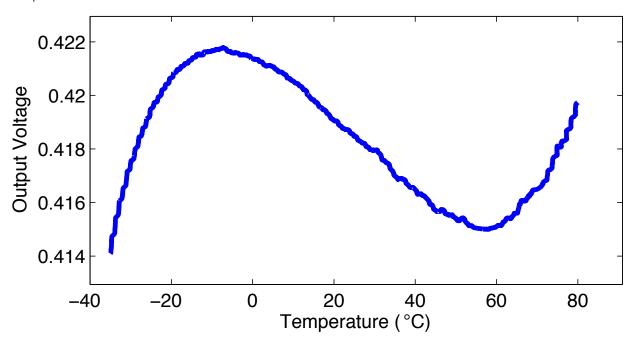

| 2.11 | Measured output voltage versus temperature. The peak variation from from -                                                                                                  |    |

|      | 35°C to 80°C equates to a sensitivity of 160ppm/°C.                                                                                                                         | 28 |

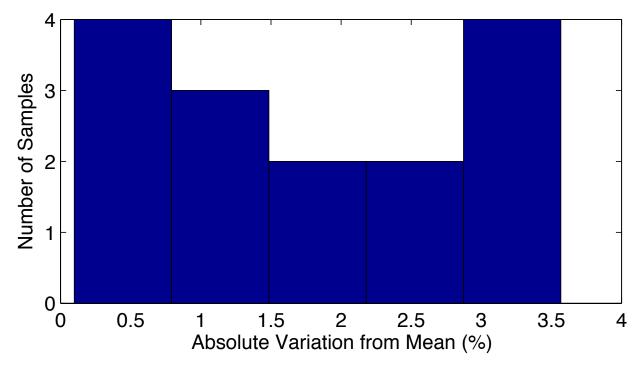

| 2.12 | Histogram of measured absolute output voltage variation from 15 samples, with                                                                                               |    |

|      | a $\sigma$ of 2.2%. The lot average is 423mV                                                                                                                                | 29 |

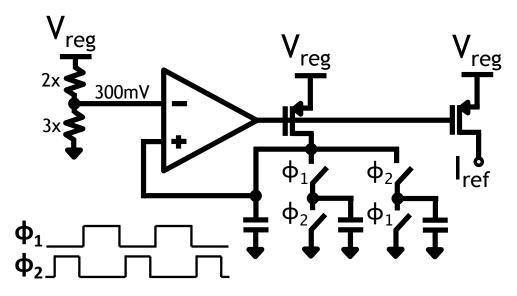

| 2.13 | Switched-capacitor bias current generation schematic, utilizing two-phase non-                                                                                              |    |

|      | overlapping clocks.                                                                                                                                                         | 30 |

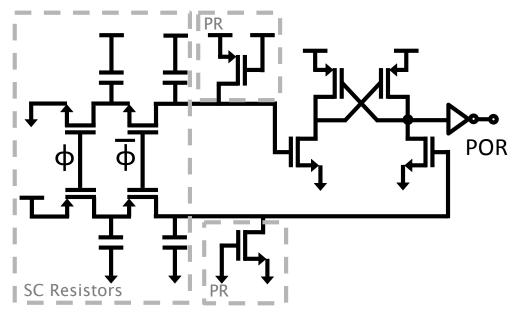

| 2.14 | Power-on reset schematic. Switched-capacitor resistors pull up against pseudo-                                                                                              |    |

|      | resistors, disabling the reset signal after several clock cycles                                                                                                            | 31 |

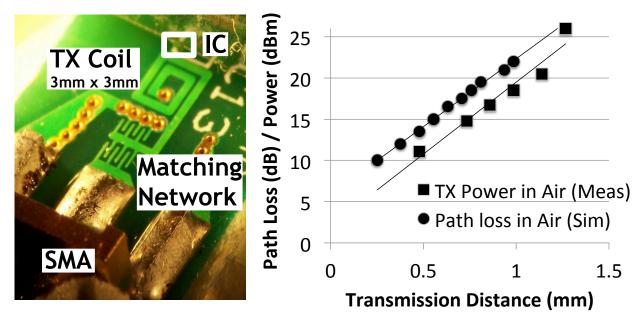

| 2.15 | Left: Setup for wireless operational range testing. The IC is attached to a micro-                                                                                          |    |

|      | manipulator using double-sided tape. Right: Simulated path loss compared to                                                                                                 |    |

|      | the measured minimum TX power required for operation in air                                                                                                                 | 32 |

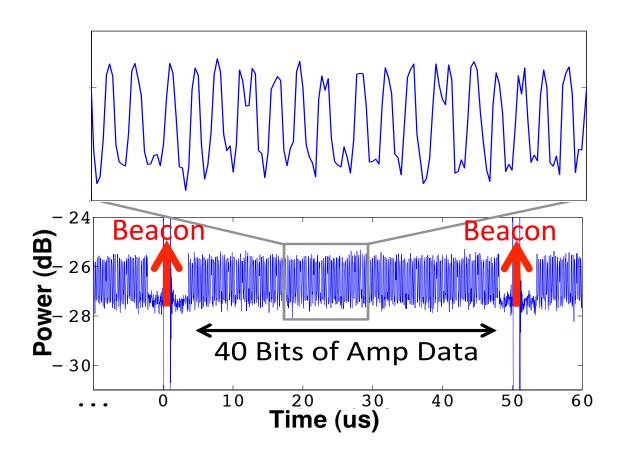

| 2.16 | A wireless packet encoded with Miller modulation. Backscatter communication                                                                                                 |    |

|      | of 40 bits of signal acquisition data is initiated by a pulse from the transmitter                                                                                          |    |

|      | (seen on either side of the packet).                                                                                                                                        | 33 |

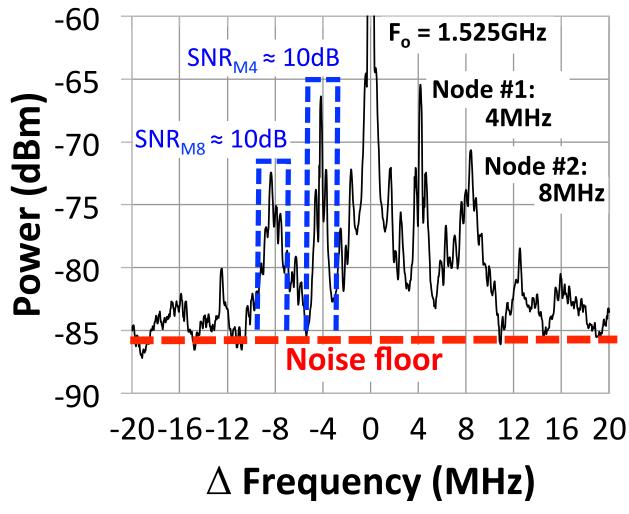

| 2.17 | Frequency spectrum of two wirelessly powered nodes, communicating simultane-                                                                                                |    |

|      | ously with the same interrogator at different sub-carrier frequencies                                                                                                       | 34 |

| 2.18 | The measured time domain waveform after filtering of M4 during a multi-node                                                                                                 |    |

|      | interrogation test. Results are compared to an ideal filtered waveform, and the                                                                                             |    |

|      | equivalent Miller waveform with decoded data is shown.                                                                                                                      | 35 |

| 2.19 |                                                                                                                                                                             | 35 |

| 2.20 | A wirelessly-powered system recording and transmitting a 1.6kHz, $150 \mu V$ sine                                                                                           |    |

|      | wave input from all channels simultaneously                                                                                                                                 | 36 |

| 2.21 | The setup for <i>in vivo</i> recording trials utilized a rat which was implanted with                                                                                       |    |

|      | a microwire array. Our system was die-attached to a PCB to facilitate wireless                                                                                              |    |

|      | powering and signal interfacing. In order to gather long data streams, a FPGA                                                                                               |    |

|      | was used to buffer the on-chip Miller-encoded neural data                                                                                                                   | 37 |

| 2.22 | 1 0 1                                                                                                                                                                       |    |

|      | LFP feedback cancelation high-pass corner was set and measured to be approxi-                                                                                               |    |

|      | mately 500Hz                                                                                                                                                                | 38 |

| 2.23 | Die photo of the full system, showing the input bonding pads, the RX coil and                                                                                               |    |

|      | PGS. The active circuit area is underneath the PGS, and is depicted by an image                                                                                             |    |

|      | of the chip layout.                                                                                                                                                         | 40 |

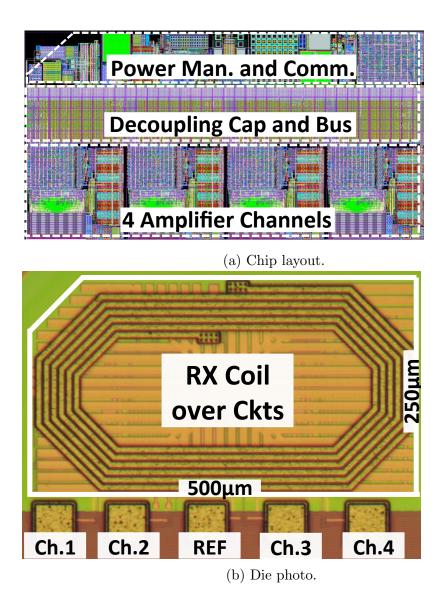

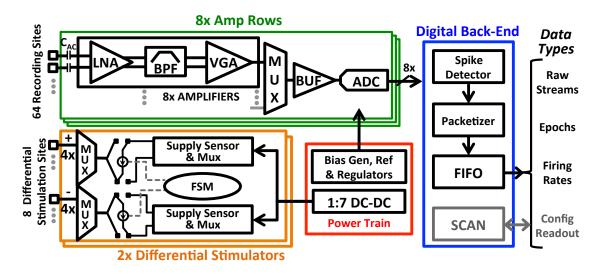

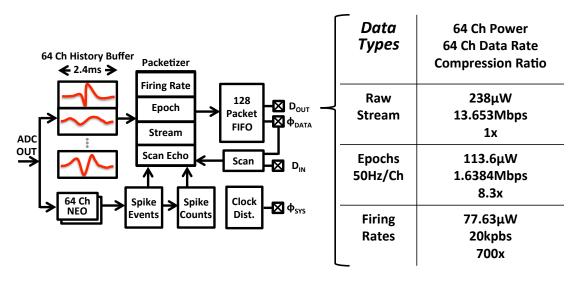

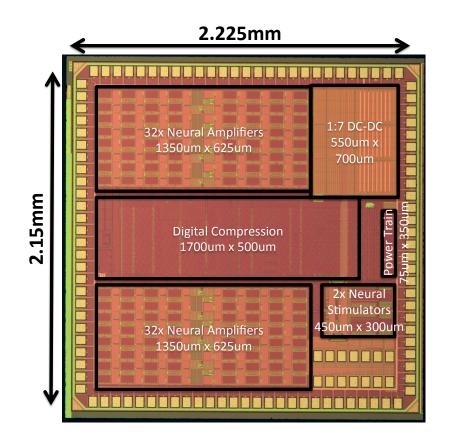

| 3.1  | The system architecture, subdivided into the primary circuit functions: Amplifi-         |    |

|------|------------------------------------------------------------------------------------------|----|

|      | cation, Stimuation, Digital Compression and Power Train.                                 | 42 |

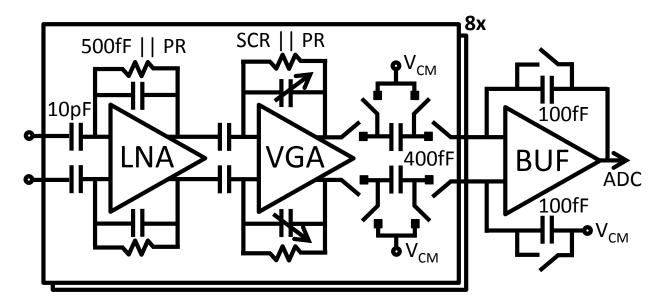

| 3.2  | Amplifier block diagram showing the LNA, VGA and ADC buffer                              | 43 |

| 3.3  | Compression block diagram and the power consumption, data rates, and com-                |    |

|      | pression ratio for different output modes                                                | 43 |

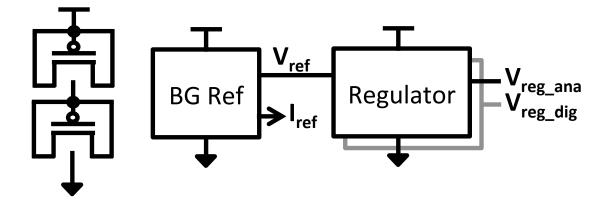

| 3.4  | A simplified block diagram depicting the components of the power management              |    |

|      | sub-system: a supply clamp, band gap reference and two regulators                        | 44 |

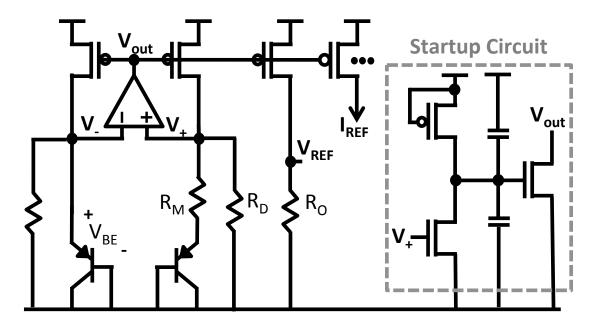

| 3.5  | Schematic of the resistive sub-division band gap reference and startup circuit.          | 45 |

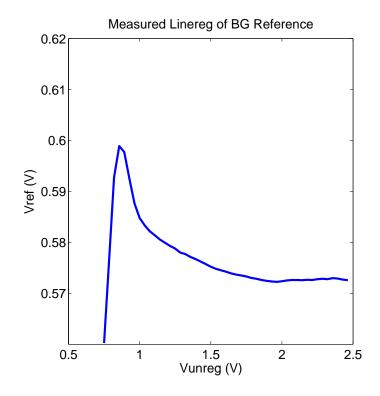

| 3.6  | The measured line regulation of the band gap reference                                   | 46 |

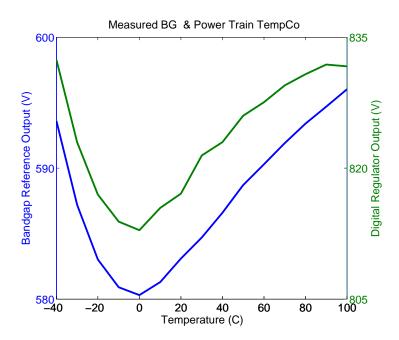

| 3.7  | The measured temperature sensitivity of the band gap reference and digital supply        |    |

|      | voltage. The temperature coefficient is approximately 180ppm/C.                          | 46 |

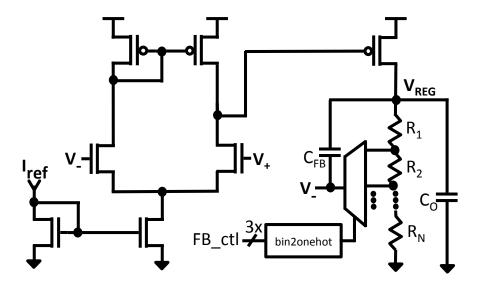

| 3.8  | The schematic of the regulator with a 3b tunable output voltage and output               |    |

|      | compensation.                                                                            | 47 |

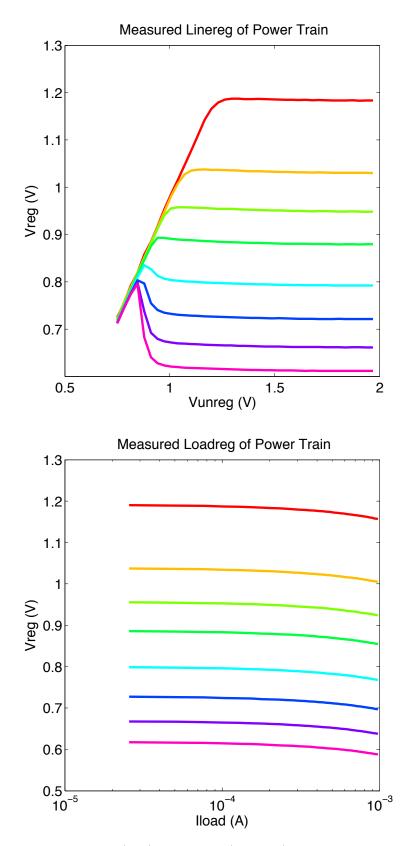

| 3.9  | The measured line (top) and load (bottom) regulation for all 3 bits of output            |    |

|      | tuning                                                                                   | 48 |

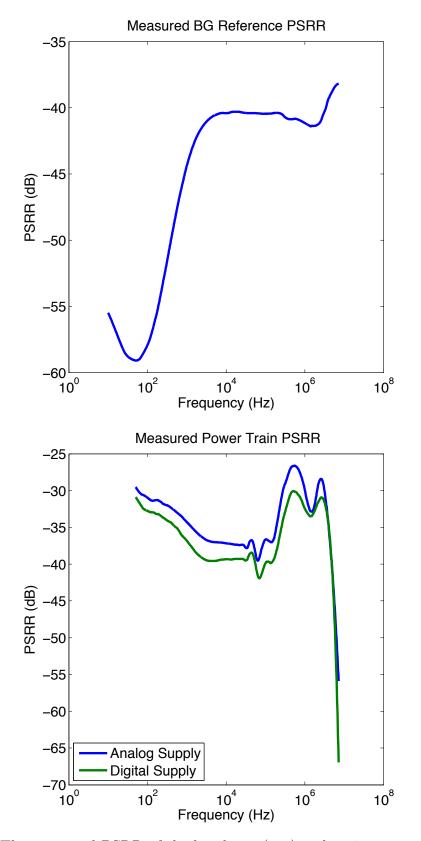

| 3.10 | The measured PSRR of the band gap (top) and entire power train (bottom)                  | 49 |

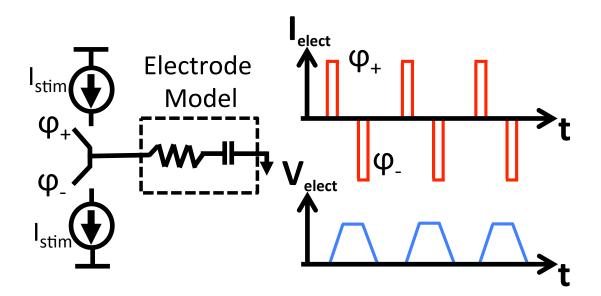

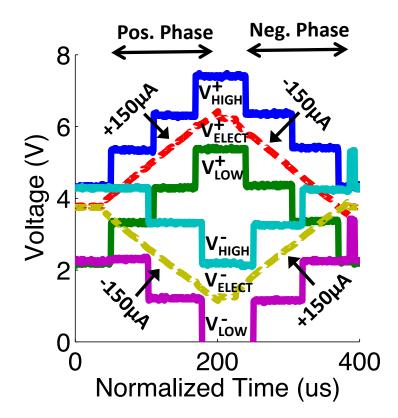

| 3.11 |                                                                                          |    |

|      | ceptual stimulation waveforms.                                                           | 50 |

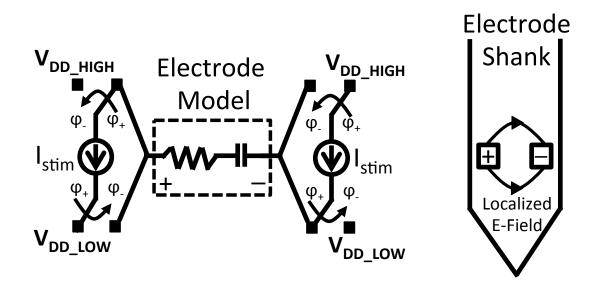

| 3.12 | The proposed differential stimulation topology which utilizes a single current           |    |

|      | source for each electrode. The current source switches between a dynamically ad-         |    |

|      | justable high and low supplies to minimize waster power and maximize recovered           |    |

|      | power respectively. The electrodes are placed adjacently on an electrode shank,          |    |

|      | localizing the electric field and reducing stimulation artifacts on recording channels.  | 51 |

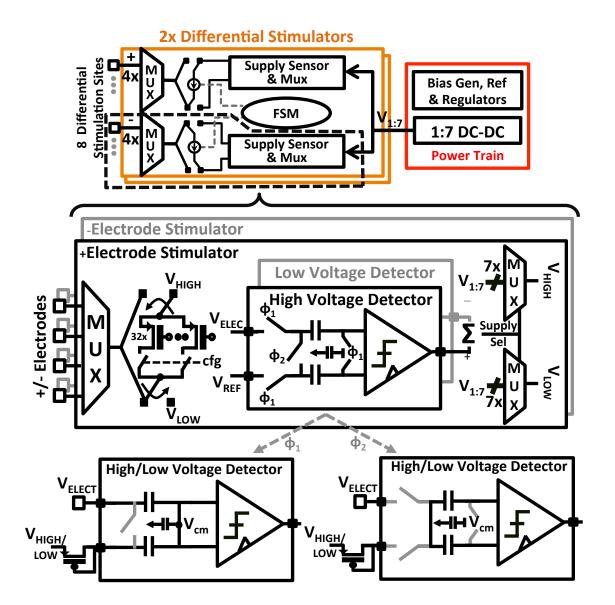

| 3.13 | The stimulator block diagram, illustrating the 6b current source, supply sensor          |    |

|      | and supply mux operation                                                                 | 53 |

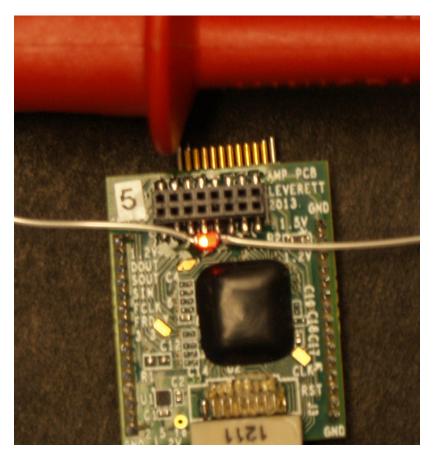

| 3.14 | A photograph of an LED being illuminated by the output of the stimulator from            |    |

|      | the wired head stage                                                                     | 54 |

| 3.15 | The layout of the differential stimulator consumes approximately 150um x 450um           |    |

|      | of area                                                                                  | 54 |

| 3.16 | Schematic of the actively switched, 1:7 switched capacitor DC-DC and schematic           |    |

|      | of the AC coupled level shifters                                                         | 55 |

|      |                                                                                          | 56 |

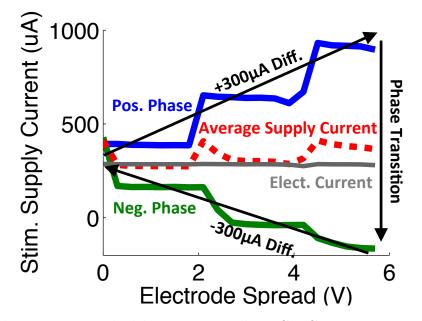

|      | The measured DNL and INL of the 6b binary weighted current DAC                           | 57 |

| 3.19 | The electrode voltage and dynamically switching stimulator supply voltages dur-          |    |

|      | ing a typical stimulation pattern of $300\mu A$ differential current with $150\mu s$ per |    |

|      | phase                                                                                    | 58 |

| 3.20 | The current supplied by $V_{unreg}$ via the DC-DC over one $300\mu A$ (differential)     |    |

|      | stimulation cycle                                                                        | 58 |

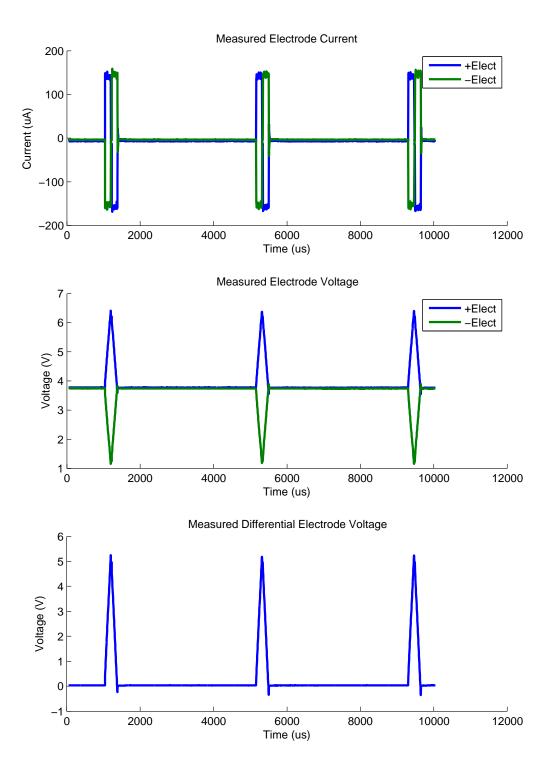

| 3.21 | A train of stimulation current pulses and voltages measured from an electrode            |    |

|      | pair with a 4ms period                                                                   | 59 |

v

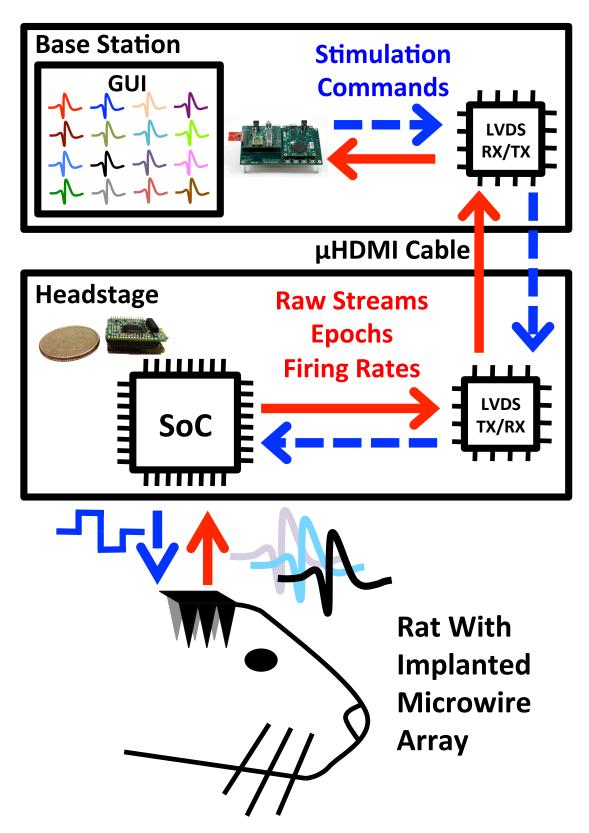

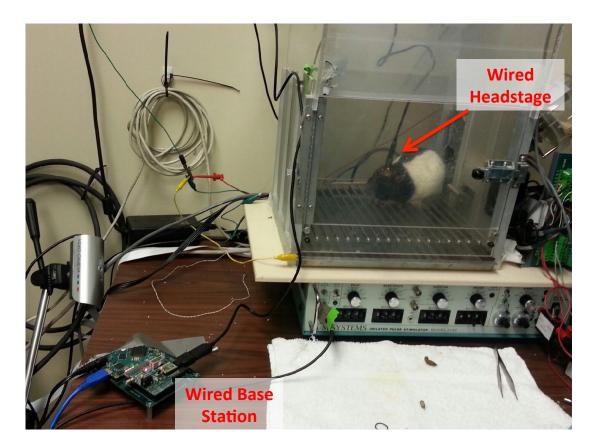

| 3.22 | The <i>in vivo</i> neuromodulation test system is composed of a microwire implanted array, a compact headstage containing the SoC, a base station, and a Graphical                                                                                                                                                                                                                                                                                                                                            |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | User Interface (GUI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61 |

| 3 23 | A photograph of the <i>in vivo</i> measurement setup as depicted in 3.22                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62 |

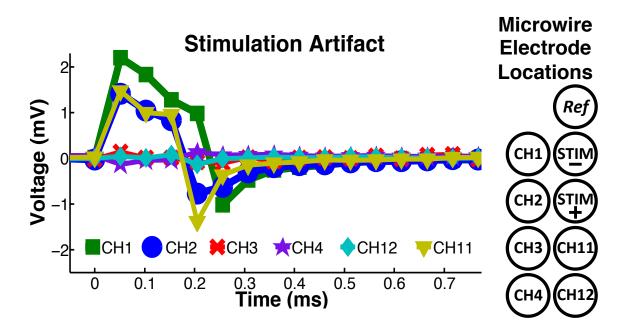

|      | In vivo stimulation artifact measured by neighboring amplifier channels.                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63 |

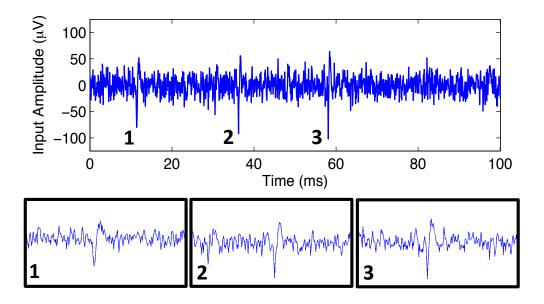

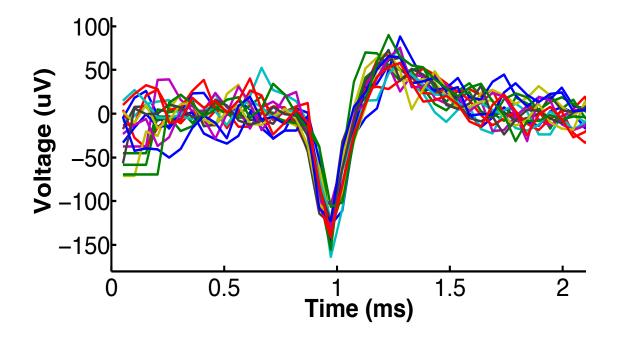

|      | Time-aligned epochs recorded from one channel of <i>in vivo</i> neural data                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63 |

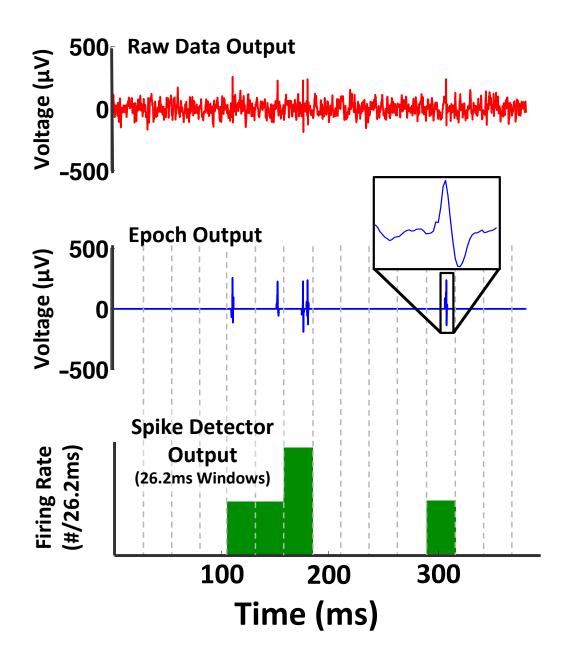

|      | There are three possible digital outputs from the neuromodulation IC with vary-<br>ing levels of compression as shown for a typical <i>in vivo</i> recording. Raw stream-<br>ing data (top) has no compression, this consumes 13.653 Mbps for 64 channels.<br>Epoch data (middle) only sends a 2 ms window of data around a detected spike<br>event, consuming 1.6384 Mbps (@50Hz firing rate) for 64 channels. Firing rates<br>(bottom) only sends the count of detected spike events in a 26.2ms window and |    |

|      | consumes 20kbps for 64 channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64 |

| 3.27 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | and dimensions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66 |

| 3.28 | System summary and comparison table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66 |

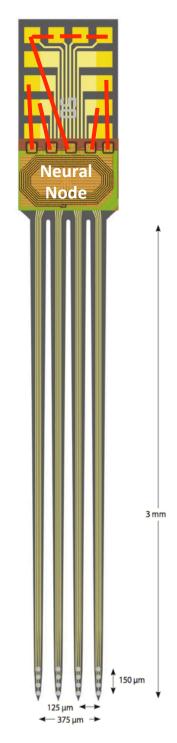

| 4.1  | An implantable neural recording probe offered by NeuroNexus, the head of the probe is approximate 450µm wide. A die photo of the neural node is oriented in the approximate location for die attach and a potential bonding diagram is shown in red, allowing for 1 recording per shank. A large area reference electrode through the is created by stitch bonding multiple recording sites.                                                                                                                  | 70 |

| 4.2  | Example post processing steps for directly etching an active neural probe from a                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | $CMOS wafer, [19]. \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                      | 71 |

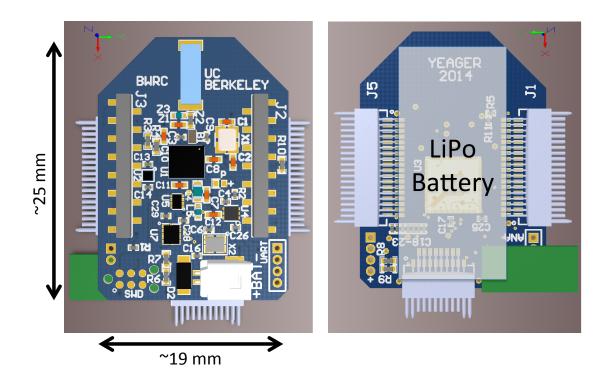

| 4.3  | A wireless headstage designed by Jaclyn Leverett and Daniel Yeager, measuring                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | 19mm x 25mm with 64 channels of neural recording and 8 channels of stimulation.                                                                                                                                                                                                                                                                                                                                                                                                                               | 73 |

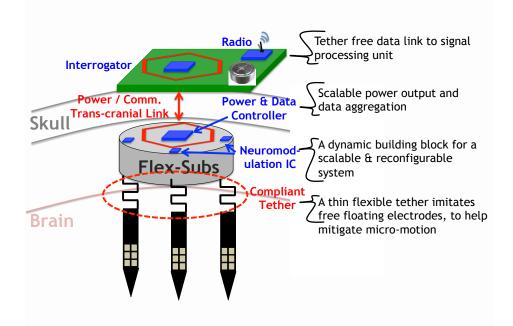

| 4.4  | Conceptual diagram of a scalable platform with compliant tethers communicating                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | to a wireless head stage through a trans-cranial link                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74 |

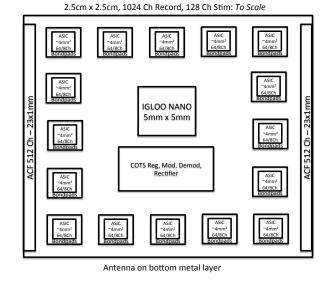

| 4.5  | A floor plan diagram showing the size and layout of a 1024 channel implantable                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | platform, with a total size of 2.5cm x 2.5cm                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75 |

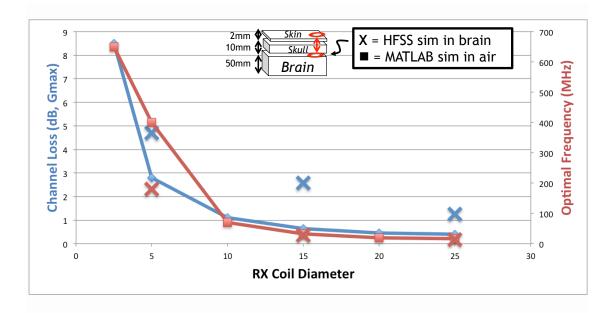

| 4.6  | The channel loss and optimal frequency as a function of the RX coil diameter.<br>For a 1024 channel platform, the maximum coil diameter is 25mm, resulting in                                                                                                                                                                                                                                                                                                                                                 |    |

|      | an optimal frequency of approximately 13.56MHz and an estimated channel loss                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | of 1-2dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75 |

# List of Tables

| 1.1 | Typical neural recording methods and their resulting measurable signal bands.       | 4  |

|-----|-------------------------------------------------------------------------------------|----|

| 1.2 | Typical Neural Recording Noise Components                                           | 9  |

| 2.1 | Table of possible reference voltages and their required multiply and divide factors | 24 |

| 2.2 | Table of output sensitivity to mismatch, process, and voltage                       | 26 |

| 2.3 | Comparison of published (measured) Bandgap Reference performance                    | 28 |

| 2.4 | Summary of System Performance                                                       | 39 |

| 2.5 | Comparison of neural recording systems with wireless telemertry                     | 39 |

| 4.1 | A comparison of prior work on neural recording and stimulation wireless head        |    |

|     | stages.                                                                             | 72 |

### Acknowledgments

I would like to start by thanking my adviser, Professor Jan Rabaey for his wisdom, guidance, encouragement and advice throughout graduate school. I could not have wished for a better experience at UC Berkeley or advisor.

I would like to thank Professor Elad Alon for countless insightful discussions and his incredible teaching. Elad's seemingly endless knowledge and his ability to quickly understand and dissect complex problems continually amazes me.

I would like to thank Professor Jose Carmena for collaborating on many projects and serving on the committee for my qualifying exam. I would also like to thank Professor Paul Wright for serving on both my dissertation and qualifying exam committees and reading this thesis.

I would like to thank Dan Yeager for being a great friend, classmate and research partner. Working with a close friend made this journey and the many long nights at BWRC much more pleasant. I would also like to thank Nathan Narevsky and Jackie Leverett for their friendship, help and contributions to the systems presented in this thesis.

Last by not least, I would like to thank my parents for their infinite love and support throughout my undergraduate and graduate studies.

# Chapter 1

# Introduction to Brain Machine Interfaces

The burden of neurological disorders has a substantial global impact on society. In 2015, for every 100,000 individuals, 1186.3 years of healthy life will be lost due to neurological disorders [1], Figure 1.1. In total, neurological disorders make up 14.23% of all healthy years of life lost due to disability, resulting in approximately 85 million years of life lost world wide at the time of this writing (2014). In addition to the emotional and physical pain inflicted on patients and families, this massive loss of life has incalculable economic consequences, both direct (cost of patient care) and indirect (loss of human productivity). Over the past few decades there has been a dramatic increase in the use of electronics and medical implants to combat disorders for humans. Some of the most common applications include artificial pacemakers and cochlear implants. Until recently, many neurological disorders have not seen the benefits of technological advances in medicine, however, research has now shown that the quality of life of patients can be improved through a direct interface with the brain.

Brain Machine Interfaces (BMIs) create a direct interface between the human brain and a machine. This enables stimulation of brain regions to mitigate the effect of some neurological conditions (ex. Parkinsons) or allows an alternate method of interacting with the physical world. For example, a patient with spinal cord damage could use a BMI to perform voluntary motor actions using an artificial actuator in virtually the same way that we see, walk or grab an object with our own natural limbs.

The vision of restoring motor functionality to handicapped patients using BMIs has existed for many decades. In 1972 the first cochlear implants became commercially available, which paved the way for BMIs as a treatment for patients suffering from severe motor impairment such as amyotrophic lateral sclerosis (ALS), spinal cord injury, stroke, and cerebral palsy. BMI research began in 1970 at UCLA; however, it wasnt until 1999 when the first experimental demonstration showed neurons could be used to directly control a robotic arm [2]. The use of BMI to improve the quality of life for these individuals is promising, however, due to the a high level of invasiveness and risk BMI primarily remains a research field.

The modern vision of a closed loop BMI and the different components required for im-

| Cause category/sequelae                      | 2005                            |                                | 2015                            |                                | 2030                            |                                |

|----------------------------------------------|---------------------------------|--------------------------------|---------------------------------|--------------------------------|---------------------------------|--------------------------------|

|                                              | YLDs<br>(100 000<br>population) | Percentage<br>of total<br>YLDs | YLDs<br>(100 000<br>population) | Percentage<br>of total<br>YLDs | YLDs<br>(100 000<br>population) | Percentage<br>of total<br>YLDs |

| Epilepsy                                     | 64.7                            | 0.73                           | 60.9                            | 0.73                           | 55.6                            | 0.71                           |

| Alzheimer and other dementias                | 147.4                           | 1.66                           | 165.4                           | 1.98                           | 203.9                           | 2.60                           |

| Parkinson's disease                          | 17.7                            | 0.20                           | 17.3                            | 0.21                           | 17.1                            | 0.22                           |

| Multiple sclerosis                           | 20                              | 0.23                           | 19.3                            | 0.23                           | 18.4                            | 0.23                           |

| Migraine                                     | 118.9                           | 1.34                           | 108.9                           | 1.31                           | 96                              | 1.22                           |

| Cerebrovascular disease                      | 176.8                           | 2.00                           | 174.9                           | 2.10                           | 177.8                           | 2.27                           |

| Neuroinfections                              | 98.4                            | 1.11                           | 71.8                            | 0.86                           | 45.6                            | 0.58                           |

| Nutritional deficiencies and<br>neuropathies | 194.9                           | 2.20                           | 174.3                           | 2.09                           | 133.9                           | 1.71                           |

| Neurological injuries                        | 425.4                           | 4.80                           | 393.5                           | 4.72                           | 360.8                           | 4.60                           |

| Total                                        | 1264.2                          | 14.27                          | 1186.3                          | 14.23                          | 1109.1                          | 14.14                          |

Figure 1.1: A World Health Organization table of years lost to disability (YLD), summarizing the number of healthy years of life lost from various neurological disorders [1].

plementation is shown in Figure 1.2. This figure depicts a large scale array of electrodes implanted in the brain used for both sensing and feedback. Neural signals are sensed and amplified for signal processing, where the information of interest is extracted. This information is analyzed in real-time, resulting in the implementation of an action (such as movement in a direction), which is relayed through a wireless interface to a multi-channel mechanical actuator. The actuators could control a limb with several degrees of freedom to perform the desired action. Sensors on the limb (e.g. pressure sensors) are used to provide feedback (e.g. tactile sensation) via electrical stimulation to the brain, resulting in a fully closed loop system.

The remainder of the chapter will cover the concepts and technological challenges in realizing a closed loop BMI for humans. Section 1.1 gives a brief overview of the different types of signals which can be measured in the brain. Section 1.2 presents the various types of recording methods and their advantages or disadvantages. Section 1.3 discusses the interface between the implanted electrode and the surrounding brain tissue, and how to model the impedance and noise. Finally, Section 1.4 examines the cell and tissue reaction to an implant and the gives an overview of prior work on mitigating this biological response.

# 1.1 Signals of the Brain

The neuron is the central element of the nervous system and transmits information through electrical and chemical signals. Like many other cells, neurons maintain a voltage gradient across their membranes by separating ions (e.g. sodium, potassium, chloride and calcium) using ion pumps. Unlike other cells, the membrane of a neuron is electrically active, allowing control of the ion gradients using voltage-gated ion channels, which are activated by

Figure 1.2: Conceptual diagram of a closed loop BMI system. Image adapted from [3].

changes in membrane potential, and chemically-gated ion channels, which are activated by interactions with chemicals in the extracellular fluid.

Neural function is enabled by the communication of neurons through the synaptic process. Typically a neuron's membrane potential rests around -65mV to -70mV, however, synaptic inputs may cause the potential to rise or fall. Once the potential surpasses a threshold, an action potential (AP) is triggered, resulting in rapid depolarization followed by repolarization. Figure 1.3 depicts the typical voltage waveform across a neuron membrane during an action potential, which typically last on the order of 1 ms.

It is possible to measure the action potential voltage in vivo by using implanted microelectrodes. These electrodes can detect the membrane currents of neurons in the vicinity of the electrode area through conductive brain tissue. Brain tissue can be modeled as linear, resistive and homogeneous, therefore, the numerous signal sources in the corresponding area are assumed to combine linearly [4]. Consequently, using different size electrodes or placing the electrodes in different physiological locations, results in different measured signals. Some of the typical measured signals are summarized in Table 1.1. Low frequency signals are typically the superposition of neural activity over a large area of the brain, resulting in the average signal for a large population of neurons. Depending on the region of the brain, these

Figure 1.3: A typical action potential voltage waveform measured across a neuron's cell membrane.

| Typical Recording Method | Signal Band           | Frequency Range (Hz) |

|--------------------------|-----------------------|----------------------|

|                          | Delta                 | 4                    |

|                          | Theta                 | 4-7                  |

| FEC                      | Mu                    | 8-12                 |

| EEG                      | Alpha                 | 8-15                 |

|                          | Beta                  | 16-31                |

|                          | Gamma                 | 31-100               |

| ECoG                     | Local Field Potential | <300                 |

| Micro-electrode array    | Single & Multi-Unit   | 300-10,000           |

Table 1.1: Typical neural recording methods and their resulting measurable signal bands.

signals have been grouped based on the frequency of the signal, such as the Delta, Theta, Alpha, Mu, Beta and Gamma bands. Averaging neural activity over a smaller region gives rise to signals typically less than 300Hz, and has been named the Local Field Potential (LFP). Finally, the limit of recording resolution is measuring the activity of single neurons adjacent to a recording electrode (Single & Multi-Unit), which can have frequency components up to 10kHz.

# **1.2** Neural Recording Techniques

There are various commonly used neural recording techniques, which can be categorized as invasive or non-invasive. The two most common non-invasive recording techniques are Electroencephalography (EEG) and functional Magnetic Resonance Imaging (fMRI). EEG, shown in Figure 1.4, measures the changing electric field over time due to the fluctuating ion concentrations during neural activity (action potentials) using electrodes on the outside of the skull, approximately 2cm above the cortex. Consequently, the electrical field (Efield) generated by a single action potential is too weak to be detected through the very lossy channel (brain tissue, skull, skin etc.). Therefore, EEG is only capable of detecting the superposition of the E-fields from the synchronous activity of many neurons across an approximate 3 cm spatial extent, Figure 1.5.

fMRI is a type of MRI that measures changing blood flow related to neural activity in the brain. This imaging technique allows data to be gathered from all regions of the brain (unlike EEG, which is limited to the cortical surface), and has high spatial resolution (down to 1mm). However, fMRI has extremely poor temporal resolution, the Blood-oxygenlevel dependence (BOLD) response takes over a second to become detectable. In addition, fMRI requires large machines which make it impractical for any mobile application. While fMRI and EEG are useful for specific applications in neural engineering, currently they do not offer both the spatial and temporal resolution necessary to control robotic prosthesis. Furthermore, neither fMRI or EEG is capable of closed loop BMI control systems using stimulation. In order to achieve the sensing resolution required to seamlessly operate a BMI and the ability to provide feedback, invasive techniques are required.

Invasive BMI techniques enable recordings over smaller cortical areas or the direct recording of action potentials (APs) from single neurons (single units) and small groups (multi-unit) of neurons. Invasive BMIs can detect firing patterns of neurons during the execution of specific and intricate motor functions. These patterns can vary greatly over time and from neuron to neuron, however, averaging across many trials yields fairly consistent patterns. There are several methods of invasive neural recording: intracranial EEG (iEEG), Electrocorticography (ECoG) and microelectrode arrays. Larger recording devices such as ECoG (Figure 1.4) or iEEG, have electrode spacing on the order of 1mm to 1cm and are placed on the surface of the brain. These devices sit directly above the cortex and average neural activity over an approximate 0.5cm range (Figre 1.5) and, therefore, are limited to detecting only Local Field Potentials (LFPs).

There are two types of microelectrode arrays: microwire and silicon micro machined arrays, shown in Figure 1.4. Micro wire arrays are the most frequently used in BMI research; they have only one recording location (at the tip of each wire) and are capable of recording deep in the cortex (up to 5mm). Silicon based probes are physically larger than the smallest microwire arrays but can allow multiple recording sites along the shank. The most common silicon probes are the Utah and the Michigan probes, both of which are manufactured on a silicon substrate using micro electromechanical mechanical systems (MEMS) processing

Figure 1.4: Examples of various neural recording techniques. A) Shows a patient wearing an EEG array during a clinical study, B) Shows a micro machined 256 channel ECoG array [5], C) A 16 and 128 channel micro wire array [6], and D) (left) A silicon "Michigan" probe array [7] (right) A silicon "Utah" probe array [8].

Figure 1.5: A comparison of the spatial resolution for different recording modalities. EEG, located on the skull, averages neural activity from approximately 3cm of cortical area. ECoG, located directly on the cortex, averages neural activity from approximately 0.5cm of cortical area. While LFP and single unit APs are recorded from smaller cortical areas within the brain. [9]

techniques. The Utah array is most similar to the microwire arrays, and only has one recording site at its tip. The Michigan probe has several electrodes positioned along the shank, allowing for recordings at multiple cortical depths.

To date, the only neural recording technique which has successfully demonstrated the control of a robotic prosthetic limb is the direct recording of APs using micro-electrode arrays. Non-invasive methods of sensing brain activity (ex. fMRI or EEG) lack the spatial or temporal resolution. Some research suggests (e.g. [10]) future neuroprosthetic devices could be controlled by ECoG or hybrid sensing solutions, electrodes implanted into the brain are required for stimulation in a closed loop BMI system. Although microelectrode arrays are very effective at providing high spatial and temporal resolution of neural activity, the recording SNR gradually decreases over months to years, eventually rendering the recording site useless. Obtaining a stable, long-term recording of large neurons from a large population of neurons across the brain is one of the key challenges faced by BMI researchers [11].

Figure 1.6: A lumped element impedance model of the electrode tissue interface.  $C_{dl}$  models the double layer capacitance,  $R_f$  represents Faradaic currents, CPE represents a constant phase delay and  $v_n$  represents a lumped noise model.

# **1.3** Electrode-Tissue Interface Model

Providing fine control of robotic prosthesis requires a large number of recording sites, and designing a system which doesn't physically constrain or burden a patient requires a high level of integration. These design constraints, coupled with CMOS scaling and other performance improvements have lead to an interest by the IC design community in the field of neuroscience and BMI. In the past decade there has been a large amount of work on integrated neural recording ICs, for example [12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25]. These ICs are intended to interface directly with recording electrodes, therefore, modeling the eletrode-tissue interface and noise sources properly is critical to achieving the desired *in vivo* performance.

The impedance of the electrode tissue interface can be modeled using lump elements as shown in Figure 1.6. The capacitance,  $C_{dl}$ , models the double layer capacitance formed by the interface boundary of the conductive electrode and the brain tissue. The resistance,  $R_f$ , models the resistance due to Faradaic current generated through redox reactions at the electrode. Lastly, the constant phase element (CPE) models the signal phase shift resulting from ion diffusion limitations, electrode surface morphologies, and other non-idealities [4]. The voltage source,  $v_n$ , represents a lumped element noise source due to both electrical and biological sources other than the signal of interest.

There are two natural sources of cortical recording noise: thermal and biological. Thermal noise is generated by the recording electrode and tissue interface. Biological noise between 500Hz to 5kHz arises from asynchronous neural activity in close proximity to the recording site and is outside of the LFP band. Prior work has modeled thermal and biological noise during cortical recording using silicon microelectrodes and found that for a 450Hz-10kHz recording bandwidth, the recording noise floor is approximately  $13.5\mu$ V (based on Section 4.2 and Table I from [26]). The total recording and amplifier input referred noise is equal to the sum of their variances, shown in Eqn. 1.1. With an amplifier input referred noise of  $6.5\mu$ V, the total estimated recording input referred noise,  $\sigma_{Total}$ , is approximately  $15\mu$ V. Many neural amplifiers target noise floors as low as 1-3 $\mu$ V (ex. [16, 17, 27]), significantly

| Signal Component           | Typical Amplitude    |

|----------------------------|----------------------|

| Thermal & Biological Noise | $13.5 \mu V$ [26]    |

| Amplifier Noise            | 1.5 - 10µV           |

| Total Noise                | $13.58 - 16.8 \mu V$ |

Table 1.2:

Typical Neural Recording Noise Components

below this recording noise floor, which results in wasted power. Table 1.2 summarizes typical Thermal and Biological noise, amplifier noise and the total overall recording noise.

$$\sigma_{Total} = \sqrt{\sigma_{Amp}^2 + \sigma_{Therm}^2 + \sigma_{Bio}^2} \tag{1.1}$$

An amplifier design can modulate the power spent in the low noise amplifier (LNA) and subsequent amplifiers to set the input referred noise. As the power of the analog front end increases the power overhead of the analog to digital converter (ADC) and digital logic will constitute a lower fraction of the total system power, and the noise efficiency of the entire system will improve. However, this methodology should be used with caution as eventually increasing the amplifier power results in diminishing returns in the overall recorded noise, despite improvements in the amplifier noise performance.

There are several factors which effect the length of time that a chronic neural recording site can remain active. The initial recording sensitivity and selectivity is determined by the proximity of the electrode to the neuron of interest and the electrode size, which sets the baseline signal to noise ratio (SNR) of the recording. The recording stability determines the rate at which the SNR of the targeted neuron changes over time. The stability can be affected by degeneration, damage, or morphological changes to the neuron. In addition, a reactive biological response from implantation causes changes in the surrounding tissue properties and results in modifications of the lumped elements in the ETI model [4]. Understanding, and mitigating this biological response to implanted electrodes is one of the critical challenges to achieving a long term recording interface with the human brain.

## **1.4** Biological Response of a Neural Implant

The implantation of micro-electrode arrays to record APs causes scar tissue formation, severely degrading the recording signal-to-noise ratio (SNR) over time. The scar tissue effectively isolates the electrodes from the signal source they are trying to detect (the neurons), rendering them useless. Even after the acute inflammatory response declines, there is a chronic increase in the observed number of glial cells around the foreign object, which causes the formation of a glial sheath, as shown in Figure 1.7. Studies have shown that the glial scarring process is similar to the fibrotic encapsulation reaction that occurs with a foreign body in soft tissue areas of the body [28]. There are several different types of cell

Figure 1.7: Timeline for the formation of glial scar tissue around an implanted neural probe over a 12 week period, [28].

involved in the biological response to foreign objects implanted in the brain, but microglia and astrocytes are the two which are central to the brains response to injury [29].

Microglia primarily act as cytotoxic cells that kill pathogenic organisms, and remain inactive until activated by injury mediated mechanisms. Upon activation, they begin to proliferate, become more compact, phagocytose foreign material, and upregulate the production of lytic enzymes to aid in foreign body degradation [29]. Additionally, since microglia are cytotoxic cells, they can produce neurotoxic factors, which can lead to neuronal death surrounding an activation site.

Astrocytes make up the majority of glial cells in the central nervous system and have many cellular extensions which envelope synapses made by neurons. They provide growth cues to neurons during central nervous system development, mechanically support the mature neuronal circuits, help control the chemical environment of the neurons, buffer the neurotransmitters and ions released during neuronal signaling, and can even modulate the firing activity of neurons [29]. During an injury, astrocytes enlarge in an activation process, transform into a reactive phenotype, and migrate toward the foreign body. Upon activation, astrocytes propagate a foreign body alert in the form of Ca2+ waves.

Reactive astrocytes are the major component of scaring in the central nervous system, and their ability to migrate and communicate to each other via Ca2+ waves ensures that the foreign body is encapsulated long term. Once an implanted electrode is encapsulated, the effective recording impedance to neighboring neurons increases significantly, making the signal undetectable. This process takes several weeks or months depending on the implanted subject. An example timeline of this effect is shown in Figure 1.7.

Improving the reliability of AP sensing using microelectrode arrays has been seen as a challenging long-term goal achievable only by preventing or permanently reducing the biological response to an implant. Prior work (e.g. [30], [31]) investigated the effect of size, shape, texture and insertion method on glial scar formation. Figure 1.8 shows a reduction in the acute reaction of an implant due to a smaller cross sectional area of an electrode site compared to the insertion shank. However, glial staining revealed that although there were minor temporal differences (on the order of 13 weeks) in the time course of the scarring, at 6 and 12 weeks post-implantation the tissue response to all of these electrodes was essentially identical. Other work investigated bioactive coatings/films containing anti-inflamatory compounds, adhesion promotors or growth proteins with limited success ([32], [33], [34]).

To date, prior work demonstrated improvement in the acute reaction, but has been unsuccessful in preventing chronic scaring. Recording sites can remain active for up to several years [35, 36, 37], and it is hypothesized that they eventually fail after "micro-motion" causes continued aggravation. Micro-motion is the independent movement of the brain with respect to the electrode array, which causes agitation to the surrounding tissue. Studies indicate that reducing or eliminating the effects of micro-motion may be the key to improving implant longevity [38]. In order to mitigate micro-motion the wired interface cables through the skull that connect the implant to recording racks must be eliminated. This requires replacing the large bulky electronics with a recording solution directly integrated on an implanted array and utilizing a wireless link to transfer power and data through the skull. Furthermore, this integrated solution must be small and compliant, such that it can move freely with the brain.

The remainder of this thesis will focus on the use of low power integrated-circuit (IC) techniques to design System-on-Chips (SoCs) to enable high density, long-term recording interfaces with the human brain by addressing the challenges of recording scale and micro motion. Chapter 2 presents the design of the smallest wireless neural sensor reported to date, which free-floats in the brain to improve recording longevity. Chapter 3 presents the highest complexity per-area neuromodulation SoC, combining neural recording, compression and stimulation to perform closed loop BMI integrated in a single IC. Finally, Chapter 4 will summarize the contributions of this thesis and discuss future work.

Figure 1.8: A reduction in the cross section area of an implant can mitigate an acute biological reaction. Image is is adapted from [31].

# Chapter 2

# Design of A Fully-Integrated, Miniaturized (0.125mm<sup>2</sup>) 10.5µW Wireless Neural Sensor

To date, the direct recording of APs is the only type of BMI proven to provide enough temporal and spatial resolution to control complex robotic prostheses. However, the implantation of micro-electrode arrays to record APs causes scar tissue formation, severely degrading the recording SNR over time. Studies indicate that reducing the amount of tissue displaced by an implant and eliminating the long-term damage caused by 'micro-motion' effects may mitigate a biological response [38]. Micro-motion is the independent movement of an implant with respect to the brain, resulting in tissue abrasion. This effect can be reduced by eliminating the interface cables and utilizing a wireless link to transfer power and data. Furthermore, the implant should be sufficiently small and light to entirely free-float in brain tissue, eliminating friction with the dura or skull.

Prior work (e.g. [14, 18, 13]) has developed wirelessly powered neural interfaces that utilize large external antennas and bulky off-chip capacitors. To enable an electrode-sized implant to float in brain tissue, an SoC solution with an order of magnitude reduction in active circuit area is required. This reduction in area also reduces the available power, necessitating a similar reduction in power consumption of the circuits. This work achieves a 10x reduction in area and 58x reduction in power, per channel, compared to prior state-ofthe-art wirelessly powered neural recording systems. This enables a fully-integrated wireless SoC without the use of any off-chip components.

The proposed system (Fig. 2.1) utilizes a subcranial interrogator to power and communicate with an array of implanted, free-floating AP sensors through the brain's dura. The dura is the outermost membrane surrounding the brain and performs an important biological role; therefore, it is desirable to re-close it after implantation. The sensor nodes are implanted lengthwise, allowing the 4 electrodes to extend deep enough to reach relevant neurons. Four data acquisition channels amplify and digitize the sensed neural potentials into an 800kbps data stream via four 10b, 20kHz ADCs. A single receive (RX) coil on the

Figure 2.1: A conceptual diagram of the implementation of a BMI utilizing the developed wireless neural sensor. The sensor free-floats under the dura, while receiving power from and communicating to an interrogator beneath the skull.

sensor couples perpendicularly to a superdural transmit (TX) coil and achieves both power and data transmission simultaneously. To further minimize the node's area/volume and maximize the antenna size, the RX coil is placed on top of the active circuitry.

Figure 2.2: System diagram, subdivided into three primary circuit blocks: Power management, communication circuitry, and data acquisition.

# 2.1 System Design

The constrained node size in Fig. 2.1 places aggressive circuit power and area constraints, which are met through system architecture decisions as well as with the choice of key circuit block topologies. A block diagram of the system architecture is shown in Fig. 2.2. The system components are sub-divided into three categories: Communication Circuitry, Power Management, and Data Acquisition. The core communication circuits include a demodulator, which enables recovery of the low-duty-cycle beacons, and the frequency locked loop (FLL), which generates the Miller subcarrier clock. The power management circuits, consist of a rectifier, supply generation and bias circuitry. A switched-capacitor (SC) bandgap reference was utilized to minimize power and area consumption [39] and self calibration techniques were employed for automatic current and resistor trim. The data acquisition block consists of a multistage neural amplifier, and a 10b counter-based ADC. The system has a total of four amplifiers and input electrodes, which share a common reference electrode.

The system architecture, is ultimately limited by the channel loss for power transfer and the communication protocol data rate. The high data rate and need for a precise clock necessitate an interrogator-provided time base. To enable robust multi-node communication while providing a low-overhead reference clock to the nodes, the communication protocol is optimized for this application using miller-encoded backscatter (Section 2.1.1). The core communication circuits include a demodulator, which enables recovery of the low-duty-cycle beacons, and the frequency locked loop (FLL), which generates the Miller subcarrier clock. The lack of a battery or external antenna requires highly optimized wireless power delivery through careful selection of the node size and wireless transmission frequency, which is discussed in Section 2.1.2.

### 2.1.1 Communication Protocol

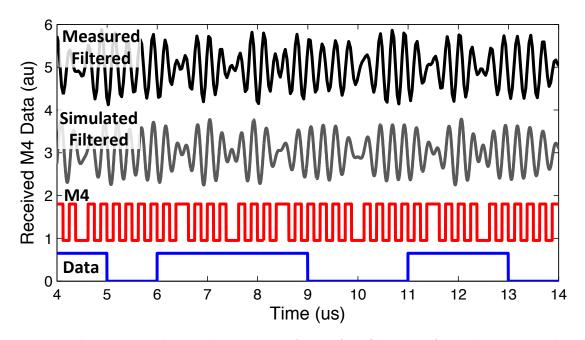

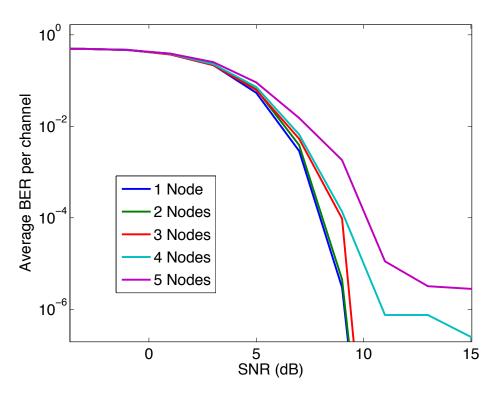

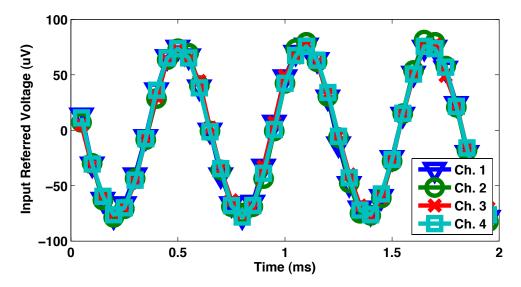

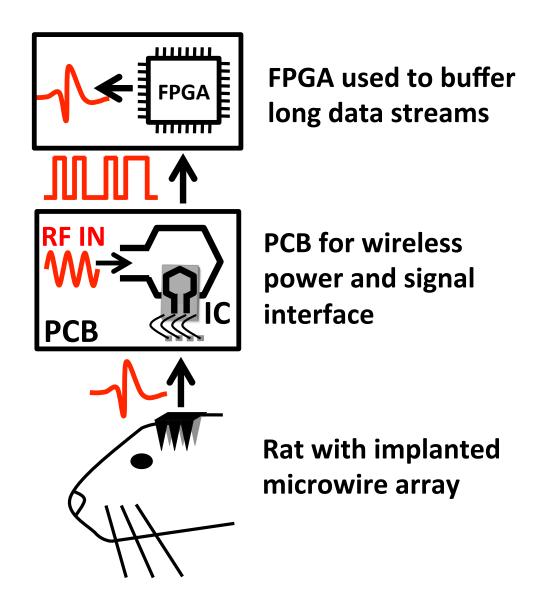

The proposed system enables a single interrogator to wirelessly power multiple implanted nodes. However, each node generates 800kbps (4ch x 10b x 20kHz) of neural data which it must continuously stream to the interrogator. Time interleaving the communication of N nodes reduces the energy per bit by a factor of N, requires N times the data rate per node, and incurs N timing overheads between the time-interleaved communication intervals. Instead, simultaneous transmission by all nodes in unique frequency bands is proposed. For this 5-node system, each node's backscatter is Miller-encoded at a programmable subcarrier frequency between 2MHz and 10MHz. Fig. 2.3 (top) shows conceptual time domain waveforms of 5 wireless packets with this system's possible subcarrier frequencies (2, 4, 6, 8, 10 MHz). Fig. 2.3 (middle) shows the frequency spectrum of 5 nodes transmitting simultaneously. Finally, Fig. 2.3 (bottom) shows a simulated time domain waveform received from 5 nodes (Raw), the band-pass filtered waveform (Filtered) isolating the Miller 4 node and the resulting data as modulation (M4) and raw bits (Data).

The Miller subcarrier frequency of each node must be precise enough such that the interrogator can filter the responses from each frequency channel. The nodes generate a precise local clock with the help of the interrogator, which sends a short downlink beacon pulse every  $50\mu s$ . The nodes recover this 20kHz clock, which initiates the ADC conversions of neural potentials as well as communication of the 40-bit data packets containing the ADC output. The 2-10MHz Miller subcarrier clock is generated by a frequency-locked loop (FLL), which locks to a multiple of the 20kHz beacons.

To initiate downlink communication, the interrogator sends two consecutive beacons, followed by PPM data. The encoding format is similar to EPC Gen2 RFID [40]. After receiving the response from a unique ID query, the interrogator initializes each node with its unique subcarrier frequency. Downlink communication is only used for initialization of the nodes. Since the downlink configuration packets are infrequent, the node discards the ADC sample when being programmed.

### 2.1.2 SAR & Frequency Selection

The maximum power available to a node is limited by the the transmission medium, transmission distance, the frequency of operation and the specific absorption rate. For this application, the transmission medium is known and the minimum transmission distance is set by the thickness of the dura above the primary motor cortex (M1). In humans, the the 99.7th percentile ( $\mu + 3\sigma$ ) for thickness of the dura measures 0.61mm [41]. This means that only the node size and transmission frequency are free variables. In biological media, operating at a frequency between 1-3GHz minimizes channel loss for edge-to-edge coupling [42] and reduces the RX coil size by several orders of magnitude compared to [14, 18, 13]. Thus, the transmission frequency for this system was selected to be 1.5GHz, trading a reduction in node size and channel loss for an increase in the specific absorption rate.