### UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Micro-Electro-Mechanical Relay Technology for Beyond-Von-Neumann Computer Architectures

### Permalink https://escholarship.org/uc/item/8cf2p91g

**Author** Hu, Xiaoer

### **Publication Date**

2022

Peer reviewed|Thesis/dissertation

#### Micro-Electro-Mechanical Relay Technology for Beyond-Von-Neumann Computer Architectures

by

Xiaoer Hu

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Ming C. Wu Professor Junqiao Wu

Spring 2022

# Micro-Electro-Mechanical Relay Technology for Beyond-Von-Neumann Computer Architectures

Copyright 2022

by

Xiaoer Hu

#### Abstract

#### Micro-Electro-Mechanical Relay Technology for Beyond-Von-Neumann Computer Architectures

by

Xiaoer Hu

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

The invention and development of complementary metal-oxide-semiconductor (CMOS) transistor technology for digital computing have led to a global information technology revolution and economic boom, which have shaped modern society. However, transistor leakage current  $(I_{OFF})$  and limited subthreshold swing set a fundamental limit on the energy efficiency of digital computing today. Micro-electro-mechanical (MEM) switches (relays) previously have been shown to be promising for energy-efficient digital computing applications, due to their abrupt ON/OFF switching characteristics and negligible OFF-state leakage current.

This dissertation focuses on novel applications of MEM relays for facilitating new computer architectures that can be much more efficient than the classic von Neumann architecture. First, MEM relays are demonstrated to operate reliably with millivolt signals at cryogenic temperatures, due to much lower hysteresis voltage and more stable ON-state resistance. A sub-10 mV relay-based inverter circuit is demonstrated at a temperature of 4 K. Our experimental study indicates that MEM relays should be able to operate at temperatures as low as 1.8 K, making them promising candidates for ultra-low power cryogenic digital interface circuits for quantum computing.

Then superconducting MEM relays using niobium (Nb) as the contact material are investigated, in order to further reduce the operation power consumption for quantum computing applications at cryogenic temperatures. The detailed fabrication process flow is shown, and temperature-dependent measurements are conducted to check the superconductivity of the Nb electrodes.

Finally, DC-voltage-driven oscillatory behavior of MEM relays is investigated via experimental study and finite-element-method-based computer simulations. Sub-harmonic injection locking and coupled oscillation behaviors of MEM relays are demonstrated, indicating that MEM relay oscillators are promising for implementing Ising machines, which can solve largescale combinatorial optimization problems much more efficiently than conventional computer architectures.

To my grandparents and parents

## Contents

| Contents |                                                 | ii                                                                                                                                                                                                                                                            |                                               |

|----------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Li       | st of l                                         | Figures                                                                                                                                                                                                                                                       | iv                                            |

| Li       | List of Tables                                  |                                                                                                                                                                                                                                                               | viii                                          |

| 1        | 1.1<br>1.2<br>1.3                               | oduction         Introduction: Digital Integrated Circuits and Next-Generation Computing         Why Micro-Electro-Mechanical (MEM) Relays?         MEM Relay Design and Operation         Dissertation Overview                                              | <b>1</b><br>1<br>5<br>8<br>12                 |

| 2        | <b>plica</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | A-Low-Voltage Operation of MEM Relays for Cryogenic Logic Ap-<br>tions Quantum Computing Benefits and Requirements                                                                                                                                            | <b>13</b><br>13<br>15<br>25<br>25<br>33<br>38 |

| 3        | 3.1<br>3.2<br>3.3<br>3.4                        | Cact Material Exploration for Cryogenic MEM Relays         Introduction: Why Superconducting Relays?         Niobium-Contact Relay Fabrication Process Development         Niobium-Contact Relay Operating Characteristics         Discussion         Summary | <b>39</b><br>39<br>42<br>45<br>49<br>51       |

| 4        | Macl<br>4.1<br>4.2                              | y of DC-Driven MEM Relay Oscillators for Implementation of Ising<br>hines<br>Ising Machine Background                                                                                                                                                         | <b>52</b><br>52<br>57<br>62                   |

|          | 4.5 | Coupling of MEM Relay Oscillators | 71              |

|----------|-----|-----------------------------------|-----------------|

| <b>5</b> | Con | Summary                           | 73              |

|          |     | Suggestions for Future Work       | 74<br><b>76</b> |

iii

# List of Figures

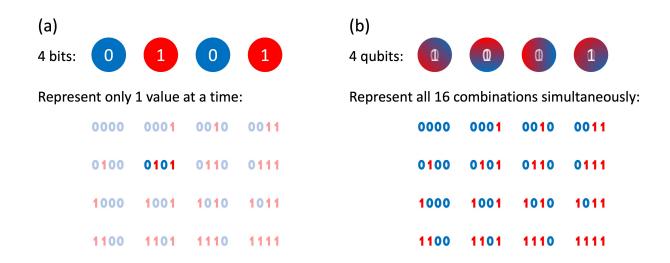

| 1.1 | Comparison of (a) 4 bits in classical computers that each can only represent 1 possible value at a time, and (b) 4 qubits in quantum computers that each can |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | represent all 16 combinations at the same time                                                                                                               | 3  |

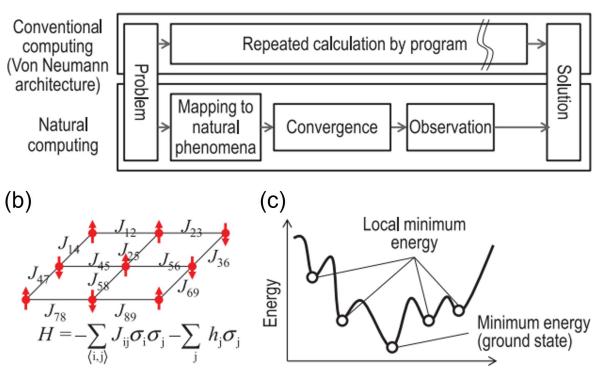

|     | ventional computing architectures and "natural" computing architectures. (b) A                                                                               |    |

|     | 9-spin Ising model. (c) The energy profile of an Ising model. Adapted from [50].                                                                             | 4  |

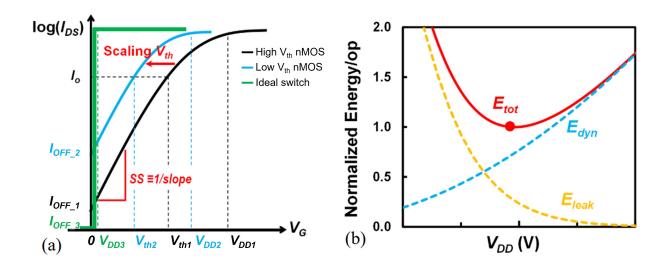

| 1.3 | Conceptual illustrations of (a) transfer I-V characteristics of a high $V_{th}$ n-channel                                                                    |    |

|     | MOSFET, a low $V_{th}$ n-channel MOSFET, and an ideal switch; (b) normalized                                                                                 |    |

|     | dynamic, static, and total energy consumed by a CMOS digital logic circuit to                                                                                |    |

|     | perform a digital operation, as a function of the supply voltage $V_{DD}$ , showing the                                                                      |    |

|     | tradeoff between dynamic energy and static energy resulting in a minimum for                                                                                 |    |

|     | total energy consumed. Reproduced from [40]                                                                                                                  | 6  |

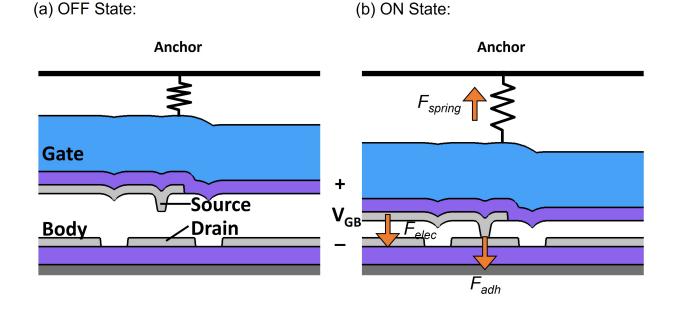

| 1.4 | A simplified illustration of MEM relay working mechanisms in (a) OFF-state and                                                                               | _  |

|     | (b) ON-state.                                                                                                                                                | 7  |

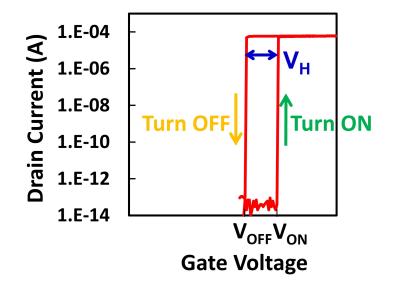

| 1.5 | A typical $I_{DS}$ -vs $V_G$ characteristic of a MEM relay, with immeasurably low $I_{OFF}$                                                                  | 0  |

| 1.0 | and abrupt switching behavior.                                                                                                                               | 8  |

| 1.6 | A simplified parallel capacitor model of a MEM relay                                                                                                         | 8  |

| 2.1 | Quantum processor with classical controller.                                                                                                                 | 14 |

| 2.2 | Monolithic integration of quantum processor with electronic control circuitry                                                                                | 14 |

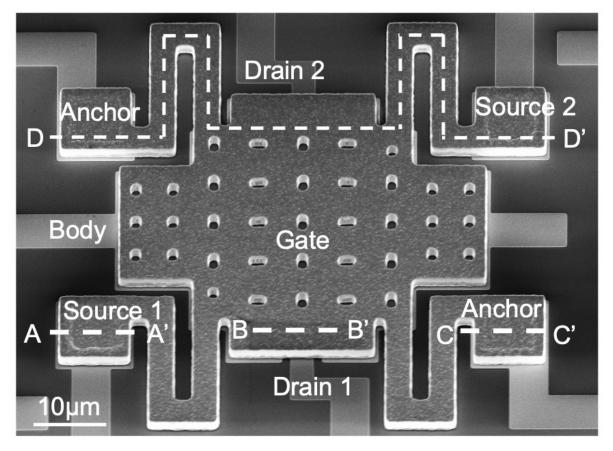

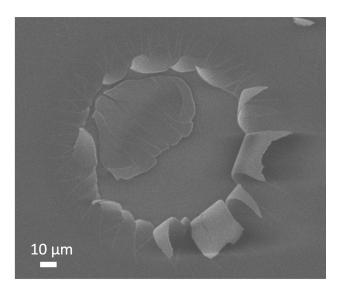

| 2.3 | 30° tilted SEM image of a MEM logic relay.                                                                                                                   | 16 |

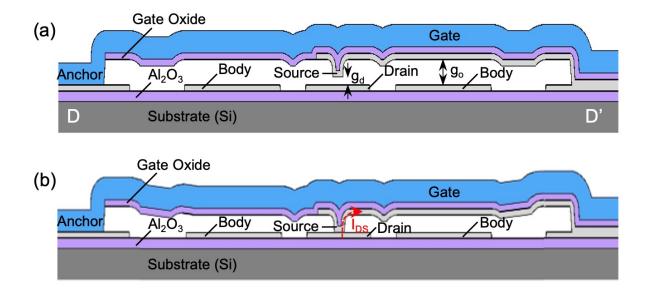

| 2.4 | Schematic cross-sectional views along D-D' of Figure 2.3: (a) OFF-state (b) ON-                                                                              |    |

|     | state                                                                                                                                                        | 17 |

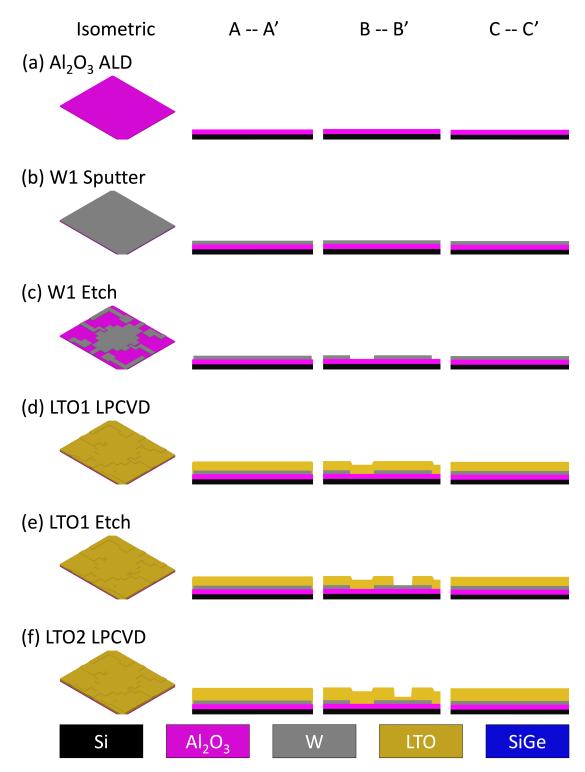

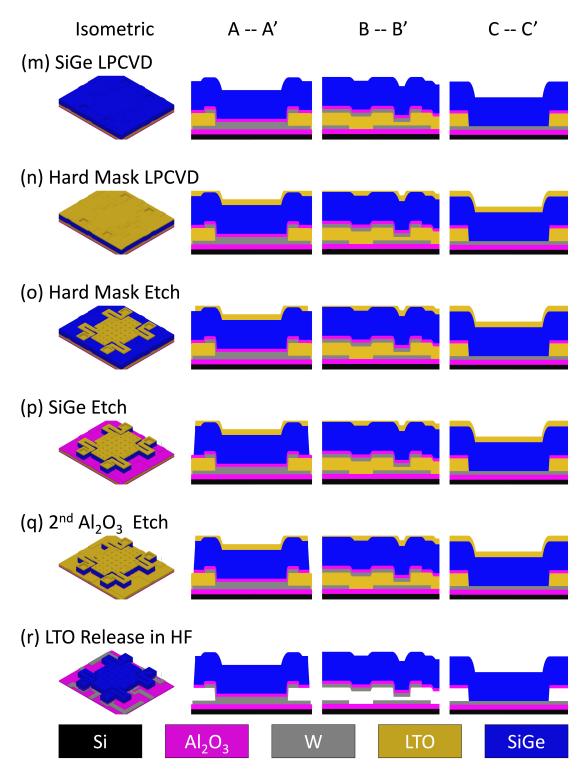

| 2.5 | Fabrication process of tungsten-contact MEM relays, showing isometric views on                                                                               |    |

|     | the left and cross-sectional views along A-A', B-B', and C-C' cutlines on the right.                                                                         | 20 |

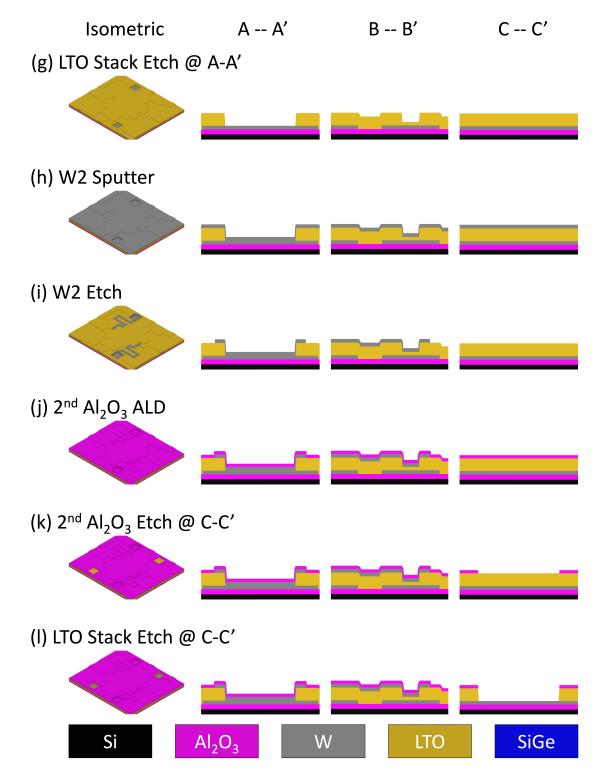

| 2.5 | Fabrication process of tungsten-contact MEM relays, showing isometric views on                                                                               |    |

|     | the left and cross-sectional views along A-A', B-B', and C-C' cutlines on the right                                                                          |    |

|     | (cont.)                                                                                                                                                      | 22 |

| 2.5 | Fabrication process of tungsten-contact MEM relays, showing isometric views on                                                                               |    |

|     | the left and cross-sectional views along A-A', B-B', and C-C' cutlines on the right                                                                          |    |

|     | (cont.)                                                                                                                                                      | 24 |

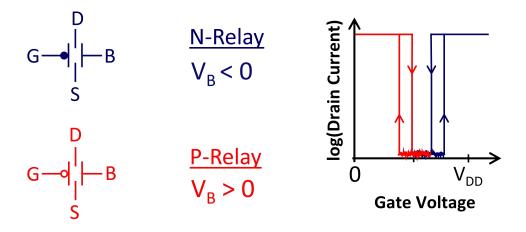

| 2.6 | Complementary relay circuit symbols and I-V characteristics                                                                                                  | 25 |

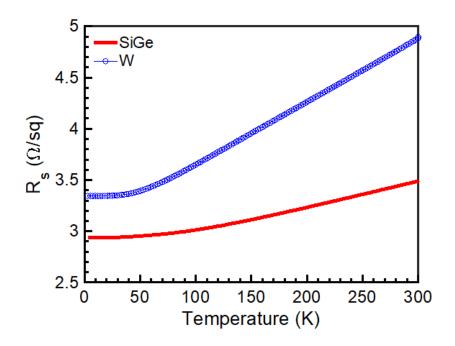

| 2.7  | Temperature dependence of sheet resistance for the W electrode layer and poly-<br>SiGe structural layer                                                                                                                                       | 26 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

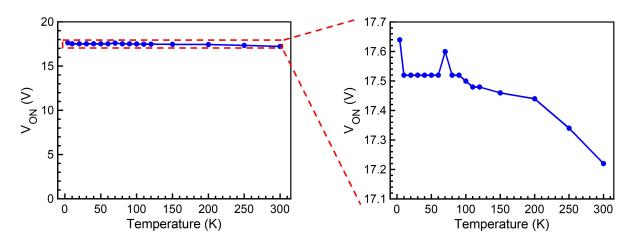

| 2.8  | Temperature dependence of relay turn-ON voltage.                                                                                                                                                                                              | 27 |

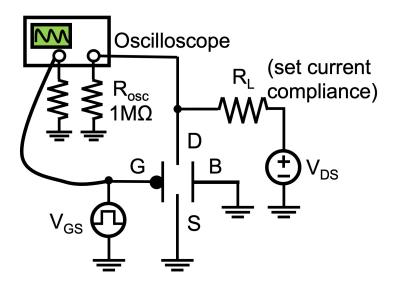

| 2.9  | Circuit schematic for relay self-oscillation test setup.                                                                                                                                                                                      | 27 |

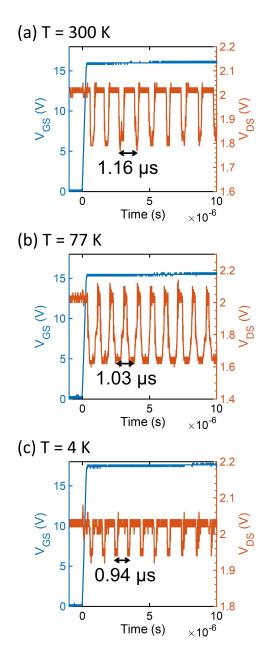

| 2.10 | Relay self-oscillation measurements taken at different temperatures: (a) 300 K, (b) 77 K, and (c) 4 K                                                                                                                                         | 28 |

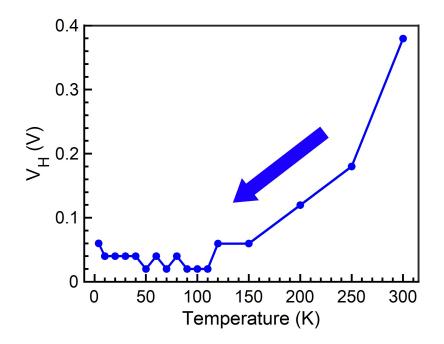

| 2.11 | Temperature dependence of relay switching hysteresis voltage                                                                                                                                                                                  | 29 |

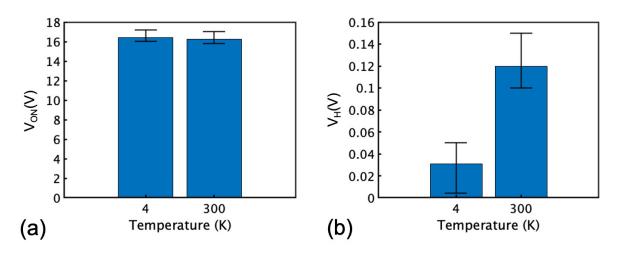

|      | Measured values for 5 MEM relays: (a) Average $V_{ON}$ at 4 K and 300 K, (b)<br>Average $V_H$ at 4 K and 300 K                                                                                                                                | 30 |

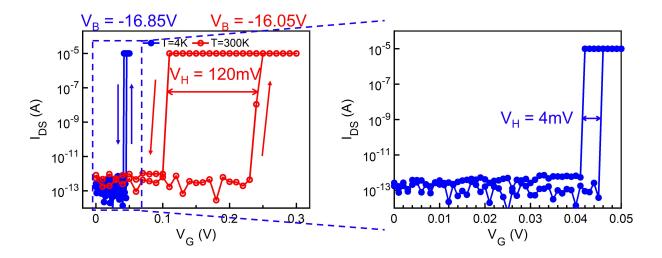

| 2.13 | Body-biased relay $I_{DS}$ -vs $V_G$ characteristics at 300 K and 4 K.                                                                                                                                                                        | 30 |

|      | Temperature dependence of relay $R_{ON}$                                                                                                                                                                                                      | 31 |

|      | Relay endurance testing at various temperatures                                                                                                                                                                                               | 32 |

|      | Relay turn-ON delay measurements with $V_B = 0$ V (a) at 300 K, and (b) at 4 K.                                                                                                                                                               | 33 |

|      | (a) schematic circuit diagram and (b) truth table of a relay-based 2:1 multiplexer integrated circuit.                                                                                                                                        | 34 |

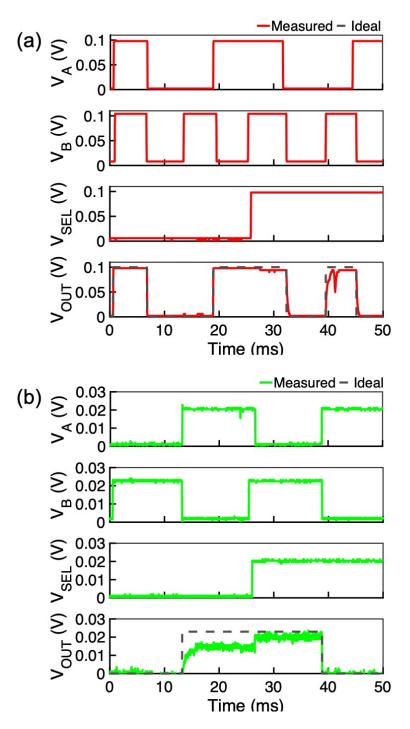

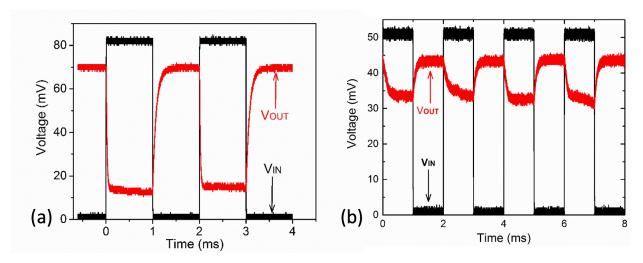

| 2.18 | Measured voltage waveforms demonstrating operation of a relay-based 2:1 multiplexer (a) at 300 K ( $V_{BP} = 15.5$ V, $V_{BN} = -14.6$ V), and (b) at 77 K ( $V_{BP} = 17.07$ V, $V_{BN} = -14.71$ V).                                        | 35 |

| 2.19 |                                                                                                                                                                                                                                               |    |

|      | relay operating as a pull-down device.                                                                                                                                                                                                        | 36 |

| 2.20 | Demonstration of sub-100 mV inverter circuit operation at 300 K: (a) relay as pull-<br>down device with $V_{DD} = 80$ mV, and (b) relay as pull-up device with $V_{DD} = 50$                                                                  |    |

|      | mV. Adapted from [87].                                                                                                                                                                                                                        | 37 |

| 2.21 | Demonstration of sub-50 mV inverter circuit operation, enabled by self-assembled molecular coating, at 300 K: (a) relay as pull-down device, and (b) relay as pull-up                                                                         |    |

|      | device. Adapted from $[63]$                                                                                                                                                                                                                   | 37 |

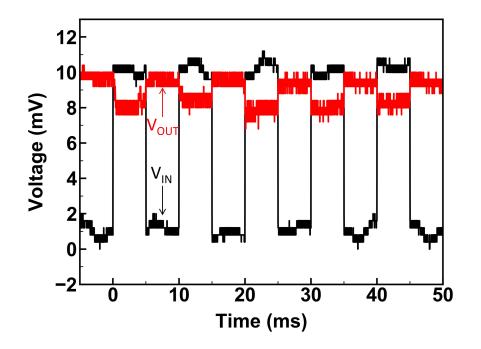

| 2.22 | Measured voltage waveforms of a sub-10 mV relay-based inverter circuit in which a MEM relay is configured as a pull-down device at 4 K                                                                                                        | 38 |

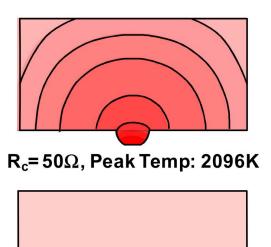

| 3.1  | ANSYS-simulated temperature contours at a contacting electrode asperity under Joule heating. For simplicity, all the contacting asperities are lumped into one, and the asperity radius is set to be 10 nm. The simulated voltage drop across |    |

|      | the contact is 1 V. Adapted from [96].                                                                                                                                                                                                        | 40 |

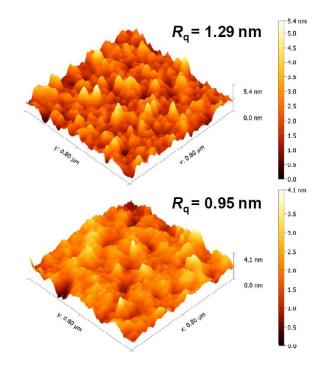

| 3.2  | Atomic force microscopy images of tungsten electrode surfaces from a fresh relay                                                                                                                                                              |    |

| 0.0  | $(R_q = 1.29 \text{ nm})$ vs. a cycled relay $(R_q = 0.95 \text{ nm})$ . Adapted from [91]                                                                                                                                                    | 41 |

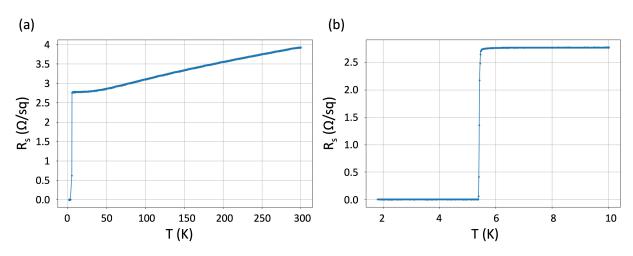

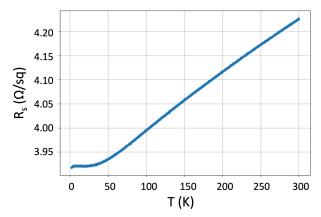

| 3.3  | Sheet resistance vs. temperature of sputtered Nb thin film: (a) measurement<br>with a temperature ramp rate of 5 K/min, and (b) measurement with a temper-<br>ature ramp rate of 0.5 K/min. The superconducting transition temperature is     |    |

|      | ature ramp rate of 0.5 K/min. The superconducting transition temperature is approximately 5.4 K.                                                                                                                                              | 43 |

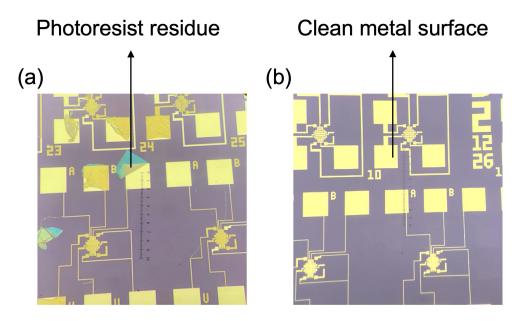

| 3.4  | Microscopic images of a relay wafer surface after Nb etching: (a) after soaking for 2 hours in MICROPOSIT Remover 1165 bath, and (b) after additional oxygen                                                                                  | 40 |

|      | plasma ashing for 1 minute at 250 °C                                                                                                                                                                                                          | 44 |

v

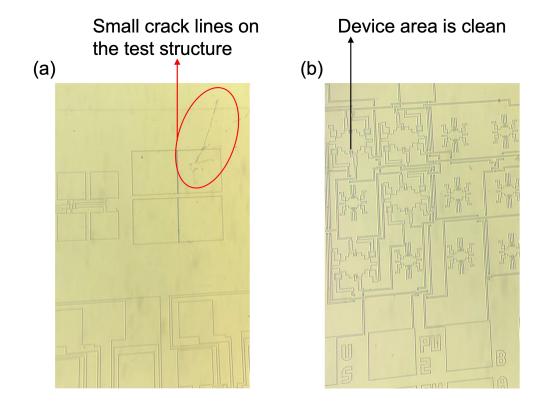

| 3.5  | Microscope images of a relay wafer surface after the second Nb film is sputtered<br>on top of LTO, showing: (a) small crack lines on a test structure, and (b) no |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | cracking issues in the device area                                                                                                                                | 45 |

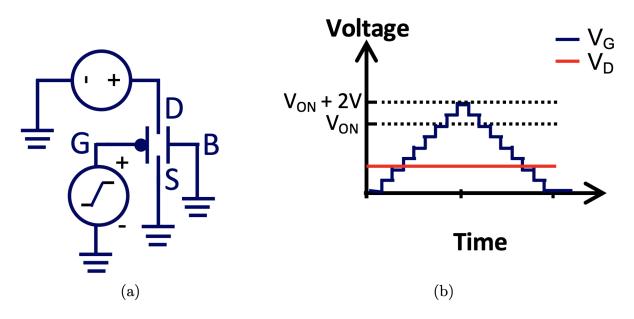

| 3.6  | The hot-switching oxide-breakdown method (a) circuit schematic and (b) voltage                                                                                    |    |

|      | timing waveforms (not to scale). Adapted from [42]                                                                                                                | 46 |

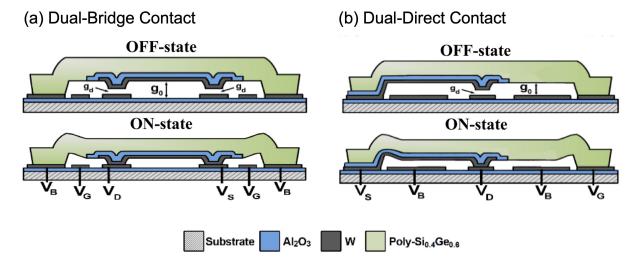

| 3.7  | Schematic cross-sections of MEM relays with different contacting electrode de-                                                                                    |    |

|      | signs, in the OFF-state and in the ON-state: (a) dual-bridge source/drain contact                                                                                 |    |

|      | design, and (b) dual-direct source/drain contact design. Adapted from [46,64,105].                                                                                | 47 |

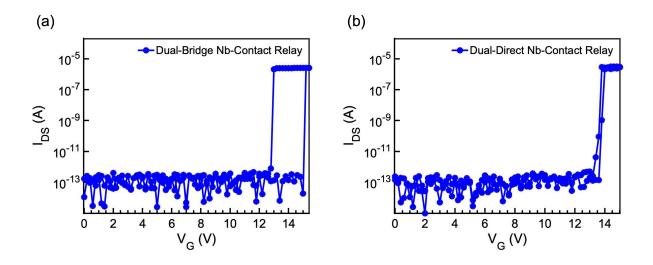

| 3.8  | Measured $I_{DS}$ -vs $V_{GB}$ characteristics of Nb-contact relays. (a) dual-bridge                                                                              |    |

|      | contact design, (b) dual-direct contact design                                                                                                                    | 47 |

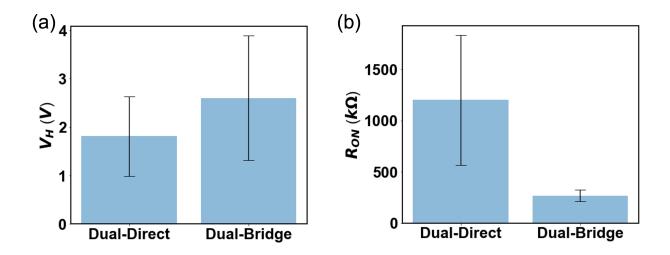

| 3.9  | Average measured values of (a) $V_H$ and (b) $R_{ON}$ for 10 Nb-contact relays of each                                                                            |    |

|      | contact design. The error bars indicate the ranges of standard deviation                                                                                          | 48 |

| 3.10 | Measured sheet resistance vs. temperature of a niobium test structure on the                                                                                      |    |

|      | fabricated chip. The temperature was ramped from $1.8 \text{ K}$ to $300 \text{ K}$ , at $1 \text{ K/min}$ .                                                      | 49 |

| 3.11 | Measured EDX spectrum of a deposited Nb film that is not superconducting at                                                                                       |    |

|      | 1.8 K, showing the presence of Fe, Al, and Cr in the Nb film                                                                                                      | 50 |

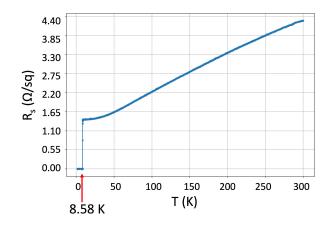

| 3.12 | Measured sheet resistance vs. temperature of a niobium film deposited in the                                                                                      |    |

|      | MRC943 tool. The temperature was ramped from 1.8 K to 300 K at a rate of 1                                                                                        |    |

|      | K/min. The superconducting transition temperature is 8.58 K                                                                                                       | 50 |

| 3.13 | Scanning electron micrograph image of a Nb film after $TiO_2$ and LTO deposition,                                                                                 |    |

|      | and vapor HF removal of the oxide layers                                                                                                                          | 51 |

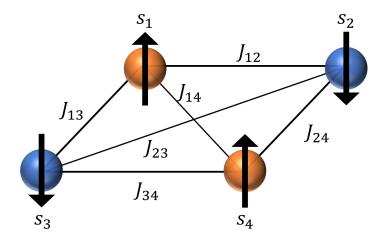

| 4.1  | Illustration of a four-spin Ising model. Each spin can be either up or down, and                                                                                  |    |

|      | the coupling strength between spin $s_i$ and $s_j$ is $J_{ij}$ .                                                                                                  | 53 |

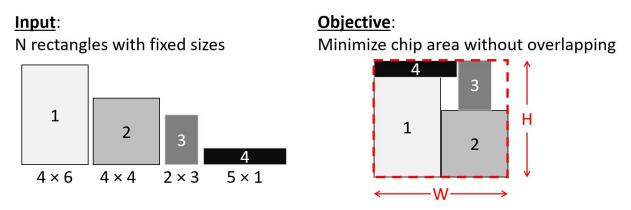

| 4.2  | The combinatorial optimization problem in VLSI floorplanning design can be                                                                                        |    |

|      | formulated as the "rectangle packing problem." Reproduced from [111]                                                                                              | 54 |

| 4.3  | The result of the U.S. map coloring problem solved by an Ising machine. Adapted                                                                                   |    |

|      | from [58].                                                                                                                                                        | 55 |

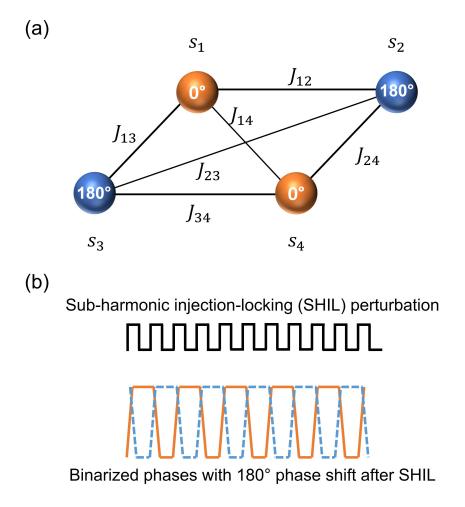

| 4.4  | Oscillator-based Ising Machine (OIM) concept: (a) Illustration of a 4-spin Ising                                                                                  |    |

|      | model implemented using oscillators. (b) A perturbing sub-harmonic injection                                                                                      |    |

|      | signal causes the oscillators to settle into one of two phase states $(0^{\circ} \text{ and } 180^{\circ})$                                                       |    |

|      | phase shift).                                                                                                                                                     | 56 |

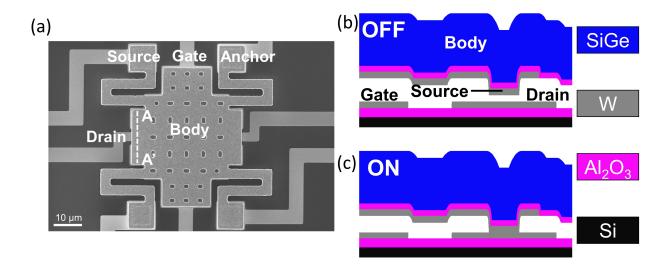

| 4.5  | (a). Plan-view SEM image of a MEM relay, and cross-sectional views along the                                                                                      |    |

|      | A-A' cutline: (b) OFF state (c) ON state.                                                                                                                         | 57 |

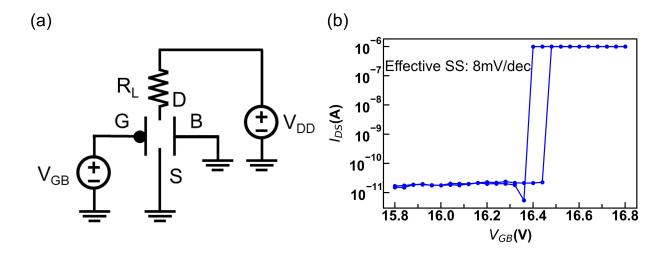

| 4.6  | (a) MEM relay operation circuit diagram. Here, $R_L$ is used to set the current                                                                                   |    |

|      | compliance. (b) Typical measured relay $I_{DS}$ - $V_{GB}$ characteristic. It is worthwhile                                                                       |    |

|      | to note here that the effective subthreshold swing is only $8 \text{ mV/dec.}$                                                                                    | 58 |

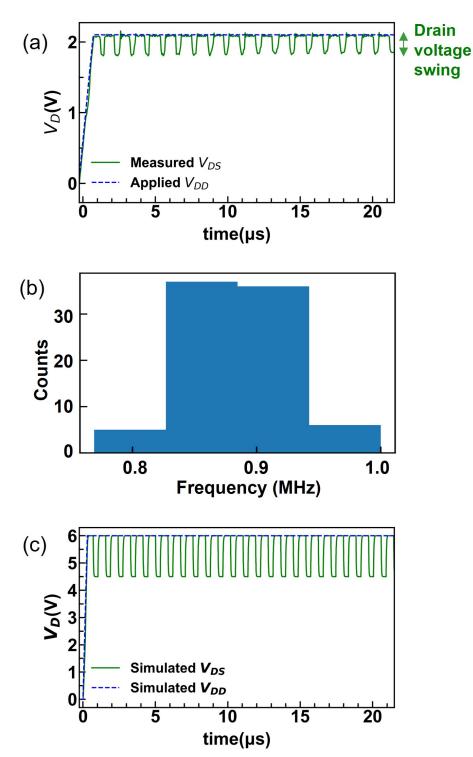

| 4.7  | DC-bias-driven MEM relay oscillation: (a) measured voltage waveforms with ap-                                                                                     |    |

|      | plied DC voltages of $V_{GB} = V_{ON} - 0.5$ V and $V_{DD} = 2.1$ V; (b) relay oscillation                                                                        |    |

|      | frequency distribution over 100 cycles; (c) simulated MEM relay oscillation be-                                                                                   |    |

|      | havior for $V_{GB} = V_{ON} - 1.8$ V                                                                                                                              | 60 |

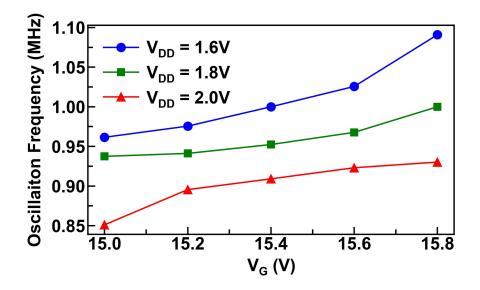

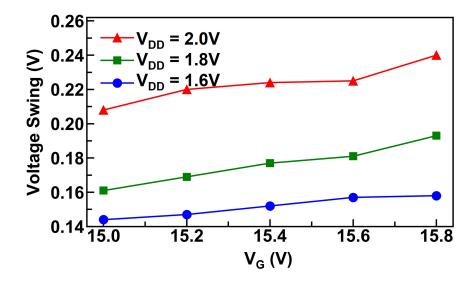

| 4.8  | Relay oscillation frequency dependence on $V_G$ for different values of $V_{DD}$                                                                                  | 61 |

| 4.9  | Relay oscillation drain voltage swing dependence on $V_G$ for different values of $V_{DD}$ .    | 62 |

|------|-------------------------------------------------------------------------------------------------|----|

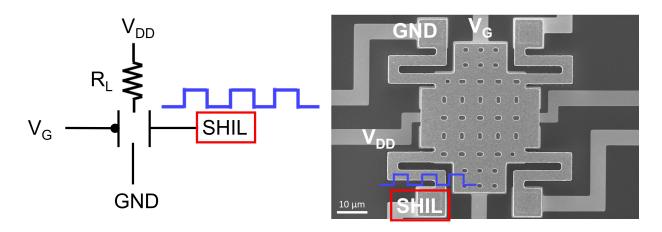

| 4.10 | A Sub-Harmonic Injection Locking (SHIL) signal is applied via the body electrode                |    |

|      | of a MEM relay                                                                                  | 63 |

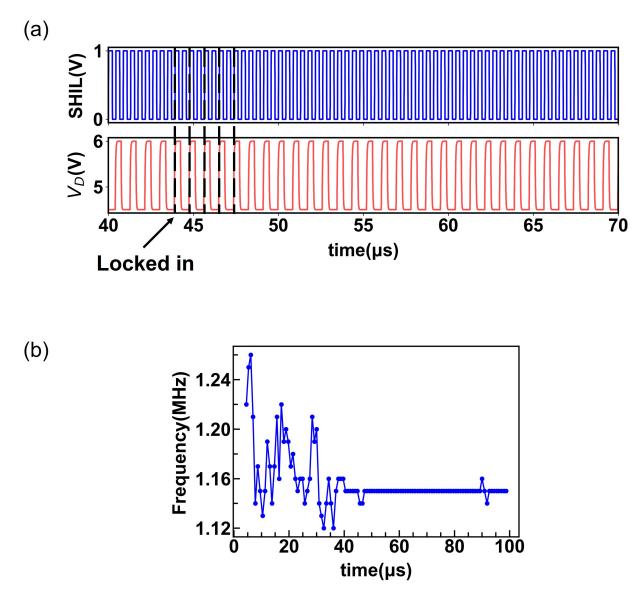

| 4.11 | MEM relay oscillation simulation results: (a) simulated voltage waveforms show-                 |    |

|      | ing phase lock with a 1 V, 2.3 MHz SHIL signal within approximately 40 cycles,                  |    |

|      | and (b) oscillation frequency vs. time, showing frequency stabilization after ap-               |    |

|      | proximately 40 $\mu s$                                                                          | 64 |

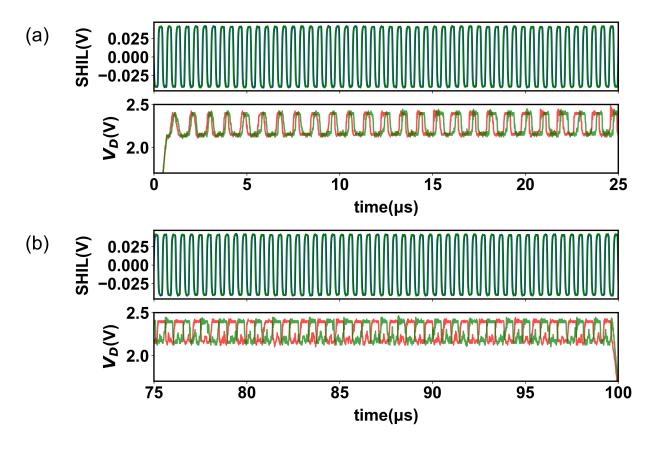

| 4.12 | Experimental SHIL results. The perturbation 60 mV peak-to-peak SHIL signals                     |    |

|      | applied to the two MEM relays are synchronized. (a) Initial independent oscil-                  |    |

|      | lation of the two MEM relays. (The $V_D$ responses of the two MEM relays are                    |    |

|      | not locked in with their respective SHIL signals.) (b) 75-100 $\mu s$ after start-up,           |    |

|      | oscillations locked in with the SHIL signals are observed, with $180^{\circ}$ phase difference. | 65 |

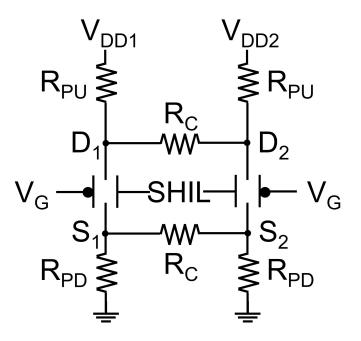

| 4.13 | Circuit diagram for two relays coupled together in a parallel configuration                     | 66 |

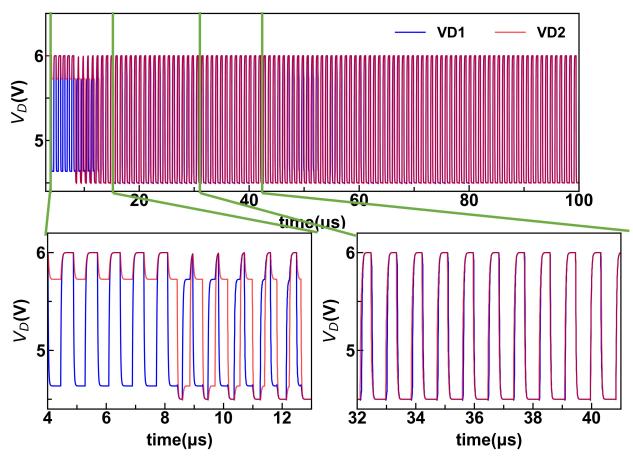

| 4.14 | Simulated voltage waveforms of relay oscillators coupled together in a parallel                 |    |

|      | configuration.                                                                                  | 67 |

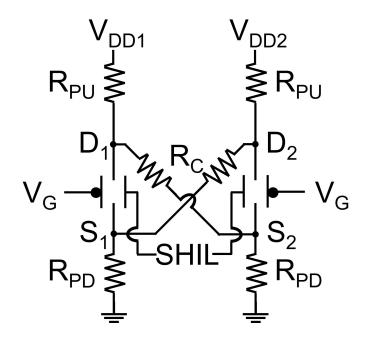

| 4.15 | Circuit diagram for two relays coupled together in an anti-parallel configuration.              | 68 |

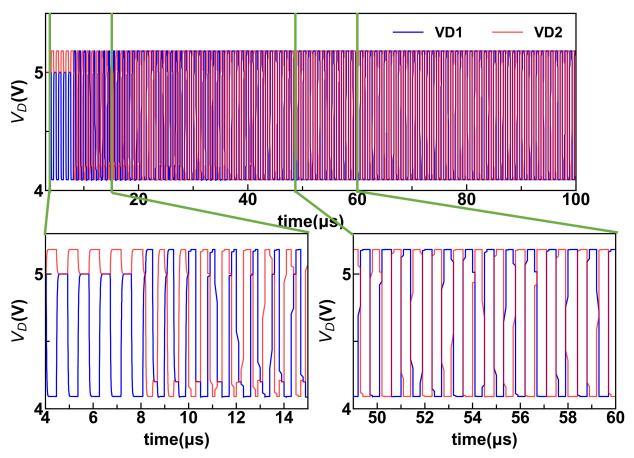

| 4.16 | Simulated voltage waveforms of relay oscillators coupled together in an anti-                   |    |

|      | parallel configuration.                                                                         | 69 |

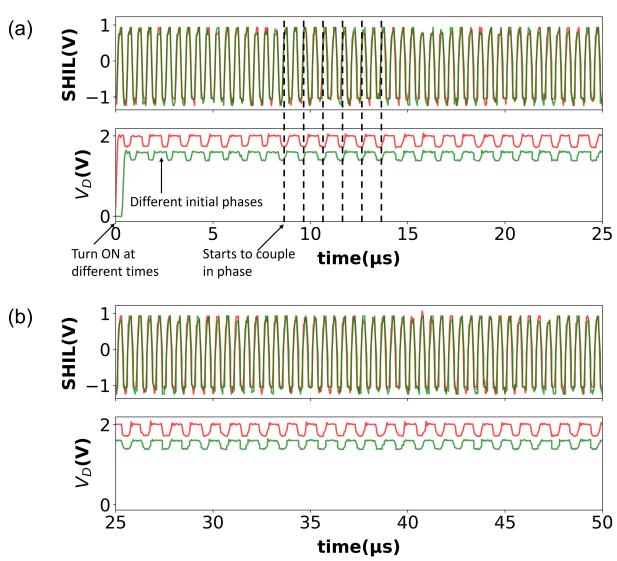

| 4.17 | Experimental parallel-coupled relay oscillation voltage waveforms: (a) 0 - 25 $\mu s$ ,         |    |

|      | and (b) 25 - 50 $\mu s$ after application of DC voltage signals. The red and green              |    |

|      | curves correspond to each of the two different relay oscillators                                | 70 |

## List of Tables

| 3.1 | Comparison of sheet resistance values for the electrode and structural layers in |    |

|-----|----------------------------------------------------------------------------------|----|

|     | W-contact and Nb-contact relays (unit: $\Omega/\Box$ )                           | 48 |

| 4.1 | Design parameters of a MEM relay for resonant frequency $(\omega_o)$ calculation | 59 |

#### Acknowledgments

First and foremost, I am extremely grateful to my advisor, Professor Tsu-Jae King Liu, who provide me with inspiring guidance and constant encouragement throughout my graduate studies at UC Berkeley, and act as a role model for me not only in academic but also in life. Her knowledge and creativity in the semiconductor field, motivation and enthusiasm to push the technical boundary, and kind personality and thoughtfulness to people, are all precious lectures in my life. I hope one day I can become a person like her, and be able to make changes not only in the technical world, but also encourage younger generations to pursue their dreams.

I would also like to thank Professor Ming Wu and Professor Junqiao Wu for serving on my dissertation committee and qualifying examination committee, and providing me with invaluable feedback and guidance on my research projects. I would like to thank Professor Ana Claudia Arias for being the committee member for my qualifying examination and preliminary examination, and providing me with frequent guidance and encouragement. I am grateful to Prof. Vivek Subramanian for advising me on my Master's thesis and strengthening my ability to think and study independently as a graduate student. Additionally, I am grateful to Profs. Jeffrey Bokor, Sayeef Salahuddin, Chenming Hu, Ali Javey, Rikky Muller, Clark Nguyen, and Jaijeet Roychowdhury for their technical support, career advice, and excellent courses in the field of electrical engineering.

I also appreciate Professor Muhammad M. Hussain for giving me the opportunity to teach the semiconductor fabrication laboratory (EE 143), and helping me to better enhance my knowledge and experience in modern semiconductor process technology. I would also like to thank Dr. Arash Nourian and Dr. Ed Henrich for providing me with the opportunity to serve as a graduate student instructor for Data-X (IEOR 135) and get a better understanding of state-of-the-art data science and machine learning techniques while teaching.

Additionally, I would like to thank the entire King Liu research group. With the help, discussion, and encouragement from Dr. Sergio Almeida, Dr. Zhixin Alice Ye, Dr. Benjamin Osoba, Dr. Urmita Sikder, Tsegereda Esatu, Lars Tatum, Dr. Xi (Robin) Zhang, Dr. Fei Ding, Dr. Thomas Rembert, Dr. Hei Kam, and Dr. Min-Wu Kim, I had a lovely journey at Berkeley. I would also like to thank Qianyi Xie for being a reliable nanolab buddy for me, discussing the process difficulties with me, and providing me with help for my experiments. I would like to thank Dr. Siqi Wang, for helping me with cryogenic measurements. I also would like to thank friends that I met in nanolab, including Yichi Zhang, Junjie Hu, Zeying Ren, Xiangli Jia, and Jason Wu, for spending time in the amazing world of nanofabrication together.

In particular, I would like to appreciate UC Berkeley Marvell Nanofabrication Laboratory staff – including Dave Taosaka, Allison Dove, Richelieu Hemphill, Ryan Rivers, Sam Tsitrin, Jay Morford, Jason Chukes, Joanna Bettinger, and Bill Flounders – for helping me to learn the fabrication equipment, analyze the process problems in the fabrication, and maintain the working status of the equipment. I especially appreciate the rapid help from Greg Mullins, Danny Pestal, and Ming Wong for EE 143 labs.

I am sincerely grateful to the EECS administrative staff. In particular, I would like to thank Shirley Salanio, for supporting me with different petitions, personal questions, useful information, and positive encouragements.

In addition to the above, I want to thank my friends, classmates, and colleagues for providing me with ideas, help, creativity, and friendship on my course projects, teaching experience, and graduate life, including Dr. Xiaosheng Zhang, Dr. Danqing Wang, Yu Sun, Andrew Aikawa, Wanwoo Noh, Dr. Yu-Hung Liao, Mahan Tajrobehkar, Dr. Ming-Yen Kao, Shikun Shen, Kevin Zheng, Xintian Liu, Ziyu Xiang, and Zheyu Lu. I would also like to thank Harikrishnan Rajagopal, Minal Shettigar, Isabel Li, and Arvind Shankar from Applied Materials, Inc., for teaching me a lot during my internship in Summer 2020. I appreciate the help from Dr. Yuxuan Cosmi Lin, Dr. Danping Peng, Thomas Li, Josh Maher, Dr. Milind Gadre, Dr. Dejiu Fan, and Qinyue He during my job hunting time.

I would also like to thank my favorite video/mobile games: Genshin Impact, Counter-Strike: Global Offensive, and Pokémon GO. I enjoyed the beautiful scenery I saw, the sweat and practice I spent on leveling/ranking up, and the interesting people I met in these games.

Finally, I am tremendously grateful to my family for their unconditional love and ceaseless support. I want to thank my grandparents for all the efforts and sacrifices they provided when I was young, and also during this Ph.D. study. Thanks must also go to my parents. Although they don't have an electrical engineering background, they tried their best to understand the semiconductor fabrications that I was doing, and encourage me to chase my dream. Without their understanding, encouragement, and support, I would never have had a chance to complete this Ph.D. journey. I want to thank Guanglong Huang, for emboldening me to overcome all the obstacles and get through all the dark moments during these years. His accompanying helps me to realize how beautiful and sweet my world is.

## Chapter 1

## Introduction

### 1.1 Introduction: Digital Integrated Circuits and Next-Generation Computing

Integrated circuit "chips" are the electronic brains used in all computing devices today, and Complementary Metal Oxide Semiconductor (CMOS) Field Effect Transistors (FETs) are the predominant type of transistors utilized in all computing chips. Steady advancement in CMOS manufacturing technology has resulted in a global information technology revolution that has shaped modern society [1]. In 1967, Gordon Moore observed that the number of CMOS transistors on the leading microprocessor chip doubles every 18 months [2]; in 1975, he revised this to a more realistic two years [3]. This observation has since become known as Moore's law, and the exponential pace of increasing transistor count per chip has been sustained for more than five decades by the semiconductor industry; as a result, microprocessor chips have become more functional and energy efficient over the past halfcentury. The first commercially produced microprocessor chip, the Intel 4004, was released in 1971 and fabricated using a 10 µm generation process; it comprised approximately 2000 transistors [4–6]. More than 50 years later, the Apple M1 Ultra, unveiled in March 2022, comprises 114 billion transistors and is fabricated using a 5 nm generation process at Taiwan Semiconductor Manufacturing Company [7,8].

The end of Moore's law will herald a new era of information technology advancement, as the emphasis of research and development shifts away from scaling down transistor dimensions and toward innovation of new devices, new device integration approaches, and new computing architectures, to sustain the exponential pace of improvement in computational ability [9, 10].

Quantum computers have the potential to effectively solve problems that are intractable for classical computers [11–13]. For example, in 1994, Peter Shor demonstrated that quantum computers are capable of effectively factoring numbers in polynomial time [11], posing a severe threat to the RSA public-key cryptosystem that is widely used for secure data transmission, which relies on the fact that classical computers, even when equipped with the most efficient algorithms, are incapable of factoring integers with a length of 1000 decimal digits [14]. Quantum computers would also have a significant impact on fields such as quantum simulation [15] and machine learning [16–18].

In a classical computer, information is encoded as a binary number or string of binary digits (bits). The state of each bit is represented as a voltage level: a high voltage corresponds to a bit value of '1' and a low voltage corresponds to a bit value of '0'. A bit can only take a single value at a time [19]. Quantum computers manipulate qubits, which leverage quantum mechanical effects to store more than one state in a single qubit via the principle of **superposition**. That is, a qubit has the ability to superpose multiple states with varying probabilities (for example, 40% 0 and 60% 1) like Schrödinger's cat [19,20], and we cannot predict which state it is in. But the instant when we measure it, it collapses into one of the definite states.

For a classical computer, for example, if there are 4 bits, there are 16 possible combinations of bit values, and only one of them can be utilized at a time, as seen in Figure 1.1 (a). In contrast, 4 qubits in superposition can each be in any of those 16 combinations simultaneously, as illustrated in Figure 1.1 (b). Moreover, this number grows exponentially with each additional qubit, so 20 qubits can store  $2^{20}$  (more than one million) values in parallel [21]. Therefore, a quantum computer with N qubits can be  $2^N$  times more efficient than a classical computer with N bits.

Figure 1.1: Comparison of (a) 4 bits in classical computers that each can only represent 1 possible value at a time, and (b) 4 qubits in quantum computers that each can represent all 16 combinations at the same time.

There are several approaches to implementing quantum computers, including superconducting qubits [13,22–25], polarized photons [26–30], trapped ions [31–34], and electron spins in silicon [35,36]. Among all the different approaches, superconducting qubits, in particular, are considered as the most promising candidate for achieving a scalable quantum processor architecture, due to high designability, scalability, fast and reliable operation, and ability to be coupled and controlled easily [13,37].

A CMOS-based digital integrated circuit can be used to control and read information out of quantum processor, but typically is designed for room temperature operation. The number of interconnections between the refrigerated quantum processor and the external CMOS controller constrain the number of qubits that can be used [38, 39]. The CMOS controller circuitry can be located in the refrigerator together with the quantum processor at cryogenic temperatures, but may dissipate heat that detrimentally affects qubit operations.

Previous studies have shown that micro/nano-electro-mechanical (M/NEM) relays can operate at much lower voltages (50 mV and below) than required for CMOS transistors, and have negligible OFF-state leakage current (in contrast with CMOS transistors), so that they are a promising candidate for Internet of Things (IoT) applications which require ultra-lowpower consumption [40–46]. Therefore, MEM relays can also be an attractive candidate to build logic controllers for quantum computing, if they can be operated reliably at cryogenic temperatures. Another attractive non-von Neumann computing architecture is the Ising model, which can efficiently solve a large number of discrete optimization problems across a wide range of fields: very-large-scale integrated circuit design, drug discovery, capacity planning, sensing, and manufacturing [47]. Many of these combinatorial optimization problems are so-called nondeterministic polynomial time (NP)-hard or NP-complete problems [48]. NP-hard or NPcomplete problems are challenging for conventional digital computers to solve efficiently with heuristic or "greedy" algorithms [49, 50]. As Figure 1.2 (a) shows, von Neumann computers use programs to solve problems in a step-by-step repeated manner; as a result, the number of computing steps and the total computing time will drastically increase when the problem size becomes large. On the other hand, these problems can be mapped onto Ising models (Figure 1.2 (b)) and solved by finding the ground (minimum energy) state of the corresponding Ising Hamiltonian (Figure 1.2 (c)) [51, 52]. As a result, Ising machines have attracted increasing interest as physical solvers for this type of minimization problem, due to their high calculation speed and energy efficiency.

Figure 1.2: Computing paradigms: (a) Procedure-based approach to solving problem in conventional computing architectures and "natural" computing architectures. (b) A 9-spin Ising model. (c) The energy profile of an Ising model. Adapted from [50].

An Ising machine comprises a set of 'spins' - each of which can take one of two values - that are coupled together. The 'spins' can take many forms, including optical parametric oscillators [49, 53], qubits [54–57], CMOS circuits [50], and electronic oscillators [58–60]. A micro-electro-mechanical (MEM) relay can be made to function as an oscillator, and therefore can potentially be used to implement Ising machines for solving complicated combinatorial optimization problems.

### 1.2 Why Micro-Electro-Mechanical (MEM) Relays?

Figure 1.3 (a) shows the drain current vs. gate voltage semi-log plot of two n-channel MOS-FETs with different threshold voltages  $(V_{th})$ , and for an "ideal switch". The subthreshold swing (SS) of conventional CMOS transistors is fundamentally limited by Boltzmann statistics to be no steeper than 60 mV/dec at room temperature. The OFF-state leakage current of a MOSFET,  $I_{OFF}$ , is the drain current when  $V_{GS} = 0$  V and  $V_{DS} = V_{DD}$ , where  $V_{DD}$  is the power-supply voltage.  $I_{OFF}$  increases exponentially with a reduction in  $V_{th}$ :

$$I_{OFF} = I_O \times 10^{-\frac{V_{th}}{SS}} \tag{1.1}$$

where  $I_O$  is defined as the current when  $V_{GS} = V_{th}$ .

Figure 1.3: Conceptual illustrations of (a) transfer I-V characteristics of a high  $V_{th}$  n-channel MOSFET, a low  $V_{th}$  n-channel MOSFET, and an ideal switch; (b) normalized dynamic, static, and total energy consumed by a CMOS digital logic circuit to perform a digital operation, as a function of the supply voltage  $V_{DD}$ , showing the tradeoff between dynamic energy and static energy resulting in a minimum for total energy consumed. Reproduced from [40].

From Figure 1.3 (a), it can be seen that a reduction in  $V_{DD}$  to reduce the dynamic power consumption of a CMOS digital circuit would result in lower ON-state current (which is undesirable because it results in slower digital circuit operation) unless  $V_{th}$  is also reduced - but this would result in higher  $I_{OFF}$  (cf. Equation 1.1) which undesirably increases static power dissipation. Thus, energy wasted due to static power dissipation (defined as  $E_{leak}$ ) increases as  $V_{DD}$  is reduced, as illustrated by the yellow curve in Figure 1.3 (b), while energy consumed to perform a digital operation ( $E_{dyn}$ , illustrated by the blue curve in Figure 1.3 (b)) is reduced. Therefore, the total energy consumed ( $E_{tot}$ ) by a CMOS digital logic circuit has a fundamental lower limit. This limit exists due to transistor OFF-state leakage and limited SS. Therefore, an ideal digital logic switch should have zero  $I_{OFF}$  and a steep switching characteristic like the green curve shown in Figure 1.3 (a), which enables ultra-low voltage operation.

A MEM relay has abrupt switching characteristics (enabling lower  $V_{DD}$  and therefore lower  $E_{dyn}$ ) and negligible OFF-state leakage current (eliminating  $E_{leak}$ ). This is because an air gap physically separates the conducting electrodes (source electrode and drain electrode) in the OFF state, as illustrated in Figure 1.4 (a), so that no leakage current can flow between these electrodes. To turn ON the relay, a voltage is applied between the gate and body electrodes, which induces an electrostatic force  $(F_{elec})$  that actuates the movable conducting electrode into physical contact with a fixed conducting electrode, as illustrated in Figure 1.4 (b). Therefore, the relay current increases abruptly when the gate voltage reaches the turn-ON voltage,  $V_{ON}$ . This process is marked with the green arrow in Figure 1.5. To turn OFF the relay, the gate voltage is reduced so that the spring restoring force  $(F_{spring})$  of the deformed movable electrode actuates it out of contact. Due to the existence of contact adhesive force,  $F_{adh}$ , the turn-OFF voltage  $(V_{OFF})$  is smaller than the turn-ON voltage. This turn-OFF process is marked with the orange arrow in Figure 1.5. The minimum gate voltage swing to switch a relay ON/OFF is the difference between  $V_{ON}$  and  $V_{OFF}$ , which is defined as hysteresis voltage,  $V_H$ .

Figure 1.4: A simplified illustration of MEM relay working mechanisms in (a) OFF-state and (b) ON-state.

Figure 1.5: A typical  $I_{DS}$  -vs.- $V_G$  characteristic of a MEM relay, with immeasurably low  $I_{OFF}$  and abrupt switching behavior.

### **1.3** MEM Relay Design and Operation

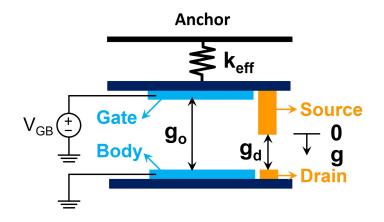

The simplified parallel capacitor model of a MEM relay is shown in Figure 1.6. The distance between the top plate and the bottom plate is labeled as  $g_o$ . The air gap between the source electrode and drain electrode is marked as  $g_d$ . The top plate is mechanically suspended through a spring with an effective spring constant of  $k_{eff}$ .

Figure 1.6: A simplified parallel capacitor model of a MEM relay.

#### CHAPTER 1. INTRODUCTION

When the top plate moves downwards by a distance g toward the bottom fixed plate, the spring restoring force  $F_{spring}$  can be written as:

$$F_{spring} = -k_{eff} \times g \tag{1.2}$$

The minus sign in Equation 1.2 indicates the spring restoring force is upward, as shown also in Figure 1.4 (b). The range of g is between 0 (when the top plate is in its as-fabricated position) and  $g_d$  (when the source and drain electrodes make contact with each other). With  $V_{GB}$  applied, the electrostatic force that actuates the top plate moving towards the bottom plate can be modeled based on the properties of parallel plate capacitors as:

$$F_{elec} = \frac{1}{2} \frac{\epsilon_0 A_{ACT} V_{GB}^2}{(g_o - g)^2}$$

(1.3)

where  $\epsilon_0$  is the vacuum permittivity,  $A_{ACT}$  is the effective actuation area (the overlap area of the parallel plates), and  $V_{GB}$  is the potential difference between the gate and body electrodes. The direction of this electrostatic force  $F_{elec}$  is downward, as indicated in Figure 1.4 (b). Therefore, the net force  $F_{total}$  (positive direction is downward) can be written as:

$$F_{total} = F_{spring} + F_{elec}$$

$$= -k_{eff} \times g + \frac{1}{2} \frac{\epsilon_0 A_{ACT} V_{GB}^2}{(g_o - g)^2}$$

(1.4)

The derivative of  $F_{total}$  over g can be written as:

$$\frac{dF_{total}}{dg} = -k_{eff} + \frac{\epsilon_0 A_{ACT} V_{GB}^2}{(g_o - g)^3}$$

(1.5)

When the suspended top plate moves down, g becomes larger. From Equations 1.2 and 1.3, the upward  $F_{spring}$  is proportional to g, and the downward  $F_{elec}$  is inversely proportional to the square of  $(g_o - g)$ . Therefore, when  $(g_o - g)$  gets small, it is possible that both  $F_{total}$  and  $\frac{dF_{total}}{dg}$  are larger than 0, resulting in non-linear positive feedback. This phenomenon is called the pull-in (PI) effect [40]. By setting both  $F_{total}$  and  $\frac{dF_{total}}{dg}$  to 0:

$$\begin{cases} 0 = -k_{eff} \times g + \frac{1}{2} \frac{\epsilon_0 A_{ACT} V_{GB}^2}{(g_o - g)^2} \\ 0 = -k_{eff} + \frac{\epsilon_0 A_{ACT} V_{GB}^2}{(g_o - g)^3} \end{cases}$$

(1.6)

we can obtain the pull-in voltage  $V_{PI}$  and the corresponding displacement of the top plate g at pull-in:

$$\begin{cases} V_{PI} = \sqrt{\frac{8k_{eff}g_o^3}{27\epsilon_0 A_{ACT}}} \\ g = \frac{g_o}{3} \end{cases}$$

(1.7)

From Equation 1.7, if g is less than 1/3 of  $g_o$ , the MEM relay turns ON before it enters the PI region of operation. That is to say,  $g_d$  should be designed to be less than 1/3 of  $g_o$ , since  $g_d$  is the maximum value that g can take. In this case, the relay is considered to operate in non-pull-in (NPI) mode. The turn-ON voltage  $V_{ON}$  can therefore be calculated by setting Equation 1.4 to be 0 and  $g = g_d$ :

$$\begin{cases} 0 = -k_{eff} \times g + \frac{1}{2} \frac{\epsilon_0 A_{ACT} V_{ON}^2}{(g_o - g)^2} \\ g = g_d \end{cases}$$

(1.8)

and the solution to Equation 1.8 is:

$$V_{ON} = \sqrt{\frac{2k_{eff}g_d(g_o - g_d)^2}{\epsilon_0 A_{ACT}}}$$

(1.9)

As noted in Figure 1.4 (b), when the relay is ON, there is an additional adhesive force  $F_{adh}$  between the two contacting electrodes primarily due to van der Waals forces [61]. The total force becomes:

$$F_{total\_ON} = F_{spring} + F_{elec} + F_{adh}$$

=  $-k_{eff} \times g_d + \frac{1}{2} \frac{\epsilon_0 A_{ACT} V_{GB}^2}{(g_o - g_d)^2} + F_{adh}$  (1.10)

#### CHAPTER 1. INTRODUCTION

Therefore, in order to turn OFF the relay, the magnitude of the spring restoring force must be at least the sum of  $F_{elec}$  and  $F_{adh}$ :

$$k_{eff}g = F_{elec} + F_{adh}$$

$$= \frac{1}{2} \frac{\epsilon_0 A_{ACT} V_{OFF}^2}{(g_o - g_d)^2} + F_{adh}$$

(1.11)

By solving Equation 1.11, we can obtain the turn-OFF voltage  $V_{OFF}$ :

$$V_{OFF} = \sqrt{\frac{2(k_{eff}g_d - F_{adh})(g_o - g_d)^2}{\epsilon_0 A_{ACT}}}$$

(1.12)

The hysteresis voltage  $V_H$  is the minimum switching voltage needed for relay-based digital integrated circuits, and it is defined by the difference between  $V_{ON}$  and  $V_{OFF}$ .  $V_H$  can be written and simplified as:

$$V_{H} = V_{ON} - V_{OFF}$$

$$= \sqrt{\frac{2k_{eff}g_{d}(g_{o} - g_{d})^{2}}{\epsilon_{0}A_{ACT}}} - \sqrt{\frac{2(k_{eff}g_{d} - F_{adh})(g_{o} - g_{d})^{2}}{\epsilon_{0}A_{ACT}}}$$

$$= \sqrt{\frac{2(g_{o} - g_{d})^{2}}{\epsilon_{0}A_{ACT}}} \times (\sqrt{k_{eff}g_{d}} - \sqrt{k_{eff}g_{d} - F_{adh}})$$

$$= \sqrt{\frac{2(g_{o} - g_{d})^{2}}{\epsilon_{0}A_{ACT}}} \times (\frac{F_{adh}}{\sqrt{k_{eff}g_{d}} + \sqrt{k_{eff}g_{d}} - F_{adh}}})$$

$$\approx F_{adh} \sqrt{\frac{(g_{o} - g_{d})^{2}}{2\epsilon_{0}A_{ACT}k_{eff}g_{d}}}}$$

$$j if k_{eff}g_{d} \gg F_{adh}$$

$$\geq F_{adh} \sqrt{\frac{2g_{d}}{\epsilon_{0}A_{ACT}k_{eff}g_{d}}}$$

$$(1.13)$$

From Equation 1.13, it can be seen that if  $g_o$  is smaller,  $V_H$  can be smaller. But  $g_o$  has to be at least  $3g_d$  for the relay to operate in NPI mode; otherwise the device is prone to failure to turn OFF [40]. It is also worth noting that the equality in Equation 1.13 holds when

$g_d = \frac{g_o}{3}$ . Therefore, the ideal design is to make the relay operate at the boundary of PI mode and NPI mode. Moreover, decreasing  $F_{adh}$  is a crucial research topic to lower the operating voltage and thereby improve the energy efficiency of MEM relays. Methods investigated to date include self-assembled molecular coating [62–64], ion beam induced oxide formation [65], contact dimple size reduction [61], and lower temperature operation [66].

### **1.4** Dissertation Overview

In order to address the challenges of data-centric computation and the limitations of present computing systems, it is necessary to explore alternatives to the conventional von Neumann computer architecture [10].

This dissertation aims to explore micro-electro-mechanical switch technology for novel applications that facilitate implementation of non-von-Neumann computing. Operation of relays with voltage signals as small as 10 mV at cryogenic temperatures is demonstrated, for quantum computing application, and superconducting materials are considered for MEM relay contact electrodes. The use of relays as DC-voltage-driven oscillators for implementation of Ising machines is also explored.

Chapter 2 presents the ultra-low voltage operation of MEM relays at cryogenic temperatures. First, an overview of quantum computing requirements and MEM relay benefits is presented. Then the MEM relay fabrication process flow is presented, followed by a study of the temperature dependence of relay properties. Millivolt operation of relay-based integrated circuits is demonstrated at 77 K and 4 K. The results indicate that MEM relays are intriguing candidates for monolithic integration of digital control circuitry with qubits, due to their suitability for ultra-low-power and cryogenic operation.

Chapter 3 describes the requirements for relay contacting electrode material, and investigates the possibility of using a superconducting material (niobium) to further reduce relay ON-state resistance at cryogenic temperatures. A detailed integrated process flow for fabricating Nb-contact relays is presented, followed by electrical characterizations and comparisons with W-contact relays.

Chapter 4 investigates the novel application of MEM relays as DC-driven non-linear oscillators to implement Ising machines for solving combinatorial optimization problems. The effects of applied voltages on the frequency and amplitude of MEM relay oscillators are studied. Furthermore, sub-harmonic injection locking and coupling of MEM relays are demonstrated experimentally, representing a significant milestone toward networked arrays of MEM relay oscillators for building Ising machines.

Chapter 5 outlines the major results and contributions of this dissertation. Additionally, suggestions for future work are provided.

## Chapter 2

## Ultra-Low-Voltage Operation of MEM Relays for Cryogenic Logic Applications

### 2.1 Quantum Computing Benefits and Requirements

Quantum computing has gained much attention recently, because it has the potential to solve computational problems that are intractable for traditional computing paradigms [38, 67]. Promising applications for quantum computing include: machine learning [17, 18, 68, 69], database searching [70, 71], financial modeling [72–76], and cryptography [77–79].

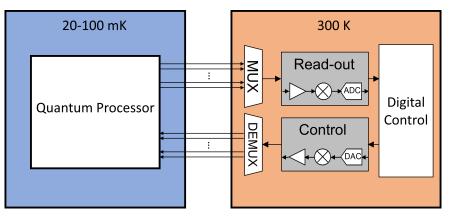

A quantum computer comprises a quantum processor and a classical electronic controller [39]. The quantum processor consists of a set of quantum bits (qubits) operating at a few tens of milli-Kelvin (mK), while the classical electronic controller that is used to read out and control the quantum processor is operated at room temperature [80], as illustrated in Figure 2.1. This approach becomes increasingly challenging and less cost-effective as the number of qubits (hence the number of interconnections between the processor and controller) grows.

Figure 2.1: Quantum processor with classical controller.

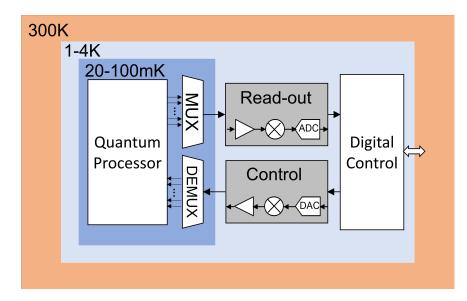

To allow for a reduction in the number of interconnections between the cryogenic chamber and the room-temperature electronics, operation of digital logic circuitry at cryogenic temperatures is of growing interest [81]. As shown in Figure 2.2, ideally the electronic control circuitry should be monolithically integrated with the qubits, at least for the multiplexer (MUX) and demultiplexer (DEMUX). These circuits should dissipate as little energy as possible in order to maintain the computer at mK temperatures [82, 83]. Otherwise qubit operation can be detrimentally impacted [84].

Figure 2.2: Monolithic integration of quantum processor with electronic control circuitry.

Therefore, improvements in energy efficiency of CMOS-based digital integrated circuits are needed for quantum computing; these generally require reductions in the circuit operating voltage,  $V_{DD}$ . In principle, MOSFETs can operate at cryogenic temperatures with very small subthreshold swing (SS). However, due to temperature-dependent oxide-interface trap density, SS for conventional bulk-silicon MOSFETs operated at 4 K is at least 10 mV/dec, which is well above the lower limit set by Boltzmann statistics [85,86]. Therefore, the supply voltage required to operate CMOS digital circuits at cryogenic temperatures is still more than 0.25 V.

Micrometer-scale electro-mechanical (MEM) relays have been experimentally demonstrated to operate with zero off-state leakage current  $(I_{OFF})$  and ultra-low switching voltage signals, enabling the demonstration of sub-50 mV digital integrated circuits at room temperature [63, 64, 87]. In this chapter, the operation of MEM relays and relay-based integrated circuits at temperatures down to 4 K is experimentally investigated for the first time [66].

### 2.2 Relay Structure and Fabrication Process

Figure 2.3 is a 30° tilted scanning electron micrograph (SEM) image of a fabricated MEM relay, which comprises a movable gate electrode suspended by four folded-flexure beams over a fixed body electrode, and two pairs of source/drain electrodes.

Figure 2.3: 30° tilted SEM image of a MEM logic relay.

The schematic cross-sectional views in Figure 2.4 show the as-fabricated air gap between the two metal conductive (source and drain) electrodes,  $g_d$ , as well as the as-fabricated actuation gap,  $g_o$ . When a voltage difference is applied between the gate and body, the electrostatic force due to the applied voltage ( $V_{GB}$ ) will actuate the movable gate towards the body. This force is opposed by the spring restoring force of the folded flexure beams. The air gap  $g_o$  is designed to be larger than three times  $g_d$  so that the relay operates in non-pull-in mode [40]. When the structure is actuated sufficiently to cause the source electrode to come into physical contact with the underlying drain electrode, current ( $I_{DS}$ ) can flow between the source and drain under the influence of an applied voltage between drain and source ( $V_{DS}$ ); this is defined as the ON-state. The minimum value of  $V_{GB}$  that causes the relay to turn ON is referred to herein as the turn-ON voltage,  $V_{ON}$ . In the ON-state, adhesive force exists between the source and drain electrodes. Therefore, to turn OFF the relay, the spring restoring force needs to exceed the sum of the adhesive force and the electrostatic force due to  $V_{GB}$ . The value of  $V_{GB}$  that is just small enough to cause the relay to turn OFF is referred to herein as the release voltage,  $V_{RL}$ . The difference between  $V_{ON}$  and  $V_{RL}$  is referred to as

the hysteresis voltage,  $V_H$ . By applying a DC bias  $(V_B)$  to the body electrode such that  $V_B = -V_{RL}$ , the relay can be switched ON and OFF by swinging the gate voltage  $(V_G)$  between 0 V and  $V_H$ . Therefore, decreasing  $V_H$  enables lower-voltage relay operation.

Figure 2.4: Schematic cross-sectional views along D-D' of Figure 2.3: (a) OFF-state (b) ON-state.

Conventional planar processing techniques are used to fabricate MEM relays, with a maximum substrate temperature below 450 °C for compatibility with post-CMOS (and postqubit) integration. Figure 2.5 illustrates the key steps in the MEM relay fabrication process, with isometric and cross-sectional views along the A-A', B-B', and C-C' cutlines defined in Figure 2.3. The starting substrate is a silicon wafer, and alignment marks are patterned on the wafer to allow subsequent deposited layers of material to be patterned in alignment with each other.

First an 80 nm-thick electrically insulating  $Al_2O_3$  layer is deposited by atomic layer deposition using a Picosun ALD system (Figure 2.5(a)). The precursor gases used are trimethylaluminum (TMA) and water vapor (H<sub>2</sub>O). The substrate temperature is set to be 300 °C. The flow of TMA from source A is set to be 150 sccm, and the H<sub>2</sub>O flow from source C is 200 sccm. The number of deposition cycles is approximately 900, which usually takes around 2 hours. An ellipsometer (Gaetner Stokes Ellipsometer) is used to check the thickness of the deposited  $Al_2O_3$  film.

Then a 60 nm-thick tungsten (W) layer is deposited by pulsed-DC sputtering using the MRC944 (MRC Sputtering System with Sputter-Etch), as shown in Figure 2.5(b). The DC source power is set to be 1 kW and the sputtering pressure is 8 mTorr; 6 sputtering cycles are required. The sheet resistance should be approximately  $3.5 \Omega/\Box$ .

Lithography and reactive ion etching (RIE) processes are performed to pattern the W layer to form fixed electrodes, including body electrodes, drain electrodes, and source electrodes, shown in Figure 2.5(c). Hexamethyldisilazane (HMDS) pre-treatment should not be used when coating the 0.43  $\mu$ m UV210 photoresist, and a hard bake step should not be used after the photoresist is developed; otherwise, it will be hard to remove the photoresist from the underlying W. An ASML DUV Stepper Model 5500/300 (ASML300) is used to expose the photoresist through a mask, with an energy dosage of 22  $mJ/cm^2$ . After the photoresist is developed, a SF<sub>6</sub> plasma in a Lam Metal TCP Etcher (Lam7) is used to remove the W in regions not protected by photoresist. The flow of SF<sub>6</sub> is 50 sccm, the upper electrode power (TCP RF) is set to be 300 W, and the lower electrode power (bias RF) is 80 W; the etching time is around 15 seconds. The photoresist is then removed by soaking in MICROPOSIT Remover 1165 at 80 °C in Msink1 (Pre-Furnace Metal Clean Sink) for at least 30 minutes, followed by ashing in oxygen plasma at 250 °C for 1 minute in Matrix (Matrix 106 Resist Removal System). The wafer needs to be cleaned in a SVC-14 bath, also in Msink1, at 80 °C for 10 minutes before entering a furnace.

Subsequently a 160 nm-thick low-temperature deposited silicon dioxide (LTO) layer is deposited as a first sacrificial layer by low pressure chemical vapor deposition (LPCVD) at 400 °C with 135 sccm  $O_2$  flow rate and 90 sccm SiH<sub>4</sub> flow rate for about 16.5 minutes, in the Tystar12 (Tystar12 Non-MOS Clean LTO LPCVD) furnace (Figure 2.5(d)). An ellipsometer is used to check the thickness of this LTO1 layer, which can be slightly greater than 160 nm.

The contact dimples are then defined by lithography and RIE processes to remove the LTO in regions over the drain electrodes (Figure 2.5(e)). HMDS pre-treatment should be used when coating the 0.43  $\mu$ m UV210 photoresist, to promote adhesion to LTO. The ASML300 is then used to expose the photoresist with an energy dosage of 20  $mJ/cm^2$ . After the photoresist is developed, the Technics-c (Technics C Plasma Etching System) is used to descum the photoresist in the small dimple regions at 50 W power for 30 seconds. Then UV bake is performed in the Axcelis (Axcelis Fusion M200PCU Photostabilizer System) using recipe U. Afterwards the Lam6 (Lam6 Oxide Rainbow Etcher) is used to etch the LTO1 film using 150 sccm Ar, 25 sccm CHF<sub>3</sub>, and 25 sccm CF4 with the TCP RF power set at 750 W for an etch rate of approximately 700 nm/min. Afterwards the wafer is soaked in MICROPOSIT Remover 1165 at 80 °C in Msink1 for 30 minutes, and processed in the Matrix for 2.5 minutes to remove any remaining photoresist. Similarly as before, a pre-furnace metal cleaning process in a SVC-14 bath at 80 °C for 10 minutes is necessary before the wafer enters a furnace.

Next, a second sacrificial layer of 60 nm-thick LTO (called LTO2) is deposited using the same LPCVD recipe in Tystar12 for about 4.5 minutes, as shown in Figure 2.5(f). Note that the thickness of the second LTO layer corresponds to  $g_d$ , while the sum of the thicknesses of the two LTO layers corresponds to  $g_o$ .

Figure 2.5: Fabrication process of tungsten-contact MEM relays, showing isometric views on the left and cross-sectional views along A-A', B-B', and C-C' cutlines on the right.

As shown in Figure 2.5(g), lithography and RIE processes are then applied to remove the LTO in regions over the fixed source electrodes. The coated photoresist is 0.87  $\mu$ m-thick UV210, exposed in AMSL300 with an energy dosage of 18  $mJ/cm^2$ . After the photoresist is developed, the same descum and UV bake steps are performed prior to etching in Lam6 for about 22 seconds to remove the LTO1 and LTO2 layers in the source anchor regions. Then the same photoresist removal and cleaning processes as before are used.

Next, a second layer of 60 nm-thick tungsten is deposited in the MRC944 using the same recipe as before (Figure 2.5(h)). This layer is patterned to form dimpled source electrodes, each extending over its corresponding drain electrode and anchored to its fixed source electrode (formed in the first W layer), as shown in Figure 2.5(i). The lithography, etching, and cleaning processes for this second W layer are the same as for the first W layer.

Next, a 55 nm-thick insulating layer of  $Al_2O_3$  is deposited by ALD using the Picosun, with approximately 550 deposition cycles (Figure 2.5(j)). Lithography and RIE processes are then used to remove this second layer of  $Al_2O_3$  and the LTO in regions over the fixed body electrodes. The UV210 photoresist is coated to be 0.87  $\mu$ m thick and is exposed with a dosage of 18  $mJ/cm^2$ , followed by developing and UV bake. A gas mixture of 30 sccm  $Cl_2$ and 60 sccm BCl<sub>3</sub> with TCP RF power = 700 W and bias RF power = 80 W was used to etch the  $Al_2O_3$  in the Lam7 etcher for about 75 seconds (Figure 2.5(k)). Then a gas mixture of 150 sccm Ar, 25 sccm CHF<sub>3</sub>, and 25 sccm CF<sub>4</sub> was used to etch LTO in the Lam6 etcher for about 28 seconds (Figure 2.5(l)). Afterwards the wafer is soaked in 1165 photoresist remover for 30 minutes, followed by a standard Matrix photoresist ashing process for 2.5 minutes, and then soaked in the SVC-14 bath for 10 minutes for pre-furnace cleaning.

Figure 2.5: Fabrication process of tungsten-contact MEM relays, showing isometric views on the left and cross-sectional views along A-A', B-B', and C-C' cutlines on the right *(cont.)*

Next a structural layer consisting of 1.9  $\mu$ m-thick p-type heavily in-situ doped polycrystalline-Si<sub>0.4</sub>Ge<sub>0.6</sub> (poly-SiGe) is deposited via LPCVD at 410 °C for approximately 4 hours in the Tystar20 (Tystar20 Non-MOS Clean Si-Ge LPCVD), as shown in Figure 2.5(m). The deposition process comprises a nucleation layer deposition step (5 minutes, 100 sccm Si<sub>2</sub>H<sub>6</sub>, 300 mTorr) followed by the poly-SiGe deposition step using 140 sccm SiH<sub>4</sub>, 60 sccm GeH<sub>4</sub>, and 45 sccm dopant gas (1% BCl<sub>3</sub> and 99% He) at 600 mTorr. These deposition conditions provide for the lowest stain gradient poly-SiGe film [88].

Lastly a 400 nm-thick LTO hard-mask layer is deposited to facilitate patterning of the thick structural layer (Figure 2.5(n)); it is deposited by LPCVD at 400 °C using the same recipe as for the LTO1 and LTO2 layers. The hard mask is patterned by coating 0.87  $\mu$ m photoresist, exposing it with an energy dosage of 18  $mJ/cm^2$  followed by developing, descum, UV bake, and etching in Lam6 for 30 seconds + 35 seconds (to avoid photoresist burning during one long etch in Lam6), as shown in Figure 2.5(o). The poly-SiGe layer is subsequently etched in Lam8 (Lam8 Poly-Si TCP Etcher) for about 310 seconds with 50 sccm Cl<sub>2</sub> and 150 sccm HBr at 12 mTorr chamber pressure, 300 W TCP RF power, and 150 W bias RF power, as shown in Figure 2.5(p). (The poly-SiGe etch rate is approximately 0.4  $\mu$ m/min.) The Al<sub>2</sub>O<sub>3</sub> layer is then etched away in the resulting exposed regions, using Lam7 with 30 sccm Cl<sub>2</sub> and 60 sccm BCl<sub>3</sub> at 700 W TCP RF and 80 W Bias RF, for about 60 seconds; this exposes the second LTO layer (Figure 2.5(q)).

Finally, vapor hydrofluoric acid (HF) is used to selectively remove the sacrificial LTO layers while avoiding capillary-force-induced stiction, as shown in Figure 2.5(r). 350 sccm of ethanol is used to desorb the H<sub>2</sub>O reaction product from the surface of the wafer, and 310 sccm of HF at 45 °C is used to remove the LTO at an etch rate of about 36 nm/min. Inert gas (1250 sccm of N<sub>2</sub>) is used to dampen the effects of changes in vapor pressures of the active gases, and to prevent ethanol saturation/condensation in the vaporizer.

Figure 2.5: Fabrication process of tungsten-contact MEM relays, showing isometric views on the left and cross-sectional views along A-A', B-B', and C-C' cutlines on the right *(cont.)*

### 2.3 Complementary Relay Operation with Body Biasing

Complementary relay operation is achieved simply by applying body biases of different polarity [64], as shown in Figure 2.6. With a negative body bias, the electrostatic field increases with increasing gate voltage, so that the relay turns ON with increasing gate voltage; this switching behavior is similar to that of an n-channel MOSFET (NMOS transistor), so a relay with negative body bias is referred to heretofore as an N-relay. With a positive body bias, the electrostatic field decreases with increasing gate voltage, so that the relay turns OFF with increasing gate voltage; this switching behavior is similar to that of a p-channel MOSFET (PMOS transistor); so a relay with positive body bias is referred to heretofore as a P-relay.

The N-Relay and P-Relay circuit symbols used herein are similar to those for NMOS and PMOS transistors, respectively. Note that for a P-relay, if  $V_G$  is zero, the device is in the ON-state. Ideally, in a complementary relay circuit, the body bias voltages should be adjusted such that the N-relays and P-relays are never both ON for the same applied gate voltage, as shown in Figure 2.6.

Figure 2.6: Complementary relay circuit symbols and I-V characteristics.

### 2.4 Temperature Dependence of Relay Properties

Changes in the electrical conductivity of the relay electrode materials are gauged by sheet resistance measurements of the contacting electrode layer (60 nm-thick W) and the structural gate electrode layer (1.9  $\mu$ m-thick p-type poly-SiGe), as shown in Figure 2.7. The poly-SiGe

does not show dopant freeze-out effects down to 1.8 K, and the resistance of W also remains low, indicating that MEM relays can operate at temperatures as low as 1.8 K. Note that the sheet resistance of the poly-SiGe layer is lower than that of the W layer; this is because the poly-SiGe layer is much thicker than the W layer.

Figure 2.7: Temperature dependence of sheet resistance for the W electrode layer and poly-SiGe structural layer.

As can be seen from Figure 2.8, the relay turn-on voltage  $(V_{ON})$  is stable over a wide range of temperatures. From the zoomed-in figure on the right, it can be seen that  $V_{ON}$ decreases slightly with decreasing temperature. This can be explained by an increase in structural stiffness, that is, an increase in the Young's modulus of the poly-SiGe film with decreasing temperature.

Figure 2.8: Temperature dependence of relay turn-ON voltage.

The relay self-oscillation frequency is used to gauge this change in Young's modulus with decreasing temperature. A DC voltage that is slightly less than  $V_{ON}$  is applied between the gate and body electrodes, while an applied  $V_{DS}$  is used to induce additional electrostatic force (in the contact dimple region) to turn on the relay (Figure 2.9). When the drain and source electrodes come into contact, the voltage difference between them decreases so the total electrostatic force decreases, causing the relay to turn off. When the source and drain electrodes are separated the voltage difference returns to the applied  $V_{DS}$ , causing the relay to turn on, and so on. Thus the relay can be made to oscillate with only DC voltages applied.

Figure 2.9: Circuit schematic for relay self-oscillation test setup.

The self-oscillation frequency ( $\omega_0$ ) of the MEM relay structure is measured at 300 K, 77 K, and 4 K respectively, as shown in Figure 2.10. Since  $\omega_0 \propto \sqrt{k} \propto \sqrt{E}$  (where k is the composite stiffness of the folded-flexure suspension beams and E is the Young's modulus), it can be qualitatively deduced that a decrease in temperature increases the Young's modulus of the structural material.

Figure 2.10: Relay self-oscillation measurements taken at different temperatures: (a) 300 K, (b) 77 K, and (c) 4 K.

The temperature dependence of the hysteresis voltage for a MEM relay is shown in Figure 2.11. It can be seen that  $V_H$  decreases dramatically with decreasing temperature, indicating that the contact adhesive force diminishes with decreasing temperature [89].

Figure 2.11: Temperature dependence of relay switching hysteresis voltage.

The average turn-ON voltage  $(V_{ON})$  and hysteresis voltage  $(V_H)$  values across 5 MEM relays are compared for room temperature vs. cryogenic temperature operation, in Figure 2.12. The average  $V_{ON}$  at 4 K (16.43 V) is similar to that at 300 K (16.23 V). A much more significant change with temperature is seen for average  $V_H$ , dropping from 120 mV at 300 K to 30 mV at 4 K.

Figure 2.12: Measured values for 5 MEM relays: (a) Average  $V_{ON}$  at 4 K and 300 K, (b) Average  $V_H$  at 4 K and 300 K.

Measured relay  $I_{DS}$ -vs.- $V_G$  characteristics are shown in Figure 2.13. As expected, the relay switches on and off abruptly as the gate voltage is swept up and down, respectively; an applied body bias voltage ( $V_B$ ) allows for low gate voltage operation. The smaller hysteresis voltage at 4 K allows MEM relay circuits to be operated with sub-10 mV voltage signals – which are roughly two orders of magnitude smaller than for MOSFETs.

Figure 2.13: Body-biased relay  $I_{DS}$ -vs.- $V_G$  characteristics at 300 K and 4 K.

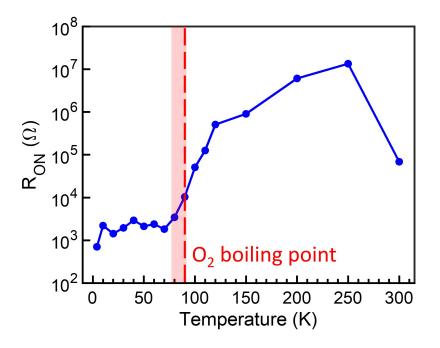

In addition to low  $V_H$ , low  $R_{ON}$  is desirable for digital circuit operation for reduced RC (electrical charging/discharging) delay. It is difficult to maintain low  $R_{ON}$  for W-contact MEM relays operating at room temperature, due to contact oxidation [46, 90, 91]. Even in a vacuum environment with 1  $\mu$ Torr pressure, trace amounts of O<sub>2</sub> can lead to native oxide formation on the surfaces of the W electrodes. Figure 2.14 shows that  $R_{ON}$  decreases dramatically for temperatures below 90 K. Since this is the boiling point of oxygen gas (O<sub>2</sub>), sub-90 K operation inhibits the formation of native oxide on the electrode surfaces and thereby allows low  $R_{ON}$  to be maintained.

Figure 2.14: Temperature dependence of relay  $R_{ON}$ .

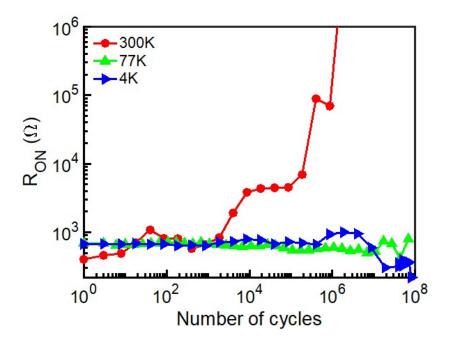

Relays used for implementing digital logic must operate properly over many switching cycles to be of practical use. Figure 2.15 compares how  $R_{ON}$  evolves over many ON/OFF switching cycles using 5 kHz square-wave gate voltage signals with 2 V gate overdrive and  $V_{DS} = 0.5$  V, at various temperatures. Considering that  $R_{ON}$  should not exceed 10 k $\Omega$  for acceptable relay-based integrated circuit performance [92], the (hot) switching endurance of a MEM relay operating at 300 K is roughly 10<sup>6</sup> cycles. For relays operated at liquid nitrogen temperature (77 K) or liquid helium temperature (4 K), however, the endurance of a relay exceeds 10<sup>8</sup> cycles, since there is no O<sub>2</sub> to oxidize the W electrodes.

Figure 2.15: Relay endurance testing at various temperatures.

Figure 2.16 shows measurements of relay turn-ON delay at 300 K and 4 K. With a preset current compliance, the voltage across the source and drain decreases when the relay turns ON; therefore, the time when the output voltage starts to drop corresponds to the time that the relay is turned ON. The mechanical turn-ON delay at 4 K (0.22  $\mu$ s) is slightly worse than that at 300 K (0.19  $\mu$ s), possibly due to lower gate overdrive ratio ( $V_{GB}/V_{ON}$ ).

Figure 2.16: Relay turn-ON delay measurements with  $V_B = 0$  V (a) at 300 K, and (b) at 4 K.

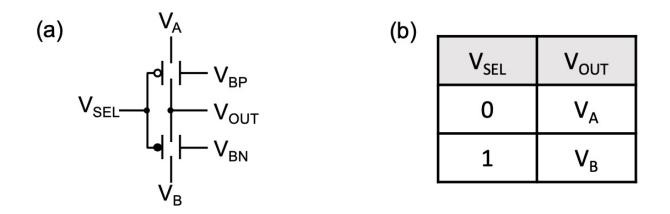

### 2.5 Millivolt Operation of Relay Integrated Circuits

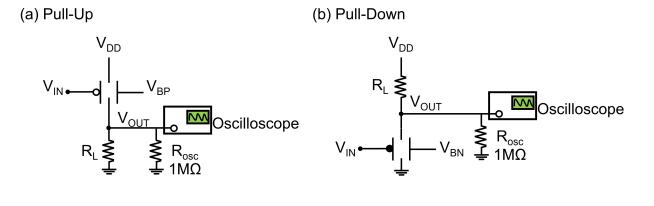

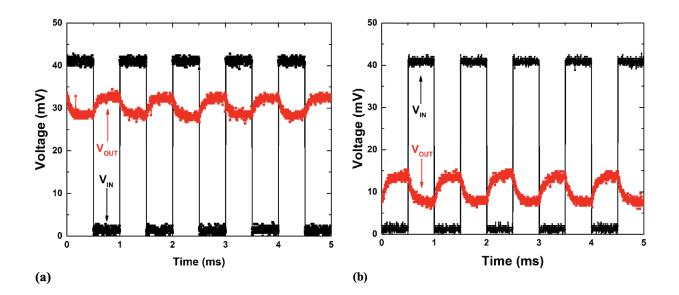

The circuit diagram and truth table for a relay-based 2:1 multiplexer integrated circuit are shown in Figure 2.17). Note that it comprises only two relays, whereas a CMOS implementation requires at least 4 transistors. The upper relay has positive body bias  $(V_{BP})$  so that it turns ON when the select voltage signal  $(V_{SEL})$  is low, while the lower relay has negative body bias  $(V_{BN})$  so that it turns ON in a complementary manner when  $V_{SEL}$  is high. Thus, the upper relay will pass the voltage signal  $V_A$  to the output (i.e.,  $V_{OUT} = V_A$ ) when  $V_{SEL}$  is low (logic '0'), and the lower relay will pass the voltage signal  $V_B$  to the output (i.e.,  $V_{OUT} = V_B$ ) when  $V_{SEL}$  is high (logic '1'). The waveforms in Figure 2.18(a) show proper circuit operation at 300 K with 100 mV signals, while the waveforms in Figure 2.18(b) show proper circuit operation at 77 K with sub-25 mV signals, made possible by smaller  $V_H$  values. (It

should be noted that  $V_{OUT}$  was monitored by an oscilloscope with an internal impedance of 1 M $\Omega$ . If a relay has high on-state resistance  $(R_{ON})$  – due to electrode surface oxide formation – the input voltage signal will not be fully passed to  $V_{OUT}$  due to the voltage divider effect.)

Figure 2.17: (a) schematic circuit diagram and (b) truth table of a relay-based 2:1 multiplexer integrated circuit.

Figure 2.18: Measured voltage waveforms demonstrating operation of a relay-based 2:1 multiplexer (a) at 300 K ( $V_{BP} = 15.5$  V,  $V_{BN} = -14.6$  V), and (b) at 77 K ( $V_{BP} = 17.07$  V,  $V_{BN} = -14.71$  V).