# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Crystal-free wireless communication with relaxation oscillators and its applications

#### **Permalink**

https://escholarship.org/uc/item/8cn151x9

#### **Author**

Burnett, David C

#### **Publication Date**

2019

Peer reviewed|Thesis/dissertation

# Crystal-free wireless communication with relaxation oscillators and its applications

by

David C Burnett

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Kristofer S.J. Pister, Chair Professor Ali M. Niknejad Professor Lance J. Kriegsfeld

Spring 2019

# Crystal-free wireless communication with relaxation oscillators and its applications

Copyright 2019 by David C Burnett

#### Abstract

Crystal-free wireless communication with relaxation oscillators and its applications

by

#### David C Burnett

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Kristofer S.J. Pister, Chair

For the last decade, the size of complete 2.4GHz wireless modules containing everything but power have stagnated at ~1cm x 1cm. This is despite continued advances in semiconductor processes due to components needed by the core communication IC. Breaking this size barrier (which also sets a power and cost barrier) by eliminating all off-chip components is the goal of the Single-Chip Mote project, of which this dissertation is a part. The major components to be eliminated are antenna, battery, and crystal oscillator. Without these components, a complete wireless module could be the size of the RFIC silicon a few millimeters on a side, or less, instead of the size of the supporting PCB.

Once those components are eliminated, advances in process scaling will lead to another size floor defined by the size of inductors, which do not scale with process. Inductor-based oscillators also put a floor on power consumption (dictated by desired swing versus achievable inductor quality factor) and, not being representable by digital cells, cannot be part of an integrated synthesis flow. In light of these limitations, understanding to what extent relaxation oscillators (the non-resonant oscillator family including RC oscillators and ring oscillators) can be used for communication is necessary to establish inductor-free performance limits and, more importantly, is necessary for future Single-Chip Mote scaling.

Contrary to general opinion, FSK communication systems based on free-running RF ring oscillators do not exhibit catastrophically poor performance but are capable of good packet delivery rate (PDR 99% or better) with moderately higher tone spacing compared to typical low-power wireless specifications (~2x when communicating with COTS base station, ~6x when communicating to another ring-based radio). Methods to work around the high jitter of rings are established; this jitter is dominated by flicker noise and is poorly represented by simulators, making accurate simulation-based design difficult. Communication and complete sensor systems can be demonstrated, and system-level chip design at the core of this work can be taught to successive generations by adopting an industrial project-based approach.

Updates and errata to this dissertation can be found at:

http://people.eecs.berkeley.edu/~db/dissertation/

To my brother

For whom I hope I've cleared a path

# Contents

| $\mathbf{C}$  | ontents                                                                                                           | ii                                     |

|---------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Li            | ist of Figures                                                                                                    | iv                                     |

| $\mathbf{Li}$ | ist of Tables                                                                                                     | x                                      |

| 1             | Introduction                                                                                                      | 1                                      |

| 2             | Reconfigurable, Wearable Sensors to Enable Long-Duration Circadian Biomedical Studies  2.1 Abstract               | 4<br>4<br>5<br>6<br>9<br>10<br>12      |

| 3             | Narrowband communication with free-running 2.4GHz ring oscillators 3.1 Abstract                                   | 15<br>15<br>16<br>17<br>20<br>25<br>32 |

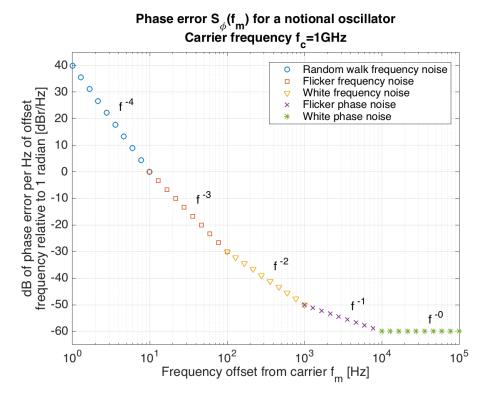

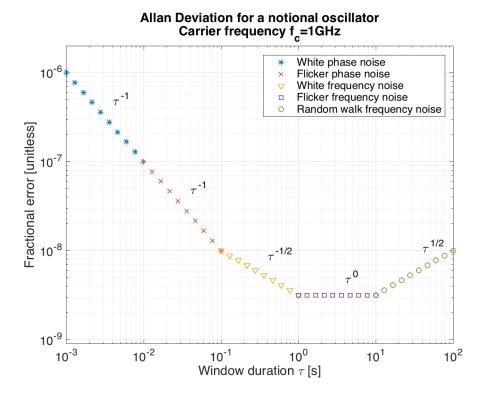

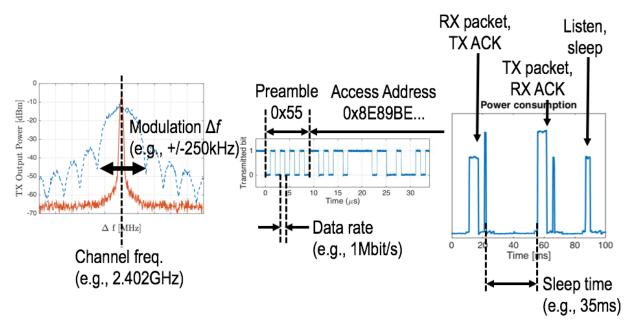

| 4             | Jitter and Phase Noise 4.1 Phase noise and jitter properties                                                      | 34<br>34<br>39<br>42                   |

| 5             | CMOS oscillators to satisfy 802.15.4 and Bluetooth LE PHY specifications without a crystal reference 5.1 Abstract | <b>45</b><br>45                        |

| 5.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

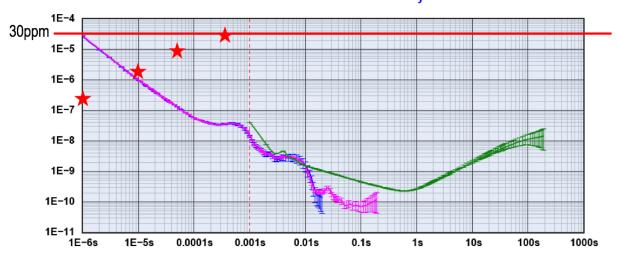

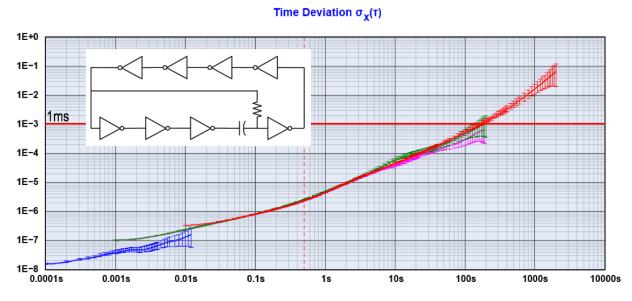

| 5.5 32kHz sleep timer jitter calculation and simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| O D COLUMN THE LANGE TO THE PARTY OF THE PAR |    |

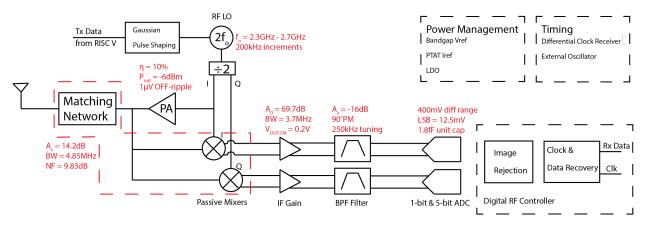

| 6 Free-running 2.4GHz ring oscillator-based FSK $TX/RX$ for ultrasmall form factors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 6.1 Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

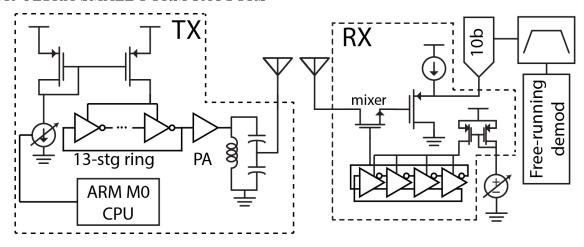

| 6.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

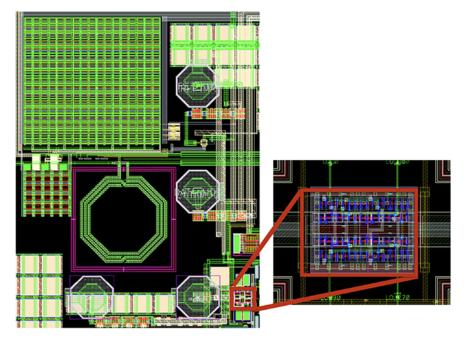

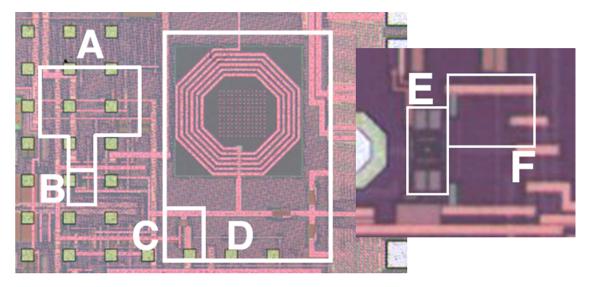

| 6.3 Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 6.4 Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 7 Demonstrated Sensor Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

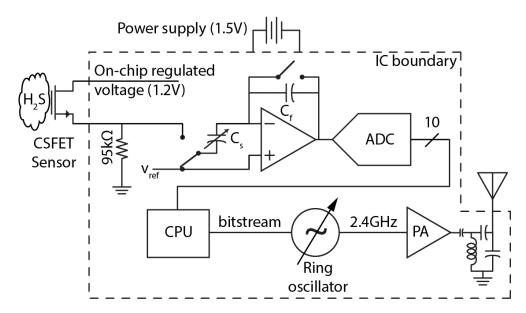

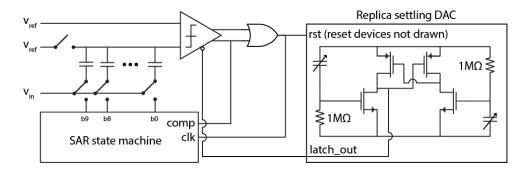

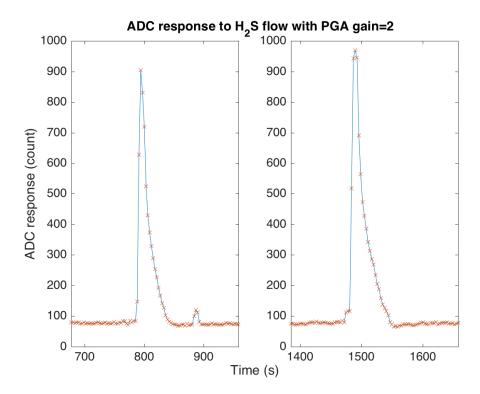

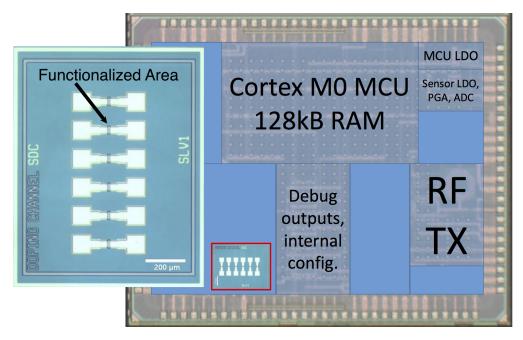

| 7.1 Two-chip Wireless H <sub>2</sub> S Gas Sensor System Requiring Zero Additional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| Electronic Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 7.2 Testing with other chemical sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 8 Tapeout class: taking students from schematic to silicon in one semeste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | er |

| 8.1 Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 8.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 8.3 Overcoming student misconceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 8.4 Teaching assistant to project manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 8.5 Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 8.6 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 8.7 Course Acknowledgement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 9 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| A SCM3 Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| A.1 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

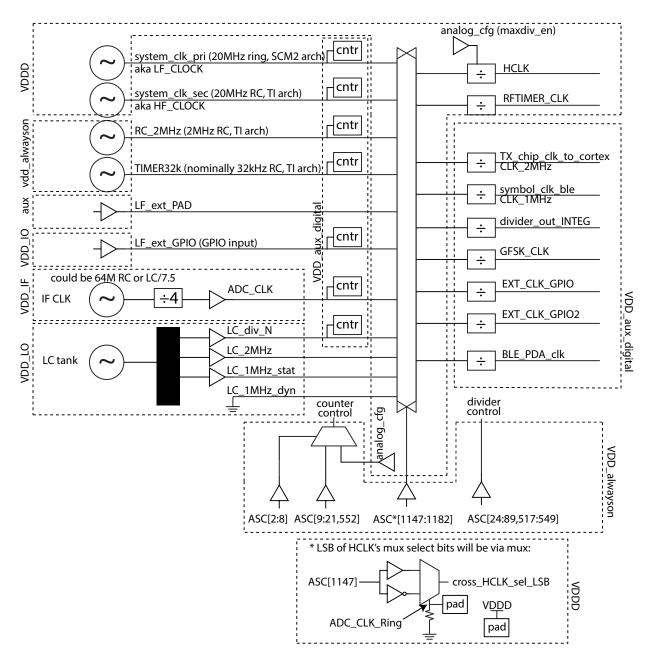

| A.2 SCM3B Clock network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

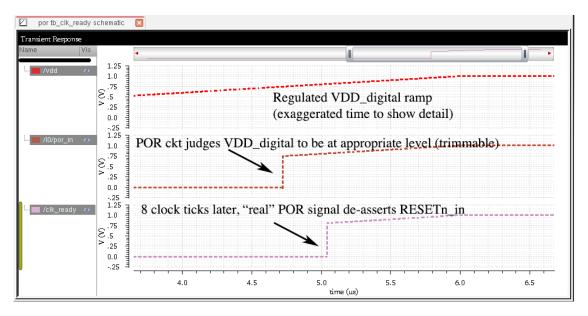

| A.3 Power-on reset (POR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

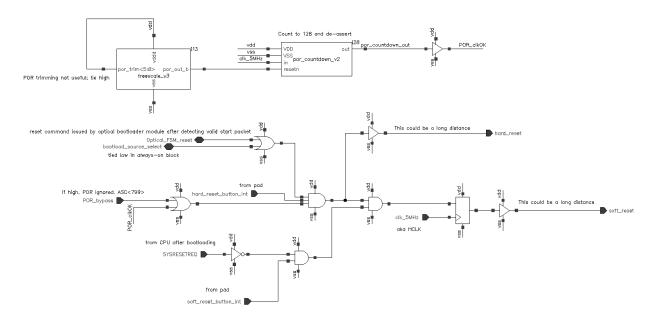

| A.4 Reset logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| B General lab advice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

# List of Figures

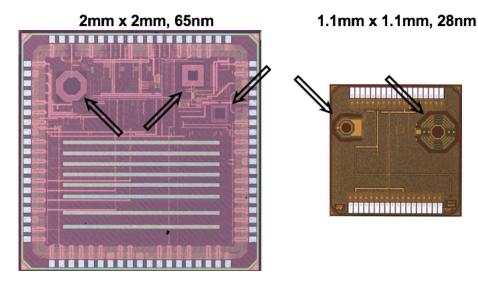

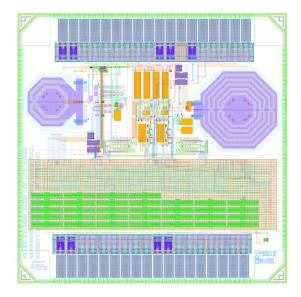

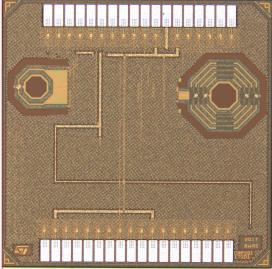

| 1.1 | Low-power wireless ICs with planar inductors indicated by arrows. ICs are pictured to relative scale. Inductors range in value from 0.8nH to 9nH. Left: Second-generation single-chip mote IC in TSMC 65nm bulk process, which included the first microprocessor-based digital system [7]. Right: IC in STMicro |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 28nm FD-SOI process, designed and fabricated as part of our new course [16].                                                                                                                                                                                                                                    | 2  |

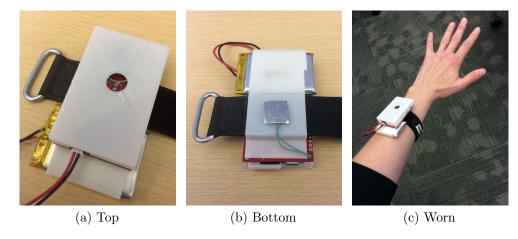

| 2.1 | Photos of current device showing light port 2.1a, skin temperature plate 2.1b,                                                                                                                                                                                                                                  | _  |

|     | and device in use 2.1c                                                                                                                                                                                                                                                                                          | 7  |

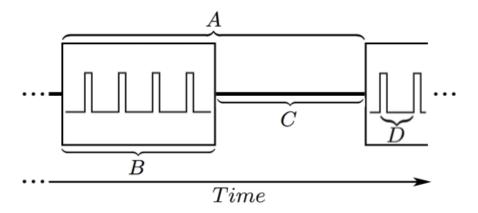

| 2.2 | Data collection timing diagram. Each pulse represents one set of sensor data                                                                                                                                                                                                                                    |    |

|     | sampled and logged. Time A is the time between the start of each sampling                                                                                                                                                                                                                                       |    |

|     | block. Time B is the duration of each sampling block. Time C is the time                                                                                                                                                                                                                                        |    |

|     | spent outside of a sampling block, when the device is in sleep mode to conserve                                                                                                                                                                                                                                 |    |

|     | power. Time D is the time between samples. Times A, B, and D are all                                                                                                                                                                                                                                            |    |

| 0.0 | user-defined via an interactive Python script                                                                                                                                                                                                                                                                   | 8  |

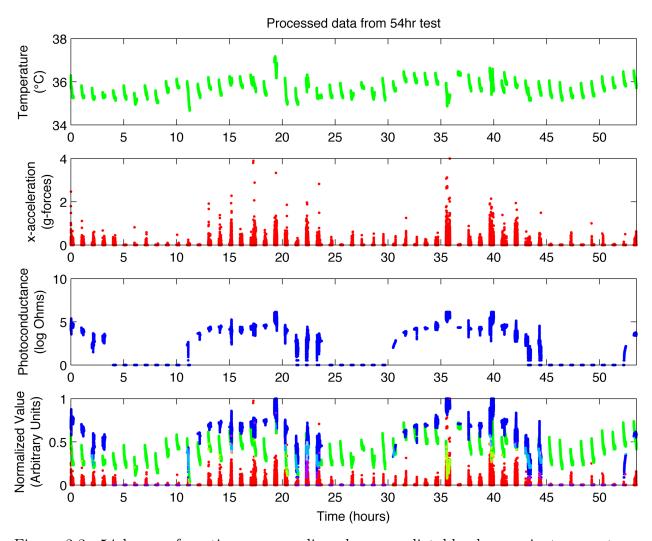

| 2.3 | 54 hours of continuous recording shows predictable changes in temperature, activity, and light across three nights and two days. A normalized, combined                                                                                                                                                         |    |

|     | overlay is also provided. Note that time to change batteries is not apparent in                                                                                                                                                                                                                                 |    |

|     | the data                                                                                                                                                                                                                                                                                                        | 11 |

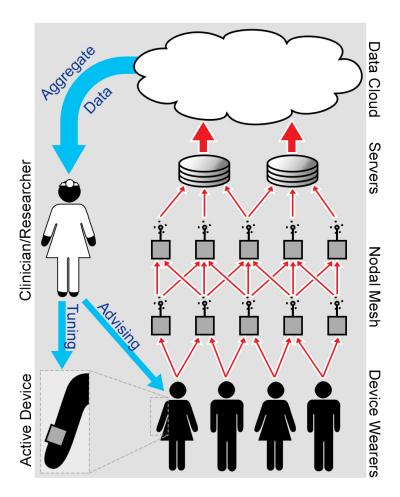

| 2.4 | Conceptualized ambient network to collect and process wearable health monitor                                                                                                                                                                                                                                   |    |

|     | data                                                                                                                                                                                                                                                                                                            | 13 |

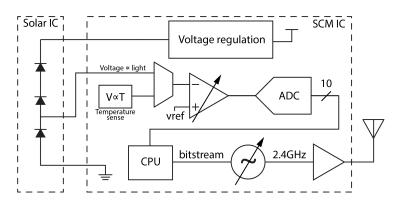

| 2.5 | Conceptual miniaturized "armband"-style system based on 2mm x 3mm single-                                                                                                                                                                                                                                       |    |

|     | chip mote (SCM) platform. Current iteration of SCM includes temperature                                                                                                                                                                                                                                         |    |

|     | sensor and external input to PGA/ADC frontend. A 3mm x 3mm solar power                                                                                                                                                                                                                                          |    |

|     | IC (current iteration called "Zappy2") was developed to power SCM from a                                                                                                                                                                                                                                        |    |

|     | nominally 1.2V supply created from three diodes in series. The voltage across                                                                                                                                                                                                                                   |    |

|     | one diode could be connected to the external ADC input to get a relative                                                                                                                                                                                                                                        |    |

|     | indication of ambient light                                                                                                                                                                                                                                                                                     | 14 |

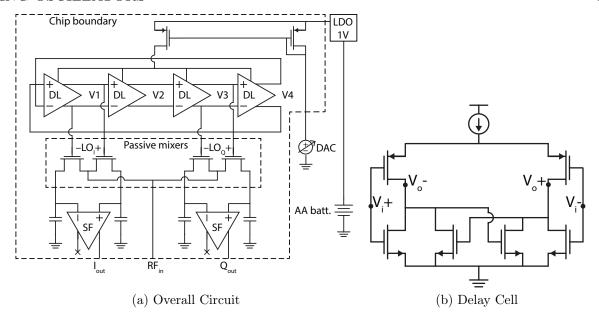

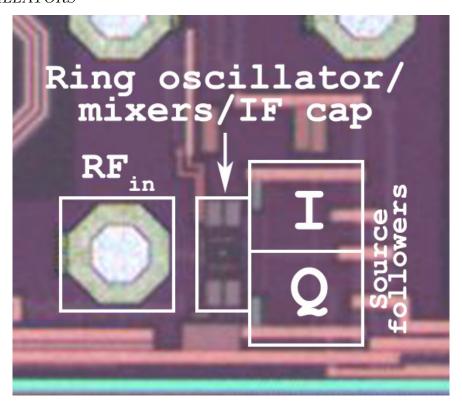

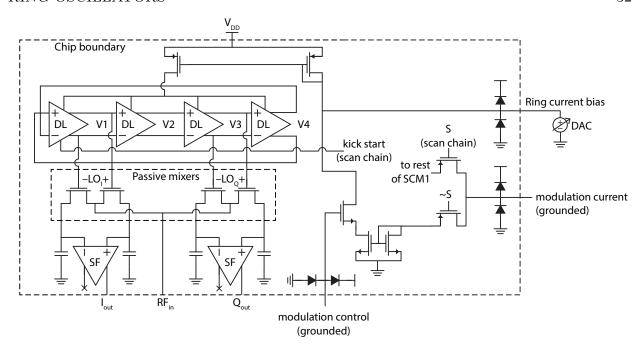

| 3.1 | Experimental oscillator & NMOS passive mixer structure, as fabricated in a 65nm bulk process, diagrammed in 3.1a. Minimum-size ring oscillator containing 4 differential delay cells (DL) in 3.1b drives single-balanced passive mixers downconverting RF signal provided by test equipment. Mixed-down intermediate frequency passes into source followers (SF) with high drive strength to                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

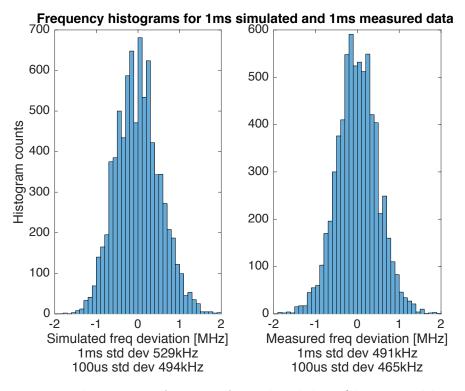

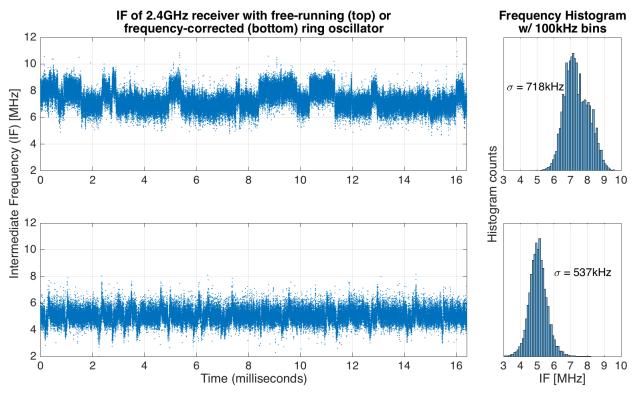

| 3.2 | pass signal off-chip. Not shown: kick-start circuit to prevent even number of ring stages from latching at power-on (only possible if cross-coupled NMOS devices in (b) are overpowered by inverters and allow $V_o + = V_i - 1$ Frequency histograms for 1ms of simulated data (determined by computational limitations) and a 1ms portion of a 16ms oscilloscope capture. Both frequency distributions were obtained from nominally 8MHz intermediate frequencies resultant from an RF input derived from ideal source (simulation) or test                                                                                                                                                                                                                                                                                       | 17 |

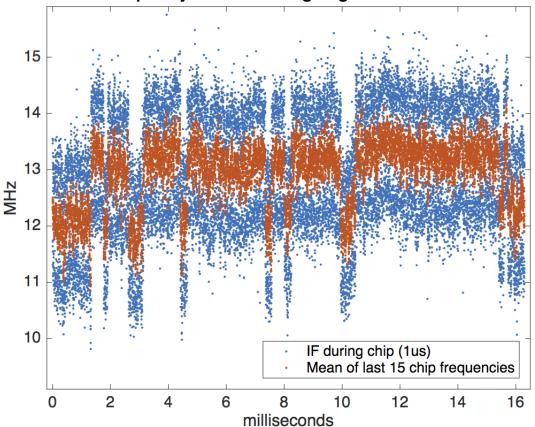

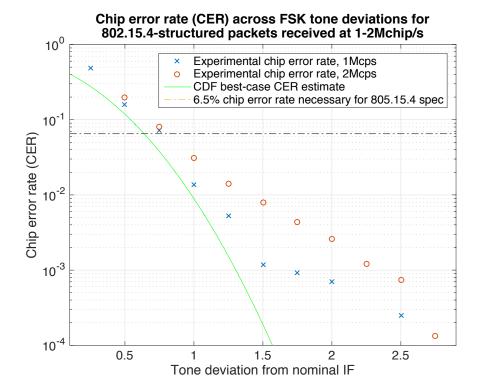

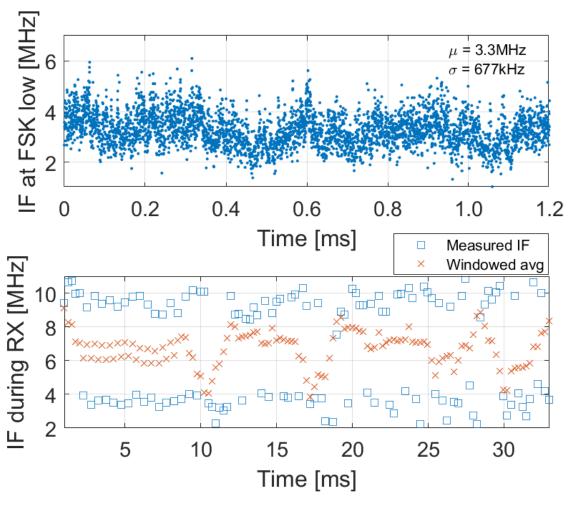

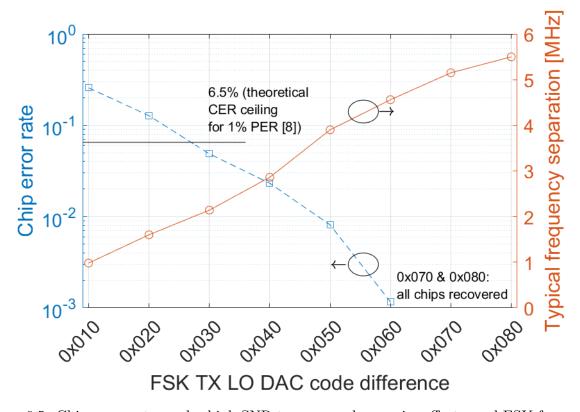

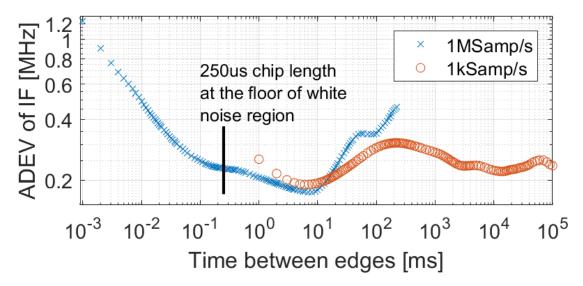

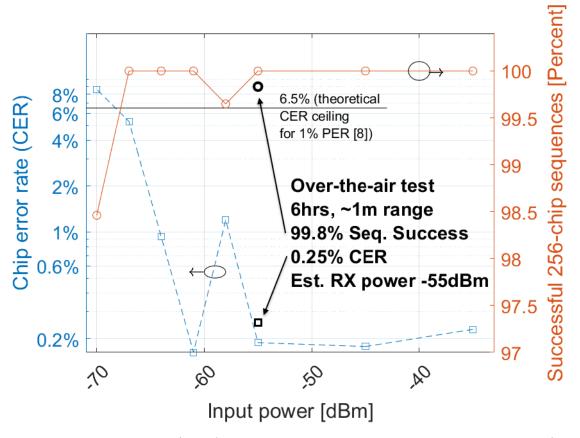

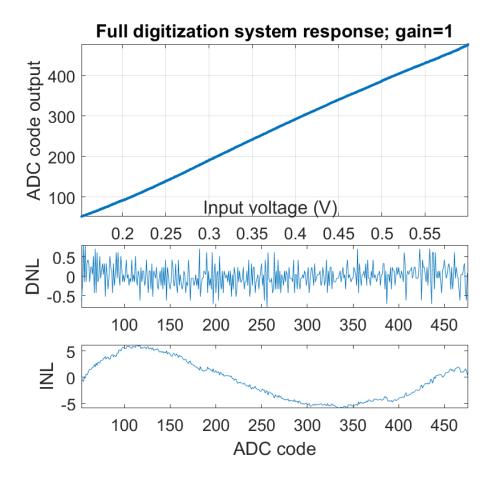

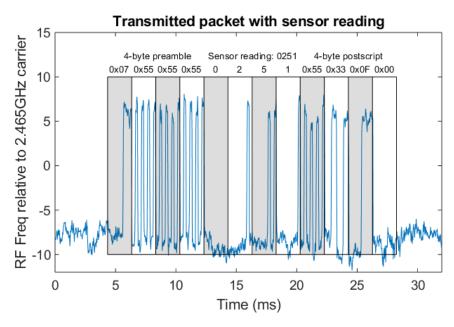

|     | equipment (measurement) mixed with a free-running ring oscillator. Standard deviations, or jitter, indicate that simulation and measurement are in good agreement. Standard deviation value for 1ms is calculated over full histogram period. Standard deviation value for $100\mu$ s is mean of jitter over 10 non-overlapping $100\mu$ s windows. Note: time-series of frequency data forming measured histogram on right is displayed in top half of Figure 3.9                                                                                                                                                                                                                                                                                                                                                                  | 19 |

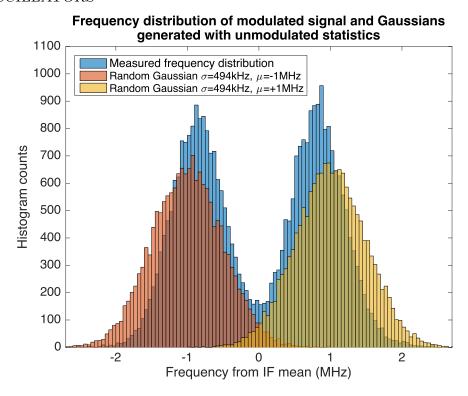

| 3.3 | Distribution of measured frequency for 2Mchip/s and $\pm 1$ MHz tone separation. Also plotted are two normally-distributed random values with measured standard deviation 494kHz, as displayed in Figure 3.2, and means of $\pm 1$ MHz. Experimental data has been post-processed to subtract the windowed average (described in Section 3.5 and displayed in Figure 3.6). This can be thought of a histogram of frequency-distances-from-moving-average. The raw measured histogram looks like a single Gaussian distribution, but subtracting the (moving) average exposes the two groupings of high and low frequency resultant from FSK modulation. This subtraction is likely responsible for the reduction in standard deviation and frequency shift, which is about 375kHz and $\pm 0.87$ MHz for each of the two modalities | 20 |

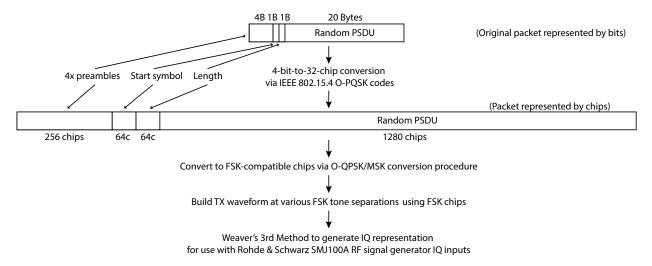

| 3.4 | Layout of 26 Byte packet, conversion to 1664 chip packet, and following steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 3.5 | in flow to generate signals received from test equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23 |

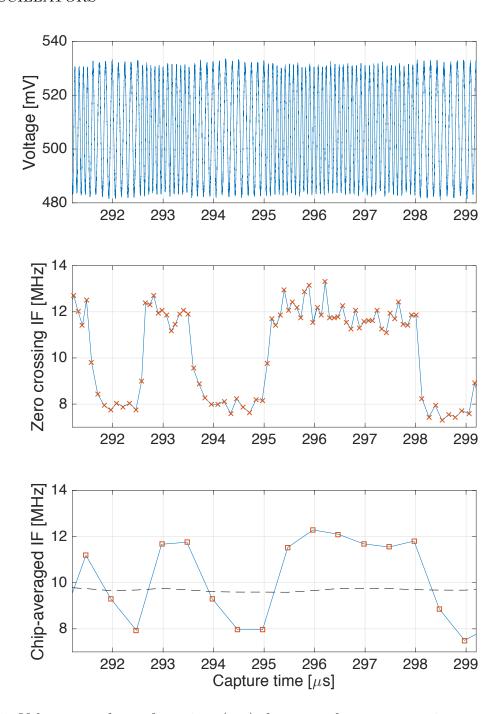

|     | per-chip frequency is compared to determine 0 or 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24 |