## UCLA UCLA Electronic Theses and Dissertations

## Title

Safe and Efficient Concurrency for Modern Programming Languages

## Permalink

https://escholarship.org/uc/item/8d04d8bx

# Author

Liu, Lun

# Publication Date 2020

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA

Los Angeles

Safe and Efficient Concurrency for Modern Programming Languages

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Lun Liu

© Copyright by Lun Liu 2020

#### ABSTRACT OF THE DISSERTATION

Safe and Efficient Concurrency for Modern Programming Languages

by

#### Lun Liu

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2020 Professor Todd D. Millstein, Chair

Safe languages provide programming abstractions, like type and memory safety, to improve programmer productivity. Unfortunately, in the domain of concurrent programming, mainstream safe languages instead choose to adopt complex and error-prone semantics by default in the name of performance. A *memory consistency model* defines the possible values that a shared-memory read may return in a multithreaded programming language. Languages today like Java and Julia have adopted a *relaxed* (or *weak*) memory model that is designed to admit most traditional compiler optimizations and obviate the need for hardware fences on most shared-memory accesses. The downside, however, is that programmers are exposed to a complex and unintuitive semantics and must carefully declare certain variables as volatile in order to enforce program orderings that are necessary for proper behavior. Not only does this *performance-by-default* approach conflict with the design philosophy of "safe" languages, but also surprisingly, very little is actually known about the practical performance cost of a stronger memory model.

In this thesis, I define the safe-by-default and performant-by-choice volatile-by-default semantics for Java and other JVM-based languages. volatile-by-default provides sequential consistency (SC) by default, while still allows expert programmers to avoid fence overheads on performance-critical libraries. I present VBD-HotSpot and VBDA-HotSpot, modifications of Oracle's HotSpot JVM that enforce the volatile-by-default semantics on Intel X86 hardware and ARM hardware. I then present a novel *speculative* technique to optimize language-level SC. Finally, I have implemented an SC enforcing Julia compiler that guarantees SC for Julia by default. Through evaluations of the above projects, I show that it is possible to measure the practical cost of strong and simple semantics for concurrent programming, and with optimizations, it is possible to have a simpler semantics for concurrent programming at a reasonable cost for certain languages.

The dissertation of Lun Liu is approved.

Harry Guoqing Xu

George Varghese

Jens Palsberg

Madan Musuvathi

Todd D. Millstein, Committee Chair

University of California, Los Angeles

2020

To my mother, for showing me the strength of a woman, and supporting me every step of the way.

## TABLE OF CONTENTS

| 1        | $\operatorname{Intr}$ | oducti  | on                                            | 1  |

|----------|-----------------------|---------|-----------------------------------------------|----|

|          | 1.1                   | Proble  | ems with Memory Models of Today's Languages   | 1  |

|          | 1.2                   | Thesis  | Statement                                     | 3  |

|          | 1.3                   | Thesis  | Organization                                  | 4  |

| <b>2</b> | Bac                   | kgrour  | $\operatorname{nd}$                           | 5  |

|          | 2.1                   | Memo    | ry Models and Compiler/Hardware Optimizations | 5  |

|          |                       | 2.1.1   | The Java Memory Model                         | 6  |

|          |                       | 2.1.2   | Missing-annotation bugs                       | 8  |

|          |                       | 2.1.3   | The Julia Memory Model                        | 9  |

|          | 2.2                   | The H   | otSpot Java Virtual Machine                   | 11 |

|          |                       | 2.2.1   | The HotSpot JVM Interpreter                   | 11 |

|          |                       | 2.2.2   | The HotSpot JVM Compiler                      | 12 |

|          | 2.3                   | The J   | ulia Compiler                                 | 13 |

| 3        | vola                  | atile-b | oy-default JVMs for Server Applications       | 14 |

|          | 3.1                   | Introd  | uction                                        | 14 |

|          | 3.2                   | volat   | ile-by-default Semantics for Java             | 18 |

|          | 3.3                   | volat   | ile-by-default JVMs for X86 and ARM           | 20 |

|          |                       | 3.3.1   | volatile-by-default Interpreter               | 21 |

|          |                       | 3.3.2   | volatile-by-default Compiler                  | 23 |

|          |                       | 3.3.3   | Optimizations                                 | 26 |

|          |                       | 3.3.4   | Correctness                                   | 27 |

|          |                       | 3.3.5   | volatile-by-default for Java and Scala        | 27 |

|   | 3.4 | Perfor | mance Evaluation of volatile-by-default                            | 28 |

|---|-----|--------|--------------------------------------------------------------------|----|

|   |     | 3.4.1  | Performance Evaluation of VBD-HotSpot                              | 28 |

|   |     | 3.4.2  | Performance Evaluation of VBDA-HotSpot                             | 42 |

| 4 | A S | pecula | tive Implementation of volatile-by-default                         | 54 |

|   | 4.1 | Design | n Overview                                                         | 54 |

|   | 4.2 | Imple  | mentation                                                          | 56 |

|   | 4.3 | Imple  | menting Per-Access Checks                                          | 60 |

|   | 4.4 | Optim  | nizing Fence Insertion                                             | 60 |

|   | 4.5 | Perfor | mance Evaluation                                                   | 62 |

|   |     | 4.5.1  | DaCapo Benchmarks                                                  | 62 |

|   |     | 4.5.2  | CheckOnly Overhead                                                 | 64 |

|   |     | 4.5.3  | Spark Benchmarks                                                   | 64 |

| 5 | A S | equen  | tial Consistency Enforcing Julia Compiler                          | 67 |

|   | 5.1 | Design | n Overview                                                         | 68 |

|   | 5.2 | Imple  | mentation                                                          | 69 |

|   |     | 5.2.1  | AddSC LLVM Pass                                                    | 69 |

|   |     | 5.2.2  | Rewrite Loads and Stores using Atomic and Fence Instructions       | 70 |

|   |     | 5.2.3  | Caveats                                                            | 72 |

|   |     | 5.2.4  | Optimizations                                                      | 72 |

|   |     | 5.2.5  | @drf annotations                                                   | 75 |

|   | 5.3 | Exper  | iments                                                             | 77 |

|   |     | 5.3.1  | BaseBenchmarks                                                     | 77 |

|   |     | 5.3.2  | Understanding the Impact of SC: Compiler Optimizations vs Hardware |    |

|   |     |        | Fences                                                             | 79 |

|    | 5.3.3       | @drf annotations               | 81 |

|----|-------------|--------------------------------|----|

|    | 5.3.4       | Hardware Instruction Selection | 82 |

| 6  | Related V   | Vork                           | 85 |

| 7  | Conclusio   | n                              | 88 |

| Re | eferences . |                                | 91 |

## LIST OF FIGURES

| 2.1  | An implementation of Dekker's mutual exclusion algorithm in Julia which is not       |    |

|------|--------------------------------------------------------------------------------------|----|

|      | guaranteed to work correctly                                                         | 10 |

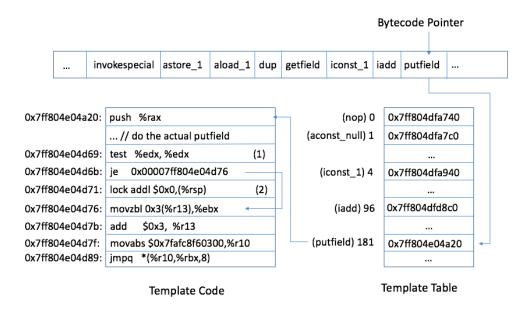

| 2.2  | Interpretation example of bytecode <pre>putfield</pre>                               | 12 |

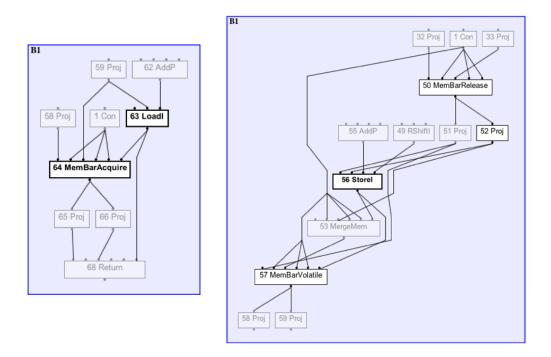

| 3.1  | Ideal graph sections for volatile loads (left) and stores (right)                    | 24 |

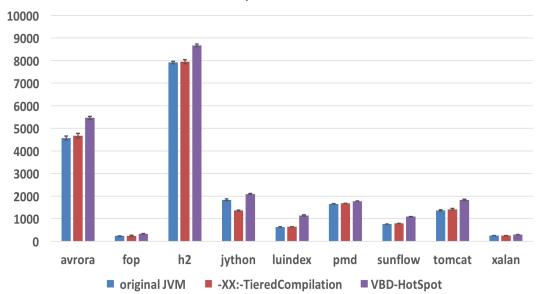

| 3.2  | Execution time in milliseconds of VBD-HotSpot on the DaCapo benchmarks.              |    |

|      | "original JVM" means running the baseline HotSpot JVM without additional             |    |

|      | $flags; ``-XX:-{\tt TieredCompilation}" means running the baseline HotSpot JVM with$ |    |

|      | -XX:-TieredCompilation; "VBD-HotSpot" shows results of running VBD-HotSpot.          | 29 |

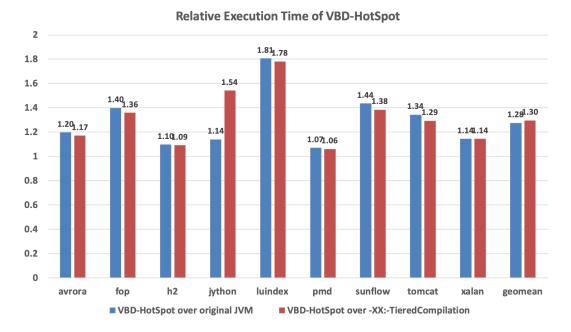

| 3.3  | Relative execution time of VBD-HotSpot on the DaCapo benchmarks                      | 29 |

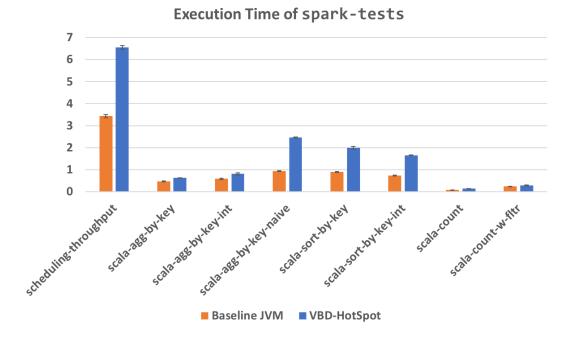

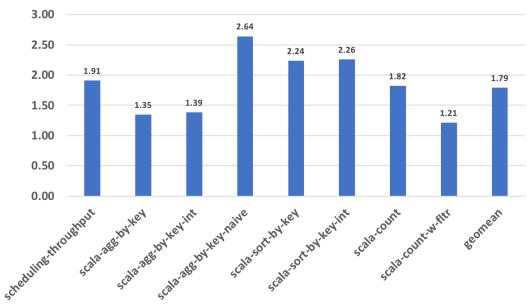

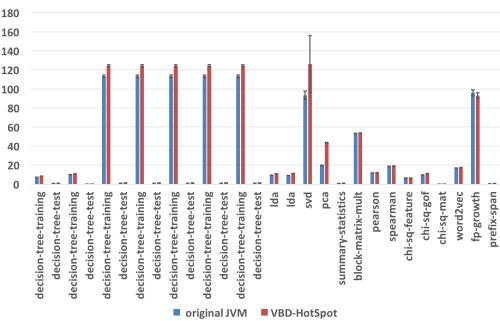

| 3.4  | Median execution time in seconds for spark-tests                                     | 32 |

| 3.5  | Relative execution time of VBD-HotSpot over the baseline JVM for ${\tt spark-tests}$ | 32 |

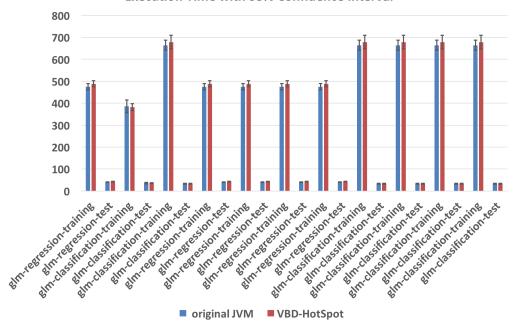

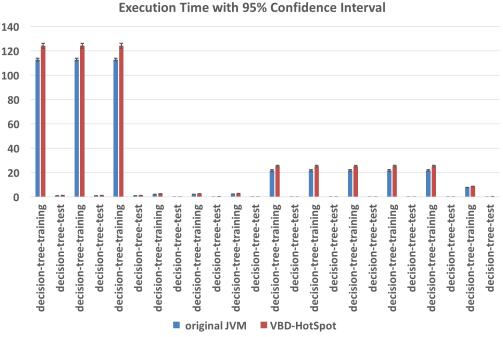

| 3.6  | Average of 10 median execution times in seconds with $95\%$ confidence intervals     |    |

|      | for mllib-tests (part 1 of 4)                                                        | 33 |

| 3.7  | Average of 10 median execution times in seconds with $95\%$ confidence intervals     |    |

|      | for mllib-tests (part 2 of 4)                                                        | 34 |

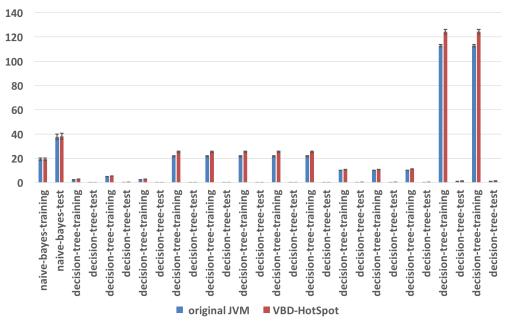

| 3.8  | Average of 10 median execution times in seconds with $95\%$ confidence intervals     |    |

|      | for mllib-tests (part 3 of 4)                                                        | 34 |

| 3.9  | Average of 10 median execution times in seconds with $95\%$ confidence intervals     |    |

|      | for mllib-tests (part 4 of 4)                                                        | 35 |

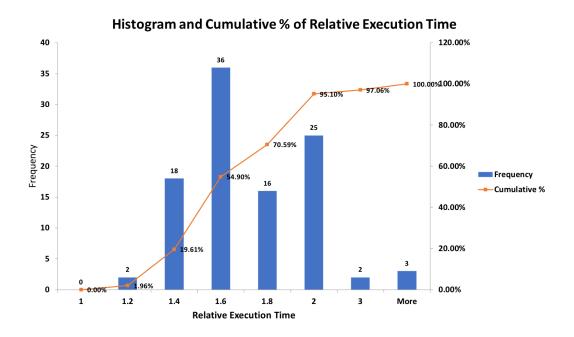

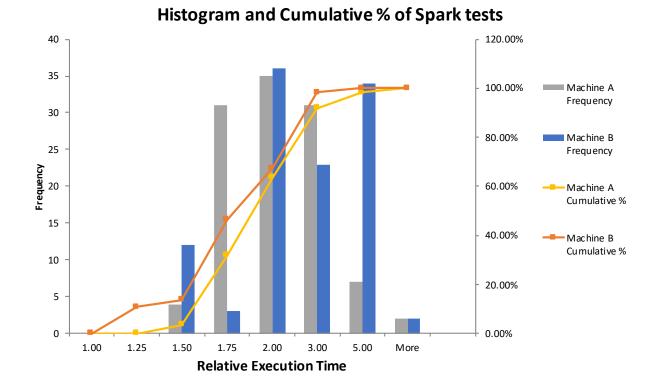

| 3.10 | Histogram and cumulative $\%$ of relative execution time for $\texttt{mllib-tests}$  | 36 |

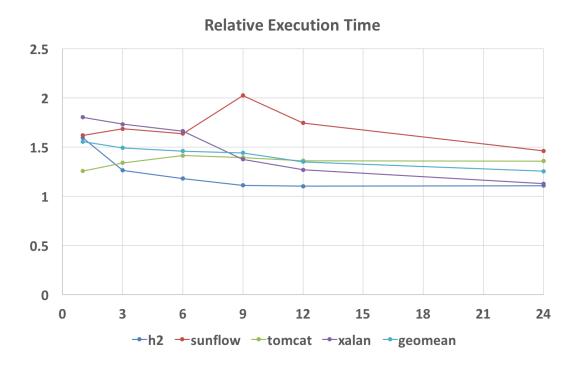

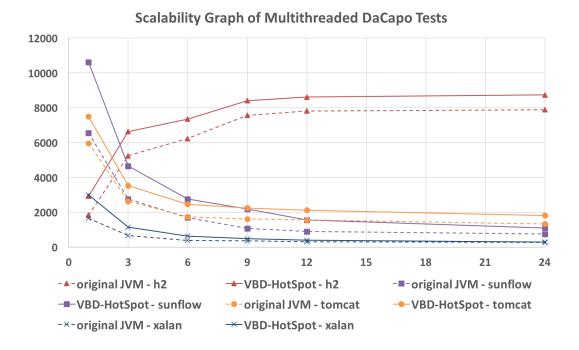

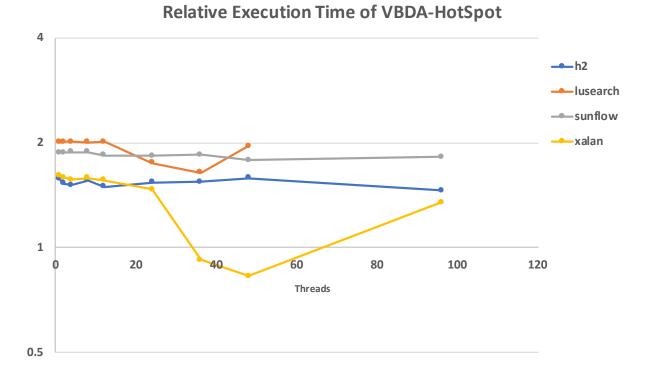

| 3.11 | Relative cost of VBD-HotSpot with different numbers of threads/cores $\ . \ . \ .$ . | 37 |

| 3.12 | Scalability graph with different numbers of threads/cores                            | 38 |

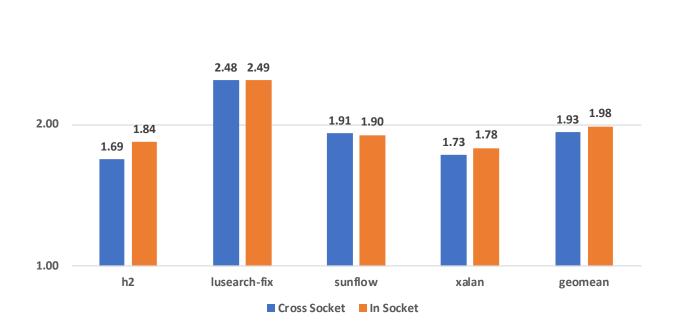

| 3.13 | Cost of VBD-HotSpot within socket and cross-socket                                   | 39 |

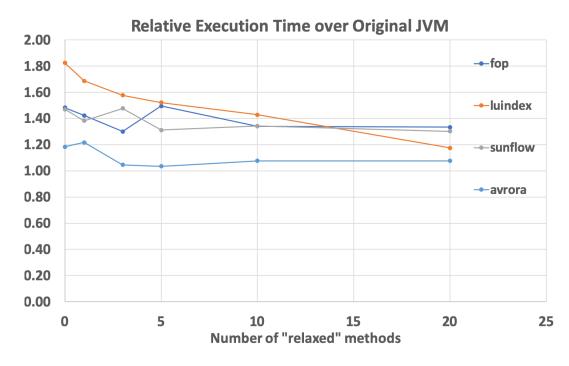

| 3.14 | Cost of VBD-HotSpot with relaxed methods                                             | 40 |

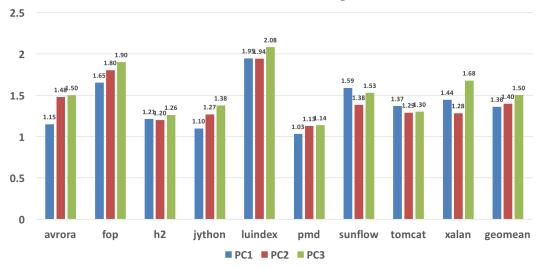

|      |                                                                                      |    |

| 3.15 | Relative execution time of the DaCapo benchmarks                                  | 41 |

|------|-----------------------------------------------------------------------------------|----|

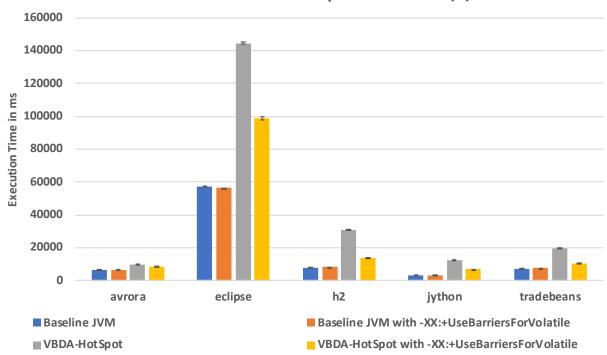

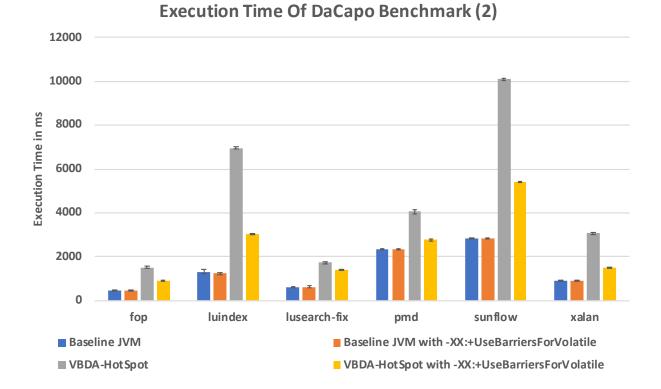

| 3.16 | Absolute execution time of VBDA-HotSpot and baseline JVM for DaCapo bench-        |    |

|      | marks on machine A                                                                | 43 |

| 3.17 | Absolute execution time of VBDA-HotSpot and baseline JVM for DaCapo bench-        |    |

|      | marks on machine A                                                                | 44 |

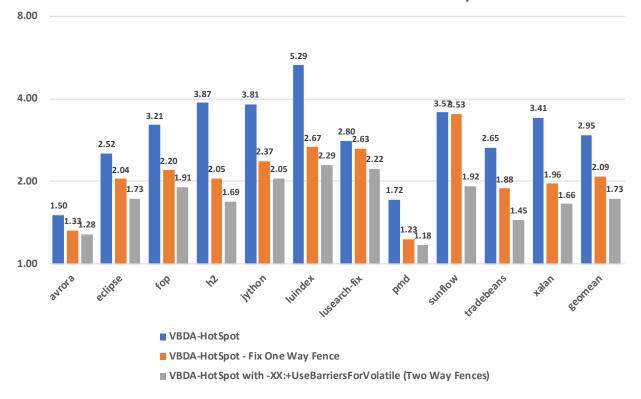

| 3.18 | Relative execution time of VBDA-HotSpot, VBDA-HotSpot with bug fix for            |    |

|      | one way fences, VBDA-HotSpot with two way fences on machine A, y-axis in          |    |

|      | logarithmic scale.                                                                | 45 |

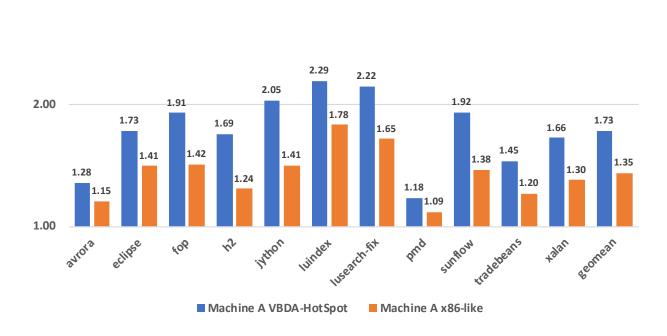

| 3.19 | Relative execution time of VBDA-HotSpot and X86-like VBDA-HotSpot over            |    |

|      | baseline JVM for DaCapo on machine A, y-axis in logarithmic scale                 | 46 |

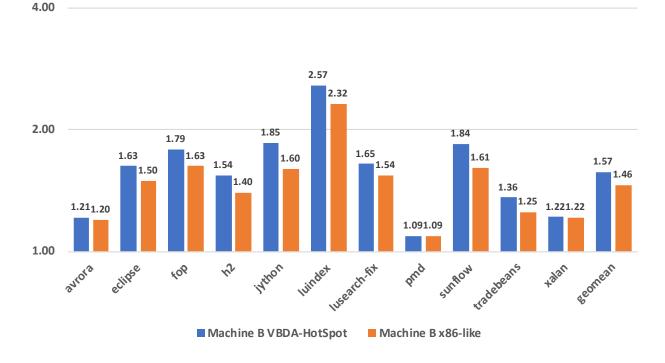

| 3.20 | Relative execution time of VBDA-HotSpot and X86-like VBDA-HotSpot over            |    |

|      | baseline JVM for DaCapo on machine B, y-axis in logarithmic scale                 | 47 |

| 3.21 | Relative cost of VBDA-HotSpot with different numbers of threads/cores on ma-      |    |

|      | chine B. lusearch does not support running with 96 threads, y-axis in logarithmic |    |

|      | scale                                                                             | 49 |

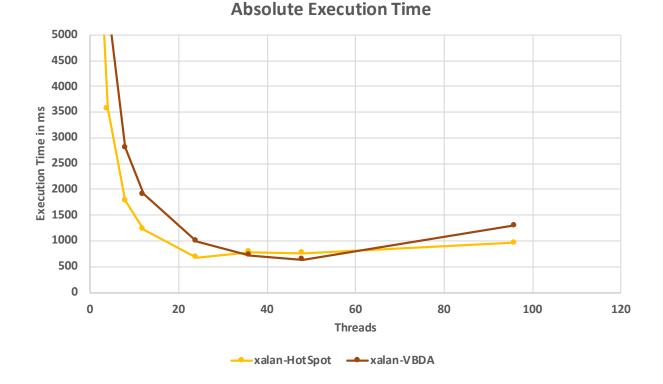

| 3.22 | Execution time of VBDA-HotSpot and baseline JVM running xalan with different      |    |

|      | numbers of threads/cores on machine B                                             | 50 |

| 3.23 | Cost of VBDA-HotSpot cross-socket and within socket on machine A, y-axis in       |    |

|      | logarithmic scale.                                                                | 51 |

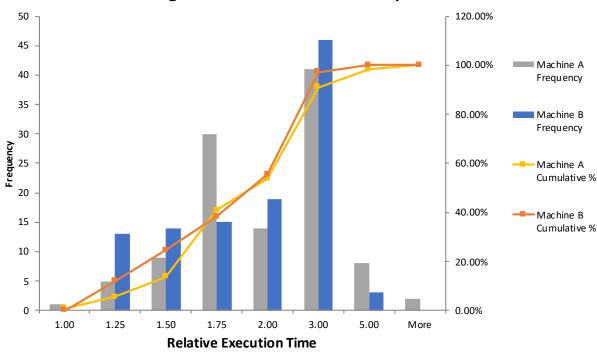

| 3.24 | Histogram and cumulative $\%$ of relative execution time of VBDA-HotSpot for      |    |

|      | Spark benchmarks.                                                                 | 52 |

| 4.1  | Just-in-time compilation of a method.                                             | 57 |

| 4.2  | The <i>slow</i> and <i>fast</i> versions of a method                              | 58 |

| 4.3  | The interpreted version of a method                                               | 59 |

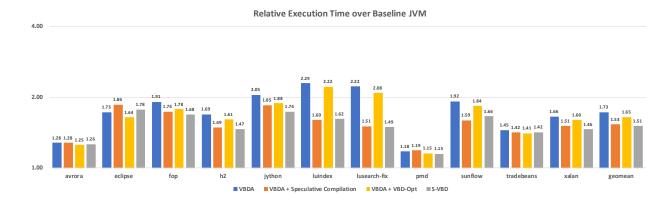

| 4.4 | Relative execution time of VBDA + speculative compilation, VBDA + VBD-Opt,          |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | S-VBD over the baseline JVM compared to VBDA-HotSpot on machine A, y-axis           |    |

|     | in logarithmic scale.                                                               | 62 |

| 4.5 | Relative execution time of VBDA + speculative compilation, VBDA + VBD-Opt,          |    |

|     | S-VBD over the baseline JVM compared to VBDA-HotSpot on machine B, y-axis           |    |

|     | in logarithmic scale.                                                               | 63 |

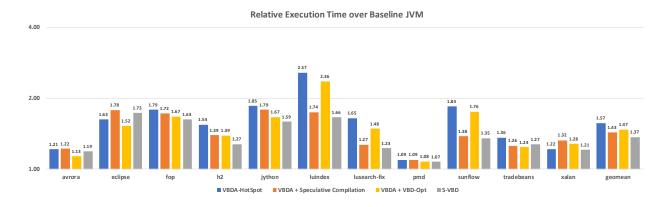

| 4.6 | Relative startup execution time of VBDA-HotSpot and S-VBD over the baseline         |    |

|     | JVM, y-axis in logarithmic scale.                                                   | 64 |

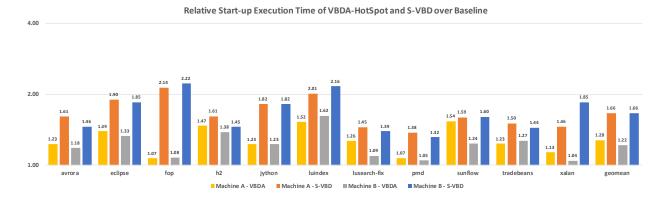

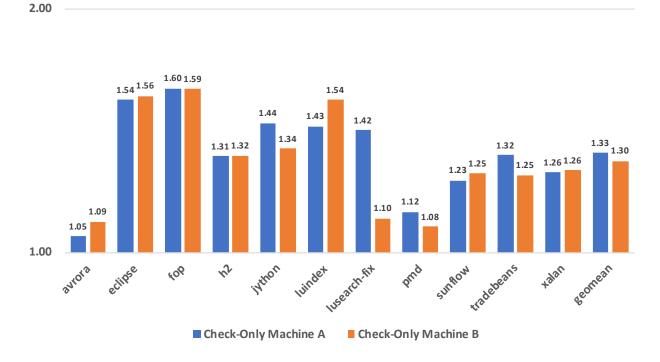

| 4.7 | Relative execution time of check-only S-VBD over baseline JVM on machine A          |    |

|     | and machine B, y-axis in logarithmic scale                                          | 65 |

| 4.8 | Histogram and cumulative $\%$ of relative execution time of VBDA-HotSpot for        |    |

|     | Spark benchmarks                                                                    | 66 |

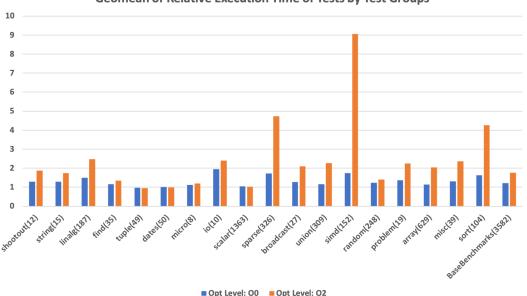

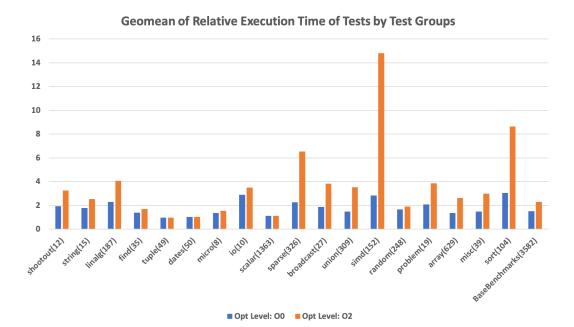

| 5.1 | Geometric mean of relative execution time of SC-Julia over the baseline Julia. Each |    |

| 0.1 | bar represents a test group in BaseBenchmarks, the number in the parenthesis        |    |

|     | after each test group name is the number of tests in that group. The last bar       |    |

|     | represents the whole benchmark suite.                                               | 78 |

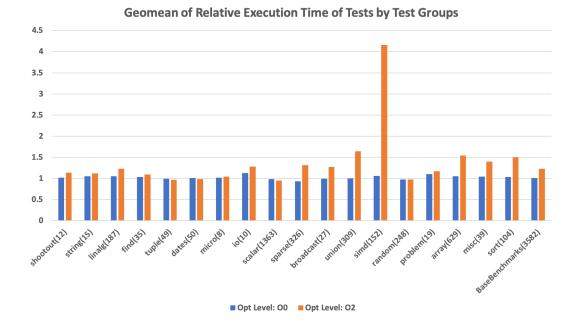

| 5.2 | Geometric mean of relative execution time of SC-Julia without hardware fences       |    |

| 0.2 | over the baseline Julia without hardware fences. Each bar represents a test group   |    |

|     | in BaseBenchmarks, the number in the parenthesis after each test group name is      |    |

|     | the number of tests in that group. The last bar represents the whole benchmark      |    |

|     | suite.                                                                              | 80 |

| 5.3 | Implementation of the library function fill! in Julia and with @drf annotation.     | 81 |

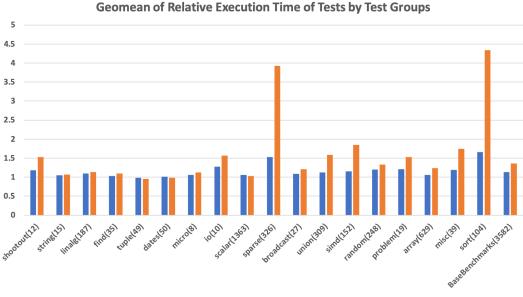

| 5.4 | Geometric mean of relative execution time of SC-Julia over the baseline Julia for   |    |

| 0.4 | BaseBenchmarks, with @drf behaviors for @simd and Base module. O0 and O2            |    |

|     | represents different optimization levels                                            | 82 |

| 5.5 | A microbenchmark that uses a loop to set every element in an array.                 | 83 |

| 0.0 | A incrobenchmark that uses a loop to set every element in an array.                 | 00 |

| 5.6 | Geometric mean of relative execution time of mSC-Julia over the baseline Julia. |    |

|-----|---------------------------------------------------------------------------------|----|

|     | O0 and O2 represents different optimization levels.                             | 84 |

#### LIST OF TABLES

| 4.1 | The implementation for volatile accesses on ARM in HotSpot (first two rows) |    |

|-----|-----------------------------------------------------------------------------|----|

|     | and an optimized implementation for memory accesses on ARM in S-VBD (last   |    |

|     | two rows)                                                                   | 61 |

| 5.1 | A list of the sin Julia and if they need SC rewriting.                      | 74 |

#### ACKNOWLEDGMENTS

I owe my deepest gratitude to my advisor, Todd Millstein, for his continuous support and guidance during my PhD. His passion and excitement during our discussions help shape the way I think about research, while his insights and encouragement help me break through obstacles in my research. He is caring, understanding, and always helpful. I have been, and will be keeping telling people how great an advisor he is.

I would like to offer my special thanks to Madan Musuvathi, who is also a great "advisor" to me. He provides so much inspiration and great ideas for each one of my PhD research project, and gives me heartfelt advice on my career plans. I can't be more grateful to the help and opportunities he gives me.

I would like to thank the rest of my committee members, Professor Jens Palsberg, Professor Harry Xu, Professor George Varghese, for serving on my committee. Their feedback has been a great help in completing my dissertation.

I would also like to thank my colleagues in the lab for the discussions, on research and on everything. It's just unfortunate that we still don't have an official name for the lab yet.

It's never possible to have a PhD without the support of family and friends. I owe a very important debt to my parent, who are the reason I stand where I am. None of it would have happened without them. Special thanks also to Jingwen, who is not only a best friend, but someone who is always supportive and believes in me, regardless of my grumpiness or moodiness when I am in "deadline mode". Thank you, too, to those who helped me settled in LA, and my friends who have been talking to me through ups and downs in this journey.

For my work in Chapter 3, I thank Professor Tyson Condie and his student Joseph Noor for permission and help to use their server as well as Ari Fogel and Saswat Padhi for permission to use their machines for performance evaluations of VBD-HotSpot. I would also like to express my gratitude to WorksOnArm and Ed Vielmetti for providing and setting up ARM server for performance evaluations of VBDA-HotSpot.

For my work in Chapter 4, I still need to thank WorksOnArm and Ed Vielmetti for

providing and setting up ARM server for the performance evaluations.

For my work in Chapter 5, I am grateful for the discussion and feedback given by Jameson Nash and Jeff Bezanson from Julia.

#### VITA

| 2015      | B.Eng in Software Engineering                |

|-----------|----------------------------------------------|

|           | Shanghai Jiao Tone University                |

|           | Shanghai, China                              |

| 2015-2020 | Graduate Student Researcher                  |

|           | Computer Science Department                  |

|           | University of California, Los Angeles        |

| 2017      | Research Intern                              |

|           | Microsoft Research                           |

|           | Redmond, Washington                          |

| 2017      | Teaching Assistant                           |

|           | CS 97: Principles and Practices of Computing |

|           | Computer Science Department                  |

|           | University of California, Los Angeles        |

| 2018      | Software Engineer Intern                     |

|           | Uber                                         |

|           | San Francisco, California                    |

| 2019      | Software Engineer Intern                     |

|           | Facebook                                     |

|           | Menlo Park, California                       |

#### PUBLICATIONS

Lun Liu, Todd Millstein, and Madan Musuvathi, Accelerating Sequential Consistency for Java with Speculative Compilation, PLDI 2019. Jun 2019.

Lun Liu, Leland Takamine, and Adam Welc, Profiling Android Applications with Nanoscope, VMIL 2018. Nov 2018.

Lun Liu, Todd Millstein, and Madan Musuvathi, A Volatile-by-Default JVM for Server Applications, OOPSLA 2017. Oct 2017.

## CHAPTER 1

## Introduction

Safe languages like Java and Julia provide programming abstractions, like type and memory safety, to improve programmer productivity. While some unsafe languages also provide such abstractions, safe languages *protect* these abstractions, ensuring that an unintentional programmer error cannot violate them. Doing so usually requires safe languages to pay the associated runtime costs, such as compiler-inserted bounds-checks, by default. Performance-minded programmers still have the flexibility to selectively use *unsafe* code fragments where the programmer, not the language, is responsible for ensuring safety.

Unfortunately, in the domain of concurrent programming, mainstream safe languages instead choose to adopt complex and error-prone semantics by default in the name of performance, breaking fundamental programming abstractions and failing to provide baseline guarantees for programmers. In this thesis, I focus on the problems with *memory consistency models*.

#### 1.1 Problems with Memory Models of Today's Languages

A memory consistency model (or simply memory model) of a programming language defines the possible values that a shared-memory read may return in that language. One of the most intuitive strong memory models is *sequential consistency* (SC) [Lam79]. It guarantees that all memory reads and writes agree on a global order, and the global order is consistent with the per-thread program order. With SC, programmers can always view the execution of their program as a sequential interleaving of the instructions from each thread.

Most mainstream languages today either have a memory model weaker than SC by default,

or don't even have a memory model. For example, Java [MPA05] only guarantee SC for certain "well- annotated" programs, and Julia does not have a well-defined memory model. The reasoning behind such decisions usually points to *performance*. Achieving SC requires the compiler to disable some common optimizations, and on current hardware platforms it further requires the compiler to restrict hardware optimizations by emitting expensive fence instructions on shared-memory accesses.

The downside of having a weak memory model, however, is that programmers must carefully annotate/write their programs in order to enforce the per-thread program orderings that are required for proper behaviors, otherwise programs are exposed to the relaxed/undefined semantics of the memory models, which is complex, unintuitive, and can violate critical program invariants. For example, under the current Java Memory Model (JMM) [MPA05] an object can be accessed before its constructor has completed, accesses to longs and doubles are not guaranteed to be atomic, and some programming idioms, such as double-checked locking [SH97, BBB17], are not guaranteed to behave correctly. This possibility is not just theoretical: errors caused by Java's weak memory model can be found across a range of widely used Java applications.

This *performance-by-default* approach to memory models is acceptable for and consistent with the design philosophy of languages like C and C++ [BA08]. However, I argue that such an approach conflicts with the design philosophy of "safe" languages like Java and Julia. Indeed, when it comes to type and memory safety, they instead employ a *safe-by-default* and *performance-by-choice* approach: in Java, for example, type and memory safety are provided by default, but there is a library of type-unsafe operations meant for use by expert programmers in performance-critical code [MPM15]; Julia uses bounds checking to ensure memory safety when access arrays, but **@inbounds** macro can be used to elide such checks in a tight loop.

Not only does the *performance-by-default* approach conflict with the design philosophy of "safe" languages, but also surprisingly, very little is actually known about the performance cost of a stronger memory model. Surely, there have been studies regarding such costs, but they are in unrealistic settings, like whole-program compilation [SS88, SFW05, KSY05]. Nobody

knows the cost of a practical implementation of SC for a modern language.

Considering the lack of measurement of the cost of a safer semantic, the decision to choose performance over programmability needs to be revisited. Essentially, choosing a memory model for a language involves an inherent performance-programmability trade-off, and such decision shouldn't be made without a better sense of what the cost of a stronger memory model like SC really is on *modern* hardwares for *modern* programming languages.

#### 1.2 Thesis Statement

My thesis states the following:

**Thesis statement** It is possible to measure the cost of strong and simple semantics for concurrent programming on *modern* hardwares for *modern* languages with *modern* language implementation techniques, and with optimizations, it is possible to have a simpler semantics for concurrent programming at a reasonable cost for certain languages.

I support the above statement by 1) implementing and evaluating the cost of SC for two different modern programming languages, and 2) developing language VM and compiler techniques to reduce such cost.

I propose a simpler and stronger memory model called volatile-by-default for Java. volatile-by-default provides SC for all programs by default, while at the same time, expert programmers retain the freedom to build performance-critical libraries that violate the SC semantics. I have implemented the volatile-by-default semantic on Oracle's HotSpot JVM and demonstrate through comprehensive empirical evaluation that the volatile-by-default semantics is arguably acceptable for a predominant use case for Java today — server-side applications running on Intel X86 architectures. I have also shown that the overhead of volatile-by-default semantics is much less than people have expected for applications running on a weaker architecture like ARM.

I also present a *speculative* approach to implement **volatile**-by-default which further reduces the average and maximum overhead of **volatile**-by-default on ARM. Additionally,

I have devised an orthogonal optimization that reduces the number of fences required to enforce the volatile-by-default semantics for ARM. Those two optimizations reduce the overhead of enforcing the volatile-by-default semantics by roughly 1/3 combined.

Besides Java, I have explored ways to provide SC for Julia. I have implemented an SC enforcing Julia compiler that guarantees SC and measured the cost of SC for Julia. I have further analyzed different factors that might affect the cost of SC and explored possibilities of using annotations to reduce the cost of SC.

#### 1.3 Thesis Organization

The thesis is organized as follows: Chapter 2 provides some background information related to the projects. Chapter 3 focuses on **volatile**-by-default semantics that provides SC for Java by default. It also covers how I implement it for HotSpot JVM and the measurement of the performance of **volatile**-by-default on both X86 and ARM. Chapter 4 describes the optimizations including a speculative compilation optimization I propose and develop to reduce the cost of **volatile**-by-default on ARM and its evaluations. Chapter 5 talks about my work to provide an SC enforcing Julia compiler and interesting finds from performance evaluations. Chapter 6 discusses about related work. Chapter 7 concludes.

## CHAPTER 2

## Background

In this chapter, I will give an overview on memory models and its relation with compiler/hardware optimizations, discuss in details about the memory models of Java and Julia, and provide some information on the HotSpot JVM and the Julia compiler.

#### 2.1 Memory Models and Compiler/Hardware Optimizations

A memory consistency model (or simply memory model) of a programming language defines the possible values that a shared-memory read may return in that language. Different kinds of memory models allow different kinds of reorderings of memory access. Stronger memory models limit more memory reorderings, and thus provide stronger guarantees of the program execution to the programs. Weaker (or relaxed) memory models allow more memory access reorderings to admit more optimizations, but in turn expose the programmers to a more complex and unintuitive semantics.

One of the most intuitive strong memory models is *sequential consistency* (SC) [Lam79]. It guarantees that all memory reads and writes agree on a global order, and the global order is consistent with the per-thread program order. With SC, programmers can always view the execution of their program as a sequential interleaving of the instructions from each thread.

Compiler optimizations that may reorder memory accesses such as *common subexpression* elimination (CSE), code motion, and dead store elimination may violate SC. Hardware optimizations like write buffers may also produce program executions that does not follow SC. In order to achieve SC, both the hardware and the compiler will need to disable such optimizations.

#### 2.1.1 The Java Memory Model

The Java memory model was defined more than a decade ago [MPA05] and attempts to strike a practical balance among programmer understandability, implementation flexibility, and program safety.

- programmer understandability The JMM designers considered sequential consistency to be "a simple interface" and "the model that is easiest to understand" [MPA05]. However, largely due to SC's incompatibility with standard compiler and hardware optimizations, the JMM adopts a weak memory model based on the DRF0 style [AH90], whereby SC is only guaranteed for *data-race-free* programs. A *memory race* occurs when two threads concurrently access the same memory location and at least one of those accesses is a write. A program is considered to be data-race-free if all instance variables that participate in a memory race are declared volatile.<sup>1</sup> The JMM guarantees SC semantics for volatile variables, which requires implementations to disable many compiler optimizations and to emit fence instructions that prevent the hardware from violating SC through out-of-order execution.

- **implementation flexibility** The SC memory model does not allow instructions to appear to be reordered. However, several important optimizations, for example out-of-order execution in hardware and common subexpression elimination in compilers, have the effect of instruction reordering. By guaranteeing SC only for data-race-free programs, the JMM can admit most traditional optimizations.

- program safety The JMM strives to ensure safety for all programs, even ones with data races. The JMM's notion of program safety is centered around the idea of preventing "outof-thin-air reads" [MPA05]. In the presence of data races, some compiler optimizations can in principle lead to a situation whereby multiple program transformations justify one another in a cycle. Such transformations can introduce values in the program that would never otherwise occur, which creates a potentially serious security concern. The

<sup>&</sup>lt;sup>1</sup>Local variables are thread-local and hence can never participate in a memory race.

JMM prevents out-of-thin-air reads by defining a complex *causality* requirement on the legal executions of incorrectly synchronized programs, which imposes some restrictions on the optimizations that a compiler may perform [MPA05].<sup>2</sup>

Because the JMM guarantees SC for data-race-free programs, programmers "need only worry about code transformations having an impact on their programs' results if those programs contain data races" [MPA05]. However, data races are both easy to introduce and difficult to detect; it is as simple as forgetting to grab a lock, grabbing the wrong lock, or omitting a necessary **volatile** annotation. Therefore in practice many programs are exposed to the effects of compiler and/or hardware optimizations, which can cause a variety of surprising behaviors and violate critical program invariants:

- **non-atomic primitives** Writes to **doubles** and **longs** are not atomic under the JMM, but rather are treated as two separate 32-bit writes. Therefore, in the presence of a data race readers can see values that are a combination of two different writes. Understanding this to be problematic, the Java Language Specification states that "implementations of the Java Virtual Machine are encouraged to avoid splitting 64-bit values where possible."<sup>3</sup>

- partially-constructed objects Consider the following example, where one thread tries to safely *publish* an object to another thread (assuming d and ready are respectively initialized to null and false):

| <u>Thread 1</u> | $\underline{\text{Thread } 2}$ |

|-----------------|--------------------------------|

| d = new Data(); | if (ready)                     |

| ready = true;   | d.use();                       |

Under the JMM, it is possible for the second thread to read the value true for ready but incur a null pointer exception on the call d.use(). More perniciously, d may be

<sup>&</sup>lt;sup>2</sup>The JMM's causality is known to disallow some optimizations that it was intended to allow, notably common subexpression elimination [CKS07, SA08]. Nonetheless, current Java virtual machines continue to perform this optimization. While there is no evidence that today's JVMs in fact admit out-of-thin-air reads, this issue must be resolved to prevent the possibility in the future.

<sup>&</sup>lt;sup>3</sup>https://docs.oracle.com/javase/specs/jls/se8/html/jls-17.html

non-null at that point but its constructor may not yet have completed, so the object is in an arbitrary state of partial construction when **use** is invoked.<sup>4</sup>

**broken synchronization idioms** The publication idiom above is one example of a custom synchronization idiom that is not guaranteed to work as expected in the JMM in the presence of data races. Other examples include double-checked locking [SH97] and Dekker's mutual exclusion algorithm.

#### 2.1.2 Missing-annotation bugs

The misbehaviors above are instances of what I call *missing-annotation bugs*. In these examples, the synchronization protocol intended by the programmer is correct and need not be changed. Rather, the error is simply that the programmer has forgotten to annotate certain variables as **volatile**. This omission allows compiler and hardware optimizations to violate intended program invariants. Adding **volatile** annotations forces the Java implementation to disable those optimizations and thereby restore the desired invariants. For example, a **double** or **long** field that is declared **volatile** will have atomic reads and writes. Similarly, declaring **ready** as **volatile** in my publication idiom above ensures that the second thread will only ever see a fully constructed object.

Missing-annotation bugs are easy to make and hence it is not surprising that they are common in Java applications. A quick search on the Apache Software Foundation's issue-tracking system found more than 100 issues where the fix required annotating a field as volatile. I report the first twenty here: SOLR-13465, YARN-10185, SHIRO-762, CASSANDRA-2490, HDFS-566, OAK-3638, YARN-8323, HDFS-4106, AMQ-6251, ARTEMIS-1945, SPARK-4282, SLIDER-101, SPARK-3567, LOG4J2-247, POOL-11, HDFS-1207, CASSANDRA-11984, AMQ-6495, APEXMALHAR-1887, OWB-529.<sup>5</sup> These errors occur in popular systems such as the Cassandra database, the HDFS distributed file system,

<sup>&</sup>lt;sup>4</sup>Java does guarantee that the final fields of d will be properly initialized when use is invoked.

<sup>&</sup>lt;sup>5</sup>Each bug contains the project name and the bug ID. Its details can be found at https://issues.apache.org/jira/browse/<ProjectName>-<BugID>. The twenty issues listed here are returned by a search in the issues tracker as of 05/12/2020.

and the Spark system for big-data  $\operatorname{processing}^6$  and can thereby impact the applications that employ these systems.

Missing-annotation bugs contrast with data races that violate program invariants due to the programmer's failure to implement the necessary synchronization protocol. Examples of the latter errors include atomicity violations that arise from failing to hold a lock or holding the wrong lock, and ordering violations that arise when threads fail to signal one another properly. Yet as Boehm et al. [Boe11] points out, missing-annotation bugs are far from "benign" but rather can cause surprising and harmful behaviors. For instance, exposing a partially constructed object, as shown above, can have serious security implications [TSM17].

#### 2.1.3 The Julia Memory Model

The Julia programming language is a new and emerging dynamic language aims to provide the flexibility of a dynamic language, while retaining good performance comparable to traditional static languages. It is open-sourced and is under active development.

Recently, Julia announced the addition of composable multi-threaded parallelism in the language [BNP]. It does not, however, provides a memory model, meaning that its memory model is implicit in the optimizations that the compiler and hardware perform. As a result, the actual behavior of its memory model is similar to that of the LLVM, which is inspired by C++0x memory model and is weaker than SC.

As a result, many surprising behaviors and violations of critical program invariants described above that can happen in Java also exist in Julia. For example, Figure 2.1 shows an implementation of the Dekker's mutual exclusion algorithm in Julia that is not guaranteed to work as expected.

Assume we have two threads both want to enter a critical section. Before they enter the critical section, they will call setAndRead() to signal their intent to enter the critical section by setting the corresponding element in lockArr, and check if the other thread has done so by checking the other element in lockArr. Under SC, the algorithm can work correctly, i.e.,

<sup>&</sup>lt;sup>6</sup>Spark is implemented in Scala, which compiles to Java bytecode and inherits Java's memory model.

```

1 import Base. Threads. @spawn

2

import Printf.@printf

3

lockArr = Int32[0; 0]

4

5

waitArr = Int32[-1; -1]

6

7

function setAndRead(threadNo)

\mathbf{if} threadNo == 1

8

lockArr[1] = 1

9

waitArr[1] = lockArr[2]

10

11

else

lockArr[2] = 1

12

waitArr [2] = lockArr [1]

13

14

\mathbf{end}

15

end

16

function test()

17

global lockArr = [0;0]

18

global waitArr = [-1; -1]

19

20

r1 = @spawn setAndRead(1)

r2 = @spawn setAndRead(2)

21

wait(r1)

22

23

wait(r2)

24

if waitArr [1] = 0 && waitArr [2] = 0

25

\# Both threads enter critical section.

26

println("SC Violation!")

27

28

return false

29

\mathbf{end}

30 end

```

Figure 2.1: An implementation of Dekker's mutual exclusion algorithm in Julia which is not guaranteed to work correctly

we will never see both elements in waitArr to be 0. However, it is possible with the current Julia runtime that test() returns 0, which means it would allow both threads to enter the critical section.

#### 2.2 The HotSpot Java Virtual Machine

The Oracle's HotSpot JVM is an implementation of the Java Virtual Machine Specification [Jav17]. It is widely used and part of the OpenJDK — the official reference implementation of Java SE.<sup>7</sup>

To execute Java bytecode instructions, HotSpot employs just-in-time (JIT) compilation. In this style, bytecodes are first executed in interpreter mode, with minimal optimizations. During execution, HotSpot identifies parts of the code that are frequently executed ("hot spots") and compiles them to optimized native code for better performance.

The HotSpot JVM has one interpreter, but its behavior depends on the underlying hardware platform being used. HotSpot includes two just-in-time compilers. The *client* compiler, also called C1, is fast and performs relatively few optimizations. The *server* compiler, also called C2 or *opto*, optimizes code more aggressively and is specially tuned for the performance of typical server applications. I have been focusing on modifying the C2 compiler in my work.

#### 2.2.1 The HotSpot JVM Interpreter

The HotSpot JVM uses a *template-based interpreter* for performance reasons. In this style a **TemplateTable** maps each bytecode instruction to a *template*, which is a set of assembly instructions (and hence platform-specific). The **TemplateTable** is used at JVM startup time to create an interpreter in memory, whereby each bytecode is simply an index into the **TemplateTable**.

$<sup>^7\</sup>mathrm{My}$  work is based on OpenJDK 8u. All specific descriptions of any technical details in this thesis is based on this version.

Figure 2.2: Interpretation example of bytecode putfield

Figure 2.2 illustrates how the template-based interpreter works. The bytecode pointer (BCP) is currently pointing at the bytecode putfield (181). The interpreter uses this bytecode as an index in the TemplateTable (right side of the figure) to find the address of the corresponding template. The interpreter then jumps to this address to begin executing the template (left side of the figure). After writing to the field, the last four lines of the template show how the interpreter reads the next BCP index, increments the BCP, and jumps to the next code section. In this example, we add 3 to BCP (%r13) to point to the next bytecode, because the length of the putfield instruction is 3 bytes: a 1-byte opcode and a 2-byte index representing the field.

#### 2.2.2 The HotSpot JVM Compiler

When the JVM identifies a "hot spot" in the code, it compiles that portion to native code. As mentioned earlier, I have modified HotSpot's high-performance server compiler, which consists of several phases. First a hot spot's bytecode instructions are translated into a high-level graph-based intermediate representation (IR) called Ideal. The compiler performs several local optimizations on Ideal-graph nodes as it creates them. It then performs more aggressive optimizations on the graph in a subsequent optimization phase. Next the optimized Ideal graph is translated to a lower-level platform-specific IR, and finally machine code is generated in the code generation phase. Optimizations are performed during each of these last two phases as well.

#### 2.3 The Julia Compiler

Like Java, Julia also has its runtime with JIT compilation. After the code has been loaded, the Julia runtime will use simple heuristics to decide if the code needs to be interpreted by its interpreter or be compiled by its compiler.

The Julia compiler is built using the LLVM toolchain [LA04]. LLVM is a compiler infrastructure that can provide compiler writers easy access to a collection of industrial strength compiler techniques. The Julia compiler can function as an LLVM front-end: if the Julia code needs to be compiled, the compiler will first generate a Julia level IR and perform some simple optimizations. After that, the Julia compiler will transform the Julia level IR into an LLVM IR.

The LLVM execution engine will execute a sequence of different LLVM *passes* to analyze, optimize, and generate the native instructions to execute. The subset of passes and the ordering of how they are executed are specified by the Julia compiler. Julia also implements their own LLVM passes and include them in the pass pipeline.

## CHAPTER 3

## volatile-by-default JVMs for Server Applications

#### 3.1 Introduction

A memory consistency model (or simply memory model) defines the possible values that a shared-memory read may return and thus plays a central role in the semantics of a multithreaded programming language. Choosing a memory model for a language involves an inherent performance-programmability trade-off. *sequential consistency* (SC) [Lam79] provides an intuitive programming model by ensuring that a program's instructions (appear to) execute in a global total order consistent with the per-thread program order. But achieving SC requires the compiler to disable some common optimizations, and on current hardware platforms it further requires the compiler to restrict hardware optimizations by emitting expensive fence instructions on shared-memory accesses.

To avoid this cost, the Java language [MPA05] has adopted a *relaxed* (or *weak*) memory model that is designed to admit most traditional compiler optimizations and obviate the need for hardware fences on most shared-memory accesses. The Java Memory Model (JMM) is based on the DRF0 style [AH90], whereby SC is only guaranteed for *data-race-free* programs. A program is considered to be data-race-free if all instance variables that participate in a memory race are declared **volatile**.<sup>1</sup> The JMM guarantees SC semantics for **volatile** variables, which requires implementations to disable many compiler optimizations and to emit fence instructions that prevent the hardware from violating SC through out-of-order execution.

The downside, however, is that programmers must carefully declare certain variables as

<sup>&</sup>lt;sup>1</sup>Local variables are thread-local and hence can never participate in a memory race.

volatile in order to enforce the per-thread program orderings that are required for proper behavior. If a programmer does not annotate the necessary variables as volatile, programs are exposed to the relaxed semantics of the JMM, which is complex, unintuitive, and can violate critical program invariants. For example, under the JMM an object can be accessed before its constructor has completed, accesses to longs and doubles are not guaranteed to be atomic, and some programming idioms, such as double-checked locking [SH97, BBB17], are not guaranteed to behave correctly. This possibility is not just theoretical: errors due to the failure to annotate certain variables as volatile, which I term *missing-annotation bugs*, can be found across a range of widely used Java applications.

This *performance-by-default* approach to memory models is acceptable for and consistent with the design philosophy of languages like C and C++ [BA08]. However, I argue that such an approach conflicts with the design philosophy of "safe" languages like Java. Indeed, when it comes to type and memory safety, Java instead employs a *safe-by-default* and *performance-by-choice* approach: type and memory safety are provided by default, but there is a library of type-unsafe operations meant for use by expert programmers in performance-critical code [MPM15].

In the same vein, I propose a *safe-by-default* and *performance-by-choice* approach to enforcing per-thread program order in Java. This approach involves a conceptually simple change to the memory model: every variable has **volatile** semantics by default, but the language allows a programmer to tag certain classes, methods, or variables as **relaxed** and provides the current JMM semantics for these portions of code. This *volatile-by-default* semantics provides a natural form of sequential consistency for Java by default, at the bytecode level: bytecode instructions (appear to) execute atomically and in program order. This also implies that all Java primitive values, including (64-bit) **doubles** and **longs**, are atomic irrespective of the bit-width of the underlying architecture. At the same time, expert programmers retain the freedom to build performance-critical libraries that violate this semantics, and they are responsible for protecting clients from any weak behaviors that can result. volatile-by-default JVMs for X86 and ARM At the outset, it is unclear if the volatile-by-default semantics is practical for Java, given the cost of memory fences on today's hardware platforms. One should deem the volatile-by-default approach as unacceptable if the only way to make programs reasonably efficient is to declare large portions as relaxed. In fact, current conventional wisdom about the cost of these fences and the associated cost of providing SC to the programmer strongly points against the volatile-by-default approach. For instance, Kaiser et al. (2017) say that SC is "woefully unrealistic" due to "the significant performance costs ... on modern multi-core architectures" [KDD17] and Demange et al. (2013) say that "SC would likely cripple performance of Java programs on all modern microprocessors." [DLZ13] I first demonstrate, through comprehensive empirical evaluation, that the volatile-by-default semantics is in fact acceptable for a predominant use case for Java today — server-side Java applications running on Intel X86 architectures. I then show that on another widely used hardware platform today, ARM, where both reads and writes can be reordered by hardware [FGP16], volatile-by-default semantics also has a much lower overhead than people have expected.

The straightforward way to implement the volatile-by-default semantics is through a source-to-source translation that adds the appropriate volatile annotations. The advantage of this approach is that it is *independent* of the JVM, allowing us to evaluate the cost of volatile-by-default semantics on various JVMs and hardware architectures. Unfortunately, neither Java nor the Java bytecode language provides a mechanism to declare array elements as volatile. Thus, such an approach fails to provide the desired semantics. I considered performing a larger-scale source-to-source rewrite on array accesses, but it would be difficult to separate the cost of this rewrite from the measured overheads. Finally, once I settled on changing an existing JVM implementation, I considered doing so in a research virtual machine [AAB05]. But it was not clear how the empirical observations from such a JVM would translate to a production JVM implementation.

Therefore I implemented the volatile-by-default semantics by directly modifying Oracle's HotSpot JVM which is part of the OpenJDK version 8u [Ope17]. I call my modified version for X86 and ARM VBD-HotSpot and VBDA-HotSpot respectively. To the best of my knowledge,

they are the first implementations of SC for a production Java virtual machine (JVM) that includes the state-of-the-art implementation technology, such as dynamic class loading and just-in-time (JIT) compilation. This in turn enables me to provide the first credible experimental comparison between SC and the JMM. This is also the first comprehensive study of the cost of providing SC for any language on ARM.

I implemented VBD-HotSpot and VBDA-HotSpot by reusing mechanisms already in place for handling volatile variables in the interpreter and compiler. This provides me two advantages. First and foremost, the correctness of VBD-HotSpot mostly follows from the correctness of the HotSpot JVM's implementation of volatile semantics. Second, I automatically obtain the benefits of optimizations that HotSpot already employs to reduce the overhead of volatile accesses. VBD-HotSpot is open-source and available for download at https://github.com/SC-HotSpot/VBD-HotSpot. VBDA-HotSpot is also open-sourced and can be found at https://github.com/Lun-Liu/schotspot-aarch64.

**Results** For the DaCapo benchmarks [BGH06] on a modern X86 server, with no relaxed annotations, the overhead of VBD-HotSpot versus the unmodified HotSpot JVM is 28% on average, with a maximum of 81%. Given that VBD-HotSpot potentially inserts a fence on *every* heap store, I believe that this overhead is less than commonly assumed. My experiments show that the benchmarks that incur the highest overheads are either single-threaded or mostly-single-threaded. Excluding these benchmarks reduces the average overhead to 21%.

Experiments on my baseline implementation for ARM, VBDA-HotSpot, show that the volatile-by-default semantics incurs a considerable performance penalty on ARM, as expected. However, I observe that the performance overhead crucially depends on the specific fences used to implement the volatile semantics. With the default fences that HotSpot employs to implement volatile loads and stores on ARM, VBDA-HotSpot incurs average and maximum overheads of 195% and 429% (!) on the DaCapo benchmarks for a modern 8-core ARM server. But employing an alternative choice of ARM fences reduces the average and maximum overheads on that machine respectively to 73% and 129%. I also find similar results on a 96-core ARM server, with VBDA-HotSpot incurring an average and maximum

overhead of 57% and 157% with the alternative fences.

Another common assumption is that the cost of SC increases with the number of processor cores and sockets. For instance, a fence on x86 stalls the processor until it has received read invalidations from all processors that have a shared copy of addresses in its pending store buffer. One expects these stalls to be longer when there are more threads in the program, and when it is running across a larger number cores and sockets. However, my evaluation shows that this assumption is not true, at least in my experimental setting. The overhead of SC *improves* with increased concurrency and with the number of sockets; apparently the increased cost of fences is compensated by the increased cost of regular memory accesses.

# 3.2 volatile-by-default Semantics for Java

Under the JMM, the onus is on programmers to employ the volatile annotation everywhere that is necessary to protect the program from compiler and hardware optimizations that can reorder instructions. By doing so, the JMM can allow most compiler and hardware optimizations. I argue that this *performance-by-default* approach is not consistent with Java's design philosophy as a "safe" programming language. Instead I advocate a *safe-by-default* and *performance-by-choice* approach to Java's concurrency semantics.

To that end, I propose the volatile-by-default semantics for Java, which makes one conceptually simple change: all instance variables are treated as if they were declared volatile. In this way, missing-annotation bugs cannot occur and all Java programs are guaranteed SC semantics by default. With this change, the volatile annotation becomes semantically a no-op. Instead, I introduce a relaxed annotation that allows a programmer to tag variables, methods, or classes that should employ the current JMM semantics. Expert programmers can use this annotation in performance-critical code to explicitly trade off program guarantees for increased performance.

Precisely defining the SC semantics requires one to specify the granularity of thread interleaving, which has been identified as a weakness of the SC memory model [AB10]. The volatile-by-default semantics does this in a natural way by providing SC at the bytecode level: bytecode instructions (appear to) execute atomically and in program order. This also implies that all Java primitive values, including (64-bit) doubles and longs, are atomic irrespective of the bit-width of the underlying architecture. The volatile-by-default semantics provides a clean way for programmers to understand the possible behaviors of their concurrent programs, provided they understand how Java statements (such as increments) are translated to bytecode.

Of course, "safety" is in the eye of the beholder, and there are many possible definitions. I argue that the volatile-by-default semantics is a natural *baseline* guarantee that a "safe" language should provide for all programs. The volatile-by-default memory model clearly satisfies the JMM's desired programmability and safety goals. In terms of programmability, volatile-by-default is strictly stronger than the JMM, so all program guarantees provided by the JMM are also provided by volatile-by-default. In terms of safety, the volatile-by-default semantics prevents all cyclic dependencies and hence rules out the particular class of such cycles that can cause out-of-thin-air reads. Moreover, volatile-by-default eliminates all missing-annotation bugs.

Further, the volatile-by-default semantics provides a more general notion of safety by protecting several fundamental program abstractions [MMM15]. First, all primitives are accessed atomically. Second, sequential reasoning is valid for all programs. This ensures, for example, that an object cannot be accessed until it is fully constructed (unless the program explicitly leaks this during construction), and more generally that program invariants that rely on program order are guaranteed regardless of whether the program has data races.

Finally, I note that though the volatile keyword is semantically a no-op in the volatileby-default semantics, it is still useful as a means for programmers to document their intention to use a particular variable for synchronization. Indeed, volatile annotations can make the code easier to understand and can be used by tools to identify potential concurrency errors. However, under the volatile-by-default semantics, and in sharp contrast to the JMM, an accidental omission or misapplication of volatile annotations will *never* change program behavior.

## 3.3 volatile-by-default JVMs for X86 and ARM

The straightforward way to implement the volatile-by-default semantics is through a source-to-source translation that adds the appropriate volatile annotations. The advantage of this approach is that it is *independent* of the JVM, allowing us to evaluate the cost of volatile-by-default semantics on various JVMs and hardware architectures. Unfortunately, neither Java nor the Java bytecode language provides a mechanism to declare array elements as volatile. Thus, such an approach fails to provide the desired semantics. I considered performing a larger-scale source-to-source rewrite on array accesses, but it would be difficult to separate the cost of this rewrite from the measured overheads. Finally, once I settled on changing an existing JVM implementation, I considered doing so in a research virtual machine [AAB05]. But it was not clear how the empirical observations from such a JVM would translate to a production JVM implementation.

Therefore, I opted to instead implement the volatile-by-default semantics through a direct modification to the Java virtual machine, which executes Java bytecode instructions. I chose to modify Oracle's HotSpot JVM, which is widely used and part of the OpenJDK — the official reference implementation of Java SE. In particular I modified the version of HotSpot that is part of the OpenJDK 8u for both X86 and ARM. The modified version for X86, called VBD-HotSpot, adds a flag -XX:+VBD that allows users to obtain volatile-by-default semantics. The ARM version, VBDA-HotSpot, has a similar flag -XX:+SC.

As mentioned in Section 2.2, to execute Java bytecode instructions, HotSpot employs just-in-time (JIT) compilation. In this style, bytecodes are first executed in interpreter mode, with minimal optimizations. During execution, HotSpot identifies parts of the code that are frequently executed ("hot spots") and compiles them to optimized native code for better performance.

The HotSpot JVM has one interpreter and two just-in-time compilers. I have implemented the volatile-by-default semantics for Java server applications, which are a dominant use case in practice. Accordingly I have modified the HotSpot interpreter as well as the HotSpot server compiler. I have implemented volatile-by-default semantics for both X86 and ARM, the two most common hardware architectures nowadays.

I implemented VBD-HotSpot and VBDA-HotSpot by reusing mechanisms already in place for handling volatile variables in the interpreter and compiler.

### 3.3.1 volatile-by-default Interpreter

Since the interpreter is platform-specific, different fence instructions are used for VBD-HotSpot and VBDA-HotSpot. I will first talk about how I make the interpreter volatile-by-default on X86, and then present my modifications to the interpreter on ARM.

Figure 2.2 shows how the HotSpot JVM handles accesses to volatile variables on X86. The SC semantics for volatile accesses is achieved by inserting the appropriate platform-specific fences before/after such accesses. In the case of X86, which has the relatively strong *total store order* (TSO) semantics [OSS09], a volatile read requires no fences and a volatile write requires only a subsequent *StoreLoad* barrier, which ensures that the write commits before any later reads [JSR18]. In the figure, %edx is already loaded with the field attribute for volatile. Instruction (1) tests if the field is declared volatile. If so, the lock instruction (2) will be executed, which acts as a StoreLoad barrier on X86; otherwise the lock instruction is skipped.

To implement my volatile-by-default semantics for X86, I therefore modified the template for putfield to unconditionally execute the lock instruction. This is done by removing instruction (1) and the following jump instruction je. I also added the lock instruction to the templates for the various bytecode instructions that perform array writes (e.g., aastore for storing objects into arrays, bastore for storing booleans into arrays, etc.).

I manually inspected the template instructions for the interpreter's implementation of all bytecodes that read from or write to memory: getfield, putfield, fast\_xgetfield, fast\_xputfield, and fast\_xaccess. The latter three bytecodes are used internally by the HotSpot JVM as special, more efficient versions of getfield and putfield. The template code for each bytecode checks the volatile attribute of the given field and adds the necessary fences if the attribute is set. In VBD-HotSpot, I elide the check of the volatile attributes and always adds the necessary fences.

Inserting memory-barrier instructions ensures that the hardware respects SC, but it does not prevent the interpreter itself from performing optimizations that can violate SC. The interpreter performs optimizations through a form of bytecode rewriting, including rewriting bytecodes to new ones that are not part of the standard Java bytecode language. For example, on encountering a **putfield** bytecode and resolving the field to which it refers, the interpreter rewrites the bytecode into a "fast" version (**fast\_aputfield** if the field is an Object, **fast\_bputfield** if the field is a boolean, etc.) The next time the interpreter executes the enclosing method, it will execute the faster version of the bytecode, avoiding the need to resolve the field again.

I manually inspected all of the interpreter's bytecode-rewriting optimizations and found that they never reorder the memory accesses of the original bytecode program. In other words, the interpreter does not perform optimizations that violate SC. However, to ensure SC semantics I had to modify the templates for all of the fast\_\*putfield bytecodes in order to unconditionally execute the lock instruction, as shown earlier for putfield.

Finally, the interpreter treats a small number of common and/or special methods, for example math routines from java.lang.Math, as *intrinsic*: the interpreter has custom assembly code for them. However, I examined the X86 implementations of these intrinsics and found that none of them contain writes to shared memory, so they already preserve SC.

Similar to X86, for ARM, I manually inspected the template instructions in the ARM interpreter for the bytecodes that read from or write to memory, such as **getfield** and **putfield**. The template code for each bytecode checks the **volatile** attribute of the given field and adds the necessary fences if the attribute is set. In VBDA-HotSpot, I have modified this template code to unconditionally add the necessary fences, thereby treating all memory reads and writes as **volatile**. Interestingly, the template code for **getfield** already unconditionally adds the necessary fences without checking the **volatile** attribute of the field, so it did not require any modification. I also treat accesses to array elements as **volatile** by inserting the appropriate fences in the template code for the corresponding bytecodes,

such as **aaload** and **aastore**. Additionally, I examined and modified bytecode-rewriting optimizations and intrinsics in the interpreter in VBDA-HotSpot the same way I treated VBD-HotSpot.

To implement the semantics of volatile on ARM, the interpreter must insert a load-load and load-store barrier after a volatile load, providing *acquire* semantics for the load; a storestore barrier and a load-store barrier before a volatile write, providing *release* semantics for the write; and a store-load barrier after a volatile write. The interpreter uses ARM's dmb (data memory barrier) instruction for this purpose. In particular, it needs a dmb ishld instruction to enforce acquire semantics after a load, dmb ish to enforce release semantics before a store, and dmb ish to enforce store-load dependencies after a store.

However, the baseline HotSpot JVM has a bug of inserting an overly weak barrier before **volatile** writes in the interpreter. Specifically it inserts a **dmb ishst** instruction, which performs a store-store barrier but not also a load-store barrier; obtaining both barriers instead requires a **dmb ish** instruction.<sup>2</sup> I have fixed this bug and use the fixed version of the baseline HotSpot JVM in all of our experiments. Interestingly, the use of **dmb ishst** before writes suffices for VBDA-HotSpot, because the preceding memory operation must end in a **dmb ish** (for stores) or a **dmb ishld** (for loads), both of which act as load-store barriers.

#### 3.3.2 volatile-by-default Compiler

When the JVM identifies a "hot spot" in the code, it compiles that portion to native code. As mentioned earlier, I have modified HotSpot's high-performance server compiler, which consists of several phases. First a hot spot's bytecode instructions are translated into a high-level graph-based intermediate representation (IR) called Ideal. The compiler performs several local optimizations on Ideal-graph nodes as it creates them. It then performs more aggressive optimizations on the graph in a subsequent optimization phase. Next the optimized Ideal graph is translated to a lower-level platform-specific IR, and finally machine code is generated

<sup>&</sup>lt;sup>2</sup>This bug has been confirmed and fixed by the developers: http://hg.openjdk.java.net/jdk/jdk/rev/e2fc434b410a

in the code generation phase. Optimizations are performed during each of these last two phases as well.

Figure 3.1: Ideal graph sections for volatile loads (left) and stores (right).

At the Ideal graph level, the semantics of volatile is implemented by three kinds of memory-barrier nodes, each of which represents a specific combination of the four basic memory barriers: *LoadLoad*, *LoadStore*, *StoreLoad*, and *StoreStore*. Figure 3.1 shows snippets of the Ideal graph for volatile loads and stores. Each volatile load is followed by a MemBarAcquire node, which enforces "acquire" semantics: subsequent instructions (both load and store) cannot be reordered before the barrier node. Each volatile store is preceded by a MemBarRelease node, which enforces "release" semantics: prior instructions cannot be reordered after the barrier node. Each volatile store is also followed by a MemBarVolatile node, which prevents subsequent volatile memory accesses from being reordered before the barrier node.<sup>3</sup>

The memory-barrier nodes in the Ideal graph are translated to their counterparts in the

<sup>&</sup>lt;sup>3</sup>On the POWER processor [MMS12], which is not multi-copy atomic, a MemBarVolatile also precedes each volatile load, but this is not necessary for X86.

lower-level IR. When generating machine code, they are finally translated into the appropriate assembly instructions. On X86 both the MemBarAcquire and MemBarRelease nodes become no-ops, since TSO already enforces those instruction orders. On ARM, MemBarAcquire becomes a dmb ish ld, and both MemBarRelease and MemBarVolatile become dmb ish. However, it is critical to keep these memory-barrier nodes in the code until the point of code generation, in order to prevent the compiler from performing optimizations that violate their semantics.

Given this structure, I chose to implement the **volatile**-by-default semantics by modifying the phase that creates the Ideal graph. Specifically, I modified that phase to emit the appropriate memory-barrier nodes around *all* loads and stores, rather than only **volatile** ones. As in the interpreter, this was done both for accesses to instance variables and to array elements.

An additional complication is that the server compiler treats many methods as intrinsic, providing a custom Ideal graph for each one. I carefully examined the implementation and documentation of these intrinsics to ensure volatile-by-default semantics. First, some intrinsics, for example math routines from java.lang.Math, only access local variables and hence need not be modified. Second, I added appropriate memory-barrier nodes in the implementations of many intrinsics that perform memory loads and/or stores. For example, getObject from sun.misc.Unsafe loads an instance variable or array element directly by offset. I modified its Ideal-graph implementation to include a subsequent MemBarAcquire node, as is already done for the getObjectVolatile intrinsic from the same class. Finally, for some intrinsics, specifically certain string operations, I simply set the flag -XX:-OptimizeStringConcat, which causes the methods to be compiled normally instead of using the intrinsic implementations.

Modifying the compiler at this early stage ensures that I need not worry about the potential for any downstream compiler optimizations to violate SC, since those optimizations already respect the semantics of memory-barrier nodes. This holds true even for the local optimizations that are performed during Ideal-graph construction. For example, the local optimizations on a **Store** node, such as redundant store elimination, already take into account the presence of any preceding memory-barrier nodes, which is necessary to avoid violating

the semantics of **volatile** stores. The ideal graph is also platform independent, I then rely on the X86 and aarch64 backend to compile the memory-barrier nodes appropriately.

#### 3.3.3 Optimizations

Another important benefit of implementing the volatile-by-default semantics in the Ideal graph is that it allows us to take advantage of the optimizations that the server compiler already performs on memory-barrier nodes at different phases in the compilation process. For example, the compiler performs an optimization to remove redundant memory-barrier instructions. In this way, the optimizations that the server compiler already performs to optimize volatile accesses are automatically used to lower the cost of SC semantics.

I also added an optimization to the compiler that removes memory barriers for accesses to objects that do not escape the current thread. The HotSpot JVM already performs an escape analysis, which I simply reuse. In fact, earlier versions of the HotSpot JVM performed this optimization for a subset of non-escaping objects called *scalar-replaceable objects*, but it seems to have been accidentally removed in version 8u: the code for the optimization is still there but it was modified such that it never actually removes any memory barriers. I updated this code to properly remove MemBarAcquire and MemBarVolatile nodes for all non-escaping objects.<sup>4</sup>

Finally, the HotSpot JVM inserts a MemBarRelease node at the end of a constructor if the object being constructed has at least one final field, in order to ensure that clients only see the initialized values of such fields after construction. In VBD-HotSpot, this MemBarRelease node is unnecessary, because each individual field write in the constructor is already surrounded by appropriate memory-barrier nodes. Therefore, VBD-HotSpot does not insert memory barriers after constructors.

$<sup>^4\</sup>mathrm{Removing}\ \mathtt{MemBarRelease}\ \mathrm{nodes}\ \mathrm{is\ trickier}\ \mathrm{to\ implement},\ \mathrm{so\ I}\ \mathrm{have\ not\ done\ it\ though\ it\ would\ be\ safe}\ \mathrm{to\ do.}$

#### 3.3.4 Correctness

My main implementation technique, in both the VBD-HotSpot and VBDA-HotSpot interpreter and compiler, is to simply reuse the existing mechanisms for handling accesses to **volatile** variables. Therefore, the correctness of VBD-HotSpot and VBDA-HotSpot largely hinges on the correctness of those existing mechanisms, which have been in wide use as well as refined and debugged over more than a decade. I also validated VBD-HotSpot's correctness in several ways. First, I added a *VBDVerify* phase in the server compiler after the creation of the Ideal graph, which traverses the Ideal graph to check that all loads and stores are surrounded by appropriate memory-barrier nodes. Second, I created a suite of several litmus tests that sometimes exhibit non-SC behavior under the unmodified HotSpot JVM, such as a version of Dekker's mutual exclusion algorithm. I have run these litmus tests many times on the VBD-HotSpot and VBDA-HotSpot compiler and they have never exhibited a non-SC behavior, which helps lend confidence in my implementation.

#### 3.3.5 volatile-by-default for Java and Scala

Finally, I note that VBD-HotSpot ensures volatile-by-default semantics for Java bytecode, but that does not immediately provide a guarantee in terms of the original Java source program. However, I have manually examined the widely used javac compiler that is part of the OpenJDK, which compiles Java source to bytecode, and ensured that it performs no optimizations that have the effect of reordering memory accesses. Hence compiling a Java program with javac and executing the resulting bytecode with VBD-HotSpot provides volatile-by-default semantics for the original program. I also examined the scalac compiler that compiles Scala source to Java bytecode<sup>5</sup> and found no optimizations that reorder memory accesses, so the same guarantees hold for Scala programs running on VBD-HotSpot.

<sup>&</sup>lt;sup>5</sup>http://www.scala-lang.org/download

## 3.4 Performance Evaluation of volatile-by-default

### 3.4.1 Performance Evaluation of VBD-HotSpot

In this section I describe my experiments that provide insight into the performance cost of SC for JVM-based server applications on X86, which are a dominant use case today. I compared the performance of VBD-HotSpot to that of the original HotSpot JVM on several benchmark suites.

#### 3.4.1.1 DaCapo Benchmarks

The DaCapo benchmarks suite is a set of open-source Java applications that is widely used to evaluate Java performance and represents a range of application domains [BGH06]. I used the DaCapo 9.12 distribution. I excluded five of the benchmarks: *batik* and *eclipse* are not compatible with Java 8; *tradebeans* and *tradesoap* fail periodically, apparently due to an incompatibility with the -XX:-TieredCompilation flag<sup>6</sup>, which VBD-HotSpot employs (see below); and *lusearch* has a known concurrency error that causes it to crash periodically.<sup>7</sup>

I ran the DaCapo benchmarks on my server machine and used the default workload and thread number for each benchmark. I used an existing methodology for Java performance evaluation [GBE07]. For each JVM invocation, I ran each benchmark for 20 iterations, with the first 15 being the warm-up iterations, and I calculated the average running time of the last five iterations. I ran a total of 10 JVM invocations for each test and calculated the average of the 10 averages.

<sup>&</sup>lt;sup>6</sup>https://bugs.openjdk.java.net/browse/JDK-8067708

<sup>&</sup>lt;sup>7</sup>Interestingly, I observed the crash when executed on the original JVM but never on VBD-HotSpot, though I cannot be sure that the bug will never manifest under SC.

**Execution Time of DaCapo with 95% confidence interval**

Figure 3.2: Execution time in milliseconds of VBD-HotSpot on the DaCapo benchmarks. "original JVM" means running the baseline HotSpot JVM without additional flags; "-XX:-TieredCompilation" means running the baseline HotSpot JVM with -XX:-TieredCompilation; "VBD-HotSpot" shows results of running VBD-HotSpot.

Figure 3.3: Relative execution time of VBD-HotSpot on the DaCapo benchmarks

Figures 3.2 and 3.3 respectively show the absolute and relative execution times of VBD-HotSpot versus the baseline HotSpot JVM. By default the HotSpot JVM uses *tiered compilation*, which employs both the client and server compilers. Since I only modified the server compiler, VBD-HotSpot employs the -XX:-TieredCompilation flag to turn off tiered compilation and employ only the server compiler. Therefore I also present the results for running the original HotSpot JVM with this flag.