# UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

# Title

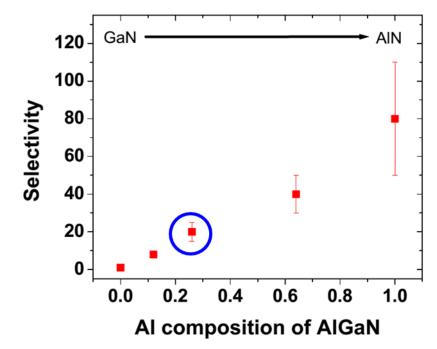

N-Polar Deep Recess MISHEMTs for mm-Wave Applications

## Permalink

https://escholarship.org/uc/item/8dc5s7fz

Author Wienecke, Steven Michael

# Publication Date 2018

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA

Santa Barbara

N-Polar Deep Recess MISHEMTs for mm-Wave Applications

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Steven M. Wienecke Jr.

Committee in charge: Professor Umesh K. Mishra, Chair Professor Mark J. W. Rodwell Professor Steven P. DenBaars Professor Bob York

December 2018

The dissertation of Steven Michael Wienecke Jr. is approved.

Mark J. W. Rodwell

Steven P. DenBaars

Bob York

Umesh K. Mishra, Committee Chair

December 2018

N-Polar Deep Recess MISHEMTs for mm-Wave Applications

Copyright © 2018

by

Steven M. Wienecke Jr.

# Dedicated to my Mother, Father, Alex, and Eric

Thank you for all your support through all the years, if you'd even given me just 1/100<sup>th</sup> of the support you have in my life I'd still be forever grateful.

#### ACKNOWLEDGEMENTS

I would like to express my most sincere and deepest gratitude to my advisor, Professor Umesh Mishra. Thank you for giving me a chance in your wonderful group, and for having confidence in me throughout the years. You have been both a wonderful mentor and friend to me throughout all these years, and I am truly grateful. I enjoyed our conversations – ranging from engineering to history to philosophy to history – and always managed to come away with something useful. I am very proud to have been a member of your research group and to be an employee at Transphorm.

I am also very grateful to Professors Steven DenBaars, Mark Rodwell, and Bob York for spending their precious time to be a part of my committee. I appreciate the insights and comments they contributed during my Qualification Examination and PhD Defense. Additionally, I am very thankful to Dr. Paul Maki and Dr. Dan Green for funding this work. Their belief in N-Polar helped keep the project alive and allowed for the excellent results achieved in this work and hopefully that of future students as well.

I have been extremely lucky to work with so many talented researchers during my stay here at UCSB. I first would like to thank Haoran Li for providing excellent epi that allowed for world record results achieved in this thesis. I appreciate here extreme patience and diligence, and her crazy vampire schedule was a perfect compliment to my schedule. I would also like to thank Stacia Keller for developing many of the MOCVD N-Polar recipes on the Thomas Swan and her near bottomless pit of MOCVD GaN and overall material

V

knowledge. I learned a lot from my interactions with her, and appreciate the patient and thoughtful answers she gave to my questions.

I would also like to thank the MBE growers Elaheh Ahmadi and Karine Hestroffer for all the n+ GaN regrowths they provided. I know these growths probably weren't the most interesting to you, but they were very important to this work and I truly appreciate your contributions.

Of course I would like to thank my fellow N-Polar HEMT teammates, Brian Romanczyk, Matthew Guidry, and Xun Zheng. We spent countless nights either in the cleanroom, measurement lab, or in the student office preparing for reviews. Though some of those sleepless nights were a bit rough, spending it with you guys helped make it manageable. Much of the NPDR MISHEMT work on sapphire substrates were processed with Brian Romanczyk. Matthew Guidry basically built the W-Band Load Pull system used to measure the world record HEMTs in this dissertation. Xun helped a great deal with electron beam lithography. I am thankful to everyone in the N-Polar HEMT team. It was always fun to bounce ideas off each other, and I am truly grateful for having the opportunity to work with each one of you. Good Luck in developing future N-Polar HEMTs for W-Band and other frequency ranges.

I am also grateful to many people within the Mishra group. Thank you to Geetak, Chirag, Onur, Anchal, and Jeong. I know not all of you overlapped with each other as much as you did with me, but I always appreciated our late night conversations. They helped make working past midnight much more enjoyable. Also, thank you to Silvia, I had fun with our late night conversations too. I will always appreciate the friendship I have developed with many of the Mishra group members, both past and present. Finally, I would

vi

like to thank the Mishra group members past and present, Geetak, Cory, Elaheh, Karine, Yuuki, Davide, Maher, Trey, Ramya, Jing, Jeonghee, Pawana, Nirupam, Shubhra, Athith, Christian Roberston, Christian Wurm, Aditya, Weiyi, Yusuke, Dan, Carl, Sansuptak, Shalini, Ajay, Nidhi, Seshadri, Matt, Trey, and anyone else I missed.

I would like to thank the cleanroom staff, Tom Reynolds, Bill Mitchell, Brian Thibeault, Don Freeborn, Nigh Cao, Adam Abrahamsen (past), Aiden Hopkins, Brian, Michael Silva, Demis, and Biljana.

I am thankful for my colleagues at Transphorm for allowing me the opportunity to work on my thesis while an employee and finally finish.

I would like to thank my family, my Mother, Father, Alex, and Eric. I love you all very much.

I am very thankful for having the opportunity to conduct excellent research within the wonderful facilities at UCSB, I am also happy to be finally free.

#### **DEC 2018**

#### **EDUCATION**

| University of California, Santa Barbara,<br>Santa Barbara, CA<br>Ph.D. Electrical Engineering<br>Expected Sept 2018<br>Project: Design, fabrication, and characterization of mm-wave N-Polar GaN HEMTs<br>Advisor: Prof. Umesh Mishra                                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| M.S. Electrical and Computer Engineering                                                                                                                                                                                                                                                                                                                  |    |

| Dec. 2012                                                                                                                                                                                                                                                                                                                                                 |    |

| University of Maryland<br>College Park, MD<br>B.S. Electrical Engineering                                                                                                                                                                                                                                                                                 |    |

| May 2010                                                                                                                                                                                                                                                                                                                                                  |    |

| PROFESSIONAL EXPERIENCE                                                                                                                                                                                                                                                                                                                                   |    |

| University of California Santa Barbara,SantaBarbara, CAGraduate Student Researcher                                                                                                                                                                                                                                                                        | ta |

| Sept 2010 – Present                                                                                                                                                                                                                                                                                                                                       |    |

| <ul> <li>Design, fabricate, and test novel N-Polar GaN HEMTs for mm-wave applications.</li> <li>Produced GaN devices demonstrating world record large signal power performance at W-Band (over 2X power density of any non-UCSB HEMT technology at 94 GHz and above).</li> <li>Wrote grant proposals and presented results to program manager.</li> </ul> |    |

| Teaching Assistant Jan                                                                                                                                                                                                                                                                                                                                    | l  |

| 2016 – June 2016                                                                                                                                                                                                                                                                                                                                          |    |

| <ul><li>Assisted in the teaching of Prof. Mishra's graduate level Semiconductor Device Physics courses.</li><li>Held office hours, prepared and graded Final Exams.</li></ul>                                                                                                                                                                             |    |

| Army Research Lab: Sensors and Electron Devices Directorate         Adelphi, MD         Engineering Technician: Electronic Materials and Devices         June                                                                                                                                                                                             | •  |

| 2010 – Aug 2010                                                                                                                                                                                                                                                                                                                                           |    |

| • Characterized the effects of partial strain relaxation on the optical properties in lattice mismatched semipolar InGaN films with polarization dependent photoluminescence measurements.                                                                                                                                                                |    |

• Compared measurements with theory to assist in the prediction band structure parameters for InGaN films.

#### 2009 - June 2010

- Jointly developed experimental procedure and signal processing code for taking Radar Cross Section Measurements within ARL's Anechoic Chamber.

- Aided in design and testing of broadband antennas for use in army's ultra-wideband radar system.

#### **PUBLICATIONS**

#### Journal Publications

- S. Wienecke, B. Romancyzk, M. Guidry, H. Li, X. Zheng, E. Ahmadi, K. Hestroffer, S. Keller, and U. K. Mishra, "N-polar GaN cap MISHEMT with record power density exceeding 6.5 W/mm at 94 GHz," *IEEE Electron Device Letters*, vol. 38, no. 3, pp. 359-362, Jan 2017. DOI: <u>10.1109/LED.2017.2653192</u>

- S. Wienecke, B. Romanczyk, M. Guidry, H. Li, X. Zheng, E. Ahmadi, K. Hestroffer, S. Keller, and U. K. Mishra, "N-Polar Deep Recess MISHEMTs with Record 2.9 W/mm at 94 GHz," *IEEE Electron Device Letters*, vol. 37, no. 6, pp. 713-716, June 2016. DOI: <u>10.1109/LED.2016.2556717</u>

- B. Romanczyk, M. Guidry, S. Wienecke, H. Li, E. Ahmadi, K. Hestroffer, S. Keller, and U. K. Mishra, "Record 34.2% efficient m-wave N-polar AlGaN/GaN MISHEMT at 87 GHz," *IETS Digital Library Electron Device Letters*, vol. 52, no. 21, pp. 1813-1814, Sept. 2016. DOI: <u>10.1049/el.2016.2664</u>

- B. Romanczyk, S. Wienecke, M. Guidry, H. Li, E. Ahmadi, X. Zheng, S. Keller, and U. K. Mishra, "Demonstration of 8 W/mm Power Density at 10, 30, and 94 GHz in State-of-the-Art Millimeter-Wave N-Polar GaN MISHEMTs," *IEEE Trans. on Electron Devices*, vol. 65, no. 1, pp. 45 – 50. Jan 2018. DOI: <u>https://doi.org/10.1063/1.5010944</u>

- H. Li, S. Wienecke, B. Romanczyk, E. Ahmadi, E. Ahmadi, M. Guidry, X. Zheng, S. Keller, and U. K. Mishra, "Enhanced mobility in vertically scaled N-polar high-electron-mobility transistors using GaN/InGaN composite channels," *Applied Physics Letters*, vol. 112, pp. 073501-1–073501-5, Jan 2018. DOI: https://doi.org/10.1063/1.5010944

- X. Zheng, M. Guidry, E. Ahmadi, K. Hestroffer, B. Romanczyk, S. Wienecke, S. Keller, and U. K. Mishra, "N-Polar GaN MIS-HEMTs on Sapphire With High Combination of Power Gain Cutoff Frequency and Three-Terminal Breakdown Voltage," *IEEE Electron Device Letters*, vol. 37, no. 1, pp. 77-80, January 2016. DOI: <u>10.1109/LED.2015.2502253</u>

- S. Keller, C. Lund, T. Whyland, Y. Hu, C. Neufeld, S. Wienecke, F. Wu, S. Nakamura, J. S. Speck, S. P. DenBaars, and U. K. Mishra, "InGaN lattice constant engineering via growth on (In,Ga)N/GaN nanostripe arrays," *Semiconductor Science and Technology*, vol. 30, no. 10, pp. 105020-1–105020-9, September 2015. DOI: 10.1088/0268-1242/30/10/105020

- M. A. Laurent, G. Gupta, S. Wienecke, a. a. Muqtadir, S. K. Keller, S. P. DenBaars, and U. K. Mishra, "Extraction of net interfacial polarization charge from Al<sub>0.54</sub>In<sub>0.12</sub>Ga<sub>0.34</sub>N/GaN high electron mobility transistors grown by metalorganic chemical vapor deposition," *Journal of Applied Physics*, vol. 116, pp. 183704-1–183704-6, November 2014. DOI: <u>10.1063/1.4901834</u>

- E. Ahmadi, R. Shivaraman, F. Wu, S. Wienecke, S. W. Kaun, S. Keller, J. S. Speck, and U. K. Mishra, "Elimination of columnar microstructure in N-face InAlN, lattice-matched to GaN, grown by plasmaassisted molecular beam epitaxy in the N-rich regime," vol. 104, pp. 072107-1–072107-3, Feb. 2014. DOI: <u>10.1063/1.4866435</u>

- X. Liu, R. Yeluri, J. Kim, S. Lal, A. Raman, C. Lund, S. Wienecke, J. Lu, M. Laurent, S. Keller, and U. K. Mishra, "In-situ metalorganic chemical vapor deposition and capacitance-voltage characterizations of Al<sub>2</sub>O<sub>3</sub> on Ga-face metal-oxide-semiconductor capacitors," Applied Physics Letters, vol. 103, pp. 053509-1–053509-5, July 2013. DOI: <u>10.1063/1.4817385</u>

- X. Liu, J. Kim, D. J. Suntrup, S. Wienecke, M. Tahhan, R. Yeluri, S. H. Chan, J. Lu, H. Li, S. Keller, and U. K. Mishra, "Metalorganic chemical vapor deposition of Al2O3 on N-face GaN and evidence of polarity induced fixed charge," *Applief Physics Letters*, vol. 104, no. 26, pp. 263511-1–263511-4, July 2014. DOI: 10.1063/1.4886768

- H. Li, B. Mazumder, B. Bonef, S. Keller, S. Wienecke, J. S. Speck, S. P. Denbaars, and U. K. Mishra, "Characterization of N-polar AlN in GaN/AlN/(Al,Ga)N heterostructures grown by metal-organic chemical vapor deposition," *Semiconductor Sci. and Technology*, avol. 32, no. 11, pp. 115004-1–

115004-5, Sept. https://doi.org/10.1088/1361-6641/aa8b30 2017,

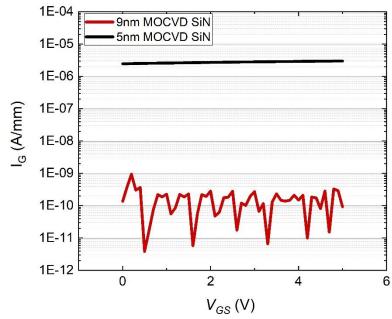

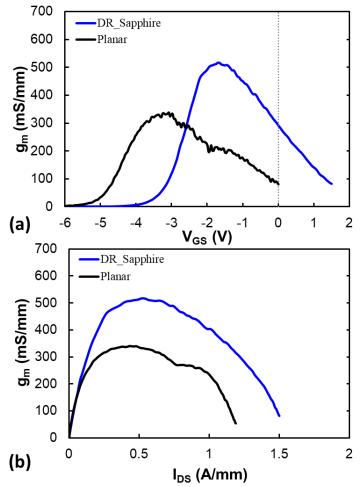

• X. Zheng, H. Li, M. Guidry, B. Romanczyk, E. Ahmadi, K. Hestroffer, **S. Wienecke**, S. Keller, U. K. Mishra, "Analysis of MOCVD SiNx Passivated N-Polar GaN MIS-HEMTs on Sapphire With High *f<sub>max</sub>*·*V<sub>DS,Q</sub>*," in *IEEE Electron Device Letters*, vol. 39, no. 3, pp. 409-412, March 2018. doi: 10.1109/LED.2018.2799160

- D. Bisi, C. D. Santi, M. Meneghini, S. Wienecke, M. Guidry, H. Li, E. Ahmadi, S. Keller, U. K. Mishra, "Observation of Hot Electron and Impact Ionization in N-Polar GaN MIS-HEMTs," in *IEEE Electron Device Letters*, vol. 39, no. 7, pp. 1007-1010, July 2018. doi: 10.1109/LED.2018.2835517

- O. S. Koksaldi, O. S. Koksaldi, J. Haller, H. Li, B. Romanczyk, M. Guidry, S. Wienecke, S. Keller, U. K. Mishra, "N-Polar GaN HEMTs Exhibiting Record Breakdown Voltage Over 2000 V and Low Dynamic On-Resistance," in *IEEE Electron Device Letters*, vol. 39, no. 7, pp. 1014-1017, July 2018. doi: 10.1109/LED.2018.2834939

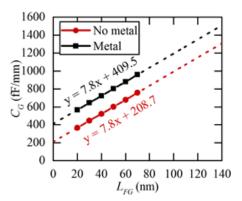

#### Conference

- S. Wienecke, B. Romanczyk, M. Guidry, H. Li, X. Zheng, E. Ahmadi, K. Hestroffer, S. Keller, and U. K. Mishra, "Effect of Sidewall Capacitance on N-Polar GaN Cap MISHEMT Performance," 2016 Lester Eastman Conference on High Performance Devices (LEC), Bethlehem, PA, August 2016. (received Best Student Paper Award)

- S. Wienecke, B. Romanczyk, M. Guidry, H. Li, X. Zheng, E. Ahmadi, K. Hestroffer, S. Keller, and U. K. Mishra, "N-Polar GaN Cap MISHEMT with Record 6.7 W/mm at 94 GHz," 74<sup>th</sup> Device Research Conference, June 2016.

- S. Wienecke, B. Romanczyk, M. Guidry, H. Li, X. Zheng, E. Ahmadi, K. Hestroffer, S. Keller, and U. K. Mishra, "N-Polar Deep Recess HEMTs for W-Band Power Applications," 42nd International Symposium on Compound Semiconductors (ISCS), Santa Barbara, CA, July 2015, pp. 197–198.

- S. Wienecke, M. Guidry, H. Li, E. Ahmadi, K. Hestroffer, X. Zheng, S. Keller, and U. K. Mishra, "Optimization of Back-Barrier Doping in Graded AlGaN N-Face HEMTs," 2014 Lester Eastman Conference on High Performance Devices (LEC), Ithaca, NY, August 2014. (received Best Student Poster Award)

- B. Romanczyk, S. Wienecke, M. Guidry, H. Li, E. Ahmadi, X. Zheng, S. Keller, and U. K. Mishra, "W-band N-polar GaN MISHEMTs with high power and record 27.8% efficiency at 94 GHz," *Electon Devices Meeting (IEDM)*, Dec. 2016

#### HONORS AND AWARDS

**University of California, Santa Barbara**: Best student paper at the 2016 Lester Eastman Conference on High Performance Devices, Best student poster presentation at the 2014 Lester Eastman Conference on High Performance Devices.

University of Maryland: National SMART Grant, Corcoran Scholarship, and Yurie Scholars in Engineering Scholarship

#### ABSTRACT

#### N-Polar GaN Deep Recess MISHEMTs for mm-Wave Applications

by

#### Steven M. Wienecke Jr.

GaN based high electron mobility transistors (HEMTs) have emerged as a leading technology for mm-wave (30-300 GHz) wireless applications. Specifically, great interest has been shown in GaN transistors for high power transmitter applications in the W-band portion of the frequency spectrum (75-110GHz) where atmospheric attenuation of RF signals experiences a local minimum. To date, reports on W-band GaN HEMTs and monolithic microwave integrated circuits (MMICs) have primarily featured devices fabricated in the Ga-Polar (0001) orientation. In this work, the advantages of N-Polar GaN are exploited to produce a metal-insulator-semiconductor (MIS-HEMT) exhibiting (at the time) record high power amplification performance at 94 GHz.

The key difference between Ga-Polar and N-Polar HEMTs is the orientation of the polarization fields. In N-Polar, the field orientation enables the fabrication of a novel recessed gate structure with the addition of an unintentionally doped (UID) GaN cap layer in the device access regions. This GaN cap serves a dual purpose. First, it effectively removes the DC-to-RF dispersion commonly seen in III-N transistors (dispersion in this sense refers to the phenomena where the device's large signal RF power performance is significantly

xi

worse than that predicted from static DC measurements). The GaN cap removes this dispersion with a smaller capacitive penalty than traditional methods typically used in Ga-Polar transistors. Secondly, the GaN cap acts to reduce surface depletion, significantly reducing sheet resistance in the access regions. By reducing both the parasitic resistive and capacitive elements of the transistor, excellent large signal RF performance is achieved at very high frequencies.

In this work, the device concept is introduced and the fabrication procedure is detailed. Several aspects of the device structure are examined, optimized, and record (at the time) performance results are presented.

# Contentsviii

| Chapter 1 – Introduction                                                    |     |

|-----------------------------------------------------------------------------|-----|

| Chapter 1.1 – Introduction to GaN:1                                         |     |

| Chapter 1.2 – RF Amplifier Key Performance Metrics:                         |     |

| Chapter 1.3 – Historical Development of GaN for RF Amplification Purposes   | 3:8 |

| Chapter 1.4 – Development of III-N HEMTs for W-Band Application:10          |     |

| Chapter 1.5 – Advantages of the N-Polar Orientation in III-N Transistors:14 |     |

| Chapter 1.5.1 – N-Polar's Natural Back-Barrier:                             |     |

| Chapter 1.5.2 – Better Ohmic Contacts:                                      |     |

| Chapter 1.5.3 – N-Polar AlGaN Top Barrier:                                  |     |

| Chapter 1.5.4 – GaN Cap in Access Region of N-Polar Transistor:20           |     |

| Chapter 1.6 – Synopsis of Thesis:                                           |     |

| References                                                                  |     |

| Chapter 2 – Planar N-Polar MISHEMT Optimization 29                          |     |

|                                                                             |     |

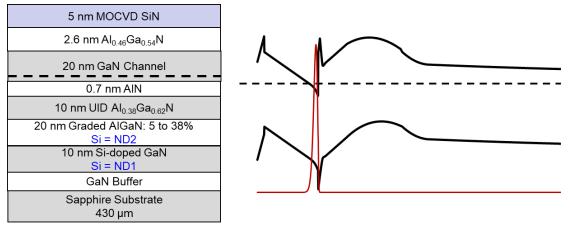

| Chapter 2.1 – MOCVD Growth and Basic Device Structure:                      |     |

| Chapter 2.1 – MOCVD Growth and Basic Device Structure:                      |     |

|                                                                             |     |

| Chapter 2.2 – Gate Cap Stack Experiments:                                   |     |

| Chapter 2.2 – Gate Cap Stack Experiments:                                   |     |

| Chapter 2.2 – Gate Cap Stack Experiments:                                   |     |

| Chapter 2.2 – Gate Cap Stack Experiments:                                   |     |

| Chapter 2.2 – Gate Cap Stack Experiments:                                   |     |

| Chapter 2.2.8 – Additional Semiconductor/Dielectric Quality Experiments:                        |

|-------------------------------------------------------------------------------------------------|

|                                                                                                 |

| Chapter 2.2.9 Gate Cap Stack Conclusion:                                                        |

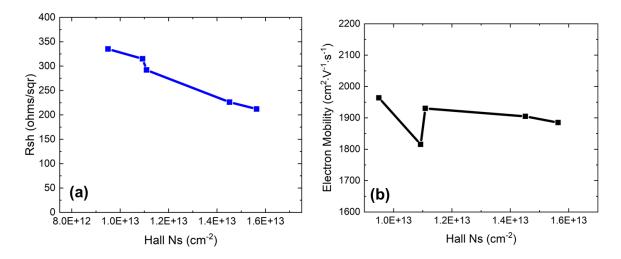

| Ch. 2.3 – Back-Barrier Doping + Channel 2DEG Density Optimization: 61                           |

| Chapter 2.3.1 – Introduction:                                                                   |

| Chapter 2.3.2 – Experimental Details + Fabrication Procedure:64                                 |

| Chapter 2.3.3 – DC and Small-Signal RF Results:                                                 |

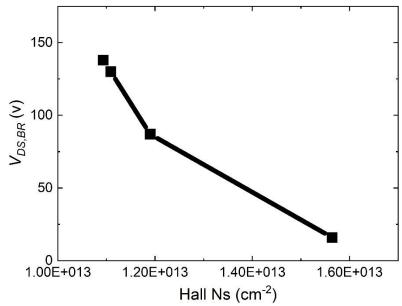

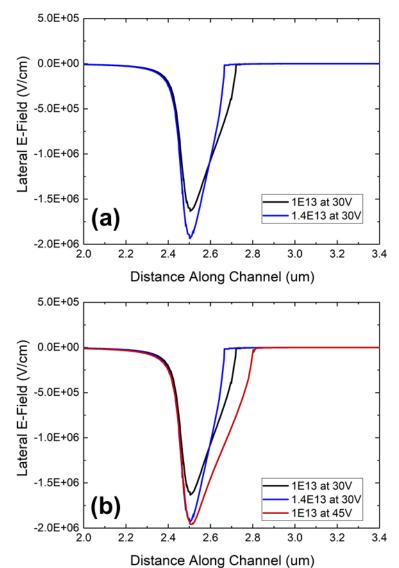

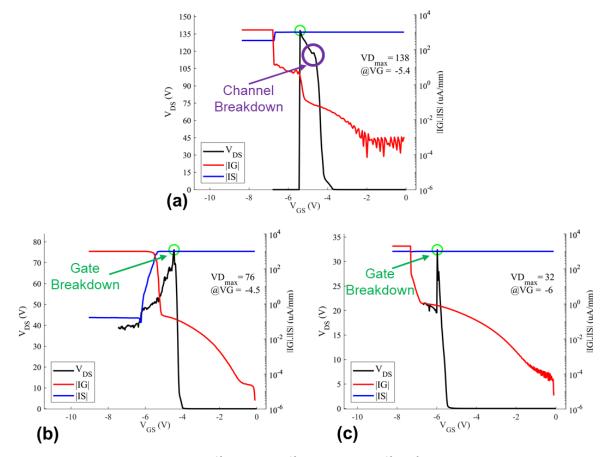

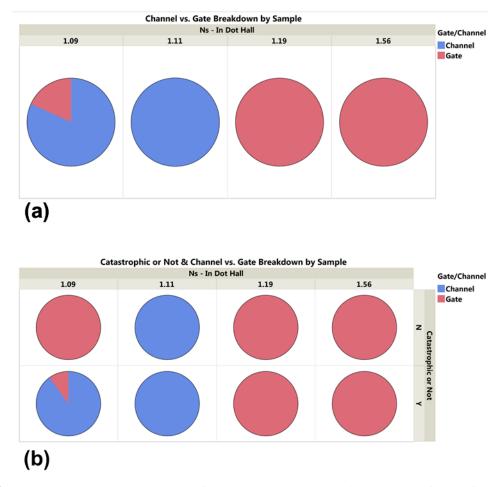

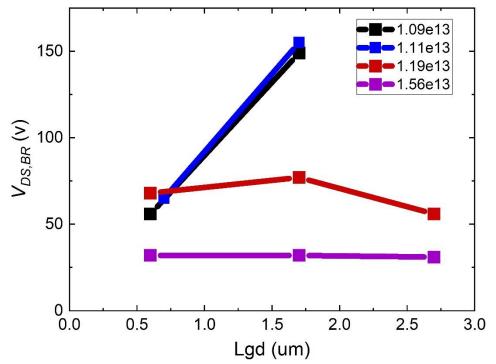

| Chapter 2.3.4 – Breakdown Voltage:                                                              |

| Chapter 2.3.5 – Dispersion:                                                                     |

| Chapter 2.3.6 – Doping Series Conclusion:                                                       |

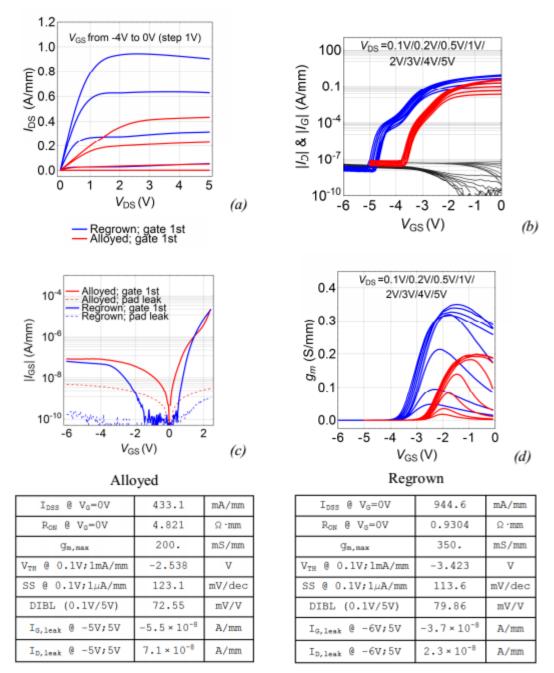

| Ch. 2.4 – Alloyed vs. Regrown Contacts                                                          |

| Chapter 2.4.1 – Experimental Details + Fabrication Procedure:85                                 |

| Chapter 2.4.2 – Alloyed vs. Regrown Contacts – Overview:                                        |

| Chapter 2.4.3 – Alloyed vs. Regrown Contacts Comparison of $1.43 \cdot 10^{13}$ cm <sup>-</sup> |

| <sup>2</sup> Sample:                                                                            |

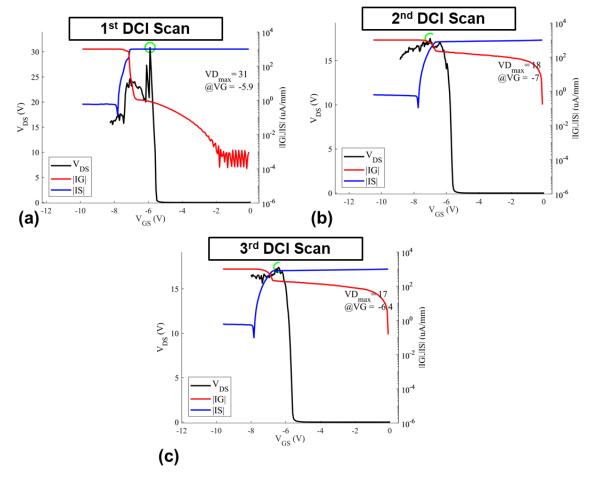

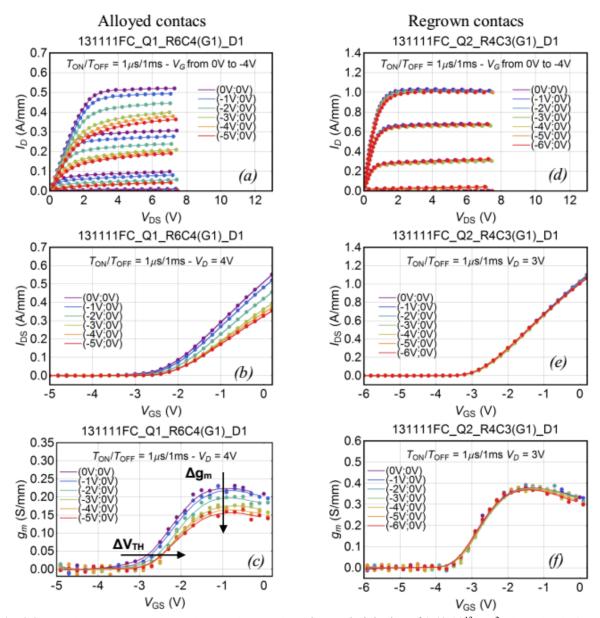

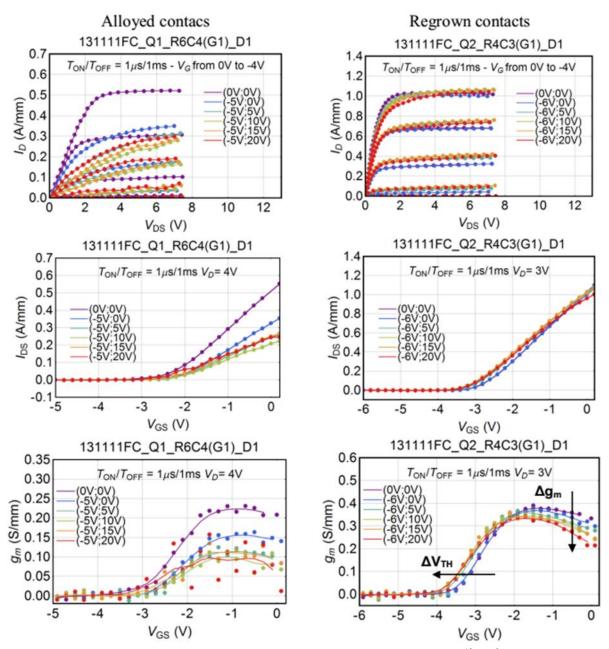

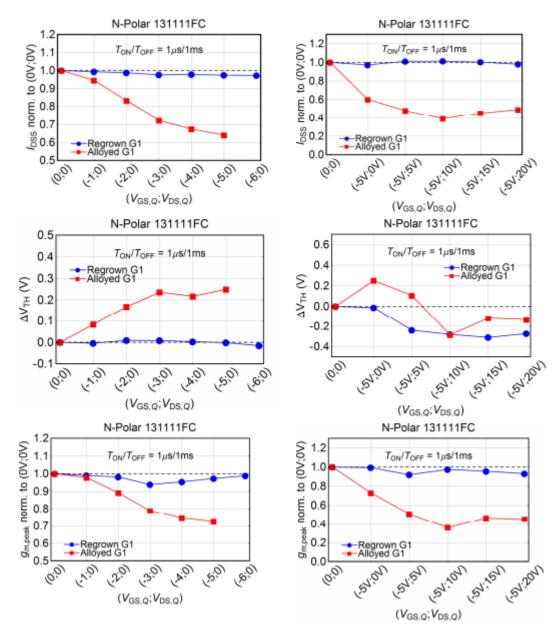

| Chapter 2.4.4 – Double Pulsed I-V Characterization:                                             |

| Chapter 2.4.5 – Small Signal RF:100                                                             |

| Chapter 2.4.6 – Conclusion:                                                                     |

| Ch. 2.5 – Planar N-Polar MISHEMT Optimization Summary:104                                       |

| References106                                                                                   |

| Chapter 3 – Intro to the N-Polar Deep Recess (NPDR) MISHEMT108                                  |

| Chapter 3.1 – Introduction + Dispersion Explanation and Traditional Solutions:                  |

|                                                                                                 |

| Chapter 3              | .2 – Deep Recess Solution to Dispersion:                | 116               |

|------------------------|---------------------------------------------------------|-------------------|

| Chapt                  | er 3.2.1 – Potential Limitations to the Ga-Polar Deep I | Recess Structure: |

|                        |                                                         | 119               |

| Chapt                  | er 3.2.2 – N-Polar Deep Recess Intro:                   |                   |

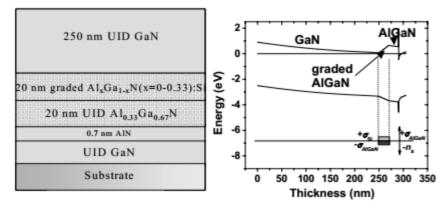

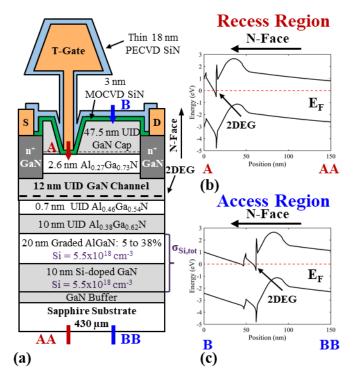

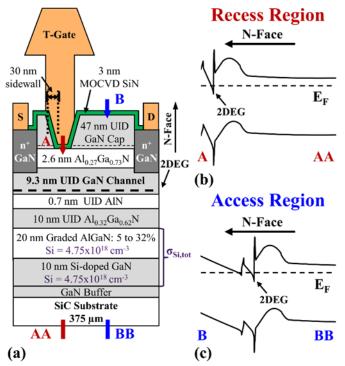

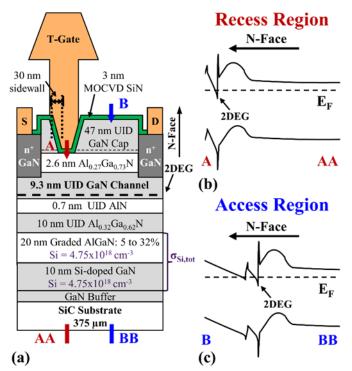

| Chapter 3              | .3 – Epi-Structure of the NPDR MIS-HEMT:                | 127               |

| Chapt                  | er 3.3.1 – Graded + Si-Doped AlGaN Back-Barrier:        | 127               |

| Chapt                  | er 3.3.2 – UID GaN Channel:                             | 129               |

| Chapt                  | er 3.3.3 – Gate Cap Stack:                              |                   |

| Chapt                  | er 3.3.4 – GaN Cap Thickness:                           |                   |

| Chapter 3              | .4 – GaN Cap Thickness Series + Fabrication Details:    | 134               |

| Chapt                  | er 3.4.1 – Growth Procedure:                            | 135               |

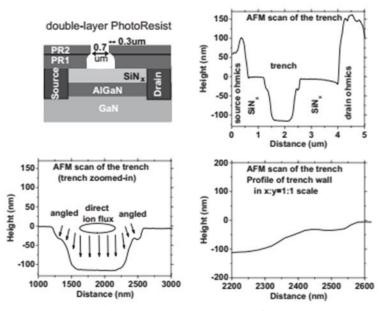

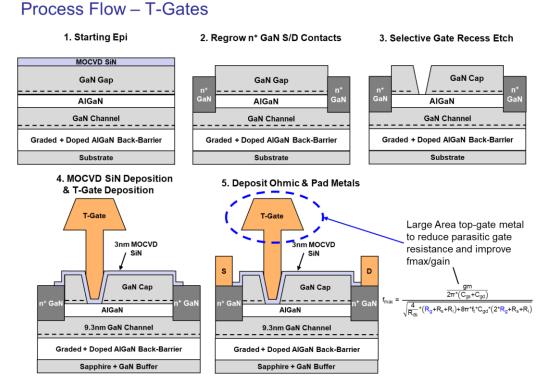

| Chapt                  | er 3.4.2 – Fabrication Procedure:                       |                   |

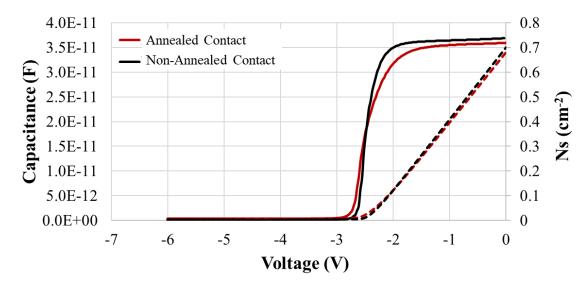

| Chapt                  | er 3.4.3 – CV and Gated TLM:                            | 139               |

| Chapt                  | er 3.4.4 – PIV Results:                                 | 145               |

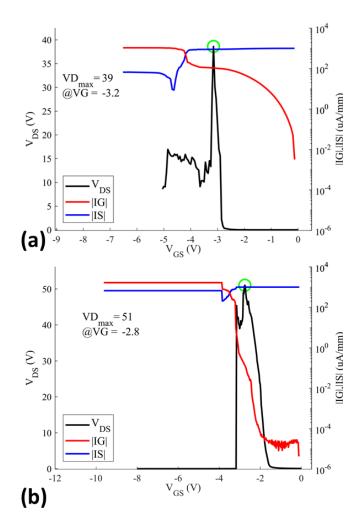

| Chapt                  | er 3.4.5 – Breakdown Voltage:                           | 146               |

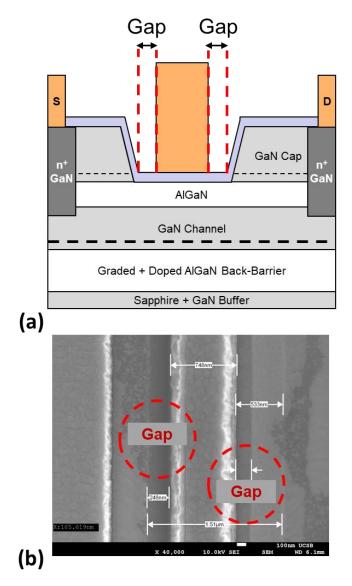

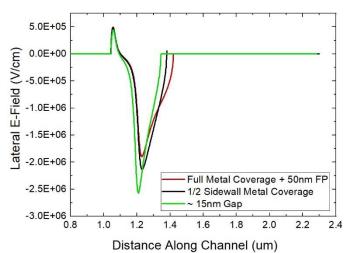

| Chapter 3              | .5 – Lateral Metal Coverage of GaN Cap Sidewall vs.     | Dispersion:       |

|                        |                                                         | 154               |

| Chapter 3              | .6 – Intro to the N-Polar Deep Recess (NPDR) MISHE      | EMT Summary:      |

|                        |                                                         | 160               |

| Reference              | 28                                                      | 161               |

| Chapter 4 – Initial T- | Gate Results on NPDR MISHEMTs                           | 163               |

| Chapter 4              | .1 – Performance Metrics for RF Power Amplifier Dev     | vices:163         |

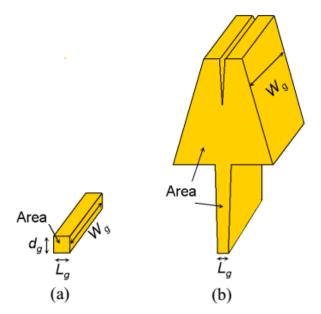

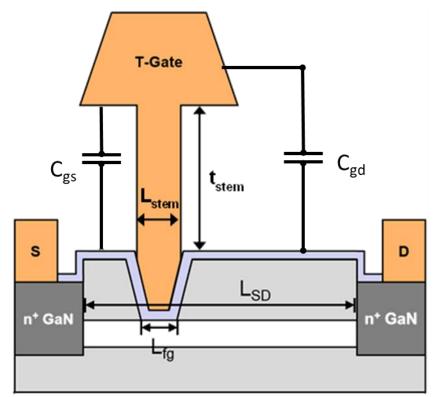

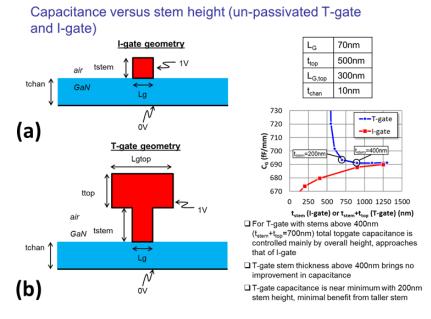

| Chapter 4              | .2 – Introduction to T-Gate Device Design:              | 167               |

|             | Chapter 4.3 – T-Gate Fabrication Procedure + Initial T-Gate Results | :172    |

|-------------|---------------------------------------------------------------------|---------|

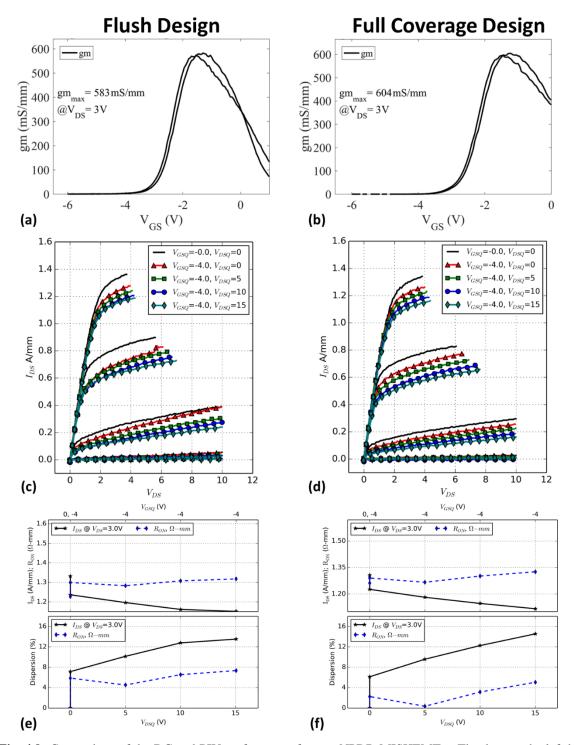

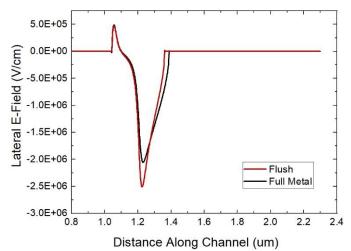

|             | Chapter 4.4 – Full Gate Metal Coverage of Sidewall vs. No Gate Me   | etal on |

|             | Sidewall:                                                           | 178     |

|             | Chapter 4.5 – Summary:                                              | 197     |

|             | References                                                          | 198     |

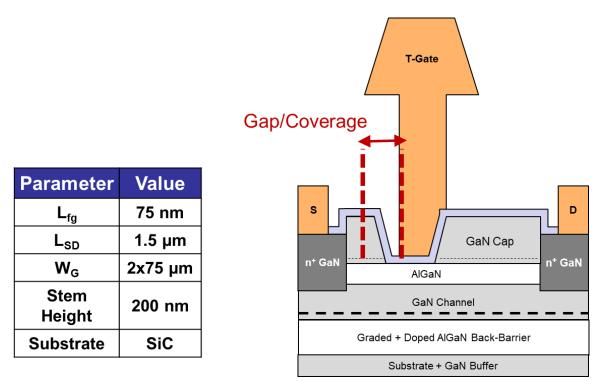

| Chapter 5 - | – Lateral Device Dimension Optimization                             | 199     |

|             | Chapter 5.1 – Growth + Fabrication Details:                         | 199     |

|             | Chapter 5.2 – Source-Drain (Gate-Drain) Spacing Series:             | 200     |

|             | Chapter 5.3 – Drain Side Metal Coverage Study on T-Gates:           | 207     |

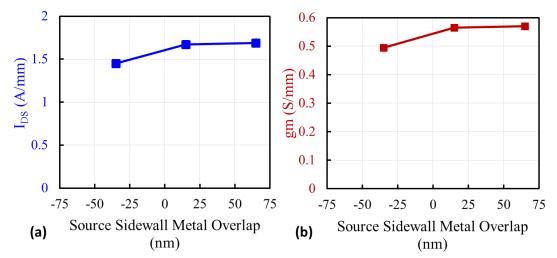

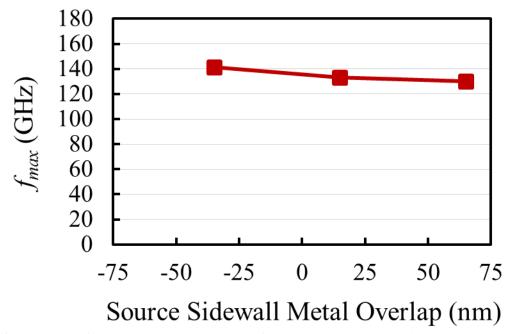

|             | Chapter 5.4 – Source Side Metal Coverage Study on T-Gates:          | 214     |

|             | Chapter 5.5 – Summary:                                              | 218     |

|             | References                                                          | 221     |

| Chapter 6   | – N-Polar GaN Cap MISHEMT with Record 6.7 W/mm at 94 GHz            | 222     |

|             | Chapter 6.1 – Introduction:                                         | 222     |

|             | Chapter 6.2 – Growth + Fabrication Details:                         | 222     |

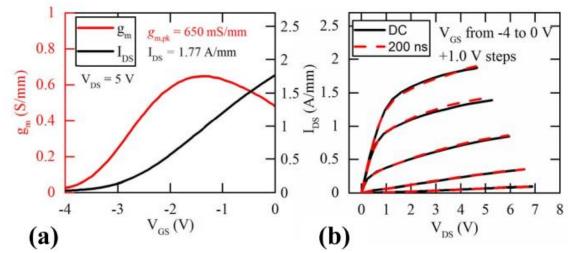

|             | Chapter 6.3 – Device Results and Discussion:                        | 223     |

|             | Chapter 6.4 – Summary:                                              | 229     |

|             | References                                                          | 230     |

| Chapter 7 - | - Conclusion + Summary and Future Work                              | 232     |

|             | Chapter 7.1 – Conclusion + Summary:                                 | 232     |

|             | Chapter 7.2 – Future Work:                                          | 237     |

|             | Chapter 7.3 – Conclusion:                                           | 240     |

|             | References                                                          | 242     |

### **Chapter 1**

#### Introduction

#### Chapter 1.1 – Introduction to GaN:

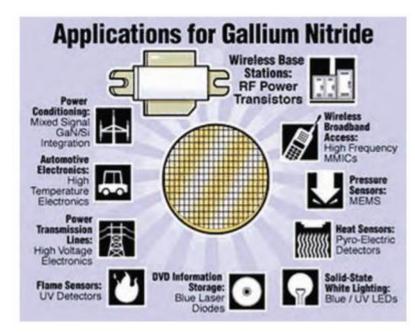

The first reports on GaN dates all the way back to 1928 in Chicago Illinois by W. C. Johnson *et al* [1]. However, research in GaN devices did not occur until 1971 when Pankove began working on the first GaN light emitting diodes (LEDs). After Pankove's initial investigations [2], progress in GaN-based devices was sluggish for many years due to the poor material quality and inability to grow p-type doped material. Improvements in the growth techniques in the 1980's and early 1990's by Akasaki, Amano, and Nakamura dramatically improved the epitaxial quality of III-N epitaxy [3-4]. Further work from these researchers also led to the successful p-type doping of GaN [5-6]. After these advances, photonic device development for LEDs and laser diodes (LDs) exploded [7-11]. Prior to the successful growth of III-N based LEDs and LDs, there was not any semiconductor family with a direct bandgap which could emit in the blue or UV portions of the spectrum. With the successful fabrication of III-N base LEDs and LDs that can emit in this range, a huge commercial industry worth over \$10 billion dollars has developed over the past 2 decades (Fig. 1.1) [12-13].

GaN and its alloys with InN and AlN posses a direct band gap ranging from 0.7 eV (InN) all the way to 6.2 eV (AlN) [14-15]. Theoretically this enables photonic devices which can emit photons anywhere from the IR to the UV portions of the electromagnetic spectrum all using only the III-N system of materials. With such qualities it makes sense that most of the early work in the III-Nitrides focused on developing the technology for use in photonic devices. However, GaN and its alloys with AlN and InN have many attractive properties for

electronic device applications as well. Table 1.1 compares some of the GaN material properties relevant to high power RF electronic devices with other semiconductors [16]. The high critical E-Field of GaN relative to

Fig. 1.1: Major current and/or projected markets for Nitride-based devices [12].

the other materials in this table enables large breakdown voltage transistors to be created with relatively small physical dimensions, reducing the parasitics of the device and allowing for better large signal gain at high frequencies. In addition, the III-N system has high values of spontaneous and piezoelectric polarization, leading to a large net polarization charge density at any heterointerface between GaN and one of its III-N alloys [17]. This enables very high two-dimensional electron gas (2DEG) densities over  $1 \cdot 10^{13}$  cm<sup>-2</sup> with reasonably high electron mobilities and saturation velocities to be induced at these heterointerfaces. The high 2DEG density and mobility leads to low extrinsic resistances and better large signal gain at high frequencies. The large 2DEG density and reasonably high saturation velocities lead to higher output current densities. Further, the wide range of accessible bandgaps along with the net

polarization charges at heterointerfaces in the III-N system offer multiple degrees of freedom in the electronic device design which simply do not exist in other semiconductor families. Together, these properties have historically made III-N high-electron-mobility-transistors (HEMTs) an attractive candidate for RF power amplification purposes [18].

| Material | Bandgap | 3    | E <sub>c</sub> | μ<br>at 300K                | V <sub>sat</sub><br>(V <sub>peak</sub> ) | 2DEG<br>density      |

|----------|---------|------|----------------|-----------------------------|------------------------------------------|----------------------|

|          | (eV)    |      | (MV/cm)        | $(cm^{-2}V^{-1}s^{-1})$     | (cm/s)                                   | (cm <sup>-2</sup> )  |

| Si       | 1.1     | 11.7 | 0.3            | 1500                        | 1<br>(1)                                 | <5x10 <sup>12</sup>  |

| InP      | 1.35    | 12.5 | 0.5            | 5400                        | 1<br>(2.3)                               | < 5x10 <sup>12</sup> |

| GaAs     | 1.43    | 13.1 | 0.4            | 8,500                       | 1<br>(2.1)                               | <5x10 <sup>12</sup>  |

| 4H-SiC   | 3.3     | 9.7  | 3              | 700                         | 2<br>(2)                                 | NA                   |

| GaN      | 3.4     | 9.5  | 3.3            | 2100 <sup>*</sup><br>(2DEG) | 1.3<br>(2.5) <sup>*</sup>                | ~1-2e13              |

**Table 1.1:** Comparison of material parameters relevant to RF electronic devices across several different semiconductors. (\* the peak saturation velocity of GaN was predicted theoretically and has not been experimentally demonstrated) [16].

#### Chapter 1.2 – RF Amplifier Key Performance Metrics:

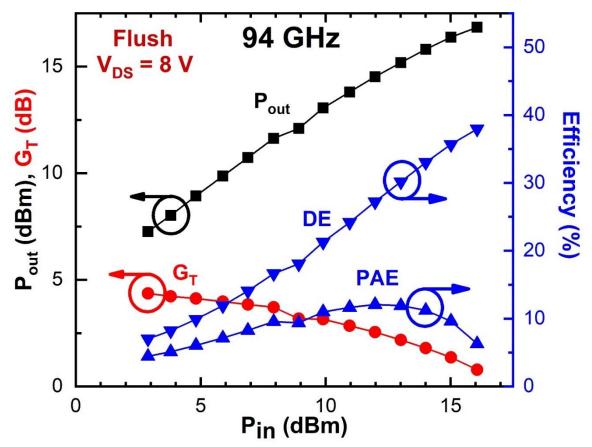

The goal of this thesis is to build the best possible semiconductor transistor for RF power amplification purposes in the W-Band (75-110 GHz) range of frequencies. In order to better understand the material in this dissertation, it is useful to review the most important aspects of RF power amplifier device fundamentals. Transistors for RF amplification purposes should be capable of producing high large signal gain, high efficiencies, and high output RF powers at the frequency range of interest. Equations for describing an RF transistor amplifier's efficiency and output RF power at a particular frequency are given below [19].

$$DE = \frac{P_{RF,out}}{P_{DC}} = \frac{P_{RF,out}}{V_{DC} \cdot I_{DC}}$$

(1.1)

$$PAE = \frac{P_{RF,out} - P_{RF,in}}{P_{DC}} = \frac{P_{RF,out}}{P_{DC}} \cdot \left(1 - \frac{1}{G}\right) = DE \cdot \left(1 - \frac{1}{G}\right)$$

(1.2)

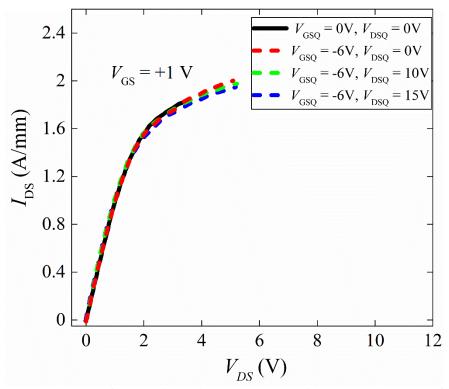

$$P_{RF,out} = \frac{\left(V_{DSQ} - V_{knee}\right) \cdot I_{DSS}}{4} \tag{1.3}$$

In equation (1.1) DE = drain efficiency,  $P_{DC}$  is the mean dissipated DC power density,  $V_{DC}$  is the mean DC voltage, and  $I_{DC}$  is the mean DC current density. In equation (1.2) PAE = power-added efficiency,  $P_{RF,out}$  = output RF power density,  $P_{RF,in}$  = input RF power density, and G = power gain at the frequency of interest. In equation (4.3),  $V_{DSQ}$  = quiescent source-drain voltage bias,  $V_{knee}$  = knee voltage of the transistor's I-V curve, and  $I_{DSS}$  = saturation current density of the transistor.

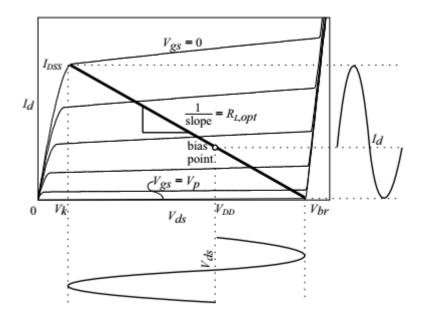

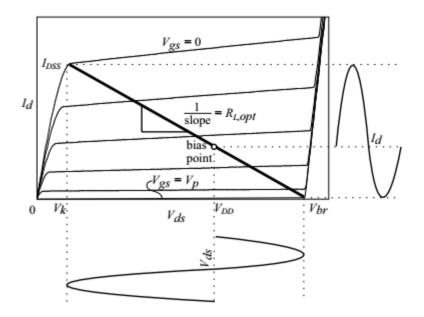

The way in which a transistor amplifier is operated determines its Amplifier "Class". There are many different types of amplifier classes, but the three which will be talked about here are Class A, Class B, and Class AB. In Class A amplifiers, the device is biased normally-on, at about half the peak-peak output current and half the peak-peak output voltage (Fig. 1.3). The main advantage of Class A operation is that it offers the highest linearity of all Amplifier Classes. However, because the transistor is always on, the peak efficiency Class A operation can achieve is only  $\approx$  50%. This is Class A's biggest drawback.

**Fig. 1.3:** Transistor operating in a Class A amplifier configuration with load line chosen for maximum power (Adapted from Mishra and Singh [20]).

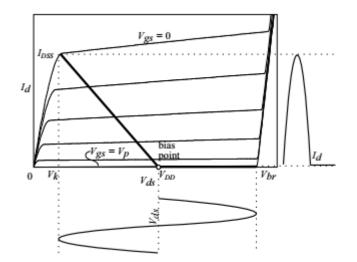

Fig. 1.4: Transistor operating in a Class B amplifier configuration (Adapted from Mishra and Singh [20]).

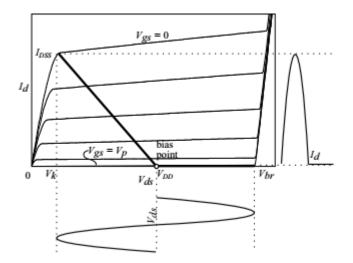

In Class B amplifiers, the device is biased at pinch-off (Fig. 1.4). The conduction angle (total number of degrees out of 360 at which the device is conducting) is  $180^{\circ}$  in this class of amplifier, meaning that the individual transistor device conducts  $\frac{1}{2}$  the time, and is in the cut-off regime the other  $\frac{1}{2}$  of the time. Because the device is only dissipating DC power

<sup>1</sup>/<sub>2</sub> the time, less DC power is consumed. This enables amplifiers of this class to theoretically achieve efficiencies as high as  $\pi/4$  (~78.6%). The drawback of Class B is that it is less linear than Class A. Further, it requires that the transistor has high RF transconductance at or near pinch-off, which is not always the case. Class AB amplifiers are a compromise between Class A and Class B. Here, the conduction angle is  $180^{\circ} < \theta < 360^{\circ}$ . It is a compromise between efficiency and linearity. Further, it relaxes the requirement of having high transconductance right at pinch-off.

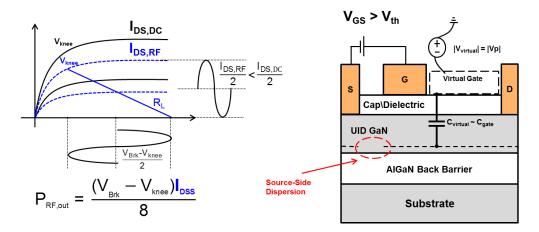

To achieve the highest possible drain efficiency allowable within any of the aforementioned Amplifier Classes, the ratio between a transistor's breakdown voltage and RF knee voltage should be high. A load line which maximizes power delivered to the load typically will cross, or at least come close to, the knee of the transistor's I-V. Therefore, the DC power dissipated at voltages below the knee voltage do not contribute to  $P_{RF,out}$ , and thus should be minimized for high drain efficiencies. Moreover, having a higher breakdown voltage allows the device to be biased to higher quiescent source-drain voltages, increasing the total  $P_{RF,out}$  and reducing the hit taken to *DE* from the power dissipated below the knee voltage. Further, the breakdown voltage sets the limit on the peak RF output power that can be expected from a given transistor device. For a Class A amplifier,  $P_{RF,out,Max}$  is given by equation 1.4.

$$P_{RF,out,Max} = \frac{\left(V_{DS,Br} - V_{knee}\right) \cdot I_{DSS}}{8} \tag{1.4}$$

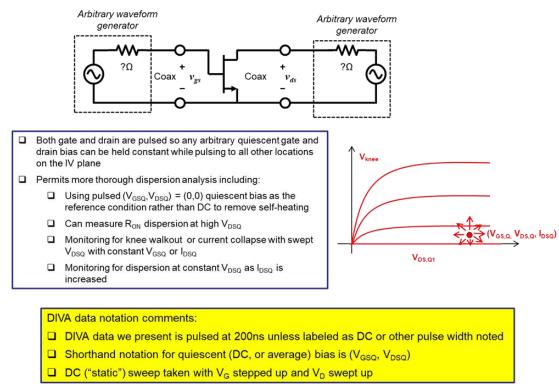

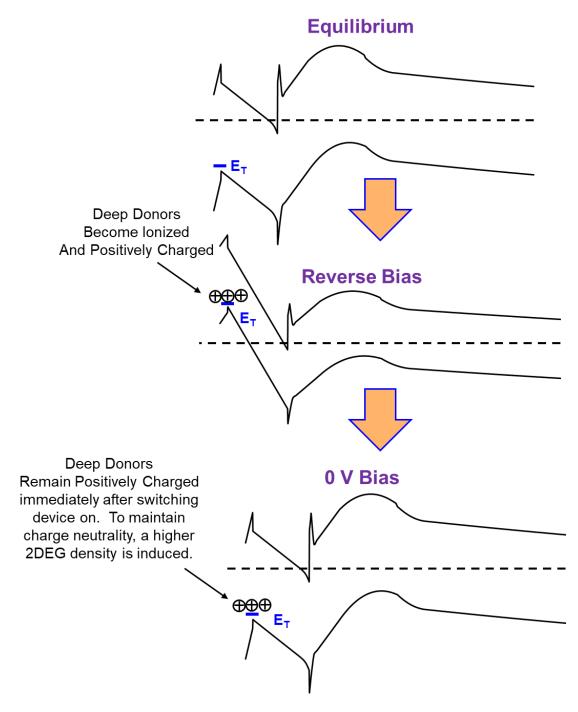

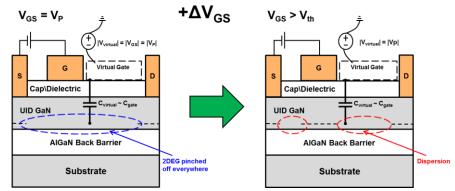

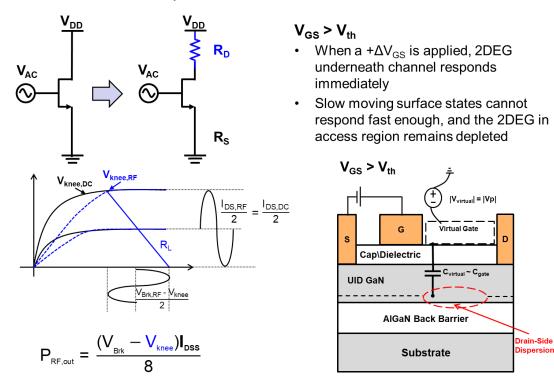

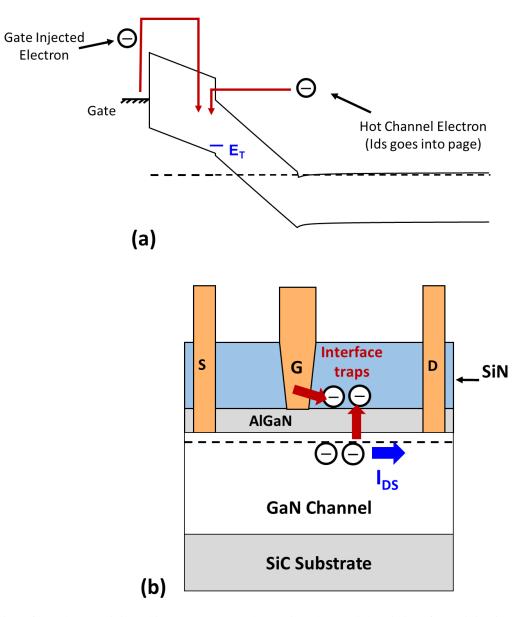

An inherent requirement for high DE in III-N transistors is the ability to control DC-to-RF dispersion. This dispersion is due to trap states in the device which cause the RF output power density to be less than what one would predict from the DC performance of the transistor in combination with equations 1.1 - 1.4 [21]. DC-to-RF dispersion plays a very large role in

III-N transistors and is explained in much greater detail in Chapter 3 of this thesis. The  $V_{knee}$  and  $I_{DSS}$  that matter in the above equations are the RF values at the application frequency. Drain-side dispersion will increase the RF  $V_{knee}$ , which will decrease both the maximum achievable RF output power as well as the drain efficiency of the device. Source-side dispersion will decrease the RF  $I_{DSS}$  and decrease the  $P_{RF,out,Max}$ . Therefore, controlling dispersion at the application frequency is critical for device performance. Successfully controlling dispersion while simultaneously achieving reasonable large signal gain at 94 GHz is an extremely important accomplishment of the work contained in this dissertation.

Power added efficiency (equation 1.2) takes into account not only the dissipated DC power, but also the input RF power required for a given output RF power. Because of this it gives a more accurate depiction of the transistor's actual overall efficiency within the circuit. As equation 1.2 shows, in order to achieve the highest possible *PAE* for a given Amplifier Class, the transistor amplifier must have both high drain efficiency and high power gain at the application frequency. *DE* is explained in the previous paragraph. Power gain *G* is related to how much an input RF signal will be amplified by the transistor amplifier at a particular frequency. During load pull measurements here at UCSB, the Maury Microwave software provides information on the transducer gain  $G_T$  of the transistor at each of the quiescent bias points. This transducer gain is related to the power gain of the transistor via equation 1.5.

$$G = 10^{\frac{G_T}{10}} \tag{1.5}$$

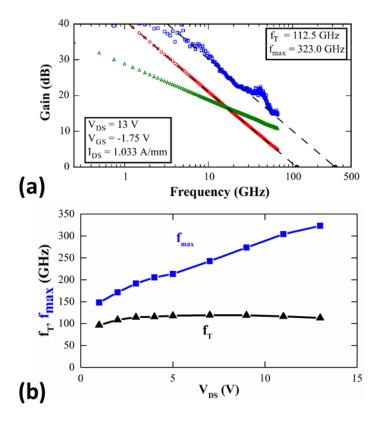

The transducer gain itself is related to (but not necessarily equal to) the unilateral gain of the transistor amplifier U. A good figure of merit for unilateral gain is the maximum frequency of oscillation, or  $f_{max}$  of the transistor (equation 1.6). This represents the frequency at which the unilateral gain becomes unity.

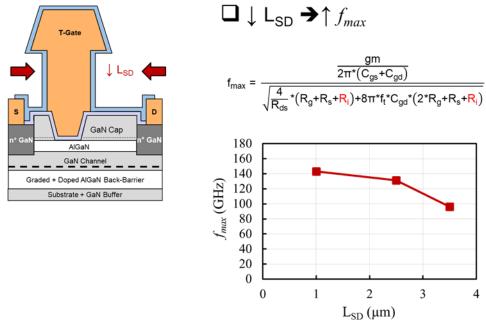

$$f_{max} = \frac{\frac{gm_{ext}}{2\pi * (C_{gs} + C_{gd})}}{\sqrt{\frac{4}{R_{ds}} * (R_g + R_s + R_i) + 4\pi * f_T * C_{gd} * (2 * R_g + R_s + R_i)}}$$

(1.6)

As an amplifier is meant to provide gain/amplify an incoming signal, the  $f_{max}$  of the transistor amplifier signifies the upper limit at which the transistor can behave as an amplifier. For reasonable power gains, the transistor amplifier must operate well below its  $f_{max}$ . Another useful figure of merit is the short-circuit current cut-off frequency  $f_T$ .

$$f_T = \frac{gm_{ext}}{2\pi * \left( \left( C_{gs} + C_{gd} \right) * \left( 1 + \frac{R_s + R_d}{R_{ds}} + C_{gd} * g_m * (R_s + R_d) \right) \right)}$$

(1.7)

# Chapter 1.3 – Historical Development of GaN for RF Amplification Purposes:

As mentioned in Section 1.1, the high critical electric fields, large 2DEG densities, and reasonably high electron saturation velocities and mobilities make III-N based HEMTs an attractive candidate for RF power amplification purposes. The first demonstration of a 2-dimensional electron gas at an AlGaN/GaN heterojunction was made by Khan in 1992 [22]. This was quickly followed by the first DC and small-signal RF measurements of an AlGaN/GaN HEMT in 1993 and 1994, respectively, by the same group [23-24].

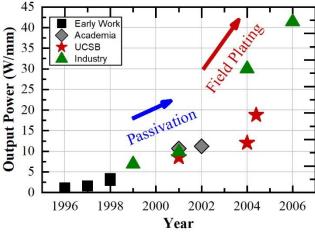

In 1996, the first large signal RF power data from an AlGaN/GaN HEMT was reported by Wu *et al* [25]. In this work he demonstrated a peak RF output power density of 1.1 W/mm at 2 GHz. For the next few years, the output power density increased steadily due to improved growth techniques, better epitaxial quality, and more advanced processing techniques (Fig. 1.6).

**Fig. 1.6:** Peak output power density versus year in III-N HEMTs. Can see large increases in power performance with introduction of techniques to reduce the DC-to-RF dispersion seen in the device [25-37].

However, the power density obtained over this period was still much lower than what one would predict if they inserted the DC values of breakdown voltage, knee voltage, and saturation current density into equation 1.4. This lower than expected RF output power density was due to DC-to-RF dispersion which can increase the RF knee voltage and/or decrease the RF current density of the transistor during large signal operation. Both of these potential effects reduce the  $P_{RF,out}$ , gain, and efficiency of the transistor amplifier. As mentioned in Section 1.2, DC-to-RF dispersion is caused by trap states locate in either the bulk semiconductor, at semiconductor heterointerfaces, or in the access regions at the surface of the III-N HEMT [38]. However, in many cases trap states in the access regions of the surface appear to be the dominant cause of this dispersion [21]. This was demonstrated in 2000 by [39] where application of an *ex situ* PECVD SiN dielectric passivation layer doubled the  $P_{RF,out}$  of the authors' III-N HEMTs. Apparently this PECVD SiN passivation layer reduced the trap density at the surface of the III-N HEMT. By 2002, use of a PECVD SiN passivation layer for reduced dispersion combined with fabrication of the AlGaN/GaN HEMT on a SiC substrate for reduced self-heating resulted in a  $P_{RF,out}$  greater than 11 W/m [32]. The adoption of field plating in 2003 further decreased the DC-to-RF dispersion in the device [33-35]. Field plating also increased the transistor's breakdown voltage. By 2006, the PECVD SiN passivation in conjunction with field plating resulted in a huge increase in  $P_{RF,out}$ with Wu *et al.* demonstrating over 40 W/mm at 4 GHz [36]. In summary, since the 1<sup>st</sup> demonstration of RF larges signal power performance in a GaN HEMT in 1996, reducing DC-to-RF dispersion has been instrumental in helping RF GaN HEMTs achieve their potential in RF transistor amplifier applications at frequencies of approximately 20 GHz or less.

#### Chapter 1.4 – Development of III-N HEMTs for W-Band Application:

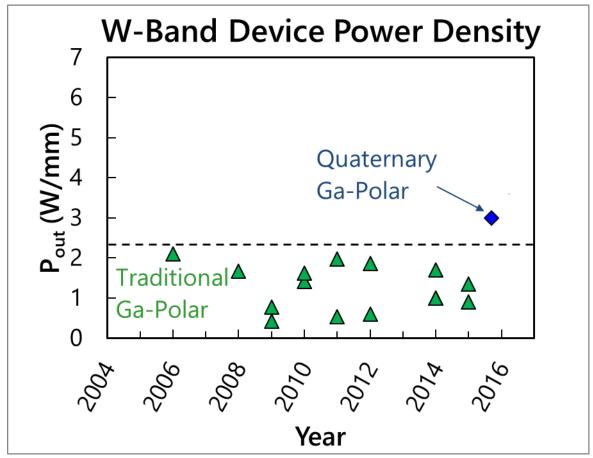

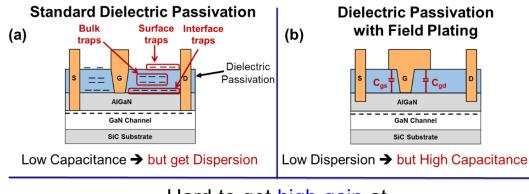

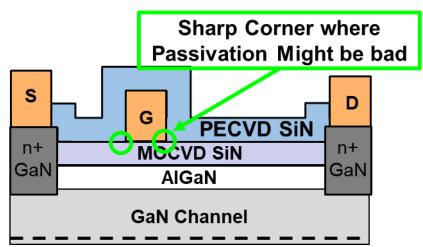

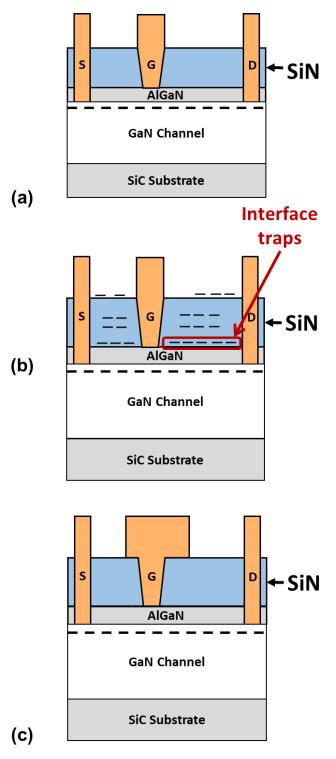

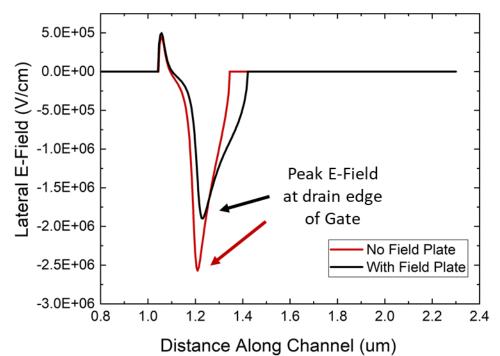

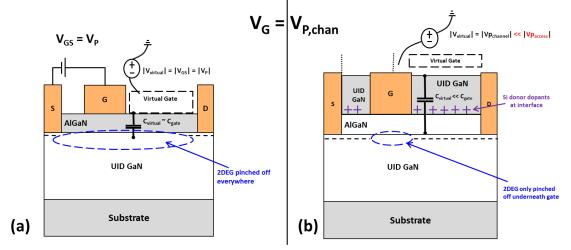

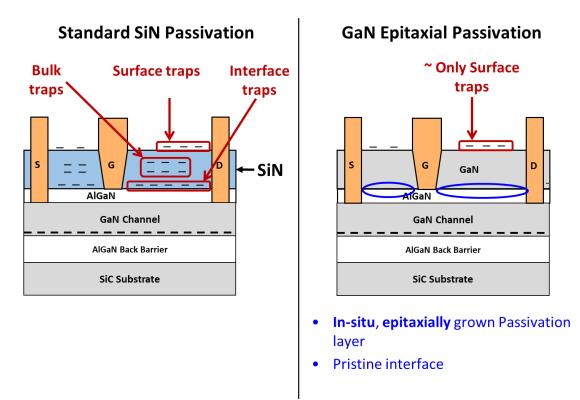

Transistors for RF amplification purposes should be capable of producing high large signal gain, high efficiencies, and high output RF powers at the frequency range of interest. Achieving all three simultaneously at W-Band (75-110 GHz) has been a struggle in the III-N material system (Fig. 1.7). As a result, relatively low  $P_{RF,out}$  has been achieved at W-Band. Further,  $P_{RF,out}$  has remained approximately flat for over a decade with conventional Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN HEMTs (Fig. 1.8) (a recent result using In<sub>y</sub>Al<sub>x</sub>Ga<sub>1-x-y</sub>N/GaN HEMTs has improved  $P_{RF,out}$  though). This is largely due to surface state related DC-to-RF dispersion. As explained in the previous section, historically, application of an *ex situ* dielectric passivation layer in conjunction with field plating has effectively removed this dispersion and enabled high power and efficiency performance in these devices [30-37], [39]. However, thick passivation layers and/or field plating is prohibitive at W-band due to the large parasitic capacitances they introduce. Thus, in order to get the sufficient small-signal RF gain (equations 1.6 and 1.7) at W-Band frequencies, most groups fabricating W-Band III-N

transistors do not use any field plating, and rely only on a relatively thin PECVD SiN passivation layers for controlling dispersion [42] (Fig. 1.9). As a result, they cannot push to higher drain voltages without experiencing large amounts of dispersion, ultimately limiting their large signal power performance at this frequency to roughly 2 W/mm in the AlGaN/GaN based HEMTs (3W/mm was recently demonstrated on an In<sub>y</sub>Al<sub>x</sub>Ga<sub>1-x-y</sub>N/GaN HEMT). Therefore, the reported RF output power densities at this frequency range has been much lower than what III-N HEMTs are theoretically capable of in absence of the DC-to-RF dispersion phenomenon.

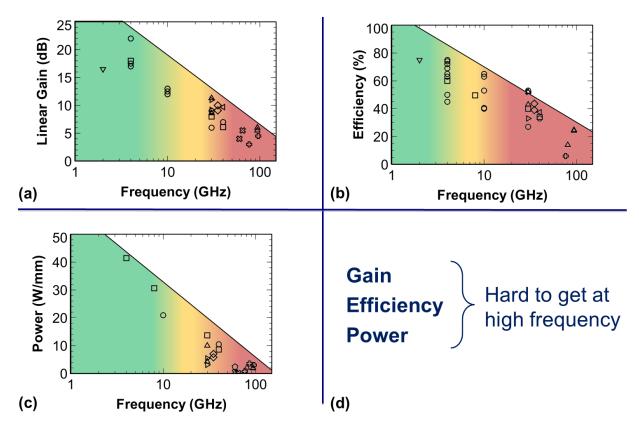

# GaN High Frequency Performance Challenges

**Fig 1.7:** Large signal power performance for III-N HEMTs with respect to frequency. (a) Linear Gain (dB), (b) *PAE*, and (c) output RF power density versus frequency. Can clearly see that that the RF large signal power performance degrades with increasing frequency. (d) Summarizes the challenges facing III-N system at higher frequencies [40].

**Fig. 1.8:** Output RF power density at the W-Band range of frequencies for Ga-Polar III-N HEMTs. Can see that the power density has remained flat in conventional (AlGaN/GaN) Ga-Polar transistors at this frequency range for over a decade. Recently, an InAlGaN top-barrier HEMT has led to a higher output power density at 94 GHz, however [41].

# Hard to get high gain at W-Band without Dispersion

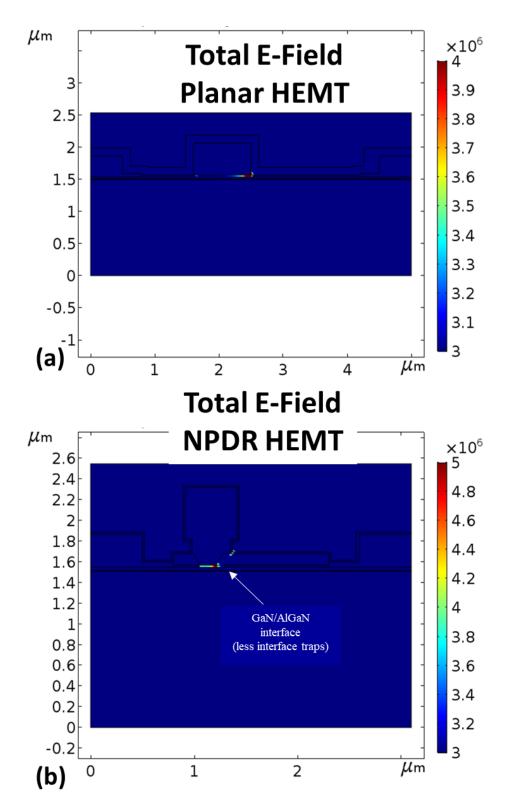

**Fig. 1.9:** (a) Dielectric passivation only, typical of many Ga-Polar transistor designed for W-Band operation [41]. Lack of field plating means higher E-Fields for a given  $V_{DS}$  bias, making electron injection into trap states more likely. (b) Field plated device. Reduced E-Fields resulting in reduced electron trapping, but higher capacitances will limit the gain at W-Band frequencies.

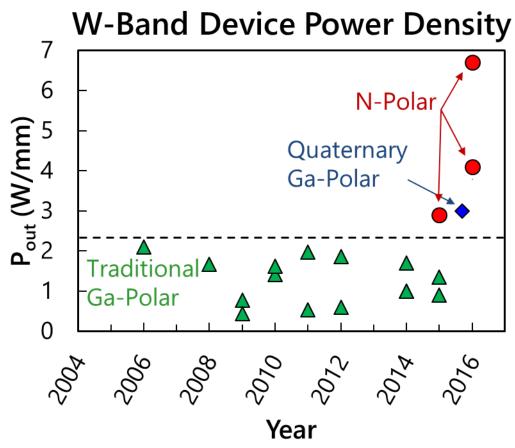

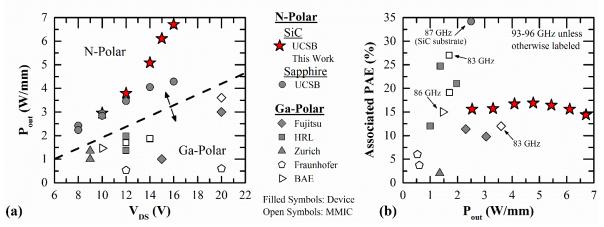

However, the N-Polar GaN metal-insulator HEMTs (MISHEMTs) reported in this work provide much higher power densities at 94 GHz (Fig. 1.10) [43-44]. The 6.7 W/mm power density reported towards the end of this dissertation is over 2x higher than the highest reported  $P_{RF,out}$  at this frequency in the Ga-Polar transistors fabricated by virtually everyone else outside UCSB [44]. Details on the differences between Ga-Polar and N-Polar GaN transistors are given in the next section.

**Fig. 1.10:** Figure 1.9 with results from this thesis added to the chart. Can see that the N-Polar MISHEMTs developed in this dissertation more than doubled the highest Ga-Polar W-Band transistor power density [43-44] [41].

#### Chapter 1.5 – Advantages of the N-Polar Orientation in III-N Transistors:

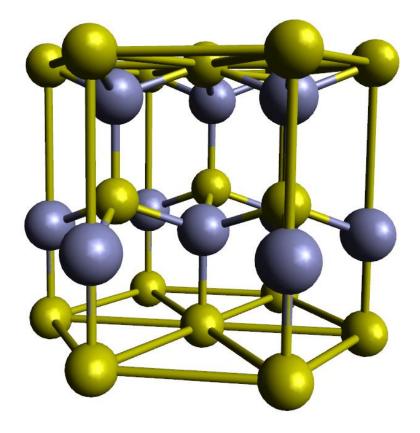

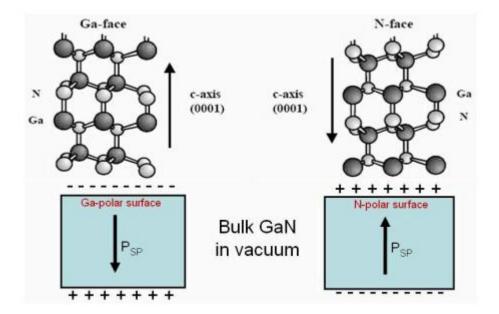

GaN and its alloys are typically grown in the wurtzite crystallographic phase (Fig. 1.11). Wurtzite GaN (as well as InN and AlN) IS a polar material, containing high values of both spontaneous and piezoelectric polarization [46]. At heterojunctions between GaN and one of its alloys with AlN or InN, a polarization discontinuity results, creating a net polarization charge at the heterointerface. The directions of maximum polarity are the (0001) and  $(000\overline{1})$ , also known as the Ga-Polar and N-Polar faces, respectively. These faces can be interpreted as the top and bottom hexagons of Fig. 1.11. Fig. 1.12 shows the bond directions

for each of these crystallographic faces. Because of the reversed bond directions, the direction of the polarization dipole is also reversed between Ga-Polar and N-Polar. However, the magnitude of the polarization constants is the same.

Fig. 1.11: One representation of the unit cell of a wurtzite crystal [45].

The opposite orientation of the polarization fields in Ga and N-Polar HEMTs is the key difference between the two, and leads to several inherent advantages for N-Polar HEMTs relative to their Ga-Polar counterparts.

Fig. 1.12: Orientation of the bond structure and polarization dipole in both Ga-Polar and N-Polar GaN [47].

Chapter 1.5.1 – N-Polar's Natural Back-Barrier:

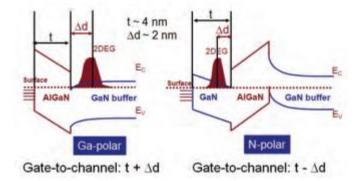

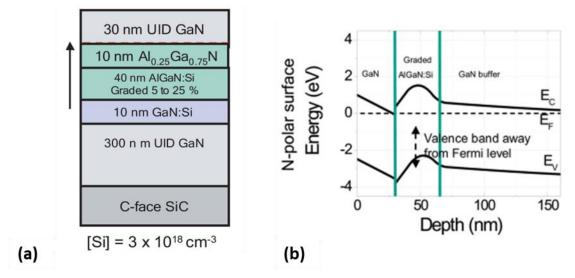

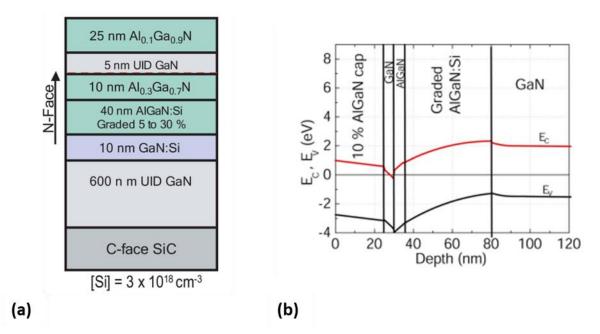

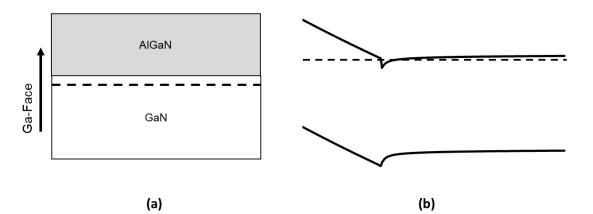

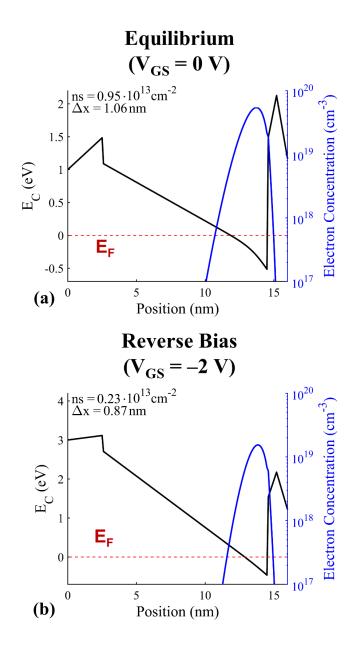

In N-Polar HEMTs, the fields are such that the charge inducing barrier is located at the back of the HEMT, not the top like in Ga-Polar (Fig. 1.13).

Fig. 1.13: Energy band diagram at equilibrium for simple Ga and N-Polar HEMT epitaxial structures [48].

This creates a natural back-barrier for the channel 2DEG in N-Polar HEMTs, improving the overall gate control of the channel charge and improving the output resistance of the device. Additionally, this back-barrier presents an additional barrier to electron transport from the channel into the bulk substrate, thus reducing the substrate leakage of the device without the use of intentional deep level acceptor dopants. This property is potentially very useful in GaN high power electronics grown on Si substrates. In such devices, the buffer of the HEMT structure is grown very thick in order to improve the crystal quality of the GaN present in the active area of the device [49]. In order to reduce substrate leakage and increase the resistivity of the buffer the buffer is heavily doped with deep acceptors like C and/or Fe. Trap levels of 0.9 eV and 2.85 eV above the Valence Band have been identified for C and Fe dopants, respectively [50-51]. These acceptor dopants successfully reduce substrate leakage and increase buffer resistance, however their energy levels are so deep in the bandgap they essentially act as traps with very long time constants [52]. Thus, any substrate leakage that does occur can potentially lead to trapping and DC-to-RF dispersion in the device, as discussed previously. Having an additional barrier to electron injection to the substrate which does not have any deep acceptor dopants present can help reduce this problem. An investigation into N-Polar transistors for power electronic device applications is outside the scope of this thesis, but this potential benefit bears mentioning.

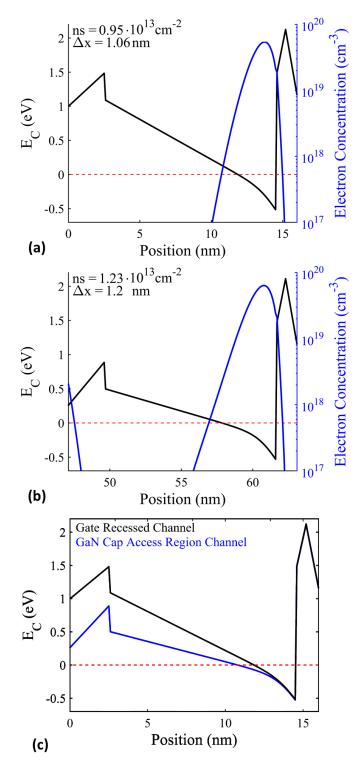

A Schrodinger-Poisson solver can be used to show that the presence of the AlGaN barrier which induces the 2DEG in either Ga or N-Polar displaces the centroid of the 2DEG away from that barrier by somewhere between 0.5 to 2 nm. By having the back-barrier induce the 2DEG charge, the centroid of the 2DEG is pushed towards the gate electrode, rather than away like in Ga-Polar (Fig. 1.13). This increases the effective aspect ratio of the N-Polar FET as well as the overall gate control of the channel charge.

It should be noted that it is possible to form a polarization induced barrier in Ga-Polar HEMTs. Although not an inherent/natural part of the Ga-Polar transistor structure, such barriers can also improve the gate control of the channel 2DEG, reduce substrate leakage, and

improve the output resistance of the transistor as well. However, certain problems can potentially arise from the use of such structures which are absent in the N-Polar implementation of a back-barrier.

In Ga-Polar, if one were to grow the entire buffer out of an  $Al_xGa_{1-x}N$ , grow a relatively thin (10-40 nm) GaN channel, and then grow a higher composition  $Al_{v}Ga_{1-v}N$  charge inducing barrier on top, such a back-barrier would be created [53]. In this case, it is not the  $\Delta E_{\rm C}$  of the  $Al_xGa_{1-x}N$  buffer which creates the barrier to channel electrons, but rather the net negative polarization charge at the backside GaN/Al<sub>x</sub>Ga<sub>1-x</sub>N pulls the GaN channel at the back up in energy and this GaN layer acts as the barrier. The problem with this implementation is that the entire buffer must be made of an  $Al_xGa_{1-x}N$  alloy, which will have a lower crystallographic quality than a binary GaN buffer would have. Further, the thermal conductivity of an Al<sub>x</sub>Ga<sub>1</sub>-<sub>x</sub>N alloy buffer is much worse than for a GaN buffer and a larger amount of self-heating would occur [54]. It is possible to only grow a layer of Al<sub>X</sub>Ga<sub>1-x</sub>N sandwiched between a GaN buffer and GaN channel for the same purpose. However, deep acceptor doping would have to be used at the bottom  $Al_xGa_{1-x}N/GaN$  interface, otherwise another 2DEG with a poor aspect ratio with respect to the gate electrode would form. Using deep acceptor doping this close to the channel could potentially cause trapping problems, as explained earlier. Additionally, an  $In_xGa_{1-x}N$  back-barrier could be used like that in [55]. However, using a lower bandgap material in a region of the device which is exposed to high electric fields could potentially lead to a reduction in breakdown voltage of the device.

#### Chapter 1.5.2 – Better Ohmic Contacts:

Having the charge inducing layer underneath the channel is beneficial for regrown contacts as well, as the n+ to 2DEG contact can be made through the lower bandgap GaN,

rather than through AlGaN like in many Ga-Polar devices. It is possible to etch away the AlGaN layer in Ga-Polar HEMTs, but this can actually lead to an increase in the contact resistance, as the top AlGaN layer is what induces the 2DEG in Ga-Polar HEMTs in the first place.

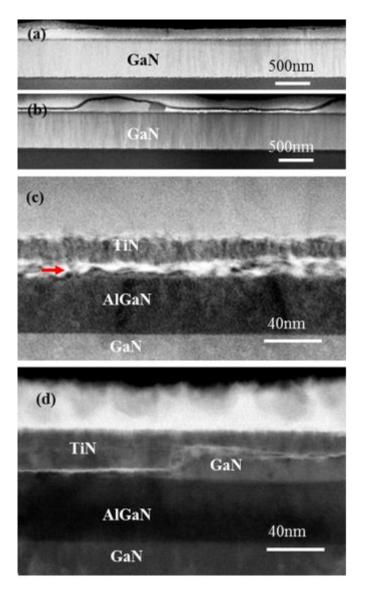

Additionally, the orientation of the polarization fields in N-Polar HEMTs enables the engineer to grade the GaN channel to InN in the contact region of the device. Because the bandgap of InN is much smaller and the polarization and quasi-electric fields are such that the CB is flat when grading from GaN to InN in the N-Polar orientation, this regrowth scheme can eliminate barriers to electron transport between the semiconductor and metallic contact (Fig. 1.14 (b)). Dasgupta *et al.* has demonstrated an extremely low contact resistance of ~ 0.025  $\Omega$ ·mm using such a regrowth design [57]. Such a scheme is not used in this dissertation, but very good contact resistances of around ~ 0.1  $\Omega$ ·mm are obtained with plasma-assisted-molecular-beam-epitaxial grown n+ GaN contacts (Fig. 1.14 (a)) [58].

**Fig. 1.14:** Simulated energy band diagram in the ohmic region of the N-Polar transistor for the case of (a) a regrown n+ GaN cap and (b) a graded GaN to InN which is n+ doped during the entirety of the grade [58]. A graded AlGaN back-barrier was used in this simulation. More details regarding this type of N-Polar back-barrier will be given in Chapter 2.

Chapter 1.5.3 – N-Polar AlGaN Top Barrier:

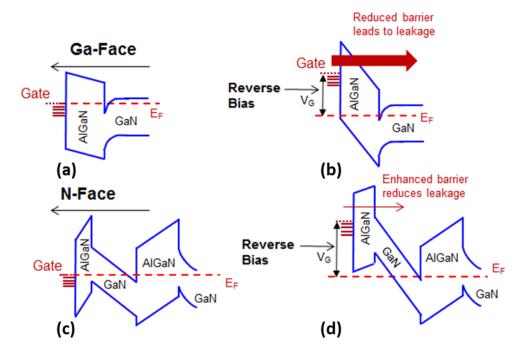

In N-Polar HEMTs, when an AlGaN layer is placed on top of the GaN channel, the polarization fields oppose the electric fields produced in a reverse biased gate drain junction (Fig. 1.15). This is in contrast to Ga-Polar HEMTs where the polarization fields are in the same direction and an applied gate-drain reverse bias rapidly reduces the tunneling barrier for gate injected electrons. However, it should be noted that the schottky barrier in N-Polar HEMTs appears to be smaller than that in Ga-Polar transistors [59-60]. Thus, in terms of leakage in HEMTs with schottky gates, N-Polar may not actually be superior to Ga-Polar.

**Fig. 1.15:** A schematic of a Ga-Polar HEMT band diagram at (a) equilibrium and (b) with a reverse gate-drain voltage applied. (c) and (d) give the energy band diagram of a N-Polar HEMT with a thin AlGaN top-barrier at equilibrium and at a reverse gate-drain voltage bias, respectively [58].

Chapter 1.5.4 – GaN Cap in Access Region of N-Polar Transistor:

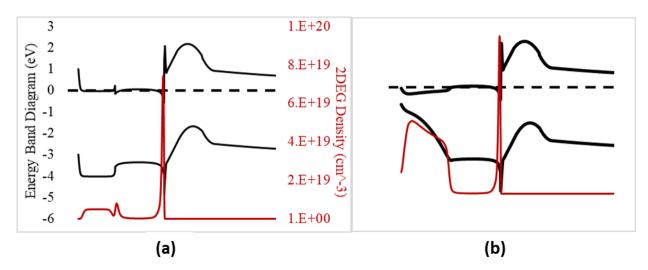

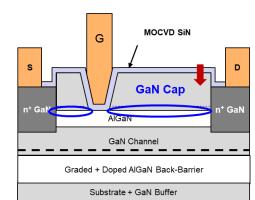

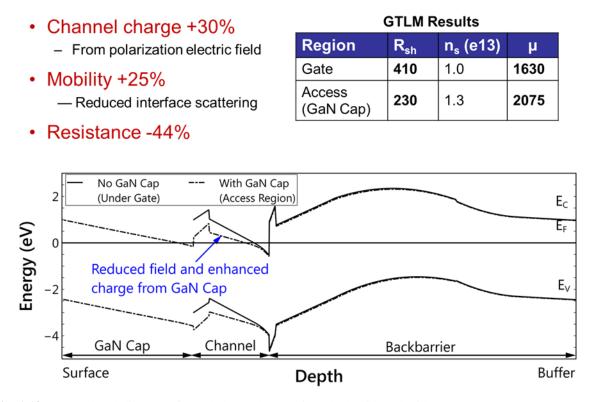

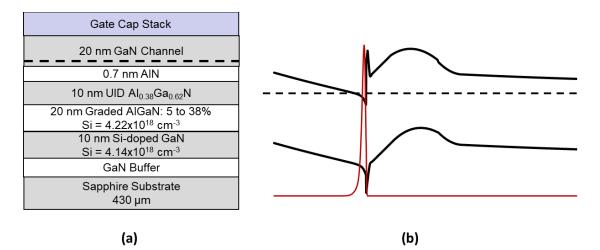

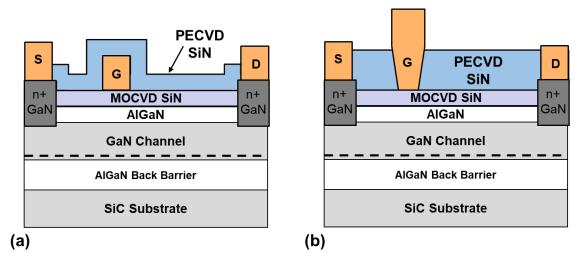

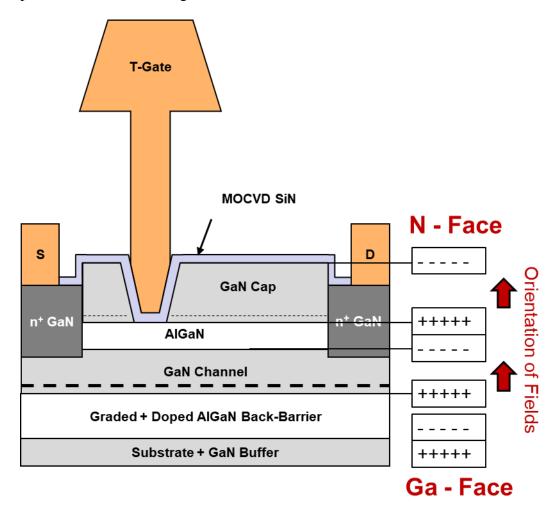

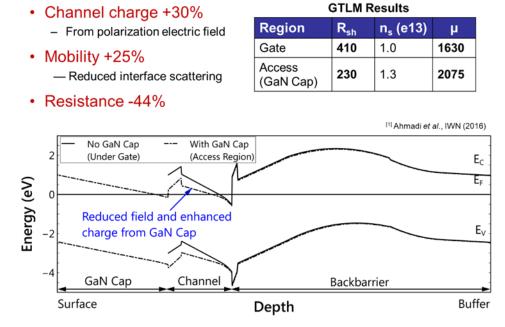

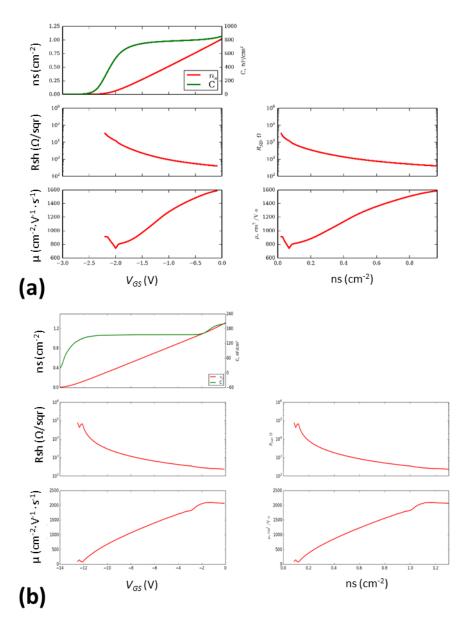

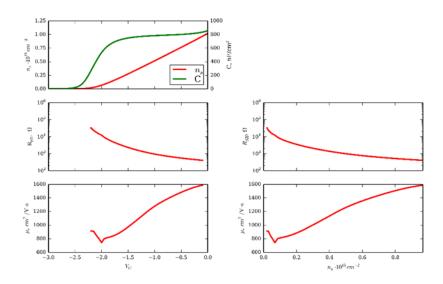

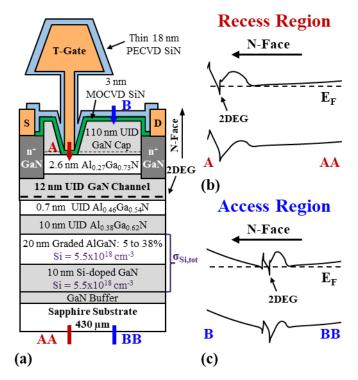

Finally, the direction of the polarization fields in N-Polar allows the device designer to add a UID GaN Cap in the access regions of the device for considerable performance improvements (Fig. 1.16). This GaN Cap serves 2 purposes. First, the GaN Cap greatly enhances access region conductivity and lowers the On-Resistance of the transistor. This is because the fields in N-Polar are such that the UID GaN cap pushes the conduction band (CB) down relative to the Fermi level ( $E_F$ ), resulting in an enhancement of the 2DEG charge in the access regions [43]. Further, the presence of the GaN cap relaxes the electric field seen by the channel 2DEG, pulling the centroid of the 2DEG away from the back GaN/AlGaN interface, reducing interfacial and alloy scattering [61]. This results in a large increase in 2DEG mobility. Together these benefits lowered the sheet resistance from 410  $\Omega$ /square in the recessed channel region to only 230  $\Omega$ /square in the GaN capped access regions for one of the devices reported on in later chapters of this dissertation (Fig. 1.17).

# GaN Cap

Enhanced Access Region Conductivity

- In-situ, epitixial

Passivation Laver

- Pristine Interface

Fig. 1.16: Cross-section of the N-Polar GaN Cap MISHEMT device structure.

Second, and this is really the key to this entire transistor design, it replaces traditional ex-situ SiN passivation with a robust, in-situ epitaxial layer for dispersion control that has a pristine interface with the underlying HEMT structure allowing for consistent and reliable

control of dispersion. This ability to control dispersion at high frequencies, while actually reducing some of the extrinsic resistances which can limit high frequency performance is really the key to our transistor's excellent W-Band power performance

**Fig. 1.18:** Energy band diagram of a scaled N-Polar transistor both with and without a GaN Cap. Can see that the conduction band is pulled down by the presence of the GaN Cap. Can also see that the magnitude of the total field in proximity of the channel 2DEG has been reduced (total field is the derivative of the conduction band profile) [62-63].

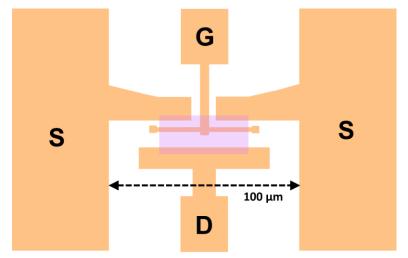

This dissertation focuses on the development of a N-Polar MISHEMT with a UID GaN Cap in the access regions of the device for W-Band power amplification purposes. Such a structure is named a N-Polar Deep Recess MISHEMT after earlier Gallium and initial N-Polar incarnations [64-67]. An overview of each chapter contained in this dissertation is given in the next section of this chapter.

### Chapter 1.6 – Synopsis of Thesis:

The goal of this dissertation is to make the best possible N-Polar MISHEMT device for large signal power performance at the W-Band range (75-110 GHz) portion of the electromagnetic spectrum. This goal has been achieved, as a N-Polar transistor with a peak RF output power density of more than 2x higher than any other device detailed in the literature at the time is reported in this thesis.

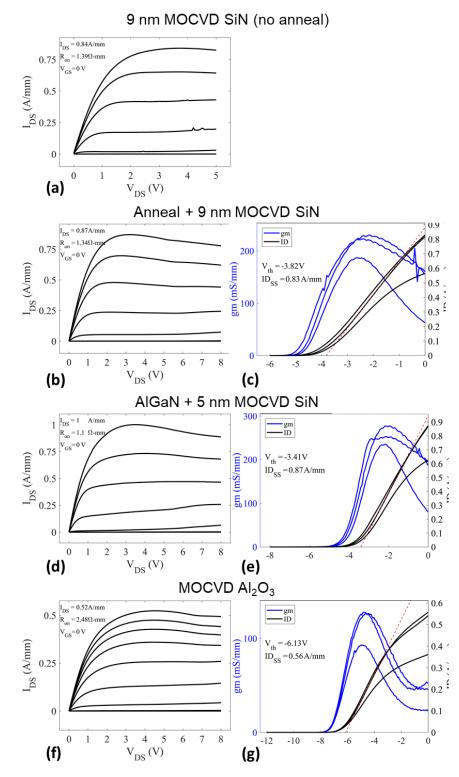

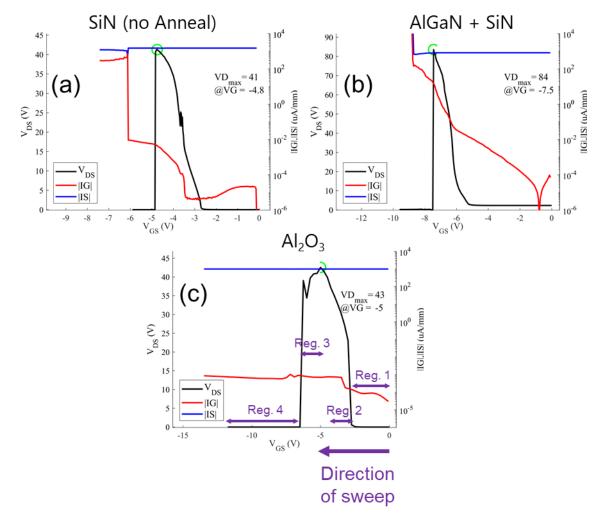

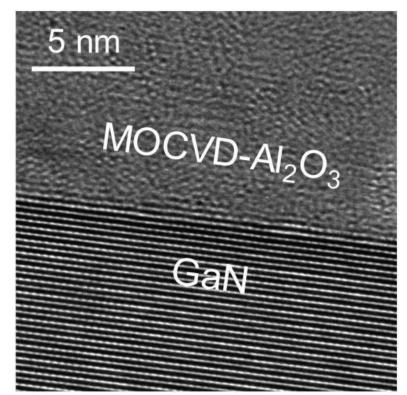

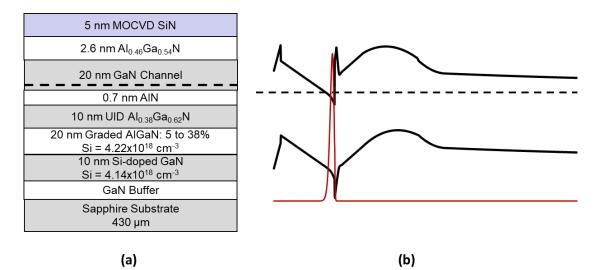

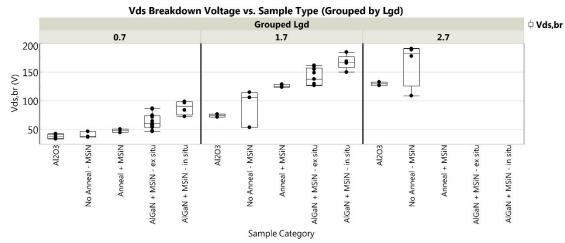

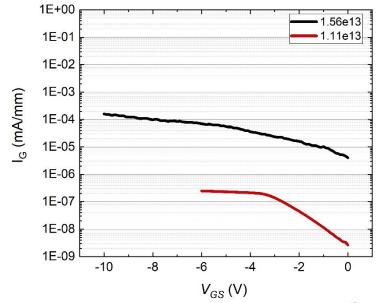

Chapter 2 begins with an experiment meant to find the best gate cap stack combination for use in high frequency N-Polar MISHEMT devices. Of the gate cap stack variations investigated, a clear winner is found that enables a significantly higher breakdown voltage than all other designs. A physics based explanation for why this gate cap stack performs the best is given. The next portion of the chapter goes over the relationship between channel 2DEG charge density and the overall device performance of the N-Polar MISHEMT, with a special focus on gate leakage and breakdown performance. Finally, an investigation into the ohmic contact design in N-Polar transistors is conducted.

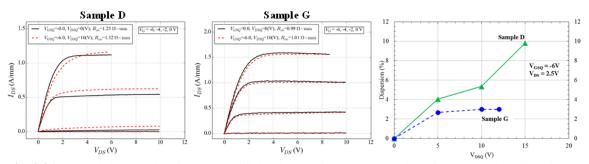

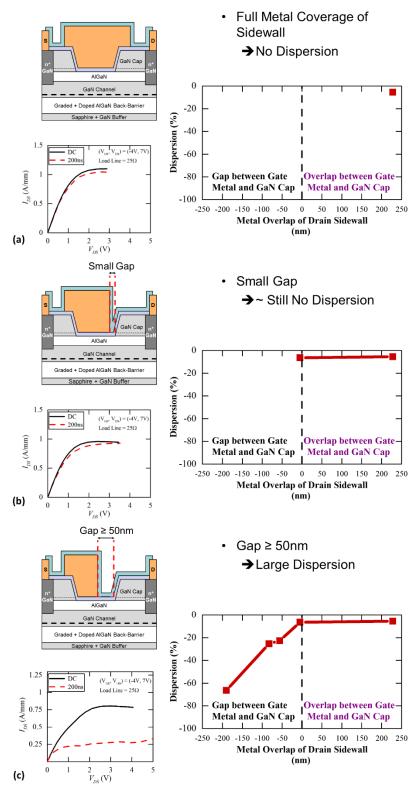

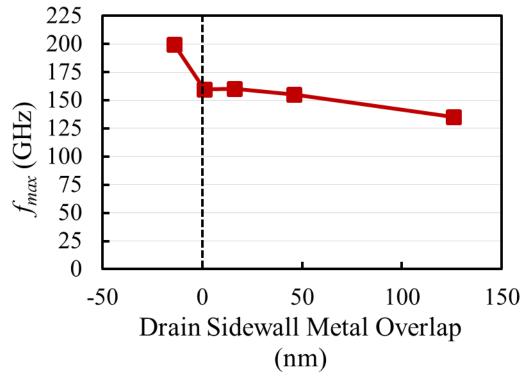

Chapter 3 gives a thorough overview of DC-to-RF dispersion and introduces the concept of the N-Polar Deep Recess design for controlling dispersion. A fabrication procedure for the N-Polar Deep Recess MISHEMT is developed and explained in detail. Initial investigations into the ability of the GaN Cap to reduce both the access region resistance and DC-to-RF dispersion are conducted. Finally, a study to determine the maximum allowable gap between the gate metal and GaN Cap sidewall while still maintaining low dispersion in relatively unstressful large signal measurements is performed.

Chapter 4 reports on the initial T-Gate results for NPDR MISHEMTs fabricated on sapphire substrates. The ability of the GaN Cap in the source-gate access region to ameliorate

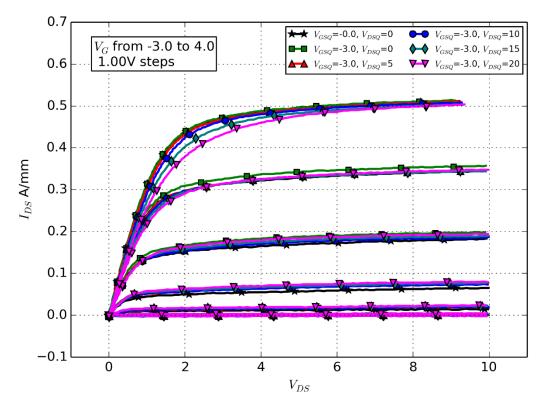

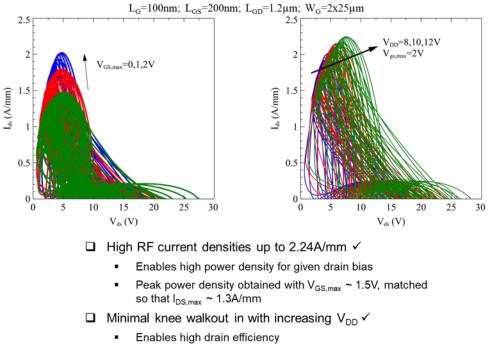

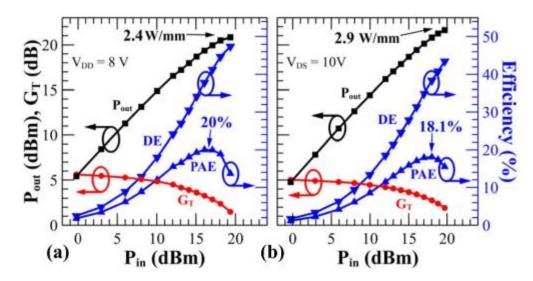

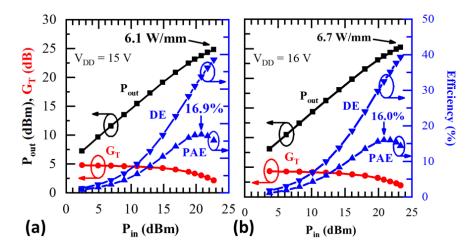

the source choke problem detailed by Palacios *et al.* [68] is detailed. Excellent large signal power performance of 4.5 W/mm with an associated *PAE* of 67% is demonstrated. An RF-IV measurement at 6 GHz shows the RF current density of the NPDR MISHEMT to be in excess of 2 A/mm at a  $V_{GS} = +2$  V, confirming the excellent control of dispersion afforded by the GaN Cap design. Finally, a (then) record  $P_{RF,out}$  of 2.9 W/mm at 94 GHz is achieved on an NPDR MISHEMT with a sapphire substrate.

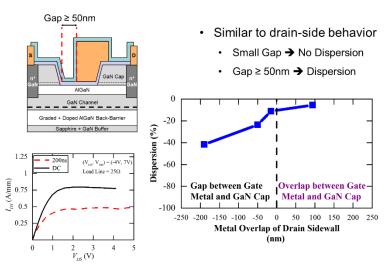

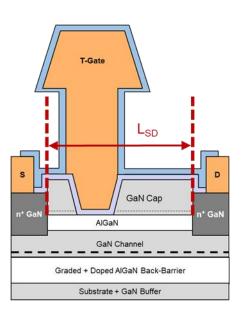

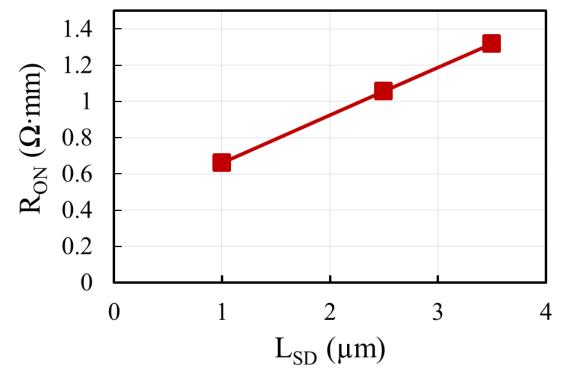

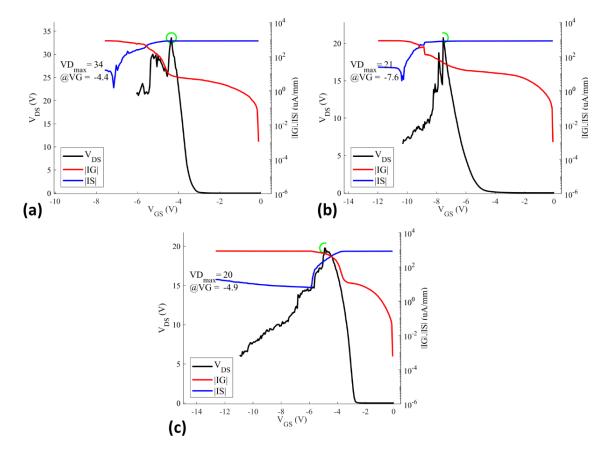

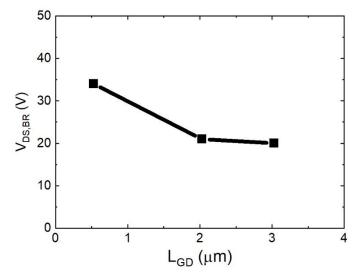

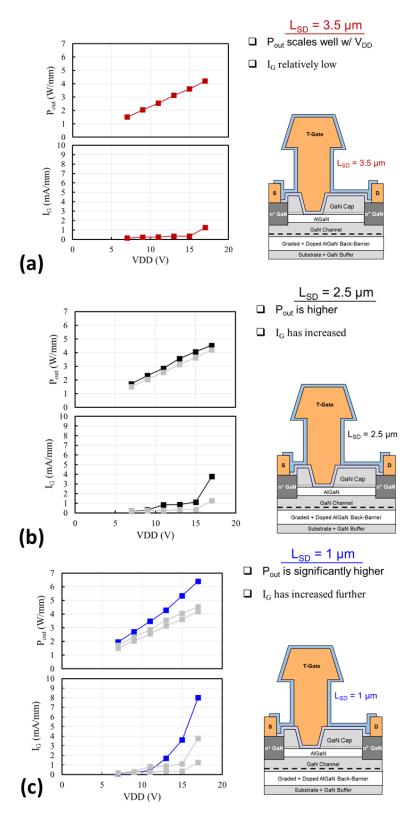

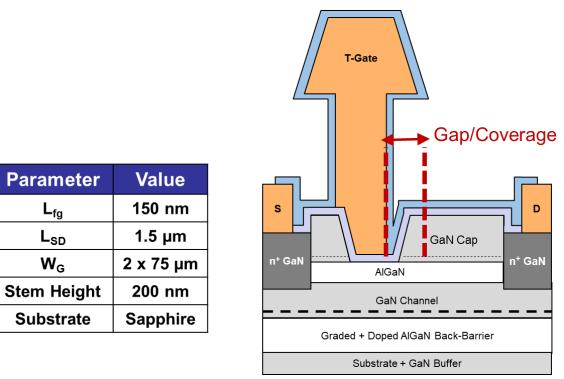

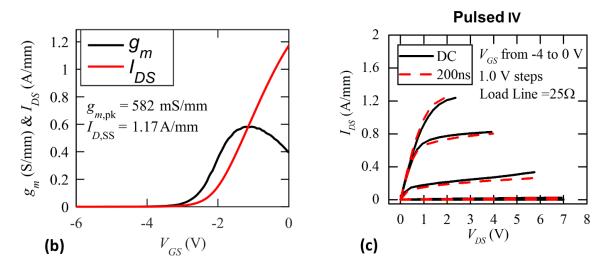

The lateral device dimensions of the NPDR MISHEMT are optimized in Chapter 5. Specifically, investigations into the optimal source-drain spacing, gate metal overlap of the source-side GaN Cap, and the gate metal overlap of the drain-side GaN Cap are explored.

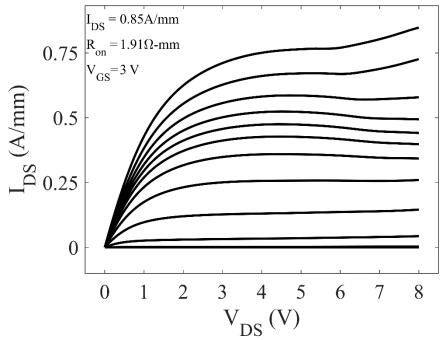

The optimized lateral device dimensions from Chapter 5 were then used to fabricate a N-Polar GaN Cap (NPDR) MISHEMT with record power performance at 94 GHz on a SiC substrate.

Finally, Chapter 7 summarizes the work contained in this thesis and presents ideas for future work/development of the NPDR MISHEMT design.

#### References

- [1] W. Johnson, J. Parson and M. Crew, "Nitrogen Compounds of Gallium. III", *The Journal of Physical Chemistry*, vol. 36, no. 10, pp. 2651-2654, 1931.

- [2] J.I. Pankove, E.A. Miller, and J.E. Berkeyheiser, "GaN electroluminescent diodes," in *IEEE International Electron Devices Meeting*, pp. 78–78, 1971

- [3] H. Amano, N. Sawaki, I. Akasaki and Y. Toyoda, "Metalorganic vapor phase epitaxial growth of a high quality GaN film using an AlN buffer layer", *Applied Physics Letters*, vol. 48, no. 5, pp. 353-355, 1986.S. Nakamura, "GaN growth using GaN buffer layer", *Japanese Journal of Applied Physics*, vol. 30, no. 10, p. 1705, 1991.

- [4] I. Akasaki, H. Amano, M. Kito and K. Hiramatsu, "Photoluminescence of Mg-doped p-type GaN and electroluminescence of GaN p-n junction LED", *Journal of Luminescence*, vol. 48-49, pp. 666-670, 1991.S. Nakamura, T. Jukai, M. Senoh, N. Iwasa, "Thermal annealing effects on p-type Mg-doped GaN films," *Japanese Journal of Applied Physics*, vol. 31, no. 2B, pp.L139

- [5] S. Nakamura, T. Mukai, M. Senoh and N. Iwasa, "Thermal Annealing Effects on P-Type Mg-Doped GaN Films", *Japanese Journal of Applied Physics*, vol. 31, no. 2, 2, pp. L139-L142, 1992.

- [6] S. Nakamura, N. Iwasa, M. Senoh and T. Mukai, "Hole Compensation Mechanism of P-Type GaN Films", *Japanese Journal of Applied Physics*, vol. 31, no. 1, 5, pp. 1258-1266, 1992.

- [7] S. Nakamura, M. Senoh and T. Mukai, "High-power InGaN/GaN double-heterostructure violet light emitting diodes", *Applied Physics Letters*, vol. 62, no. 19, pp. 2390-2392, 1993.

- [8] S. Nakamura, T. Mukai and M. Senoh, "Candela-class high-brightness InGaN/AlGaN doubleheterostructure blue-light-emitting diodes", *Applied Physics Letters*, vol. 64, no. 13, pp. 1687-1689, 1994.

- [9] S. Nakamura, M. Senoh, S. Nagahama, N. Iwasa, T. Yamada, T. Matsushita, H. Kiyoku, Y. Sugimoto, T. Kozaki, H. Umemoto, M. Sano and K. Chocho, "InGaN/GaN/AlGaN-based laser diodes with modulation-doped strained-layer superlattices grown on an epitaxially laterally overgrown GaN substrate", *Applied Physics Letters*, vol. 72, no. 2, pp. 211-213, 1998.

- [10] T. Fujii, Y. Gao, R. Sharma, E. Hu, S. DenBaars and S. Nakamura, "Increase in the extraction efficiency of GaN-based light-emitting diodes via surface roughening", *Applied Physics Letters*, vol. 84, no. 6, pp. 855-857, 2004.

- [11] Nitronex, "GaN applications." http://www.nitronex.com/gan\_applications.html.

- [12] L. Global Gallium Nitride (GaN) Semiconductor Device Market Size study, "Global Gallium Nitride (GaN) Semiconductor Device Market Size study, by Device Type (Opto, Power, RF), by Wafer Size, by Application (Power Drives, Supply and Inverter, RF, Lighting and Laser) – Tactical Business", *Thetacticalbusiness.com*, 2018. [Online]. Available: https://thetacticalbusiness.com/515409/global-gallium-nitride-gan-semiconductor-device-market-sizestudy-by-device-type-opto-power-rf-by-wafer-size-by-application-power-drives-supply-and-inverter-rflighting-and-laser/. [Accessed: 16- Nov- 2018].

- [13] T. Matsuoka, H. Okamoto, M. Nakao, H. Harima and E. Kurimoto, "Optical bandgap energy of wurtzite InN", *Applied Physics Letters*, vol. 81, no. 7, pp. 1246-1248, 2002.

- [14] W. Yim, E. Stofko, P. Zanzucchi, J. Pankove, M. Ettenberg and S. Gilbert, "Epitaxially grown AlN and its optical band gap", *Journal of Applied Physics*, vol. 44, no. 1, pp. 292-296, 1973.

- [15] G. Microwave, "Gallium Nitride Overview." http://www.gainmicrowave.com/public/gallium nitride overview.php

- [16] O. Ambacher, B. Foutz, J. Smart, J. Shealy, N. Weimann, K. Chu, M. Murphy, A. Sierakowski, W. Schaff, L. Eastman, R. Dimitrov, A. Mitchell and M. Stutzmann, "Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures", *Journal* of Applied Physics, vol. 87, no. 1, pp. 334-344, 2000.

- [17] U. Mishra, Shen Likun, T. Kazior and Yi-Feng Wu, "GaN-Based RF Power Devices and Amplifiers", *Proceedings of the IEEE*, vol. 96, no. 2, pp. 287-305, 2008.

- [18] R. Coffie, "Characterizing and Suppressing DC-to-RF Dispersion in AlGaN/GaN High Electron Mobility Transistors," Ph.D. dissertation, University of California, Santa Barbara, CA, 2003.

- [19] U. Mishra and J. Singh, *Semiconductor Device Physics and Design*. Springer Verlag, 2007.

- [20] R. Vetury, N. Zhang, S. Keller and U. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs", *IEEE Transactions on Electron Devices*, vol. 48, no. 3, pp. 560-566, 2001.

- [21] M. Khan, J. Kuznia, J. Van Hove, N. Pan and J. Carter, "Observation of a two-dimensional electron gas in low pressure metalorganic chemical vapor deposited GaN-AlxGa1-xN heterojunctions", *Applied Physics Letters*, vol. 60, no. 24, pp. 3027-3029, 1992.

- [22] M. Asif Khan, A. Bhattarai, J. Kuznia and D. Olson, "High electron mobility transistor based on a GaN-AlxGa1-xN heterojunction", *Applied Physics Letters*, vol. 63, no. 9, pp. 1214-1215, 1993.

- [23] M. Asif Khan, J. Kuznia, D. Olson, W. Schaff, J. Burm and M. Shur, "Microwave performance of a 0.25 μm gate AlGaN/GaN heterostructure field effect transistor", *Applied Physics Letters*, vol. 65, no. 9, pp. 1121-1123, 1994.

- [24] Y. Wu, B. Keller, S. Keller, D. Kapolnek, S. Denbaars and U. Mishra, "Measured microwave power performance of AlGaN/GaN MODFET", *IEEE Electron Device Letters*, vol. 17, no. 9, pp. 455-457, 1996.

- [25] S. Sheppard, K. Doverspike, W. Pribble, S. Allen, J. Palmour, L. Kehias and T. Jenkins, "High-power microwave GaN/AlGaN HEMTs on semi-insulating silicon carbide substrates", *IEEE Electron Device Letters*, vol. 20, no. 4, pp. 161-163, 1999.

- [26] G. Sullivan, J. Higgins, M. Chen, J. Yang, Q. Chen, R. Pierson and B. McDermott, "High power RF operation of AlGaN/GaN HEMTs grown on insulating silicon carbide substrates", *Electronics Letters*, vol. 34, no. 9, p. 922, 1998.

- [27] U. Mishra, Yi-Feng Wu, B. Keller, S. Keller and S. Denbaars, "GaN microwave electronics", *IEEE Transactions on Microwave Theory and Techniques*, vol. 46, no. 6, pp. 756-761, 1998.

- [28] Y. Wu, S. Keller, P. Kozodoy, B. Keller, P. Parikh, D. Kapolnek, S. Denbaars and U. Mishra, "Bias dependent microwave performance of AlGaN/GaN MODFET's up to 100 V", *IEEE Electron Device Letters*, vol. 18, no. 6, pp. 290-292, 1997.

- [29] L. Shen, S. Heikman, B. Moran, R. Coffie, N.Q. Zhang, D. Buttari, I.P. Smorchkova, S. Keller, U. K. Mishra, "AlGaN/AlN/GaN high-power microwave HEMT," in *IEEE Electron Device Letters*, vol. 22, no. 10, pp. 457-459, Oct. 2001. doi: 10.1109/55.954910

- [30] L. Eastman, V. Tilak, J. Smart, B. Green, E. Chumbes, R. Dimitrov, Hyungtak Kim, O. Ambacher, N. Weimann, T. Prunty, M. Murphy, W. Schaff and J. Shealy, "Undoped AlGaN/GaN HEMTs for microwave power amplification", *IEEE Transactions on Electron Devices*, vol. 48, no. 3, pp. 479-485, 2001.

- [31] Y. Ando, Y. Okamoto, H. Miyamoto, T. Nakayama, T. Inoue and M. Kuzuhara, "10-W/mm AlGaN-GaN HFET with a field modulating plate", *IEEE Electron Device Letters*, vol. 24, no. 5, pp. 289-291, 2003.

- [32] A. Chini, D. Buttari, R. Coffie, S. Heikman, S. Keller and U. Mishra, "12 W/mm power density AlGaN/GaN HEMTs on sapphire substrate", *Electronics Letters*, vol. 40, no. 1, p. 73, 2004.

- [33] Y. Wu, A. Saxler, M. Moore, R. Smith, S. Sheppard, P. Chavarkar, T. Wisleder, U. Mishra and P. Parikh, "30-W/mm GaN HEMTs by Field Plate Optimization", *IEEE Electron Device Letters*, vol. 25, no. 3, pp. 117-119, 2004.

- [34] Y.F. Wu, M. Moore, A. Saxler, T. Wisleder, and P. Parikh, "40-W/mm double field-plated GaN HEMTs," in Proc. 64<sup>th</sup> Device Res. Conf, (DRC), 2006, pp. 151-152.

- [35] Chini, A., Buttari, D., Coffie, R., Shen, L., Heikman, S., Chakraborty, A., Keller, S. and Mishra, U.K., 2004. Power and linearity characteristics of field-plated recessed-gate AlGaN-GaN HEMTs. *IEEE Electron Device Letters*, 25(5), pp.229-231.

- [36] Yi-Feng Wu, D. Kapolnek, J. Ibbetson, P. Parikh, B. Keller and U. Mishra, "Very-high power density AlGaN/GaN HEMTs", *IEEE Transactions on Electron Devices*, vol. 48, no. 3, pp. 586-590, 2001.

- [37] Bisi, D., Meneghini, M., de Santi, C., Chini, A., Dammann, M., Brückner, P., Mikulla, M., Meneghesso, G. and Zanoni, E., 2013. "Deep-level characterization in GaN HEMTs-Part I: Advantages and limitations of drain current transient measurements," *IEEE Transactions on electron devices*, vol. 60, no. 10, pp. 3166-3175.

- [38] B. Green, K. Chu, E. Chumbes, J. Smart, J. Shealy and L. Eastman, "The effect of surface passivation on the microwave characteristics of undoped AlGaN/GaN HEMTs", *IEEE Electron Device Letters*, vol. 21, no. 6, pp. 268-270, 2000.

- [39] U.K. Mishra, "Current Status and Future Directions in GaN-Based Electronics," in *International Workshop* on Nitride Semiconductors (IWN), Orlando, FL, USA, Oct. 2016.

- [40] K. Shinohara, D. Regan, Y. Tang, A. Corrion, D. Brown, J. Wong, J. Robinson, H. Fung, A. Schmitz, T. Oh, S. Kim, P. Chen, R. Nagele, A. Margomenos and M. Micovic, "Scaling of GaN HEMTs and Schottky"

Diodes for Submillimeter-Wave MMIC Applications", *IEEE Transactions on Electron Devices*, vol. 60, no. 10, pp. 2982-2996, 2013.

- [41] S. Wienecke, B. Romanczyk, M. Guidry, H. Li, X. Zheng, E. Ahmadi, K. Hestroffer, L. Megalini, S. Keller, and U. K. Mishra, "N-Polar Deep Recess MISHEMTs with Record 2.9 W/mm at 94 GHz," *IEEE Electron Device Let.*, vol. 37, no. 6, pp. 713–716, June 2016, DOI: <u>10.1109/LED.2016.2556717</u>

- [42] S. Wienecke, B. Romanczyk, M. Guidry, H. Li, X. Zheng, E. Ahmadi, K. HEstroffer, S. Keller, and U. K. Mishra, "N-Polar GaN Cap MISHEMT with Record Power Density Exceeding 6.5 W/mm at 94 GHz," *IEEE Electron Device Let.*, vol. 38, no. 3, pp. 359–361. March 2017, DOI: 10.1109/LED.2017.2653192

- [43] <u>https://minerva.mlib.cnr.it/mod/book/view.php?id=269&chapterid=106</u>

- [44] O. Ambacher, B. Foutz, J. Smart, J. Shealy, N. Weimann, K. Chu, M. Murphy, A. Sierakowski, W. Schaff, L. Eastman, R. Dimitrov, A. Mitchell and M. Stutzmann, "Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures", *Journal* of Applied Physics, vol. 87, no. 1, pp. 334-344, 2000.

- [45] M. Murphy, K. Chu, H. Wu, W. Yeo, W. Schaff, O. Ambacher, J. Smart, J. Shealy, L. Eastman and T. Eustis, "Molecular beam epitaxial growth of normal and inverted two-dimensional electron gases in AlGaN/GaN based heterostructures", *Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures*, vol. 17, no. 3, p. 1252, 1999.

- [46] Nidhi, "Optimization of the High Frequency Performance of N-polar Nitride-Based Transistors," Ph.D. dissertation, University of California, Santa Barbara, CA, 2011.

- [47] M. Uren, S. Karboyan, I. Chatterjee, A. Pooth, P. Moens, A. Banerjee and M. Kuball, ""Leaky Dielectric" Model for the Suppression of Dynamic R<sub>ON</sub> in Carbon-Doped AlGaN/GaN HEMTs", *IEEE Transactions* on Electron Devices, vol. 64, no. 7, pp. 2826-2834, 2017.

- [48] A. Chini, G. Meneghesso, M. Meneghini, F. Fantini, G. Verzellesi, A. Patti, and F. Iucolano, "Experimental and Numerical Analysis of Hole Emission Process From Carbon-Related Traps in GaN Buffer Layers," in *IEEE Transactions on Electron Devices*, vol. 63, no. 9, pp. 3473-3478, Sept. 2016. doi: 10.1109/TED.2016.2593791

- [49] A. Polyakov, N. Smirnov, A. Govorkov, T. Yugova, A. Markov, A. Dabiran, A. Wowchak, B. Cui, J. Xie, A. Osinsky, P. Chow and S. Pearton, "Electrical properties of GaN (Fe) buffers for AlGaN/GaN high electron mobility transistor structures", *Applied Physics Letters*, vol. 92, no. 4, p. 042110, 2008.

- [50] M. Meneghini, P. Vanmeerbeek, R. Silvestri, S. Dalanale, A. Banaerjee, D. Bisi, E. Zanoni, and G. Menegheso+, "Temperature-dependent dynamic R<sub>ON</sub> in GaN-based MIS-HEMTs: Role of surface traps and buffer leakage," IEEE Trans. Electron Devices, vol. 62, no. 3, pp. 782–787, Mar. 2015, doi: 10.1109/TED.2014.2386391

- [51] R. Chu, "Gate-Recessed GaN High Electron Mobility Transistors with Scaled Gate Length," Ph.D. dissertation, University of California, Santa Barbara, CA, 2008.

- [52] W. Liu and A. Balandin, "Thermal conduction in AlxGa1-xN alloys and thin films", *Journal of Applied Physics*, vol. 97, no. 7, p. 073710, 2005.

- [53] T. Palacios, A. Chakraborty, S. Heikman, S. Keller, S. P. DenBaars and U. K. Mishra, "AlGaN/GaN high electron mobility transistors with InGaN back-barriers," in *IEEE Electron Device Letters*, vol. 27, no. 1, pp. 13-15, Jan. 2006. doi: 10.1109/LED.2005.860882

- [54] M. Grundmann, BANDENG. [Online]. Available: http://my.ece.ucsb.edu/mgrundmann/bandeng.htm.

- [55] S. Dasgupta, Nidhi, D. Brown, F. Wu, S. Keller, J. Speck and U. Mishra, "Ultralow nonalloyed Ohmic contact resistance to self aligned N-polar GaN high electron mobility transistors by In(Ga)N regrowth", *Applied Physics Letters*, vol. 96, no. 14, p. 143504, 2010.

- [56] D. Denninghoff, "Highly Scaled N-polar GaN MIS-HEMTs," Ph.D. dissertation, University of California, Santa Barbara, CA, 2008.

- [57] S. Rajan, "Advanced Polarization Engineering for GaN-based Transistors, Ph.D. dissertation, University of California, Santa Barbara, CA, 2006.

- [58] S. Rajan, A. Chini, M. Wong, J. Speck and U. Mishra, "N-polar GaN/AlGaN/GaN high electron mobility transistors", *Journal of Applied Physics*, vol. 102, no. 4, p. 044501, 2007.

- [59] E. Ahmadi, S. Keller and U. Mishra, "Model to explain the behavior of 2DEG mobility with respect to charge density in N-polar and Ga-polar AlGaN-GaN heterostructures", *Journal of Applied Physics*, vol. 120, no. 11, p. 115302, 2016.

- [60] S. Wienecke, B. Romanczyk, M. Guidry, H. Li, E. Ahmadi, K. Hestroffer, X. Zheng, S. Keller, and U. K. Mishra, "N-polar GaN Cap MISHEMT with record 6.7 W/mm at 94 GHz," 2016 74th Annual Device

*Research Conference (DRC)*, Newark, DE, 2016, pp. 1-2. doi: 10.1109/DRC.2016.7548406

[61] B. Romanczyk, S. Wienecke, M. Guidry, H. Li, E. Ahmadi, X. Zheng, S. Keller, U. K. Mishra, "Demonstration of Constant 8 W/mm Power Density at 10, 30, and 94 GHz in State-of-the-Art Millimeter-Wave N-Polar GaN MISHEMTs," in *IEEE Transactions on Electron Devices*, vol. 65, no. 1, pp. 45-50, Jan.

doi: 10.1109/TED.2017.2770087

- [62] L. Shen, et al., "Unpassivated GaN/AlGaN/GaN Power High Electron Mobility Transistors with Dispersion Controlled by Epitaxial Layer Design," J. Electron. Mater., vol. 33, no. 5, pp. 422–425, May 2004.