#### An Integrated Multilevel Converter with Sigma Delta Control for LED Lighting

by

Daniel L. Gerber

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Seth R. Sanders, Chair Elad Alon Duncan S. Callaway

Spring 2017

# An Integrated Multilevel Converter with Sigma Delta Control for LED Lighting

Copyright 2017 by Daniel L. Gerber

#### Abstract

#### An Integrated Multilevel Converter with Sigma Delta Control for LED Lighting

by

Daniel L. Gerber

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Seth R. Sanders, Chair

High brightness LEDs have become a mainstream lighting technology due to their efficiency, life span, and environmental benefits. As such, the lighting industry values LED drivers with low cost, small form factor, and long life span. Additional specifications that define a high quality LED driver are high efficiency, high power factor, wide-range dimming, minimal flicker, and a galvanically isolated output. The flyback LED driver is a popular topology that satisfies all these specifications, but it requires a bulky and costly flyback transformer. In addition, its passive methods for cancelling AC power ripple require electrolytic capacitors, which have been known to have life span issues. This dissertation details the design, construction, and verification of a novel LED driver that satisfies all the specifications. In addition, it does not require a flyback transformer or electrolytic capacitors, thus marking an improvement over the flyback driver on size, cost, and life span.

This dissertation presents an integrated circuit (IC) LED driver, which features a pair of generalized multilevel converters that are controlled via sigma-delta modulation. The first is a multilevel rectifier responsible for power factor correction (PFC) and dimming. The PFC rectifier employs a second order sigma-delta loop to precisely control the input current harmonics and amplitude. The second is a bidirectional multilevel inverter used to cancel AC power ripple from the DC bus. This ripple-cancellation module transfers energy to and from a storage capacitor. It uses a first order sigma-delta loop with a preprogrammed waveform to swing the storage capacitor voltage. The system also contains an output stage that powers the LEDs with DC and provides for galvanic isolation. The output stage consists of an H-bridge stack that connects to the output through a small toroid transformer.

The IC LED driver was simulated and prototyped on an ABCD silicon test chip. Testing and verification indicates functional performance for all the modules in the LED driver. The driver exhibits moderate efficiency at half voltage. Although the part was only testable to half voltage, loss models predict that its efficiency would be much higher at full voltage. The driver also meets specifications on the line current harmonics and ripple cancellation.

This dissertation introduces multilevel circuit techniques to the IC and LED research

space. The prototype's functional performance indicates that integrated multilevel converters are a viable topology for lighting and other similar applications. Dedication

Dedicated to my family and friends, who have been unwavering in their love and support.

# Contents

| Co       | onten | nts                                                                                                          | ii |

|----------|-------|--------------------------------------------------------------------------------------------------------------|----|

| Li       | st of | Figures                                                                                                      | iv |

| Lis      | st of | Tables                                                                                                       | ix |

| 1        | Intr  | oduction to LED Drivers                                                                                      | 1  |

|          | 1.1   | The Lighting Industry                                                                                        | 1  |

|          | 1.2   | The LED Driver                                                                                               | 4  |

|          | 1.3   | LED Driver Topologies                                                                                        | 7  |

|          |       | 1.3.1 Linear LED Drivers                                                                                     | 7  |

|          |       | 1.3.2 Switched-Mode LED Drivers                                                                              | 8  |

|          |       | 1.3.3 Flyback LED Drivers                                                                                    | 8  |

|          |       | 1.3.4 Resonant and Soft Switching LED Drivers                                                                | 11 |

|          |       | 1.3.5 Switched Capacitor LED Drivers                                                                         | 12 |

|          | 1.4   | Power Ripple and Flicker                                                                                     | 12 |

|          | 1.5   | Outline of Dissertation                                                                                      | 17 |

| <b>2</b> | Mul   | tilevel Converters and Sigma Delta Control                                                                   | 18 |

|          | 2.1   | Project Specifications                                                                                       | 18 |

|          | 2.2   | Multilevel Converters                                                                                        | 19 |

|          |       | 2.2.1 Diode Clamped Multilevel Inverter                                                                      | 20 |

|          |       | 2.2.2 Capacitor Clamped Multilevel Inverter                                                                  | 21 |

|          |       | 2.2.3 Multilevel Topology for an Integrated LED Driver                                                       | 22 |

|          |       | 2.2.4 Control Scheme for a Multilevel Converter                                                              | 23 |

|          | 2.3   | Sigma-Delta Modulation                                                                                       | 23 |

|          |       | 2.3.1 Quantization $\ldots$ | 23 |

|          |       | 2.3.2 Noise Shaping with a Sigma-Delta Loop                                                                  | 24 |

|          |       | 2.3.3 Higher Order Sigma-Delta Loop                                                                          | 26 |

|          | 2.4   | Research Contribution                                                                                        | 27 |

# 3 LED Driver Design Architecture

$\mathbf{28}$

| <br>Мос |                                       |

|---------|---------------------------------------|

|         | Julo 20                               |

|         |                                       |

|         |                                       |

|         |                                       |

|         |                                       |

|         | 37                                    |

|         | 39                                    |

|         | 42                                    |

|         | 42                                    |

|         |                                       |

|         |                                       |

|         |                                       |

|         |                                       |

|         |                                       |

|         |                                       |

|         |                                       |

|         |                                       |

|         | 56                                    |

|         | . 56                                  |

|         | 57                                    |

|         | 58                                    |

|         | 60                                    |

|         | 62                                    |

|         |                                       |

|         |                                       |

|         |                                       |

|         |                                       |

|         |                                       |

|         |                                       |

|         | 69                                    |

|         |                                       |

|         |                                       |

|         |                                       |

| •       | • • • •                               |

|         | · · · · · · · · · · · · · · · · · · · |

# List of Figures

| tribution of installed lighting types over the next decade. By 2030, LEDs are<br>expected to mostly replace all other forms of lighting. (b) Lighting energy con-<br>sumption over the next decade. Due to the switch to LEDs, lighting energy<br>consumption is expected to decrease by 40%<br>Teardown of an EcoSmart PAR30 LED flood light. The driver plug sits inside<br>the base of the housing and connects the glass filled screw socket to the LEDs. | 3                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sumption over the next decade. Due to the switch to LEDs, lighting energy consumption is expected to decrease by 40%                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| consumption is expected to decrease by 40%                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Teardown of an EcoSmart PAR30 LED flood light. The driver plug sits inside<br>the base of the housing and connects the glass filled screw socket to the LEDs.                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| the base of the housing and connects the glass filled screw socket to the LEDs.                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ő ő                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Sample plots of current vs voltage for the incandescent bulb and the LED (not                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| to scale). The incandescent bulb has a linear or resistive relationship, and either                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| voltage or current control may be employed to regulate the power. The LED                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| has an exponential relationship. A small deviation in voltage could determine                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| whether the LED is on or off. As such, current control is desirable to regulate                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LED power.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The linear LED driver                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                                                                                                                                   |

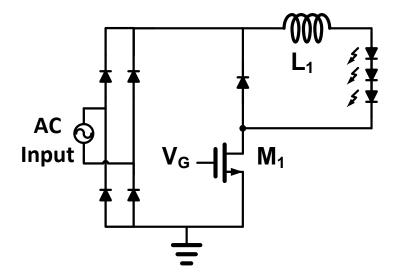

| The buck-based LED driver                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                                                                                                                                                                                                                                                                                                                                                                                                   |

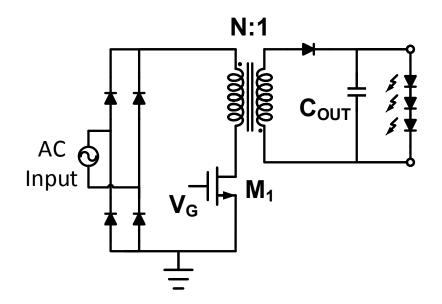

| The flyback LED driver.                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                                                                                                                                                                                                                                                                                                                                                                                                                   |

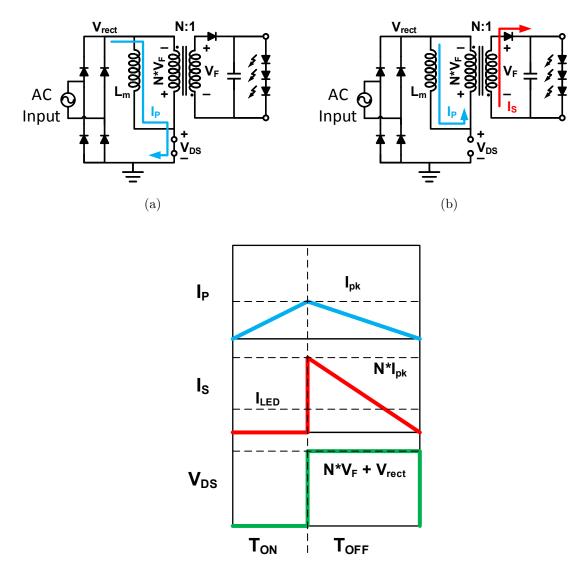

| Analysis of a flyback LED driver operating in critical conduction mode, as de-                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| picted in [28]. (a) Equivalent circuit with switch ON. (b) Equivalent circuit with                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| switch OFF. (c) Current and voltage transients in the flyback converter.                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                  |

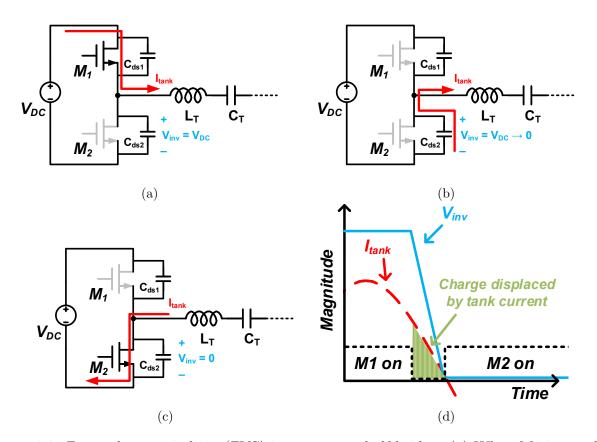

| Zero voltage switching (ZVS) in a resonant half bridge. (a) When M1 is on, the                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| inverter node $V_{inv}$ is pulled high and the parasitic drain-source capacitance $C_{ds2}$                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| is charged to $V_{DC}$ . (b) During the dead time, the tank current $I_{tank}$ discharges                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $C_{ds2}$ . (c) M2 turns on when $V_{inv}$ reaches zero. This way, there is zero voltage                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| across M2 when it turns on. (d) Waveforms demonstrating ZVS                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                                                                                                                                                                                                                                                                                                                                                                                  |

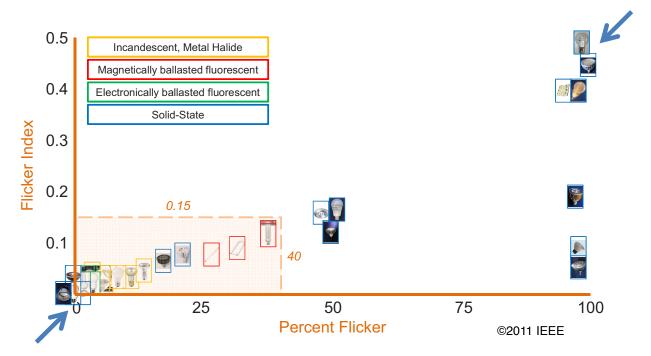

| Flicker chart from [41] that displays percent flicker and flicker index for different                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| types of lamps. LED lamps may fall on either side of the spectrum, depending                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| on their quality and whether or not they contain ripple cancellation measures.                                                                                                                                                                                                                                                                                                                                                                                | 13                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Sample plots of current vs voltage for the incandescent bulb and the LED (not to scale). The incandescent bulb has a linear or resistive relationship, and either voltage or current control may be employed to regulate the power. The LED has an exponential relationship. A small deviation in voltage could determine whether the LED is on or off. As such, current control is desirable to regulate LED power |

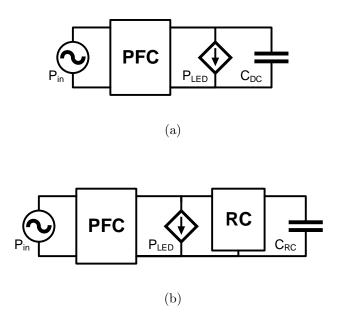

| 1.10 | Methods for reduction or cancellation of 120 Hz power ripple from the driver's power-factor correction (PFC) input module. It is desirable for the driver's output to the LEDs, $P_{LED}$ , to be constant. (a) Passive ripple cancellation involves the use of a large DC capacitor $C_{DC}$ to filter the ripple. (b) An active ripple cancellation strategy that involves the use of a separate power converter for ripple cancellation. The ripple-cancellation (RC) module includes a storage capacitor $C_{RC}$ that can be much smaller than $C_{DC}$ . | 14       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

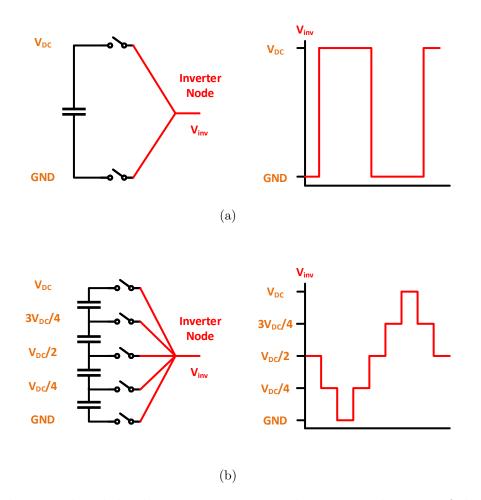

| 2.1  | Theoretical multilevel converters. $V_{inv}$ can be connected to any of the levels of the DC capacitor bus, producing the output waveforms on the right. (a) Two-level inverter, or half-bridge. (b) Five-level inverter.                                                                                                                                                                                                                                                                                                                                      | 19       |

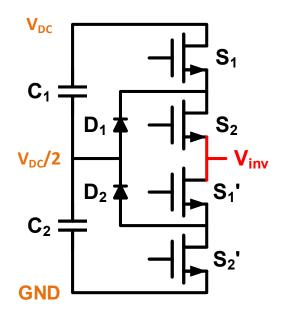

| 2.2  | Diode clamped three-level inverter. Any switch $S_x$ switches complementary to $S'_x$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20       |

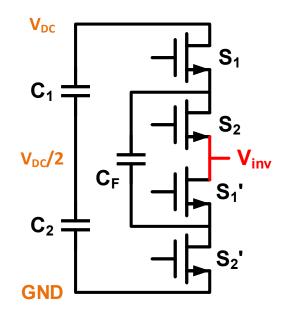

| 2.3  | Capacitor clamped three-level inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22       |

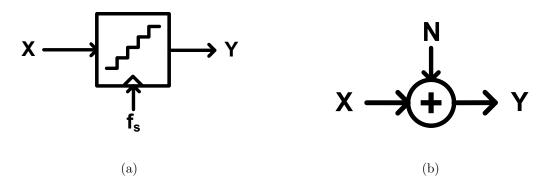

| 2.4  | (a) A quantizer block with a sampling rate $f_s$ and quantization noise. (b) Equivalent small signal model with a noise input $N$ .                                                                                                                                                                                                                                                                                                                                                                                                                            | 24       |

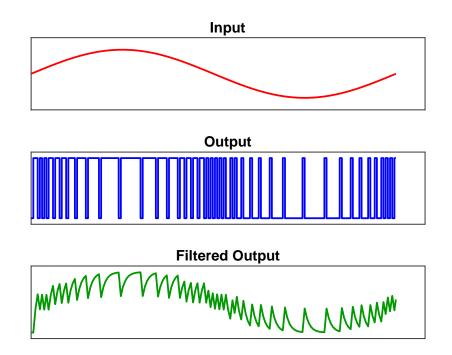

| 2.5  | Sample output waveforms of a sigma-delta modulator. The filtered output uses a low pass filter with cutoff frequency at $f_s/2$ .                                                                                                                                                                                                                                                                                                                                                                                                                              | 25       |

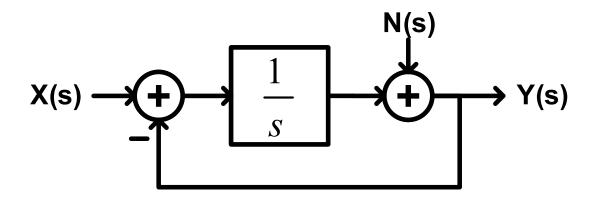

| 2.6  | Small signal block diagram of a sigma-delta modulator. The input is $X(s)$ , the output is $Y(s)$ , and the quantization noise input is $N(s)$ . The transfer functions in Equations 2.3 and 2.4 can be derived from this block diagram. The filtered                                                                                                                                                                                                                                                                                                          | 20       |

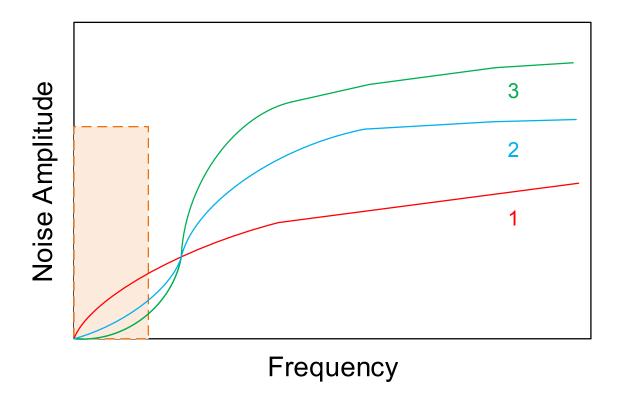

| 2.7  | output in Figure 2.5 can be obtained by passing $Y(s)$ through a low pass filter. Noise transfer function for a 1st, 2nd, and 3rd order sigma-delta modulator. An output low pass filter could be designed to cut out the high frequency noise, as indicated by the orange rectangle. Higher order sigma-delta modulators have lower quantization noise in the signal band, but higher quantization noise at higher frequencies.                                                                                                                               | 25<br>26 |

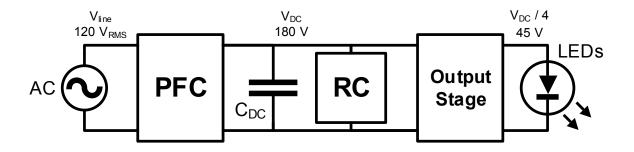

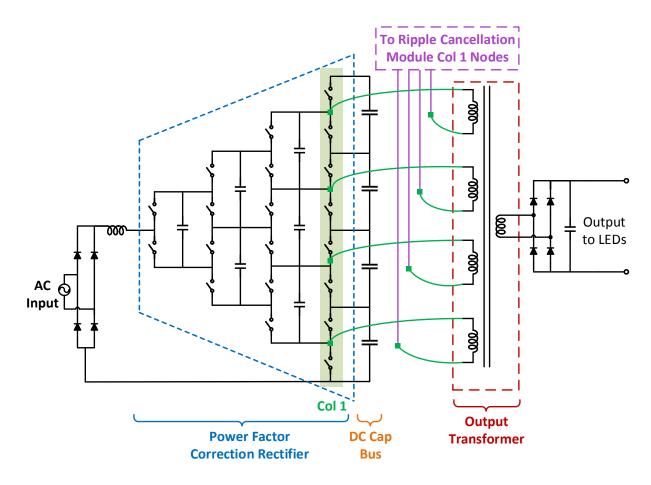

| 3.1  | Block diagram of the LED driver with power-factor correction (PFC), ripple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20       |

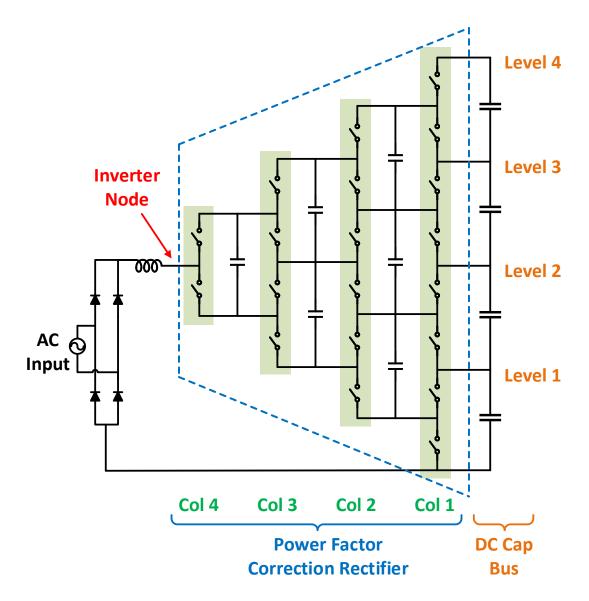

| 3.2  | cancellation (RC), and output stage. $C_{DC}$ indicates the DC capacitor bus Generalized multilevel schematic for the PFC rectifier with switching columns highlighted in green. The DC capacitor bus helps define the DC levels, buffers power flow, and connects to the output stage (not shown here). It is shared with                                                                                                                                                                                                                                     | 28       |

|      | the circuits in Figures 3.3 and 3.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30       |

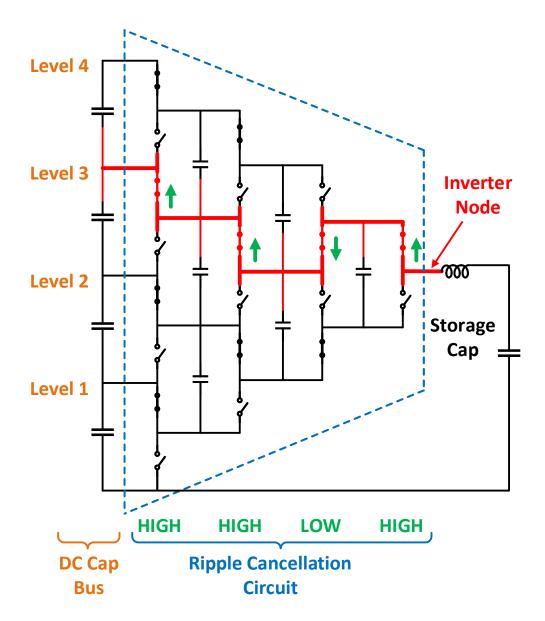

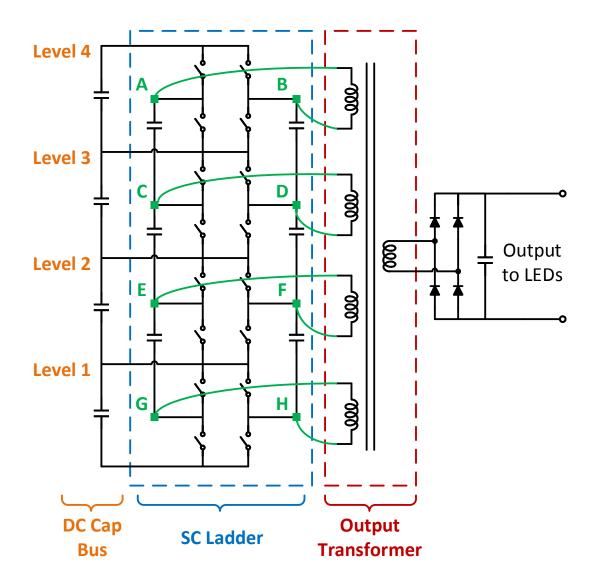

| 3.3  | Generalized multilevel schematic for the ripple-cancellation module with an ex-<br>ample switch configuration for connecting the inverter node to level 3. The DC                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 3.4  | capacitor bus helps define the DC levels, buffers power flow, and connects to the output stage (not shown here). It is shared with the circuits in Figures 3.2 and 3.4. The output stage is comprised of an integrated H-bridge stack and an output                                                                                                                                                                                                                                                                                                            | 31       |

| 0.4  | transformer. The H-bridge stack is clocked at 50 kHz. The DC capacitor bus is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|      | shared with the circuits in Figures 3.2 and 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32       |

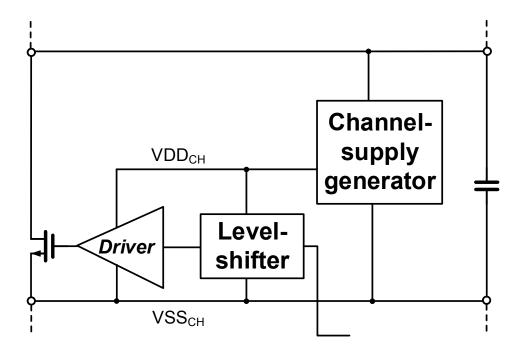

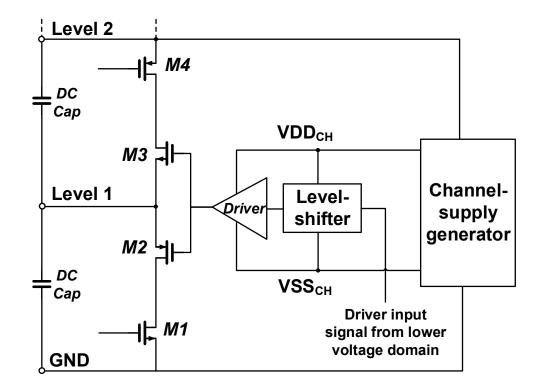

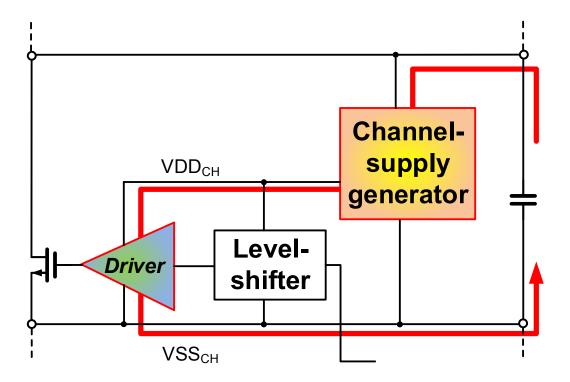

| 3.5         | The full switching channel for the power LDMOS switch. Each switching channel consists of a high-side channel supply, a level shifter, and a driver (buffer). The                                                                                                                                                                                                                                                                                                                                      |                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|             | channel supply is powered from a DC or flying capacitor and generates the $VDD_{CH}$ voltage at five volts above $VSS_{CH}$ .                                                                                                                                                                                                                                                                                                                                                                          | 33             |

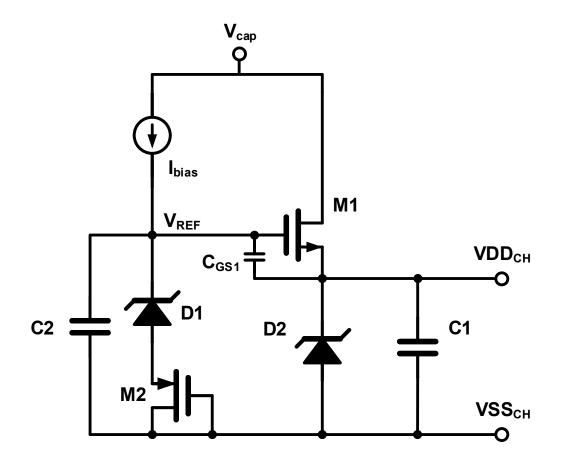

| 3.6         | The channel supply generator for the switching channel is a low dropout (LDO) regulator. The main LDO power transistor M1 uses circuit feedback to fix the                                                                                                                                                                                                                                                                                                                                             |                |

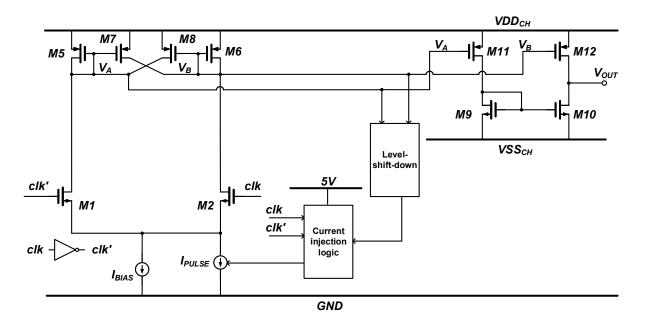

| 3.7         | output $VDD_{CH}$ at five volts above $VSS_{CH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34             |

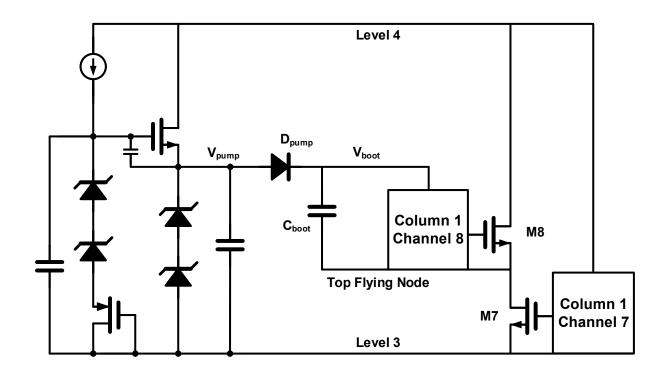

| 3.8         | $V_{OUT}$ . In this figure, the digital input signal is labeled as clk This diagram depicts the bootstrapping set up for supplying the top switching channel of column 1. Note that the channel blocks consist of a channel supply, level shifter, and driver. On the left, a modified channel supply maintains the static $V_{pump}$ voltage at 11 V to 12 V above level 3. When M7 is closed, $V_{pump}$ charges $C_{boot}$ through $D_{pump}$ . When M8 is closed (M7 open), $D_{pump}$ blocks cur- | 35             |

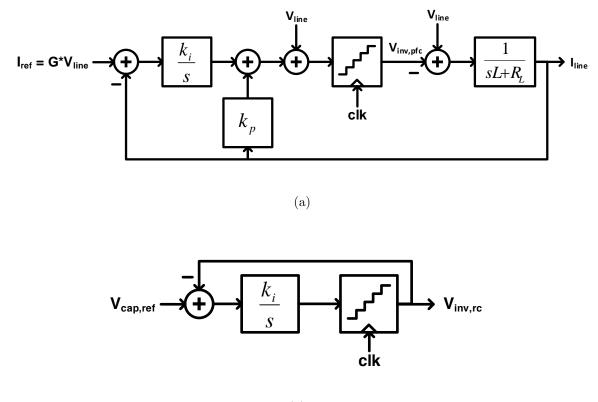

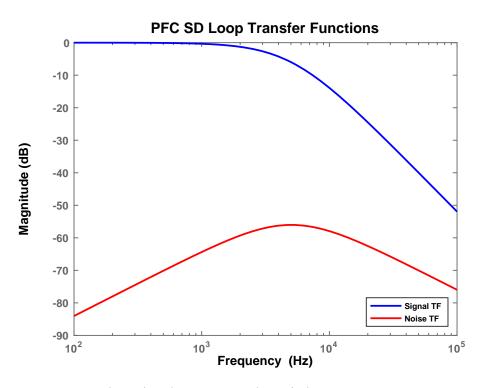

| 3.9<br>3.10 | rent, allowing $V_{boot}$ to be higher than level 4. Channel 8 (the top switching channel) is supplied from $C_{boot}$                                                                                                                                                                                                                                                                                                                                                                                 | 36<br>38<br>39 |

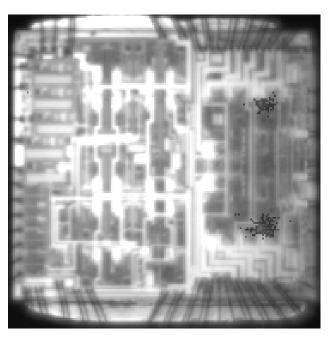

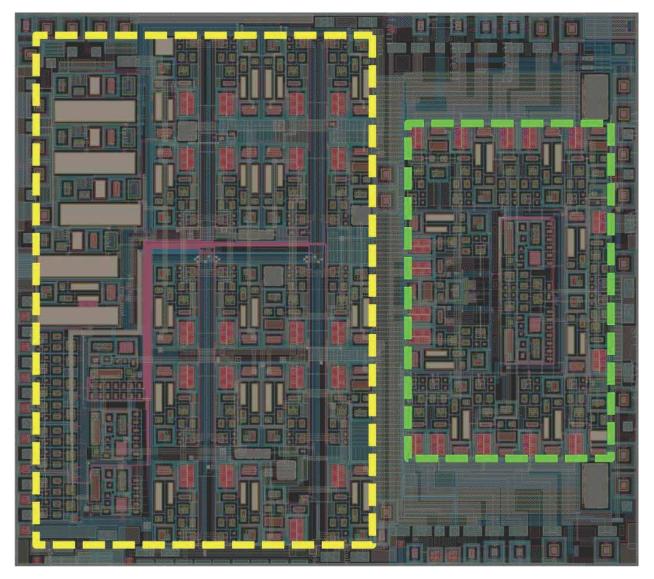

| 4.1         | Die photo of the prototype IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42             |

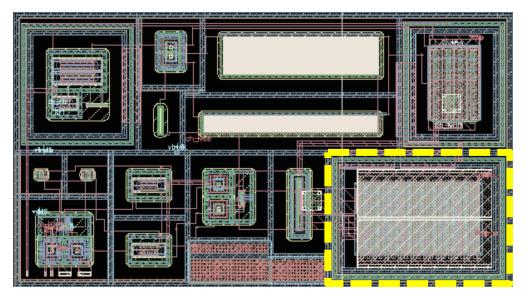

| 4.2         | The prototype IC layout with dimensions of 7.08mm X 6.28mm. The multilevel                                                                                                                                                                                                                                                                                                                                                                                                                             | 43             |

| 4.3         | converter is on the left (yellow). The H-bridge stack is on the right (green)<br>The layout for the switching channel with the power LDMOS highlighted in<br>yellow. The channel supply, level shifter, and driver account for roughly 80% of                                                                                                                                                                                                                                                          | 40             |

| 4.4         | the layout area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44             |

|             | can be integrated in CMOS on the IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44             |

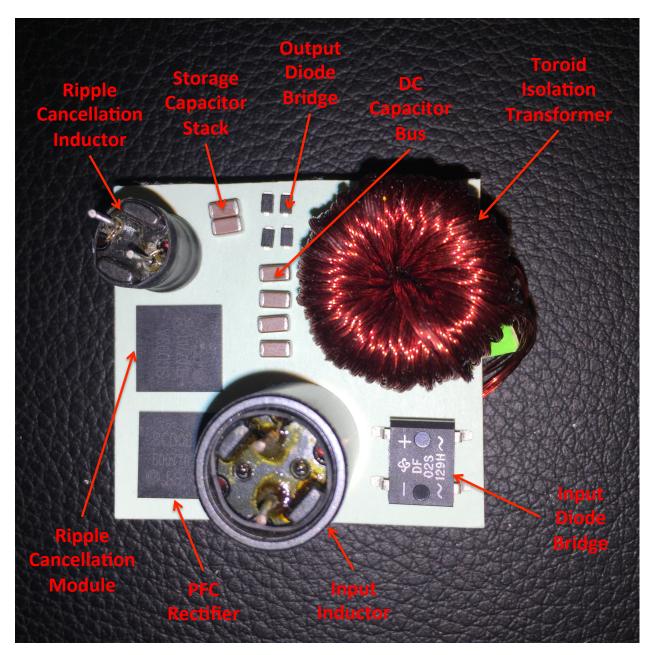

- 4.5 A mock layout of the power board with the various components from Table 4.1. Since the digital and analog control can be integrated, these components indicate the total size of the LED driver. For reference, the two IC packages are 1x1 cm, and the card is 4.3x3.8 cm. The layout can be even more tight if the magnetic components are stacked on top of the flat components.

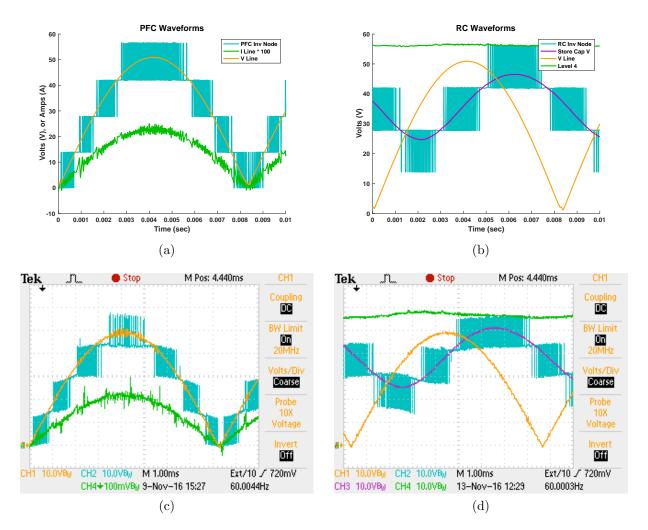

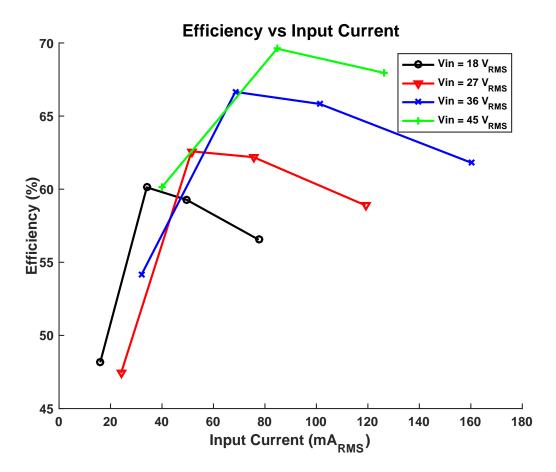

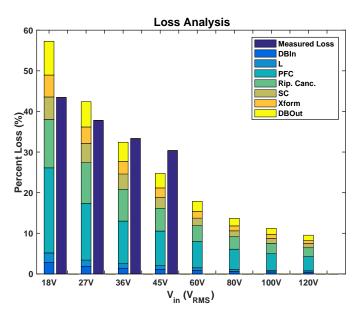

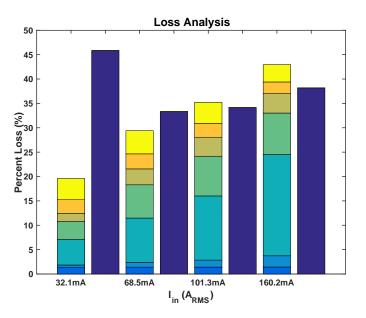

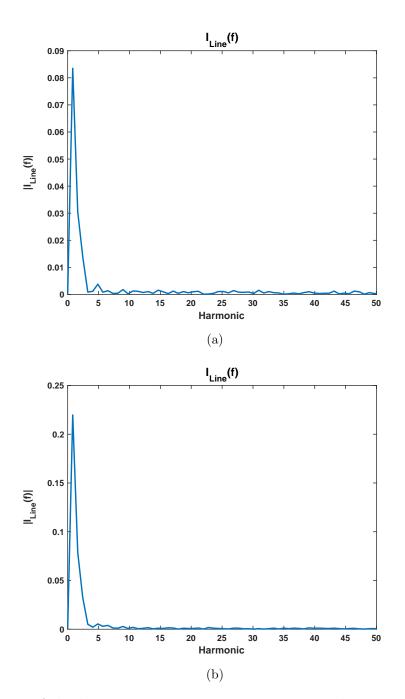

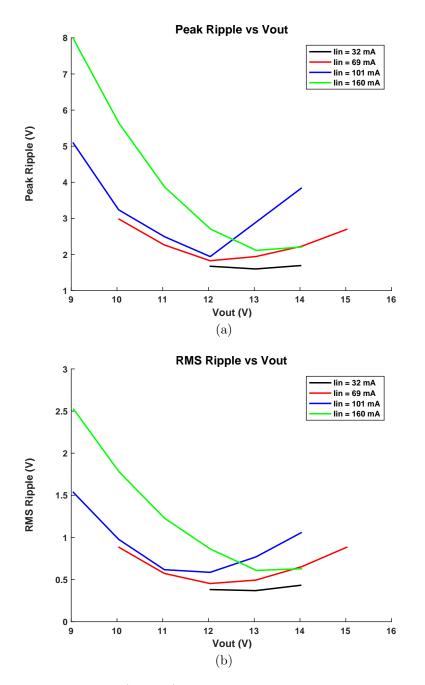

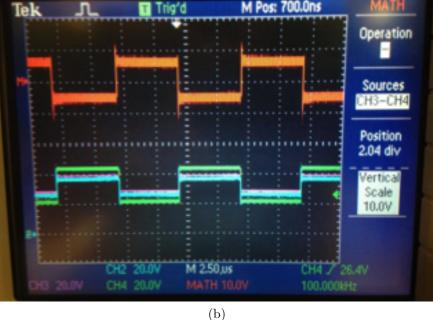

- Simulated and experimental waveforms that demonstrate the functionality of the 4.6power-factor correction (PFC) rectifier and ripple-cancellation module. (a) Simulated PFC waveforms with the line voltage (vellow), line current (green), and the PFC rectifier inverter node of Figure 3.2 (blue). The line current is scaled by 100 for visibility. (b) Simulated ripple-cancellation module waveforms. Waveforms include the line voltage (yellow), the voltage at level 4 of the DC capacitor bus (green), the voltage across the storage capacitor (purple), and the ripplecancellation module inverter node from Figure 3.3 (blue). (c) Experimental PFC rectifier waveforms from oscilloscope. The line current (green) is measured as the voltage across a 1 ohm current sense resistor. Horizontal divisions are 1 ms. Vertical divisions are 10 V for the line voltage (yellow) and PFC rectifier inverter node (blue), and are 100 mV for the line current (green). (d) Experimental ripple-cancellation module waveforms. Horizontal divisions are 1 ms and vertical 48Efficiency versus input current (the rated input current is 167 mA). The output 4.7voltage was set at the optimal value using an electronic load. In general, the output voltage and current is determined by the total voltage drop of the series 51Loss versus input voltage. The lower voltages each compare a loss model (left bar) 4.8to the actual measured loss (right dark blue bar). The loss model can somewhat provide a projection of how the system would perform. The model and data correspond to operation at close to 80 mA input current. . . . . . . . . . . . . . . . . 524.9 Loss versus input current at 36  $V_{\rm RMS}$  input, with same legend as Figure 4.8. The loss model does not properly account for losses in the switching channels, which dominate at light loads. 524.10 FFT of the line current input  $I_{\text{Line}}$ . Line current harmonics are all less than 5% of the fundamental. Data is obtained at  $V_{in,RMS} = 36 \text{ V}$ , and (a)  $I_{in,RMS} = 68.5 \text{ mA}$ , or (b)  $I_{in,RMS} = 160 \text{ mA.}$ 534.11 Ripple at the top (level 4) of the DC capacitor bus as a function of the output voltage. Input voltage is  $36 V_{RMS}$ . (a) Peak to peak ripple voltage of DC level 4. 55

- 4.12 Proposed configuration for the LED driver without the H-bridge stack. The transformer windings connect to the column 1 flying nodes of the PFC rectifier and the ripple-cancellation module (not shown).56

vii

46

| 4.13 | Proposed switching channel architecture that uses a complementary PMOS for each of the even numbered switches. The channel supply generator creates the static supply rails $VDD_{CH}$ and $VSS_{CH}$ which are respectively 5 V above and below level 1               | 58       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

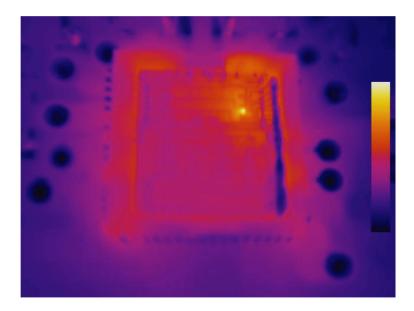

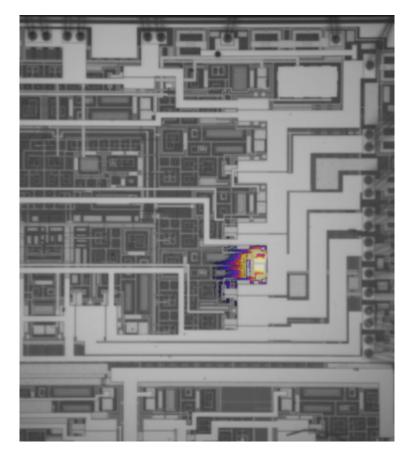

| A.1  | Thermal camera image of the chip undergoing test 1. The DC input voltage is between 70 V and 90 V. The hot spot indicates the general location of the 20 mA                                                                                                            | C D      |

| A.2  | leakage                                                                                                                                                                                                                                                                | 63<br>64 |

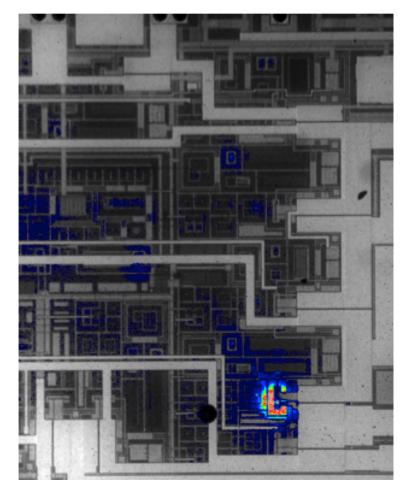

| A.3  | PHEMOS image of the chip undergoing test 1. There is an abnormally high                                                                                                                                                                                                |          |

| A.4  | current density in the driver of the gate driving channel                                                                                                                                                                                                              | 65       |

| A.5  | The PHEMOS detected a large current density in the driver                                                                                                                                                                                                              | 66<br>67 |

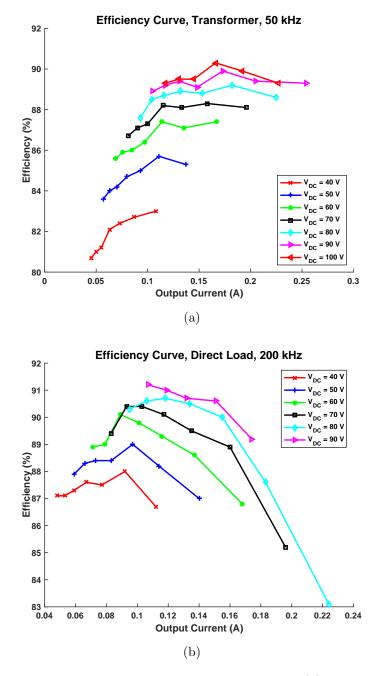

| B.1  | The performance curves for the output stage. (a) Direct load, switching at 200 kHz. (b) Transformer output to load, switching at 50 kHz                                                                                                                                | 70       |

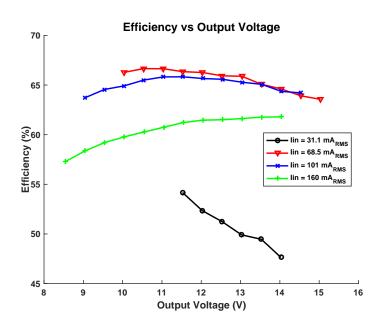

| B.2  | Efficiency vs output voltage for 36 $V_{RMS}$ input. The output voltage increases in increments of 0.5 V, and spans the range of correct functionality.                                                                                                                | 71       |

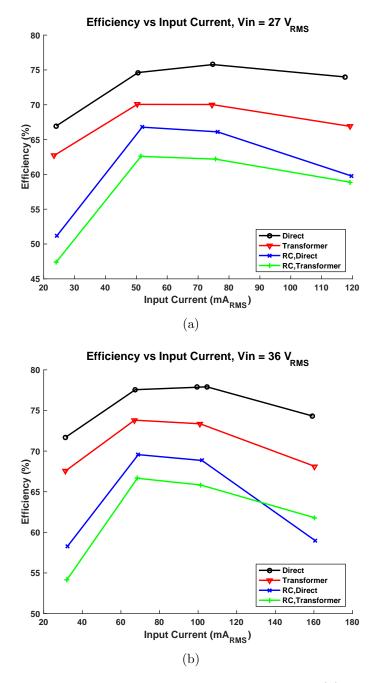

| B.3  | The performance of alternate configurations at (a) $V_{in} = 27 V_{RMS}$ , and (b) $V_{in} = 36 V$<br>The configurations are with direct output or transformer output, and with or<br>without the ripple-cancellation (RC) module. For reference, the standard config- |          |

|      | uration is "RC, Transformer".                                                                                                                                                                                                                                          | 73       |

# List of Tables

| 1.1 | Several capacitors for ripple cancellation found on Digikey [48]. The top row is                       |    |

|-----|--------------------------------------------------------------------------------------------------------|----|

|     | intended for active ripple cancellation, and the bottom two are for passive. The                       |    |

|     | volumetric requirements are much less in active ripple cancellation. For passive                       |    |

|     | ripple cancellation, the cost of a ceramic capacitor is prohibitively high, and its                    |    |

|     | volume is similar to an electrolytic equivalent. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 16 |

| 4.1 | Power components used in the prototype LED driver                                                      | 45 |

### Acknowledgments

I would like to give special thanks to my advisor Professor Seth Sanders for all his knowledge, guidance, and support throughout my time at Berkeley. Additional thanks to my fellow group members, whose advice and support have proven invaluable on many occasions. Finally, I would like to thank my family and friends, who have encouraged and supported me through the endeavor.

# Chapter 1

# Introduction to LED Drivers

## 1.1 The Lighting Industry

Since the invention of the light bulb, lighting has been central to productivity and advancement. Newly electrified communities and industrialized nations both prioritize lighting as the first and most important electrical load to be connected. In 2013, lighting accounted for 17% of the total US electrical energy consumption [1]. As such, there is significant motivation to increase the performance of lighting technology. For the industry, this means increasing the efficiency and efficacy of commercial and residential lamps.

Over the past century, the lighting industry has transitioned through multiple technologies [2]. The earliest technology, the incandescent bulb, established the industry and saw widespread use through the end of the 20th century. Incandescent bulbs operate by the principle of incandescence, in which an electric current heats the tungsten filament until it emits light.

The incandescent bulb's successor, the fluorescent bulb, was also present for much of the 20th century. By 1951, fluorescent lamps were the dominant lighting technology in the US. The helical compact fluorescent lamp (CFL) became available for purchase in 1995, and became popular in the residential sector. The fluorescent bulb contains mercury gas, which emits ultraviolet radiation when subject to an electric current. The ultraviolet radiation is absorbed by the bulb's phosphor coating, which in turn releases visible light through fluorescence. CFLs became popular because they require a third the power and last 5-10 times longer than the incandescent bulb [3–6].

Despite their superior efficiency and life span, CFLs have several notable drawbacks. First, CFLs contain mercury gas, which damages the environment if released [7, 8]. Recycling CFLs requires an extensive and specialized process. Another drawback of the CFL is that it has a lower color rendering index (CRI) than the incandescent bulb [2, 9–11]. The CRI is a metric for how accurately a lamp can render colors. Light sources such as daylight or incandescent lamps have a perfect CRI of 100. CFLs have a CRI in the low 80's, and various colors rendered under a CFL may appear in the wrong shades. The final drawback of CFLs is that they have a cooler correlated color temperature (CCT). Lamps with a cooler CCT illuminate with a white or blue tone, whereas lamps with a warmer CCT appear as yellow and orange. Many people prefer the relaxing feel of a warmer CCT, and studies show that a cooler CCT may have an adverse effect on sleep [12–14].

Since the early 2000's, the light emitting diode (LED) has transitioned from indicator lights to becoming mainstream in the lighting industry. Today, LEDs are recognized for their efficiency, reliability, and environmental benefits. The LED is a semiconductor diode with a positive-type and negative-type dopant. When the LED is subject to a voltage potential, the electrons and holes at the dopant junction are able to recombine and release energy in the form of light. LEDs use roughly 80% as much power as CFLs and last more than twice as long [3–6]. Many case studies have shown that the combination of efficiency and life span makes LEDs the most economic choice (i.e. lowest life cycle cost) for lighting. LEDs have a slightly greater environmental impact than incandescent bulbs due to a higher concentration of toxic metals (per lumen). However, they are significantly more environmentally friendly than CFLs [7, 8]. Unfortunately, LEDs also suffer a similarly low CRI and color temperature [11]. Some of the more expensive LED lamps can have CRI and color temperatures that are nearly as good as the incandescent lamp.

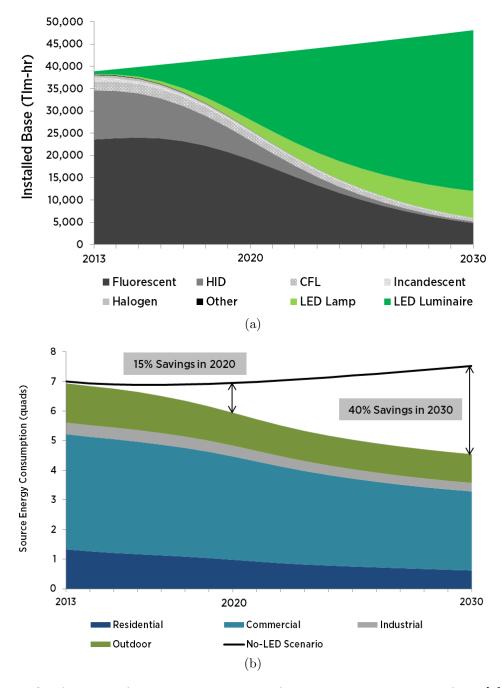

Since 2010, LED lamps have seen an increase in market share as technological improvements have lowered manufacturing costs. Figure 1.1 shows that by 2030, LEDs are expected to have mostly replaced incandescents and CFLs [1]. Since LEDs will become the cornerstone of the lighting industry, there is great industrial motivation to produce efficient, economic, and high quality LED lamps. This dissertation is centered around enhancing an LED lamp by designing an improved LED driver.

Figure 1.1: DOE forecast of the lighting industry from 2013 to 2030, taken from [1]. (a) Distribution of installed lighting types over the next decade. By 2030, LEDs are expected to mostly replace all other forms of lighting. (b) Lighting energy consumption over the next decade. Due to the switch to LEDs, lighting energy consumption is expected to decrease by 40%.

## 1.2 The LED Driver

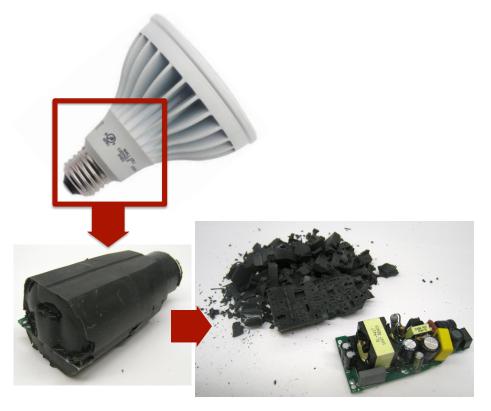

The LED driver supplies power to the LEDs in a lamp. As shown in Figure 1.2, the driver includes all of the electronics between the building 120  $V_{RMS}$  distribution and the LEDs. LEDs are recognized as the most economic choice for lighting, and so it is important that the LED driver be equally inexpensive, efficient, and reliable.

Other types of lamps have their own methods of providing power to the bulb. The incandescent lamp does not require a driver since a bulb can attach directly to the AC 120  $V_{RMS}$  distribution. Fluorescent lamps require a driver that serves two purposes. On startup, the fluorescent lamp driver is responsible for providing a voltage high enough to ionize the inert gas inside the bulb. Once the gas is ionized, its resistance decreases with current, which leads to an unstable positive feedback. Therefore, the fluorescent lamp driver must also act as a ballast and control the current flowing through the bulb.

There are several technical challenges in driving LEDs that are not present with the incandescent bulb [15–17]. The first is that LEDs require DC power. The incandescent bulb works with either AC or DC since any type of current can heat the filament. However, LEDs block reverse current, and so the driver must rectify the AC input to DC. Rectification can be accomplished with a simple diode bridge. However, many applications and standards

Figure 1.2: Teardown of an EcoSmart PAR30 LED flood light. The driver plug sits inside the base of the housing and connects the glass filled screw socket to the LEDs.

require a high power quality.

Power quality can be evaluated with a metric known as power factor. A perfect unity power factor occurs when the input current is purely sinusoidal and in phase with the input voltage. The incandescent bulb has nearly unity power factor because its load profile approximates that of a resistor. The overall power factor encapsulates both the displacement factor and the distortion factor [18]. Harmonic distortion on the input current is a major concern for higher power LED lamps. It can be measured as the agglomerate of the input current harmonics. The total harmonic distortion (THD) is measured as

$$\text{THD} = \frac{\sqrt{\sum_{n=2}^{\infty} I_n^2}}{I_1} \tag{1.1}$$

where  $I_n$  and  $I_1$  represent the n-th harmonic and the fundamental of the input current respectively. The distortion power factor is closely related to the THD, and is measured as

$$\frac{I_{1,rms}}{I_{rms}} = \frac{1}{\sqrt{1 + (\text{THD})^2}}$$

(1.2)

where  $I_{rms}$  is the root mean square (RMS) of the input current, and where  $I_{1,rms}$  is the root mean square (RMS) of the fundamental.

Many standards exist for regulating the power factor and harmonic distortion in loads. For lighting in particular, standards such as IEC 61000-3-2 (US) and EN 61000-3-2 (Europe) specify the acceptable limitations on specific line-current harmonics [19]. As such, it is often important and desirable for the LED driver to be able to perform power-factor correction (PFC). Passive PFC involves using a passive LC filter to remove harmonics from the line current. However, a 60 Hz filter is bulky and expensive, and so passive techniques are almost never used exclusively. Active PFC involves the use of active switching patterns to remove harmonics. Some LED drivers perform PFC through active techniques with the assistance of a small passive filter that is designed to filter out the high switching frequency.

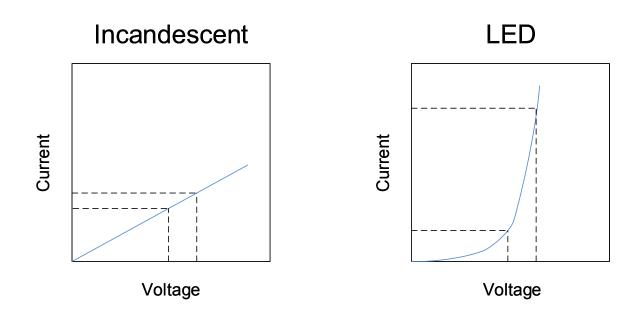

Another technical challenge in driving LEDs is that they have an exponential current-voltage relationship. First consider an incandescent bulb, whose current-voltage relationship approximates that of a resistor. The current through the filament is proportional to voltage, and so the bulb's power (and luminous output) can be controlled by its voltage. However, an LED's current varies exponentially with its voltage, as shown in Figure 1.3. In such a relationship, small deviations in LED voltage can cause large swings in LED current. An LED's brightness varies almost linearly with its current, and so small deviations in voltage can lead to a drastically different luminous output. It is difficult to regulate a driver's output voltage to the degree required. As such, LED drivers must employ precise current control in order to regulate the luminous output of the LEDs.

An additional challenge is that LEDs have a fast luminous response to power ripple. As discussed in Section 1.1, LEDs generate light when charge carriers recombine and release photons. Relative to electrical distribution frequencies, charge recombination is a very fast

Figure 1.3: Sample plots of current vs voltage for the incandescent bulb and the LED (not to scale). The incandescent bulb has a linear or resistive relationship, and either voltage or current control may be employed to regulate the power. The LED has an exponential relationship. A small deviation in voltage could determine whether the LED is on or off. As such, current control is desirable to regulate LED power.

process. In contrast, the incandescent bulb generates light via incandescence, which occurs after electrical power is converted to thermal energy. Thermal processes such heat transfer tend to be relatively slow. Since the incandescent bulb has a relatively long thermal time constant, it can effectively filter the 120 Hz power ripple from the input.

LEDs have a time constant that is much smaller than that of the AC input. The driver's AC input may transfer 120 Hz power ripple to the LEDs, which may in turn cause 120 Hz LED flicker [20]. Flicker can have an adverse effect on human health including headaches, loss of concentration, and seizures. As such, the LED driver must have a means of reducing power ripple at the LEDs. Ripple and flicker will be further discussed in Section 1.4.

Finally, high brightness LED lamps require careful thermal management. LED life span degrades exponentially with increasing the operating temperature [21]. For safety considerations, the LED heat sink must be galvanically isolated from the power train. Providing a means to galvanically isolate the LEDs allows the LEDs to be directly mounted on the heat sink. Thus, galvanic isolation of the LEDs is a desired circuit function.

### **1.3 LED Driver Topologies**

Over the past decade, the LED industry has matured through the design and improvement of LED driver circuit topologies. This section provides a survey of the various LED driver technologies on the market or in publication. It explains and evaluates how each topology address the design challenges in Section 1.2.

#### **1.3.1** Linear LED Drivers

The linear LED driver, shown in Figure 1.4, is based on the linear regulator [22, 23]. Linear LED drivers are generally smaller and less expensive than other topologies because they do not require bulky magnetics. In addition, linear drivers do not require high voltage switching for operation, and thus inject very little electromagnetic interference (EMI) onto the line. As shown in Figure 1.4, the linear driver can vary the impedance of multiple strings of LEDs in order to control the driver's input impedance. With control over the input impedance, the driver may precisely regulate the input current, thereby allowing it to perform both power-factor correction (PFC) and current regulation.

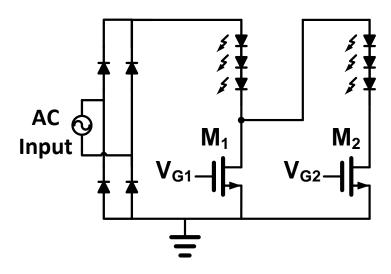

The most notable disadvantage of the linear driver is its relatively low efficiency. In addition to control loss, the efficiency of a linear regulator is inversely proportional to its voltage conversion ratio. Since the drop across any switch (i.e.  $M_1$  and  $M_2$ ) is loss, the linear LED driver ultimately suffers low efficiency whenever the string of LEDs is not perfectly matched to the input voltage. Another disadvantage is that the LEDs are not galvanically isolated from the power train, which as explained in Section 1.2, can be a safety concern. Finally, the linear LED driver is difficult to adapt to industry applications with specific input or output impedance specifications.

Figure 1.4: The linear LED driver.

Figure 1.5: The buck-based LED driver.

#### 1.3.2 Switched-Mode LED Drivers

Switched-mode LED drivers perform voltage conversion through high frequency switching. The conversion voltage drop primarily occurs across an inductor, which allows switched-mode converters to be much more efficient than linear regulators. Control over the switching duty cycle allows for output power regulation. A popular switched-mode LED driver is the buck-based driver [16, 24], shown in Figure 1.5. By carefully adjusting the duty cycle and conversion ratio, the converter can simultaneously regulate the current to the LEDs and provide PFC at the input. Other popular switched-mode converter topologies such as the boost converter [25, 26] and the buck-boost converter [27] have also been utilized in LED drivers.

The buck-based LED driver has several disadvantages. First, this topology may require a relatively large inductor  $(L_1)$  in order to properly provide PFC and avoid discontinuous condition mode (DCM). In [24], the inductor was sized at 5.5 mH for an 86 kHz design. High frequency switching can reduce the required inductance at the cost of additional gate drive loss. Another drawback is that the main power switch  $(M_1)$  must be sized such that it can withstand both the peak line voltage and the LED output current. Finally, the buck-based LED driver is not galvanically isolated at its output. The boost and buck-boost LED drivers allow for larger conversion ratios, but still have the same core disadvantages as the buck LED driver.

#### **1.3.3** Flyback LED Drivers

The flyback LED driver, shown in Figure 1.6, is an isolated buck-boost converter that utilizes the magnetizing inductance in the transformer [16, 28–32]. Due to its efficient switched-mode conversion and galvanically isolated output, the flyback LED driver is currently the

Figure 1.6: The flyback LED driver.

mainstream topology for high brightness LED lamps. As discussed in Section 2.1, this dissertation uses the flyback driver as a baseline for comparison of life span and form factor.

An analysis of the flyback converter's operation in critical conduction mode is shown in Figure 1.7. In this analysis, the flyback transformer is modeled as an ideal transformer with a primary side magnetizing inductance. When the switch turns on, the input voltage is connected across the primary winding and the transformer's magnetizing inductance  $L_m$ . The step in voltage across  $L_m$  causes the magnetizing current through  $L_m$  to ramp up. When the switch turns off, the magnetizing current flows through the ideal transformer's primary winding, ultimately powering the LEDs via the secondary winding.

The disadvantages of the flyback LED driver are in its size and cost. First, the flyback transformer is often bulky and expensive. Since this topology requires the transformer to store energy in its magnetizing inductance, the flyback transformer is larger than an isolation transformer delivering the same V-A rating. One way to reduce the transformer size is to operate in critical conduction mode as shown in Figure 1.7. Critical conduction mode allows the magnetizing current to be reduced and prevents core saturation. The other disadvantage is that the main switch  $M_1$  has to be even larger than that of the buck-based driver. The nominal switch stress can be derived from Figure 1.7c as:

$$S = V_{pk}I_{pk} = (V_{rect} + V_F N)(I_{LED}\frac{2}{N(1-D)})$$

(1.3)

where  $V_F$  and  $I_{LED}$  are the LED string voltage and current,  $V_{rect}$  is the DC rectified line input, and N is the turns ratio. In addition, sizing of M<sub>1</sub> must account for a substantial overshoot voltage at turn-off due to leakage inductance in the flyback transformer.

(c)

Figure 1.7: Analysis of a flyback LED driver operating in critical conduction mode, as depicted in [28]. (a) Equivalent circuit with switch ON. (b) Equivalent circuit with switch OFF. (c) Current and voltage transients in the flyback converter.

#### **1.3.4** Resonant and Soft Switching LED Drivers

While resonant LED driver topologies have not yet had a major industiral impact, they have become quite prevalent in research [33–35]. Resonant converters often contain a resonant tank at the output. Adjusting the converter's switching frequency can modulate the resonant tank impedance, which ultimately makes it possible to regulate the output current. In certain designs, the resonant tank capacitors can also provide galvanic isolation [34, 35].

Another distinct benefit of the resonant converter is that it allows for soft switching [36–38]. With modern industrial demand on size and efficiency, it is increasingly clear that switching converters greatly benefit from zero voltage switching (ZVS). Zero voltage switching involves the use of resonant techniques to ensure that the drain-source voltage of an open power switch is zero before this device turns on. This is hugely beneficial in ensuring that the device is not blocking and conducting at the same time, thus reducing switch stress

Figure 1.8: Zero voltage switching (ZVS) in a resonant half bridge. (a) When M1 is on, the inverter node  $V_{inv}$  is pulled high and the parasitic drain-source capacitance  $C_{ds2}$  is charged to  $V_{DC}$ . (b) During the dead time, the tank current  $I_{tank}$  discharges  $C_{ds2}$ . (c) M2 turns on when  $V_{inv}$  reaches zero. This way, there is zero voltage across M2 when it turns on. (d) Waveforms demonstrating ZVS.

and preventing shoot-through. Section 3.2.2 and appendix B.1 discuss how soft-switching techniques are important to the LED driver presented in this dissertation.

Even if switch stress is not a concern, ZVS is very beneficial in improving a converter's efficiency. Power MOSFETs often contain substantial parasitic drain-source capacitance  $C_{ds}$ . When a switch without ZVS turns on, the parasitic capacitor charge  $q = C_{ds}v_{ds}$  flows through the channel as loss. Figure 1.8 illustrates how the resonant inductor can discharge the parasitic capacitance of switch M2 and allow for ZVS. In this case, the switching dead time is tuned based on the resonant frequency of  $C_{ds}$  with the tank inductor  $L_T$ . During this dead time,  $C_{ds2}$  is completely discharged and the drain-source voltage across M2 goes to zero. Once the drain-source voltage across M2 reaches zero, M2 should switch on. It is important to note that if M2 does not turn on as soon as  $C_{ds2}$  is discharged, the tank current  $I_{tank}$  will have to flow through the reverse diode of M2. Since the reverse diode introduces loss, it is best to turn on M2 exactly when its drain-source voltage is zero.

The final benefit of soft switching is that it reduces the high frequency harmonic switching noise that the converter would otherwise inject onto the line. ZVS smooths the current spikes that would otherwise be present at each switching edge.

Quasi-resonant converters are a type of converter that is mainly designed around soft switching. In many cases, the quasi-resonant converter topology comes from a standard converter topology, but with a small resonant tank near the power switch. Unlike normal resonant converters, quasi-resonant converters do not use a resonant tank to regulate output current. However, they still enjoy the benefits of increased efficiency and reduced EMI. Various quasi-resonant LED drivers have been proposed as soft switching variations of the flyback [39] or boost [40] LED drivers.

#### 1.3.5 Switched Capacitor LED Drivers

Switched capacitor converters have recently been in the research spotlight for low to moderate power conversion. Unsurprisingly, they have been considered for lighting applications [34, 35]. The switched capacitor converter uses an array of switches and capacitors to perform conversion. Its major advantage is that no magnetics are required. As such, the switched capacitor converter is very amenable to integration.

As explained in Section 3.2.2, the output stage of the LED driver presented in this dissertation uses an isolated 4:1 H-bridge stack. For applications that do not require isolation, a 4:1 switched capacitor ladder can be used as an alternative output stage topology. Appendix B.1 directly compares the performance of the H-bridge stack and the switched capacitor ladder.

### **1.4** Power Ripple and Flicker

Flicker is a steady state oscillation in a lamp's intensity. As mentioned in Section 1.2, flicker is usually due to AC power ripple at the input of a lamp driver. This effect is most severe in LEDs due to their relatively fast luminous response to power. Low frequency flicker can induce seizures in epileptics [20, 41]. In others, it may induce headaches, eye strain, and a loss of concentration. Humans can only perceive flicker up to 60-90 Hz. However, adverse biological effects may still occur in the presence of lights that flicker up to 200 Hz.