# UC Santa Cruz UC Santa Cruz Electronic Theses and Dissertations

# Title

A Fast, Parallel, and Multi-Language Hardware Compilation Framework

Permalink

https://escholarship.org/uc/item/8h18x5f0

Author Wang, Sheng-Hong

Publication Date 2022

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA SANTA CRUZ

## A FAST, PARALLEL, AND MULTI-LANGUAGE HARDWARE COMPILATION FRAMEWORK

A dissertation submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

### COMPUTER ENGINEERING

by

### **Sheng-Hong Wang**

December 2022

The Dissertation of Sheng-Hong Wang is approved:

Professor Jose Renau, Chair

Professor Cormac Flanagan

Professor Scott Beamer

Peter Biehl Vice Provost and Dean of Graduate Studies Copyright © by

Sheng-Hong Wang

2022

# **Table of Contents**

| Li | st of ]                          | Figures                                                                                                                                                                                                   |                                                       |                    |         |                           |                                          |                                            |                                       |                                  |                                       |                  |                                       | vi                                           |

|----|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------|---------|---------------------------|------------------------------------------|--------------------------------------------|---------------------------------------|----------------------------------|---------------------------------------|------------------|---------------------------------------|----------------------------------------------|

| Li | st of [                          | <b>Tables</b>                                                                                                                                                                                             |                                                       |                    |         |                           |                                          |                                            |                                       |                                  |                                       |                  |                                       | viii                                         |

| Ał | ostrac                           | t                                                                                                                                                                                                         |                                                       |                    |         |                           |                                          |                                            |                                       |                                  |                                       |                  |                                       | ix                                           |

| Ac | knov                             | vledgments                                                                                                                                                                                                |                                                       |                    |         |                           |                                          |                                            |                                       |                                  |                                       |                  |                                       | xi                                           |

| 1  | Intr                             | oduction                                                                                                                                                                                                  |                                                       |                    |         |                           |                                          |                                            |                                       |                                  |                                       |                  |                                       | 1                                            |

| 2  | Live<br>2.1<br>2.2<br>2.3<br>2.4 | HD Overview<br>HDL Support Choice<br>Hardware IR Choice<br>LiveHD Overview<br>Clarification                                                                                                               | <br>                                                  | •••••              | <br>    | <br>                      | <br>                                     | <br>                                       | <br>                                  | · ·                              | <br>                                  | •                | <br>                                  | 9<br>10                                      |

| 3  | <b>Rela</b><br>3.1<br>3.2<br>3.3 | <b>ted Work</b><br>Live Techniques in Live<br>Hardware Description<br>Software Programming                                                                                                                | Language                                              | Comp               | ilers a | nd I                      | Rs .                                     |                                            |                                       |                                  |                                       |                  |                                       | 15                                           |

| 4  | <b>LGr</b><br>4.1<br>4.2<br>4.3  | aph: A Unified Low-levenIntroductionLGraph-IR Construction4.2.1Node, Pin, and4.2.2LGraph TraversLGraph-IR Characteris4.3.1SSA Graph4.3.2Reduced Logic4.3.3N-ary Gates4.3.4Signed Wires4.3.5Wire Width Sem | on and Trav<br>Edge Cons<br>al<br>tics<br>Instructior | versal<br>structio | on      | <br><br><br><br>Cells<br> | · · · ·<br>· · · ·<br>· · · ·<br>· · · · | · · ·<br>· · ·<br>· ·<br>· ·<br>· ·<br>· · | · · · · · · · · · · · · · · · · · · · | · · ·<br>· · ·<br>· · ·<br>· · · | · · · · · · · · · · · · · · · · · · · | ·<br>·<br>·<br>· | · · · · · · · · · · · · · · · · · · · | 24<br>24<br>25<br>27<br>27<br>28<br>28<br>30 |

|   |            | 4.3.6  | Bitwidth Inference                                          |

|---|------------|--------|-------------------------------------------------------------|

|   |            | 4.3.7  | Global Inference                                            |

|   |            | 4.3.8  | Prototype Inference                                         |

|   | 4.4        | LGrap  | h Attribute Design                                          |

|   |            | 4.4.1  | Non-Hierarchical Attribute 34                               |

|   |            | 4.4.2  | Hierarchical Attribute                                      |

|   | 4.5        | 3rd Pa | rty Tools Integration                                       |

|   |            | 4.5.1  | Mockturtle                                                  |

|   |            | 4.5.2  | OpenTimer                                                   |

|   | 4.6        | Lesson | n Learned: The Deprecated but Fast Memory-Mapped Library 36 |

|   |            | 4.6.1  | Evaluation Setup                                            |

|   |            | 4.6.2  | Memory Mapped Library Results                               |

|   | 4.7        | Conclu | usions                                                      |

|   |            |        |                                                             |

| 5 |            |        | High-Level Language Neutral AST-IR for Hardware Description |

|   |            | guages | 42                                                          |

|   | 5.1        |        | uction                                                      |

|   | 5.2        |        | T Model                                                     |

|   |            | 5.2.1  | Tree Structure         46                                   |

|   |            | 5.2.2  | Attribute in LNAST Nodes    48                              |

|   |            | 5.2.3  | Neutral Node Types for HDLs    48                           |

|   |            | 5.2.4  | Function Call in LNAST                                      |

|   |            | 5.2.5  | Scope Flexibility 51                                        |

|   | 5.3        | LNAS   | T Transformations in LiveHD                                 |

|   |            | 5.3.1  | From HDLs to LNAST 52                                       |

|   |            | 5.3.2  | From High-Level LNAST to HDLs                               |

|   |            | 5.3.3  | From LNAST to LGraph                                        |

|   |            | 5.3.4  | From LGraph to Low-Level LNAST 54                           |

|   | 5.4        | Lesson | n Learned                                                   |

|   |            | 5.4.1  | The Deprecated CFG and Yosys to LGraph passes               |

|   |            | 5.4.2  | The Deprecated Persistence                                  |

|   | 5.5        | LNAS   | T Evaluation                                                |

|   |            | 5.5.1  | Setup                                                       |

|   |            | 5.5.2  | Results                                                     |

|   | 5.6        | Conclu | usion                                                       |

| ~ |            | ( D    |                                                             |

| 6 |            |        | Ilel Compilation Framework for HDLs59Solution50             |

|   | 6.1        |        | uction                                                      |

|   | 6.2        |        | el Compilation                                              |

|   |            | 6.2.1  | Dependency Tree                                             |

|   | ( <b>^</b> | 6.2.2  | Parallelism in Compilation Passes                           |

|   | 6.3        |        | HDLs Compilation                                            |

|   |            | 6.3.1  | Parallel I/O Pass    71                                     |

|              |     | 6.3.2  | Bitwidth Pass                                                 | 73 |  |  |

|--------------|-----|--------|---------------------------------------------------------------|----|--|--|

|              | 6.4 | Setup  |                                                               | 75 |  |  |

|              | 6.5 | Evalua | tion                                                          | 76 |  |  |

|              |     | 6.5.1  | Multi-Threaded Scalability                                    | 77 |  |  |

|              |     | 6.5.2  | Single-Threaded Performance                                   | 84 |  |  |

|              | 6.6 | Conclu | isions                                                        | 85 |  |  |

| 7            | Con |        | and Future Opportunities                                      | 86 |  |  |

|              | 7.1 | Future | work                                                          | 87 |  |  |

|              |     | 7.1.1  | Resolving High-level Program Structural at LNAST              | 87 |  |  |

|              |     | 7.1.2  | A Finer-granularity of Parallelization                        | 88 |  |  |

|              |     | 7.1.3  | A Verifiable Pyrope Compilation                               | 88 |  |  |

|              |     | 7.1.4  | An Ene-to-End Parallel and Incremental Hardware Compilation . | 89 |  |  |

|              | 7.2 | Concu  | sion                                                          | 89 |  |  |

| Bibliography |     |        |                                                               |    |  |  |

# **List of Figures**

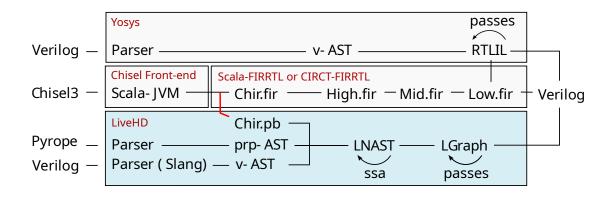

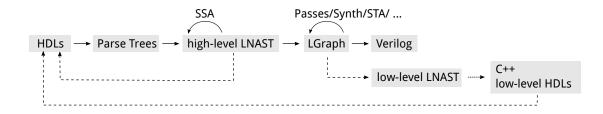

| 2.1        | Overview of LiveHD compilation flow and comparisons between Yosys and Chisel3/FIRRTL compilers.                                                                                                                         | 10 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

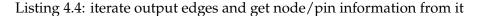

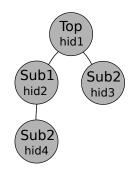

| 4.1        | A hierarchical LGraph. A sub-graph node is a sub-module instantiation.<br>The hierarchical traversal will walk into the sub-graph structure                                                                             | 26 |

| 4.2        | The tree hierarchical view for Figure 4.1. Each instantiation has a unique hid and hierarchical attribute table.                                                                                                        | 26 |

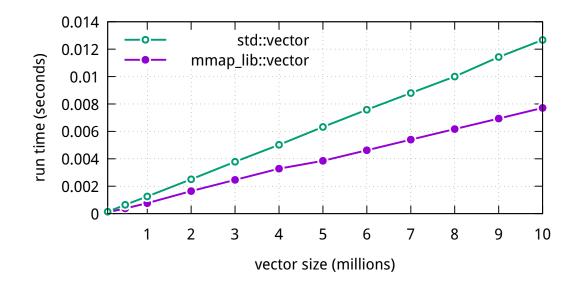

| 4.3        | LGraph's mmap_lib::vector has faster run-time compared to the std::vector                                                                                                                                               | 38 |

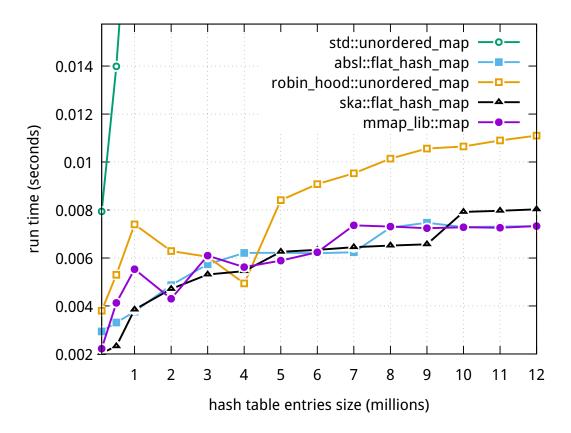

| 4.4        | LGraph's mmap_lib::map is in par with best-in-class maps for entry sizes less than 10 million but faster for entry sizes in the order of 10 million                                                                     | 39 |

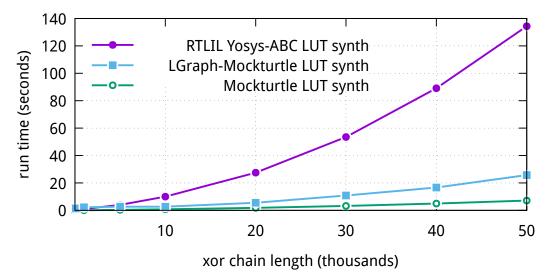

| 4.5        | The LGraph-Mockturtle flow is faster than Yosys-ABC flow under all tested scenarios                                                                                                                                     | 40 |

| 5.1        | The original LiveHD only has LGraph-Yosys interface that handles Sys-<br>temVerilog/Verilog                                                                                                                             | 43 |

| 5.2<br>5.3 | The new LiveHD flow with LNAST. The passes with physical lines in-<br>dicates the contribution of this thesis. The dash-lines indicate the other<br>students' projects that are still under-developed                   | 45 |

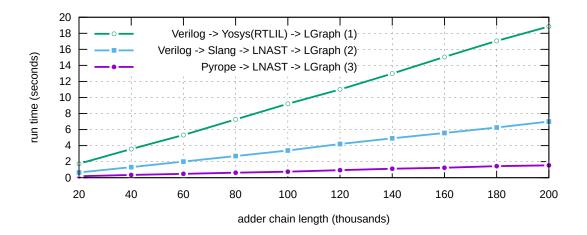

|            | one for tested circuits.                                                                                                                                                                                                | 57 |

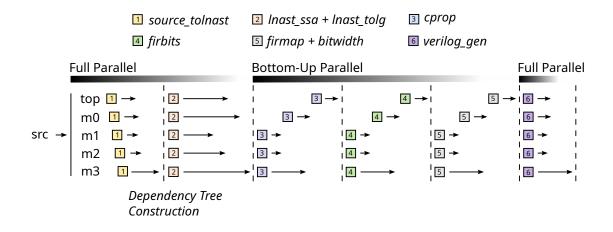

| 6.1        | The LiveHD parallel compilation example with a hierarchical FIRRTL front-end. Module <i>m</i> <sup>3</sup> is significantly larger than the others. The vertical dashed lines represent the Synchronization barriers.   | 63 |

| 6.2        | The LiveHD parallel compilation example with a hierarchical FIRRTL front-end. Module <i>m</i> 3 is significantly larger than the others. The vertical                                                                   | 00 |

|            | dashed lines represent the Synchronization barriers                                                                                                                                                                     | 63 |

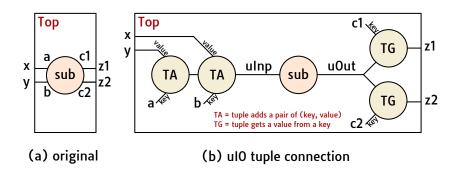

| 6.3        | A sub-module instantiation in top-module. The sub-module has inputs $(a, b)$ and outputs $(c1, c2)$ . LiveHD aggregates these I/O as tuple uIn-<br>p/uOut to isolate functional dependency while connecting the top and |    |

|            | sub at the <i>lnast_tolg</i> pass                                                                                                                                                                                       | 68 |

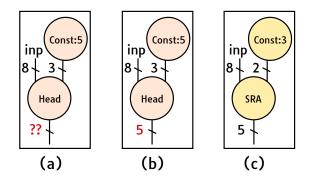

| 6.4 | Idea illustration of FIRRTL bits analysis and FIRRTL-LGraph mapping passes. The FIRRTL <i>head_op</i> extract the MSB 5-bits from the <i>inp</i> signal. (a) a FIRRTL-equivalent LGraph with an FIRRTL <i>head_op</i> . (b) the LGraph |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | after <i>firbits</i> analysis. (c) mapping to LGraph <i>shift_right_op</i>                                                                                                                                                             | 75 |

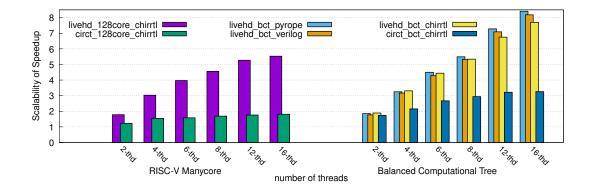

| 6.5 | LiveHD compiler shows high speedup scalability for a balanced compu-                                                                                                                                                                   |    |

|     | tation tree circuit in Pyrope, Verilog, and CHIRRTL HDLs. LiveHD also                                                                                                                                                                  |    |

|     | scales better for a RISC-V Manycore RISCV processor compared to the                                                                                                                                                                    |    |

|     | Circt-FIRRTL compiler                                                                                                                                                                                                                  | 77 |

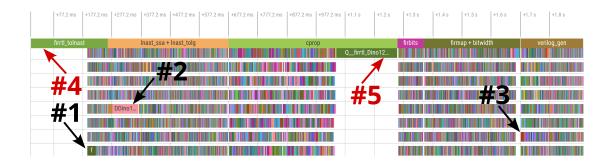

| 6.6 | LiveHD's parallel schemes establish remarkable thread utilization for an                                                                                                                                                               |    |

|     | 8-threaded compilation.                                                                                                                                                                                                                | 78 |

| 6.7 | LiveHD exhibits high thread utilization and speedup for all FIRRTL, Ver-                                                                                                                                                               |    |

|     | ilog, and Pyrope HDLs in the BCT compilation.                                                                                                                                                                                          | 82 |

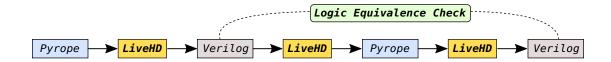

| 7.1 | A potential verification flow to check the compiler correctness of Pyrope                                                                                                                                                              |    |

|     | HDL                                                                                                                                                                                                                                    | 88 |

# List of Tables

| 2.1 | Detailed contributions from the author                                        | 12 |

|-----|-------------------------------------------------------------------------------|----|

| 4.1 | The reduced number of operator types in LGraph are designed to sim-           |    |

|     | plify the compilation complexity                                              | 29 |

| 4.2 | Capability comparison between relevant tools                                  | 32 |

| 5.1 | Four groups of operators in the LNAST IR                                      | 50 |

| 6.1 | The LiveHD passes in the compilation order.                                   | 67 |

| 6.2 | FIRRTL bitwidth management operators                                          | 74 |

| 6.3 | Compiler flags or commands for fair evaluations                               | 76 |

| 6.4 | IPC drop and frequency downscaling are two reasons why the high thread        |    |

|     | utilization from 1 to 8 threaded compilation does not give the ideal speedup. | 81 |

| 6.5 | LiveHD provides outstanding compilation speedup in single-threaded            |    |

|     | and multi-threaded scenarios                                                  | 83 |

### Abstract

A Fast, Parallel, and Multi-Language Hardware Compilation Framework

by

### Sheng-Hong Wang

A set of new Hardware Description Languages (HDLs) with a higher level of expressiveness has emerged to ease the difficulty of depicting complex hardware design. However, the increased compilation time also becomes a new bottleneck on the designer's productivity and adds more burden to the already lengthy hardware EDA flow. Meanwhile, these new HDLs tend to be developed with a stand-alone compiler, making an HDL compilation innovation hard to share with the compiler community.

I design and implement LiveHD, a new multi-threaded, fast, and generic compilation framework across many HDLs (FIRRTL, Verilog, and Pyrope). Internally, a high-level generic AST-like IR, LNAST, is used to interface the front-end source languages. Then LiveHD translate the LNAST-IR into a low-level LGraph IR, which supports most of the compilation passes and optimizations. I propose new fully and bottomup parallel passes to handle HDLs. The resulting compiler is able to parallelize all of the compiler steps.

LiveHD can achieve 5.5x speedup scalability when elaborating a multicore RISC-V designed in the FIRRTL HDL. It also gets from 7.7x to 8.4x speedup scalability for a benchmark designed in all three HDLs. This is achieved with a fast single-threaded LiveHD baseline where it has 6x speedup compared to compilers such as Scala-FIRRTL and 8.6x against Yosys on Verilog. The highly parallelized and generic LiveHD compilation framework will open many exciting opportunities in the HDLs compiler and EDA research domain.

### Acknowledgments

First, I sincerely thank my advisor Professor Jose Renau, the kindest person in the world. Jose always opens the gate for students whenever they need a discussion, help, and advice on issues in either research or personal life. Jose's creative research ideas always broaden my mind and encourage me to make breakthroughs beyond the things that seemed impossible initially. Thousands of hours of brain-storming discussion and latenight co-debugging sessions with Jose make this thesis possible.

I would also like to thank Professor Cormac Flanagan and Professor Scott Beamer for accepting to review and providing valuable feedback for both my advancement and thesis work. This thesis wouldn't have been complete without their input.

Special thanks to my labmate Rafael, who gives me a warm hand at the beginning of my Ph.D. I will never forget how he patiently explained the codebase structures, gave valuable suggestions on doing the research, and how he helped on revising our co-authored papers even when he graduated.

Last, I would like to thank my wife, Rachel; she took most of the child-caring during these 5 years; without her push and support, I would definitely need to spend at least 2 more years finishing the PhD. Also, thank my daughter, Julie. You can't imagine how a 1-year baby girl could sit quietly and watch her dad read the paper and type code for the whole night; she's my sweet angel. Thanks to my son, Gary, who lightens my life and brings even more joy and laughs to my home.

# Chapter 1

# Introduction

A resurgence in hardware accelerators is thriving with the continued power and performance scaling and the emergence of new specialized domains, such as Machine Learning. This trend is shown in the latest systems like Apple M1/M2, Qualcomm Snapdragon, and AMD/Xilinx FPGA. These systems are usually equipped with a dedicated Neural Engine to process AI applications. The enormous potential market for AI processors also encourages hundreds of new hardware startups to design novel AI chips, such as Groq, Tenstorrent, Esperanto, and many others. However, the current hardware development flow contrast with agile methods that became popular in modern software development. In industry, there is a notorious problem that hardware designers have to wait days or even weeks for the time-consuming EDA compilation flow to be finished.

The lengthy EDA compilation consists of source code elaboration, logic synthesis, placement & routing (P&R), and timing analysis and modifications. Each phase may need to perform circuit simulation to guarantee the behavior works correctly. Usually, designers have to go through several iterations of the entire EDA flow to optimize the circuit and meet timing closure.

The elaboration step translates the source code into the EDA tool's internal intermediate representation (IR). When the input HDL is Verilog, the source code elaboration usually takes a small portion of the time. However, when it comes to modern high-level HDLs, the 'elaboration' step refers to HDL compilation. Due to the more significant level of expressiveness, new HDLs like Chisel3/FIRRTL [15,45], PyRTL [24], and Pyrope [76] have garnered much interest since they make it easier to describe hardware. Each new HDL has a unique compiler that produces Verilog output from the high-level code. Thus, Verilog is frequently referred to as the assembly code output in software language compilers. This also means that the traditional elaboration step now consists of nearly the whole compilation stack as in software languages. The highlevel semantic HDL code has to go through a complex compilation stack, which adds non-trivial time to the original EDA flows and makes the EDA flow even lengthier.

To address the long-standing problem of slow EDA compilation time, our group has built several 'live' hardware synthesis techniques, such as LiveSynth [70], SMatch [71], and LiveSim [78] to target logic synthesis, P&R, and simulation, respectively. When a baseline result has firstly been produced, and the designer decides to modify a small portion of front-end source code, these 'live' techniques could help to perform an incremental compilation and get a new design output within a few seconds.

Nevertheless, the designer still has to wait for a slow initial baseline compila-

tion before taking advantage of the 'live' techniques. This prerequisite hinders the designer's productivity harshly and is the core research topic that this dissertation wants to address.

Compilation infrastructures carefully tuned for speed is a crucial step for building a fast and incremental EDA compilation flow. Some facts affect the compilation time. The first is the parallel compilation scheme and scalability to address the sea of modules in a SoC. The second is the IR iteration time which directly affects the algorithm performance of a compiler pass. The third is to avoid unnecessary re-parsing between compilation steps. Besides focusing on the speed metric, some other features are also essential for an excellent hardware IR. For example, the IR iterator should be able to traverse through the whole design hierarchy without flattening the entire design. The IR data model should prevent code duplication among passes. The IR should be generic enough and provide friendly APIs for integrating other third-party tools. In this dissertation, I propose LiveHD, a new hardware development framework, to be the compilation infrastructure. LiveHD provides fast HDL and EDA compilation speed and serves as a common database to integrate with novel hardware compilation passes, such as the 'live' techniques and the other open source tools [43, 44, 80].

LiveHD is built on top of a graph structure called LGraph (Live Graph) [69, 84]. LGraph is a sparse graph representation that serves as a design database and is carefully crafted for incremental live hardware development. LGraph is an LLVM-like infrastructure of hardware design tools, representing large-scale designs in different VLSI phases. It aims to provide incremental elaboration, synthesis, and simulation. LGraph is carefully crafted with a minimal number of IR node type; the limited node types could reduce the compiler passes design and time complexity.

Though LGraph provides many excellent features as a hardware compiler infrastructure, it is essentially a low-level graph IR, making it hard to interface directly with modern HDLs. Modern HDLs usually define high-level semantics such as aggregate types and circuit attributes. In order to enable multiple HDLs to leverage the fast compilation that LiveHD provides, I introduce a new high-level IR called LNAST (for Language Neutral AST). The LNAST IR is the standard interface that allows easy translation of new languages to LiveHD. By targeting LNAST instead of LGraph, the language designer does not need to worry about SSA, control-flow conversion, variable scopes, and many other constructs shared by most languages. In a way, LNAST is more accessible to translate to because it has a control flow with several operations.

The IR design is a critical component in compiler development [53, 54]. It is common practice for a compiler tool stack to have multiple layers of IR, ranging from high-level to low-level representations. An excellent high-level IR has simple semantics to express the high-level source language and hides details about the language syntax to the back-end compiler stack. It must be independent of the front-end programming language and leverage shared code optimization. In the new LiveHD model, we can view LNAST as a tree-like high-level IR and LGraph as a graph-like low-level IR.

Nowadays, hardware designers need to integrate thousands of modules into a deep design hierarchy that constitutes a modern SoC. Even more challenging, many hardware tools lack scalable or parallel compilation steps that software compilers have. On the other hand, the enormous module instances in a SoC provide an opportunity for boosting the compilation throughput from a parallelized compiler. In this thesis, I further proposed a new multi-threaded and high scalability compilation scheme in the LiveHD framework. Furthermore, the parallelized mechanism is suitable for multiple HDLs.

In summary, the main contributions in this dissertation are:

- a low-level LGraph IR for fast HDL compilation, synthesis, simulation, and interfacing other tools

- a high-level LNAST IR to bridge different HDLs into LiveHD.

- implementing many hardware-specific compiler passes based on LNAST and LGraph IR, and precious lessons learned about hardware compiler design exploration among passes and IRs.

- a generic and parallelized compilation scheme capable of compiling multiple HDLs front-end.

Multiple communities will benefit from LiveHD. Developers of new HDLs can map to LNAST and leverage the existing compiler infrastructure. Physical design groups can integrate into LGraph to provide support for different front-end languages and to evaluate integration with other steps, moving beyond simple benchmarks regularly used for specific steps in physical design. RTL circuit designers can use the integrated open-source flow, which provides a shallow entry-level barrier, instead of spending time integrating tools from different domains. We see LiveHD as the LLVMlike system in hardware design since it provides a convergence point for both language developers and back-end engineers. Users can access the open-sourced LiveHD project code base at [41].

The remainder of this dissertation is organized as follows to discuss how the proposed LNAST-IR, LGraph-IR, and parallelized LiveHD framework boost compilation throughput for multi-HDLs:

Chapter 2 takes a quick overview of the internal steps of the LiveHD framework and discusses the language abstractions and IR choices.

Chapter 3 takes a quick overview of the 'live' synthesis and simulation techniques that have been published that will be an excellent complement for our proposed fast multi-threaded HDL compilation framework. I then introduce important related works, including hardware and software IR designs, and other hardware compilation framework that shares the same goal of LiveHD goal to be a generic development framework for hardware language compilation and tool development.

Chapter 4 discusses work done for the low-level LGraph IR. Critical features of LGraph include a unified data model and API, a fast memory mapped library design, integration with third-party tools, and hierarchical design traversal for third-party tools. I further explain some of the compilation pass implementations based on LGraph. Some more depth IR design considerations for hardware are also discussed in this chapter.

Then, Chapter 5 presents our high-level LNAST IR. LNAST offers one main

benefit to the LiveHD framework. It acts as a bridge for the LiveHD flow to interface with different HDLs at the front end. By targeting LNAST instead of LGraph, the language designer does not need to worry about SSA, control flows conversion, variable scopes, and many other constructs shared by most languages. This chapter will also discuss the passes implemented on LNAST.

In Chapter 6, I propose a new design to parallelized LiveHD framework. I demonstrate how LiveHD can extract a dependency tree during the IR lowering process. Then I illustrate how to turn each pass into either a fully-parallelized or bottom-up parallelized mechanism based on the dependency tree relations. I then explain the special care that needs to be taken for different front-end HDLs.

Finally, I provide my final thoughts on Chapter 7 and talk about potential future open research projects that this work could inspire. In my Ph.D. journey, I also have collaboratively work on other projects that are not discussed in the thesis. I codesigned the semantics and syntax of the new Pyrope HDL, along with the LiveHD framework. I also participated in several exciting research prototypes with LiveHD, including leveraging LiveHD's multi-languages code generation ability [40] to increase the compiler testing coverage.

# Chapter 2

# **LiveHD Overview**

This chapter gives a concise summary of the steps that occur internally within the LiveHD framework. It also discusses the language abstraction and IR options available.

### 2.1 HDL Support Choice

Verilog is the language that is considered to be the industry standard, and Chisel3 is the most widely used modern alternative to Verilog. Therefore, it was apparent in the early design process that LiveHD would need to support both languages. LiveHD also supports Pyrope, an HDL still in development that already has features like the global inference that affect the compile design options. Because we want LiveHD to support the full Verilog 2001 language and some SystemVerilog features, the compiler needs to pay attention to many details. LiveHD can directly interface Verilog and Chisel3 generated code at compile time. This allows for optimizations to be performed across modules.

LiveHD uses Slang [8] to parse Verilog. Even non-synthesizable constructs like classes are no problem for Slang, which can handle most of SystemVerilog. The synthesizable subset is the only one LiveHD will accept. When it comes to Chisel3 [15], LiveHD accepts CHIRRTL, which is comparable to the FIRRTL [45] but is directly produced by Chisel3. The original Scala-FIRRTL [45] compiler will accept the same CHIRRTL before each of the various lowering steps that are performed within FIRRTL. A specialized parser is implemented in LiveHD to handle Pyrope.

### 2.2 Hardware IR Choice

LiveHD has two internal IRs, LNAST [85] and LGraph [84]. The LNAST and the LGraph internal IRs have their own associated data structures in LiveHD. LNAST is a control flow language-neutral intermediate representation that maintains the control flow. LNAST can be derived from any of the three different HDLs. Compared to IRs produced by non-hardware compilers, LNAST is somewhere between the HIR and MIR produced by Rust [11], or it is closer to the AST than the IR used in LLVM [54]. LGraph is a form of graph representation more analogous to a hardware netlist. There is a lowering or translation step from LNAST to LGraph.

Internally, LNAST is equipped with a Static Single Assignment (SSA) [27] pass that is able to enable its very own compiler optimization steps. However, for the purposes of this particular piece of research, the most crucial function of LNAST is to handle all control flow structures properly before it generates an LGraph.

HDL-specific passes, such as bitwidth inference and code optimization, are included in LGraph. Even though it is possible to complete some of the steps in LNAST, the design process can be made much simpler using LGraph's various traversal algorithms, such as topological sort.

### 2.3 LiveHD Overview

Figure 2.1: Overview of LiveHD compilation flow and comparisons between Yosys and Chisel3/FIRRTL compilers.

The high-level structure of the LiveHD compiler is illustrated in Figure 2.1. Currently, the front end of LiveHD is capable of compiling three different HDLs. These HDLs are FIRRTL, Pyrope, and Verilog. As an example, prp-AST was generated by our very own Pyrope parser, sv AST was generated using Slang [8], and Chir.pb was generated using Protocol 10 Buffers [4].

Every language has a unique pass responsible for translating its internal AST to the LNAST-IR. After entering LNAST, the internal data for all three languages becomes identical. Because LNAST is the target structure, the language designer does not have to be concerned with SSA, the conversion of control flows, variable scopes, or any of the other numerous constructs common to most languages. The fact that the input is not required to be in SSA form by LNAST is because LNAST itself is internally equipped with an SSA transformation. Thus, targeting LNAST relieves language designers' efforts.

LNAST does not have language-specific nodes. On the contrary, it makes it possible to create function calls to black-boxed modules whenever required. This is taken advantage of by the FIRRTL pass, which transforms a FIRRTL operation into a function call to an LNAST node of blackbox. It is a different approach to MLIR [55] that involves the creation of dialect for custom nodes. The LNAST approach allows custom passes for each language while enabling each compiler pass to handle semantics appropriately.

The front-end design will be represented as LGraph when translated from LNAST. An LNAST node can require multiple LGraph nodes. LGraph makes use of the majority of the LiveHD compilation passes in order to generate optimized Verilog output. These compilation passes include copy-propagation, constant folding, peephole optimization, and bitwidth inference. A hierarchical graph is the key characteristic of LGraph. We refer to a graph

as hierarchical when it can point to other graphs. There are many different constructs,

such as hierarchical iterators that can be used to manage graphs.

# 2.4 Clarification

LiveHD is a large project that many students have collaborated and contributed

to together. The specific contributions made in this thesis are summarized in Table 2.1.

Table 2.1 Detailed contributions from the author

| item                                                                                                                                                               | comments                                           |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| Parallelized LiveHD                                                                                                                                                | main designer                                      |  |  |  |

| End-to-end Pyrope compilation flow                                                                                                                                 | main designer except the parser <sup>1</sup>       |  |  |  |

| End-to-end FIRRTL compilation flow                                                                                                                                 | main designer                                      |  |  |  |

| End-to-end Verilog compilation flow                                                                                                                                | collaboration <sup>2</sup>                         |  |  |  |

| LNAST IR infrastructure                                                                                                                                            | main designer with high collaboration $^3$         |  |  |  |

| LGraph IR infrastructure                                                                                                                                           | collaboration <sup>4</sup>                         |  |  |  |

| FIRRTL to LNAST                                                                                                                                                    | main designer with high collaboration $^5$         |  |  |  |

| LNAST SSA transformation                                                                                                                                           | main designer                                      |  |  |  |

| LNAST to LGraph pass                                                                                                                                               | main designer                                      |  |  |  |

| Cprop pass                                                                                                                                                         | main designer with high collaboration <sup>6</sup> |  |  |  |

| FIRRTL bit analysis pass                                                                                                                                           | main designer                                      |  |  |  |

| FIRRTL map pass                                                                                                                                                    | main designer                                      |  |  |  |

| Bitwidth inference pass                                                                                                                                            | main designer with high collaboration <sup>7</sup> |  |  |  |

| LGraph Mockturtle integration                                                                                                                                      | collaboration <sup>8</sup>                         |  |  |  |

| <ul> <li><sup>1</sup> Pyrope parser is designed by Kenneth Mayer, a MS student alumni</li> <li><sup>2</sup> Verilog parser is maintained by Prof. Renau</li> </ul> |                                                    |  |  |  |

<sup>3</sup> co-develop the LNAST interfaces and the tree library with Prof. Renau

<sup>4</sup> co-develop the LGraph interfaces and the graph library with Prof. Renau

<sup>6</sup> co-develop with Prof. Renau to handle tuple structure

<sup>7</sup> the initial prototype is also designed by Hunter Coffman; I and Prof. Renau keep improve the codebase

<sup>8</sup> the initial prototype is designed by Qian Chen; I continue the design and perform the benchmarking

<sup>&</sup>lt;sup>5</sup> the intitial prototype that interfaces hi-FIRRTL is designed by Hunter Coffman, a MS student alumni; I continue his work but re-design most part of the codebase to handle CHIRRTL, the highest format of FIRRTL

# **Chapter 3**

# **Related Work**

First, this section will discuss the live programming techniques that intrigue our interest in starting the LiveHD research concept. After that, I discuss the IR designs and frameworks relevant to software and hardware communities.

## 3.1 Live Techniques in LiveHD

Unlike hardware development, software development is much more agile than Hardware design. For example, a trivial change in a large software project like the Linux kernel requires less than one minute to recompile incrementally. More recently, Live programming has received much attention in the software community. In Live programming, developers can see the output from their code change immediately as if the program is always running. Faster feedback leads to a more productive and less frustrating development experience [28]. A couple of seconds is the recommended [28] value to have a *responsive user* interaction. As a complementary perspective of this thesis, the ultimate goal for LiveHD is building an interactive hardware design experience, much like live programming, by providing feedback within a few seconds. This is possible by applying three principles for incremental hardware design: (1) divide the job into partition regions or check-points; (2) incrementally transform these partition regions where the code change happens; and (3) hot-reload the partition regions into a running program without restarting.

Three main live programming techniques in LiveHD have been proposed, including LiveSynth [70], SMatch [71], and LiveSim [78]. These tasks are designed under the three incremental principles. They only handle the sub-jobs related to the code change, then merge results into the background program without re-running from the beginning. LiveSynth focuses on logic synthesis, and SMatch performs P&R for FPGA. LiveSim is our live simulator.

These research prototypes still have two substantial problems. Before moving on to the incremental phase, the baseline synthesis or simulation must be completed for any of these live techniques to even be considered. However, waiting for these protracted baseline compilations eliminates the incremental phase's benefits. In addition, all the prototypes can only accept the low-level Verilog as inputs, despite highlevel HDLs becoming increasingly widespread. Even if the high-level HDLs are used, their elaboration/compilation times are no longer negligible. Throughout this thesis, LiveHD will devise a parallelized compilation strategy in addition to two new fast IRs to address these concerns. After that, the brand-new LiveHD framework will be able to compile new high-level HDLs rapidly and further enable fast-baseline circuit synthesis and simulation for future research.

### 3.2 Hardware Description Language Compilers and IRs

HDL compilation, hardware IR design, and tools have recently been a research hotspot in the open-source community [2, 3, 10, 12, 16, 24, 29, 45, 47, 50, 58–60, 63, 64, 67, 73, 75, 76, 79, 83, 89]. Nonetheless, most proposed works are tightly knit to their source language, and compilation speed is not the priority. On the other hand, several software languages compiler have evolved toward parallelism or multi-language support.

#### Yosys

Yosys [89] is a framework for register-transfer-level (RTL) synthesis. It takes Verilog-2005 as the input and converts it to its internal RTLIL [89] IR through a Verilog Abstract Syntax Tree (v-AST in Figure 2.1). RTLIL cannot represent high-level HDL constructs like *tuple* or *vector*. Several front-end passes are needed in Yosys to translate the initial Verilog AST to RTLIL and further down to a more netlist-like construct through the *proc* and *opt* steps. Yosys compilation is sequential, and these front-end passes are not trivial and could easily take Yosys minutes when compiling large designs.

#### Scala-FIRRTL

FIRRTL is the IR in Chisel3 [15]. The first FIRRTL compiler is implemented in Scala [65](Scala-FIRRTL). A front-end Chisel3 compiler produces CHIRRTL as the input for the ScalaFIRRTL compiler (Figure 2.1). The Scala-FIRRTL compiler is not designed for compiling languages other than Chisel3/FIRRTL. Moreover, due to the AST-centric and non-SSA representation of FIRRTL, it is not easy to find use-def chains for a variable. Multiple tree iterations must be performed to build the data structures for AST transformations. The long tree traversal time, together with sequential compilation in Scala-FIRRTL, is a problem for large digital designs.

#### CIRCT-FIRRTL

CIRCT [10,32] is a new experimental hardware IR extended from MLIR [55] and LLVM [54] communities. CIRCT framework shares the same ideas as LiveHD, i.e., to be the unified hardware development center. Theoretically, it is possible to compile multiple languages through interfacing various front-end MLIR dialects designed in CIRCT. Right now, the CIRCT-FIRRTL flow (Figure 2.1) is concurrently developed with LiveHD, with a focus on FIRRTL input.

#### Other HDL IRs and compilers

LLHD [73] and CoreIR [60] are IRs aiming to be the generic hardware representation for the RTL abstraction level. LLHD is a statically-typed hardware IR designed to capture SystemVerilog. In LLHD, the bitwidth of variables must be explicitly defined. Thus it cannot be easily interfaced with modern HDLs, which only set bitwidth on the modules' I/O. In CoreIR, input HDLs like Halide [72] and Verilog are now supported, and the compilation speed is not the main concern. Furthermore, before mapping to these two IRs, extra bitwidth analysis passes are required to map HDLs' bits-centric operators. Several works [9, 20, 52, 59, 62, 63, 75] have been proposed to handle the HLS abstraction. Generally, the higher abstraction offers more freedom for expressive syntaxes. However, it usually puts more burden on the compiler to reason about the relationship between high-level code and the generated circuit. Also, in terms of multilanguage compilation ability, these HLS projects cannot compile Verilog source. Thus, they lose the opportunity to reuse and optimize Verilog designs.

Some IRs are designed specifically for back-end EDA tool development. In the commercial world, OpenAccess (OA) is an "open" format meant to provide interoperability among IC design tools. Ironically, OA requires signing NDAs that limit its usage. The other commercial option is MilkyWay from SynopsysTM. However, since this is a proprietary format from Synopsys, not much can be said about it. The commercial nature of both options makes them hard to adopt for academic research. The OpenRoad [50] project tries to build a machine-learning-driven automatic RTL-to-GDS flow in the open-source community without human interference. Several open-source projects aim to leverage Python as the host to build new HDL and the corresponding compilers. Representative works are PyMTL and Mamba [47,58], Magma [3], and My-HDL [29]. Rsyn [34] and Ophidian [35] are two open-source frameworks for physical design. They provide an extensible infrastructure that allows users to leverage existing code and focus on new algorithms and tasks.

# 3.3 Software Programming Language Compilers

Several software frameworks have similar design concept as LiveHD in terms of parallelism and multi-language support.

#### **Parallel compilation**

The two widely used C/C++ compilation frameworks, GCC [81] and LLVM [54] mostly rely on the build system such as Makefile to achieve file-level compilation parallelism. Few of the LLVM internal passes like the linker can also be parallelized.

Several research works have been recently proposed improving the compilation parallelism. The challenges of increasing scalability for Git and GCC applications are discussed in the research work by Bernardino et al. [18]. The parallel GCC project [17] also aims to conduct a multi-threaded compilation on the intra-procedure optimizations in GCC. Researchers in [38,48] have been working on getting higher parallelism in the link time optimization (LTO) stage. In Lighting Bolt [66], the authors discuss how they design the parallel mechanism to improve the performance of the binary optimization pass.

Elixir [33] is a functional language that also focuses on constructing highly scalable applications. The internal framework launches multiple compilers to handle separate files simultaneously. When a function dependency bottleneck occurs, the framework sends *waiting signals* to the dependent caller-compiler and pauses until the dependency is resolved.

#### Multi-language support

GraalVM [31,87] is a Java virtual machine framework that bridges multiple languages by using Truffle [39] as the front-end IR. They are analogous to the LiveHD compiler and its front-end IR, LNAST [85]. The AST of several languages is mapped to the common Truffle AST in this framework. A series of back-end GraalVM optimizations like tree rewriting and just-in-time(JIT) compiling are applied to the common Truffle AST. Click and Paleczny [23] present a graph-based SSA intermediate representation to express optimization elegantly. The Common Intermediate Language (CIL) [61] is used in the .NET system, and it is also an IR designed for multiple languages such as C# and Basic.

# **Chapter 4**

# LGraph: A Unified Low-level Graph-IR for Productive Hardware Design

In the first part of this chapter, the discussion focuses on the essential aspects of LGraph IR that were created with the development of hardware compilation tools in mind. This chapter also reviews the considerations regarding the IR design of LGraph's hardware. Additionally, some integration prototypes for third-party tools are presented. In the final part of this chapter, a lesson learned from the LiveHD development is reported, a fast but deprecated memory-mapped library. The memorymapped library and the LGraph-Mockturtle are assessed to know how well the integration works together.

# 4.1 Introduction

Specialized hardware accelerators provide extra performance, power, and area in multiple areas in the post-Moore's law era. A new momentum of hardware design innovation would come from open-source EDA tools and highly productive hardware design flows. Hardware designers want a fast design flow to iterate between synthesis and its analysis. EDA tool developers, in particular from the open-source community, want to work with a common model and API to focus on the tool's algorithm development.

Ideally, a productive hardware design flow should have a very short design iteration period. This helps designers quickly implement the new design idea based on the feedback from an interactive environment. Whereas, in a traditional design flow, it is common for designers to wait for hours or even days to obtain the design result.

Open-source EDA tools also play a vital role in hardware innovation as fellow researchers and hardware developers could contribute their novelty without facing licensing constraints. In recent years, research work such as DATC [49], qflow [5], VTR [74] and OpenROAD [50] focus on integrating tools of different design stages into a single RTL-to-GDSII flow. Some of the single-stage tools are ABC [19], Mockturtle [80], and Yosys [89] for logic synthesis, OpenTimer [43, 44], OpenSTA [46] for static timing analysis, RePlAce [22] and NTUPlace3 [21] for placement and NCTU-GR [57] and TritonRoute [51] for routing; Verilator [79], LiveSim [78], and Essent [16,67] for simulation.

These works on integrating open-source tools have shown the potential to

build a tapeout-ready flow. Despite the correctness of these design flows, they are still far from ideal. One crucial source of issues is the lack of a common data model and APIs. Individual tools are developed using different data structures, which raises the integration difficulty. Moreover, tools not developed using a common data model end up replicating code and efforts. For example, almost every tool implements its own netlist parser. This code replication further causes a non-negligible portion of the flow execution time. To make matters worse, not all tools implement standards equally, causing compatibility issues.

Several sources for the slow hardware compilation flow include design elaboration, logic synthesis, timing analysis, placement, and routing. State-of-art incremental technique like LiveSynth [70] and SMatch [71] have been applied to provide an interactive experience but are limited to synthesis. However, EDA tools are IO-heavy applications. Re-parsing netlists or libraries to the tools' internal data structure adds much to the flow's run time. As mentioned in [69], it would take Yosys [89] tens of seconds to parse a reasonably large RTL file, which leads to a less productive design experience. The situation worsens when the project goes into debug or optimization phase. Although changes applied in multiple flow iterations are small, designers must repeatedly wait for the same re-parsing time.

Performing design synthesis and static timing analysis in a hierarchical manner is essential for productivity in the hardware design flow. However, as mentioned in [36], most open-source logic synthesis and STA tools such as OpenTimer, Mockturtle, and ABC lack hierarchical design support as compared to industrial tools. In order to optimize the whole design, the designer must flatten the hierarchical design and then feed it to these tools. However, physically flattening every submodule during the logic synthesis phase would increase the complexity of the back-end physical synthesis. Furthermore even if each tool implements the hierarchical feature, the insidious code replication among these tools still violates the DRY (do not repeat yourself) principle in software development.

In this chapter, I present Live Graph(LGraph), our attempt to build an infrastructure for productive hardware design flow. The following are the highlighted key features of the LGraph-IR:

#### Unified data model/API

LGraph has a unified data model and API in C++17 for digital circuits. LGraph is meant to represent netlists in different phases of the design flow from RTL to layout, including simulation and code generation. The easy-to-use APIs vastly reduce the design effort of tool developers. More importantly, the nature of the unified data model prevent possible code duplication and avoids parsing and generating the netlist between the internal stages of the RTL-to-GDSII flow.

### Hierarchical design traversal

The hierarchical cross-module traversal ability of LGraph empowers the integrated third-party tools to run the core algorithm in a virtually flattened form. Therefore, LGraph could implicitly achieve global optimization without affecting the physical design phase.

#### Third-party tool integration

LGraph is currently being integrated with some open-source tools such as Mockturtle, OpenTimer, and Yosys. Open-source EDA tool developers could leverage LGraph's succinct API and generic data structures to implement their algorithms. Alternatively, they can leverage other integrated third-party tools to complete the design flow together.

# 4.2 LGraph-IR Construction and Traversal

### 4.2.1 Node, Pin, and Edge Construction

A single LGraph represents a single netlist module. LGraph comprises nodes, node\_pins, edges, and tables of attributes. An LGraph node is affiliated with a node\_type, and each type defines different amounts of input and output node\_pins. For example, a node can have three input pins and two output pins. Each of the IO pins can have many edges to other graph nodes. Every node\_pin has an affiliated node\_pid. A pair of a driver\_pin and a sink\_pin constitute an edge. In the API example in List 4.1, an edge is connected from a driver\_pin (pid1) to a sink\_pin (pid3). The bitwidth of the driver\_pin determines the edge bitwidth.

```

auto node = lg->create_node(Node_Type_Op);

auto dpin = node.setup_driver_pin(1);

dpin.set_bits(8);

auto spin = node2.setup_sink_pin(3);

dpin.connect(spin);

```

Listing 4.1: Selected API examples for LGraph construction

## 4.2.2 LGraph Traversal

LGraph is a bidirectional graph representation supporting topological sort traversal in an input-forward and output-backward manner. If the order in which nodes are visited does not matter for the algorithm, developers can choose the fast iterator, which will visit the next node in the cache line. Besides nodes iteration, LGraph also provides an API for visiting each input and output edges of a node.

```

1 // unordered but very fast traversal

2 for (const auto &node:lg->fast()) {...}

3

4 // propagates forward from each input/constant

5 for (const auto &node:lg->forward()) {...}

6

7 // propagates backward from each output

8 for (const auto &node:lg->backward()) {...}

```

Listing 4.2: API examples for LGraph traversal

for (const auto &inp\_edge : node.inp\_edges()) {...}

for (const auto &out\_edge : node.out\_edges()) {...}

Listing 4.3: API examples for edge iteration of a node in LGraph

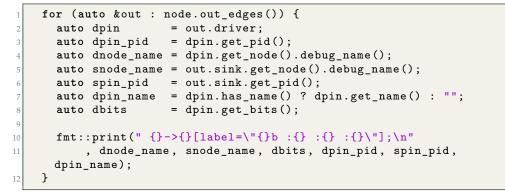

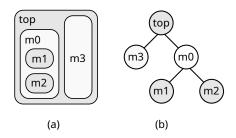

Figure 4.1: A hierarchical LGraph. A sub-graph node is a sub-module instantiation. The hierarchical traversal will walk into the subgraph structure.

Figure 4.2: The tree hierarchical view for Figure 4.1. Each instantiation has a unique hid and hierarchical attribute table.

LGraph supports hierarchical traversal. Each sub-module of a hierarchical design will be transformed into a new LGraph and represented as a sub-graph node in the parent module, as shown in Figure 4.1. Suppose a hierarchical traversal is used when the iterator encounters a sub-graph node, it will load the persistent tables of the subgraph to the memory and traverse the sub-graph recursively, ignoring the sub-graph input/outputs. This cross-module traversal treats the hierarchical netlist just like a flattened design. In this way, all integrated third-party tools can automatically achieve global design optimization or analysis by leveraging the LGraph hierarchical traversal feature.

for (const auto &node:lg->forward\_hier()) {...}

Listing 4.5: API example for LGraph hierarchical traversal

## 4.3 LGraph-IR Characteristics

Several important characteristics when designing LGraph-IR are discussed in this section. I also provide a comparison summary between LGraph/LiveHD and other related tools in Table 4.2.

## 4.3.1 SSA Graph

LGraph has an SSA representation, but others such as Yosys' internals do not. The term "SSA-graph" refers to a wire or network that has a driver from a single source. The SSA representation has been demonstrated to be very useful in conventional compilers for the purpose of simplifying passes. Pointers do not exist in hardware, and loops are used very infrequently, making the SSA an even more interesting concept.

#### 4.3.2 Reduced Logic Instruction Set (RLIS) Cells

Logic cell need different graph nodes to represent functionality. Most EDA tools have many logic cells or gate options. While some cells are commonly used, such as *add*, *subtract*, *concatenate wires*, *pick bits*, *one\_hot\_encoding*, many cells are only created for a specific function. Yosys has over 100 types, XLS has 60, and FIRRTL 37. LGraph logic cells have been designed to reduce the number of gates. In a way, it tries to be a Reduced Instruction Set Logic (RLIS). It is similar to that RISC is a reduced instruction set vs. CISC. The goal has been to have the smallest amount of cells covering all the options without the overhead. The reason for choosing the RLIS philosophy is to reduce the design complexity of passes and optimizations on the IR. Table 4.1 summarizes the carefully crafted RLIS LGraph operators.

#### 4.3.3 N-ary Gates

LGraph logic cells are n-ary (see Table 4.1). N-ary means that cells like *or* or *add* can have an unlimited number of inputs. This allows for simpler graphs and easier optimizations because there is no need to have a chain of operators representing the same functionality.

| 1          | 1 7                                        |

|------------|--------------------------------------------|

| Operator   | Functionality                              |

| Const      | constant number or strings                 |

| Sum        | summation of n-inputs                      |

| Mult       | multiplication of n-inputs                 |

| Div        | division of 2-inputs                       |

| And        | and-gate with n-inputs                     |

| Or         | or-gate with n-inputs                      |

| Xor        | xor-gate with n-inputs                     |

| Ror        | reduced-or-gate with n-inputs              |

| Not        | bitwise not operation                      |

| Get_mask   | get signed value from a given bit position |

| Set_mask   | turn a node from unsigned to signed        |

| Sext       | signed extend from a given bit position    |

| $LT^1$     | less than operation                        |

| $GT^2$     | greater than operation                     |

| $EQ^3$     | equal to operation                         |

| SHL        | logical shift left                         |

| SRA        | arithmetic shift right                     |

| LUT        | look-up table in FPGA                      |

| Mux        | n-to-1 multiplexer                         |

| IO         | Graph input or output                      |

| Memory     | models variant memory types <sup>4</sup>   |

| Flop       | models variant flop types <sup>5</sup>     |

| Latch      | models Latch gate                          |

| Fflop      | models fluid-pipeline flop [68]            |

| Sub        | models submodule and function-call         |

| TupAdd     | add a field to high-level tuple struct     |

| TupGet     | get a field from high-level tuple struct   |

| AttrSet    | set a attribute to a variable              |

| AttrGet    | get a attribute from variable              |

| CompileErr | indicate a compile error during a pass     |

| motor 1    |                                            |

**Table 4.1** The reduced number of operator types in LGraph are designed to simplify the compilation complexity

**note:** <sup>1</sup> greater-or-equals-to operation could be represented as !LT, <sup>2</sup> less-or-equals-to operation could be represented as !GT, <sup>3</sup> not-equals-to operation could be represented as !EQ <sup>4</sup> provides an interface to model memory like combinational/sequential read, also accepts and generates high-level memory data struct <sup>5</sup> provides an interface to model flops like asynchronous/synchronous reset, positve/negative edge reset, and reset initialization value.

### 4.3.4 Signed Wires

Most EDA flows have to deal with signed and unsigned wires. In a flow like Yosys, logic cells behave differently with signed and unsigned inputs/outputs. This separation adds even more complexity to the logic cells. In FIRRTL, most of the 37 existing cells also have different behavior regarding cell inputs' signedness. However, signed representation is indeed a superset of unsigned. If the flow supports signed, there is no reason to support unsigned. Choosing a unified signed representation leads to less design overhead (positive values in an unsigned result have the upper bit zero). For example, the bitwidth inference pass no longer needs to differentiate a cell's different input signedness.

Compilations in the proposed signed representation require one extra bit in the LGraph IR. A design module can be broadly categorized into (1) internal logic and (2) IO. LiveHD implements a *bitwidth* pass that calculates each variable's max/min value (gate). Suppose the min value of a variable is always larger or equivalent to zero, and this variable is semantically unsigned. In this case, the *verilog\_gen* pass will generate an unsigned Verilog syntax when the variable is an internal logic (case-I). For a design module, if all the internal logic has a positive minimum value, then all the internal logic will generate unsigned Verilog statements. In this scenario, there is no overhead from LiveHD's universal signed representation for the module's internal logic. On the other hand, if a module's internal logic has a negative minimum value from the *bitwidth* pass, there will be an extra signed bit overhead on the generated Verilog, and we have to rely on the synthesis tools to find pruning opportunities.

The interesting part is the IO. Theoretically, we can also generate unsigned IOs when the min value is positive, which will be the most common case in other CAD tools. Currently, our *verilog\_gen* pass will always generate signed IOs. This is because we plan to interface with other LiveHD passes in the future, and those future passes will also be universally signed. This design choice will save us a lot of development effort in the future. These extra signed 1-bits on the IOs produce extra overhead, but they could be potentially optimized away from synthesis tools. In fact, the future LiveHD will integrate synthesis tools, and global analysis and synthesis steps will take care of this overhead from the LiveHD front-end compilation.

## 4.3.5 Wire Width Semantics

LGraph wires are designed to be always signed, but maybe equally interesting, the cell semantics are independent of the wire widths. This means that a gate-like *concatenate* is not allowed because it is wire width dependent. We make this design choice because even if the designer specifies a 'maximum' number of bits to a wire, the tool should be allowed to optimize the wire's bitwidth. This already happens in synthesis tools that can simplify away wires. LiveHD brings the same concept/ideas to LGraph.

#### 4.3.6 Bitwidth Inference

Verilog specifies the bitwidths for each wire. Other modern HDLs like Chisel [15] or Pyrope [76] have a different bitwidth semantic depending on the operators. For these

## **Table 4.2** Capability comparison between relevant tools

|                         | Losyskey | FIRRTL 451          | relativ                  | L.F.              | Vert (13)  | ilator (791       | LERGY (1101       | oon Liveth                                                               |

|-------------------------|----------|---------------------|--------------------------|-------------------|------------|-------------------|-------------------|--------------------------------------------------------------------------|

| HDLs                    | Verilog  | FIRRTL <sup>0</sup> | C++<br>DSLX <sup>1</sup> | Verilog<br>Halide | $SV^{2,3}$ | SV                | FIRRTL            | Verilog<br>SV <sup>4</sup><br>FIRRTL <sup>0</sup><br>Pyrope <sup>5</sup> |

| Cell Types              | >100     | ~37                 | ~60                      | ~40               | ~60        | >100 <sup>6</sup> | >100 <sup>a</sup> | 31                                                                       |

| Aggr. Type <sup>7</sup> | no       | yes                 | yes                      | yes               | yes        | yes               | yes               | yes                                                                      |

| Signedness              | $S/U^8$  | S/U                 | S/U                      | S/U               | S/U        | S/U               | S/U               | S                                                                        |

| N-ary Gate              | no       | no                  | yes                      | no                | no         | no                | yes               | yes                                                                      |

| Global Inf <sup>9</sup> | no       | no                  | no                       | no                | no         | no                | yes               | yes                                                                      |

| Formal                  | yes      | yes                 | yes                      | yes               | no         | no                | no                | no                                                                       |

| Simulation              | yes      | yes                 | yes                      | no                | yes        | yes               | yes               | yes                                                                      |

| Synthesis               | yes      | no                  | no                       | no                | todo       | no                | no                | yes                                                                      |

| FPGA                    | yes      | no                  | no                       | no                | no         | no                | yes               | yes                                                                      |

<sup>0</sup> highest format, CHIRRTL

<sup>1</sup> Google's high-level synthesis language

<sup>2</sup> SystemVerilog

<sup>3</sup> At the time of writing, SystemVerilog is implemented

<sup>4</sup> we integrate Slang [8] to bridge SystemVerilog

<sup>5</sup> Pyrope <sup>6</sup> includes many simulation-only constructs

<sup>7</sup> High-level aggregate types like tuple, vector <sup>8</sup> Signed/Unsigned

<sup>9</sup> Clobal types in force as

<sup>9</sup> Global type inference

<sup>*a*</sup> summation of all dialect CIRCT included

languages, the flow can not know all the bitwidths at the elaboration phase; a bitwidth analysis must be performed to gain knowledge of each gate's bit size before code generation. LiveHD has been designed to allow the generic bitwidth inference for every HDLs.

## 4.3.7 Global Inference

Another flexibility that LiveHD provides is global inference. Some programming languages have global type inference, others have local type inference, and others like Verilog and FIRRTL have no inference. To support a wider superset of languages, LiveHD is designed to perform both global and local inference. The types, bits, and other attribute fields are propagated through the graph hierarchy. Other tools, except ML-based like Clash [86] and Lava [77], seem to have local type inference or none.

## 4.3.8 **Prototype Inference**

Currently, LiveHD does not have a working object model, but the object methods and attributes are built following prototype inheritance. This means that an object/struct can be extended and changed. It does not require specifying a fixed type.

## 4.4 LGraph Attribute Design

The design attribute stands for the characteristic given to an LGraph node or node\_pin. For instance, the characteristic of a node name and node physical placement. Even though a single LGraph represents a particular module, it can be instantiated multiple times, for example, the *sub2* node in Figure 4.1. In this case, the same module could have different attributes in the different hierarchies of the netlist. A good design of attribute structure should be able to represent both non-hierarchical and hierarchical characteristics.

## 4.4.1 Non-Hierarchical Attribute

Non-hierarchical LGraph attributes include pin\_name, node\_name, and line of source code. Such properties should be the same across different LGraph instantiations. Two instantiations of the same LGraph module will have the same user-defined node name on every node. For example, in Figure 4.1, instantiations of a subgraph 2 in both top and sub-graph 1 would maintain the same non-hierarchical attribute table.

node.set\_name(std::string\_view name);

Listing 4.6: API example for LGraph attribute setting

## 4.4.2 Hierarchical Attribute

I introduced a new hierarchical LGraph attribute design after an inspirational discussion with the author of FIRRTL. LGraph's hierarchical attribute is achieved using a tree data structure to record the design hierarchy. In LGraph, every graph has a unique id (lg\_id). Every instantiation of a graph forms some nodes in the tree, and every tree node is indexed by a unique hierarchical id (hid). As shown in Figure 4.2, we can identify a unique instantiation of a graph and generate its hierarchical attribute table. An example of a hierarchical attribute is wire delay.

Listing 4.7: API example for LGraph hierarchical attribute setting

## 4.5 **3rd Party Tools Integration**

The integration of third-party tools into LGraph is intuitive. Most tools have APIs to construct netlists in their internal data structure. Thus, we can first create an object of the tool in the LGraph program, traverse the LGraph netlist and use the tool's API to build an equivalent circuit on the fly inside the object. Then we make the object perform its primary functions, for instance, synthesis. Finally, we map the tool's data structure back into LGraph. Currently, Mockturtle and OpenTimer are being integrated into LGraph as initial prototypes.

## 4.5.1 Mockturtle

LGraph uses Mockturtle's library for LUT-based synthesis [80]. We first partition combinational groups and map these groups from LGraph to Majority-Inverter Graph (MIG) [14] for synthesis. The synthesized MIG networks are then technology mapped to k-bit Lookup table (KLUT) networks and stitched back to LGraph.

## 4.5.2 OpenTimer

The synthesized LGraph then uses the integrated OpenTimer to perform timing analysis. Again we traverse the LGraph netlist and build the corresponding Open-Timer structure, compute timing inside the OpenTimer object and return the criticalpath information.

# 4.6 Lesson Learned: The Deprecated but Fast Memory-Mapped Library

There are several important lessons we learned along with the LGraph-IR evolution. The lesson on using the memory-mapped library is the most important one.