# **UC Merced** UC Merced Electronic Theses and Dissertations

# Title

Memory Management for Big Memory Systems

# Permalink

https://escholarship.org/uc/item/8hs0p4gw

# Author

Ren, Jie

# Publication Date 2022

# **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, MERCED

# Memory Management for Big Memory Systems

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering and Computer Science

by

Jie Ren

Committee in charge:

Professor Dong Li, Chair Professor Hyeran Jeon Professor Xiaoyi Lu

2022

Copyright Jie Ren, 2022 All rights reserved. The dissertation of Jie Ren is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

(Professor Hyeran Jeon)

(Professor Xiaoyi Lu)

(Professor Dong Li, Chair)

University of California, Merced

2022

### TABLE OF CONTENTS

|           | Signature Page                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           | List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           | Vita and Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Chapter 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Chapter 2 | Background72.1Big Memory Applications72.2Heterogeneous Memory Based Big Memory Systems8                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter 3 | Efficient Billion-Point Nearest Neighbor Search on Heterogeneous Memory103.1Introduction113.2Preliminary and Related Works133.2.1ANNS and Similarity Graphs133.2.2Heterogeneous Memory133.3HM-ANN143.3.1Graph Construction via Top-Down Insertions and Bottom-up<br>Promotions143.3.2HM-ANN Graph Search Algorithm163.3.3Performance Model-Guided Parameter Selection183.4Evaluation203.4.1Methodology203.4.2Experiment Results213.4.3Ablation Studies233.5Conclusions25 |

| Chapter 4 | Efficient Tensor Migration and Allocation on Heterogeneous MemorySystems for Deep Learning264.1 Introduction274.2 Background304.3 Analysis and Characterization of Main Memory Accesses in DNN324.3.1 Profiling Framework324.3.2 Observations and Preliminary Analysis334.4 Design35                                                                                                                                                                                     |

|           | 4.4.1 Overview                                                     |  |

|-----------|--------------------------------------------------------------------|--|

|           | 4.4.2 Dynamic Profiling and Data Reorganization                    |  |

|           | 4.4.3 Handling Short-Lived Tensors                                 |  |

|           | 4.4.4 Adaptive Layer-Based Migration                               |  |

|           | 4.4.5 Discussions                                                  |  |

|           | 4.5 Applying Sentinel to GPU                                       |  |

|           | 4.6 Implementation                                                 |  |

|           | 4.7 Experimental Results                                           |  |

|           | 4.7.1 Experimental setup                                           |  |

|           | 4.7.2 Sentinel on Optane-based HM                                  |  |

|           | 4.7.3 Sentinel on GPU-based HM                                     |  |

|           | 4.8 Related Work                                                   |  |

|           | 4.9 Conclusions                                                    |  |

| Chapter 5 | Democratizing Billion-Scale Model Training                         |  |

| 1         | 5.1 Introduction                                                   |  |

|           | 5.2 Background and Related Work                                    |  |

|           | 5.3 Unique Optimal Offload Strategy                                |  |

|           | 5.3.1 DL Training as a Data-Flow Graph                             |  |

|           | 5.3.2 Limiting CPU Computation                                     |  |

|           | 5.3.3 Minimizing Communication Volume                              |  |

|           | 5.3.4 Maximizing Memory Savings                                    |  |

|           | 5.3.5 A Unique and Optimal Offload Strategy                        |  |

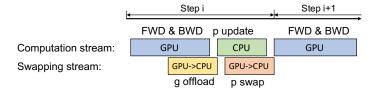

|           | 5.4 ZeRO-Offload Schedule                                          |  |

|           | 5.4.1 Single GPU Schedule                                          |  |

|           | 5.4.2 Scaling to Multi-GPUs                                        |  |

|           | 5.5 Optimized CPU Execution                                        |  |

|           | 5.5.1 Implementing the CPU Optimizer                               |  |

|           | 5.5.2 One-Step Delayed Parameter Update                            |  |

|           | 5.6 Evaluation                                                     |  |

|           | 5.6.1 Evaluation Methodology                                       |  |

|           | 5.6.2 Experimental Results                                         |  |

|           | 5.7 Conclusions                                                    |  |

| Chapter 6 | Enabling Large Dynamic Neural Network Training with Learning-based |  |

| 1         | Memory Management                                                  |  |

|           | 6.1 Introduction                                                   |  |

|           | 6.2 Background                                                     |  |

|           | 6.2.1 Dynamic Neural Networks                                      |  |

|           | 6.2.2 Breaking Memory Capacity Wall                                |  |

|           | 6.2.3 Using Machine Learning to Guide Tensor Migration 87          |  |

|           | 6.3 Overview                                                       |  |

|           | 6.4 Design                                                         |  |

|           | 6.4.1 Design of Input Features                                     |  |

|           | 6.4.2 Output of the Learned Model                                  |  |

|           | 6.4.3 Light Neural Network Model                                   |  |

|           |      | 6.4.4 Model Training                                            |

|-----------|------|-----------------------------------------------------------------|

|           |      | 6.4.5 Runtime Design                                            |

|           | 6.5  | Implementation                                                  |

|           | 6.6  | Evaluation                                                      |

|           |      | 6.6.1 Methodology                                               |

|           |      | 6.6.2 Overall Performance                                       |

|           |      | 6.6.3 Performance Analysis                                      |

|           |      | 6.6.4 Scalability of DyNN-Offload                               |

|           |      | 6.6.5 Construction of Learned Model                             |

|           |      | 6.6.6 Idiom-based Representation                                |

|           |      | 6.6.7 Evaluation of DyNN Model Partition                        |

|           |      | 6.6.8 Impact of Handling Misprediction                          |

|           | 6.7  | Related Work                                                    |

|           | 6.8  | Conclusion                                                      |

| Chapter 7 | Opti | imizing Large-Scale Plasma Simulations on Big Memory System 106 |

| •         | 7.1  | Introduction                                                    |

|           | 7.2  | Background                                                      |

|           | 7.3  | Performance Characterization                                    |

|           |      | 7.3.1 Profiling Results                                         |

|           | 7.4  | Performance Optimization on PM                                  |

|           |      | 7.4.1 Static Data Placement                                     |

|           |      | 7.4.2 Dynamic Data Placement                                    |

|           |      | 7.4.3 Implementation Details                                    |

|           | 7.5  | Evaluation                                                      |

|           |      | 7.5.1 Experimental Setup                                        |

|           |      | 7.5.2 Evaluation Results                                        |

|           | 7.6  | Related Work         125                                        |

|           | 7.7  | Conclusions                                                     |

| Chapter 8 | Scal | able Page Management for Multi-Tiered Large Memory Systems 127  |

| F         | 8.1  | Introduction                                                    |

|           | 8.2  | Background and Related Work                                     |

|           |      | 8.2.1 Multi-Tiered Large Memory Systems                         |

|           |      | 8.2.2 Large Memory Systems                                      |

|           |      | 8.2.3 Two-Tiered Heterogeneous Memory                           |

|           | 8.3  | Overview                                                        |

|           | 8.4  | Adaptive Memory Profiling                                       |

|           | 011  | 8.4.1 Adaptive Memory Regions                                   |

|           |      | 8.4.2 Adaptive Page Sampling                                    |

|           |      | 8.4.3 Profiling Overhead Control                                |

|           | 8.5  | Holistic Page Management                                        |

|           | 0.5  | 8.5.1 Which Memory Region to Migrate?                           |

|           |      | 8.5.2 Where to Migrate Memory Regions?                          |

|           | 8.6  | Adaptive Migration Mechanism       140                          |

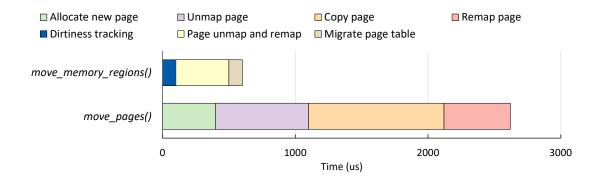

|           | 0.0  | 8.6.1 Performance Analysis of Page Migration Mechanism 140      |

|           |      |                                                                 |

|           |      | 8.6.2   | Adaptive Page Migration Schemes      | 141 |

|-----------|------|---------|--------------------------------------|-----|

|           | 8.7  | Implen  | nentation                            | 142 |

|           | 8.8  | Evaluat | tion                                 | 143 |

|           |      | 8.8.1   | Experimental Setup                   | 143 |

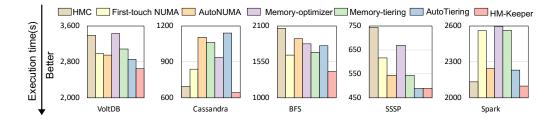

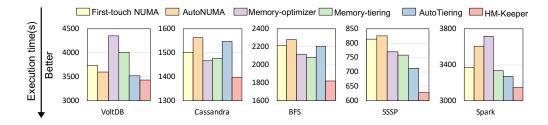

|           |      | 8.8.2   | Overall Performance                  | 144 |

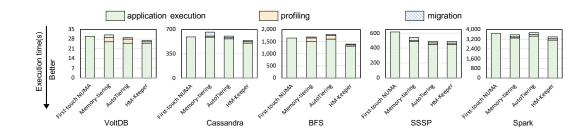

|           |      | 8.8.3   | Effectiveness of Adaptive Profiling  | 149 |

|           |      | 8.8.4   | Effectiveness of Migration Strategy  | 150 |

|           |      | 8.8.5   | Effectiveness of Migration Mechanism | 151 |

|           | 8.9  | Conclu  | sions                                | 152 |

| Chapter 9 | Conc | lusions | and Future Directions                | 153 |

|           | 9.1  | Conclu  | sions                                | 153 |

|           | 9.2  | Future  | Directions                           | 155 |

# LIST OF FIGURES

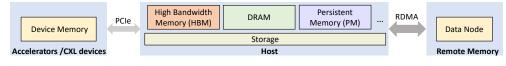

| Figure 2.1:   | The architecture of heterogeneous memory based big memory systems                                                                              | 8         |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

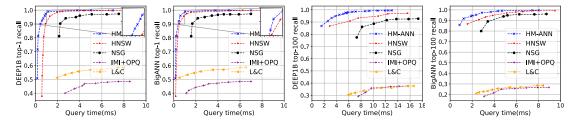

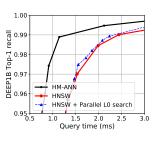

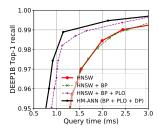

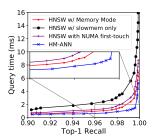

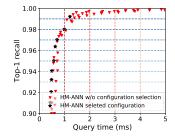

| Figure 3.1:   | Query time vs. recall curve in (a) DEEP1B top-1, (b) BigANN top-1, (c) DEEP1B top-100, (b) BigANN top-100, respectively                        | 22        |

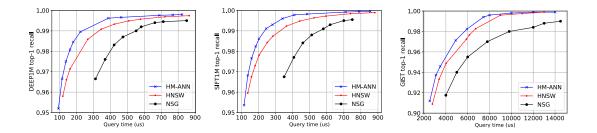

| Figure 3.2:   | Query time vs. recall curve with (a)DEEP1M, (b)SIFT1M, and (c)GIST         respectively.       2                                               | 23        |

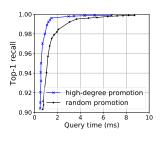

| Figure 3.3:   |                                                                                                                                                | 24        |

| Figure 3.4:   | HNSW with parallel L0 search                                                                                                                   | 24        |

| Figure 3.5:   |                                                                                                                                                | 24        |

| Figure 3.6:   |                                                                                                                                                | 25        |

| Figure 3.7:   |                                                                                                                                                | 25        |

| Figure 3.8:   |                                                                                                                                                | 25        |

| Figure 4.1:   | An example to show tensor access patterns across layers in ResNet-32. This                                                                     |           |

|               | figure shows the first three layers and the last three layers in ResNet-32 3                                                                   | 34        |

| Figure 4.2:   | Data processing in a TensorFlow operation, nn.conv2d                                                                                           | 34        |

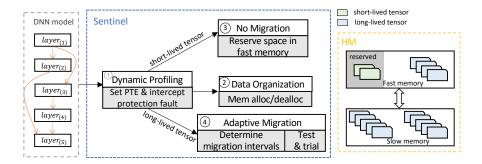

| Figure 4.3:   | Overview of Sentinel. The white and shadow boxes represent functionality                                                                       |           |

|               | and mechanisms, respectively                                                                                                                   | 35        |

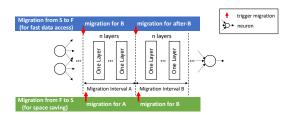

| Figure 4.4:   | Tensor migration based on the migration intervals. "S" and "F" stand for slow and fast memories respectively.                                  | 38        |

| Figure 4.5:   | Performance (training throughput) variance as we change the migration interval length (MIL). "SP" stands for sweet spot (the optimum migration | 38        |

| Figure 4.6:   |                                                                                                                                                | 14        |

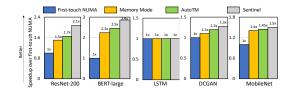

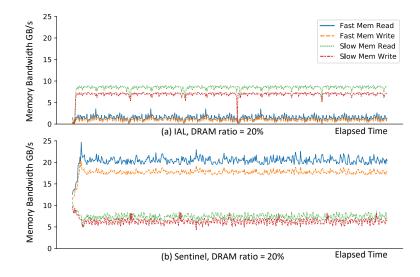

| Figure 4.7:   | Performance speedup of IAL, AutoTM and Sentinel over slow-memory<br>only. The red horizontal line shows performance of fast-memory only.       |           |

|               |                                                                                                                                                | 17        |

| Figure 4.8:   | Performance with first-touch NUMA, Memory Mode, AutoTM and Sentinel,                                                                           | • ′<br>17 |

| Figure 4.9:   | 5                                                                                                                                              | + /<br>18 |

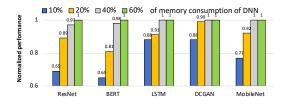

| U             | Performance with Sentinel under various sizes of fast memory. The fast                                                                         | ro        |

| 1 iguie 4.10. | memory size is shown as the percentage of peak memory consumption of                                                                           |           |

|               |                                                                                                                                                | 19        |

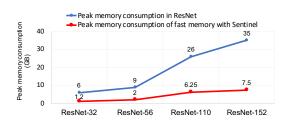

| Figure 4 11.  | Comparison between peak memory consumption of DNN models and fast                                                                              | r)        |

| 1 iguie 4.11. |                                                                                                                                                | 19        |

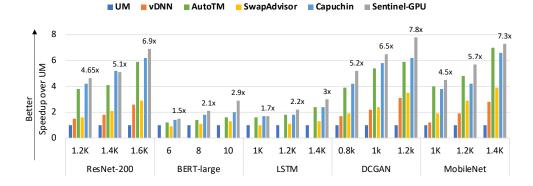

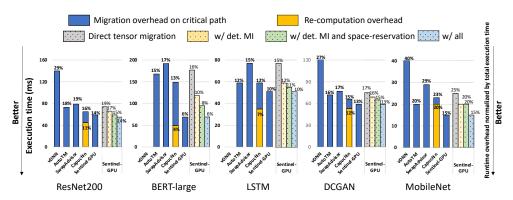

| Figure 4 12.  | Performance of UM, vDNN, AutoTM, SwapAdvisor, and Capuchin and                                                                                 |           |

| 1 iguie 4.12. | Sentinel-GPU, normalized by that of UM. vDNN cannot work for BERT and                                                                          |           |

|               | -                                                                                                                                              | 51        |

| Figure 4 13.  | Performance breakdown for vDNN, AutoTM, SwapAdvisor, Capuchin and                                                                              | 1         |

| 1 15uic 7.13. | Sentinel-GPU. "det. MI" stands for "determine an appropriate migration                                                                         |           |

|               | interval length". Percentage numbers on top of bars are the ratio in terms of                                                                  |           |

|               |                                                                                                                                                | 52        |

|               | execution time of one training step.                                                                                                           | , _       |

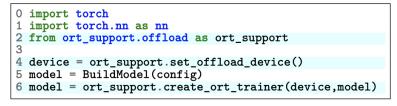

| Figure 5.1:  | ZeRO-Offload can be enabled with a few lines of change. The code on left    |         |

|--------------|-----------------------------------------------------------------------------|---------|

|              | shows a standard training pipeline, while the right shows the same pipeline |         |

|              | with ZeRO-Offload enabled.                                                  | 57      |

| Figure 5.2:  | The dataflow of fully connected neural networks with $M$ parameters. We     |         |

|              | use activation checkpoint to reduce activation memory to avoid activation   |         |

|              | migration between CPU and GPU.                                              | 63      |

| Figure 5.3:  | ZeRO-Offload training process on a single GPU.                              | 65      |

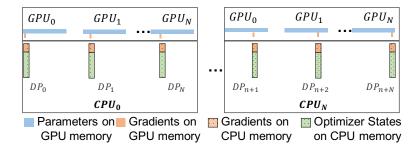

| Figure 5.4:  | ZeRO-Offload data placement with multiple GPUs                              | 66      |

| Figure 5.5:  | Code representing ZeRO-Offload that combines unique optimal CPU offload     |         |

| -            | strategy with ZeRO-powered data parallelism.                                | 66      |

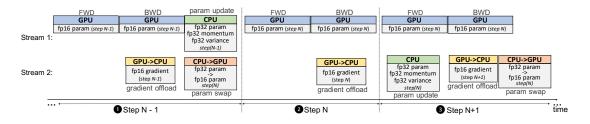

| Figure 5.6:  | Delayed parameter update during the training process.                       | 69      |

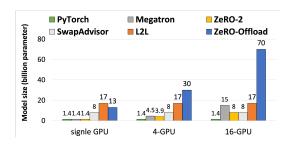

| Figure 5.7:  | The size of the biggest model that can be trained on single GPU, 4 and 16   |         |

| -            | GPUs (one DGX-2 node).                                                      | 73      |

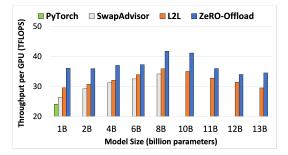

| Figure 5.8:  | The training throughput with PyTorch, L2L, SwapAdvisor and ZeRO-            |         |

| C            | Offload on a single GPU with a batch size of 512.                           | 73      |

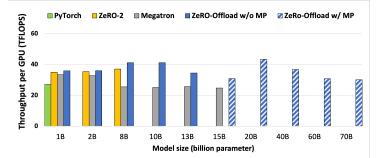

| Figure 5.9:  | Training throughput with PyTorch, ZeRO-2, Megatron-LM, ZeRO-Offload         |         |

| e            | without model parallelism and ZeRO-Offload with model parallelism           | 75      |

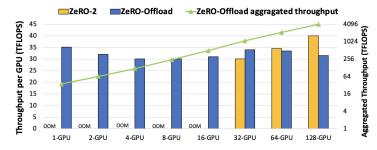

| Figure 5.10: | Comparison of training throughput between ZeRO-Offload and ZeRO-2           |         |

| C            | using 1–128 GPUs for a 10B parameter GPT2.                                  | 76      |

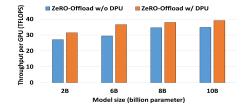

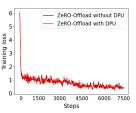

| Figure 5.11: | The training throughput is compared for w/o DPU and w/ DPU to GPT-2.        |         |

| e            | Batch size is set to 8                                                      | 77      |

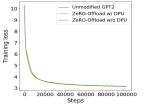

| Figure 5.12: | The training loss curve of unmodified GPT-2, ZeRO-Offload w/o DPU and       |         |

| e            | ZeRO-Offload with DPU.                                                      | 77      |

| Figure 5.13: | The fine-tuning loss curve of BERT, ZeRO-Offload w/o DPU and ZeRO-          |         |

| 0            | Offload with DPU.                                                           | 77      |

| Figure 5.14: | Comparison of training throughput with enabling offload strategies and      |         |

| -            | optimization techniques step-by-step in ZeRO-Offload.                       | 78      |

|              |                                                                             |         |

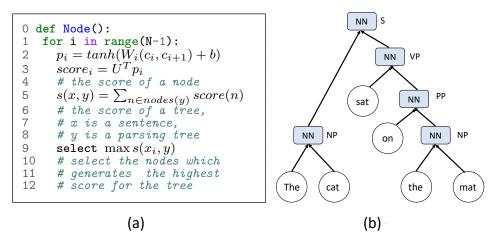

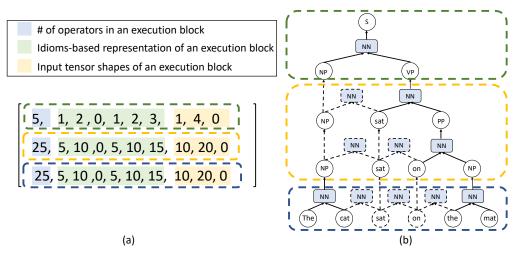

| Figure 6.1:  | An DyNN example.(a) Implementation of each tree node in DyNN (b) The        |         |

|              | Tree-FC network where S, PP, NP and VP stand for sentence, preposition      |         |

|              | phrase, noun phrase, and verb phrase respectively.                          | 86      |

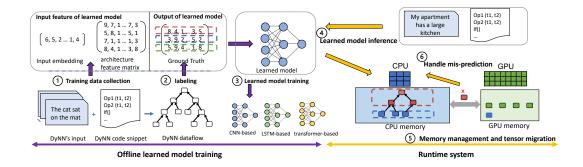

| Figure 6.2:  | The overview of DyNN-Offload.                                               | 88      |

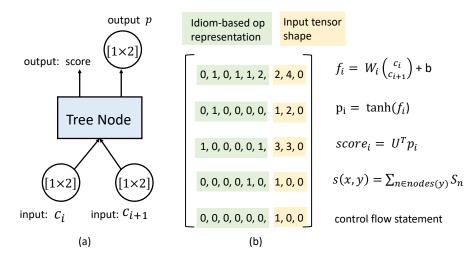

| Figure 6.3:  | An AFM example to show the static structure of the Tree-FC shown in         |         |

|              | Figure 6.1. (a) A node in DyNN with input and output tensors; (b) AFM       |         |

|              | representation along with computation in operators.                         | 92      |

| Figure 6.4:  | An example of the learned model output. (a) shows an output of the learned  |         |

|              | model with three execution blocks. (b) shows the dataflow graph of DyNN     |         |

|              | with a given input, and how the output maps back to the operators           | 93      |

| Figure 6.5:  | An example of using DyNN-Offload.                                           | 98      |

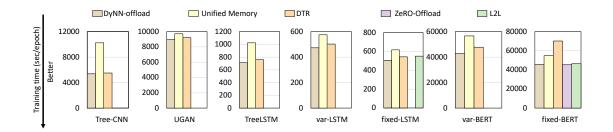

| Figure 6.6:  | Performance comparison between existing solutions and DyNN-Offload          |         |

|              | with seven workloads.                                                       | 100     |

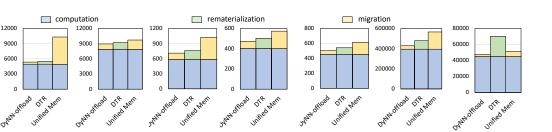

| Figure 6.7:  | Performance breakdown for DyNN-Offload, DTR and unified memory.             | 101     |

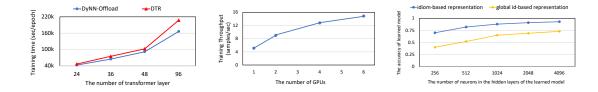

| Figure 6.8:  | Scalability evaluation of DyNN-Offload with a variety of model scales in    |         |

|              | var-Bert.                                                                   | 102     |

| Figure 6.9:  | Scalability evaluation of DyNN-Offload in terms of system scales (i.e., the | <i></i> |

|              | number of GPUs).                                                            | 102     |

| •            | Evaluation of the effectiveness of the idiom-based representation                                                 | 102 |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----|

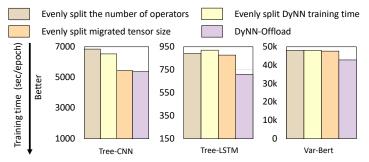

| Figure 6.11: | The training time with DyNN-Offload and three heuristic solutions to                                              |     |

|              | partition DyNNs                                                                                                   | 103 |

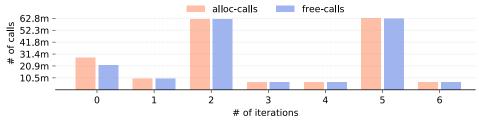

| Figure 7.1:  | The number of memory allocation/deallocation across iterations                                                    | 111 |

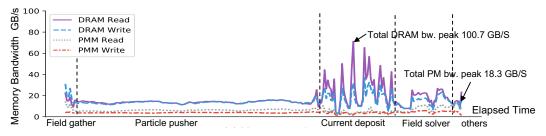

| Figure 7.2:  | Memory bandwidth consumption in major phases.                                                                     | 112 |

| Figure 7.3:  | The overview of data management on Optane-based HM                                                                | 114 |

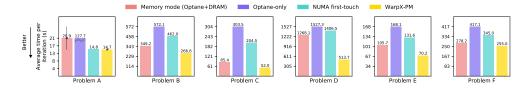

| Figure 7.4:  | Performance comparison between Memory mode, Optane-only, NUMA                                                     |     |

|              | first-touch and WarpX-PM.                                                                                         | 122 |

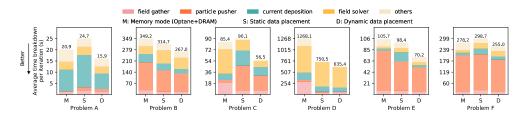

| Figure 7.5:  | Performance breakdown of main phases of excution to compare the static<br>and dynamic placement with memory mode. | 122 |

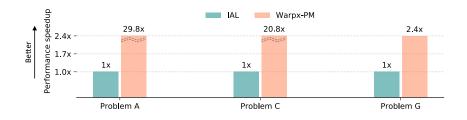

| Figure 7.6:  | Performance comparison between IAL (a state-of-the-art page migration                                             | 122 |

| 1 iguie 7.0. | solution for HM) and WarpX-PM.                                                                                    | 123 |

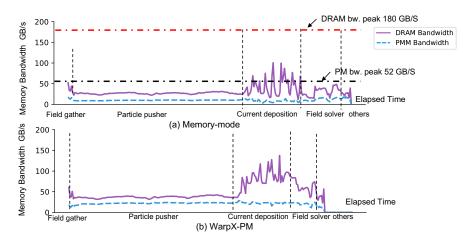

| Figure 7.7:  | Memory bandwidth consumption in one iteration.                                                                    | 124 |

| Figure 7.8:  | Performance with different number of helper threads. "th" is the number of                                        |     |

|              | helper threads.                                                                                                   | 124 |

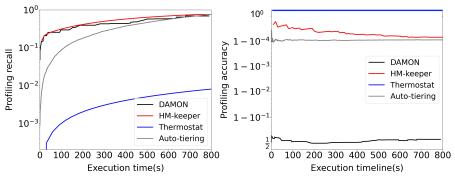

| Figure 8.1:  | Comparison of different memory profiling methods in terms of their effectivenes                                   | SS  |

|              | of identifying frequently accessed pages (hot pages). The profiling overhead                                      |     |

|              | is set as 5% of total execution time.                                                                             | 129 |

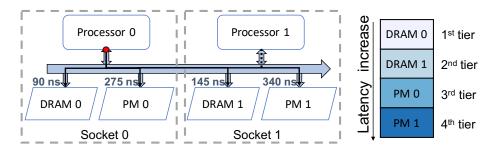

| Figure 8.2:  | An example of multi-tiered memory system.                                                                         | 131 |

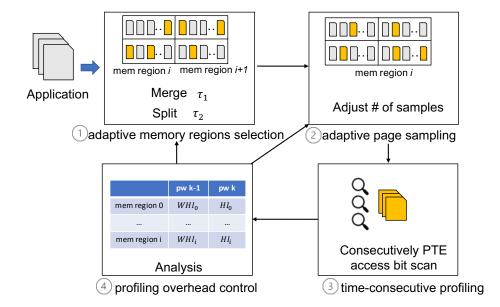

| Figure 8.3:  | The overview of memory profiling in HM-Keeper.                                                                    | 135 |

| Figure 8.4:  | Performance breakdown for migration mechanisms.                                                                   | 141 |

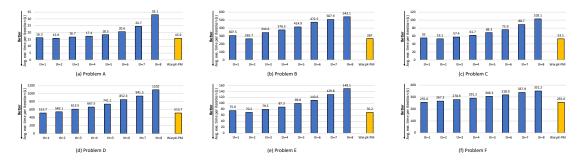

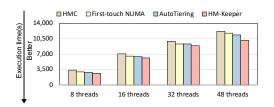

| Figure 8.5:  | Performance comparison between existing solutions and HM-Keeper on the                                            |     |

|              | Optane-based multi-tiered memory system.                                                                          | 146 |

| Figure 8.6:  | Performance comparison between existing solutions and HM-Keeper on the                                            |     |

|              | emulated multi-tiered memory system.                                                                              | 146 |

| Figure 8.7:  | Breakdown of application execution time.                                                                          | 147 |

| Figure 8.8:  | Execution time of VoltDB with different number of client threads                                                  | 148 |

| Figure 8.9:  | Evaluating HM-Keeper with different large page sizes. We use the SSSP                                             |     |

|              | application for evaluation.                                                                                       | 148 |

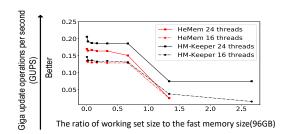

| Figure 8.10: | Evaluation of HM-Keeper on two-tiered HM and comparison with HeMem.                                               | 150 |

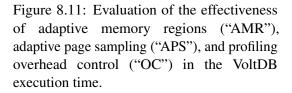

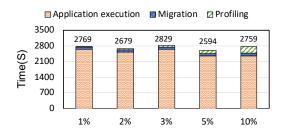

| Figure 8.11: | Evaluation of the effectiveness of adaptive memory regions ("AMR"),                                               |     |

|              | adaptive page sampling ("APS"), and profiling overhead control ("OC")                                             |     |

|              | in the VoltDB execution time.                                                                                     | 150 |

| Figure 8.12: | Execution time with setting various of profiling overhead targets when                                            |     |

|              | execute voltDB with HM-Keeper.                                                                                    | 151 |

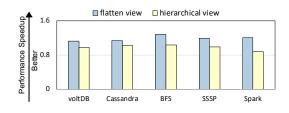

| Figure 8.13: | Comparison between flatten- and hierarchical view-based migration. Performan                                      | nce |

|              | speedup is calculated based on the performance of first-touch NUMA                                                | 151 |

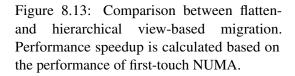

| Figure 8.14: | Performance comparison between Nimble, move_pages() and HM-Keeper                                                 |     |

|              | in page migration mechanism. The performance speedup is calculated based                                          |     |

|              | on the performance of using <i>move_pages()</i>                                                                   | 151 |

|              |                                                                                                                   |     |

# LIST OF TABLES

| Table 2.1: | DRAM, HBM, PM comparison                                                                   | 8   |

|------------|--------------------------------------------------------------------------------------------|-----|

| Table 3.1: | Indexing time and memory consumption for graph-based methods on billion-<br>scale datasets | 22  |

| Table 4.1: | Comparison between existing work on HM management for DNN training.                        | 31  |

| Table 4.2: | Hardware overview of experimental system                                                   | 45  |

| Table 4.3: | DNN model for evaluation. "Sen.", stands for Sentinel                                      | 46  |

| Table 4.4: | Total size of migrated tensors in one training step.                                       | 47  |

| Table 4.5: | Maximum Batch Size with vDNN, AutoTM, SwapAdvisor, Capuchin and                            |     |

|            | Sentinel-GPU                                                                               | 52  |

| Table 5.1: | Memory savings for offload strategies that minimize communication volume                   |     |

|            | compared to the baseline                                                                   | 64  |

| Table 5.2: | Hardware overview of experimental system                                                   | 71  |

| Table 5.3: | Model configuration in evaluation.                                                         | 72  |

| Table 5.4: | Adam latency (s) for PyTorch (PT) and CPU-Adam.                                            | 77  |

| Table 6.1: | Distribution of Jaccard distance value for all training samples.                           | 86  |

| Table 6.2: | DyNNs for evaluation.                                                                      | 99  |

| Table 6.3: | Learned model performance with different model complexity. "LM" stands                     |     |

|            | for learned model.                                                                         | 102 |

| Table 7.1: | Compare the memory capacity and simulation scale on supercomputers                         | 110 |

| Table 7.2: | The distribution of object size.                                                           | 112 |

| Table 7.3: | The breakdown of execution time.                                                           | 112 |

| Table 7.4: | Notation for performance modeling                                                          | 116 |

| Table 7.5: | Input problems used in evaluation                                                          | 120 |

| Table 7.6: | Platform Specifications                                                                    | 120 |

| Table 7.7: | Quantifying memory traffic between two NUMA nodes                                          | 124 |

| Table 8.1: | Hardware overview of experimental system.                                                  | 145 |

| Table 8.2: | Workloads for evaluation.                                                                  | 145 |

| Table 8.3: | The number of memory accesses when using voltDB                                            | 147 |

#### ACKNOWLEDGEMENTS

To begin with, I would like to express my deepest thanks to my advisor, Professor Dong Li. He was the key to me having a memorable PhD journey and pursuing a career in academia. He spent incredible time training and mentoring me, guiding me to grow to be a passionate, independent researcher. When I felt lost, he taught me that keep doing good work, and everything else will follow. When I self-doubted, he always believed in my potential and encouraged me never to be afraid of reaching high. I have been very fortunate to have him as my advisor.

Next, I am very grateful to my committee members, Professor Hyeran Jeon and Professor Xiaoyi Lu, for their great support and feedback about my work. And my special thanks to all my mentors and co-authors, especially Dr. Minjia Zhang, Dr. Ivy Peng, Dr. Leo Chunhua Liao, and Professor Harry Xu. It has been my great pleasure working with them. I really enjoyed our meetings and research discussions, which were invaluable research experiences.

In addition, I would like to thank my friend, Dr. Xueting Li. We shared joy, anxiety, frustration, and happiness altogether in the last five years. I am so lucky to have her by my side. I also would like to thank all my labmates from the UC Merced PASA lab. They have been the greatest set of friends and colleagues.

Last but not least, I want to thank my family. I cannot thank my cousin, Fang Ren, enough for her unconditional support. I enjoyed all the beautiful summer days we spent together. I dedicate this dissertation to my parents, Haomin Guo and Zhaohua Ren, who are the best parents anyone could ever ask for. They are my rock in life.

#### VITA

| 2017 | B. S. in Computer Science and Engineering, Beijing Institute of Technology              |

|------|-----------------------------------------------------------------------------------------|

| 2022 | Ph. D. in Electrical Engineering and Computer Science, University of California, Merced |

### PUBLICATIONS

**Jie Ren**, Dong Xu, Ivy Peng, Jiawen Liu, Kai Wu, Dong Li. "HM-Keeper: Scalable Page Management for Multi-Tiered Large Memory Systems". A submission to ASPLOS'23.

**Jie Ren**, Shuangyan Yang, Dong Xu, Christian Navasca, Chenxi Wang, Guoqing Harry Xu, Dong Li. "DyNN-Offload: Enabling Large Dynamic Neural Network Training with Learning-based Memory Management". A submission to ASPLOS'23.

**Jie Ren**, Samyam Rajbhandari, Reza Yazdani Aminabadi, Olatunji Ruwase, Shuangyan Yang, Minjia Zhang, Dong Li and Yuxiong He. "ZeRO-Offload: Democratizing Billion-Scale Model Training". In 27th USENIX Annual Technical Conference. ATC'21.

**Jie Ren**, Jiaolin Luo, Kai Wu, Minjia Zhang, Hyeran Jeon, and Dong Li, "Sentinel: Efficient Tensor Migration and Allocation on Heterogeneous Memory Systems for Deep Learning". In 27th IEEE International Symposium on High-Performance Computer Architecture. HPCA'21.

**Jie Ren**, Jiaolin Luo, Ivy Peng, Kai Wu, and Dong Li, "Optimizing Large-Scale Plasma Simulations on Persistent Memory-based Heterogeneous Memory with Effective Data Placement Across Memory Hierarchy". In 35th International Conference on Supercomputing. ICS'21.

Kai Wu, **Jie Ren**, Ivy Peng and Dong Li. "ArchTM: Architecture-Aware, High Performance Transaction for Persistent Memory". In 19th USENIX Conference on File and Storage Technologies. FAST'21.

Jiawen Liu, **Jie Ren**, Roberto Gioiosa, Dong Li and Jiajia Li. "Sparta: High-Performance, Element-Wise Sparse Tensor Contraction on Heterogeneous Memory.". In 26th Principles and Practice of Parallel Programming. PPoPP'21.

**Jie Ren**, Minjia Zhang, and Dong Li, "HM-ANN: Efficient Billion-Point Nearest Neighbor Search on Heterogeneous Memory". In 34th Conference on Neural Information Processing Systems. Neurips'20.

**Jie Ren**, Kai Wu, and Dong Li, "EasyCrash: Exploring Non-Volatility of Non-Volatile Memory for High Performance Computing Under Failures". In IEEE International Conference on Cluster Computing. CLUSTER'20.

Ivy Peng, Kai Wu, **Jie Ren**, Maya Gokhale and Dong Li, "Demystifying the Performance of HPC Scientific Applications on Non-Volatile Memory-based Memory Systems". In International Parallel and Distributed Processing Symposium. IPDPS'20.

Kai Wu, Ivy Peng, **Jie Ren**, and Dong Li, "Ribbon: High Performance Cache Line Flushing for Persistent Memory". In 29th International Conference on Parallel Architectures and Compilation Techniques. PACT'20.

**Jie Ren**, Kai Wu, and Dong Li, "Understanding Application Recomputability without Crash Consistency in Non-Volatile Memory". In Workshop on Memory Centric Programming for HPC. MCHPC'18.

Kai Wu, **Jie Ren**, and Dong Li, "Runtime Data Management on Non-Volatile Memory-based Heterogeneous Memory for Task-Parallel Programs". In 30th ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis. SC'18.

### ABSTRACT OF THE DISSERTATION

#### Memory Management for Big Memory Systems

by

Jie Ren

Doctor of Philosophy in Electrical Engineering and Computer Science

University of California Merced, 2022

Professor Dong Li, Chair

The memory system has been evolving at a fast pace recently, driven by the emergence of largescale applications and the advance in hardware technology. This trend calls for the birth of big memory systems with extreme heterogeneity, which combines multiple memory technologies with different latency, bandwidth, and capacity to construct main memory. The conventional memory management methods are not adequate to handle the increasing complexity that heterogeneity brings forward, and will fail to deliver the full potential of the new memory. Specifically, the heterogeneity of memory systems brings a substantial disparity in the performance and efficiency, making the decision of which technology to use at what times intricate.

The performance of heterogeneous memory-based big memory systems highly depends on the data locality. By dynamically profiling memory access behaviors, memory management solutions move frequently accessed (or hot) data from slow to fast memory and less frequently accessed (or cold) data from fast to slow memory. However, the decision of how to spread data across all memory components in big memory systems, which data to move, and at what times is not trivial.

This dissertation proposes a series of techniques, spanning from architecture, runtime systems, operating systems, programming models, to applications and algorithms, which are used to efficiently identify *which* data in applications are performance-critical, timely determine *when* to perform data migration, and select *where* to place those data in big memory systems. Specifically, this dissertation contains six common scenarios using big memory systems with big memory applications such as machine learning/artificial intelligence applications, large-scale scientific simulation, and in-memory databases. We propose several software techniques for the efficient use of big memory systems in all scenarios. By doing so, this dissertation identifies bottlenecks in the existing memory management solution, explores the unique characteristics of different types

of applications, and bridges gaps from different system stacks to remedy bottlenecks. Evaluation results based on real-world big memory systems illustrate that with efficient data placement, our solutions outperform existing OSes-based and hardware-based memory management solutions.

# **Chapter 1**

# Introduction

The era of big memory systems come upon us. From the application perspective, we see the emergence of machine learning, big data, scientific simulation, and in-memory database applications, which call for large memory capacity because of large datasets and high performance enabled by high memory bandwidth for efficient data processing. From the hardware technology perspective, the emergence of 3D XPoint, through silicon via (TSV) technology and fast interconnect, brings the potential of significantly increasing memory capacity or memory bandwidth while reducing memory production cost. Furthermore, the emergence of GPU-like accelerators brings large performance improvement to data-intensive applications, but imposes high requirements on memory bandwidth and memory capacity. The above trend is calling for the birth of memory systems with extreme heterogeneity, which combines multiple memory technologies to construct big memory systems.

We summarize the features of big memory systems as follow.

- Memory heterogeneity. The big memory systems combine multiple memory technologies with differences in latency, bandwidth, cost, and other new design parameters such as persistence and asymmetric read and write performance. The extreme heterogeneity requires to redesign the memory hierarchy to accommodate big memory systems.

- Huge memory capacity. Different from traditional memory systems, which have only a few hundreds of gigabytes of DRAM per node, a typical big memory system contains a few terabyte of memory per node. One of the commonly used big memory system is build with Intel Optane DC PM and DRAM. With Intel Optane DC PM, the memory capacity on a single machine can achieve 6TB [83]. The Amazon web service also provides big memory

instances (up to 24 TB per node) for customers to conduct the memory intensive workloads. The huge memory capacity requires memory management techniques must be scalable.

Memory management is one of the most important and challenging tasks in the computer system, which includes memory (de)allocation, data placement and migration, etc. The rapid development of memory techniques has brought new challenges in memory management - the memory system becomes more complicated than ever. To maximize the performance of big memory systems, via proper data tiering, allows for the desired performance levels of the aforementioned classes of applications. To achieve this, software-level [52, 61, 116, 162, 226, 227, 234, 241] and hardware-level [13, 31, 168, 169] approaches in heterogeneous memory (HM) management build the necessary mechanisms to maximize the utility of the fastest available memory component via corresponding dynamic migration of frequently accessed data. The task to identify which data is most appropriate to move and at what times, depending on the available data access information and performance estimates.

A typical memory management (i.e., performance optimization) on HM includes three steps, which are *memory profiling*, *migration strategy* and *migration mechanism*. The first step, *memory profiling*, answers the question to *which* data in applications are performance-critical and need to involve in data migration. The second step, *migration strategy*, answers questions to *when* to perform data migration, and *where* to place those data in HM. The third step, *migration mechanism*, answers the question to *how* to efficiently migrate data.

The unique features in big memory systems makes the memory management becoming particular challenging. We summarize the challenges as follow.

*Memory profiling.* Big memory systems require high accurate and scalable memory profiling methods. It's difficult to striking the right balance between accurate and overhead when profiling big memory systems. Some existing work [103, 141] explore sampling-based hardware performance counters such as Intel's PEBS and AMD's IBS to track memory accesses. Performance counters count and sample specific events by hardware, which leads to inaccurate profiling results, especially in TB-scale big memory system. Some existing works [78, 95, 104, 248] manipulate specific bits in page table entries (PTEs) to track memory accesses at a per-page granularity. Manipulating PTE provides high accuracy in tracking memory accesses. However, the profiling overhead scales linearly with the number of tracked pages, which takes several seconds to track millions of pages (i.e., TB-scale, which is commonly seen in bit memory systems). Such profiling method is too slow to respond to time-changing access patterns. In this dissertation, we proposal techniques which utilize applications' domain knowledge to reduce profiling overhead

in Chapter 3, 4, 5, and 7. We demonstrate machine learning can be used to predict the memory access patterns in dynamic neural networks (DyNN) to avoid expensive memory profiling in Chapter 6. We also introduce a high-accurate, lightweight memory profiling method for TB-scale multi-tiered memory based on adaptively merging/splitting memory regions, described in Section 8.

*Migration strategy.* Migration strategy needs to make data migration decision based on memory profiling results. It should timely capture hot data without violating the capacity of fastest (or fast) memory. Existing work [98, 234] leverage caching algorithm such FIFO, LRU as migration strategy. Caching algorithm is not suitable for big memory systems because following two reasons. First, the fastest (or fast) memory component in big memory systems contains hundreds of gigabytes. Maintaining FIFO or LRU list for fastest (or fast) memory component is too expensive to make data migration decision timely. Second, big memory systems usually contains multiple memory tiers. A single FIFO or LRU list can not provide enough information to make migration decision due to multiple migration destination. The dissertation uses a greedy algorithm to fetch data into fast memory aggressively in Chapter 3; proposes a lightweight performance model to decide whether performs data migration based on memory component bandwidth and latency in Chapter 7, and proposes a migration strategy for multiple memory tier based on memory access heuristic in Chapter 8.

*Migration mechanism.* Data migration is not free. Data migration overhead depends on performance features of source and destination memory components, as well as data structure and data size of migrated data. Minimizing the data migration overhead is critical to obtain performance gain from memory management. Existing work [234] leverages concurrent migration and bi-direction migration to reduce the huge page migration overhead in Linux. The dissertation discuss how to maximize the overlap between data migration and computation using performance model in Chapter 4 and 7. In Chapter 8, we also proposal a novel data migration mechanism to optimize read intensive data migration performance.

The above challenges in existing memory management runtime motivate the development of our techniques that can break the trade-offs in big memory systems management and improve the runtime system efficiency for modern big memory applications. This dissertation consists of a series of techniques, spanning operating systems (OSes), runtime systems, applications, and algorithms, aiming to address above challenges, optimizing away runtime system inefficiencies, and thus, significantly improve the efficiency of big memory systems while making them easier for users to deploy and manage their applications. In particular, the contributions of this dissertation • **Contribution 1.** *HM-ANN* [181], a novel approximate nearest neighbor search (ANNS) algorithm which breaks the fundamental tradeoff in ANNS algorithms between query latency and accuracy and enables fast and highly accurate billion-scale ANNS on HM based big memory systems.

The state-of-the-art ANNS algorithms face a fundamental tradeoff between query latency and accuracy, because of limited main memory capacity: To store indices in main memory for fast query response, they have to limit the number of data points in DRAM or store compressed vectors, which hurts search accuracy. The emergence of HM brings opportunities to largely increase memory capacity and break the above tradeoff. However, HM consists of both fast (but small) memory and slow (but large) memory, and using HM inappropriately slows down query time significantly. To make best utilization of both fast and slow memory in HM, *HM-ANN* takes both memory and data heterogeneity into consideration and enables billion-scale similarity search on a single node. HM-ANN provides 95% top-1 recall in less than 1ms on billion-scale datasets, and is 2x-5.8x faster than state-of-the-art.

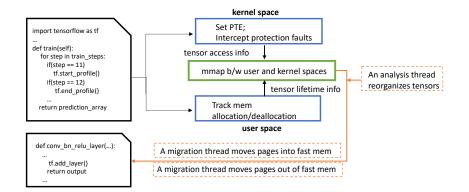

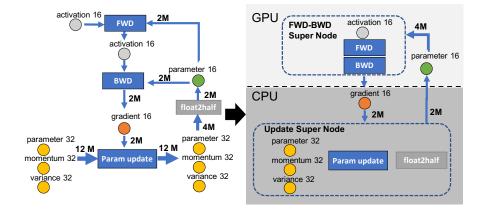

• **Contribution 2.** *Sentinel* [178], a software runtime system for Tensorflow that automatically optimizes tensor placement in static deep neuron networks (DNN) training on HM.

Memory capacity is a major bottleneck for training deep DNN. HM combining fast (e.g., GPU device memory) and slow memories (e.g., CPU host memory) provides a promising direction to increase memory capacity. However, HM imposes challenges on tensor migration and allocation for high performance DNN training. Prior work unnecessarily causes tensor migration due to page-level false sharing, and wastes fast memory space. To address above problems, we design Sentinel, which coordinates operating system (OS) with runtime-level profiling dynamically, and enables co-allocating tensors with similar lifetime and memory access frequency into the same pages to improve tensor movement efficiency. With the above optimizations, Sentinel successfully avoids out-of-memory (OOM) issues for large models on GPU, and outperforms five state-of-the-art memory management solutions for DNN training.

• **Contribution 3.** *ZeRO-Offload* [179], a novel heterogeneous deep learning (DL) training technology that makes large transformer-based model training accessible to everyone.

are:

Training extremely large models such as natural language processing (NLP) models with billions of parameter is challenging. It often requires refactorization of the models and the accesses to prohibitively expensive GPU clusters. *ZeRO-Offload* utilizes both memory and computation resources in host CPU to enable large DL model training with limited GPU resources. Specifically, *ZeRO-Offload* places memory-consuming tensors such as optimizer states on CPU memory, and computation-intensive tensors such as parameters on GPU memory. *ZeRO-Offload* enables 10x bigger model training on a single GPU and achieves near-linear speedup on up to 128 GPUs.

• **Contribution 4.** *DyNN-Offload*, a memory management system to train dynamic neural networks (DyNN) with limited GPU capacity.

Managing tensors in DyNN to save GPU memory is challenging, because the dynamic model structure of DyNN leads to input-dependent tensor access patterns. *DyNN-Offload* proposes a learned approach (using a neural network) to increase the predictability of tensor accesses to facilitate memory management. *DyNN-Offload* enables fast inference while providing high prediction accuracy of the learned model. Specifically, *DyNN-Offload* reduces input feature space and model complexity based on a new representation of DyNN, and converts the hard problem of making predictions for individual tensors or operators into a simpler problem of making predictions for a group of operators. We implement *DyNN-Offload* with cross-platform machine learning library onnxruntime. *DyNN-Offload* outperforms state-of-the-art solutions by 2%-50% in terms of training time with the same GPU memory capacity and enables 8x larger model training without out of memory.

• **Contribution 5.** *WarpX-PM* [177], a automatic data placement solution for particle-in-cell (PIC) method on HM-based big memory systems.

The PIC method is an important model that uses computational particles to simulate plasma particles, such as electrons and protons. High-fidelity PIC simulations often use billions and even trillions of particles, which requires high memory capacity. I explored the usage of HM to enable large-scale plasma simulations at unprecedented scales on a single machine. By analysing the performance of PIC simulation in detail and designed a novel dynamic data placement strategy, we implemented the strategy in a DOE mission-critical application, WarpX. *WarpX-PM* accelerates the execution of WarpX on HM by over 60% (compared with the case of no management).

• Contribution 6. HM-Keeper, an application-transparent page management system that

supports the efficient use of multi-tiered big memory systems.

Multi-terabyte big memory systems are often characterized with more than two memory tiers for large memory capacity and high performance. Those tiers include slow and fast memories with different latencies and bandwidths. Making effective, transparent use of the multi-tiered large memory system requires a page management system, based on which the application can make the best use of fast memories for high performance and slow memories for large capacity. However, applying existing solutions to multi-tiered large memory systems has fundamental limitation because of non-scalable, low-quality memory profiling mechanisms and unawareness of rich memory tiers in page migration policies. To address the above problems, *HM-Keeper* is designed based on two principles: (1) The memory profiling mechanism must be adaptive based on spatial and temporal variation of memory access patterns. (2) The page migration must employ a holistic design principle, such that any slow memory tier has equal opportunities to directly use the fastest memory. HM-Keeper largely outperforms existing page management solutions on large memory systems. Memory-consuming applications such as in-memory databases, billionscale graph processing, and many other big data applications can greatly benefit from HM-Keeper.

The remainder of this dissertation document is organized as follows.

Chapter 2 includes background descriptions for the emerging of big memory applications 2.1, the emerging of advanced hardware techniques 2.2. Chapter 3 introduces *HM-ANN*, a efficient billion-point nearest neighbour search on HM-based big memory systems. Chapter 4 describes *Sentinel*, a efficient tensor migration and allocation solution on HM for deep learning. Chapter 5 proposes techniques used in *ZeRO-Offload* to democratizing billion-scale model training. Chapter 6 introduces a learning based approach to predict tensor accesses in DyNN called *DyNN-Offload*. Chapter 7 discusses *WarpX-PM*, which contains optimizing large-scale plasma simulations on HM with effective data placement across memory hierarchy. Chapter 8 introduces a scalable page management soluyion for multi-tiered big memory systems called *HM-Keeper*. Finally, we conclude in Chapter 9 with some exciting future directions.

# **Chapter 2**

# Background

## 2.1 **Big Memory Applications**

As application data sizes ever exploding, big memory applications are emerging. Big memory applications are used to solve big problems in math and science. The memory access patterns in big memory applications typically are complex and irregular. Traditional memory management techniques fail to scale in the necessary capacities and speeds to accelerate modern analytics. We summarize the commonly used big memory applications as follow.

Machine learning and artificial intelligence applications. Machine learning and artificial intelligence applications, such as deep neural networks (DNN), have been shown preliminary success in many field. The memory wall exist in both training and inference DNN models. For example, NLP model size has been increased 200x in last three years. Existing works try to reduce memory consumption and break the memory wall of deploying ML/AI applications, such as using low-precision tensors [236], distributed training [72, 115, 173, 195], tensor redundancy removal [172], tensor migration on heterogeneous memory [77, 79, 158, 178, 179], and tensor rematerialization [38, 55, 88, 100, 196].

Large-scale scientific simulations. Large-scale scientific simulations are widely used to understand physics, chemistry, and biology. Scientific simulation can be extremely memory-consuming. For example, in plasma simulation [30], the simulation quality depends on the number of particles used in the simulation. To enable high-resolution scientific simulation, hundreds of supercomputer nodes are used simultaneously [208, 210]. The large capacity of persistent memory (PM) provides the opportunity to enable extra-scale scientific simulation. However, memory management for scientific simulation is challenging due to its extremely complex data

Figure 2.1: The architecture of heterogeneous memory based big memory systems. access patterns.

**In-memory database.** In-memory database are widely used in cases where the response time is critical, such as real-time bidding and caching. Existing works deploy in-memory database on non-volatile memory DIMM (NVDIMM) to utilize NVDIMM's high memory capacity [1, 2, 8, 22, 46, 130, 213]. The data access patterns of in-memory database are usually irregular, depending on the data structure used in the database and database access distribution. The unique challenge in memory management at the operating system (OS) level for in-memory database at application-level, which can conflict with OS-level memory management. To get the best performance, memory management solutions must be coordinate at all system stacks.

### 2.2 Heterogeneous Memory Based Big Memory Systems

The emergence of advanced hardware technologies such as 3D XPoint, through silicon via (TSV) technology and fast interconnect, brings the potential of significantly increasing memory capacity or memory bandwidth while reducing memory production cost. We introduce real-world memory devices which as commonly used to build heterogeneous memory based big memory systems as follow.

|           |         | · · · ·               |                   |

|-----------|---------|-----------------------|-------------------|

|           | DRAM    | High Bandwidth Memory | Persistent Memory |

|           | DKAM    | (TSV)                 | (3D-Xpoint)       |

| Bandwidth | 1x      | 2x                    | 0.1 - 0.25x       |

| Latency   | 1x      | 0.75x                 | 4 - 8x            |

| Capacity  | limited | very small            | large             |

| \$/GB     | 1x      | $\sim 4x$             | 0.3x              |

Table 2.1: DRAM, HBM, PM comparison

Figure 2.1 shows the architecture of heterogeneous memory based big memory systems. The host memory system contains High Bandwidth Memory (HBM), traditional DRAM, and Persistent Memory. The host memory system can access data in accelerators' memory or fabric attached memory such as CXL device through PCIe. The host memory system can also access remote memory node through RDMA. Different memory components in figure 2.1 has significant difference in terms of memory access latency, bandwidth, capacity, and production cost. Table 2.1 summarize the difference between HBM, DRAM and PM.

# Chapter 3

# **Efficient Billion-Point Nearest Neighbor Search on Heterogeneous Memory**

The state-of-the-art approximate nearest neighbor search (ANNS) algorithms face a fundamental tradeoff between query latency and accuracy, because of small main memory capacity: To store indices in main memory for fast query response, They have to limit the number of data points or store compressed vectors, which hurts search accuracy. The emergence of heterogeneous memory (HM) brings opportunities to largely increase memory capacity and break the above tradeoff: Using HM, billions of data points can be placed in main memory on a single machine without using any data compression. However, HM consists of both fast (but small) memory and slow (but large) memory, and using HM inappropriately slows down query time significantly. In this work, we present a novel graph-based similarity search algorithm called HM-ANN, which takes both memory and data heterogeneity into consideration and enables billion-scale similarity search on a single node without using compression. On two billion-sized datasets BIGANN and DEEP1B, HM-ANN outperforms state-of-the-art compression-based solutions such as L&C [51] and IMI+OPQ [50] in recall-vs-latency by a large margin, obtaining 46% higher recall under the same search latency. We also extend existing graph-based methods such as HNSW and NSG with two strong baseline implementations on HM. At billion-point scale, HM-ANN is 2X and 5.8X faster than our HNSW and NSG baselines respectively to reach the same accuracy.

## 3.1 Introduction

Efficient billion-scale nearest neighbor search has become a significant research problem [23, 24, 90, 93], inspired by the needs of machine learning based applications. Since the number of entities (images, documents, etc) grows enormously fast, it becomes challenging to find correspondences in large datasets when there is a requirement for real-time responses (e.g., in several milliseconds). Exhaustive search is infeasible at billion-point scales, because it is extremely computational demanding. Hence, practitioners resort to indexing structures that perform the approximate nearest neighbor search (ANNS) by restricting a query to search only a subset of the dataset that includes the desired neighbors [29, 68, 108]. Among those ANNS, it has been demonstrated that similarity graphs, such as Hierarchical Navigable Small World (HNSW) [128] and Navigating Spread-out Graph (NSG) [58], obtain superior performance relative to tree structure based [28, 29, 136, 237], locality sensitive hashing (LSH) based [63], and inverted multi-index (IMI) based [108] approaches, and they overall provide the best-in-class latency-vs-accuracy trade-off on most public benchmark datasets.

While obtaining good search speed and accuracy, one major limitation of existing similarity graphs is that they are very memory consuming and easily run out of memory with a few hundred millions of vectors. When the dataset becomes too large to fit on a single machine, the compressed representations of the database points are used, such as Hamming codes [143] and product quantization [51, 59, 89, 94, 142]. However, the performance of these methods deteriorates rapidly at higher recall targets, because they calculate approximate distance based on compressed vectors instead of on the original data vectors. Douze et. al. [51] propose Linkand-Code (L&C), which combines a similarity graph with quantized nodes and exploits neighbor nodes to refine the estimation of distance. However, this approach still works poorly at high recall targets. In [198], the authors explore slow storage to achieve billion-scale ANNS in a single machine. However, this approach is based on a fundamental assumption that the persistent media such as SSD is several orders of magnitude slower than DRAM. Based on this assumption, data accesses to the persistent media during search should be zero. As a result, it maintains a copy of compressed data in memory with product quantization [198], which results in loss of in-memory search quality. It then preforms a re-ranking using full-precision coordinates stored on SSD, using block-level data accesses but with expensive SSD accessing time.

In this work, we present a fast and accurate approximate nearest neighbor search algorithm for extremely large scale ANN search, called HM-ANN, which is built on top of Heterogeneous Memory. Heterogeneous Memory (HM) combines cheap, slow but extremely large memory with expensive, fast but small memory (e.g., traditional DRAM) to achieve a good balance between production cost, memory performance and capacity. The emergence of HM brings opportunities to significantly improve ANNS. Because of the large memory capacity, HM can use full-precision vectors with accurate distance computation. Since memory access latency/bandwidth of slow memory component in HM is much faster than slow storage such as SSD, it is possible to occasionally access data in slow memory during search without paying expensive cost of data accesses. That being said, releasing full performance potential of HM for ANNS is challenging. Although the slow memory such as PMM performs ~80X times faster than SSD, it is still ~3X slower than DRAM in terms of random access latency. Therefore, a naive data placement strategy can hurt the search efficiency badly. It then raises the following research question: can we leverage HM for ANNS to achieve both high search accuracy and low search latency, especially when the dataset cannot in DRAM (fast memory)? Specifically, the algorithm should have a clear advantage over the state-of-the-art ANNS solutions.

HM-ANN enables fast and highly accurate billion-scale ANNS on HM. In particular, we make the following contributions. (1) We present a fast and accurate billion-scale nearest neighbor search solution on a single node without compression. Specially, we generalize the HNSW construction algorithm to have a top-down insertion phase and a bottom-up promotion phase. The top-down phase creates navigable small world graph as the bottom-most layer, which is also the largest, placed to the slow memory; The bottom-up promotion phase promotes pivot points from the bottom layer graph to form upper layers that are placed in the fast memory, which allows most search accesses to happen in fast memory without losing much accuracy. (2) We explore memory management techniques such as dynamic migration to prefetch to-be-accessed data from slow memory to fast memory and parallel search to reduce search time in slow memory. (3) We introduce a performance model to select search-related hyperparameters that satisfy search time and recall constraints. (4) We conduct extensive evaluation and show that on two billion-scale datasets, HM-ANN provides 95% top-1 recall in less than one millisecond; HM-ANN outperforms state-of-the-art compression-based solutions such as L&C [51] and IMI+OPQ [50] in terms of recall-vs-latency by a large margin, getting 46% higher recall under the same search latency budget; Since NSG and HNSW have never been scaled up to a billion vector on a single machine, we create two strong baselines for them: using first-touch NUMA and hardware-managed caching, respectively. Our results show that for 95% top-1 recall, HM-ANN outperforms the baselines by 2X-5.8X in terms of search latency.

### **3.2 Preliminary and Related Works**

#### **3.2.1** ANNS and Similarity Graphs

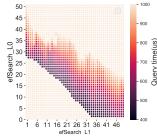

Similarity graphs like HNSW [128] and NSG [58] have demonstrated superior performance with polylogarithmic search and graph construction complexity for ANNS [54, 112, 198]. Take HNSW as an example, which consists of multiple layers. The bottom-layer (L0) contains all database elements, and the above layers are randomly selected, nested subsets of database elements. The sizes of the layers follow a geometric progression. During the graph construction phase, HNSW connects elements in each layer based on the closeness relationship. The connections of an element consist both long-range links and short-range links to establish the small world properties. HNSW constrains the length of the neighbors list of each element by a parameter M. HNSW starts the search at the top layer, and performs a *1-greedy search* until it reaches the nearest neighbor of the query in that layer. That node is then used as an entry point in the next layer to start search again. At the bottom layer L0, which contains all elements, HNSW performs a *best-first beam search* to get the final candidates. HNSW uses a parameter *efSearch*, which decides the candidate queue length, to control search time vs. accuracy trade-off. Despite their outstanding performance, similarity graphs are memory-consuming. For example, for the Deep1B [23] dataset, they require 384 bytes per vector, which translates to >350 GB DRAM when including all overheads of data structures, causing out-of-memory failure. Therefore, existing work mostly evaluate their solutions with a few millions vectors [58, 128].

### 3.2.2 Heterogeneous Memory

Heterogeneous memory (HM) is emerging. It combines multiple memory components to construct main memory. HM is typically composed of a high-capacity memory technology such as non-volatile memory (but high memory access latency) and a high-performance memory technology (with limited memory capacity) such as DRAM. To make HM performance close to that of DRAM-only, previous work focuses on hardware- [13, 31, 168, 169, 215] and software-based [52, 116, 125, 180, 223, 226, 227] solutions to manage data placement on HM. Optane PMM and DRAM are commonly used to build HM. With PMM, the memory capacity on a single machine can achieve 6TB [87]. However, the latency and bandwidth of PMM is only 1/3 and 1/6 of DRAM. There are two operating modes for PMM, *Memory Mode* and *App-direct Mode*. In Memory Mode, DRAM works as a hardware-managed cache to PMM. Running the application in this mode does not require application modifications. App-direct Mode allows the programmer to explicitly control memory accesses to PMM and DRAM. HM-ANN works in App-direct Mode

and outperforms Memory Mode in billion-scale dataset search (Section 3.4).

### 3.3 HM-ANN

The design of HM-ANN generalizes HNSW, whose hierarchical structure naturally fits into HM. Elements in upper layers consume a small portion of the memory, making them good candidates to be placed in fast memory (small capacity); The bottom-most layer has all the elements and has the largest memory consumption, which makes it suitable to be placed in slow memory. Unlike HNSW, where the majority of search happens in the bottom-most layer, elements in upper layers now have faster access speed, so it is a reasonable strategy to increase the access frequency of upper layers. On the other hand, since accessing L0 is slower, it is preferable to have only a small portion of it to be accessed by each query. The key idea of HM-ANN is therefore to build high-quality upper layers and make most memory accesses happen in fast memory, in order to provide better navigation for search at L0 and reduce memory accesses in slow memory.

**Notations.** In the rest of the paper, we let V denote the dataset with N = |V| to build the graph; we refer the graph in the layer  $i \in \{0, 1, ..., l\}$  of HM-ANN as  $G_i = (V_i, E_i)$  where  $V_i$  is the vertex set and  $E_i$  is the edge set. We refer  $N_i$  as the number of elements in the layer i, and we have  $N_i = |V_i|$ . Because L0 contains all the elements in database, we have  $V_0 = V$  and  $N_0 = N$ . Based on the hierarchical structure of HM-ANN, we have  $V_i \subsetneq V_{i-1}$ . Similar to the existing effort [128], we introduce  $M_i$  as the maximum number of established connection for each point v in the layer i. For  $v \in V$ , we let D(v) denote the degree of node v, and  $D(v) = \sum_{u \in V} m(v, u)$  where m(v, u) = 1 if there exits a link between node v and node u.

### 3.3.1 Graph Construction via Top-Down Insertions and Bottom-up Promotions

We generalize the HNSW construction algorithm to include two phases: a top-down insertion phase and a bottom-up promotion phase (Alg. 1).

**Top-down insertions.** The top-down insertion phase is the same as HNSW (Line 1 in Algorithm 1), where we incrementally build a hierarchical graph by iteratively inserting each vector v in V as a node in G. Each node will generate up to M (i.e., the neighbor degree) out-going edges. Among those, M - 1 are short-range edges, which connect v to its M - 1 nearest neighbors according to their pair-wise Euclidean distance to v. The rest is a long-range edge that connects v to a randomly picked node, which may connect other isolated clusters. It is theoretically justified that graphs (e.g., L0) constructed by inserting these two types of edges guarantees to have the small world properties [58, 128, 221].

**Bottom-up promotions.** The goal of the second phase is to build a high-quality projection of L0 elements into the layer 1 (L1), such that search in L0 can find true nearest neighbours of the query with only a few number of hops. Ideally, HM-ANN wants to achieve the goal that performing 1-greedy search in L0 is sufficient to achieve high recall, so that the slowdown caused by accessing the slow memory is minimal. A straightforward way to project the L0 elements into L1 is to randomly select a subset of elements in L0 to be L1, similar to what HNSW already does to build upper layers. However, we observe that such an approach leads to poor index quality. As a result, many searches end up happening in L0 (slow memory), causing long search latency.

\_

| Algorithm 1: HM-ANN Graph Construction Algorithm.                                                    |  |  |

|------------------------------------------------------------------------------------------------------|--|--|

| <b>Input:</b> vector set $V$ , vector dimension $d$ , number of established connection $M$ , size of |  |  |

| dynamic candidate list efConstruction                                                                |  |  |

| Output: Multi-layer graph HM-ANN                                                                     |  |  |

| <b>Parameters :</b> # of nodes in layer $i N_i$ , HM-ANN layer depth $l$                             |  |  |

| 1 build graph $hnsw \leftarrow HNSW(V, d, M, efConstruction)$ ;                                      |  |  |

| 2 for $v in V$ do                                                                                    |  |  |

| 3 $D[v] \leftarrow$ the degree of $v$ as in zero-layer L0;                                           |  |  |

| 4 sort $D$ for descending order ;                                                                    |  |  |

| 5 remove nodes in layer 1 to $l$ ;                                                                   |  |  |

| 6 $ep \leftarrow$ get the highest degree node $v$ in $D(v)$ ;                                        |  |  |

| 7 for $v$ in $V$ in $D(v)$ descending order do                                                       |  |  |

| 8 for $i \leftarrow l1$ do                                                                           |  |  |