## **UC Santa Cruz**

#### **UC Santa Cruz Electronic Theses and Dissertations**

#### **Title**

Thermal-Aware CAD for Modern Integrated Circuits

#### **Permalink**

https://escholarship.org/uc/item/8nk4056k

#### **Author**

Logan, Sheldon Logan Paul

#### **Publication Date**

2013

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA SANTA CRUZ

### THERMAL-AWARE CAD FOR MODERN INTEGRATED CIRCUITS

A dissertation submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

**COMPUTER ENGINEERING**

by

**Sheldon Logan**

June 2013

|              | is approved:                        |

|--------------|-------------------------------------|

|              | Professor Matthew R. Guthaus, Chair |

|              | Professor Jose Renau                |

|              | Professor Martine Schlag            |

| Tyrus Miller |                                     |

Vice Provost and Dean of Graduate Studies

The Dissertation of Sheldon Logan

Copyright © by

Sheldon Logan

2013

## **Table of Contents**

| Li | st of I  | Figures                                                   | vi  |

|----|----------|-----------------------------------------------------------|-----|

| Li | st of T  | Tables                                                    | ix  |

| Al | Abstract |                                                           |     |

| A  | cknow    | eledgments                                                | xii |

| 1  | Intr     | oduction                                                  | 1   |

|    | 1.1      | Thesis Contributions and Outline                          | 3   |

| 2  | Bacl     | ground and Previous Work                                  | 5   |

|    | 2.1      | Floorplanning                                             | 5   |

|    |          | 2.1.1 Area                                                | 6   |

|    |          | 2.1.2 Wirelength                                          | 6   |

|    |          | 2.1.3 Temperature                                         | 9   |

|    | 2.2      | Floorplanning Representation                              | 9   |

|    |          | 2.2.1 SP Representation                                   | 10  |

|    | 2.3      | Floorplanning Methods                                     | 12  |

|    |          | 2.3.1 Genetic Algorithms                                  | 13  |

|    |          | 2.3.2 Force Directed                                      | 13  |

|    |          | 2.3.3 Simulated Annealing                                 | 14  |

|    | 2.4      | SP Simulated Annealing Floorplanning                      | 14  |

|    |          | 2.4.1 SP Floorplanning Moves                              | 15  |

|    |          | 2.4.2 SP Floorplanning Cost Function                      | 15  |

|    | 2.5      | Flip Chip Packaging                                       | 16  |

|    |          | 2.5.1 C4 Bump Placement and Floorplanning Co-optimization | 17  |

|    | 2.6      | Power Supply Networks (PSNs)                              | 17  |

|    |          | 2.6.1 Electrical Modelling                                | 18  |

|    |          | 2.6.2 Electrical Simulation                               | 19  |

|    | 2.7      | PSN Requirements                                          | 19  |

|    |          | 2.7.1 Voltage Droop                                       | 20  |

|    | 2.8      | PSN Synthesis                                             | 21  |

|    |          | 2.8.1 Wire Sizing                                         | 21  |

|   |      | 2.8.2 Power Bump Placement                                             | 22         |

|---|------|------------------------------------------------------------------------|------------|

|   |      | 2.8.3 Decap Placement                                                  | 24         |

| 3 | The  | rmal Background                                                        | 26         |

| J | 3.1  | Heat Generation                                                        | 26         |

|   | 5.1  | 3.1.1 Transistor Switching Heating                                     | 26         |

|   |      | 3.1.2 Interconnect Joule Heating                                       | 28         |

|   | 3.2  | Substrate Temperature Modeling                                         | 31         |

|   | ٥    | 3.2.1 Thermal Modeling of Interconnect                                 | 33         |

|   | 3.3  | Thermal Reliability Issues                                             | 35         |

|   | 0.0  | 3.3.1 Negative Bias Temperature Instability                            | 35         |

|   |      | 3.3.2 Leakage Currents                                                 | 37         |

|   |      | 3.3.3 Thermal Effects on Interconnect Resistivity                      | 39         |

|   |      | 3.3.4 Thermal Effects on Electromigration                              | 40         |

|   |      | 3.3.5 Thermal Effects on Package Reliability                           | 41         |

| 4 | Imn  | proving IC Temperatures through Floorplanning                          | 47         |

| • | 4.1  | Floorplanning Influence on Overall Chip Temperature                    | 47         |

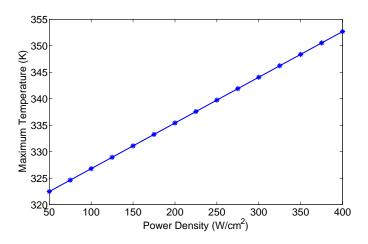

|   |      | 4.1.1 Temperature and Power Density                                    | 49         |

|   |      | 4.1.2 Temperature and Thermal Coupling                                 | 51         |

|   | 4.2  | Proposed Thermal Floorplanning Techniques                              | 53         |

|   | 1.2  | 4.2.1 Powerspreading Cost to Reduce Thermal Coupling                   | 54         |

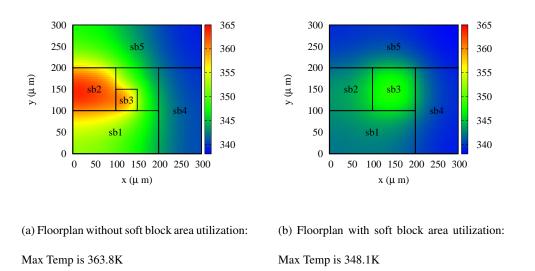

|   |      | 4.2.2 Whitespace Allocation to Lower Block Power Densities             | 57         |

|   | 4.3  | Proposed Thermal Floorplanning                                         | 59         |

| 5 | Miti | igating C4 Bump Failures from Thermal-Cyclic Fatigue                   | 61         |

|   | 5.1  | Bump Placement Effect on Package Reliability                           | 61         |

|   | 5.2  | Floorplanning Effect on Package Reliability                            | 63         |

|   | 5.3  | Floorplanning and Bump Placement Co-Optimization                       | 64         |

|   | 3.3  | 5.3.1 Quadratic Bump Placement                                         | 64         |

|   |      | 5.3.2 Proposed Floorplanning and bump placement Co-optimization        | 68         |

|   |      |                                                                        |            |

| 6 |      | ucing High Temperatures in Interconnect                                | <b>7</b> 0 |

|   | 6.1  | Using Decoupling Capacitance to Reduce PSN Interconnect Temperatures . | 71         |

|   | 6.2  | Decap Redistribution Algorithm to Reduce Joule Heating                 | 72         |

|   |      | 6.2.1 Partitioning and Budgeting                                       | 72         |

|   |      | 6.2.2 Sensitivity Simulation                                           | 73         |

|   |      | 6.2.3 Reallocation                                                     | 75         |

|   | 6.3  | Algorithm Example                                                      | 76         |

|   | 6.4  | Decap Redistribution Algorithm to Reduce Temperature                   | 77         |

| 7 | Red  | undant Power Bump Placement                                            | <b>7</b> 9 |

|   | 7.1  | Bump Failure Classification                                            | 81         |

|   |      | 7.1.1 Voltage violations                                               | 81         |

|   |      | 7.1.2 Electromigration violations                                      | 81         |

|   |      | 7.1.3 Calculating Bump Failure Violations                              | 82         |

|     | 7.2    | Bump Redundancy                                                     | 83       |

|-----|--------|---------------------------------------------------------------------|----------|

|     | 7.2    | 7.2.1 Generating the Redundancy Coverage Sets                       | 83<br>89 |

|     | 7.3    | Redundant Bump Set Generation                                       | 89<br>90 |

|     |        | 1                                                                   | 90       |

|     |        | 7.3.2 Improved Greedy Bump Redundancy                               | 90<br>91 |

|     | 7.4    | 7.3.3 ILP Bump Redundancy                                           |          |

|     | 7.4    | Algorithm Example                                                   | 92<br>92 |

|     |        | $\mathcal{E}^{-p}$                                                  | 92<br>94 |

|     |        | 7.4.2 Naive                                                         |          |

|     |        | 7.4.3 Improved Greedy                                               | 95       |

|     |        | 7.4.4 ILP                                                           | 96       |

|     | -      | erimental Setup                                                     | 99       |

|     | 8.1    | Thermal-Aware Floorplanner                                          |          |

|     | 8.2    | Floorplanning and Bump Placement Co-Optimization                    |          |

|     | 8.3    | Decap Redistribution                                                |          |

|     | 8.4    | Redundant Bump Placement                                            | 103      |

|     | Exp    | eriments                                                            | 105      |

|     | 9.1    | Thermal-Floorplanning Experiments                                   | 105      |

|     |        | 9.1.1 Fast Thermal Floorplanning                                    | 105      |

|     |        | 9.1.2 Dynamic Whitespace Allocation                                 | 106      |

|     |        | 9.1.3 Static Whitespace Allocation                                  | 108      |

|     |        | 9.1.4 Example Floorplanning Result                                  | 109      |

|     | 9.2    | Floorplanning and Bump Placement Co-optimization                    | 110      |

|     | 9.3    | Baseline Experiment - HPWL Optimization                             | 110      |

|     |        | 9.3.1 Temperature Optimization                                      | 112      |

|     |        | 9.3.2 Thermal Floorplanning with Bump Placement                     | 112      |

|     |        | 9.3.3 Example Floorplanning and Bump placement Result               | 114      |

|     | 9.4    | Decap Redistribution                                                | 115      |

|     |        | 9.4.1 Baseline Experiment                                           | 115      |

|     |        | 9.4.2 Decap Redistribution to Minimize Total Joule Heating Power    | 117      |

|     |        | 9.4.3 Decap Redistribution to Minimize $\Delta T \dots \dots \dots$ | 118      |

|     |        | 9.4.4 Additional Decap                                              | 120      |

|     | 9.5    | Redundant bump placement                                            |          |

|     |        | 9.5.1 Baseline Experiments                                          |          |

|     |        | 9.5.2 Naive Greedy Method                                           |          |

|     |        | 9.5.3 Improved Greedy Method and ILP                                |          |

|     |        | 9.5.4 Partial Coverage                                              |          |

| LO  | Cone   | clusion                                                             | 126      |

|     |        | Thesis Contributions                                                | 126      |

|     |        | Future Work                                                         |          |

| Ril | hlingr | raphy                                                               | 129      |

| •   | onogi  | чриј                                                                | 14       |

# **List of Figures**

| 2.1  | Two floorplans for the same circuit illustrating the concept of floorplanning whitespace                                                                               | 7  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | The differences in routing estimates for 5 pins using the various wirelength                                                                                           |    |

| 2.3  | metrics                                                                                                                                                                | 8  |

|      | tween the Blocks                                                                                                                                                       | 10 |

| 2.4  | The Ordering of Blocks based on Positive Step Lines <4 1 2 3>                                                                                                          | 10 |

| 2.5  | The Ordering of Blocks based on Negative Step Lines <1 2 4 3>                                                                                                          | 11 |

| 2.6  | Horizontal Constraint Graph                                                                                                                                            | 12 |

| 2.7  | Vertical Constraint Graph                                                                                                                                              | 12 |

| 2.8  | Flip Chip Package showing C4 connections                                                                                                                               | 16 |

| 2.9  | A Simple VDD Power Supply Network showing the basic Circuit Elements                                                                                                   |    |

|      | used to model the PSN                                                                                                                                                  | 18 |

| 2.10 | Voltage drop at a power supply node caused by the current draw of a transistor                                                                                         | 20 |

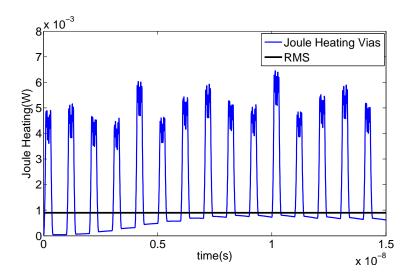

| 3.1  | An example from the ibmpg1 transient benchmark shows that Joule heating in the wires has a much larger RMS value than the power supply pads                            | 29 |

| 3.2  | An example from the ibmpg2 transient benchmark shows that lower metal layers suffer from larger Joule heating than global metal layers                                 | 30 |

| 3.3  | An example from the ibmpg2 transient benchmark shows that Joule heating in the vias between different metal layers is not very significant ( $1 \times 10^{-3}$ W). 31 |    |

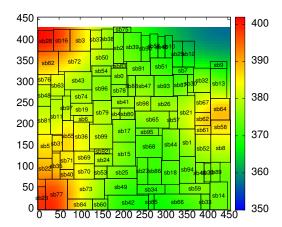

| 3.4  | IC temperature map for GSRC n100 circuit showing temperature hotspots. The circuit dimensions are in $\mu$ m and the temperature is in Kelvin (K)                      | 33 |

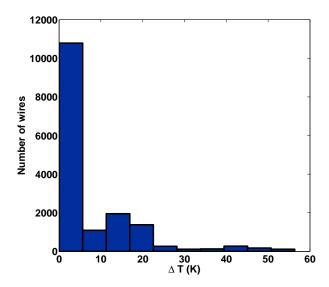

| 3.5  | Distribution of $\Delta$ Temperatures and actual Temperatures of wires for the IBMpg1 benchmark showing the skewed $\Delta$ Temperatures and less skewed               |    |

|      | wire temperatures                                                                                                                                                      | 36 |

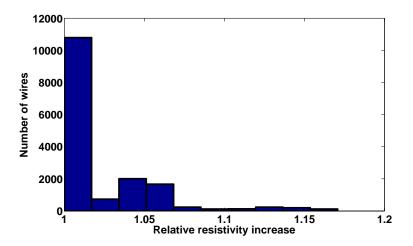

| 3.6  | Most wires experience a small change in resistance, but a few critical wires                                                                                           | 50 |

| 0.0  | experience large increases in resistance, up to 1.18 times the original value.                                                                                         | 40 |

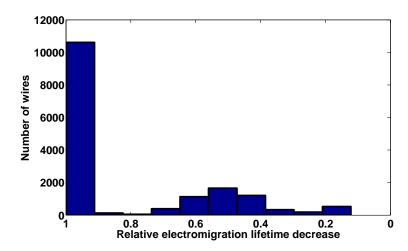

| 3.7  | Most wires experience a small decrease in electromigration lifetime. However a significant amount of wires have their lifetime reduced to 0.5 of the                   | .0 |

|      | original value and some have as high reductions as 0.2 of the original value.                                                                                          | 41 |

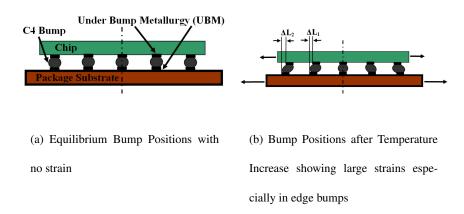

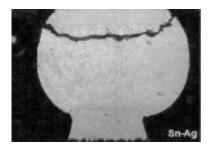

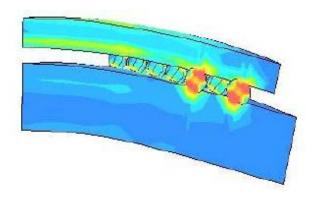

| 3.8<br>3.9 | CTE mismatch causes large strains in C4 bumps                                                                                                                                                                                                                                                                                                         | 42<br>43 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

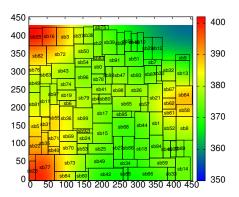

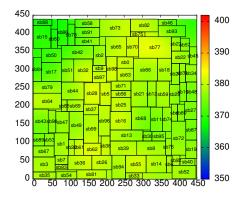

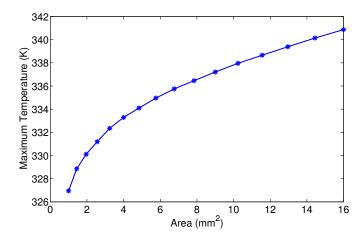

| 4.1        | Example floorplans from n100 showing how block layout can affect peak temperature.                                                                                                                                                                                                                                                                    | 48       |

| 4.2        | Maximum temperature vs power density for an isolated block showing a linear relationship.                                                                                                                                                                                                                                                             | 49       |

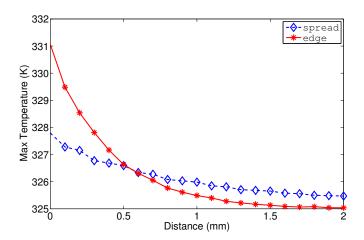

| 4.3        | Soft block area utilization can reduce maximum temperatures significantly.                                                                                                                                                                                                                                                                            | 50       |

| 4.4<br>4.5 | Hard block area utilization can reduce maximum temperatures also Maximum temperature vs distance from edge for a 100 W/cm² block (red) showing decrease in maximum temperature as block's distance from the edge increases. Maximum temperature vs separation distance for two 100 W/cm² (blue) blocks showing decrease in maximum temperature as the | 51       |

| 4.6        | blocks are moved further apart                                                                                                                                                                                                                                                                                                                        | 52       |

|            | sity.                                                                                                                                                                                                                                                                                                                                                 | 53       |

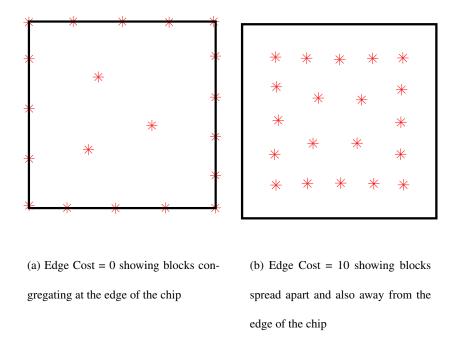

| 4.7        | Simple floorplan showing the necessity of including an edge cost to move blocks from the edge of a chip                                                                                                                                                                                                                                               | 56       |

| 5.1        | Two Floorplans for the GSRC N50 Benchmark showing different bump placements and consequently different minimum number of cycles to fail-                                                                                                                                                                                                              |          |

| 5.2        | ure                                                                                                                                                                                                                                                                                                                                                   | 62<br>63 |

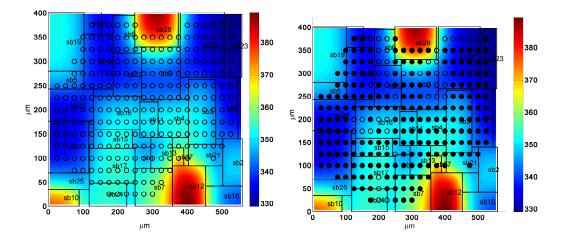

| 5.3<br>5.4 | Example bump placement flow for n30 benchmark                                                                                                                                                                                                                                                                                                         | 66<br>69 |

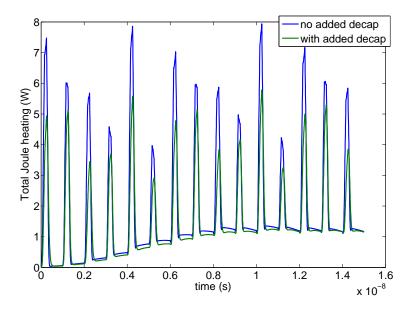

| 6.1        | Decap is a viable mechanism for reducing Joule heating power as can be seen by the reduced peaks of total Joule heating.                                                                                                                                                                                                                              | 72       |

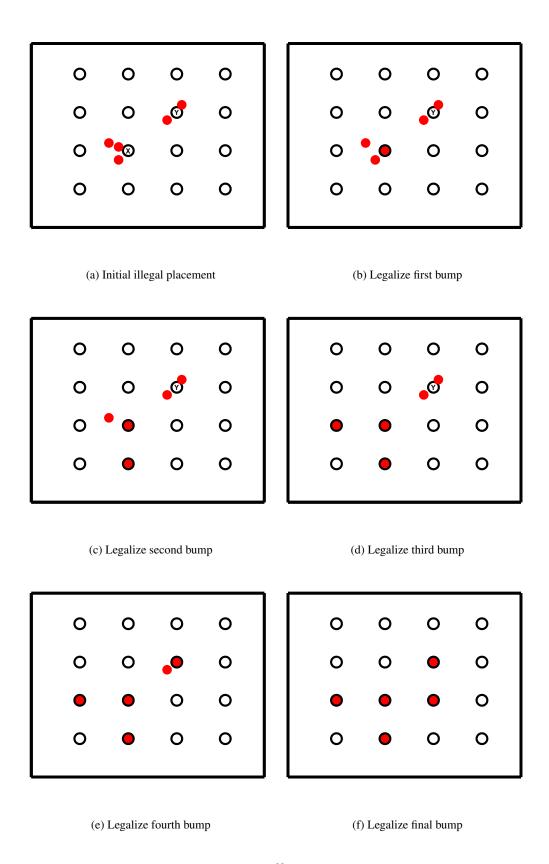

| 6.2        | Initial decap allocation and redistribution for first stage of the algorithm                                                                                                                                                                                                                                                                          | 70       |

| 6.3        | with decap percentages represented by the size of the shaded area Decap is moved from the $\delta C_i$ s of the low sensitivity blocks (A and B) to                                                                                                                                                                                                   | 76       |

| 0.5        | the $\delta C_i$ s of the high sensitivity blocks (C and D)                                                                                                                                                                                                                                                                                           | 77       |

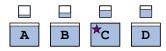

| 7.1        | Example from ibmpg2 benchmark showing voltage violations and electromigration failures caused by a single-bump defect. Bumps are represented as large circles and node voltages represented as small circles. Only a small fraction of the entire benchmark is shown for image clarity with dimensions                                                | 00       |

| 7.2        | in $\mu$ m                                                                                                                                                                                                                                                                                                                                            | 80<br>82 |

| 7.3        | Current slack model showing exponential relationship and approximated relationship with fewer data points                                                                                                                                                                                                                                             | 86       |

| 7.4        | Linear model of redundant bump placement for a failing bump causing static voltage failures in the ibmpg2 benchmark                                                                                                                                                                                                                                   | 88       |

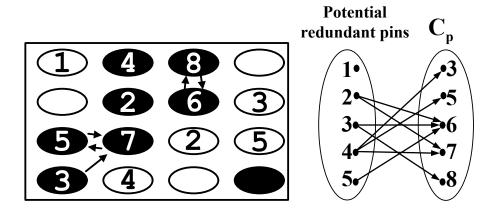

| 7.5 | Example bump placement, showing corresponding redundancy mappings.                |     |

|-----|-----------------------------------------------------------------------------------|-----|

|     | An arrow from a the redundant bump location to a bump in the opposing             |     |

|     | set, means that bump is covered by that redundant bump location                   | 93  |

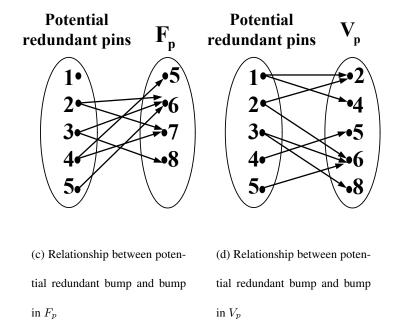

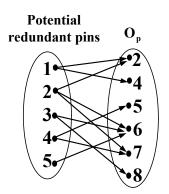

| 7.6 | Relationship between potential redundant bump and bump in $O_p$ $(F_p \cup V_p)$  | 94  |

| 7.7 | ILP constraints and corresponding matrix for $O_p$ set shown in Figure 7.6.       | 97  |

| 7.8 | ILP constraints and corresponding matrix for $O_p$ set considering partial        |     |

|     | coverage                                                                          | 98  |

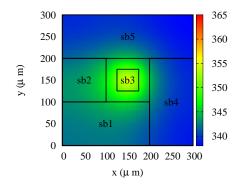

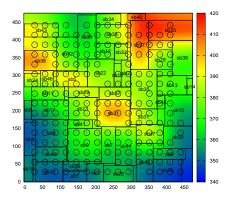

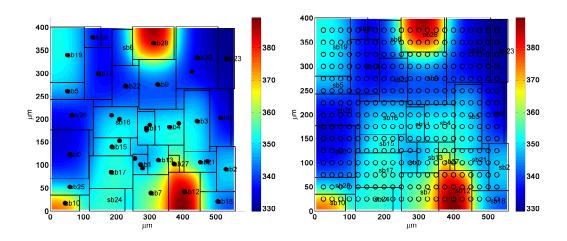

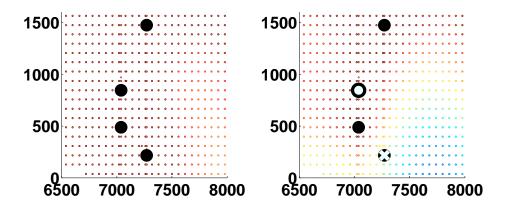

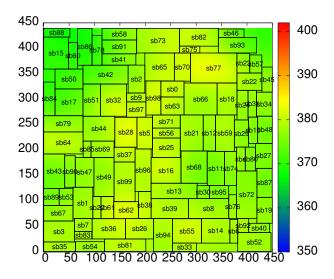

| 9.1 | Example results for n100 benchmark showing how significant reductions in          |     |

|     | floorplan temperatures by using the proposed thermal-aware floorplanning methods. | 111 |

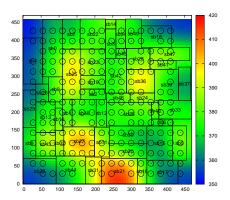

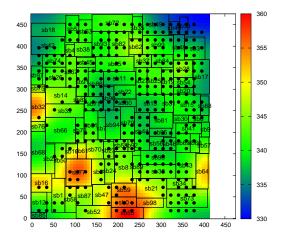

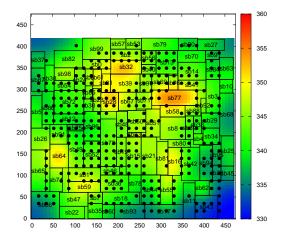

| 9.2 | Example Results for n100 Showing Increase in Bump Reliability (100×)              |     |

|     | Using Proposed Methods                                                            | 116 |

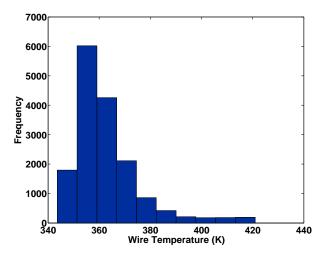

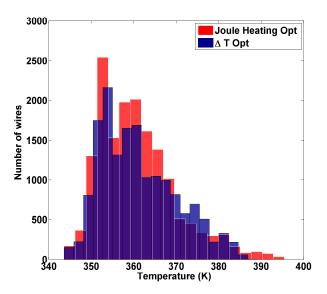

| 9.3 | The ibmpg1t benchmark illustrates that the $\Delta T$ optimized decap redistribu- |     |

|     | tion has fewer wires in the high temperature bins as compared to the Joule        |     |

|     | heat optimized decap redistribution                                               | 119 |

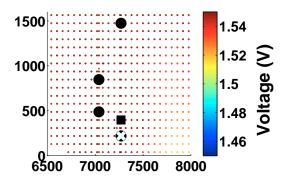

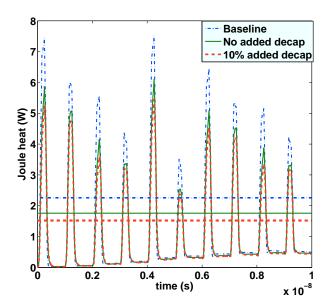

| 9.4 | An example from the ibmpg1t benchmark shows the decrease in total Joule           |     |

|     | heating in wires when redistributing decap and adding additional decap.           |     |

|     | Horizontal lines represent RMS values.                                            | 122 |

## **List of Tables**

| 7.1         | Definitions of Terminology                                                                                                                                     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.1         | Peak Temperature Optimization Results Showing That The Proposed Power                                                                                          |

|             | Metric Can Significantly Reduce Floorplan Temperatures                                                                                                         |

| 9.2         | Dynamic Whitespace Utilization Peak Temperature Results for Hard and                                                                                           |

|             | Soft Blocks Showing Further Reduction in Floorplan Temperatures 108                                                                                            |

| 9.3         | Static Whitespace Utilization Peak Temperature Results for Soft Blocks                                                                                         |

|             | Showing Increased Reduction in Floorplan Temperatures 109                                                                                                      |

| 9.4         | Temperature Optimization Results Showing Increase in Bump Reliability . 113                                                                                    |

| 9.5         | Bump Placement Optimization Results Showing Added Increase in Bump                                                                                             |

|             | Reliability                                                                                                                                                    |

| 9.6         | Joule heating reduces the PSN interconnect electromigration lifetime by up                                                                                     |

|             | to 0.12×                                                                                                                                                       |

| 9.7         | Joule heating-aware decap redistribution increases interconnect electromi-                                                                                     |

|             | gration reliability by an average of $1.39 \times \dots \dots 118$                                                                                             |

| 9.8         | Temperature-aware decap redistribution increases interconnect electromi-                                                                                       |

|             | gration reliability by an average of $1.66 \times \dots \dots$ |

| 9.9         | Adding 10% more decap increases interconnect electromigration reliability                                                                                      |

|             | by an average of $2.20 \times \dots \times 121$                                                                                                                |

| 9.10        |                                                                                                                                                                |

| ,,,,        | Redundant Sets Generated by Using the ILP Formulation vs. The Naive                                                                                            |

|             | Method                                                                                                                                                         |

| 9.11        | Bump Redundancy Set Generation using Partial Coverage Showing De-                                                                                              |

| <b>7,11</b> | crease in Size of Redundant Sets When Partial Coverage is Considered 125                                                                                       |

#### **Abstract**

#### Thermal-Aware CAD for modern integrated circuits

by

#### Sheldon Logan

Power density in modern integrated circuits (ICs) continues to increase at an alarming rate. In turn, larger power densities result in higher peak temperatures which can reduce chip reliability and further increase leakage power consumption. Thermal-aware CAD design is a method to combat these problems. However most existing thermal-aware CAD research has focused on thermal-aware floorplanning and placement. These thermal-aware floorplanners have several problems such as long execution times and being limited to only one method of reducing peak temperatures. In addition most thermal-aware CAD research has only focused on reducing chip peak temperatures and not other reliability concerns such as high interconnect temperatures, wire/C4 bump electromigration, and thermal-cyclic C4 bump failure.

This thesis proposes several new algorithms and methodologies that can be used to directly reduce high on chip temperatures and mitigate the reliability concerns caused by these high temperatures. Experimental results show that the proposed thermal-floorplanning moves based on whitespace utilization, coupled with a method of quickly evaluating temperature effects can reduce on chip-temperatures on average by 7K with only a modest 4.2% increase in wirelength and 1.12x increase in execution time. In addition, a method for cooptimizing floorplanning and C4 bump placement using a quadratic optimization process is shown to increase the lifetime of bumps from thermal-cyclic fatigue by  $47\times$  with only

a modest 3% increase in HPWL wirelength. To combat bump electromigration, a single-bump redundancy technique based on Integer Linear Programming (ILP) is proposed, and shown to be able to reduce the number of redundant bumps to guarantee single-bump redundancy by 68% as compared to a naive bump placement approach. Finally, an algorithm to redistribute decoupling capacitance, is shown to be able to reduce interconnect temperatures by 12.5K on average and provide a  $1.66\times$  increase in electromigration lifetime.

#### Acknowledgments

First of all, I would like to thank God, my Lord and saviour for guiding me through the many troubles and tribulations that I have encountered through my PhD.

I would like to also express my deepest gratitude to my adviser Matthew Guthaus, without his help and motivation I would have never seen the finish line. I thank him for initially taking me into his lab during my second year in graduate school at a point where I was lost and indifferent about graduate school and research. I thank him for his initial patience as I got up to speed in CAD and his continual motivation along the way, which quelled the many thoughts I have had of quitting. More importantly, I want to thank him for his contribution of ideas, thoughts and funding, which allowed me to finish my PhD.

In addition to my adviser, I would like to thank the rest of my thesis committee:

Professor Jose Renau and Professor Martine Schlag for their assistance for helping me complete my thesis.

I thank my fellow lab-mates in UCSC VLSI-DA group: Seokjoong Kim, Xuchu Hu, Rajsaktish Sankaranarayanan, Marcelo Siero, Walter Condley, Derek Chan and Keven Woo, for their friendships but more importantly the ideas and contributions that allowed me to finish my PhD.

I also wish to thank the graduate adviser Carol Mullane, for her help during my PhD journey. She always willing to provide suggestions and helped me with a lot of paperwork and special problems.

I would also to like to thank my friends from church and from graduate school (Audries Blake, Emily Scheese, Sarah Romano, Neil Miller and Mikhail Rudenko) that I

have accumulated during my time in Santa Cruz who encouraged me to reach my goal.

Last but not the least, I would thank my parents and extended family that helped me along the journey with their countless words of motivation and support. Without them, it would have been impossible to complete my journey.

## **Chapter 1**

## Introduction

High on-chip temperatures have quickly become one of the major concerns for modern integrated circuit (IC) designers. Extreme power densities due to the aggressive scaling of transistor sizes have resulted in large peak temperatures and drastic temperature gradients. These large peak temperatures and gradients lead to several reliability concerns in modern integrated circuits such as electromigration, NBTI, increases in leakage power and thermal-cyclic fatigue. Consequently, most designers now consider temperature, along with power, in the early parts of the design phase.

Reducing the overall chip temperature is one of the best methods of combating the reliability concerns caused by high temperatures in modern ICs and this is usually done via thermal-aware floorplanning [7,17,18,26,33,48,49,62,114]. Thermal-aware floorplanning, consists of adjusting the cost function of a floorplanner to include some temperature metric in addition to the other typical design metrics.

Thermal-aware floorplanning however, can only reduce the high IC temperatures by a certain amount with the resulting IC temperatures potentially still leading to other

reliability problems such as mechanical failure of C4 solder bumps. These bumps fail due to thermal-cyclic fatigue which is caused by the coefficient of thermal expansion (CTE) mismatch between the substrate and package.

Another reliability issues caused by high IC temperatures is the increase in interconnect resistivity and electromigration. Resistivity increases result in IR drop and voltage droop violations leading to timing and signal integrity issues [88]. Increases in interconnect electromigration can potentially lead to breaks in the interconnect or failure of C4 bumps, which would result in complete IC failure.

The increases in resistivity and electromigration are only going to worsen as designs move to smaller technologies. Decreased wire cross section areas, lower supply voltages and low-K dielectrics between metal layers all increase interconnect temperatures [12, 28, 36]. Lower supply voltages result in higher currents due to the inverse proportional relationship between voltage and current. Low-K dielectrics exacerbate the temperature problems since the dielectric used to electrically insulate the various metal layers have very low thermal conductivity which leads to poor dissipation of heat from the metal wires, especially in the higher layers. 3D-ICs further suffer from this problem because interconnect layers in the highest tiers are located very far from the heat sink.

Other reliability issues caused by high IC temperatures are increases in NBTI and increases in circuit leakage. NBTI is the degradation of the threshold voltages, drive currents and noise margins in negative bias transistors. These degradations can lead to circuit timing errors and in the worst case, catastrophic circuit failure. The magnitude of circuit current leakage is strongly correlated to temperature and thus, high chip temperatures can lead to dramatic increases in power usage due to the sudden increase in leakage current.

#### 1.1 Thesis Contributions and Outline

This thesis proposes several CAD algorithms and methodologies that reduce high IC temperatures and also mitigate the reliability issues caused by these temperatures. Chapter 2 introduces the background for the algorithms and methodologies and Chapter 3 introduces the thermal background knowledge required to understand them. The algorithms and methodologies are detailed in Chapters 4, 5, 6, 7. The experimental setup for the algorithms and methodologies are presented in Chapter 8 and the results and discussions from these experiments are detailed in Chapter 9. Finally the contributions of this thesis are concluded in Chapter 10.

Chapter 4 contains the contributions to thermal floorplanning. It introduces an effective way to lower maximum temperatures in floorplanning by adjusting white space usage, in addition to moving blocks around in a floorplan, which is what is typical done. It also presents a power metric cost for thermal floorplanning that is faster than other methods and still results in excellent solutions [53].

Chapter 5 contains the contributions to thermal-cyclic bump fatigue. It first introduces a simplified stress/strain/fatigue model for C4 solder bumps that can be used during floorplanning to guide C4 bump placement. It then presents a quadratic C4 bump placement algorithm that optimizes for both wirelength and reliability which can be used to increase the lifetime of C4 bumps from thermal-cyclic fatigue [54].

Chapter 6 contains the contributions to the area of reducing interconnect temperatures. It presents a methodology for the redistribution and/or allocation of decoupling capacitance (decap) to reduce the Joule heating power in the PSN interconnect. The method-

ology is based on a gradient-based algorithm and can lead to significant increases in PSN integrity.

Finally Chapter 7 contains the contribution to reducing the impact of interconnection electromigration in circuits. It presents a methodology to create PSNs that are single-bump redundant, meaning if any bump fails due to electromigration and/or manufacturing the PSN will still be able to meet its' requirements. The methodology uses an Integer Linear Program (ILP) to generate the smallest set of redundant bumps to guarantee single-bump redundancy. The chapter also presents a methodology which uses thermal modeling for determining which bumps are critical to the PSN design and it is also the first work to consider C4 bump manufacturing defects in PSN design.

## **Chapter 2**

## **Background and Previous Work**

This chapter provides background information on the various VLSI problems addressed throughout the thesis and also details the CAD algorithms and methodologies proposed by other researchers to combat these problems. Sections 2.1, 2.2, 2.3 and 2.4 analyzes the floorplanning problem and shows how previous researchers have tackled thermal-aware floorplanning. Sections 2.5 introduces the concept of flip-chip packaging and analyzes the flip-chip C4 bump placement problem. Finally, Sections 2.6, 2.7 and 2.8 introduces the concept of a Power Supply Network (PSN) and then analyzes the various problems associated with PSN synthesis: wire sizing, decap placement, and power bump placement.

## 2.1 Floorplanning

The floorplanning problem is defined as follows: Given a set of blocks, find the optimal orientation of those blocks to minimize certain design metrics such that no blocks overlap. The classical floorplanning design metrics are area and wirelength. Recently floorplanning has been extended to consider other metrics such as maximum temper-

ature [7, 17, 18, 26, 33, 48, 49, 62], power supply noise [10, 111] and leakage [27, 114]. This thesis focuses on the classical metrics in addition to maximum temperature.

#### 2.1.1 Area

The floorplan area metric (Area<sub>f</sub>) is calculated as

$$Area_f = width_{max} \times height_{max}$$

(2.1)

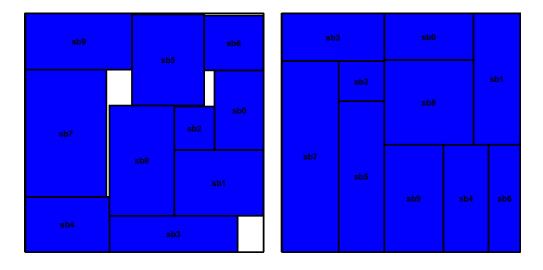

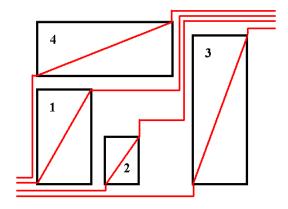

where width $_{\rm max}$  is the maximum width of the floorplan and height $_{\rm max}$  is the maximum height of the floorplan. If the area of the floorplan is larger than the total area of the blocks then the floorplan contains whitespace. More formally, floorplanning whitespace is defined as any area within the floorplan that is not being occupied by a block. Figure 2.1 shows two floorplans for a circuit. Figure 2.1(a) contains whitespace while Figure 2.1(b) contains no whitespace.

Recently, researchers have focused on fixed-area floorplanning [1, 3]. In fixedarea floorplanning the area metric is modified to

$$Area_{f} = \begin{cases} 1 & \text{if } (width_{max} \times height_{max} < Area_{fix}) \\ \frac{width_{max} \times height_{max}}{Area_{fix}} & \text{otherwise} \end{cases}$$

(2.2)

where  $Area_{fix}$  is the area designated to hold the floorplan.

#### 2.1.2 Wirelength

The wirelength metric is used to estimate the total wiring required to route the pins within the floorplan. There are three main methods to estimate wirelength, Half Perimeter Wirelength (HPWL), Steiner Wirelength and rectilinear Minimum Spanning Tree

- (a) Floorplan with whitespace  ${\rm Area}_f > {\rm Total}$  area of blocks

- (b) Floorplan with no whitespace. Area $_f$  = Total area of blocks

Figure 2.1: Two floorplans for the same circuit illustrating the concept of floorplanning whitespace

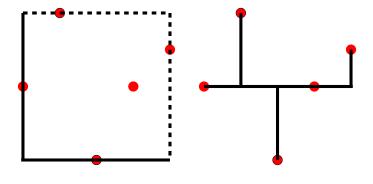

(MST) Wirelength as shown in Figure 2.2. HPWL is the estimate used in this thesis since most floorplanners in literature use this metric [1,2,7,8,18,33,40,49,62,114] and also due to the ease and quickness of HPWL calculation. Some floorplanners in the past however have used the other estimation techniques [73,79].

HPWL estimates wirelength by creating a bounding box around all the pins and taking half the perimeter of the bounding box as an estimate of the total wiring required to route that pin as shown in Figure 2.2(a). Steiner based estimates calculates the wirelength by creating a Steiner tree using the pins as vertices and using the sum of the edge lengths of the tree as the wirelength estimate as shown in Figure 2.2(b). Minimum spanning tree estimates calculates the wirelength by creating a Minimum Spanning tree using the pins as vertices and using the sum of the edge lengths of the tree as the wirelength estimate as

- (a) Routing estimate for 5 pins using the HPWL estimate

- (b) Routing estimate for 5 pins using the Steiner wirelength es-

timate

(c) Routing estimate for 5 pins using the MST estimate

Figure 2.2: The differences in routing estimates for 5 pins using the various wirelength metrics.

shown in Figure 2.2(c).

Wirelength estimation is also used during floorplanning to estimate routing congestion within floorplanning blocks. Blocks with potential high routing congestion have their area increased as a method of mitigating potential routing problems. This technique is

called area utilization.

#### 2.1.3 Temperature

The temperature metric of choice for most floorplanners is the maximum temperature of the floorplan [7,17,18,26,33,48,49,62,114]. However, using maximum temperature as a floorplanning metric significantly increases the runtime of the floorplanner since computing thermal profiles takes much longer than calculating the other metrics such as floorplan area or HPWL. Most previous floorplanning research has used grid-based thermal simulators [26,33,114] which require significant amount of time to compute thermal profiles. Some researchers [17,48] have tried to decrease the runtime for calculating thermal profiles by using a simplified thermal model, but this results in significant loss of accuracy in maximum temperature calculations and consequently suboptimal floorplanning solutions. In general, most floorplanners trade off accuracy in temperature calculations for run-time. The temperature is typically modeled using detailed finite-element (FEM) simulation [11,96], compact resistive network modeling [82], or other approximations [67,94,107].

### 2.2 Floorplanning Representation

Each floorplan in the solution space is represented using some form of floorplanning representation such as Sequence Pair (SP) [58], B\*-tree, [8], Corner Block List [31, 56], slicing tree [43, 105] or Transitive Closure Graph TCG [50]. The floorplanners proposed in this thesis are based on SP representation due to its simple data structure and efficient representation.

### 2.2.1 SP Representation

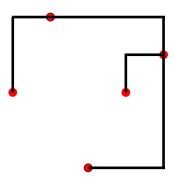

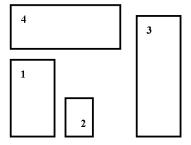

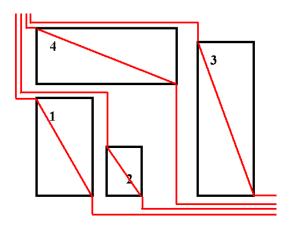

The SP representation consists of two sequences, positive and negative step lines, which capture the geometric information of a floorplan. Figure 2.4 and Figure 2.5 show the positive and negative step lines respectively for the floorplan shown in Figure 2.3. The sequence pair for the floorplan is thus  $<4 \ 1 \ 2 \ 3>$  (positive) and  $<1 \ 2 \ 4 \ 3>$  (negative).

Figure 2.3: A Floorplan Containing 4 Blocks showing the Geometric Relationships between the Blocks

Figure 2.4: The Ordering of Blocks based on Positive Step Lines <4 1 2 3>

The order of the blocks in the two sequence determines the geometric orientation of the blocks. If block x occurs before block y in both sequences then block x is to the left

Figure 2.5: The Ordering of Blocks based on Negative Step Lines <1 2 4 3>

of y. An example of this relation is blocks 1 and 3. However, if block x occurs before block y in the positive sequence and block y occurs before block x in the negative sequence then block x is above y. Blocks 1 and 4 are a good example of this relation. There are several methods of obtaining a floorplan from a sequence pair. The method that is used in the thesis is longest common subsequence ([86]).

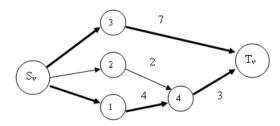

Another method of compacting a sequence pair uses horizontal and vertical constraint graphs. These graphs are constructed from the "left of" and "below" constraints obtained from the sequence pair. An example of the horizontal and vertical constraint graphs obtain from the floorplan in Figure 2.3 are shown in Figure 2.6 and Figure 2.7, respectively. The weight of the vertices in the horizontal and vertical constraint graphs are the width and height of the blocks. The longest path in the vertical and horizontal constraint graph represents the height and width of the chip. The x coordinate and y coordinate of a block is calculated by finding the longest path to that block in the horizontal and the vertical constraint graphs respectively. Consequently the blocks are packed in a down and to the left

manner.

Figure 2.6: Horizontal Constraint Graph

Figure 2.7: Vertical Constraint Graph

## 2.3 Floorplanning Methods

There are many different methods of solving the floorplanning problem. Most of the methods however can be separated into two categories, iterative approaches and constructive approaches. Iterative methods include simulated annealing [1, 2, 8, 17], force-directed approaches [114] and genetic algorithms [33]. Constructive methods include analytical [40] and structural partitioning [16]. The method of floorplanning used throughout the thesis is simulated annealing since it is the method used by most previous thermal-aware floorplanners [7, 15, 17, 33, 102] and its ease of implementation.

#### 2.3.1 Genetic Algorithms

Genetic Algorithms are iterative methods of searching through a solution space that try to mimic evolutionary principles. They make changes to an initial set of solutions (called an initial population) by the use of three operators: crossover, mutation and reproduction. Each initial solution is called a chromosome and the quality of each solution is evaluated using a fitness function. Reproduction finds high quality chromosomes and duplicates them. Crossover selects two random chromosomes and swaps some portions of each chromosome with some probability. Finally, the mutation operator takes a chromosome and randomly changes a portion of it. These three operators are applied to the initial population to produce a new population and the process is repeated until a stopping criterion is met. Hung *et al.* [33] proposed a thermal-aware floorplanner based on genetic algorithms. It uses a slicing-tree floorplan representation and a grid-based thermal simulator [82]. The major disadvantage of this method of thermal-aware floorplanning is long execution times required by the thermal simulator.

#### 2.3.2 Force Directed

Force Directed techniques for floorplanning transforms the problem to a statics problem of force balancing. The connectivity between blocks acts as attractive forces while filling forces are introduced to spread apart blocks, remove overlap and reduce floorplanning whitespace. Zhou *et al.* [114] proposed a thermal-aware floorplanner using a force-directed approach. In addition to the normal filling forces and attractive forces the authors incorporate a thermal force which is used to move hot blocks away from areas of high temperature.

One of the major disadvantages of using force-directed floorplanning methods is dealing with overlap. Usually after all the force balancing has been completed there is significant overlap hence there has to be a post processing step to remove any remaining overlap which will affect the quality of the solution. The second disadvantage of this method is runtime required to calculate the temperatures needed for the thermal forces.

#### 2.3.3 Simulated Annealing

Simulated Annealing [42] is an iterative method of searching large solution spaces for a close to optimal solution. It consists of making incremental changes to an initial solution and accepting or rejecting the change based on the difference in the optimality between the two solutions. If the new solution is better than the old solution the change will always be accepted. However, to avoid being caught in local minima, if the change is worse than the new solution might be accepted depending on difference in optimality and the elapsed time of the annealer. More bad moves are accepted if the elapsed time is small and/or if the difference in optimality is small. The quality of a solution is evaluated by some cost function.

## 2.4 SP Simulated Annealing Floorplanning

SP-based floorplanning forms the basis of most previous thermal-aware floorplanners [7, 15, 17, 75, 102] and entails searching through the floorplanning solution space (represented as sequence pairs) using simulated annealing. The search is accomplished by modifying the sequence pair and the blocks in the floorplan. The quality of the floorplanning solution is evaluated using a simple cost function.

#### 2.4.1 SP Floorplanning Moves

Typically, SP floorplanners have four moves. The first move is to swap the location of two blocks by swapping two pair of numbers in both sequence pairs. The second moves entails moving a single block by swapping a pair of numbers in only one sequence pair. The third move rotates a block which entails swapping a blocks height for its width. And the final move changes the aspect ratio of a soft block by adjusting its height and width.

#### 2.4.2 SP Floorplanning Cost Function

The cost function for a SP based floorplanner usually includes the classical floorplanning metrics area and HPWL. Thermal-aware floorplanners [15, 17, 75, 75, 102] include the additional metric maximum temperature, leading to the following cost function

$$cost = \alpha \cdot Area_f + \beta \cdot HPWL + \eta T_{Max}$$

(2.3)

where  $T_{Max}$  is the maximum chip temperature and  $\alpha$ ,  $\beta$ ,  $\eta$ , are the different weights associated with each value.

A major disadvantage of using  $T_{Max}$  in a cost function is that only moves that directly affect the hottest temperature hotspot decrease the cost function. If a move significantly decrease temperatures in the other hotspots of the chip the cost function is not decreased and the annealer will more than likely not accept the move decreasing the efficiency of thermal-based floorplanning moves. The second disadvantage of using  $T_{Max}$  is the long computation times required to calculate floorplan temperatures compare the other metrics, HPWL and area.

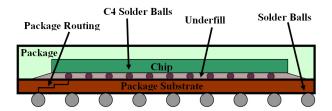

## 2.5 Flip Chip Packaging

There are two main methods of connecting IC dies to package substrates, wire bonding and flip chip. Wire bonding routes bond wires from the I/O pads located on the perimeter of the die to the package. The flip chip method, also called Controlled Collapse Chip Connection (C4), connects the die to the substrate using C4 solder bumps located throughout the die area. A sideways view of a flip chip package is shown in Figure 2.8 highlighting the C4 solder bump connections between the chip and package.

Figure 2.8: Flip Chip Package showing C4 connections.

There are several advantages of flip chip designs over wire-bonded designs. Since the I/O connections can be located throughout the die, the length of wires connecting the die to the package can be greatly reduced leading to better performance. Also, since the I/O connections are not limited to the perimeter of the die, more I/O connections are feasible than in wire bonded designs. Lastly, wire bonded designs usually require larger packages due to the I/O pads and bonding wires. These advantages along with the increase in complexity and size of ICs have resulted in many modern designs using flip chip connections [68].

#### 2.5.1 C4 Bump Placement and Floorplanning Co-optimization

The C4 bump placement problem can be defined as follows: Given a set of required package chip connections find the optimal placement of C4 bumps to minimize certain design metrics. The floorplan of the circuit affects the location of C4 bumps especially for data I/O connections, consequently, most researchers have tried to optimize the location of C4 bumps and the floorplan concurrently. Most previous methods of C4 bump placement/floorplanning have focused on minimizing design metrics such as total wirelength and skew [32, 46, 70, 80, 95]. Other works have focused on how the C4 placement affects the PCB routability [21]. None of these works however consider the C4 bump reliability as a design metric although there have been studies on the reliability of C4 bumps in flip-chip packages [44, 65, 78, 90].

### 2.6 Power Supply Networks (PSNs)

PSNs are used in ICs to deliver power to the various transistors that comprise the circuit. A PSN contains power bumps from the package, wires (interconnect) and decoupling capacitors (decaps). The power bumps and the decaps supply current to transistors in the circuit. The interconnect distributes the current throughout the circuit from the power bumps/decaps to the transistors. There are several possibilities available for the topology of the wires in the PSN, namely trees and grids. In most modern designs however, grids are mainly used and thus this thesis focuses on power supply grids. The decaps act as a local energy supply and assist in reducing the dynamic voltage droop ( $L\frac{di}{dt}$ ) caused by the sudden current draw of the localized transistor switching.

#### 2.6.1 Electrical Modelling

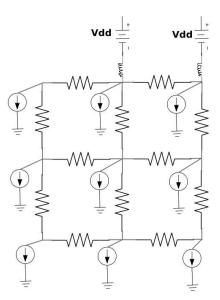

PSNs are modelled using simple electrical elements such as current sources, voltage sources, resistors, capacitors and inductors. The power bumps are modeled as inductors in series with resistors attached to an ideal, off-chip voltage source. The interconnect is modeled as a network of resistors with some inductance and capacitance. The transistors are modeled as individual, distributed current sources with a small amount of diffusion capacitance. An example of an electrical circuit for a power grid is shown in Figure 2.9. It should also be noted that the current drawn by transistors is macro-modeled to occur at each mesh node for easier calculation. In reality, the number of transistors (current sources) would be much larger than the number of nodes in the mesh.

Figure 2.9: A Simple VDD Power Supply Network showing the basic Circuit Elements used to model the PSN.

#### 2.6.2 Electrical Simulation

The voltages for a PSN are calculated using Modified Nodal Analysis (MNA) according to

$$G \cdot v(t) + C \cdot \dot{v}(t) = i(t) \tag{2.4}$$

where G is the conductance matrix, C is the admittance matrix (inductance and capacitance elements), v(t) represents the time varying nodal voltages and i(t) represents the vector of current sources corresponding to the transistors in the design. The conductance and admittance matrices are obtained by applying Kirchhoff's current law at each node of the circuit. If the backward Euler method is used to solve the transient system, Equation 2.4 can be written as:

$$\left(\frac{C}{h} + G\right)v\left(t\right) = i\left(t\right) + \frac{C}{h}v\left(t - h\right) \tag{2.5}$$

where h is the time step of the simulation.

For PSN steady state simulations the admittance matrix is ignored and Equation 2.4 becomes

$$G \cdot v = i \tag{2.6}$$

where v and i are the steady state node voltages and transistor currents of the PSN.

### 2.7 PSN Requirements

A typical PSN has three requirements: 1) The steady state current density through each power bump and the interconnect should be below a certain threshold to ensure no

failures from electromigration. 2) The DC voltage at each node in the circuit should be above a specified voltage to ensure the correct functionality of the circuit. Lower voltages causes transistors to switch slower and can significantly impact the timing of the circuit. 3) The transient voltage droop caused by the sudden switching of transistors should be above a certain threshold to ensure the correct functionality of the circuit.

#### 2.7.1 Voltage Droop

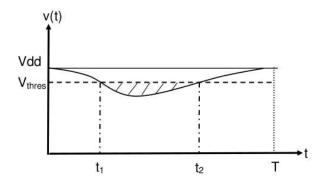

Voltage Droop is defined as the decrease in voltage in the PSN as the transistors turn on and current is drawn through the interconnect as shown in Figure 2.10.

Figure 2.10: Voltage drop at a power supply node caused by the current draw of a transistor.

Occasionally the voltage might droop below the voltage minimum leading to timing issues in circuits. The voltage droop  $g_j$  at a specific node j in the PSN is defined to be

$$g_{j} = \int_{0}^{T} \max \left(V_{thres} - v_{j}\left(t\right), 0\right) dt$$

(2.7)

where T is the clock period,  $V_{thres}$  is the minimum voltage threshold, and  $v_j$  (t) is the voltage at node j as shown in Figure 2.10.

### 2.8 PSN Synthesis

PSN synthesis creates a PSN network that meets certain requirements(Section 2.7). It entails sizing interconnect, placing decap and finally placing power supply bumps to supply the PSN with energy.

#### 2.8.1 Wire Sizing

The wire sizing problem can be defined as follows: Given the interconnect network for a PSN, size individual wires optimally within the routing constraint. Larger wires have smaller resistances which results in lower amounts of IR drop and voltage droop. Larger wires also tend to have smaller amounts of electromigration since the amount of electromigration is proportional to the size of the wire. However all the wires within a PSN cannot be made large due to the routing constraints of modern ICs. Routing resources have to be saved for data nets and the clock network.

Researchers have proposed several methods to solve the wire sizing problem. Sapatnekar *et al.* [81] proposed a heuristic which partitions the PSN interconnect recursively and then optimally size the wires in each partition. Wang *et al.* [97] proposed a method of solving the wire sizing problem using a sequential network simplex algorithm. Both of these works, however, size wires for electromigration constraints and IR drop but do not consider other reliability issues such as Joule heating in the interconnect. Recently, researchers have proposed PSN wire-sizing algorithms that optimize for the traditional metrics in addition to Joule heating in the interconnect [99].

Researchers have attempted to solve the joule heating problem in the PSN inter-

connect through other methods than wire sizing. Yokogawa *et al.* . demonstrated that stacking vias between the metal wires and the substrate can help decrease temperatures in PSN interconnect due to increased thermal conductivity between the wires and substrate [104]. Lele *et al.* proposed a method to reduce interconnect Joule heating by optimally sizing signal repeaters [38], but this method is not applicable to PSN interconnects since no repeaters are used.

#### 2.8.2 Power Bump Placement

The power bump placement problem is defined as follows: Place VDD and GND power bumps to ensure that all the PSN requirements are met while minimizing the number of VDD and GND bumps used.

Researchers have proposed many different algorithms to solve the power bump placement problem [37, 64, 77, 109, 113]. Sato *et al.* [77] proposed a greedy formulation that successively places power bumps at the points of highest IR drop in the circuit until the IR drop requirement has been met. To accelerate the algorithm, an incremental matrix inversion is proposed that decreases the computation time required for each PSN simulation. The algorithm does not consider the electromigration constraints for each bump.

Zhong *et al.* [113] proposed a bump placement methodology that is based on simulated annealing. They use an iterative solver to accelerate the computation time for each PSN simulation that is required for each simulated annealing move. The major disadvantage of this approach is that number of bumps is fixed since searching through the solution space with a variable number of bumps is prohibitively time consuming using simulated annealing. This approach also does not consider electromigration in the power bumps

Zhao *et al.* [109] proposed a Mixed Integer Linear Program (MILP) formulation that places bumps so as to satisfy electromigration and IR drop constraints. The MILP formulation proposed is

$$\begin{aligned} & \min \quad \sum_{i \in PC} z_i, \ z_i \in \{0,1\} \\ & \text{s.t.} \quad I_{thres} \cdot z_i - I_i \geq 0 \\ & I_i \geq 0 \\ & v_i - \text{VDD} \cdot z_i \geq 0 \\ & v_i \geq V_{thres} \\ & v_i \leq \text{VDD} \\ & V_{and} \ I \ \text{satisfy Equation 2.6} \end{aligned}$$

where PC is a set of all possible bump locations,  $z_i$  is a binary variable indicating whether a bump is located at bump position i,  $I_i$  is the current through a power bump i,  $v_i$  is the voltage of node i, V is the set of all node voltages, I is the set of all node currents,  $I_{thres}$  is the maximum allowable current through a power bump,  $V_{thres}$  is the maximum tolerable voltage drop in the circuit and VDD is the voltage of a power bump. One major disadvantage of this method is the significant runtime required to solve MILP's that contain many variables. The authors propose methods of macro-modelling the PSN to reduce the problem size which unfortunately leads to solutions that can be far from optimal.

All the aforementioned works on power bump placement have focused on creating an initial bump placement that minimizes the total number of power bumps while ensuring power supply integrity including static voltage violations and electromigration failure of power bumps. They do not consider the robustness of the bump placement in the presence of a single bump failure.

### 2.8.3 Decap Placement

The decap placement problem is defined as follows: Place the minimum amount of decap so that the transient voltage droop is above a specified threshold. More formally the decap insertion problem can be formulated as

minimize

$$\sum_{j=1}^{m} g_j(c_1, \dots, c_m)$$

subject to  $c_i \leq d_i$  and

$$\sum_{j=1}^{m} c_i \leq C_{tot}$$

(2.8)

where  $c_i$  is the capacitance at node i,  $d_i$  is the maximum capacitance at node i and  $C_{tot}$  is the maximum total capacitance.  $g_j$  is the voltage droop at node j as previously shown in Equation 2.7.

Researchers have proposed several methods for doing decap placement [23,39,47, 52,55,76,84,101,103,110–112]. These methods can be separated into two main categories, those that are based on sensitivity analysis [23,47,71,84] and those that try to estimate the decap to be inserted at a node based on the magnitude of the voltage droop [101,110–112]. Other methods of solving the decap allocation problem have been proposed in literature. Some researchers have formulated the decap placement problem as a semidefinite program [39,52]. Other researchers have focused on the decap placement problem in 3D ICs [76, 115].

The sensitivity used by most researchers compute the change in total voltage droop with respect to capacitance and is formally defined as follows [23, 47, 71, 84]:

$$s_{ij} = \frac{\partial g_j(c_1, \dots, c_m)}{\partial c_i} \tag{2.9}$$

where  $s_{ij}$  is the sensitivity of decap allocated at node i to removing power supply drop  $g_j$  at node j. These sensitivities are calculated using adjoint sensitivity analysis. The sensitivity

$s_{i,all}$  of a decap allocated at node i to remove power supply at all nodes can be found using

$$s_{i,all} = \int_{0}^{T} \left( v'_{i,all} \left( T - t \right) \right) \times \dot{v}_{i} \left( t \right) dt$$

(2.10)

where  $\dot{v_i}\left(t\right)$  is the derivative of the voltage at node i and  $v_{i,all}^{'}\left(T-t\right)$  is the voltage at node i in the adjoint network.

The decaps for each node are then calculated using a conjugate gradient method once the sensitives shown in Equation 2.10 are computed [23, 47, 84]. Another method of solving Equation 2.8 given the sensitivities calculated in Equation 2.10 is a sequence of linear programs [71]. In this approach the non linear equations governing the relationship between the sensitivity, droop and capacitance are linearized and then repeatedly solved using a linear programming solver until the total droop has been minimized or the decoupling capacitance budget has been exhausted. The sequence of linear programming optimization can be formally defined as

$$\begin{array}{lll} \text{minimize} & \displaystyle \sum_{j=1}^m c_j \\ \\ \text{subject to} & g_j & \leq & \displaystyle \sum_{j=i}^m s_{ij} \Delta c_i \\ \\ & c_i & \leq & d_i \\ \\ & \displaystyle \sum_{j=1}^m c_j & \leq & C_{tot} \end{array}$$

One disadvantage of using this approach is that the runtime of the algorithm is dependent on the number of violation nodes in the design. Calculating the individual sensitivities  $s_{ij}$  for each node requires building and solving an the adjoint network specific to that node, consequently a design with a large number of violation nodes will require many adjoint simulations and will have a significant runtime.

# Chapter 3

# Thermal Background

This chapter provides the thermal background information needed to understand the proposed thermal-aware CAD algorithms and methodologies detailed in the thesis and is separated into three parts. Sections 3.1 and 3.2 give a brief overview of heat generation and substrate temperature modeling respectively. Section 3.3 introduces models used for the various thermal reliability concerns

# 3.1 Heat Generation

There are two main sources of heat generation in modern ICs. The majority of the heat is produced from transistors while the rest is produced as Joule heating in the IC interconnect.

# 3.1.1 Transistor Switching Heating

Most heat energy in ICs is created by the transistors. The total power consumed by a transistor is separated into three major components: dynamic, short-circuit and leak-

age. The total is

$$P_{\text{total}} = P_{\text{dynamic}} + P_{\text{short-circuit}} + P_{\text{leakage}}$$

(3.1)

where  $P_{\rm total}$  is the total transistor power,  $P_{\rm dynamic}$  is the transistor dynamic power,  $P_{\rm short-circuit}$  is the short circuit power and  $P_{\rm leakage}$  is the leakage power.

The dynamic power component depends on several factors such as the switching activity of the transistor, the clock frequency and the load capacitance. More formally the dynamic power of a transistor is

$$P_{\text{dynamic}} = 0.5\alpha_s V_{\text{dd}}^2 f_c C_L \tag{3.2}$$

where  $\alpha_s$  is the transistor activity factor (switching probability),  $V_{dd}$  is the supply voltage value,  $f_c$  is the clock frequency and  $C_L$  is the load capacitance [59].

The short circuit power for a transistor is

$$P_{\text{short-circuit}} = I_{\text{short-circuit}} V_{\text{dd}}$$

(3.3)

where  $I_{\rm short-circuit}$  is the short circuit current which depends on several factors such as  $\alpha_s$ ,  $C_L$ , threshold voltage, signal slew, carrier mobility,  $f_c$  and  $V_{\rm dd}$  [5]. Both the threshold voltage and carrier mobility are dependent on temperature, consequently, increasing IC temperatures has the negative effect of increasing short-circuit power indirectly through  $I_{\rm short-circuit}$ .

The transistor leakage power has three major components: reverse-biased junction leakage current, gate direct tunneling leakage and sub-threshold leakage with the major component being the sub-threshold leakage [69]. The sub-threshold current is

$$I_{\text{sub}} = I_{\text{s0}} \exp \frac{V_{gs} - V_{th}}{nV_T} \left( 1 - \exp \frac{-V_{ds}}{V_T} \right)$$

(3.4)

where  $V_T$  is the thermal voltage,  $I_{s0}$  is a constant that is device dependent and n is a constant [61]. The thermal voltage is calculated as follows:

$$V_T = kT/q \tag{3.5}$$

where k is the Boltzmann constant, q is the charge of an electron and T is the absolute temperature in Kelvin.

The amount of heat generated from each source ( $P_{\rm dynamic}, P_{\rm short-circuit}, P_{\rm leakage}$ ) varies from circuit to circuit and depends on factors such as the technology used, the clock frequency, vdd voltage etc.

## 3.1.2 Interconnect Joule Heating

Heat is also generated in ICs by transporting current through the interconnect to the transistors. This heat is created due to the interconnect resistance and is referred to as Joule heating. The Joule heating power at a given time,  $J\left(t\right)$ , in each wire/interconnect segment is

$$J(t) = i^2(t)R \tag{3.6}$$

where R is the resistance of the interconnect segment and  $i\left(t\right)$  is the current through the segment.

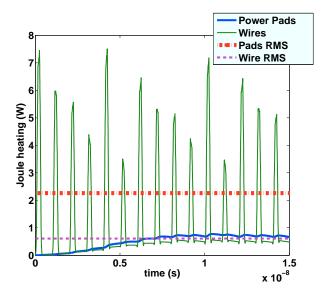

In a typical IC most of the Joule heating occurs in the Power Supply Network (PSN) since all the energy required for the circuit flows through it. Within a PSN Joule heating occurs in the wires, power supply bumps, and vias between layers in greatly differing magnitudes. Figure 3.1 shows the transient Joule heating power of the wires and pads for the ibmpg1 PSN benchmark [35]. The Joule heating in the power supply pads stays

roughly constant as soon as the PSN approaches its steady state response. However, the Joule heating of the wires has spikes corresponding to the transistors switching which leads to a much larger Joule heating RMS value of 2.3W in the wires compared to 0.6W in the power supply pads.

Figure 3.1: An example from the ibmpg1 transient benchmark shows that Joule heating in the wires has a much larger RMS value than the power supply pads.

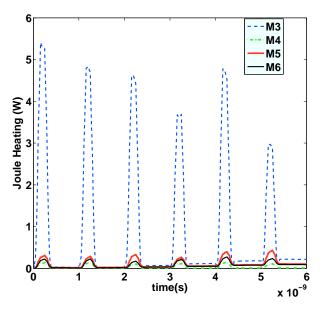

The amount of Joule heating varies across the different metal layers in a typical PSN, with the lowest metal layer having the largest Joule heating RMS power due to the large current spikes on this metal layer as a result of its' proximity to the switching transistors. Figure 3.2 shows the distribution of Joule heating across the various metal layers in the ibmpg2 transient benchmark. Most Joule heating occurs on the lowest metal layer (1.61W RMS), which is significant since this metal layer has the smallest wire dimensions and is consequently more susceptible to electromigration. The smaller width of the lower metal wires leads to less heat diffusion to the substrate and consequently higher wire temperatures. In addition, the proximity to the substrate means that heat from the device switching

activity likely already increases the temperature (and therefore decreases MTTF) of the wire due to  $T_{sub}$  in Equation 3.13.

Figure 3.2: An example from the ibmpg2 transient benchmark shows that lower metal layers suffer from larger Joule heating than global metal layers.

The RMS Joule heating values for the M5 and M6 wires are 0.18W and 0.14W, respectively, which is not as large as the value for the M3 layer. However, the impact of Joule heating is still significant since the M5 and M6 layers are located farther from the heat sink and consequently have much larger thermal resistance to the substrate which leads to higher temperatures. The Joule heating in the vias between metal layers is insignificant in comparison to the Joule heating in the wires and pads (RMS value of only 0.0009W) as illustrated in Figure 3.3.

Figure 3.3: An example from the ibmpg2 transient benchmark shows that Joule heating in the vias between different metal layers is not very significant  $(1 \times 10^{-3} \text{W})$ .

# 3.2 Substrate Temperature Modeling

The temperature of an IC is governed by the rate of heat generation and removal. Most of the heat generated in ICs flows from the transistor junction through the substrate, to the heat spreader, to the package, and is finally removed through the heat sink to the ambient air. Some of the heat, although not the majority, flows in the opposite direction toward the package and the package bumps which are in contact with the PCB and the ambient air. The rate at which heat is removed is governed by the heat conduction equation

$$\rho c_{p} \frac{\partial T\left(\vec{r},t\right)}{\partial t} = \nabla \cdot \left[k\left(\vec{r},T\right) \nabla T\left(\vec{r},t\right)\right] + g\left(\vec{r},t\right)$$

(3.7)

where g is volume power density (W/m<sup>3</sup>), T is temperature (K),  $c_p$  is specific heat capacity (J/KgK),  $\rho$  is the density of the material and k is the thermal conductivity of the material.

The boundary conditions for Equation 3.7 are usually assumed to be as follows:

The vertical sides of the chip, and the side not attached to the heat sink are assumed to be adiabatic. The side of the chip attached to the heat sink is assumed to be convective and is modeled using the following equation [69]:

$$k(\vec{r},T)\frac{\partial T(\vec{r},t)}{\partial n_i} = h_i(T_a - T(\vec{r},t))$$

(3.8)

For homogeneous materials (whose thermal conductivity is temperature independent) at steady state, Equation 3.7 can be simplified to

$$-k\nabla^2 T = q \tag{3.9}$$

Due to size and complexity of most modern ICs, Equation 3.9 is usually applied at the block level for thermal modeling. Consequently g corresponds to the average power density of the transistors that comprise the block, T is the temperature of the block, and k is the combined thermal conductivity of the materials which separate the transistors from the heat sink, usually bulk silicon, but this may vary depending on the specific manufacturing for the IC (for example SOI).

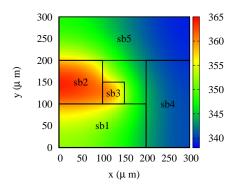

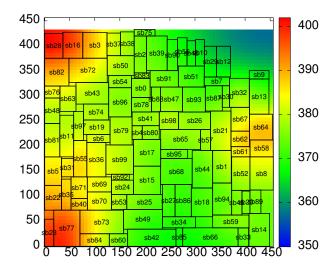

The temperature map for an IC is obtained by solving Equation 3.7 using several methods such as Finite Element Method [74], Finite Difference [89, 98], Random walk [100] or Green-based methods [30,107,108]. Figure 3.4 shows a thermal map for the GSRC n100 floorplanning benchmark circuit and highlights the non-uniformity of the temperature map on modern ICs with large hotspots and temperature gradients.

Figure 3.4: IC temperature map for GSRC n100 circuit showing temperature hotspots. The circuit dimensions are in  $\mu$ m and the temperature is in Kelvin (K)

### 3.2.1 Thermal Modeling of Interconnect

IC interconnect temperatures are governed by the substrate temperature of the IC in the vicinity of the interconnect and the quantity of Joule heating in the interconnect. Joule heating leads to the interconnect experiencing a temperature increase,  $\Delta T_{\rm wire}$ , which is proportional to the root mean square (RMS) value of the Joule heating power [6] and is computed using

$$\Delta T_{\text{wire}} = \frac{RR_{\theta}}{D} \int_{0}^{D} i^{2}(t) \, dt. = i_{\text{RMS}}^{2}(t) \, RR_{\theta}$$

(3.10)

where  $i_{RMS}$  is the RMS value of the current,  $R_{\theta}$  is the thermal resistance of the interconnect to the substrate, R is the resistance of the interconnect, and D is the duration over which the Joule heating is being analyzed.

The thermal resistance,  $R_{\theta}$ , is measured with respect to the substrate since the majority of heat produced in an IC is removed from the heat sink attached to the back-side

of the substrate as stated in Section 3.2. This thermal resistance can be estimated [6] as

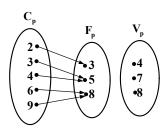

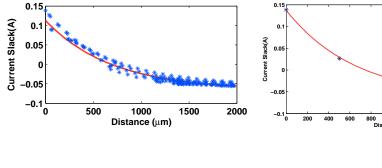

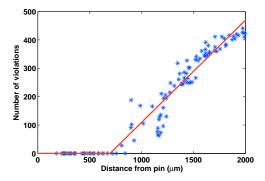

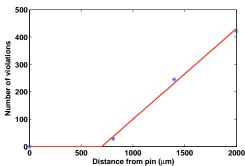

$$R_{\theta} = \frac{t_{\rm ins}}{K_{\rm eff}LW_{\rm eff}} \tag{3.11}$$