# UC San Diego UC San Diego Electronic Theses and Dissertations

Title

Optics in data center network architecture

Permalink https://escholarship.org/uc/item/8nv683wc

Author Farrington, Nathan

Publication Date 2012

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

### **Optics in Data Center Network Architecture**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

Nathan Farrington

Committee in charge:

Professor Amin Vahdat, Chair Professor Bill Lin Professor George Papen Professor Stefan Savage Professor George Varghese

2012

Copyright Nathan Farrington, 2012 All rights reserved. The dissertation of Nathan Farrington is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2012

### DEDICATION

To my family.

### EPIGRAPH

And the Lord said, "Behold, they are all one people with one language; and this is only the beginning of what they will do, and now nothing they have imagined will be impossible for them."

GENESIS 11:6

# TABLE OF CONTENTS

| Signature Pa   | ge                                                                                                                                                                                                                                                                                                                                                                                                                                 | ii                                         |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Dedication .   | i                                                                                                                                                                                                                                                                                                                                                                                                                                  | v                                          |

| Epigraph .     |                                                                                                                                                                                                                                                                                                                                                                                                                                    | v                                          |

| Table of Con   | tents                                                                                                                                                                                                                                                                                                                                                                                                                              | vi                                         |

| List of Figure | es                                                                                                                                                                                                                                                                                                                                                                                                                                 | х                                          |

| List of Tables | s                                                                                                                                                                                                                                                                                                                                                                                                                                  | ci                                         |

| Acknowledge    | ements                                                                                                                                                                                                                                                                                                                                                                                                                             | ii                                         |

| Vita           |                                                                                                                                                                                                                                                                                                                                                                                                                                    | v                                          |

| Abstract of t  | he Dissertation $\ldots \ldots x$                                                                                                                                                                                                                                                                                                       | v                                          |

| Chapter 1      | 1.1 Scope                                                                                                                                                                                                                                                                                                                                                                                                                          | $\begin{array}{c} 1 \\ 4 \\ 5 \end{array}$ |

| Chapter 2      | 2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                   | 8<br>9<br>0                                |

|                | 2.2       Technologies       1         2.2.1       Racks       1         2.2.2       Switches       1         2.2.3       Cables and Transceivers       1                                                                                                                                                                                                                                                                          | $     1 \\     1 \\     2 \\     3   $     |

|                | 2.3       Motivation       1         2.3.1       Merchant Silicon and the Commodity       1         Top-of-Rack Switch       1                                                                                                                                                                                                                                                                                                     |                                            |

|                | 2.4       Design of a 3,456-port Switch       1         2.4.1       Overview       1         2.4.2       Pod Switch: Organization       1         2.4.3       Pod Switch: Line Card       2         2.4.4       Pod Switch: Uplink Card       2         2.4.5       Fiber Management       2         2.4.6       Core Switch Array       2         2.4.7       Incremental Deployment       2         2.5       Comparison       3 |                                            |

|           | 2.6 EEP: Ethernet Extension Protocol                                                               |

|-----------|----------------------------------------------------------------------------------------------------|

|           | 2.6.1 IEEE 802.1ad Traffic Groomer Design                                                          |

|           | 2.6.2 EEP Traffic Groomer Design                                                                   |

|           | 2.6.3 Implementation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 36$           |

|           | 2.6.4 Evaluation                                                                                   |

|           | 2.7 64-port Switch ASICs                                                                           |

|           | 2.8 Related Work                                                                                   |

|           | 2.9 Discussion                                                                                     |

|           |                                                                                                    |

| Chapter 3 | Millisecond-scale Optical Circuit Switching                                                        |

| -         | 3.1 Introduction                                                                                   |

|           | 3.2 Background and Motivation                                                                      |

|           | 3.2.1 The Oversubscription Problem                                                                 |

|           | 3.2.2 Enabling Technologies                                                                        |

|           | 3.3 Architecture                                                                                   |

|           | 3.3.1 Overview                                                                                     |

|           | 3.3.2 Simulation Study at Scale                                                                    |

|           | 3.4 Design and Implementation                                                                      |

|           | 3.4.1 Hardware                                                                                     |

|           | 3.4.2 Software                                                                                     |

|           | 3.4.3 Control Loop                                                                                 |

|           | 3.5 Evaluation                                                                                     |

|           | 3.5.1 Communication Patterns                                                                       |

|           | 3.5.2 Debouncing and EDC                                                                           |

|           | 3.5.3 Throughput versus Stability                                                                  |

|           | 3.5.4 Unidirectional Circuits                                                                      |

|           | 3.5.5 How Responsive is Helios?                                                                    |

|           | 3.5.6 How Scalable is Helios?                                                                      |

|           | 3.6 Lessons Learned                                                                                |

|           | 3.7    Hardware Requirements    74                                                                 |

|           | 3.7.1 Performance Measurements                                                                     |

|           |                                                                                                    |

|           | v v                                                                                                |

|           | 3.8 Related work $\ldots \ldots 77$ |

| Chapter 4 | Microsecond-scale Optical Circuit Switching                                                        |

| Chapter 1 | 4.1 Introduction                                                                                   |

|           | 4.2 Technology                                                                                     |

|           | 4.3 Mordia OCS Prototype                                                                           |

|           | 4.3.1 Data Plane                                                                                   |

|           | 4.3.2 Control Plane                                                                                |

|           | 4.3.3 Implementation                                                                               |

|           | 4.3.4 Scalability                                                                                  |

|           | 0                                                                                                  |

|           | $4.3.5  \text{Analysis}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $          |

|              | 4.4  | Evalua    | tion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                  | 97 |

|--------------|------|-----------|------------------------------------------------------------------------------------------------------|----|

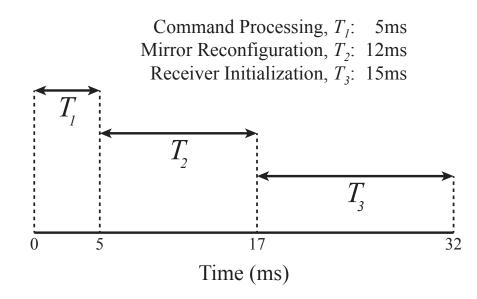

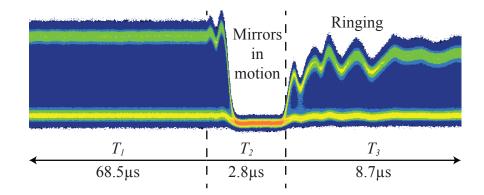

|              |      | 4.4.1     | Wavelength-Selective Switch Timings 9                                                                | )7 |

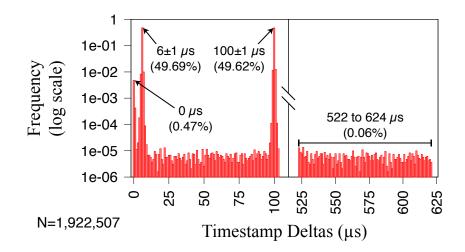

|              |      | 4.4.2     | Synchronization Packet Jitter                                                                        | )8 |

|              |      | 4.4.3     | Measurements of $T_2 + T_3$                                                                          | 99 |

|              |      | 4.4.4     | Duty Cycle Measurements                                                                              | )1 |

|              | 4.5  | Traffic   | Matrix Scheduling                                                                                    | )2 |

|              |      | 4.5.1     | All-to-All Example                                                                                   | )3 |

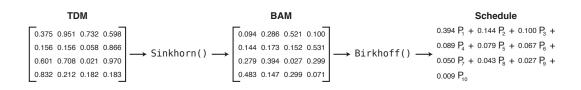

|              |      | 4.5.2     | Traffic Matrix Scheduling Algorithm 10                                                               | )7 |

|              | 4.6  | Related   | d Work                                                                                               | 1  |

|              | 4.7  | Discuss   | sion $\ldots \ldots 11$ | 13 |

| Chapter 5    | Cone | clusion . |                                                                                                      | 15 |

| Bibliography |      |           |                                                                                                      | 18 |

### LIST OF FIGURES

| Figure 1.1:  | An electrical conductor attenuates the input power             | 5  |

|--------------|----------------------------------------------------------------|----|

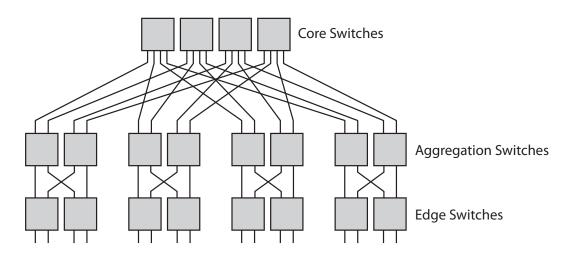

| Figure 2.1:  | A 3-tier (5-stage) FatTree using 4-port switching elements     | 11 |

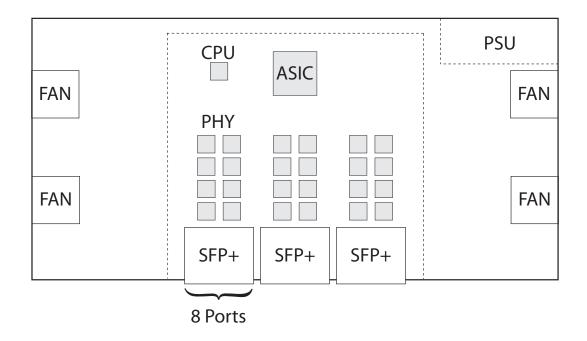

| Figure 2.2:  | Layout of a 24-port 10 GbE TOR switch.                         | 18 |

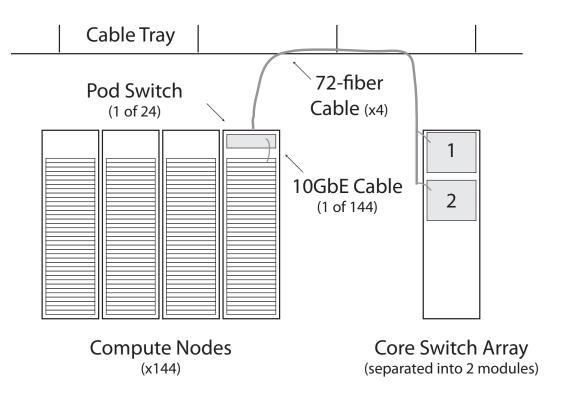

| Figure 2.3:  | Example deployment of the 3,456-port switch.                   | 19 |

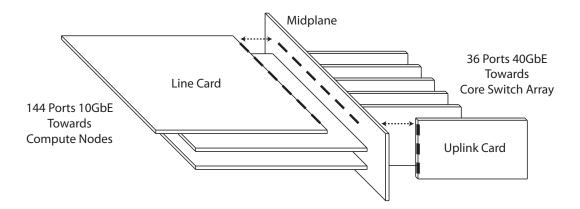

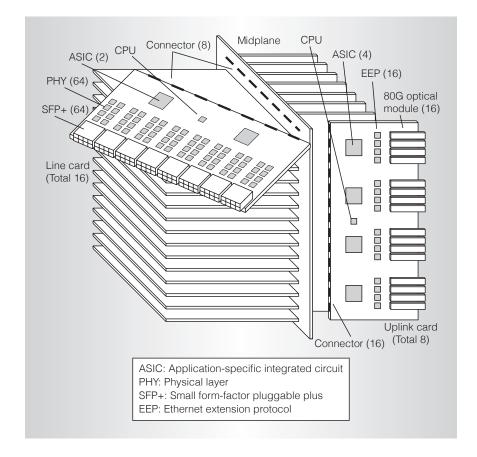

| Figure 2.4:  | Pod switch physical organization.                              | 20 |

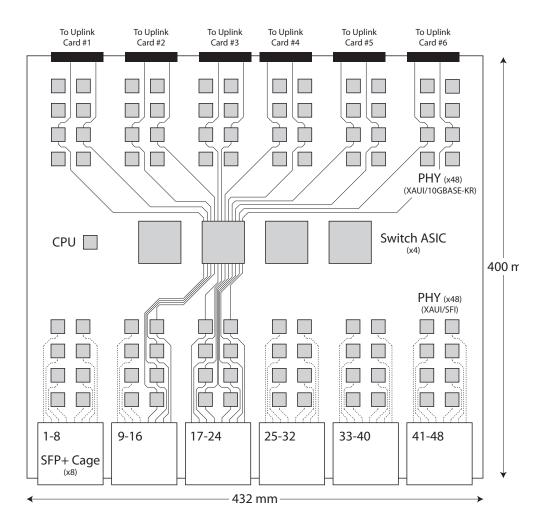

| Figure 2.5:  | Pod switch line card                                           | 22 |

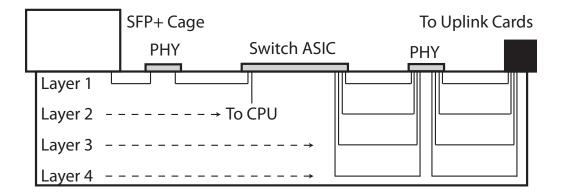

| Figure 2.6:  | Layers of the pod switch line card circuit board               | 23 |

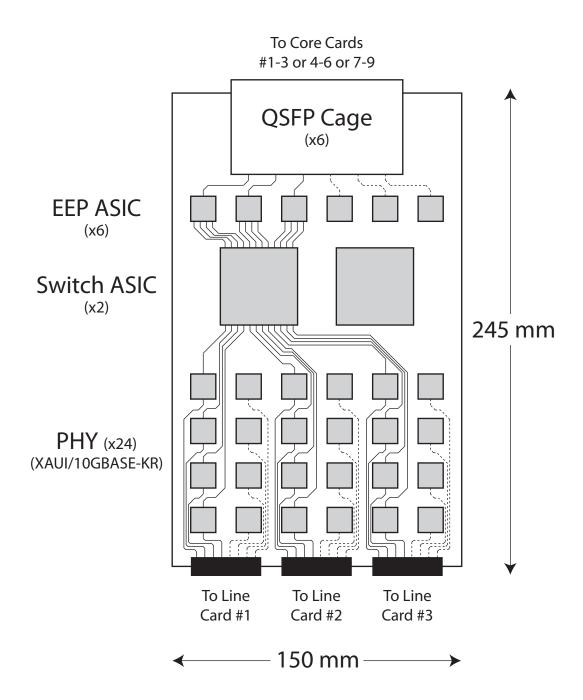

| Figure 2.7:  | Pod switch uplink card.                                        | 24 |

| Figure 2.8:  | Fiber management units.                                        | 25 |

| Figure 2.9:  | Core switch array card.                                        | 27 |

| Figure 2.10: | Topology of the 3,456-port switch.                             | 28 |

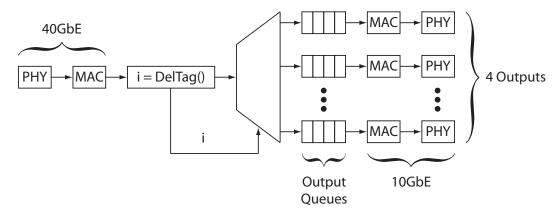

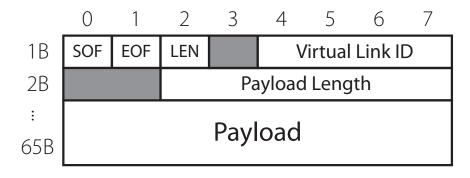

|              | IEEE 802.1ad grooming datapath.                                | 33 |

|              | IEEE 802.1ad degrooming datapath.                              | 34 |

| Figure 2.13: | EEP frame format.                                              | 35 |

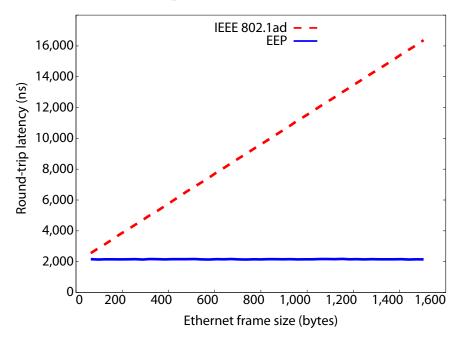

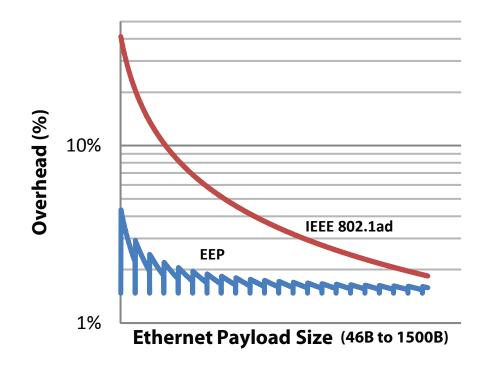

| Figure 2.14: | Traffic groomer latency measurements                           | 37 |

| Figure 2.15: | Traffic groomer oversubscription.                              | 38 |

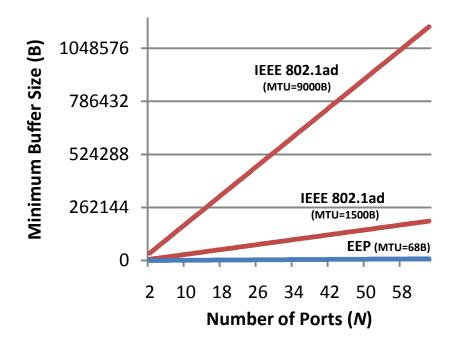

| Figure 2.16: | Traffic groomer minimum buffer sizes.                          | 39 |

| Figure 2.17: | 1,024-port pod switch with 64-port switch ASICs                | 40 |

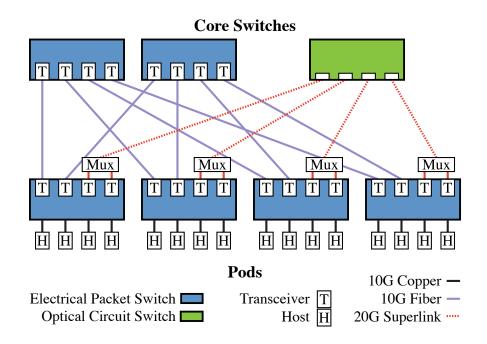

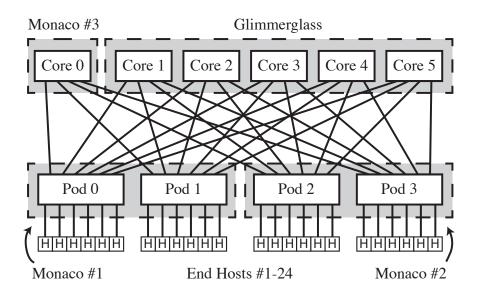

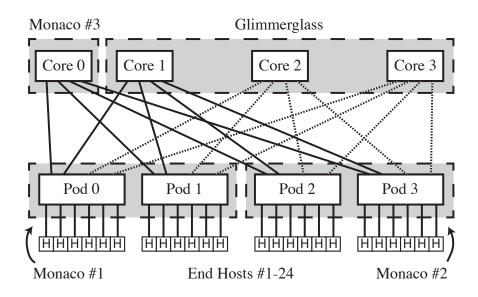

| Figure 3.1:  | Helios is a 2-level FatTree of pod switches and core switches  | 45 |

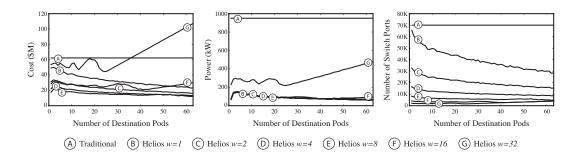

| Figure 3.2:  | Simulation comparing traditional and Helios-like network       | 54 |

| Figure 3.3:  | Helios prototype with five circuit switches                    | 58 |

| Figure 3.4:  | Helios prototype with three circuit switches and WDM           | 59 |

| Figure 3.5:  | Helios control loop                                            | 60 |

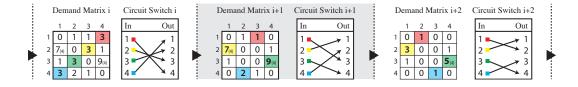

| Figure 3.6:  | Example of Compute New Topology with 4 pods and $w = 4$        | 61 |

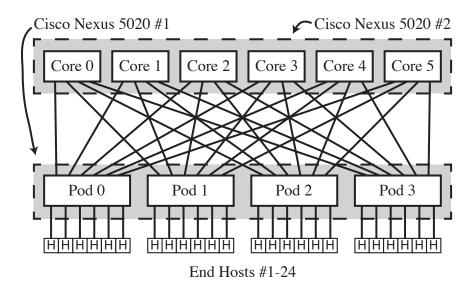

| Figure 3.7:  | Traditional FatTree network of packet switches                 | 63 |

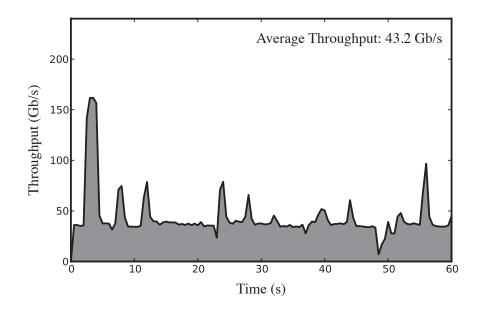

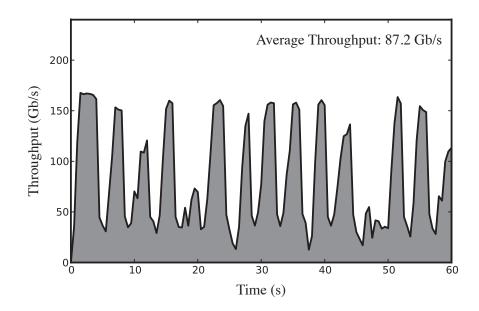

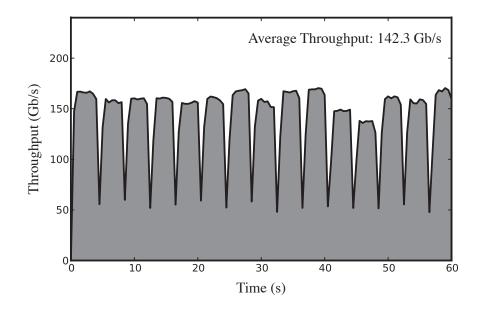

| Figure 3.8:  | Throughput with baseline Fulcrum software                      | 65 |

| Figure 3.9:  | Throughput without "debouncing"                                | 66 |

| 0            | Throughput without "debouncing" and EDC                        | 67 |

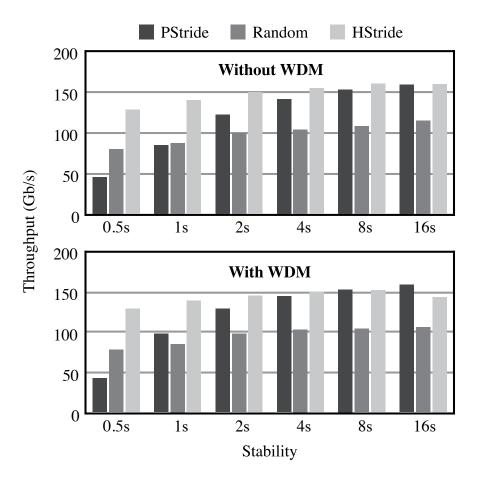

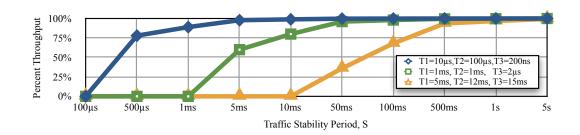

|              | Throughput as a function of stability.                         | 68 |

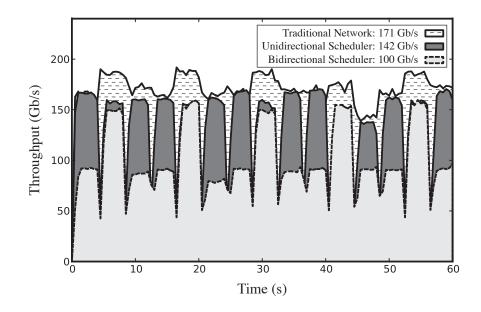

| -            | Unidirectional vs. bidirectional circuit scheduling.           | 70 |

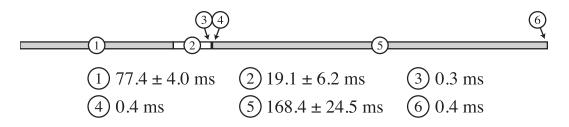

|              | Profile of the Helios control loop.                            | 70 |

| Figure 3.14: | OCS characterization during reconfiguration.                   | 71 |

| Figure 3.15: | OCS measurements.                                              | 75 |

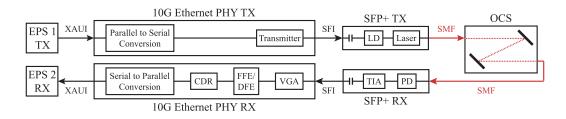

| Figure 3.16: | End-to-end data path.                                          | 75 |

| -            | Throughput compared to a pure EPS                              | 77 |

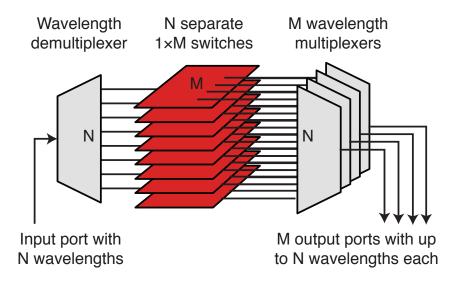

| Figure 4.1:  | A $1 \times M$ wavelength-selective switch (adapted from [73]) | 84 |

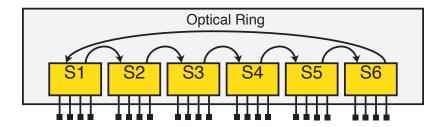

| Figure 4.2:  | Unidirectional optical ring of stations.                       | 85 |

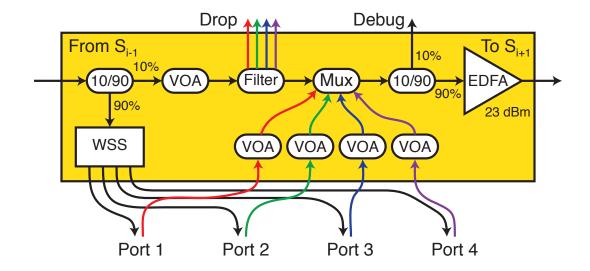

| Figure 4.3:  | A station in the optical ring.                                 | 86 |

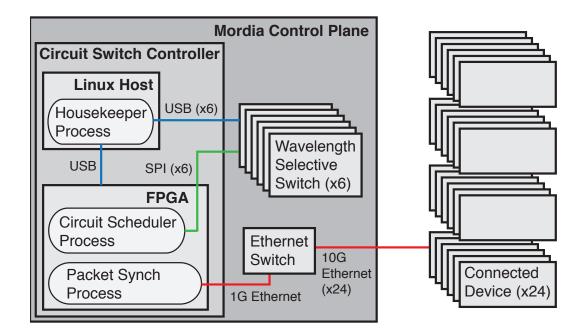

| Figure 4.4:  | Control plane of the 24-port Mordia OCS prototype           | 87 |

|--------------|-------------------------------------------------------------|----|

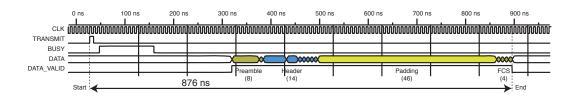

| Figure 4.5:  | Sync packet propagation delay inside the FPGA               | 87 |

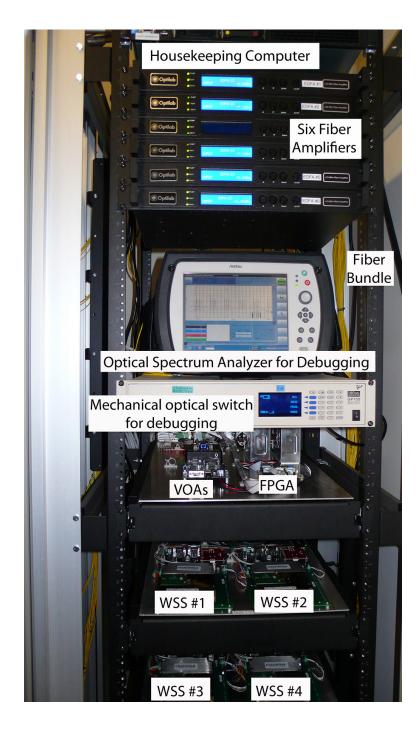

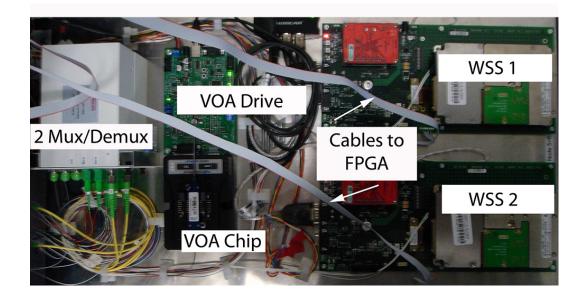

| Figure 4.6:  | Mordia components (front view)                              | 91 |

| Figure 4.7:  | Mordia components (overhead view)                           | 92 |

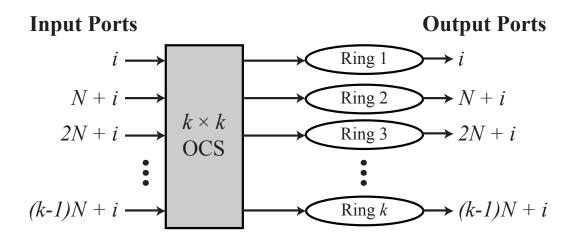

| Figure 4.8:  | Stacked rings can increase total port count                 | 94 |

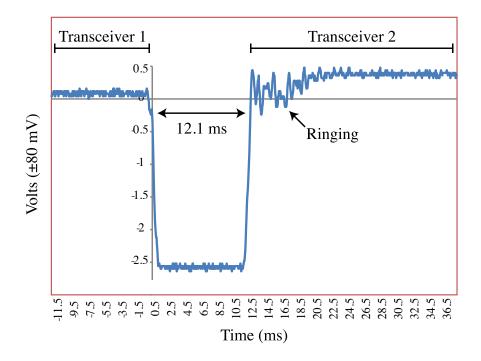

| Figure 4.9:  | Oscilloscope trace of a WSS during reconfiguration          | 97 |

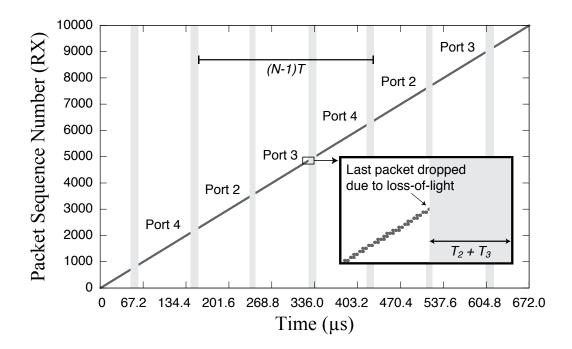

| Figure 4.10: | Synchronization packets received by connected devices       | 99 |

| Figure 4.11: | Equal-length timeslots                                      | 00 |

| Figure 4.12: | Variable-length timeslots                                   | 01 |

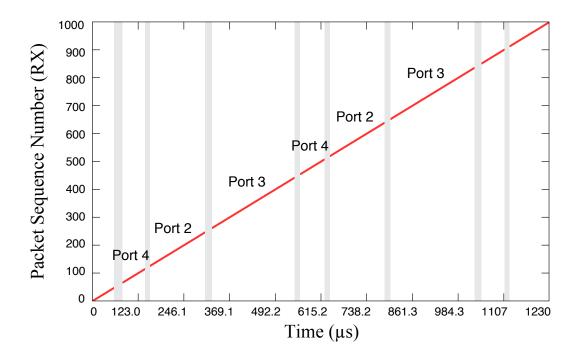

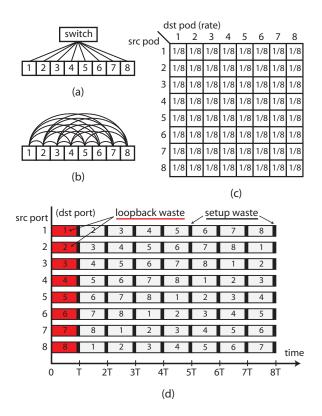

| Figure 4.13: | Histogram of $T_2 + T_3$ using 705 samples                  | 02 |

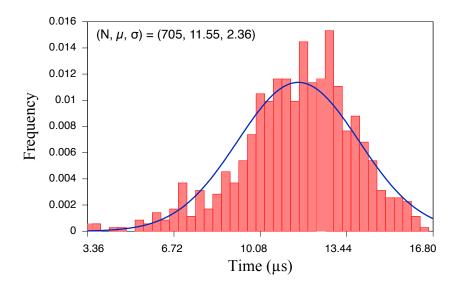

| Figure 4.14: | Eight pods with an all-to-all communication pattern 10      | 04 |

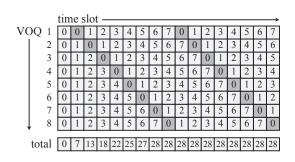

| Figure 4.15: | Virtual output queue (VOQ) buffer occupancies 10            | 06 |

| Figure 4.16: | Example run of the TMS scheduling algorithm 10              | 07 |

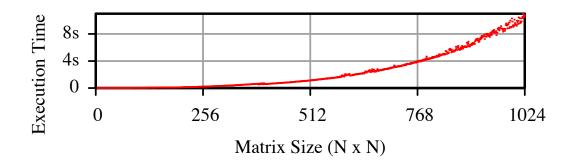

| Figure 4.17: | Execution time of the Sinkhorn matrix scaling algorithm 10  | 09 |

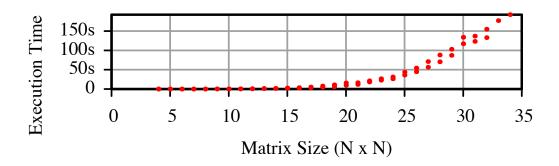

| Figure 4.18: | Execution time of the BvN matrix decomposition algorithm 12 | 10 |

### LIST OF TABLES

| Table 1.1: | Attenuation and maximum length of AWG 7 copper wire | 6   |

|------------|-----------------------------------------------------|-----|

| Table 2.1: | Ethernet switch models.                             | 12  |

| Table 2.2: | Data center communication cables and transceivers   | 13  |

| Table 2.3: | Comparison of 10 GbE switch ASICs                   | 17  |

| Table 2.4: | Comparison of three optical transceiver standards   | 31  |

| Table 2.5: | Part counts.                                        | 31  |

| Table 2.6: | Part costs and power estimates.                     | 31  |

| Table 2.7: | Comparison of three equivalent FatTree networks     | 32  |

| Table 2.8: | Xilinx Virtex-5 device utilization.                 | 36  |

| Table 3.1: | Component cost and power consumption                | 52  |

| Table 3.2: | Circuit scheduler computation time                  | 72  |

| Table 4.1: | Comparison of 2D and 3D MEMS-based OCS              | 83  |

| Table 4.2: | Bill of materials                                   | 90  |

| Table 4.3: | Performance of Mordia compared to Helios            |     |

| Table 4.4: | Minimum duty cycle limits the number of timeslots   | 111 |

|            |                                                     |     |

#### ACKNOWLEDGEMENTS

I would like to thank my advisor, Professor and SAIC Chair Amin Vahdat, for his mentorship and support over the past several years, from whom I have learned my valuable lessons, such as the importance of finishing projects, how to choose problems, and how to lead through code. I would like to thank the other steller members of my committee: Bill Lin, George Papen, Stefan Savage, and George Varghese. I could not ask for a better group of experts to donate their valuable time to helping me graduate. Although Amin is my sole advisor, I have worked closely with three others through the past few years that I consider to be honorary advisors: George Porter, Yeshaihu Fainman, and George Papen. I am very lucky to have had no less than four world-class researchers investing their time and effort in me.

Research in the field of computer science is seldom a solo activity. I would like to thank my numerous collaborators, who are listed next.

Chapter 2, in part, reprints material as it appears in the paper titled "Data Center Switch Architecture in the Age of Merchant Silicon", published in the Proceedings of the 17th IEEE Symposium on High-Performance Interconnects, August 2009, by Nathan Farrington, Erik Rubow, and Amin Vahdat [1].

Chapter 2, in part, reprints material as it appears in the paper titled "Scale-Out Networking in the Data Center", published in IEEE Micro, 30(4), pp 29–41, July/August 2010, by Amin Vahdat, Mohammad Al-Fares, Nathan Farrington, Radhika Niranjan Mysore, George Porter and Sivasankar Radhakrishnan [2].

Chapter 3, in part, reprints material as it appears in the paper titled "Helios: A Hybrid Electrical/Optical Switch Architecture for Modular Data Centers", published in the Proceedings of the 2010 ACM SIGCOMM Conference, by Nathan Farrington, George Porter, Sivasankar Radhakrishnan, Hamid Hajabdolali Bazzaz, Vikram Subramanya, Yeshaiahu Fainman, George Papen, and Amin Vahdat [3].

Chapter 3, in part, reprints material as it appears in the paper titled "Hardware Requirements for Optical Circuit Switched Data Center Networks", published in the Proceedings of the 2011 Optical Fiber Communication Conference, by Nathan Farrington, Yeshaiahu Fainman, Hong Liu, George Papen, and Amin Vahdat [4].

Chapter 4, in part, has been submitted for publication in a paper titled "Mordia: A Data Center Network Architecture for Microsecond Circuit Switches", by Nathan Farrington, Richard Strong, Alex Forencich, Pang-chen Sun, Tajana Rosing, Yeshaiahu Fainman, Joseph Ford, George Papen, George Porter, and Amin Vahdat.

Chapter 4, in part, reprints material as it appears in the paper titled "Hunting Mice with Microsecond Circuit Switches", published in the Proceedings of the 11th ACM Workshop on Hot Topics in Networks, October 2012, by Nathan Farrington, George Porter, Yeshaiahu Fainman, George Papen, and Amin Vahdat [5].

VITA

| 2003      | Bachelor of Science in Computer Engineering <i>cum laude</i> , University of Florida                         |

|-----------|--------------------------------------------------------------------------------------------------------------|

| 2003-2008 | Department of Defense, SPAWAR Systems Center Pacific                                                         |

| 2009      | Master of Science in Computer Science, University of California, San Diego                                   |

| 2010      | Candidate of Philosophy in Computer Science (Computer En-<br>gineering), University of California, San Diego |

| 2008-2012 | Research Assistant, Department of Computer Science and<br>Engineering, University of California, San Diego   |

| 2012      | Teaching Assistant, Department of Computer Science and<br>Engineering, University of California, San Diego   |

| 2012      | Doctor of Philosophy in Computer Science (Computer Engi-<br>neering), University of California, San Diego    |

### PUBLICATIONS

Nathan Farrington, George Porter, Yeshaiahu Fainman, George Papen, and Amin Vahdat, "Hunting Mice with Microsecond Circuit Switches", *Proceedings of the* 11th ACM Workshop on Hot Topics in Networks (HotNets 2012), October 2012.

Nathan Farrington, Yeshaiahu Fainman, Hong Liu, George Papen, and Amin Vahdat, "Hardware Requirements for Optical Circuit Switched Data Center Networks", *Proceedings of the Optical Fiber Communication Conference and Exposition and the National Fiber Optic Engineers Conference (OFC/NFOEC 2011)*, pp 1–3, March 2011.

Nathan Farrington, George Porter, Sivasankar Radhakrishnan, Hamid Hajabdolali Bazzaz, Vikram Subramanya, Yeshaiahu Fainman, George Papen, and Amin Vahdat. "Helios: A Hybrid Electrical/Optical Switch Architecture for Modular Data Centers", *Proceedings of the ACM SIGCOMM 2010 Conference*, pp 339–350, August 2010.

Amin Vahdat, Mohammad Al-Fares, Nathan Farrington, Radhika Niranjan Mysore, George Porter, and Sivasankar Radhakrishnan, "Scale-out Networking in the Data Center", *IEEE Micro*, 30(4), pp 29–41, July/August 2010.

Nathan Farrington, Erik Rubow, and Amin Vahdat, "Data Center Switch Architecture in the Age of Merchant Silicon", *Proceedings of the 17th IEEE Symposium* on High Performance Interconnects (HOTI 2009), pp 93–102, 2009.

### ABSTRACT OF THE DISSERTATION

### **Optics in Data Center Network Architecture**

by

Nathan Farrington

#### Doctor of Philosophy in Computer Science (Computer Engineering)

University of California, San Diego, 2012

Professor Amin Vahdat, Chair

Modern data center networks with their vast scale and bandwidth requirements are necessarily optical networks. Only optical communication technology has demonstrated capacities of 10 Gb/s, 40 Gb/s, and higher, over distances of more than 10 m. However, traditional data center network architectures limit the use of optics to the physical cables only, requiring wasteful electrical-optical-electrical conversions between every pair of switches. This dissertation presents three data center network architectures that use optics in novel ways for scaling the network, while simultaneously reducing CAPEX and OPEX, and managing cabling complexity.

The first architecture is a single large electronic packet switch with enough ports and enough capacity to interconnect every host in the data center. This architecture uses a FatTree topology of merchant silicon switch ASICs, and manages the resulting cabling complexity using a combination of horizontal-vertical arrangements of circuit boards, and aggregation to higher bitrates for multiplexing over thin optical fiber cables.

The second architecture is a hybrid electrical/optical network, with a smaller portion of the core switches being electrical packet switches and the remaining switches being optical circuit switches. Wavelength division multiplexing reduces the number of optical circuit switches and cables even further. This architecture has a lower CAPEX and OPEX than a traditional data center network, while also having a performance that approaches that of a traditional fully packet switched network. Measurements are presented from a fully working prototype network called Helios.

The third architecture is a microsecond-scale optical circuit switch that is fast enough to completely replace electronic packet switches for bulk traffic. A novel circuit scheduling algorithm is presented called traffic matrix scheduling that can support arbitrary communication patterns and executes in polynomial time. Measurements are presented from a fully working prototype switch called Mordia.

The combination of these architectures and their promise of less expensive bandwidth scaling will hopefully bring data center operators closer to the goal of treating the entire data center as a single computer.

# Chapter 1

# Introduction

Consider a data center with 1,024 racks, with each rack containing 20 servers, with each server containing 16 processor cores, 64 GB of memory, and 48 TB of storage. If these servers are interconnected with a high-performance data center network (DCN), the resulting cluster will be a supercomputer having 327,680 cores, 1.31 PB of memory, and 983 PB of storage. Such supercomputers are routinely used by companies such as Google, Microsoft, Facebook, Yahoo!, Amazon.com, eBay, and others, to provide modern web and mobile applications such as social networking, search, maps, video streaming, e-commerce, and multiplayer gaming.

This dissertation addresses the question of how should this high-performance DCN be physically constructed? Deeper integration of optical communications technologies, namely optical transmission and optical switching, into DCNs, can substantially improve performance, cost, and energy efficiency, thereby making possible to run applications that previously were too demanding for current network technologies. To briefly summarize the findings, DCNs should be constructed using select optical communications technologies to overcome the cost, power, performance, and scalability problems of traditional electronic packet switched (EPS) DCNs.

Modern data center networks with their vast scale and bandwidth requirements are necessarily optical networks. Only optical communication technology has demonstrated capacities of 10 Gb/s, 40 Gb/s, and higher, over distances of more than 10 m. However, traditional data center network architectures limit the use of optics to the physical cables only, requiring wasteful electrical-optical-electrical conversions between every pair of switches. This dissertation presents three data center network architectures that use optics in novel ways for scaling the network, while simultaneously reducing CAPEX and OPEX, and managing cabling complexity.

The first architecture (chapter 2) is a single large electronic packet switch with enough ports and enough capacity to interconnect every host in the data center. This architecture uses a FatTree topology of merchant silicon switch ASICs, and manages the resulting cabling complexity using a combination of horizontalvertical arrangements of circuit boards, and aggregation to higher bitrates for multiplexing over thin optical fiber cables.

Although other FatTree switches comprised of merchant silicon ASICs have existed prior to this dissertation, these switches were all point solutions. A data center network engineer would still have to create a solution by networking these switches together. In other words, one would still need to resolve the problem of cabling complexity. In contrast, the ambitious design of the first switch architecture spans up to an entire data center while simultaneously eliminating cabling complexity. The number of long cables is dramatically reduced from 3,456 to 96, with the 96 cables further reduced to just 24 independent bundles. Although the author cannot take credit for this phenomena, industry has moved decidedly in the direction of constructing future data center networks as FatTrees of merchant silicon, using the same techniques presented in this first architecture.

The second architecture (chapter 3) is a hybrid electrical/optical network, with a smaller portion of the core switches being electrical packet switches and the remaining switches being optical circuit switches. Wavelength division multiplexing reduces the number of optical circuit switches and cables even further. This architecture has a lower CAPEX and OPEX than a traditional data center network, while also having a performance that approaches that of a traditional fully packet switched network. Measurements are presented from a fully working prototype network called Helios. In an example data center network with 64 pods, each containing 1,024 host, allocating 10% of core switches as EPS switches and the other 90% of the core switches as OCS switches (Optical Circuit Switches), yields a cost reduction of \$62.2M down to \$22.1M, a power consumption reduction of 950.3 kW down to 157.2 kW, and a cabling complexity reduction of 65,536 long cables down to 14,016. This represents reductions of 2.8x, 6.0x, and 4.7x, respectively. Furthermore, this architecture is realizable today with commercially available components.

The second architecture shows clear wins in terms of CAPEX and OPEX reduction. But in order to realize these wins, the performance of the network must be on par with traditional FatTree EPS networks. Measurements are presented from the Helios prototype showing that a FatTree EPS network achieved an efficiency of 71.3% throughput compared to an ideal switch, while the Helios EPS/OCS hybrid network achieved an efficiency of 59.2%, over the same set of communication patterns. When these performance metrics are applied to the example data center network, the FatTree EPS would cost 1,331 \$/Gb/s and the hybrid EPS/OCS architecture would cost 569 \$/Gb/s. So while the FatTree EPS network might have more absolute performance, the performance achieved by the hybrid EPS/OCS network is more more cost effective. The same holds true for power consumption and cabling complexity.

The third architecture (chapter 4) is a microsecond-scale optical circuit switch that is fast enough to completely replace electronic packet switches for bulk traffic. A novel circuit scheduling algorithm is presented called traffic matrix scheduling that can support arbitrary communication patterns and executes in polynomial time. Measurements are presented from a fully working prototype switch called Mordia.

The primary difference between the second and third architectures is that the second architecture uses millisecond-scale OCS switches that assume a single input-output port assignment until the global traffic demand matrix changes sufficiently to warrant a reassignment, while the third architecture uses microsecondscale OCS switches that can switch between a schedule of assignments to approximate any communication pattern. This makes microsecond-scale OCS switches much more useful than millisecond-scale switches and further reduces the need for EPS switches entirely.

The combination of these architectures and their promise of less expensive bandwidth scaling will hopefully bring data center operators closer to the goal of treating the entire data center as a single computer.

### 1.1 Scope

There are several related questions which are outside the scope of this dissertation. One similar and important question is *what is the best DCN topology*? When viewed from the lens of graph theory, a DCN can be understood as a graph, with vertices representing cores and switches, and weighted edges representing data communication links. The author's investigation into this problem suggestions that the question of the optimal topology is closely intertwined with both communication patterns as well as packaging constraints. There has been preliminary work in this field [6]. We differentiate between "topology" and "architecture" by noting that a topology is a parameterized mathematical construct, but by itself is not a network. In contrast, an architecture is a blueprint for constructing a network, and a network will have a particular topology. Architecture encompasses many practical details such as cost, power consumption, packaging, and cabling complexity, as well as traditional network metrics such as capacity and latency.

Another popular question is *what is the best communication protocol (e.g. link-layer, addressing, transport)*? There has been much work in this field as well. Currently, software-defined networking (SDN) and network virtualization are popular research directions, and many are seeking to understand how such technologies could fit into a DCN architecture. Eventually, it is hoped that all such questions will be answered, however this dissertation focuses only on the question of data center network architecture.

Figure 1.1: An electrical conductor attenuates the input power.

# 1.2 Copper is Dead

Although the title of this section might seem sensational, the fact that copper physically cannot support the high bitrates required by WANs, HPC interconnects, and now most recently DCNs, is actually conventionally accepted by the optical and electrical engineering communities. However, this fact is not yet well known in computer science.

Consider an electrical conductor used for data communication, such as a copper cable (Figure 1.1). If input power is applied to the electrical conductor then a smaller amount of output power will be measured on the other side. The input power is attenuated and typically is dissipated as heat.

What is the minimum output power? Measurements of a 10 Gb/s SFP+ optical transceiver showed a receiver sensitivity of -19 dBm (12.59  $\mu$ W). In other words, the receiver required an input power level of at least 12.59  $\mu$ W to differentiate between zeros and ones. Receiver sensitivity varies widely between different communication technologies (electrical, optical, wireless). The exact receiver sensitivity is actually immaterial for this section, but -19 dBm is assumed as the minimum output power for this example.

What is the maximum input power? Consider a copper wire with a diameter of 3.6 mm, corresponding to an American Wire Gauge (AWG) number of 7. This is a relatively thick wire for data communication. Such a wire would have a fusing current<sup>1</sup> of 561 A, meaning that after carrying 561 A for 10 seconds, this wire would melt<sup>2</sup>. For this example, 561 A is the maximum input current. Assuming a

<sup>&</sup>lt;sup>1</sup>https://en.wikipedia.org/w/index.php?title=American\_wire\_gauge&oldid= 523999576

$<sup>^{2}</sup>$ A safe amperage for this wire would be far less, around 30 A.

| Bit Rate (Gb/s) | dB/m  | Loss/m | Max length (m) |

|-----------------|-------|--------|----------------|

| 1               | 0.721 | 15.3%  | 106            |

| 10              | 2.28  | 40.8%  | 33.5           |

| 40              | 4.56  | 65.0%  | 16             |

| 100             | 7.21  | 81.0%  | 10.6           |

Table 1.1: Attenuation and maximum length of AWG 7 copper wire.

signaling level of 1 V, the maximum input power would be 57.49 dBm (561 W).

Subtracting these two numbers, 57.49 - (-19) = 76.49, gives a power budget of 76.49 dB. In other words, if an input power of 57.49 dBm is attenuated by 76.49 dB, then the output power would be -19 dBm, which is the minimum output power in this example.

How much power is lost due to attenuation by the copper cable? Unfortunately, the attenuation of an electrical conductor increases with the square root of the signal frequency. Miller and Ozaktas [7] gives an attenuation of  $7.2 \times 10^{-6}\sqrt{f}$  dB/m for AWG 7 copper wire. Table 1.1 shows the attenuation of AWG 7 copper wire in terms of loss per meter, for the common bit rates of 1 Gb/s, 10 Gb/s, 40 Gb/s, and 100 Gb/s. The results are sobering. At 10 Gb/s, 40.8% of the input power is lost per meter. At 100 Gb/s, 81.0% of the input power is lost per meter. This is compounded. For two meters, 96.39% of the input power is lost at 100 Gb/s. The last column shows the theoretical maximum cable length for AWG 7 copper wire.

One should note that the IEEE 1000BASE-T standard supports 1 Gb/s Ethernet (1.25 Gb/s at Layer 1) at distances of 100 m using 8 strands of the much thinner AWG 24 copper wire, with a power consumption far lower than 561 W. The reason is that 1000BASE-T uses sophisticated digital signal processing (DSP) to increase the signal-to-noise ratio. The Shannon-Hartley Theorem (1.1) gives the capacity, C, of a communication channel as

$$C = f \, \lg(1 + \text{SNR}) \tag{1.1}$$

C is proportional to the signal frequency, f, but only logarithmically proportional to the signal-to-noise ratio. This means that DSP techniques that increase the SNR provide exponentially smaller benefit than increasing the signal frequency, and cannot be used to overcome the fact that the attenuation of copper cables is frequency-dependent. At sufficiently high bitrates, copper is dead.

In contrast, the attenuation of single-mode optical fiber is  $2.0 \times 10^{-4}$  dB/m, meaning that it has a loss rate of 0.0046% per meter, and this loss rate is independent of frequency. Optical fiber also has a theoretical maximum bandwidth (frequency) of 50 THz, corresponding to a maximum bitrate of 330 Tb/s [8]. In addition, optical fiber is extremely thin and light, so it can be bundled into densely into cables to further increase the capacity, and is resistant to electromagnetic interference.

But optical communications are not a panacea to the problems encountered in constructing high-performance interconnects. The required lasers add cost, heat, and reliability concerns. Optical fiber is also more fragile than copper wire. But despite these concerns, there is currently no known alternative communications technology that can compete with optical fiber for implementing high-performance networks. The future of data center networking is optical networking.

# Chapter 2

# Reducing Cabling Complexity with Optics

Traditional packet-switched data center networks (DCNs) that scale to tens of thousands of hosts currently use highly-specialized and custom ASICs, with correspondingly high development costs. Simultaneously, these networks also face significant performance and management limitations at scale. Just as commodity processors and disks now form the basis of computing and storage in the data center, there is an opportunity to leverage emerging high-performance commodity merchant switch silicon as the basis for a scalable, cost-effective, modular, and more manageable DCN fabric. Due to the ever increasing demand for bisection bandwidth, DCNs are necessarily constructed as a mesh of interconnected packet switches. However, these switches are currently packaged individually, which wastes resources, and connected manually, which is labor intensive and error prone. This chapter describes how to save cost and power by repackaging an entire DCN as a distributed multi-stage switch using a FatTree topology of merchant silicon ASICs instead of a crossbar topology of proprietary ASICs, with optical fiber used to replace multiple copper cables via bandwidth aggregation. Compared to a FatTree of discrete packet switches, a 3,456-port 10 Gigabit Ethernet realization of this design costs 52% less, consumes 31% less power, occupies 84% less space, and reduces the number of long, cumbersome cables from 6,912 down to 96, relative to existing approaches.

## 2.1 Introduction

With the help of parallel computing frameworks such as MapReduce [9], organizations routinely process petabytes of data on computational clusters containing thousands of nodes. For these massively parallel workloads, the principal bottleneck is often not the performance of individual nodes, but rather the rate at which nodes can exchange data over the network. Many data center applications demonstrate little communication locality, meaning that the communication substrate must support high aggregate bisection bandwidth for worst-case communication patterns. Unfortunately, modern DCN architectures typically do not scale beyond a certain amount of bisection bandwidth [10] and become prohibitively expensive well in advance of reaching their maximum capacity [11], in some cases oversubscribed by a factor of 240 [12].

There is interest in replacing these expensive packet switches with many smaller, commodity switches, organized into a FatTree topology [11]. But as the number of packet switches grows, so does the cabling complexity and the difficulty of actually constructing the network, especially on a tight schedule and with a minimum amount of human error. FatTrees have been used successfully in telecom networks [13], HPC networks [14], and on chips [15], but not yet in data center Ethernet networks. One reason is the fear of the resulting cabling complexity from trying to interconnect thousands of individual switches and the overhead of managing a large number of individual switch elements.

In addition to the cabling problem, networks of discrete packet switches are unnecessarily wasteful in the data center. The relative close proximity of the compute nodes and the single administrative domain provide opportunities for eliminating redundant components, such as packaging, power conditioning circuitry, and cooling. Multiple CPUs and memory banks could be consolidated to save cost and power. Consolidation could also reduce the cost of inter-switch links, which often use expensive and power hungry optical transceivers.

This chapter describes the design a multi-stage switch architecture leveraging merchant silicon to reduce the cost, power consumption, and cabling complexity of DCNs, while also increasing the bisection bandwidth available to parallel applications such as MapReduce. In essence, a FatTree of discrete packet switches is repackaged as a single distributed multi-stage switch, and redundant components are eliminated to save cost and power. One realization of this architecture is presented: a 3,456-port 10 Gigabit Ethernet (10 GbE) switch with 34.56 Tb/s of bisection bandwidth. Using commodity 24-port 10 GbE merchant silicon as the fundamental building block, cost, power, and cabling complexity is further reduced by the design and implementation of a new Layer 2 protocol, called Ethernet extension protocol (EEP), in hardware to aggregate four 10 GbE links into a single 40 GbE link, and vice versa. Aggregation to higher bitrates makes optical fiber cables more economical and helps justify their use in replacing multiple copper cables. The combination of custom packaging, the EEP protocol, and optical fiber, reduces the number of inter-switch cables from 6,912 to just 96. This architecture generalizes to 65,636 ports of 10 GbE with 64-port 10 GbE switch silicon.

# 2.1.1 Bisection Bandwidth, Cabling Complexity, and Fat-Trees

The primary goal when constructing a DCN for a computational cluster is to provide enough bisection bandwidth so that communication-intensive parallel computations can maintain high levels of CPU utilization. A bisection of a network is a partition into two equally-sized sets of nodes. The sum of the capacities of links between the two partitions is called the bandwidth of the bisection. The *bisection bandwidth* of a network is the minimum such bandwidth along all possible bisections. Therefore, bisection bandwidth can be thought of as a measure of worstcase network capacity.

Cabling complexity is the number of long inter-switch cables required to construct a particular DCN. Short intra-rack cables or cables that cross between adjacent racks are not difficult to install and maintain, but long cables require planning and overhead cable trays. They are also more difficult to test and to replace after a break. This in turn increases the cost of the network.

The FatTree topology is very promising because it provides an enormous amount of bisection bandwidth while using only small, uniform switching elements.

Figure 2.1: A 3-tier (5-stage) FatTree using 4-port switching elements.

Figure 2.1 shows a small example of the FatTree topology constructed from 4-port switching elements. This example is equivalent to a 16-port switch. Bandwidth scaling is achieved by having multiple, redundant paths through the network. However, if one is not careful, these links can translate into a large degree of cabling complexity, making the network impractical to construct and maintain.

## 2.2 Technologies

DCNs are composed of racks, switches, cables, and transceivers. This section briefly reviews these four technologies.

### 2.2.1 Racks

Almost all data processing and networking equipment is housed in large metal racks [16]. A typical rack measures 0.6 m wide by 1.0 m deep by 2.0 m high, has an unloaded weight of 170 kg, and can support a maximum load of 900 kg[17]. A 2.0 m high rack is partitioned into 42 vertical rack units (denoted as RU, or simply U). Each RU is 44.45 mm (1.75 in) high. Rack-mountable equipment occupies one or more rack units.

Racks are lined up side-by-side in rows. To assist with cooling, rows face front-to-front and back-to-back to form what are called *cold aisles* and *hot*

*aisles* [18]. A cold aisle is at least 1.22 m (4 ft) wide and allows human access to the front panels of the racks. A hot aisle is at least 0.9 m wide and is heated by the air exhaust from the servers' cooling fans. Most cables are in the hot aisles.

Generally, there are three ways to route cables between racks. If the racks are in the same row, then the simplest way is to run the cables inside the racks. Specialized wire management solutions exist to facilitate this. If there are lots of cables, then it may be best to leave the top one or two RUs empty. If the racks are in different rows, then it is common to run the cables along the ceiling, suspended in overhead cable trays. This is standard practice since it reduces clutter and prevents safety hazards [18]. Some data centers have raised floors with removable tiles. The space underneath the floor can also be used to route cables, including power cables.

### 2.2.2 Switches

The most common Ethernet switch in the data center is the so-called *top-of-rack* (TOR) switch. This is a 1-RU switch that is placed in the top position in a rack and connects to all of the compute nodes in that rack. These switches are becoming commodities due to the recent emergence of merchant silicon. TOR<sub>1</sub> in Table 2.1 is a 48-port GbE / 4-port 10 GbE switch. Prices typically range between \$2,500 and \$10,000. TOR<sub>10</sub> is a 24-port 10 GbE switch, with prices between \$5,000 and \$15,000. Both switches consume approximately 200 W of power.

Table 2.1: Ethernet switch models.

|              | $\mathrm{TOR}_1$ | $\mathrm{TOR}_{10}$ | EOR    |

|--------------|------------------|---------------------|--------|

| GbE Ports    | 48               | 0                   | 0      |

| 10 GbE Ports | 4                | 24                  | 128    |

| Power $(W)$  | 200              | 200                 | 11,500 |

| Size (RU)    | 1                | 1                   | 33     |

Also present in data centers are so-called *end-of-row* (EOR) switches. An EOR switch derives its name from the fact that it is placed in a rack, sometimes by itself due to its size, and all nearby switches in other racks connect directly to it. EOR switches are also called *modular* switches, because they accept a

variety of modules, called *line cards*, with different Layer 1 interfaces and different combinations of switching fabrics and network processors. EOR in Table 2.1 is a 128-port 10 GbE switch. Prices range between \$500,000 and \$1,000,000.

### 2.2.3 Cables and Transceivers

Table 2.2 lists properties of Ethernet cables and transceivers. The Telecommunications Industry Association recommends Cat-6 UTP instead of Cat-5e for new data center installations [18]. MMF120 is 120 strands of MMF in a single cable. Note that the maximum range depends on the modal bandwidth of the cable. Ranges shown here reflect the highest-quality cable at the time of standardization.

Table 2.2: Data center communication cables and transceivers.

|                | Cat-6 | Twinax | MMF120 | Units |

|----------------|-------|--------|--------|-------|

| Cable cost     | 0.41  | 11.2   | 23.3   | \$/m  |

| Cable weight   | 42    | 141    | 440    | g/m   |

| Cable diameter | 5.5   | 7      | 25     | mm    |

### **Gigabit Ethernet**

| Standard          | 1000BASE-T | N/A | 1000BASE-SX |    |

|-------------------|------------|-----|-------------|----|

| Range             | 100        | N/A | 550         | m  |

| Transceiver cost  | 10         | N/A | 36          | \$ |

| Transceiver power | 0.42       | N/A | 0.5         | W  |

#### 10 Gigabit Ethernet

| Standard          | 10GBASE-T | 10GBASE-CX4 | 10GBASE-SR |    |

|-------------------|-----------|-------------|------------|----|

| Range             | 30        | 15          | 300        | m  |

| Transceiver cost  | 100       | 100         | 250        | \$ |

| Transceiver power | 6         | 0.1         | 1          | W  |

### 40 Gigabit Ethernet

| Standard          | N/A | N/A | 40GBASE-SR4 |    |

|-------------------|-----|-----|-------------|----|

| Range             | N/A | N/A | 300         | m  |

| Transceiver cost  | N/A | N/A | 600         | \$ |

| Transceiver power | N/A | N/A | 2.4         | W  |

The term "Ethernet cable" usually refers to unshielded twisted pair (UTP) copper cable. UTP cable is available in different grades, which do not always correspond directly with IEEE Layer 1 standards. For example, Cat-5e allows

GbE links of up to 100 m and Cat-6a allows 10 GbE links of up to 100 m. Twinax ("InfiniBand") shielded cable allows 10 GbE links of up to 15 m, but with different engineering trade offs. For example, since twinax is shielded, the manufacturing cost is higher than UTP, but transceivers are less expensive and consume less power.

Optical fiber cables are becoming more common in the data center as 10 GbE is introduced. Multimode fiber (MMF) is often preferred over single-mode fiber (SMF) because optical transceivers for multimode fiber are significantly less expensive. OM-3 "laser grade" MMF allows 10 GbE links longer than 300 m. Distribution fiber cable can pack multiple fiber strands within a single physical cable. Typical densities are multiples of 12. A bidirectional link actually requires two fibers, so a 120-strand fiber cable only has 60 bidirectional communication channels.

A transceiver converts signals between a circuit board and a communications cable. For UTP and twinax copper cable, transceivers are packaged into a chip and placed directly onto the circuit board. Ethernet is standardized for speeds of 1 Gb/s over UTP (1000BASE-T), and 10 Gb/s over twinax (10GBASE-CX4) and UTP (10GBASE-T). UTP uses the popular "RJ-45" connector, whereas twinax uses the Fujitsu "InfiniBand" connector.

There are a number of different Layer 1 protocols for optical fiber, depending on the carrier wavelength, the bit rate, the encoding, multimode vs. single mode, etc. The networking industry has taken the 7-Layer OSI model quite literally by separating the Ethernet MAC functions (Layer 2) from the Ethernet PHY transceiver functions (Layer 1) through the use of pluggable optical transceiver modules. These modules are standardized by various Multi Sourcing Agreements (MSAs) to define standard mechanical and electrical form factors. This allows Ethernet device manufacturers to specialize in Layer 2 and Layer 3 functionality, and allows the end user to choose their desired Layer 1 protocol just by plugging in a module.

The most common optical module standard for GbE is the SFP module [19]. Recently, SFP+ [20] has become the dominant standard for 10 GbE. These modules use the LC connector, which couples two fibers together into close proximity. The QSFP transceiver is being developed for 40 GbE using an emerging standard to be named 40GBASE-SR4. This module will be slightly larger than SFP and SFP+ modules and will use an MT connector with 8 optical fibers (4 transmit, 4 receive). MT connectors are available with up to 72 optical fibers.

### 2.3 Motivation

Al-Fares et al. [11] proposes the construction of a 3-tier FatTree of 2,880 commodity 48-port GbE TOR switches, providing 27.648 Tb/s of bisection bandwidth. However, this network is almost impossible to construct following their suggested packaging. It would require 1,128 separate cable bundles, each of which must be manually and independently routed and installed. They partitioned the network into 48 separate pods (switches and servers) that communicate through a core switch array of 576 48-port switches. Assuming that a pod has a 3 m diameter and the distance between two pods is 1.5 m, their proposal would require 226,972 m of cable, weighing 9,532 kg.

Two simple rules will at least allow the construction of small FatTrees, thereby gaining the benefit of the FatTree topology and commodity switches. First, minimize the number of unique cable bundles. The Al-Fares proposal required k(k-1)/2 bundles because the top tier of the network was collocated with the k pods. However, by placing the top tier in a central location, only k bundles are required (from the pods to the central location). Second, use optical fiber cable instead of copper cable. Compared to copper, fiber is much thinner and lighter. Cables containing more than 72 fibers are readily available.

Following these rules, an alternative FatTree network based on the recently commoditized 24-port 10 GbE TOR switch could be constructed. At the time of writing, these switches are available from several manufacturers for between \$5K and \$15K. Connecting 720 such switches into a 3-tier FatTree topology will yield a bisection bandwidth of 34.56 Tb/s. Each of the 24 pods will contain 24 switches, co-located in a single rack. The 144 core switches will be distributed

over 4 racks. The 3,456 long fiber cables can be combined into just 24 bundles of cable. The estimated total cost is approximately \$7.2M, which is \$2,000 per port. This network is both less expensive and provides more bisection bandwidth than a traditional DCN constructed from modular packet switches [11].

# 2.3.1 Merchant Silicon and the Commodity Top-of-Rack Switch

The original IP routers used in the Internet were implemented entirely in software running on CPUs. As total Internet traffic grew, stand-alone IP routers emerged containing hardware acceleration for the most common network functionality (e.g. longest prefix matching, CRC calculation), with the CPU being relegated to less common or more complicated functionality (e.g. control messages, routing protocols). The hardware acceleration is now called the fast path, and the software running on the CPU is now called the slow path.

For small IP routers and Ethernet switches, it is possible to implement the entire fast path on a single chip. Network equipment manufacturers such as Cisco, HP, Juniper, Brocade, and Force10, have traditionally designed their own ASICs, for use solely in their own products. For larger products, multiple ASICs are used. Little is known publicly about these ASICs, except one can assume that their capabilities follow Moore's law.

The last decade has seen the introduction of merchant silicon: networking ASICs produced for the network equipment mass market. For example, there are currently at least three separate makers of 24-port 10 GbE switch ASICs: Broad-com, Fulcrum, and Fujitsu. All three product offerings provide similar degrees of functionality. Table 2.3 shows that the three chips also have similar properties. Due to NDAs, some numbers could not be published, but they are comparable.

Several companies have used these ASICs to create 24-port TOR switches. Since purchasing merchant silicon is much easier and less expensive than creating a custom switch ASIC, these companies can offer TOR switches at a lower cost to consumers, which was the original motivation for constructing an entire DCN out of TOR switches. Because these manufacturers choose from the same pool of

|         | 1        |                        |                           |

|---------|----------|------------------------|---------------------------|

| Maker   | Broadcom | Fulcrum                | Fujitsu                   |

| Model   | BCM56820 | FM4224                 | MB86C69RBC                |

| Ports   | 24       | 24                     | 26                        |

| Cost    | NDA      | NDA                    | \$410                     |

| Power   | NDA      | $20 \mathrm{W}$        | $22 \mathrm{W}$           |

| Latency | < 1 us   | 300  ns                | 300  ns                   |

| Area    | NDA      | $40 \ge 40 \text{ mm}$ | $35 \ge 35 \ \mathrm{mm}$ |

| SRAM    | NDA      | 2  MB                  | 2.9 MB                    |

| Process | 65  nm   | 130  nm                | 90 nm                     |

**Table 2.3**: Comparison of 10 GbE switch ASICs.

merchant silicon, they differentiate their products primarily through the features in their custom software. But the board and chassis designs are usually very similar.

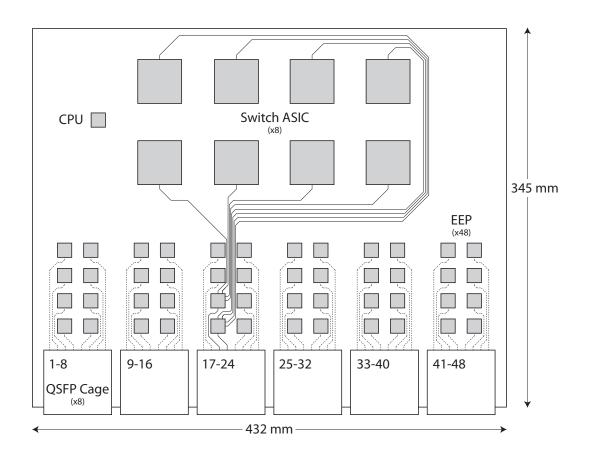

Figure 2.2 shows the board layout of a 24-port 10 GbE TOR switch; the cost and power consumption of these parts are given in Table 2.6. The power supply unit (PSU) and fans are physically separated from the main circuit board for signal integrity. Each SFP+ cage allows for up to 8 SFP+ modules. There is one PHY chip per SFP+ module.

A switch ASIC by itself is not an Ethernet switch; it is only the fast path. To build a functional switch, several other chips are needed, as well as software for handling networking protocols such as Minimum Spanning Tree or OSPF. This software runs on a local CPU. The CPU does not need to be very powerful since the amount of required computation is typically small. Common operating systems include Linux and VxWorks. The CPU also requires supporting chips such as DRAM for system memory and flash for secondary storage.

A switch also contains several PHY chips, which are used to bridge the Layer 1 protocol supported by the ASIC with the Layer 1 protocol exposed by the switch. For example, an ASIC may only support XAUI natively, but by adding a PHY chip, the XAUI protocol can be converted into 10GBASE-T, which allows Cat-6a cables to be connected to the switch.

These three classes of chips: ASICs, CPUs, and PHYs, are the primary building blocks of switches and routers. Sometimes switches will contain other chips such as flash memory for nonvolatile storage or FPGAs for glue logic. Also present are power supply units (PSUs) and fans. Although optical transceiver

Figure 2.2: Layout of a 24-port 10 GbE TOR switch.

modules are not technically part of the switch, they are included in the analysis since they contribute greatly to the overall cost and power.

# 2.4 Design of a 3,456-port Switch

This section describes the design of a 3,456-port 10 GbE switch. What makes this switch novel is that it is comprised entirely of merchant silicon, connected in a FatTree topology. In contrast, large Ethernet switches from traditional network equipment manufacturers use multiple proprietary ASICs and a crossbar topology. One simple and completely optional ASIC, called EEP, is introduced in section 2.6 to further reduce the cost, power consumption, and cabling complexity of the overall design. In section 2.5, it is shown how this switch is strictly better than a FatTree of commodity TOR switches.

Figure 2.3: Example deployment of the 3,456-port switch.

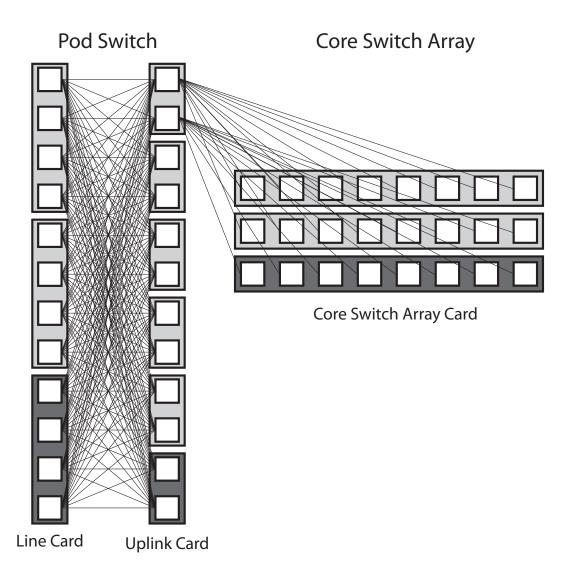

### 2.4.1 Overview

Figure 2.3 shows an overview of the 3,456-port switch. Rather than build one monolithic switch, the design is separated into 24 pod switches and a core switch array. A pod switch occupies 4 rack units of space, whereas each of the two core switch array modules occupies 9 rack units of space. A pod switch is basically the bottom two tiers of the FatTree; the core switch array forms the top tier.

Each pod switch can function as a standalone 144-port 10 GbE switch. But when connected to the core switch array, the pod switches act as a single noninterfering [21, p112] switch. The pod switches can also be incrementally deployed as the network is built out. When fully deployed, the switch has 3,456 ports and 34.56 Tb/s of bisection bandwidth. Each pod switch connects to the core switch array with four parallel cables, each cable carrying 72 multimode fibers. These cables can be routed in an overhead cable tray.

The core switch array is not a monolithic switch; it is a collection of 144 individual 24-port switches. The array is separated into two modules to provide

Figure 2.4: Pod switch physical organization.

fault tolerance and to allow a limited form of incremental deployment. It is also possible to divide the core switch array into 4 modules, but our analysis showed that it would increase the overall cost of the system. The core switch array is shown installed into a single rack for illustration purposes, but in actual deployment, the modules would be physically separate to provide fault tolerance of critical network infrastructure, e.g. in the face of localized power failure.

### 2.4.2 Pod Switch: Organization

The pod switch is constructed from multiple circuit boards, assembled as shown in Figure 2.4. The midplane separates and connects the three line cards and the six uplink cards. The horizontal-vertical arrangement allows each line card to connect directly with each uplink card, and vice versa. At the center of the switch chassis is a single midplane circuit board. The midplane provides three important functions. First, it connects the line cards to the uplink cards through high-density high-speed electrical connectors. Second, it provides power to all of the line cards and daughter cards. Third, it contains a CPU that manages the state of the pod switch. The midplane design is quite simple since communication signals from each line card pass directly to each uplink card, and vice versa. Since the line cards are mounted horizontally and the uplink cards are mounted vertically, this can be called a *horizontal-vertical arrangement*.

The electrical connectors are inexpensive and available from several ven-

dors [22]. The male connectors are attached to the midplane and the female connectors are attached to the cards. Each connector has at least 16 pins to support 8 differential channels of 10 GbE between one line card and one uplink card. There are 18 connectors per pod switch, plus additional connectors for power distribution.

In addition to these boards, the chassis also contains dual redundant power supply units (PSUs), which have been omitted from Figure 2.4 for clarity. They are located in the back of the chassis on the left and right sides of the uplink cards.

### 2.4.3 Pod Switch: Line Card

Figure 2.5 shows the layout of a line card. Each line card essentially replaces four discrete 24-port switches from the edge layer of the network and eliminates redundant components. The four switch ASICs separate the board into two halves. The bottom half of the board contains 48 SFP+ optical transceiver cages and 48 PHY chips, to convert between the SFP+ 10G electrical interface (SFI) and the IEEE XAUI standard for 10 GbE. Figure 2.5 shows 12 solid traces running from the SFP+ cages, to the PHYs, to one of the switch ASICs. The other traces are shown with dotted lines to indicate that they also continue, but have been removed from the diagram for clarity.

The CPU is shown off to the side. It connects directly to the four switch ASICs using the PCI Express bus. This allows the CPU software to configure the switch ASICs, and allows exceptional Ethernet frames to be sent from the switch ASICs over the PCI Express bus to the CPU for further processing.

The top half of the board contains an additional 48 PHYs and 6 electrical connectors. These PHYs convert between XAUI and 10GBASE-KR, which is the IEEE standard for 10 GbE over backplanes. 10GBASE-KR is more robust than XAUI when passing between different boards. Figure 2.5 shows an additional 12 traces from the switch ASIC to one row of PHYs on the top half of the board. Two traces from each switch ASIC are routed to each of the 6 uplink cards.

Circuit boards are divided into multiple layers and can be categorized as either signal layers or power/ground layers. Figure 2.6 shows that the line card requires four separate signal layers to route all copper traces. Congestion occurs in

Figure 2.5: Pod switch line card.

Figure 2.6: Layers of the pod switch line card circuit board.

the top half of the board where each switch ASIC must connect to each connector. This figure is not to scale.

### 2.4.4 Pod Switch: Uplink Card

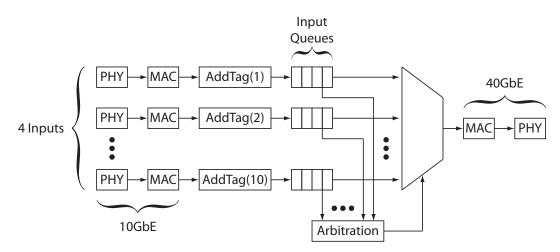

The uplink card performs two functions. First, it acts as a switch fabric for the pod switch, allowing the 12 switch ASICs on the 3 line cards to connect to each other. Second, it forwards traffic to and from the core switch array.

Figure 2.7 shows the layout of an uplink card. Each uplink card essentially replaces two discrete 24-port switches from the aggregation layer of the network. Like the line card, the uplink card is also divided into two halves. The bottom half connects to the midplane with electrical connectors. The 8 traces from each line card are routed to 8 PHYs, and then split between the two switch ASICs. In Figure 2.7, traces connecting to the first switch ASIC are shown as solid lines, whereas traces connecting to the second switch ASIC are partially shown as dotted lines. This half of the board requires two separate signal layers. Other traces have been removed from the diagram for clarity.

The top half of the board contains six EEP ASICs and six QSFP cages. Each EEP ASIC connects to four ports of the switch ASIC using the XAUI protocol and connects to one of the QSFP modules using the QSFP electrical interface. The EEP ASIC is described in more detail in section 2.6. Essentially, the top half of the board is aggregating the 24 ports of 10 GbE into 6 ports running the custom

Figure 2.7: Pod switch uplink card.

Figure 2.8: Fiber management units.

EEP protocol at 40 Gb/s.

Experience from a prototype system indicates that most exceptional packet processing happens either on the line card or in the core switch array, rather than on the uplink card. For this reason, a dedicated CPU is deliberately omitted from the uplink card. Instead, all 6 uplink cards are managed by system-level CPU located on the midplane. It is also possible to place a CPU on each uplink card with a modest increase in cost.

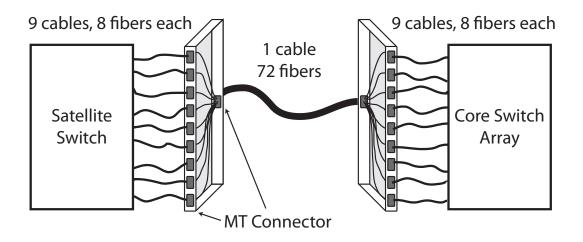

### 2.4.5 Fiber Management

QSFP modules use a high-density fiber connector called an MT-connector. QSFP specifically uses an MT-connector with 8 parallel fibers and collects them into one cable. Since each pod switch can support 36 such QSFP modules, this would mean 36 parallel 8-fiber cables that must be routed to the core switch array.

Cable management is simplified by aggregating nine 8-fiber cables into a single 72-fiber cable by using a mechanical device called a fiber management unit, shown in Figure 2.8. Such devices are commercially available. This reduces the 36 parallel 8-fiber cables into 4 parallel 72-fiber cables.

A 72-strand fiber cable from a pod switch is split into nine separate 8-fiber cables, corresponding to the pod switch's nine separate QSFP modules. Each 8fiber cable terminates at a different core card. Just like the pod switch midplane, this is another horizontal-vertical arrangement, but performed with cables.

### 2.4.6 Core Switch Array

The core switch array contains 18 independent core switch array cards, partitioned into two modules with 9 cards each. The choice of core switch array packaging is largely arbitrary since the 144 separate 24-port switches do not communicate with each other directly. The cards do not connect to a backplane and their co-location is merely a matter of simplifying cable management and packaging. The absence of a backplane greatly reduces the cost of the core switch array and allows our design to scale to even larger FatTree switches in the future.

Figure 2.9 shows the layout of a core switch array card. Each card essentially replaces eight discrete 24-port switches from the core layer of the network. Each card contains a CPU, 8 switch ASICs, 48 EEP ASICs, and 48 QSFP modules. Figure 2.9 shows 8 traces from two EEP ASICs connecting to the 8 different switch ASICs. Although there are a total of 192 connections between the EEP ASICs and the switch ASICs, only 8 signal layers are required, one per switch ASIC. A 9th signal layer is required for the CPU to connect to the switch ASICs. Current circuit board manufacturing techniques make it difficult to design boards with more than 10 signal layers, so this layout is the most efficient in terms of board area utilization without becoming an engineering challenge. More exotic designs can double the number of signal layers to 20, but the engineering challenge increases correspondingly.

Figure 2.10 shows the internal topology of the 3,456-port switch. Only one of the 24 pod switches is shown. When fully deployed, each ASIC on each line card connects to each ASIC on each uplink card, and each pod switch connects to each of the 144 core switch ASICs. Each uplink card connects to exactly three core switch array cards, for a total of 18 core switch array cards in a fully deployed system. The fact that this is a small, finite number is useful for scaling to larger FatTree switches in the future. In order to achieve full bisection bandwidth, each pod switch must connect to each of the 144 core switch ASICs. If a mistake is made when constructing the network, a pod switch might end up with two or more

$Figure \ 2.9: \ Core \ switch \ array \ card.$

Figure 2.10: Topology of the 3,456-port switch.

parallel links to the same core switch ASIC, which would subtract from the overall bisection bandwidth.

By design, the EEP protocol helps prevent installation mistakes. The four links leaving an ASIC on a pod switch uplink card travel to a single core switch array card, where they connect to four *different* core switch ASICs. The core switch array card is designed such that the top row of 24 QSFP modules connect only to the top row of switch ASICs, and the bottom row of QSFP modules only to the bottom row of switch ASICs. Therefore, as long as each pod switch connects to *exactly* one upper and one lower port on each core switch array card, the network will achieve full bisection bandwidth.

### 2.4.7 Incremental Deployment

The 3,456-port switch was designed to support incremental deployment. A very small network can start with a single pod switch and no core switch array. Each pod switch line card can be installed as more ports are needed. However, all 6 uplink cards must be installed for non-interfering throughput. Uplink cards can also be installed incrementally to reduce cost or if some degree of oversubscription can be tolerated. Each uplink card provides 1/6 of the total aggregate pod switch bandwidth. For a single pod switch, the QSFP modules are not needed.

A single pod switch can provide up to 1.44 Tb/s of bisection bandwidth. Adding a second pod switch then requires the installation of the core switch array. However, if fault tolerance is not a concern, then it is possible to install just one of the two core switch array modules. Also, if some degree of oversubscription can be tolerated, then not all nine core switch array cards need be installed. Each core switch array card provides 1/18 of the total aggregate core switch array bandwidth.

One core switch array module can support up to 12 pod switches with no oversubscription. In this deployment, each pod switch will connect all of its uplink cables to the same core switch array module, rather than splitting them between the two modules. Once the 13th pod switch is installed, both core switch array modules will be required. The four 72-strand fiber cables from each of the pod switches must be distributed evenly among the core switch arrays. This could require disconnecting and reconnecting a small number of cables.

This upgrade could be performed while the switch is operational, without dropping any packets. The idea is to use the management interface to take certain pod switch uplink cards offline, migrate the cables, and then reactivate the uplink cards. As long as only a few uplink cards are disabled at any one time, the overall network should maintain connectivity but with a slightly reduced amount of bisection bandwidth.

# 2.5 Comparison

In this section, the design from section 2.4 is compared with two other possible implementations of a 3,456-port 10 GbE FatTree switch. These are referred to as Network 1, 2, and 3, respectively.

**Network 1.** This network can be constructed immediately without any hardware engineering. It is comprised of 720 discrete 24-port 10G TOR switches (see  $\text{TOR}_{10}$  in Table 2.1) connected in the same FatTree topology described in section 2.4. All inter-switch links use SFP+ optical transceivers and multimode fiber cable.

**Network 2.** This network requires board and chassis design. Instead of discrete TOR switches, the boards and chassis from section 2.4 are used. However, Network 2 does not use EEP or 40 GbE QSFP modules. Instead, Network 2 simply replaces these components with additional 10 GbE PHYs and SFP+ modules.