© 2023 IEEE

IEEE Transactions on Power Electronics, 2023

# A General Analysis of Resonant Switched Capacitor Converters Using Peak Energy Storage and Switch Stress Including Ripple

N. M. Ellis

N. C. Brooks

M. E. Blackwell

R. A. Abramson

S. Coday

R. C. N. Pilawa-Podgurski

Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# A General Analysis of Resonant Switched Capacitor Converters Using Peak Energy Storage and Switch Stress Including Ripple

Nathan M. Ellis, *Member, IEEE*, Nathan C. Brooks, *Student Member, IEEE*, Margaret E. Blackwell, *Student Member, IEEE*, Rose A. Abramson, *Student Member, IEEE*, Samantha Coday, *Member, IEEE*, Robert C. N. Pilawa-Podgurski, *Senior Member, IEEE*

Abstract—This work presents a general analytical framework enabling large-signal characterization of resonant switchedcapacitor (ReSC) power converters that accounts for passive component voltage and current ripple, for operation at and above resonance. From this, appropriate phase durations for minimized rms currents are derived, in addition to expressions for total passive component volume using an intuitive peak energy method. An example hardware prototype validates both the derived waveforms and timings-as well as total passive volume—through three comparable hardware configurations, one of which minimizes passive component volume. In addition, the proposed technique formulates analytical expressions for both rms currents and peak blocking voltages, facilitating refined loss estimation and component selection. Subsequent calculation of the large-signal Volt-Amp (VA) switch stress metric allows a more accurately quantified trade-off between active and passive components compared to prior work, which has not fully accounted for ripple. Four common ReSC topologies are exemplified throughout, with topology specific parameters documented for reference.

Index Terms—DC-DC converters, hybrid switched capacitor, resonant power conversion.

# I. INTRODUCTION

RESONANT switched capacitor (ReSC) power converters (e.g., Fig. 1) are a relatively new class of converter topology primarily relying on capacitors as energy transfer elements, leveraging their superior energy density over magnetics [1]. However, to mitigate the well-known slow-switching limit (SSL) impedance [2] and associated pulse inrush currents in pure switched capacitor (SC) converters, some small inductance is introduced to enable "soft-charging" of the flying capacitors [3]–[5]. When soft-charged, capacitor voltage ripple may be greatly increased without incurring large SSL losses. This allows for more effective energy density utilization of the capacitors which perform most of the voltage conversion [6], while the added magnetics are subjected to

Manuscript received XXXXXXX; accepted XXXXXXXX. Parts of the analysis in Section III of this paper were presented at the 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL) [DOI: 10.1109/COMPEL53829.2022.9830004]. (Corresponding author: Robert Carl Nikolai Pilawa-Podgurski.)

The authors are with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720 USA (e-mail: nathanmilesellis@berkeley.edu; nathanbrooks@berkeley.edu; black-well@berkeley.edu; rose\_abramson@berkeley.edu; scoday@berkeley.edu; pi-lawa@berkeley.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

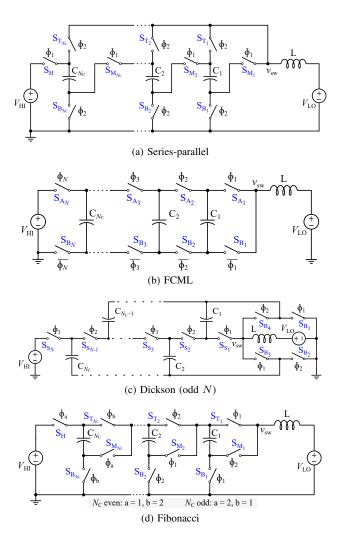

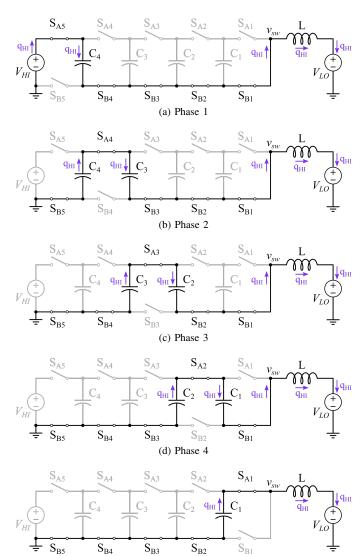

Fig. 1. Four common N:1 ReSC converters with "inductor-at-the-output": (a) series-parallel, (b) flying capacitor multilevel (FCML), (c) Dickson (odd N), and (d) Fibonacci. Here N refers to the conversion ratio and  $N_{\rm C}$  refers to the total number of capacitors.

reduced volt-seconds. Recent demonstrations [7]–[12] have considered these benefits and illustrate dramatic net reductions in overall ReSC converter volume as compared with more traditional architectures (e.g. buck/boost).

Prior literature has presented analytical methods to calculate both the minimum achievable passive component volume and output impedance for these types of converter; however, these analyses are often limited to ReSC converters operating exactly at resonance (e.g., [12], [13]). While this operating point facilitates zero current switching (ZCS) for reduced switching loss, other work in [14]–[21] has established that operating some ReSC converters above resonance can significantly improve overall converter efficiency through a reduction in rms currents and associated conduction losses, despite increases in relative switching loss. Although above resonance operation has been demonstrated in practice, a characteristic analysis has been lacking. The framework presented in [12] is not applicable, while a provision (parameter  $\beta$ ) in [13], [22] characterizing the ratio of rms to dc current allows the analysis therein to be extended to above-resonance operation without being explicitly derived.

This work therefore contributes a generalized analytical technique enabling complete characterization of ReSC operation while operating both at and above resonance. No small-ripple approximations are made, resulting in an accurate large-signal solution accounting for both voltage and current ripple on capacitors and inductors, respectively. In addition, the presented analysis is simplified with respect to [12] (which required instantaneous power integrals to be evaluated) and only requires the use of inherent topology characteristics, such as the number of components and phases, and standard charge flow vectors, similar to those described by the analytical method for pure SC converters presented in [2].

While the methodology presented here can be extended and applied to any ReSC converter topology, this work restricts its application to a subset of ReSC converters capable of operating effectively above resonance. Specifically, this work considers fixed-ratio (N:1) ReSC converter topologies with a single inductor placed in series with the low-side port, as is the case for several common example topologies depicted in Fig. 1. Termed "direct" in [22], [23], "inductor-at-the-output" in [19], and here as "inductor-at-the-low-side-port" (to accommodate step-up 1:N variants), these structures are capable of operating both at or significantly above their nominal resonant switching frequency. When operated above resonance, the inductor enters a forward continuous conduction mode where the converter exhibits a lower sensitivity to component or timing mismatch, in addition to the aforementioned reduction in rms current.

In contrast, LC-tank type ReSC structures (e.g. [10], [24]-[28]), termed "indirect" in [23], are constrained to at- or near- resonant operation since they either incur excessive circulating currents when operated above resonance, or hardcharging losses when operated below resonance without the introduction of discontinuous conduction states or dynamic off-time modulation [27], [29], [30]. Consequently, tank-based topologies have a susceptibility to component and timing mismatch and require either active auto-tuning control [31], [32], or accurate component tolerance and stability with aging, temperature, and bias-disqualifying Class II multilayer ceramic capacitors (MLCCs) [33] and soft-saturating magnetics. Conversely, the switches within tank topologies generally experience favorable constant blocking voltages that are independent of load since voltage ripple is hidden within LC-tank elements [17], [28]—serving to simplify design. Both "direct" and "indirect" topology variations exhibit theoretically identical total passive component volume when operated at

TABLE I

SURVEY OF ANALYTICAL METHODS

FOR SWITCHED-CAPACITOR CONVERTERS

|         | Work            | Type     | Above<br>Resonance | Analyzes Ripple                                          |                               | Calculates<br>Loss |

|---------|-----------------|----------|--------------------|----------------------------------------------------------|-------------------------------|--------------------|

|         |                 | Type Res |                    | Passives                                                 | Switches                      | Loss               |

| SC      | Seeman [2]      | -        | -                  | $\Delta v_{\mathrm{C}}$                                  | None                          | Yes                |

| Pure SC | McRae [39]      | -        | -                  | $\Delta v_{ m out}$                                      | $\Delta v_{ m out}$           | Yes                |

| ReSC    | Pasternak [22]  | Direct   | Yes                | $\Delta i_L *$                                           | $\Delta i_L*$                 | Yes                |

|         | He [27]         | Indirect | -                  | $\Delta v_{\rm C}, \; \Delta v_{\rm out}, \; \Delta i_L$ | None                          | Yes                |

|         | McLaughlin [13] | Both     | No                 | $\Delta i_L$                                             | $\Delta i_L$                  | Yes                |

|         | Ye [12]         | Both     | No                 | $\Delta v_{\rm C},\Delta i_L$                            | None                          | No                 |

|         | This Work       | Direct   | Yes                | $\Delta v_{\rm C},  \Delta i_L$                          | $\Delta v_{\rm C},\Delta i_L$ | No                 |

<sup>\*</sup>explicit derivation of rms current provided for at-resonance operation only.

resonance, irrespective of inductor count, when inductance is distributed accordingly [12]. However, unless a common core can be used in indirect multi-inductor designs, the magnetics of direct single inductor ReSC designs scale more favorably [34], lending further preference to direct variants. Moreover, the LC tanks within indirect topologies require bidirectional inductor current, necessitating a  $2\times$  increase in flux density ripple,  $\Delta B$ , as compared to the uni-polar current observed in equivalent direct converters, where much of the spectral power is concentrated at dc, having implications for magnetic losses [35], [36].

Following this reasoning, the subset of ReSC converters evaluated in this work (single inductor "direct" topologies) are simultaneously highly attractive and challenging to fully analyze. Analytical expressions for peak ratings are derived for both the capacitor voltages and inductor current, aiding the practicing engineer in component selection. These expressions also permit a derivation of the minimum passive component volume, both at- and arbitrarily above- resonance. The general expressions derived herein collapse into the results presented in [12] when constrained to resonant operation, further validating this general approach. In addition, this framework is used to improve the fidelity of calculated switch stress metrics. Prior switch stress computations typically use simplified voltage and current calculations to characterize the switches, such as neglecting the effects of capacitor voltage ripple on switch voltage [2], [12], [20], [37] or neglecting the effects of inductor current ripple on switch current [2], [12]. Here we calculate the precise peak switch voltages and rms currents and demonstrate that prior simplifying assumptions can lead to significant under-sizing of switches for high-ripple designs. Moreover, while minimized passive component volume is emphasized, the presented framework assists with global optimization efforts (e.g., [38]) by providing the large-signal values and waveforms needed for accurate loss estimation.

Table I summarizes, categorizes, and highlights the limitations of several analytical approaches to SC and ReSC analysis presented in the literature. For example when assessing passive volume, [12] addresses both capacitor voltage ripple,  $\Delta v_{\rm C}$ , and inductor current ripple,  $\Delta i_{L}$ , for both direct and indirect

topologies, strictly at resonance. However, the impact of ripple on switch stress is not considered.

Furthermore, since this article constrains consideration to steady-state fixed-ratio converter operation, several important additional aspects are not discussed here, but have been investigated in prior work. These include: start-up, shut-down and transient response [40]–[46]; capacitor voltage and inductor current balancing [47]–[53]; lossless regulation [54], [55] and droop control [2], [56]; zero voltage switching (ZVS) capability [19]; and reliability [57].

This work is organized as follows. Section II presents the base assumptions and analytical framework necessary to characterize the operation of a general (lossless) fixed-ratio ReSC topology. Section III introduces closed-form expressions for phase timings both at and arbitrarily above resonance. A direct energy-based approach for quantifying total passive component volume/mass through assessment of per-component peak energy storage requirements is proposed in Section IV, along with an optimization method to minimize total passive volume. Generalized results are presented for several common ReSC topologies. Section V presents a hardware example illustrating the described analysis. Switch stress including full capacitor voltage and inductor current ripples is assessed in Section VI. Section VII summarizes and discusses the results obtained in Sections III-VI, and contextualizes the trade-offs between different ReSC topologies. Finally, Section VIII concludes this work.

#### II. FRAMEWORK DEFINITION

The proposed framework stems from conventional vectorized descriptions of switched capacitor converters in [2], [5], [22], [58] and is derived from fundamental charge-balance and zero volt-second principles. In addition, we assume periodic steady-state operation, with dynamic response beyond the scope of this work. Ideal circuit elements are also assumed, with no ohmic losses or parasitic effects. This assumption is valid for moderate- to heavy-load operation and where ohmic losses have minimal impact on the large-signal dynamics of a converter designed for high efficiency (e.g.  $\eta \ge 95\%$ ). Phase durations are chosen so each phase begins and ends with the same inductor current, implying zero inductor voltseconds within each phase. This constraint is justified in Appendix A, and validated with hardware in Section V. Lastly, input and output bypass capacitance is assumed large with respect to the flying capacitors, thus the input and output sources can be considered ideal as is done in many existing models and analyses [2], [5], [9], [17], [22], [56]. Finite input/output bypass capacitors may be included as part of a comprehensive analysis that facilitates port voltage ripple constraints [59], [60], however, this adds significant analytical complexity and is omitted here for conciseness. This framework applies not only to two-phase ReSC, but also to multi-phase/multi-resonant converters—more than two phases in a switching period—such as the flying capacitor multi-level (FCML) converter in Fig. 1b.

To begin, several topologically-defining vectors are obtained through careful analysis and deduction for each ReSC structure under consideration. These are summarized in Table II and

TABLE II

DEFINITION OF CHARACTERISTIC TERMS

| N                               | Conversion ratio, $N:1$ for $N \in \mathbb{N} \geq 2$                                                                                       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| $N_{\rm C}$                     | Total number of flying capacitors                                                                                                           |

| $N_{ m P}$                      | Total number of phases within a switching period                                                                                            |

| $N_{\rm S}$                     | Total number of switching devices                                                                                                           |

| $a_{{\scriptscriptstyle X},ji}$ | Net charge through the $i{\rm th}$ element of type $X$ (C, L, or S), during phase $j,$ normalized to high-side charge quantity $q_{\rm HI}$ |

| $v_i$                           | Mid-range dc voltage on $i{\rm th}$ capacitor, normalized to high-side voltage $V_{\rm HI}$                                                 |

| $c_i$                           | Capacitance of $i$ th capacitor, normalized to arbitrary scaling capacitance $C_0$                                                          |

| $\kappa_j$                      | Equivalent capacitance seen by the inductor during phase $j$ , normalized to capacitance $C_0$                                              |

| $\omega_{0,j}$                  | Natural angular frequency of the equivalent LC network during phase $j$                                                                     |

| $t_j$                           | Time duration of phase $j$                                                                                                                  |

| $	au_j$                         | Time duration of phase $j$ normalized to the full switching period $T_{\rm sw}$                                                             |

listed in order of appearance throughout the following sections. General matrices are defined in addition to example values for the series-parallel topology depicted in Fig. 1a.

# A. Charge Flow Matrices: $a_x$

As is typical for purely capacitor-based converters [2], periodic steady-state analysis of ReSC structures also begins by assessing charge flow through the converter. To do so, charge flow quantities through all circuit elements are normalized to the amount of charge periodically conducted by the high-side port,  $q_{\rm HI}$ , as

$$q_{X,ji} = q_{HI} a_{X,ji} \tag{1}$$

where X is the circuit element type (e.g., capacitor, C; inductor, L; or switch, S), j is the phase index, and i is the element index. The charge quantity  $q_{\rm HI}$  is itself an operating parameter defined as

$$q_{\rm HI} = \frac{I_{\rm HI}}{f_{\rm SW}} = I_{\rm HI} T_{\rm SW} \tag{2}$$

where  $I_{\rm HI}$  is the average high-side port current and  $f_{\rm SW}$  is the periodic switching frequency (with associated switching period  $T_{\rm SW}$ ). Subsequently the normalized charge flow matrix,  $a_{\rm X}$ , is comprised of topologically-dependent entries which are invariant of operating point (i.e., power level, voltage, and switching frequency) whereas  $q_{\rm HI}$  scales the charge conducted through all elements in unison, while preserving their relative relationships.

Periodic steady-state requires the capacitors conduct zero net charge per full switching period, as described by

$$\sum_{j=1}^{N_{\rm P}} a_{{\rm c},ji} = 0, \tag{3}$$

where  $N_{\rm P}$  is the number of operating phases. Utilizing this

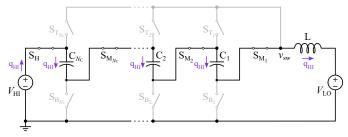

(a) Phase 1: Series connection

Fig. 2. Charge flow in an N:1 Series-Parallel converter.

characteristic, values for  $a_c$ , and subsequently  $a_L$  and  $a_s$ , can then be obtained by inspection.

For example, Fig. 2 depicts the periodic steady-state charge flow through an N:1 series-parallel step-down converter operating with two switching phases  $(N_{\rm P}=2)$  and with  $N_{\rm C}=N-1$  flying capacitors. During phase 1, charge  $q_{\rm HI}$  is provided by the high-side source  $V_{\rm HI}$ , and is admitted by all series-connected flying capacitors. In adherence with (3), each flying capacitor must then release charge  $q_{\rm HI}$  during phase 2. Subsequently, the normalized capacitor charge values,  $a_{{\rm C},ji}$ , for the series-parallel topology are

$$\mathbf{a}_{\mathbf{c}_{[N_{\mathbf{P}}\times N_{\mathbf{C}}]}} = \begin{bmatrix} \frac{q_{\mathbf{C},11}}{q_{\mathbf{HI}}} & \frac{q_{\mathbf{C},12}}{q_{\mathbf{HI}}} & \dots & \frac{q_{\mathbf{C},1N_{\mathbf{C}}}}{q_{\mathbf{HI}}} \\ \frac{q_{\mathbf{C},21}}{q_{\mathbf{HI}}} & \frac{q_{\mathbf{C},22}}{q_{\mathbf{HI}}} & \dots & \frac{q_{\mathbf{C},2N_{\mathbf{C}}}}{q_{\mathbf{HI}}} \end{bmatrix}$$

$$= \begin{bmatrix} 1 & 1 & \dots & 1 \\ -1 & -1 & \dots & -1 \end{bmatrix}$$

(4)

where the first row's entries correspond to phase 1 and the second row's entries correspond to phase 2. The charge matrices  $a_L$  and  $a_S$  are similarly determined.

Also apparent from Fig. 2, the charge admitted by  $V_{\rm LO}$  over both phases is equal to  $q_{\rm LO}=(N_{\rm C}+1)\,q_{\rm HI}$ , yielding the converter's voltage conversion ratio:

$$\frac{V_{\rm HI}}{V_{\rm LO}} = \frac{I_{\rm LO}}{I_{\rm HI}} = \frac{q_{\rm LO}f_{\rm sw}}{q_{\rm HI}f_{\rm sw}} = \frac{(N_{\rm C}+1)\,q_{\rm HI}}{q_{\rm HI}} = N. \tag{5}$$

Moreover, converter power throughput,  $P_{\rm HI}$ , may be expressed in terms of the average high-side charge  $q_{\rm HI}$  as

$$P_{\rm HI} = I_{\rm HI} V_{\rm HI} = \frac{q_{\rm HI}}{T_{\rm CNV}} V_{\rm HI}.$$

(6)

Table VIII records the charge flow matrices for the flying capacitors,  $a_C$ , the low-side inductor,  $a_L$ , and the switches,  $a_S$ , for the four common ReSC topologies depicted in Fig. 1.

# B. Mid-Range Flying Capacitor Voltage Vector: v

Each flying capacitor's mid-range voltage is defined as the dc value symmetrically centered between the maximum and minimum voltage, as dictated by ripple. This value is distinct from the time-averaged dc voltage which can deviate significantly in multi-phase converters. Here the mid-range voltages can be derived from an assumption of zero average voltage across the inductor (i.e., zero volt-seconds) within each phase. Under this assumption, the inductor may be treated as a short circuit when applying average KVL loops to each phase. Subsequently the absolute mid-range voltages of each flying capacitor,  $V_{\rm C_I}$ , may be expressed with respect to the high-side voltage,  $V_{\rm HI}$ , as

$$V_{\mathbf{C}_i} = V_{\mathsf{HI}} \, v_i, \tag{7}$$

where  $v_i$  represents the normalized (to  $V_{\rm HI}$ ) mid-range voltage. By applying per-phase average KVL to the N:1 series-parallel depicted in Fig. 2, during phase 2 each flying capacitor is connected in parallel with—and thus holds a voltage equal to— $V_{\rm LO}$ . Using the conversion ratio relationship established in (5), the normalized capacitor voltage vector,  $\boldsymbol{v}$ , is defined as

$$\boldsymbol{v}_{[1\times N_{\mathrm{C}}]} = \begin{bmatrix} \frac{V_{\mathrm{C}_{1}}}{V_{\mathrm{HI}}} & \frac{V_{\mathrm{C}_{2}}}{V_{\mathrm{HI}}} & \cdots & \frac{V_{\mathrm{C}_{N_{\mathrm{C}}}}}{V_{\mathrm{HI}}} \end{bmatrix}$$

$$= \begin{bmatrix} \frac{1}{N} & \frac{1}{N} & \cdots & \frac{1}{N} \end{bmatrix}.$$

(8)

Although beyond the scope of this work, certain multiresonant topologies—e.g., the multi-resonant doubler [61] and the cascaded series-parallel [62]—or switching schemes—e.g., split-phase switching [63], [64]—have mid-range voltages dependent on load [58], adding significant analytical complexity.

# C. Capacitance Vector: c

While some topologies have no strict constraints on capacitance sizing (e.g. FCML converter), others require specific relative sizing to prevent hard-charging and retain simplified clocking schemes, as derived in [5], [58], [65], [66] for example. The absolute capacitance of each flying capacitor,  $C_i$ , is normalized to a single capacitance value,  $C_0$ , as

$$C_i = C_0 c_i \tag{9}$$

and by doing so, the required relative capacitor relationships are preserved as the single value  $C_0$  changes—a useful feature for the analytical passive component volume minimization performed in Section IV.

Considering the exemplar series-parallel topology, all capacitors conduct equal charge in each phase, and must express identical voltage ripple characteristics when connected in parallel during phase 2. Thus, by Q=CV (and to ensure soft-charging behavior) each capacitor must be equal in value, yielding

$$\boldsymbol{c}_{[1\times N_{\mathrm{C}}]} = \begin{bmatrix} \frac{C_1}{C_0} & \frac{C_2}{C_0} & \cdots & \frac{C_{N_{\mathrm{C}}}}{C_0} \end{bmatrix}$$

$$= \begin{bmatrix} 1 & 1 & \cdots & 1 \end{bmatrix}.$$

(10)

The normalized capacitance vector, c, is documented in Table VIII for the series-parallel, Dickson, and Fibonacci

topologies; and for the FCML topology, all capacitances are chosen to be equal for simplicity.

#### D. Lumped Equivalent Capacitance Vector; $\kappa$

During each switching phase j, the inductor forms a secondorder resonant impedance network with the connected flying capacitors, which have an equivalent lumped capacitance,  $C_{e,j}$ . This value is then normalized with respect to  $C_0$ , yielding  $\kappa$ :

$$C_{e,j} = C_0 \,\kappa_j. \tag{11}$$

In phase 1 of the example series-parallel converter (Fig. 2), all capacitors are connected in series and the equivalent capacitance seen by the inductor is

$$C_{e,1} = C_1 ||C_2|| \cdots ||C_{N_c} = \frac{1}{N_C} C_0$$

(12)

whereas in phase 2 all capacitors are connected in parallel relative to the inductor and the equivalent capacitance is

$$C_{e,2} = C_1 + C_2 + \dots + C_{N_c} = N_C C_0.$$

(13)

More generally, the normalized equivalent capacitance vector,  $\kappa$ , is defined and shown for the series-parallel topology as

$$\boldsymbol{\kappa}_{[N_{\mathrm{P}} \times 1]} = \begin{bmatrix} \frac{C_{\mathrm{c},1}}{C_0} \\ \frac{C_{\mathrm{c},2}}{C_0} \end{bmatrix}$$

$$= \begin{bmatrix} \frac{1}{N_{\mathrm{C}}} \\ N_{\mathrm{C}} \end{bmatrix}$$

(14)

and is tabulated for additional topologies in Table VIII.

This section has obtained fundamental topology-dependent parameters. However, in order to fully characterize the large signal behaviour of a ReSC converter, including passive volume and switch stress both at and above resonance (discussed in Sections IV-VII), switching-frequency dependencies must also be derived. The following Section III explores how phase timings and current waveforms depend on switching frequency.

#### III. PHASE TIMINGS

A "direct" ReSC converter can be switched at its natural resonant switching frequency,  $f_{\rm sw,0}$ , to achieve zero current switching (ZCS) at each phase transition. However, dissimilar to "indirect" or LC-tank topologies, the switching frequency of a direct topology may also be increased without incurring increased circulating currents [16]. Subsequently, we define a free parameter,  $\Gamma$ , as the ratio of the actual switching frequency,  $f_{\rm sw}$ , to the natural resonant switching frequency

$$\Gamma = \frac{f_{\text{sw}}}{f_{\text{sw},0}} = \frac{T_{\text{sw},0}}{T_{\text{sw}}}.$$

(15)

Resonant ZCS is obtainable at  $\Gamma=1$  (i.e., at-resonance operation), while for  $\Gamma>1$  (i.e., above-resonance operation) the inductor enters continuous conduction mode (CCM). In practice, values of  $\Gamma<1$  (i.e., below-resonance operation) would only be implemented with a modified discontinuous conduction mode (DCM) or dynamic off-time modulation (DOTM) [29], [30], otherwise SSL losses would reemerge.

The motivation for operation above resonance operation has been explored in [14]–[18], [20], [21] as a method for reducing conduction losses and improving overall efficiency. However, for several topologies—including the FCML converter and resonant N-phase implementations of Cockcroft-Walton and Dickson converters [67], [68]—the phase durations depend heavily on the relationship between the natural resonant switching frequency and the implemented  $f_{\rm sw}$ . Given that a rigorous proof of the necessary phase timings for above resonance operation has not been demonstrated in the literature, [16], [17] instead relied on closed-loop control to converge on appropriate phase durations.

Therefore, this section expands on an earlier version of this work in [21] to explicitly derive the required relative phase durations for any given switching frequency at or above resonance ( $\Gamma \geq 1$ ). Continuous closed-form expressions are derived for phase-timing durations which minimize the peak, peak-to-peak, and rms inductor current both at resonance and for arbitrary frequencies above resonance. The presented analysis yields a robust method for explicitly determining the phase durations as well as the inductor current waveform used for the switch stress analysis in Section VI.

#### A. Phase Duration Vector: au

Each phase duration,  $t_j$ , can be defined in terms of the full switching period,  $T_{\rm sw}$ , using a normalization parameter,  $\tau_j$ ,

$$t_j = T_{\rm sw} \, \tau_j \tag{16}$$

where  $T_{\rm sw}$  defines the sum of all  $N_{\rm P}$  phase durations

$$T_{\text{sw}} = \sum_{j=1}^{N_{\text{P}}} t_j.$$

(17)

The normalized phase duration vector,  $\tau$ , is deduced from the resonance of the inductor current  $i_L(t)$  for each topology and as a function of  $\Gamma$ .

When operating at the resonant switching frequency,  $f_{\rm sw,0}$  (i.e.,  $\Gamma=1$ ), each phase is half-wave resonant with  $i_{\rm L}(t)$  starting and ending at 0 A. Thus the phase duration,  $t_j$ , equals half the duration of the natural resonant period,  $T_{0,j}$ , of the lumped LC resonant tank in the jth phase or

$$t_j|_{\Gamma=1} = T_{\text{sw},0} \cdot \tau_j|_{\Gamma=1} = \frac{T_{0,j}}{2}$$

(18)

as per (16).

The natural angular frequency,  $\omega_{0,j}$ , associated with  $T_{0,j}$  can be expressed as

$$\omega_{0,j} = \frac{1}{\sqrt{L \cdot C_0 \kappa_j}} = \frac{2\pi}{T_{0,j}} = \frac{\pi}{t_j|_{\Gamma=1}}$$

(19)

since parameter  $\kappa_j$  defines the lumped equivalent capacitance.

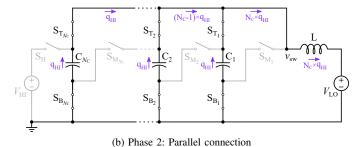

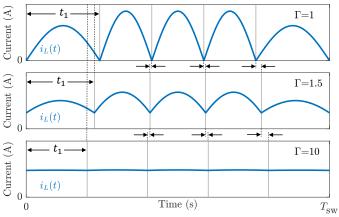

Calculating the phase durations,  $t_j$ , for operation above resonance (i.e.,  $\Gamma > 1$ ) requires further analysis. Within each phase j, if the inductor is subjected to zero volt-seconds, then it forms a symmetrically centered sinusoidal segment<sup>1</sup>, as depicted in Fig. 3. Continuity in  $i_L(t)$  between adjacent

<sup>&</sup>lt;sup>1</sup>Appendix A demonstrates timings calculated under this assumption always satisfy both charge balance and inductor current continuity in periodic steadystate.

Fig. 3. Two adjacent phases of the inductor current waveform,  $i_L(t)$ , operating above resonance. Each phase constitutes a symmetrically centered sinusoidal segment with angular frequency governed by (19).

phases (including  $j=N_{\rm P}$  and j=1) can be expressed mathematically as

$$I_{\text{pk},j}\cos\left(\omega_{0,j}\frac{t_{j}}{2}\right) = I_{\text{pk},j+1}\cos\left(\omega_{0,j+1}\frac{-t_{j+1}}{2}\right), \quad \forall j \leq N_{\text{P}}$$

(20)

where  $I_{pk,j}$  is the peak current in phase j.

Furthermore during phase j, the inductor conducts charge  $q_{\mathbf{L},j}$ , where

$$\begin{aligned} q_{\text{L},j} &= \int_{-\frac{t_{j}}{2}}^{\frac{t_{j}}{2}} I_{\text{pk},j} \cos(\omega_{0,j} t) dt \\ &= \frac{2I_{\text{pk},j}}{\omega_{0,j}} \sin\left(\omega_{0,j} \frac{t_{j}}{2}\right) = q_{\text{HI}} a_{\text{L},j}, \quad \forall j \leq N_{\text{P}} \end{aligned} \tag{21}$$

which relates to the known normalized charge flow matrix,  $a_{\rm L}$ , and can be rearranged with respect to  $I_{{\rm pk},j}$  as

$$I_{\text{pk},j} = \frac{q_{\text{HI}} a_{\text{L},j} \omega_{0,j}}{2 \sin\left(\omega_{0,j} \frac{t_j}{2}\right)}, \quad \forall j \le N_{\text{P}}.$$

(22)

Combining the phase-to-phase current continuity (20) and perphase charge flow (22) yields

$$\frac{a_{\text{L},j} \, \omega_{0,j}}{\tan\left(\omega_{0,j} \frac{t_{j}}{2}\right)} = \frac{a_{\text{L},j+1} \, \omega_{0,j+1}}{\tan\left(\omega_{0,j+1} \frac{t_{j+1}}{2}\right)}, \quad \forall j \le N_{\text{P}}. \tag{23}$$

Equation (23) can be solved using (19) and (16), to determine appropriate normalized phase durations,  $\tau_j$ , for each phase. The resultant vector,  $\tau$ , is documented for the four topologies in Table VIII. For all two-phase converters,  $\tau_j$  is notably independent of  $\Gamma$ , as will be demonstrated for the series-parallel converter in Example 1. However, as detailed in [21], phase durations for the FCML converter vary with  $\Gamma$ . This derivation, documented as Example 2, is more complex, yielding an implicit transcendental equation with an approximated numerical solution.

# Example 1: Series-Parallel Converter

Consider the two-phase series-parallel topology with arbitrary conversion ratio N in Fig. 2 as an example. Substituting the normalized equivalent capacitance vector,  $\kappa_j$ , (from Table VIII) into the natural angular frequency,  $\omega_{0,j}$ , during each phase in (19) yields

$$\omega_{0,1} = \sqrt{N-1} \cdot \frac{1}{\sqrt{LC_0}} \tag{24}$$

and

$$\omega_{0,2} = \frac{1}{\sqrt{N-1}} \cdot \frac{1}{\sqrt{LC_0}}$$

(25)

with the corresponding relationship between these two frequencies as

$$\omega_{0,1} = (N-1)\,\omega_{0,2}.\tag{26}$$

Next, (26) and values for normalized inductor charge flow,  $a_{L,j}$ , (recorded in Table VIII) are substituted into the steady-state charge flow and inductor continuity constraint given by (23), yielding

$$\tan\left(\omega_{0,1}\frac{t_1}{2}\right) = \tan\left(\frac{\omega_{0,1}}{N-1} \cdot \frac{t_2}{2}\right). \tag{27}$$

The argument of each tangent is then equated to find a relationship between the two phase time durations

$$t_1 = \frac{1}{N-1} t_2. (28)$$

For this two-phase topology

$$T_{\rm sw} = t_1 + t_2,$$

(29)

and therefore the normalized phase durations,  $\tau_i$ , become

$$\tau_{[N_{\rm P} \times 1]} = \begin{bmatrix} \frac{t_1}{T_{\rm sw}} \\ \frac{t_2}{T_{\rm sw}} \end{bmatrix}$$

$$= \begin{bmatrix} \frac{1}{N} \\ \frac{N-1}{N} \end{bmatrix}$$

(30)

where  $\tau$  only varies with conversion ratio and not  $\Gamma$ . This result is also recorded in Table VIII.

In addition, substituting (26) and (28) into (20) reveals  $I_{pk,1} = I_{pk,2}$ —a consistent result for all two-phase converters considered in this work.

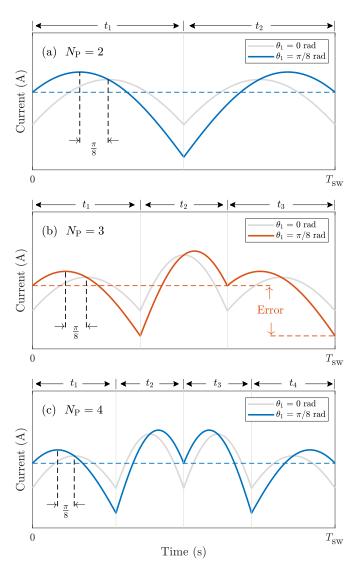

Example 2: Flying Capacitor Multi-Level (FCML) Converter

While Example 1 exhibits consistent phase durations atand above-resonance, the phase durations are more complex for the higher order  $(N \ge 3)$  resonant FCML converter. Extensive literature explores the dynamic behavior of the PWM regulating FCML converter, both using time domain [47], [48], [50], [52], [53], [69] and frequency domain [70]–[72] methods. However less discussion surrounds the resonant, fixed-ratio variation capable of achieving smaller magnetic volume. In regulating mode, conventional symmetric phaseshifted PWM dictates identical phase durations. However in resonant mode, phase durations deviate to accommodate the differing natural resonant frequencies within each phase. This adjustment improves capacitor balancing and overall converter efficiency [16], [17], [21]. While [16], [17] explored aboveresonance operation of N=3 and N=6 FCML converters, these works expanded on the valley current control scheme in [73] to converge on optimal phase durations through active feedback without providing an analytical solution. Here we provide an accurate closed form solution for appropriate phase timings, accounting for all  $\Gamma \geq 1$ .

Fig. 4 depicts the phase progression for an exemplar FCML converter with N=5. Using this same nomenclature, (31)

Fig. 4. Schematics for the phase progression of a 5:1 FCML converter (N=5), highlighting the charge flow during each phase. Charge flow is normalized with respect to the high-side input charge quantity  $q_{\rm HI}$ .

(e) Phase 5

describes the normalized lumped capacitance presented to the inductor during each phase,  $\kappa$ , in terms of arbitrary integer conversion ratio N.

$$\kappa_j = \begin{cases} 1 & \text{for } j \in \{1, N\} \\ \frac{1}{2} & \text{for } j \in 2 \le \mathbb{N} \le (N - 1) \end{cases}$$

(31)

Consequently the first and last phases have identical durations, while all phases in between have a different (but equal) duration. Thereby, we can limit consideration to the first and second phase intervals only, where the full switching period may be expressed as

$$T_{\text{sw}} = \sum_{j=1}^{N} t_j = 2t_1 + (N-2)t_2.$$

(32)

Evaluating (19) with (31)

$$\sqrt{2}\,\omega_{0,1} = \omega_{0,2} \tag{33}$$

and substituting into (23) produces an implicit equation for  $t_1$

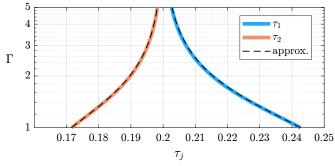

Fig. 5. Numerical solution of relative phase durations  $\tau_1$  and  $\tau_2$  for a 5:1 FCML converter across  $\Gamma$ . The closed-form approximations are superimposed with dashed lines and differ by less than 0.03% of the switching period.

Fig. 6. Simulated inductor current waveforms  $i_{\rm L}(t)$  for a 5:1 resonant FCML converter, demonstrating the required change in phase durations as a function of  $\Gamma$ .

and  $t_2$ ,

$$\sqrt{2} \tan\left(\omega_{0,1} \frac{t_1}{2}\right) = \tan\left(\sqrt{2} \,\omega_{0,1} \frac{t_2}{2}\right). \tag{34}$$

This implicit equation of phase durations does not reduce analytically, but it can be solved numerically using (32) as a constraint. From inspection of the numerical solution, an accurate closed-form expression for the relative phase durations is approximated as a function of N and  $\Gamma$  as

$$\tau_{1} = \frac{t_{1}}{T_{\text{sw}}} \approx \left(\frac{1}{N} - \frac{\sqrt{2}}{2\sqrt{2} + N - 2}\right) \cdot \frac{\Gamma}{\pi} \sin\left(\frac{\pi}{\Gamma}\right) + \frac{\sqrt{2}}{2\sqrt{2} + N - 2}$$

(35)

$$\tau_{2} = \frac{t_{2}}{T_{\text{sw}}} \approx \left(\frac{1}{N} - \frac{1}{2\sqrt{2} + N - 2}\right) \cdot \frac{\Gamma}{\pi} \sin\left(\frac{\pi}{\Gamma}\right) + \frac{1}{2\sqrt{2} + N - 2}.$$

(36)

Fig. 5 shows both the numerical and analytical approximations for  $\tau_1$  and  $\tau_2$  for an N=5, FCML converter example. The error between the numerical and analytical results is negligible, validating the accuracy of (35) and (36). Finally, Fig. 6 depicts simulated inductor current waveforms for various  $\Gamma$ , highlighting the change required in  $t_1$  (and correspondingly  $t_2$ ) to ensure zero volt-second per phase.

#### IV. PASSIVE COMPONENT VOLUME/MASS

To characterize passive component volume/mass, and subsequently enable converter size/weight minimization, expressions are derived for both total flying capacitor and inductor volume/mass, as dictated by their peak energy storage requirements.

A direct energy method is demonstrated here, expanding on the flying capacitor analysis in [58], and using the phase timings derived in Section III to further obtain expressions for peak inductor energy. Dissimilar to [12], this approach circumvents the need to analytically generalize and integrate instantaneous power waveforms (i.e.,  $p(t) = v(t) \cdot i(t)$ ) for every passive component.

While the results of the proposed method and [12] are equivalent for operation at resonance, the proposed method generalizes the passive component requirements for arbitrary switching frequencies *above* resonance (i.e.,  $\Gamma > 1$ ) where both the peak flying capacitor voltage and inductor current are diminished.

# A. Total Peak Flying Capacitor Energy Storage

To calculate the total flying capacitor energy storage requirement, consider the peak voltage expressed on each flying capacitor, as a function of load, while noting these events may not occur simultaneously in time for each flying capacitor. Moreover, since a flying capacitor may admit charge over multiple phases before achieving its peak voltage—as is the case for the multi-resonant doubler [61] and cascaded seriesparallel [62] topologies—a modified charge flow quantity  $\hat{a}_{\mathrm{C},i}$  is defined describing the maximum deviation in stored charge on the ith flying capacitor throughout a full switching cycle². For converters in which each flying capacitor only admits charge during a single phase (e.g., Fig. 1),  $\hat{a}_{\mathrm{C},i}$  is defined as

$$\hat{a}_{C,i} = \max_{j \in [N_P]} a_{C,ji}, \tag{37}$$

which for two-phase converters may be simplified to

$$\hat{a}_{c,i} = |a_{c,ii}| \quad \forall j \in \{1, 2\}$$

(38)

since each capacitor must admit and release the same quantity of charge across both phases in periodic steady-state.

Subsequently the peak-to-peak voltage ripple,  $\Delta v_{\mathrm{pp},i}$ , on each flying capacitor, i, may be described as

$$\Delta v_{{\rm pp},i} = \frac{\hat{q}_{{\rm c},i}}{C_i} = \frac{q_{{\rm HI}}\,\hat{a}_{{\rm c},i}}{C_0c_i} \eqno(39)$$

The peak energy storage requirement follows for the *i*th capacitor across all phases as

$$E_{C,pk,i} = \max_{j \in [N_P]} \left\{ \frac{1}{2} C_i V_{pk,C_i}^2 \right\}$$

$$= \frac{1}{2} C_0 c_i \cdot \left( V_{HI} v_i + \frac{1}{2} \Delta v_{pp,i} \right)^2$$

(40)

where the peak capacitor voltage is the mid-range voltage plus half the peak-to-peak voltage ripple, or  $V_{\rm pk,C_{\it i}}=V_{\rm C_{\it i}}+\frac{1}{2}\Delta v_{\rm pp,\it i}$ .

The total peak flying capacitor energy over all  $N_{\rm C}$  capacitors is then

$$E_{\text{C,tot}} = \sum_{i=1}^{N_C} E_{\text{C,pk},i}.$$

(41)

Substituting (6), (39) and (40) into (41) yields

$$E_{\text{C,tot}} = \frac{C_0 V_{\text{HI}}^2}{2} A_1 + \frac{V_{\text{HI}} q_{\text{HI}}}{2} A_2 + \frac{q_{\text{HI}}^2}{8C_0} A_3$$

(42)

where

$$A_1 = \sum_{i=1}^{N_{\rm C}} c_i v_i^2 \tag{43}$$

$$A_2 = \sum_{i=1}^{N_{\rm C}} v_i \hat{a}_{{\rm C},i} \tag{44}$$

$$A_3 = \sum_{i=1}^{N_{\rm C}} \frac{\hat{a}_{{\rm C},i}^2}{c_i} \tag{45}$$

This result is similar to that described in [58] where notation  $\alpha$ ,  $\beta$ ,  $\theta$  is used in place of  $A_1$ ,  $A_2$ , and  $A_3$ . Furthermore, the impact of switching frequency on capacitor ripple, and therefore peak storage, is subsumed within  $q_{\rm HI}$ , recalling (2) and (15).

The total volume of the capacitive elements can then be computed as

$$Vol_{C,tot} = \frac{E_{C,tot}}{\rho_{c}}$$

(46)

where  $\rho_{\rm c}$  is the volumetric energy density (J/m³) of the chosen capacitor technology. Alternatively, total mass (kg) may be defined using each components' specific density [1]. Similarly, a cost density metric defining stored Joules per unit cost (J/\$) may be used.

#### B. Peak Inductor Energy Storage

Next, peak inductor energy storage is calculated, accounting for converter operation above resonance (i.e.,  $\Gamma > 1$ ). For simplicity, the inductor is assumed to have a constant inductance with applied current bias and to be saturation limited, as is often the case for low-loss ferrite materials. Consequently, the minimum inductor volume is proportional to the peak energy stored therein.

First, the per-phase resonance equation (19) is rearranged to give

$$L = \frac{1}{\omega_{0,j}^2 \kappa_j C_0} \tag{47}$$

and (15), (16), (18), and (19) are substituted into the peak inductor current in (22)

$$I_{\text{pk},j} = \frac{q_{\text{HI}} a_{\text{L},j} \omega_{0,j}}{2 \sin\left(\omega_{0,j} \frac{t_j}{2}\right)} = \frac{q_{\text{HI}} a_{\text{L},j} \omega_{0,j}}{2 \sin\left(\frac{\pi}{2\Gamma} \cdot \frac{\tau_j}{\tau_j|_{\Gamma=1}}\right)}.$$

(48)

Using (47) and (48), the peak inductor energy over all phases, j, can then be expressed as

$$E_{\text{L,pk}} = \max_{j \in [N_{\text{P}}]} \left\{ \frac{1}{2} L I_{\text{pk},j}^2 \right\} = \frac{q_{\text{H}}^2}{2C_0} B_1 \tag{49}$$

$<sup>^2\</sup>mathrm{Appendix}$  B describes the general form of the modified charge flow quantity  $\hat{a}_{\mathrm{C},i}$  for any ReSC converter with any sequence of capacitor charging/discharging.

where

$$B_{1} = \max_{j \in [N_{P}]} \left\{ \frac{a_{L,j}^{2}}{4\kappa_{j}} \cdot \frac{1}{\sin^{2}\left(\frac{\pi}{2\Gamma} \cdot \frac{\tau_{j}}{\tau_{j}|_{\Gamma-1}}\right)} \right\}.$$

(50)

For converters with  $\tau_j$  independent of  $\Gamma$ ,  $B_1$  is simplified since  $\tau_j = \tau_j|_{\Gamma=1}$ . Furthermore, for all converters operating in resonant ZCS mode (i.e.,  $\Gamma=1$ ), (50) reduces to

$$B_1\big|_{\Gamma=1} = \max_{j \in [N_P]} \left\{ \frac{a_{\mathrm{L},j}^2}{4\kappa_j} \right\} \tag{51}$$

The total inductor volume can then be computed as

$$Vol_{L} = \frac{E_{L,pk}}{\rho_{I}} = \frac{q_{HI}^{2}}{2\rho_{L}C_{0}}B_{1}$$

(52)

where  $\rho_L$  is the volumetric energy density  $(J/m^3)$  of the inductor. Again, specific density (J/kg) or cost density (J/\$) may alternatively be used in mass or cost constrained applications, respectively.

# C. Minimization of Passive Components

Passive components typically comprise the large majority of a converter's volume (or mass). Thus, a converter's volume may be approximately minimized by considering only the volume of the passive components. To do so, an expression for total passive volume—as defined by peak energy storage requirements—is constructed using (46) and (52).

$$\begin{aligned} \text{Vol}_{\text{tot}} &= \text{Vol}_{\text{C}} + \text{Vol}_{\text{L}} \\ &= \left( \frac{C_0 V_{\text{HI}}^2}{2\rho_{\text{c}}} A_1 + \frac{V_{\text{HI}} q_{\text{HI}}}{2\rho_{\text{c}}} A_2 + \frac{q_{\text{HI}}^2}{8\rho_{\text{c}} C_0} A_3 \right) + \frac{q_{\text{HI}}^2}{2\rho_{\text{L}} C_0} B_1. \end{aligned} \tag{53}$$

Total passive volume is then minimized by differentiating with respect to the normalized capacitance  $C_0$

$$\frac{\partial \text{Vol}_{\text{tot}}}{\partial C_0}\bigg|_{C_0 = C_0^*} = 0 = \frac{V_{\text{HI}}^2}{2\rho_{\text{c}}} A_1 - \frac{q_{\text{HI}}^2}{8\rho_{\text{c}} C_0^{*2}} A_3 - \frac{q_{\text{HI}}^2}{2\rho_{\text{L}} C_0^{*2}} B_1 \quad (54)$$

which is solved explicitly for the minimizing normalized capacitance  $C_0^*$  as

$$C_0^* = \frac{q_{\rm HI}}{V_{\rm HI}} \sqrt{\frac{\frac{1}{4}A_3 + \frac{\rho_{\rm C}}{\rho_{\rm L}}B_1}{A_1}}$$

(55)

for a given  $\Gamma$ ,  $V_{\rm HI}$ ,  $q_{\rm HI}$ , and passive energy density ratio  $\rho_{\rm c}/\rho_{\rm L}$ . The composite terms  $A_1$ ,  $A_3$ , and  $B_1$  are all known functions of topology and a given choice of switching frequency (i.e.,  $\Gamma$ ). By then substituting  $C_0^*$  into (47), we obtain the corresponding inductance value,  $L^*$ , that maintains  $f_{\rm sw,0}$  while minimizing passive volume.

Back substituting (55) into (53) and replacing  $q_{\rm HI}$  using (2) yields the minimal achievable total passive component volume,

$$Vol_{tot}^* = \frac{P_{HI}}{f_{sw} \rho_c} \left( \frac{A_2}{2} + \sqrt{A_1 \left( \frac{1}{4} A_3 + \frac{\rho_c}{\rho_L} B_1 \right)} \right).$$

(56)

Furthermore, (56) can be normalized with respect to power throughput, natural resonant switching frequency  $f_{\text{sw},0}$  (as per (15)), and capacitor energy density  $\rho_{\text{c}}$ . The resulting normalized minimum total passive component volume,  $M_{\text{vol}}^*$ ,

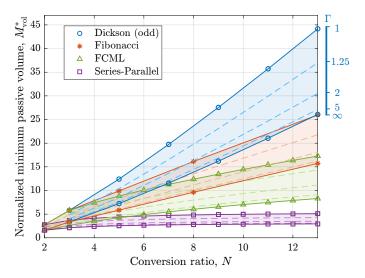

Fig. 7. Normalized minimum total passive volume versus conversion ratio for  $\rho_{\rm C}/\rho_{\rm L}=100$ , and  $1\leq \Gamma<\infty$ . The range of  $\Gamma$  is annotated for the Dickson topology only, but applies similarly for all topologies plotted. For  $\Gamma>5$ , diminishing ripple reductions result in minimal reductions in volume.

may be used to directly compare different topologies and is solely a function of the above-resonance parameter,  $\Gamma$ ; the ratio of passive densities,  $\rho_{\rm C}/\rho_{\rm L}$ ; and invariant topological parameters:

$$M_{\text{vol}}^* = \frac{\text{Vol}_{\text{tot}}^*}{\left(\frac{P_{\text{HI}}}{f_{\text{sw,0}}\,\rho_{\text{C}}}\right)} = \frac{1}{\Gamma} \left(\frac{A_2}{2} + \sqrt{A_1 \left(\frac{1}{4}A_3 + \frac{\rho_{\text{C}}}{\rho_{\text{L}}}B_1\right)}\right). \tag{57}$$

This is a similar normalized passive volume metric as obtained in [12], but now includes terms accounting for above resonance operation. The normalized minimum passive volume is visualized across a range of conversion ratios, N, in Fig. 7 for the Dickson (odd), Fibonnaci, FCML, and series-parallel topologies depicted in Fig. 1. The relative energy density ratio of capacitors to inductors in this plot is chosen as  $\rho_{\rm c}/\rho_{\rm L}=100$ , following the empirical scaling trends analyzed in [1]. As the switching frequency is increased above resonance, the minimum passive volume also decreases due to a reduction in peak voltage and current ripple. However, as  $\Gamma$  is increased further the reduction in minimum passive volume becomes relatively small as ripple becomes negligible relative to dc values.

One additional consideration not captured in the preceding analysis is capacitor-ripple-induced clamping—operation where capacitor voltage ripple imposes a reverse voltage bias on inactive switches. This condition leads to reverse conduction in practice, resulting in unintended converter operation and significant losses. Detailed in [58] for the Dickson topology, here we record similar power limitations for the three remaining topologies in Table III. These limits are obtained by setting the flying capacitor voltage ripple—as related to load via (39) and (2)—equal to the maximum allowable ripple condition, i.e., the point at which unintended reverse conduction begins to occur. As expected, this constraint scales with input voltage, switching frequency, and  $C_0$ . Therefore, it could be beneficial to design with volume sub-optimal  $C_0 > C_0^*$ , so as to extend the load range in lower voltage

TABLE III

MAXIMUM POWER (VOLTAGE RIPPLE CONSTRAINED)

| Topology        | Maximum Power (P <sub>MAX</sub> )                                            |

|-----------------|------------------------------------------------------------------------------|

| Series-Parallel | $V_{\scriptscriptstyle  m HI}^2 C_0 f_{ m sw} \cdot rac{2}{N(N-1)}$         |

| FCML            | $V_{\scriptscriptstyle  m HI}^2 C_0 f_{ m sw} \cdot rac{1}{N}$              |

| Dickson         | $V_{\scriptscriptstyle  m HI}^2 C_0 f_{ m sw} \cdot rac{2(N-1)}{N(N+1)}$    |

| Fibonacci       | $V_{\scriptscriptstyle \rm HI}^2 C_0 f_{\rm sw} \cdot \frac{2}{N F_{N_C+1}}$ |

applications subject to strict switching frequency constraints.

#### V. HARDWARE VALIDATION

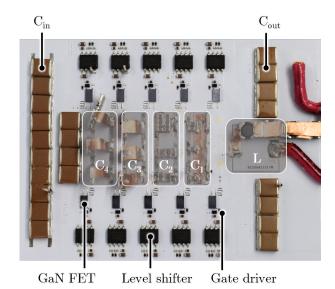

The preceding analysis is applied to the design of a 5:1 (i.e., N=5) FCML converter hardware prototype, whose schematic is depicted in Fig. 1b. The PCB, switches, and gate driving circuitry—depicted in Fig. 8 and listed in Table IV are identical to the hardware demonstration in [21], while the passive components are replaced with values minimizing total passive volume. Switch operation is controlled in accordance with the clocking scheme depicted in Fig. 4. Table V defines this design example's chosen operating point. The target output power of  $P_{\rm HI} = V_{\rm HI} \cdot I_{\rm HI} = 77 \, {\rm W}$  corresponds to the demonstration strated peak efficiency point in [21] when using the same switching devices at the same input voltage of  $V_{\rm HI} = 200 \, \rm V$ . Similarly,  $\Gamma = 1.25$  was selected, having demonstrated a good balance between switching and conduction losses in [21]. To emphasize achievable passive volume reductions, a modestly high switching frequency of  $f_{\rm sw}=250\,{\rm kHz}$  is chosen here, implying  $f_{\rm sw,0} = f_{\rm sw}/\Gamma = 200 \, \rm kHz$ .

We note that the choice of  $\Gamma$ ,  $f_{\rm sw}$  and the selected switch sizings largely dictate converter efficiency. Section VI presents a method to derive both peak blocking voltage,  $V_{\rm ds,max}$ , and rms current,  $I_{\rm rms}$ , for each switch as a function of  $\Gamma$ , which facilitates conventional loss estimation and optimization across frequency, with the effects of lage ripple behavior now fully modeled. However, a detailed loss assessment is beyond the scope of this work, with the following design example focusing on passive component volume only. In practice, the described design flow may be iterated in conjunction with complimentary large ripple enhanced loss calculations, allowing for comprehensive converter optimization that accurately captures the well known trade-off between passive component volume and converter efficiency.

Having specified an operating point in Table V, passive component volume is now calculated in accordance with Section IV. First, the high-side average charge  $q_{\rm HI}=1.54\,\mu{\rm C}$ —as per (2), (6), and the relative phase durations are evaluated as  $\tau_1=0.233$  and  $\tau_2=0.178$  using (35) and (36). Temporarily setting  $\Gamma=1$  gives  $\tau_1|_{\Gamma=1}=0.243$  and  $\tau_2|_{\Gamma=1}=0.172$ . Values for  $\hat{a}_{\rm C}$ , c, v,  $a_{\rm L}$ , and  $\kappa$  are retrieved from Table VIII. Subsequently, the requisite coefficients necessary to compute total

Fig. 8. Annotated photograph of the FCML converter used to validate the passive volume calculations. Constructed on a white soldermask, the hardware presented in [21] is modified to include the passive component cases depicted in Fig. 9.

TABLE IV SWITCHING COMPONENT DETAILS

| Component                  | Description                   | Part Name |

|----------------------------|-------------------------------|-----------|

| $S_{A_{1-5}}, S_{B_{1-5}}$ | 100 V, 3.2 m $\Omega$ GaN-FET | EPC2218   |

| Gate Driver                | 5 V, 7 A / 5 A                | LMG1020   |

| Isolator                   | Power and Signal              | ADUM5240  |

passive volume using (53) are evaluated as  $A_1 = 1.2$ ,  $A_2 = 2$ ,  $A_3 = 4$ , and  $B_1 = 0.537$ . The only remaining unknowns are technology dependent passive energy densities,  $\rho_C$  and  $\rho_L$ , and the choice of  $C_0$ —whose minimizing expression  $C_0^*$  is given in (55).

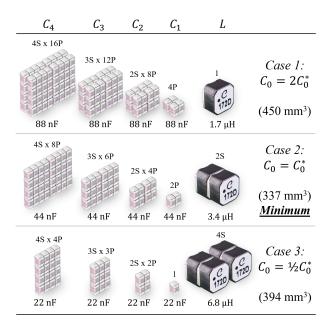

To demonstrate that  $C_0 = C_0^*$  results in minimized total passive component volume, three sets of passive components depicted as Cases 1-3 in Fig. 9-were implemented in hardware. To ensure consistent energy densities  $\rho_c$  and  $\rho_L$  across all instances of the same passive type, regardless of value or applied bias, each passive component is constructed using series and/or parallel combinations of either a small unit capacitor or unit inductor. These unit elements, summarized in Table VI, both have competitive energy densities representative of their respective technologies [1]. A Class I MLCC capacitor (e.g., C0G/NP0) with  $\rho_c = 8800 \,\text{J/m}^3$  is used, given the stability, low loss, and achievable tolerances of these dielectrics in tuned ReSC designs [10]. Likewise, the unit inductance is a low loss stable ferrite with  $\rho_{\rm L} = 123 \, {\rm J/m}^3$ . Using these densities, the prescribed operating parameters, and (55), the normalizing capacitance value minimizing total passive component volume is found to be  $C_0^* = 44 \,\mathrm{nF}$ , with associated inductance  $L^* = 3.4 \,\mu\text{H}$  using (47). Last, having obtained  $C_0^*$ , Table III is consulted to ensure that the target power of 77 W does not exceed the capacitor ripple limitation.

TABLE V

SPECIFIED 5:1 FCML CONVERTER OPERATING POINT

| Description         | Parameter                            | Value             |

|---------------------|--------------------------------------|-------------------|

| High-Side Voltage   | $V_{\scriptscriptstyle m HI}$        | $200\mathrm{V}$   |

| Power Level         | $P_{\scriptscriptstyle \mathrm{HI}}$ | $77\mathrm{W}$    |

| Switching Frequency | $f_{ m sw}$                          | $250\mathrm{kHz}$ |

| Above Resonance     | Γ                                    | 1.25              |

Fig. 9. The total passive component volume for three different 5:1 FCML converter solutions with identical resonant switching frequency.  $P_{\rm HI}=77\,\rm W,$   $\Gamma=1.25,~f_{\rm sw}=250\,\rm kHz,~V_{\rm HI}=200\,\rm V.$  All components are depicted to relative scale. For Case 2,  $C_0=C_0^*=44\,\rm nF,$  resulting in approximately minimal total component volume.

TABLE VI UNIT PASSIVE COMPONENT DETAILS

| Component                   | C                            | $oldsymbol{L}$                    |

|-----------------------------|------------------------------|-----------------------------------|

| Description                 | C0G, 0805                    | Ferrite                           |

| Part Name                   | C2012C0G1H223J125AA          | LPS5030-172                       |

| Ratings                     | $22\mathrm{nF},50\mathrm{V}$ | $1.7\mu\mathrm{H},~3.3\mathrm{A}$ |

| Dimensions (mm)             | $2.00\times1.25\times1.25$   | $5.00\times5.00\times3.00$        |

| Volume (mm <sup>3</sup> )   | 3.13                         | 75.0                              |

| Density (J/m <sup>3</sup> ) | 8800                         | 123                               |

In this case,  $P_{\rm MAX} = 88 \, {\rm W}$  ensuring correct operation with a  $10 \, \%$  margin.

For each of the three cases in Fig. 9, values for both  $C_0$  and L differ, but all cases express an identical natural resonant frequency,  $f_{\rm sw,0}$ , leading to the same switching frequency,  $f_{\rm sw}$ , for a given  $\Gamma$ . Case 1 uses a capacitance  $C_0$  twice as large as the minimizing value (i.e.,  $C_0 > C_0^*$ ), Case 2 uses the optimal design choice (i.e.,  $C_0 = C_0^*$ ), and Case 3 uses a capacitance  $C_0$  half the minimizing value (i.e.,  $C_0 < C_0^*$ ).

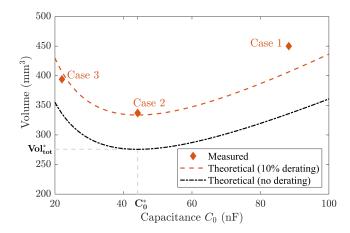

Fig. 10. Total measured passive volume versus  $C_0^{\ast}$  for three constructed cases, along with theoretically derived continuous functions of (53) with and without a 10% passive component derating. The error between measured and theoretical datapoints results from practical component rating availability. Minimizing capacitance  $C_0^{\ast}$  is highlighted, illustrating that even with imperfect component selection, a minimized result is still achieved.

Fig. 10 compares the resulting total passive volumes with the theoretically calculated volume using (53). The theoretical volume assumes all passives are rated at their precise maximum energy storage requirement, with no voltage or current derating, and a continuum of part availability. Conversely, the chosen unit inductor has a practical current derating of 2.9 A (instead of 3.3 A) to avoid saturation and ensure a stable inductance value. Similarly, while the flying capacitors nominally experience dc voltages in multiples of 40 V, a 50 V dielectric is chosen to accommodate each element's voltage ripple. Similar approximations are expected for practical design constraints and, as demonstrated in Fig. 10, lead to a realized passive volume inflated from the theoretical. However, the applied deratings do not significantly alter the optimal value of  $C_0^*$ and  $L^*$ , provided a similar degree of voltage/current margin is applied to both capacitors and inductors. To illustrate this, a 10% derating is applied to each passive's voltage or current, which when squared in (40) and (49) gives a 21 % increase in expected volume. This modified theoretical result is also plotted in Fig. 10, showing closer agreement with volumes measured in practice.

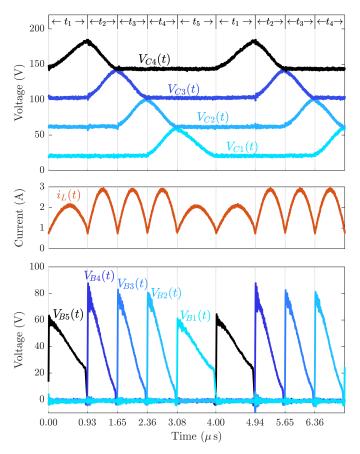

Fig. 11 depicts measured flying capacitor voltage and inductor current waveforms at the described operating point with  $C_0=C_0^*=44\,\mathrm{nF}$  and  $L=L^*=3.4\,\mathrm{\mu H}$ . Taking measured peak inductor current, peak flying capacitors voltages, and applying  $\frac{1}{2}LI_{\mathrm{pk}}^2$  and  $\frac{1}{2}C_0V_{\mathrm{pk}}^2$  reveals total peak inductor and capacitor energies of  $14.3\,\mathrm{\mu J}$  and  $1.4\,\mathrm{mJ}$ , respectively. Dividing by passive energy densities  $\rho_{\mathrm{L}}$  and  $\rho_{\mathrm{C}}$  yields the theoretically expected minimum volume of  $\mathrm{Vol}_{\mathrm{tot}}^*=275\,\mathrm{mm}^3$ , as predicted by (56) and plotted in Fig. 10, further validating the preceding analysis.

# VI. SWITCH STRESS

Section IV and Section V aim to minimize total passive component volume of capacitors and inductors while assuming in practice these elements comprise the large majority of a converter's overall volume. However, this minimization may incur increased voltage and current ripple, which would

Fig. 11. Measured flying capacitor voltage waveforms (top), inductor current (middle), and switch voltages,  $V_{\rm ds}$ , (bottom) for minimized volume Case 2, where  $V_{\rm HI} = 200~{\rm V}$ ,  $P_{\rm HI} = 77~{\rm W}$ ,  $f_{\rm sw} = 250~{\rm kHz}$ , and  $\Gamma = 1.25$ . Switches are controlled in accordance with the clocking scheme depicted in Fig. 4 with phase timing durations calculated using (35) and (36). For each phase the inductor current waveform is a centered symmetric sinusoidal segment, further validating the zero volt-seconds per phase assumption.

subsequently be imposed on the adjacent switching devices. This in turn may lead to increased switch stress, resulting in volume/loss increases within the active devices. One conventional metric characterizing switch stress is the volt-amp (VA) product [2], [12], [22], [74]. This metric assumes linear device scaling and commonly serves as a proxy for total switching device area and/or loss in a given converter when summed across all switching devices. That is, an improved VA rating translates to a smaller and/or more efficient power converter. In this work, we propose a VA metric that takes into account the full effect of the inductor current and capacitor voltage ripples, improving upon calculations presented in past literature by providing a metric with greatly increased fidelity.

#### A. Current Stress

Rather than using average current for the total VA rating, as in [2], [12], here we calculate the rms current through each switch—for both at- and above-resonance operation—using the inductor current waveform derived in Section III. Utilizing rms current is similar to the analysis performed in [20], [37] and captures conduction losses, thermal requirements, and the effects of operating frequency on switch current ripple.

The normalized charge flow,  $a_{s,ji}$ , through the *i*th switching device is obtained using the procedure described in Sec-

tion II-A and the results for four topologies are recorded in Table VIII where switches adhere to the naming convention depicted in Fig. 1. In phase j, the ratio of the peak current through switch  $S_i$  relative to the peak inductor current, as defined in (48), is equivalent to the ratio of respective charge flow, or

$$\frac{I_{\text{pk},S_{i},j}}{I_{\text{pk},j}} = \frac{a_{\text{S},ji}}{a_{\text{L},i}}.$$

(58)

For each switch,  $S_i$ , the total rms current in a switching period is constructed from a squared sum of per-phase rms currents as

$$\begin{split} I_{\text{rms},S_{i}} &= \sqrt{\frac{1}{T_{\text{sw}}}} \int_{0}^{T_{\text{sw}}} i_{S_{i}}^{2}(t) \ dt \\ &= \sqrt{\frac{1}{T_{\text{sw}}}} \sum_{j=1}^{N_{\text{P}}} \int_{-\frac{t_{j}}{2}}^{\frac{t_{j}}{2}} \left( I_{\text{pk},S_{i},j} \cos(\omega_{0,j} t) \right)^{2} \ dt \\ &= \frac{I_{\text{HI}}}{2} \sqrt{\frac{\pi}{\Gamma}} \sum_{j=1}^{N_{\text{P}}} \frac{a_{s,ji}^{2}}{\tau_{j}|_{\Gamma=1}} \cdot \left( \frac{\frac{\pi}{\Gamma} \cdot \frac{\tau_{j}}{\tau_{j}|_{\Gamma=1}} + \sin\left(\frac{\pi}{\Gamma} \cdot \frac{\tau_{j}}{\tau_{j}|_{\Gamma=1}}\right)}{1 - \cos\left(\frac{\pi}{\Gamma} \cdot \frac{\tau_{j}}{\tau_{j}|_{\Gamma=1}}\right)} \right) \end{split}$$

(59)

where (16) and (19) are substituted for  $t_j$  and  $\omega_{0,j}$ , respectively, and  $q_{\rm HI}$  is substituted for the high-side input current,  $I_{\rm HI}$ , using (2). A similar analytical expression for the inductor current rms may be derived as

$$I_{\rm rms,L} = \frac{I_{\rm HI}}{2} \sqrt{\frac{\pi}{\Gamma} \sum_{j=1}^{N_{\rm P}} \frac{a_{\rm L,j}^2}{\tau_j|_{\Gamma=1}} \cdot \left( \frac{\frac{\pi}{\Gamma} \cdot \frac{\tau_j}{\tau_j|_{\Gamma=1}} + \sin\left(\frac{\pi}{\Gamma} \cdot \frac{\tau_j}{\tau_j|_{\Gamma=1}}\right)}{1 - \cos\left(\frac{\pi}{\Gamma} \cdot \frac{\tau_j}{\tau_j|_{\Gamma=1}}\right)} \right)}.$$

(60)

Interestingly, both the switch and inductor rms currents are independent of both  $C_0$  and  $f_{\rm sw}$ , varying only with  $\Gamma$  and  $I_{\rm HI}$ . For all two-phase converters, the normalized phase durations are invariant to  $\Gamma$  (i.e.,  $\tau_j = \tau_j|_{\Gamma=1}$ ) leading to further simplification of (59) and (60). In all cases an increase in  $\Gamma$  results in reduced rms currents, as expected.

The results in (59) and (60) have been validated using the measured inductor current waveforms presented in Fig. 11, where switch current waveforms can be extracted from  $i_{\rm L}(t)$  on a phase-by-phase basis.

#### B. Voltage Stress

Prior work in [2], [12], [20], [37], only calculated switch voltage stresses based on the mid-range capacitor voltages, thereby neglecting the effects of capacitor voltage ripple. In this analysis, the peak voltage indicates switch stress, and more fairly characterizes the performance of switches under the large ripple conditions typical in converters designed for minimized passive volume.

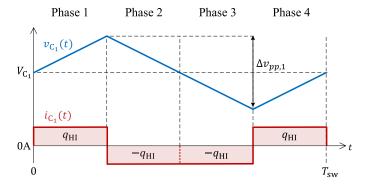

When a switch is disabled, its blocking voltage,  $V_{\mathrm{ds},i}$ , is dictated by proximal flying capacitors. In every phase, large-signal KVL is applied to obtain expressions for the voltage imposed upon each switch, inclusive of flying capacitor voltage ripple. However the phase and time of occurrence for the peak blocking voltage in each switch is not immediately obvious by inspection. For the ReSC topologies presented in

this work, the maximum (or minimum) of  $V_{\rm ds}$  in each phase occurs either at its beginning,  $j_{\rm start}$ , or end,  $j_{\rm end}$ . Therefore the instantaneous blocking voltage immediately before and after each phase transition must be investigated, after which the maximum value is recognized.

Using the 5:1 FCML converter depicted in Fig. 4 as an example, at the start of phase 1 switch  $S_{\rm B5}$  experiences a blocking voltage of

$$V_{\text{ds},B_5}\Big|_{(j=1)_{\text{start}}} = V_{\text{HI}} - \left(V_{\text{HI}}v_4 - \frac{1}{2}\Delta v_{\text{pp},4}\right)$$

(61)

whereas at the end of phase 1 switch  $S_{\rm B5}$  experiences

$$V_{\text{ds},B_5}\Big|_{(j=1)_{\text{end}}} = V_{\text{HI}} - \left(V_{\text{HI}}v_4 + \frac{1}{2}\Delta v_{\text{pp},4}\right)$$

(62)

where  $v_4$  is the normalized mid-range voltage of capacitor  $C_4$  and its voltage ripple  $\Delta v_{\mathrm{pp},i}$  is defined by (39). In this case (61) clearly expresses the peak blocking voltage condition in phase 1. Continuing the analysis for every phase shows (61) is also the maximum switch voltage stress,  $V_{\mathrm{ds,max,B_5}}$ , for switch  $B_5$  over the entire switching period.

This search is expanded to all switches, where phases in which a switch is turned on may be ignored since these switches will have  $0\,\mathrm{V}$  across them. For convenience, Table VII documents the generalized result for peak voltage stress on each switching element for four common topologies. The calculated peak blocking voltage for the FCML topology is validated against the measured  $V_{\mathrm{ds}}$  waveforms depicted in Fig. 11 for switches  $S_{\mathrm{B},1-5}$ .

# C. Total VA Switch Rating

To compute a converter's total VA rating, the rms current of each switch is multiplied by its corresponding peak voltage, before summing across all elements:

$$VA_{tot} = \sum_{i=1}^{N_S} V_{ds, max, i} \cdot I_{rms, i}.$$

(63)

In choosing  $C_0$  to minimize the total passive volume (i.e.  $C_0 = C_0^*$ ), (55) can be substituted into the  $V_{\rm ds,max}$  expressions listed in Table VII. Here it becomes apparent  $V_{\rm HI}$  can be factored out of all  $V_{\rm ds,max}$  expressions. Similarly, the high-side current,  $I_{\rm HI}$ , is a factor of  $I_{\rm rms}$ , as per (59). Subsequently, the VA rating in (63) can be normalized with respect to input power,  $P_{\rm HI} = V_{\rm HI} I_{\rm HI}$ , yielding a metric,  $M_{\rm VA}^*$ , independent of power level or switching frequency

$$M_{\text{VA}}^* = \frac{\text{VA}_{\text{tot}}}{V_{\text{HI}}I_{\text{HI}}} \tag{64}$$

and can be used to directly compare the switch utilization of different ReSC topologies. Trade-offs between this normalized switch stress metric and the normalized minimimum passive volume,  $M_{\text{vol}}^*$  are visualized in Section VII.

# VII. DISCUSSION

The previous sections describe a comprehensive large-signal assessment of ReSC converters when operating in periodic steady-state, either at or above resonance. Section IV derived a normalized minimum total passive volume metric,  $M_{\text{vol}}^*$ ,

TABLE VII Maximum Switch Voltage Stress

| $V_{\mathbf{ds,max},i}$       |                                                |                                                                                     |                                                   |  |  |

|-------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------|--|--|

| Series-Parallel               |                                                |                                                                                     |                                                   |  |  |

| $S_{\mathrm{T}_i}$            | $rac{i}{N}V_{\scriptscriptstyle  m HI}$ $+$   | $\frac{i}{2}\frac{q_{\rm HI}}{C_0}$                                                 | $i \in \{1 \leq \mathbb{N} \leq N_{\mathbf{C}}\}$ |  |  |

| $S_{\mathbf{B}_i}$            | $rac{i}{N}V_{\mathrm{HI}}$ $+$                | $\frac{N\!-\!i}{2}\frac{q_{\rm HI}}{C_0}$                                           | $i \in \{1 \le \mathbb{N} \le N_{\mathbf{C}}\}$   |  |  |

| $S_{\mathbf{M}_i}$            | ${1\over N}V_{\scriptscriptstyle { m HI}}$ $+$ | $\frac{1}{2}\frac{q_{\rm HI}}{C_0}$                                                 | $i \in \{1 \leq \mathbb{N} \leq N_{\mathrm{C}}\}$ |  |  |

| $S_{\mathrm{H}}$              | $rac{N-1}{N}V_{\mathrm{HI}}$ +                | $\frac{1}{2}  \frac{q_{\rm HI}}{C_0}$                                               |                                                   |  |  |

|                               |                                                | FCML                                                                                |                                                   |  |  |

| $S_{\mathbf{A}_i}$            | ${1\over N}V_{\rm HI}$ +                       | $rac{q_{ m HI}}{C_0}$                                                              | $i \in \{2 \leq \mathbb{N} \leq N-1\}$            |  |  |

| $\mathcal{O}_{A_i}$           | ${1\over N}V_{\scriptscriptstyle { m HI}}$ $+$ | $\frac{1}{2}\frac{q_{\rm HI}}{C_0}$                                                 | $i \in \{1, N\}$                                  |  |  |

| $S_{\mathbf{B}_i}$            | ${1\over N}V_{\scriptscriptstyle { m HI}}$ $+$ | $\frac{q_{ m HI}}{C_0}$                                                             | $i \in \{2 \leq \mathbb{N} \leq N-1\}$            |  |  |

| ~в <sub>і</sub>               | ${1\over N}V_{\scriptscriptstyle  m HI}$ $+$   | $\frac{1}{2} \frac{q_{\rm HI}}{C_0}$                                                | $i \in \{1, N\}$                                  |  |  |

|                               |                                                | Dickson                                                                             |                                                   |  |  |

| $S_{\mathbf{B}_i}$            | ${1\over N}V_{\scriptscriptstyle { m HI}}$ +   | $\frac{1}{2} \frac{q_{\rm HI}}{C_0}$                                                | $i \in \{1 \leq \mathbb{N} \leq 4\}$              |  |  |

| $S_{\mathbf{S}_i}$            | ${2\over N}V_{\scriptscriptstyle { m HI}}$ $+$ | $\tfrac{1}{N-1} \tfrac{q_{\rm HI}}{C_0}$                                            | $i \in \{2 \leq \mathbb{N} \leq N-1\}$            |  |  |

|                               | ${1\over N}V_{\scriptscriptstyle { m HI}}$ +   | $\frac{1}{2}\frac{q_{\rm HI}}{C_0}$                                                 | $i \in \{1, N\}$                                  |  |  |

| Fibonacci                     |                                                |                                                                                     |                                                   |  |  |

| $S_{\mathrm{T}_i}$            | $rac{F_{(i+1)}}{N}V_{\mathrm{HI}}$ +          | $\frac{F_{(N_{\text{\tiny C}}-i+1)}}{2}\frac{q_{\text{\tiny HI}}}{C_0}$             | $i \in \{1 \le \mathbb{N} \le N_{\mathbf{C}}\}$   |  |  |

| $\overline{S_{\mathrm{B}_i}}$ | $rac{F_i}{N}V_{\scriptscriptstyle  m HI}$ $+$ | $\frac{F_{(N_{\rm C}-i+2)}}{2}\frac{q_{\rm HI}}{C_0}$                               | $i \in \{1 \le \mathbb{N} \le N_{\mathbf{C}}\}$   |  |  |

| $\overline{S_{\mathbf{M}_i}}$ | $rac{F_{(i+1)}}{N}V_{\mathrm{HI}}$ $+$        | $\frac{F_{(N_{\hbox{\scriptsize C}}-i+1)}}{2}\frac{q_{\hbox{\scriptsize HI}}}{C_0}$ | $i \in \{1 \leq \mathbb{N} \leq N_{\mathrm{C}}\}$ |  |  |

| $S_{\mathrm{H}}$              | $rac{F_{N_{ m C}}}{N}V_{ m HI}$ +             | $\frac{F_1}{2} \frac{q_{\rm HI}}{C_0}$                                              |                                                   |  |  |

| -                             |                                                |                                                                                     |                                                   |  |  |

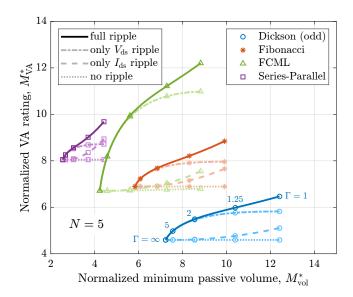

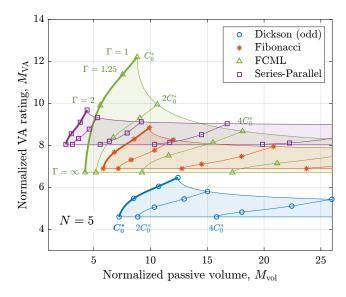

in (57), while Section VI derived a normalized total switch stress,  $M_{\rm VA}^*$ , in (64). These normalized metrics at the minimum volume are evaluated in Fig. 12 for an example N=5 conversion ratio and  $\rho_{\rm C}/\rho_{\rm L}=100$ —a conservative representation of the peak capabilities of Class I ceramic capacitors (e.g., C0G) and ferrite inductors. Here each topology can be compared across the full range of possible switching frequencies, from resonant to above resonant operation  $(1 \le \Gamma < \infty)$ . For a decided  $\Gamma$ , converters with smaller  $M_{\rm vol}^*$  and  $M_{\rm VA}^*$  are expected to offer improved performance, with both a reduced minimum passive volume and VA rating.

In Fig. 12, each topology is visibly differentiated when considering its  $M_{\rm vol}^*$  versus  $M_{\rm VA}^*$ , indicating a quantitative measure of design trade-offs. For example, the Dickson topology exhibits the lowest  $M_{\rm VA}^*$ , suggesting improved efficiency when total switch volume/area is constrained. Viewed differently, for the same conversion efficiency across all four topologies, the Dickson converter's switches are expected to realize a smaller total footprint area/volume. Conversely, the Dickson requires a greater total passive volume than the other topologies when operated at the same power level. The series-parallel topology exists on the opposite extreme: trading worsened total switch stress for superior total passive volume.

Fig. 12. Normalized switch VA rating versus normalized minimum total passive volume, using  $\rho_{\rm C}/\rho_{\rm L}=100.$  Each curve describes a sweep of  $1\leq\Gamma<\infty$  where the rightmost point on each curve is  $\Gamma=1.$  Also plotted is the result when inductor current ripple and/or capacitor voltage ripple are neglected from the switch stress calculations (dashed), as per conventional analysis using small ripple approximations.

The FCML and Fibonacci converters lie between these two extremes. For all converters, both VA rating and passive volume decrease with increasing  $\Gamma$ , due to reduced inductor current and capacitor voltage ripple. However, while the VA rating provides a correlative proxy for the relative switching losses between a set of converter topologies at a given switching frequency, it does not include a frequency dependent term and thus increasing  $\Gamma$  does not directly translate to both a smaller and more efficient converter design. Instead, the VA rating in Fig. 12 should be viewed as informing the relative loss dissipation between topologies at a specified switching frequency, where total loss estimates are calculated separately. The choice of a specific switching frequency is dictated by conventional loss calculations (e.g., [13], [22]), which can now be augmented with the rms of complete current waveforms and ripple enhanced blocking voltages, as derived in Section VI.

To further emphasize the improved fidelity of the presented analysis, Fig. 12 also depicts the resulting curves if either capacitor voltage ripple, inductor current ripple, or both are neglected in the calculation of  $M_{VA}^*$ . In the "no ripple" case, the switch voltage is calculated using the mid-range capacitor voltages only, neglecting capacitor and therefore switch voltage ripple. Likewise, the switch rms current is calculated assuming a constant current through the inductor, equal to the low-side current. The "only  $V_{\rm ds}$  ripple" case calculates switch voltage including the peak voltage across the switches, while the "only  $I_{ds}$  ripple" case calculates the rms of the switch current including the sinusoidal ripple on the inductor current. The "full ripple" case includes the effects of capacitor voltage and inductor current ripples on both the switch voltage and rms current, giving the highest accuracy. The inclusion of voltage ripple in the switch stress calculation is significant, with the FCML converter seeing almost double the switch stress when at resonance (i.e.,  $\Gamma = 1$ ) compared to the calculated result when large-signal ripple is neglected. This reveals fully