# UCLA UCLA Electronic Theses and Dissertations

# Title

Temperature-Insensitive CMOS Quantum Controller With >99% Fidelity for Universal Single-Qubit Gates

Permalink https://escholarship.org/uc/item/8pk450hs

Author Wang, Yen-Hsiang

**Publication Date**

2023

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Temperature-Insensitive CMOS Quantum Controller

With >99% Fidelity for Universal Single-Qubit Gates

A dissertation submitted in partial satisfaction of the

requirements for the degree Doctor of Philosophy

in Electrical Engineering

by

Yen-Hsiang Wang

2023

© Copyright by

Yen-Hsiang Wang

2023

#### ABSTRACT OF THE DISSERTATION

Temperature-Insensitive CMOS Quantum Controller With >99% Fidelity for Universal Single-Qubit Gates

by

Yen-Hsiang Wang Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2023 Professor Mau-Chung Frank Chang, Chair

Fault-tolerant quantum computing is built upon high-fidelity universal quantum gates enabled by scalable quantum processors. However, the scalability of microwave-based quantum processors is hindered by large layout pitch size of 1mm due to high-Q resonant circuits and for crosstalk reduction. We therefore choose to work on the more scalable dc-pulse-based quantum processor utilizing the position-based double-quantum-dot charge qubit with a 200nm pitch.

To alleviate prior difficulty encountered in transmitting fast-edged waveforms generated by arbitrary waveform generators via meter-long cables, we propose a scalable architecture to partition the quantum controller and house only its low-power output stage with the qubit chip within low-parasitic packaging. To enable high-fidelity universal single-qubit gates, we derive requirements for the precision of control waveforms, propose temperature-insensitive design methodologies without device models at cryogenic temperatures, and develop an inductor-less, precise, and fully integrated dc-pulse-based quantum controller achieving 4.3ps maximum error in pulse width and highly linear pulse height control. A closed-loop, automated, multi-variable calibration using an on-chip 2ps/step pulse-swallowing cyclic TDC is devised to ensure temperature-insensitive performances.

Our quantum controller prototype is fabricated in 28nm bulk CMOS and verified through measurements down to 77K. Comparing the performance with state-of-art dc-pulse-based quantum controllers, our work has reduced the shortest duration of a pulse by over 3X, improved the linear resolution of width tuning by over 40X, reduced the width uncertainty by three orders of magnitude, realized an on-chip high-precision pulse width calibration, and largely improved the precision of height tuning to enable high-fidelity universal single-qubit gates.

The dissertation of Yen-Hsiang Wang is approved.

Kang Lung Wang

Yuanxun Wang

Wentai Liu

Mau-Chung Frank Chang, Committee Chair

University of California, Los Angeles

2023

To my family

# **TABLE OF CONTENTS**

| Chapter | 1 Intr | roduction to quantum computing                                               | 1      |

|---------|--------|------------------------------------------------------------------------------|--------|

| 1.1.    | Sign   | nificance of quantum computing                                               | 1      |

| 1.2.    | Cor    | nerstones for quantum computing                                              | 2      |

| 1.2     | .1.    | Scalability                                                                  | 2      |

| 1.2.    | .2.    | Universality                                                                 | 3      |

| 1.2.    | .3.    | Fidelity                                                                     | 6      |

| 1.3.    | Coo    | ling power constraints                                                       | 7      |

| Chapter | 2 Sca  | lable quantum processors                                                     | 9      |

| 2.1.    | Mic    | rowave-based versus dc-pulse-based quantum processors                        | 9      |

| 2.2.    | Pos    | ition-based DQD charge qubit                                                 | 12     |

| 2.2.    | .1.    | Universal single-qubit quantum gates                                         | 12     |

| 2.2.    | .2.    | Requirements on control waveforms for high fidelity                          | 17     |

| 2.2.    | .3.    | Fidelity bottleneck in physics experiments                                   | 20     |

| 2.3.    | Prop   | posed architecture for a scalable quantum processor                          | 20     |

| Chapter | 3 Te   | emperature-insensitive quantum controller for high-fidelity universal single | -qubit |

| gates   |        |                                                                              | 22     |

| 3.1.    | Ten    | nperature-insensitive design methodology                                     | 22     |

| 3.2.    | Qua    | antum controller design with temperature-insensitive performance             | 29     |

| 3.2.    | .1.    | Limitation of state-of-art dc-pulse-based controllers                        | 29     |

| 3.2.    | .2.    | Proposed architecture for the quantum controller                             | 31     |

| 3.2.    | .3.    | Temperature-insensitive width controller                                     | 33     |

| 3.2.4.        | Temperature-insensitive height controller                                         |

|---------------|-----------------------------------------------------------------------------------|

| 3.2.5.        | Core logic and SPI45                                                              |

| Chapter 4 Liq | uid nitrogen dip testing47                                                        |

| 4.1. Cry      | ogenic testing setup47                                                            |

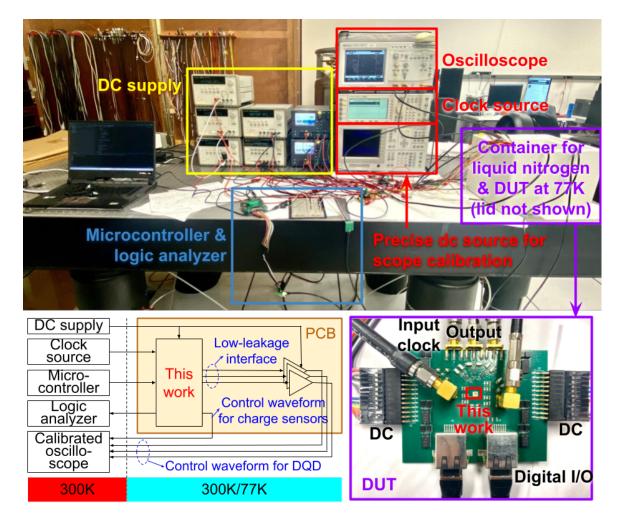

| 4.1.1.        | Mixed-signal automated testing47                                                  |

| 4.1.2.        | Testing with thermal shock                                                        |

| 4.1.3.        | Suitable on-board components and PCB material                                     |

| 4.1.4.        | On-board output buffer                                                            |

| 4.1.5.        | Final testing board                                                               |

| 4.2. Tem      | perature-insensitive performance for high-fidelity universal single-qubit gates60 |

| 4.2.1.        | Successive approximating algorithm for pulse width calibration60                  |

| 4.2.2.        | Temperature-insensitive maximum error in pulse width                              |

| 4.2.3.        | Matching of MOM capacitors                                                        |

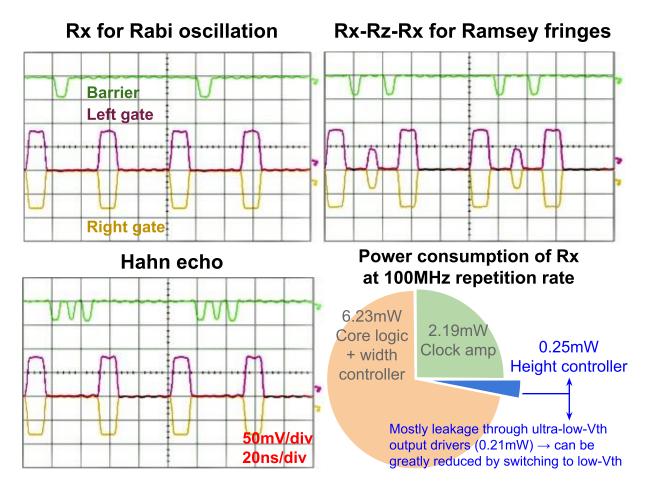

| 4.2.4.        | Waveforms for universal single-qubit gates and power consumption70                |

| Chapter 5 Cor | nclusion and Future Work72                                                        |

| Chapter 6 Bib | liography75                                                                       |

# LIST OF FIGURES

| Figure 1-1: (a) 1mm-pitch superconducting qubits with resonant circuits (Kandala, et al. 2017). (b) |

|-----------------------------------------------------------------------------------------------------|

| 200nm-pitch position-based DQD charge qubits (Yang, et al. 2016)                                    |

| Figure 1-2: Representation of a qubit's state on the Bloch sphere                                   |

| Figure 1-3: An example of universal quantum gate set                                                |

| Figure 1-4: Surface-code-compatible qubit placement in the 54-qubit "Sycamore" quantum              |

| processor from Google (Arute, et al. 2019)7                                                         |

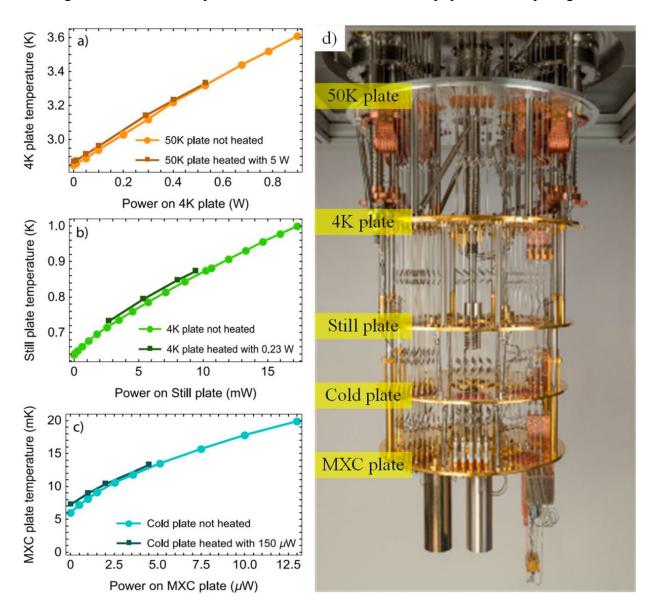

| Figure 1-5: Cooling power of a commercial dilution refrigerator in various chambers (Bonen 2020).   |

|                                                                                                     |

| Figure 2-1: (a) Placement of superconducting qubits compatible with heavy hexagonal surface         |

| code (Chakraborty, et al. 2022). (b) A 2-channel non-multiplexed quantum controller in 14nm         |

| FinFET for superconducting qubits (Chakraborty, et al. 2022)10                                      |

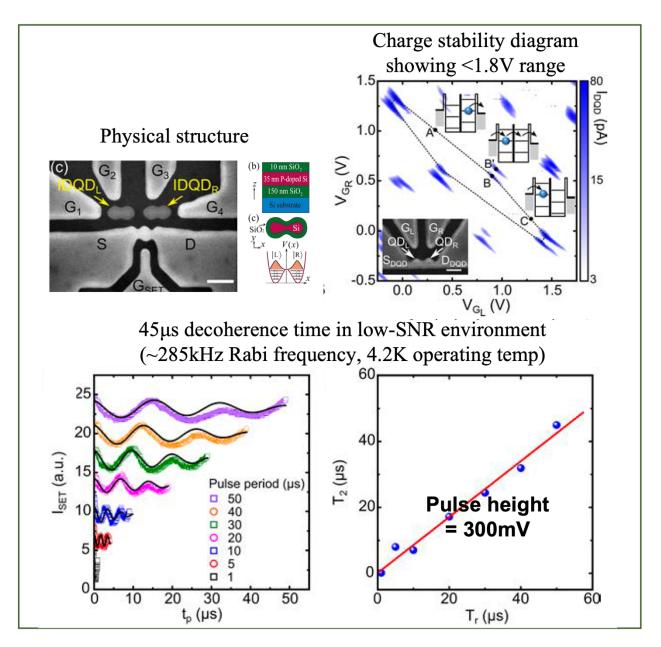

| Figure 2-2: Hard-wall-confined position-based DQD charge qubit (Yang, et al. 2016) (Gorman,         |

| Hasko and Williams 2005)11                                                                          |

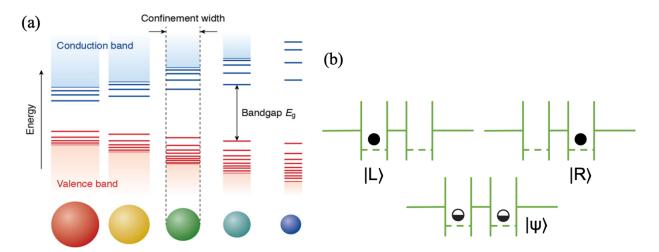

| Figure 2-3: (a) Discretized energy states of QD (Rabouw and Donega 2017). (b) Illustration of       |

| quantum states of a position-based DQD charge qubit                                                 |

| Figure 2-4: (a) Energy diagram with (blue) and without (red) interdot coupling. (b) Eigenstates on  |

| the Bloch sphere with (blue) and without (red) interdot coupling14                                  |

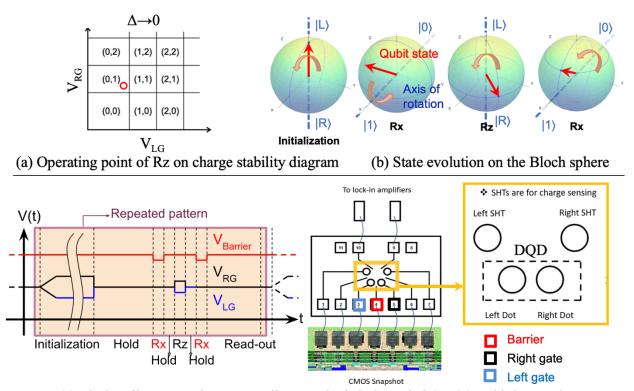

| Figure 2-5: Principle and implementation of the X rotation, or Rabi oscillation15                   |

| Figure 2-6: Principle and implementation of the Z rotation, or Ramsey fringes16                     |

| Figure 2-7: Precision requirements on control waveforms versus qubit operating temperature19        |

| Figure 2-8: Proposed architecture of a scalable quantum processor                                   |

| Figure 3-1: Speed-up of digital gates at cryogenic temperatures (Van Dijk, et al. 2020)23           |

|-----------------------------------------------------------------------------------------------------|

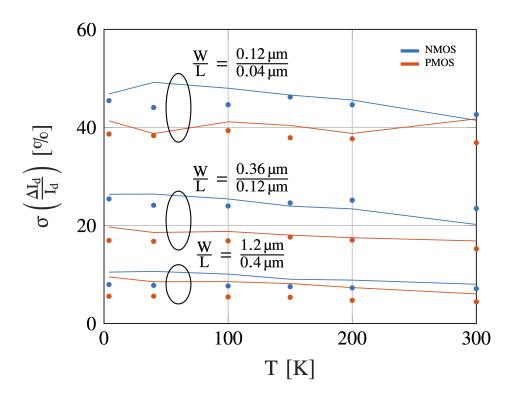

| Figure 3-2: Worsened matching in drain current as temperature drops (biased at a fixed $g_m/I_D$ of |

| 10V <sup>-1</sup> in saturation) ('t Hart, et al. 2018)                                             |

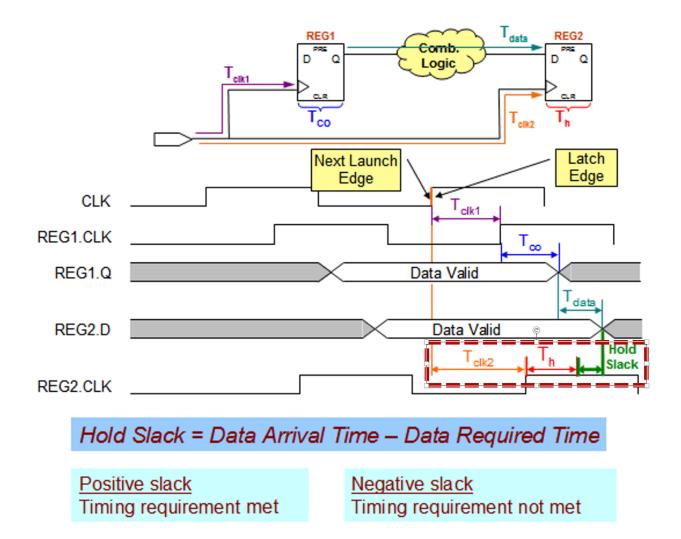

| Figure 3-3: Illustration of hold time requirement (Zhang 2016)26                                    |

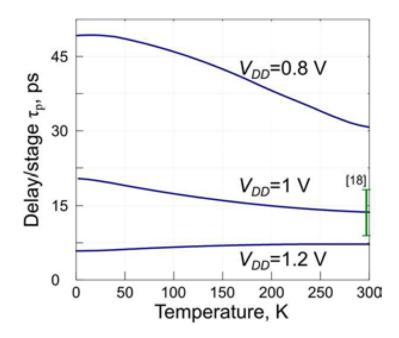

| Figure 3-4: Delay per stage of a 101-stage ring oscillator in 28nm bulk CMOS versus temperature     |

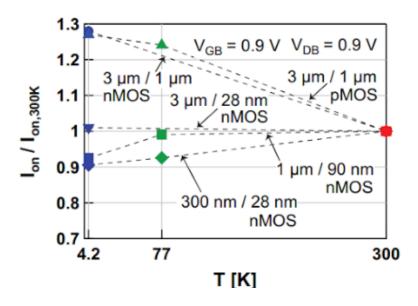

| (Ismail-zade, et al. 2020)27                                                                        |

| Figure 3-5: "On" current versus temperature in 28nm bulk CMOS (Beckers, et al. 2017)                |

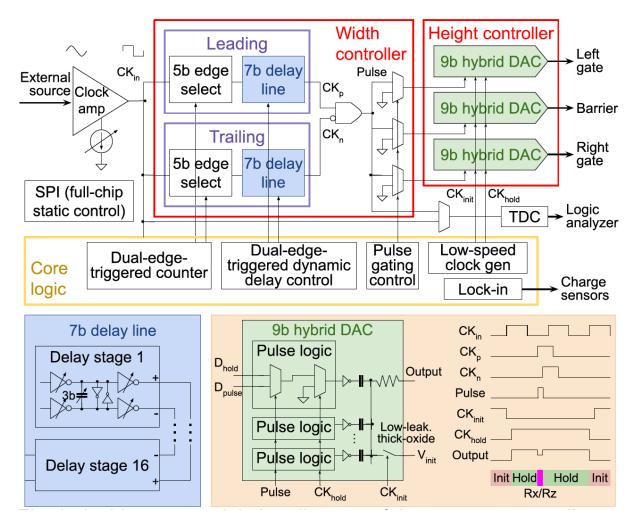

| Figure 3-6: Architecture and timing diagram of proposed quantum controller                          |

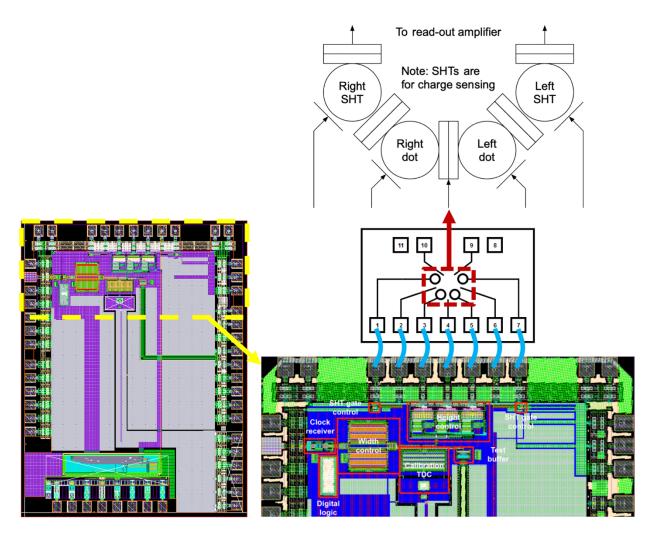

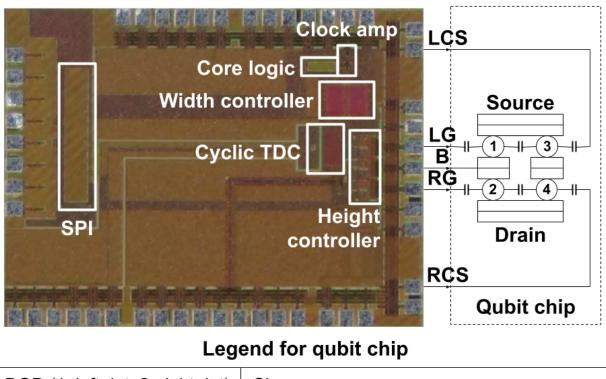

| Figure 3-7: Chip layout and intended integration with the qubit                                     |

| Figure 3-8: Two-step architecture for width control                                                 |

| Figure 3-9: Schematic of the programmable clock amplifier                                           |

| Figure 3-10: Schematic of inverter-C delay stage in the 7-bit delay line                            |

| Figure 3-11: Major contributors to the nonlinearity of width control                                |

| Figure 3-12: Post-layout simulated INL profile of the 7-bit delay line                              |

| Figure 3-13: Layout of the 7-bit delay line for good linearity                                      |

| Figure 3-14: Principle of pulse-swallowing cyclic TDC (Chen, Lin and Hwang 2014)40                  |

| Figure 3-15: Schematic of our pulse-swallowing cyclic TDC40                                         |

| Figure 3-16: Cyclic and matched layout of the TDC for good linearity                                |

| Figure 3-17: Proposed calibration flow for optimal precision in width control41                     |

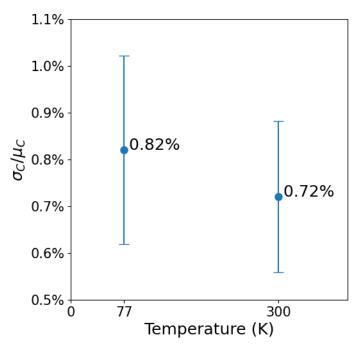

| Figure 3-18: Conceptual diagram of the height controller44                                          |

| Figure 3-19: Linearity of the segmented CDAC (5 thermometer-coded MSBs + 4 binary-coded             |

| LSBs) with 0.7% $\sigma C \mu C$ of the 2fF unit capacitor                                          |

| Figure 3-20: Layout and conceptual diagram (Matthias 2022) of custom-made MOM capacitor           |

|---------------------------------------------------------------------------------------------------|

| using metal 2 to metal 545                                                                        |

| Figure 4-1: Mixed-signal automated setup for liquid nitrogen dip testing49                        |

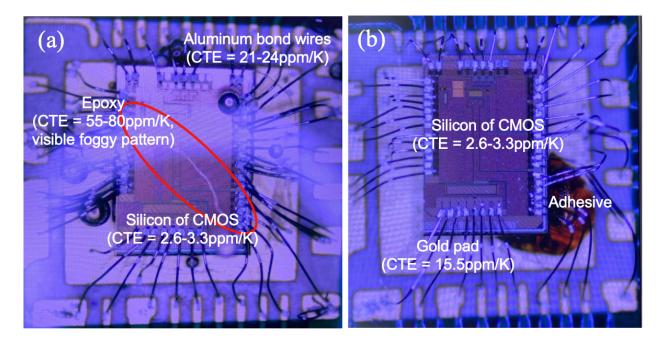

| Figure 4-2: Chip-board assembly: (a) Cracked chip due to large CTE mismatches between CMOS        |

| chip and epoxy. (b) Final working design with low CTE mismatches                                  |

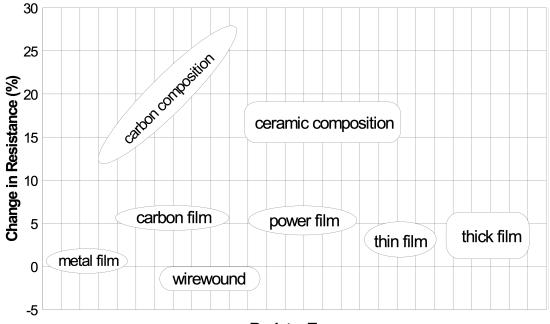

| Figure 4-3: Change in resistance of various resistor types from 298K to 83K (Patterson, Hammoud   |

| and Gerber 2001)                                                                                  |

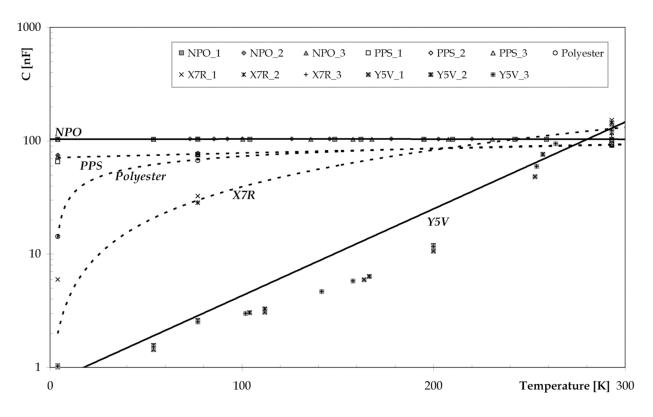

| Figure 4-4: Capacitance of various capacitor types versus temperature from 300K to 4K             |

| (Teyssandier and Prêle 2010)53                                                                    |

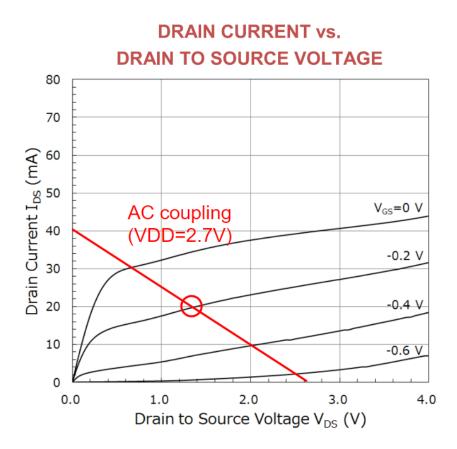

| Figure 4-5: Desired operating point of pHEMT and the load line of the $68\Omega$ load55           |

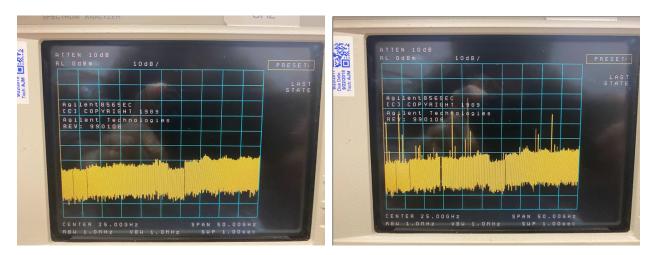

| Figure 4-6: Spectrum at the output of the buffer before (left) and after (right) powering up55    |

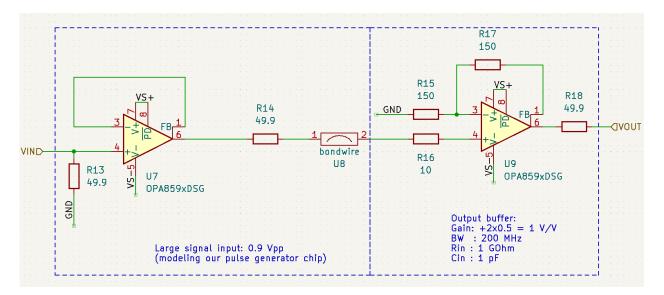

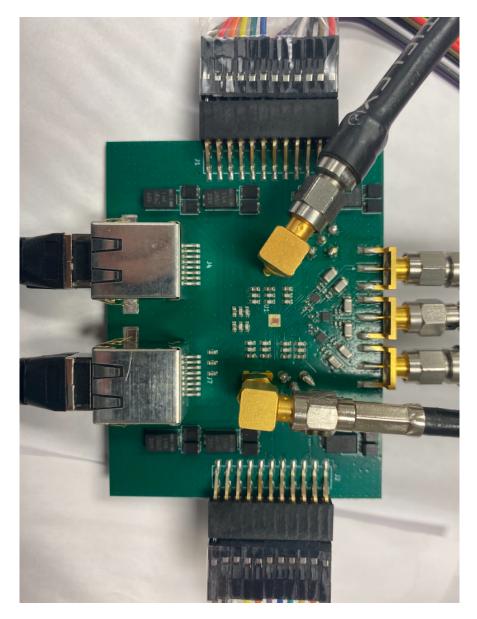

| Figure 4-7: Op-amp-only testing board57                                                           |

| Figure 4-8: Schematic of a signal path on the op-amp board mimicking the final testing board57    |

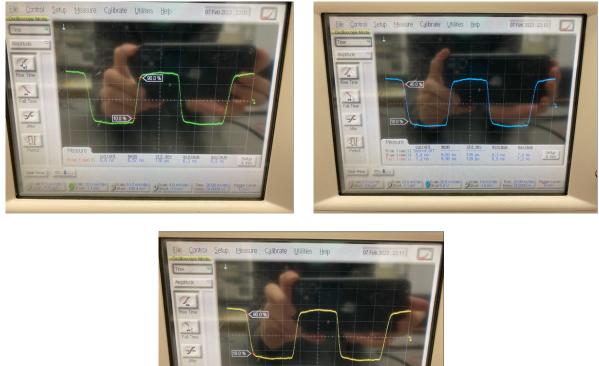

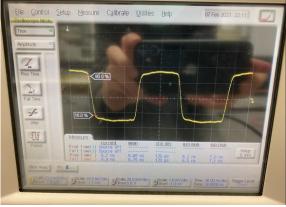

| Figure 4-9: Clear output waveforms from all three paths measured at 77K                           |

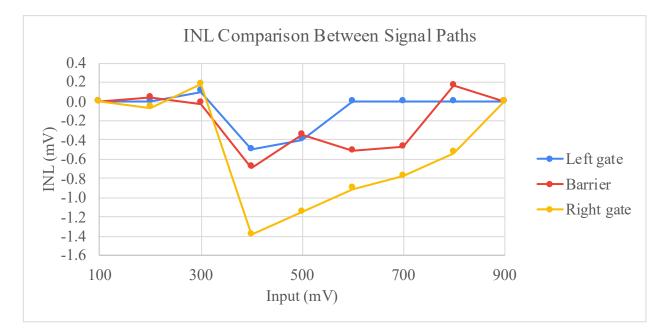

| Figure 4-10: Sanity check on linearity of all three paths                                         |

| Figure 4-11: Final testing board with op-amp-based output buffer                                  |

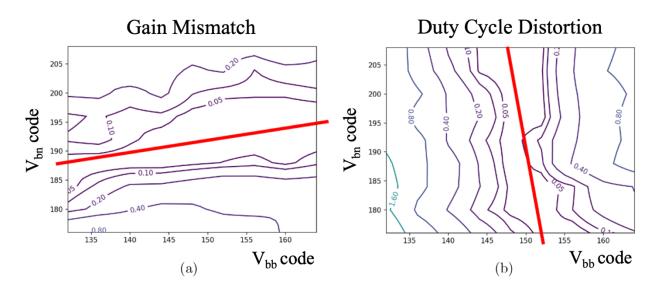

| Figure 4-12: Dependency of (a) gain mismatch and (b) duty cycle distortion on the two calibration |

| variables on X and Y axis. Red lines indicate the best combination                                |

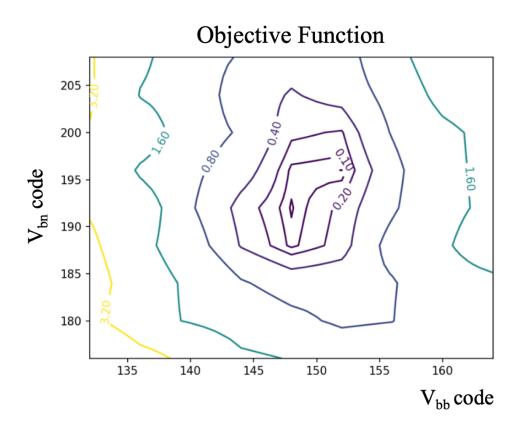

| Figure 4-13: Plot of the objective function near the global optimum. Rugged contours indicate the |

| non-convexity of this objective                                                                   |

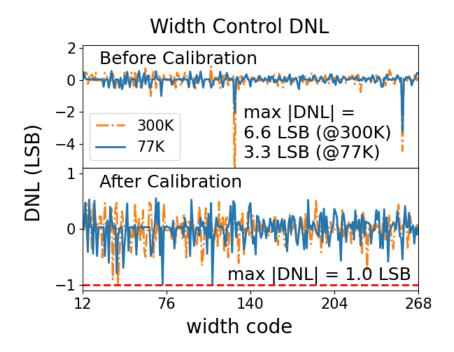

| Figure 4-14: DNL profile of width control at 300K and 77K63                                       |

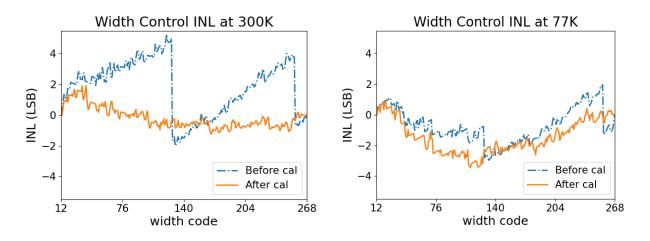

| Figure 4-15: INL profile of width control at 300K and 77K63                                       |

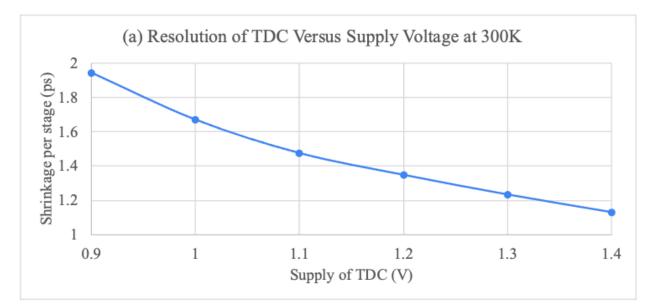

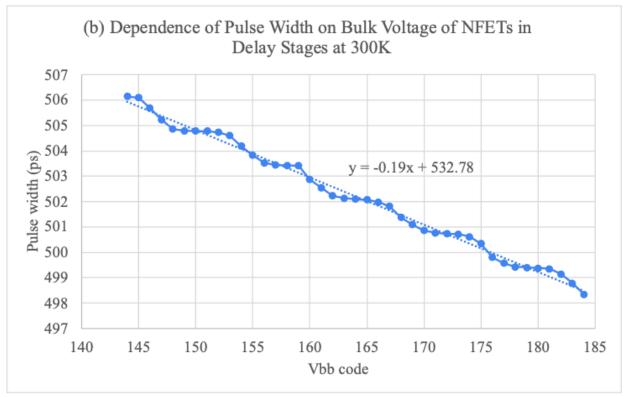

| Figure 4-16: (a) Resolution of TDC versus its supply at 300K. (b) Pulse width versus bulk voltage |

|---------------------------------------------------------------------------------------------------|

| of NFETs in delay stages at 300K65                                                                |

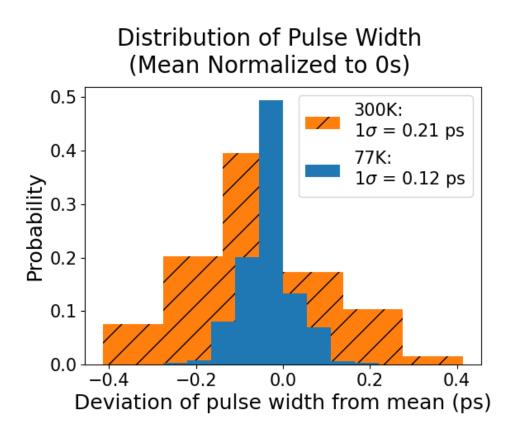

| Figure 4-17: Worst-case uncertainty in pulse width at 300K and 77K after linearity calibration.66 |

| Figure 4-18: INL of the output buffer plus the oscilloscope                                       |

| Figure 4-19: Matching property of the 2fF unit MOM capacitor versus temperature                   |

| Figure 4-20: Measured waveforms for universal single-qubit gates with lock-in capability and at-  |

| speed power breakdown at 77K71                                                                    |

| Figure 5-1: Chip micrograph and intended integration with the qubit chip73                        |

# LIST OF TABLES

| Table 1-1: Analysis of computational advantage of quantum computers (IBM Corporation 2018)  | 5). |

|---------------------------------------------------------------------------------------------|-----|

|                                                                                             | .2  |

| Table 3-1: Comparison of transistor characteristics at 300K and 4K (Van Dijk, et al. 2020)2 | 23  |

| Table 4-1: CTE of adhesives.   5                                                            | ;1  |

| Table 4-2: Temperature-insensitive performance in width precision for high fidelity.        | 56  |

| Table 5-1: Comparison with state-of-art inductor-less dc-pulse-based quantum controllers7   | 74  |

#### ACKNOWLEDGMENTS

During my graduate studies at UCLA, I received extensive support, help, and guidance from amazing people around me. This dissertation would not materialize without them.

Firstly, I would like to express my utmost gratitude to my advisor, Professor Mau-Chung Frank Chang, for his unwavering support and guidance. He led me through countless obstacles, and always encouraged me during my darkest hours. He is also an inspiring scholar who I look up to. I would also like to thank Professor Pei-Wen Li and her group from National Yang Ming Chiao Tung University for many detailed discussions on the quantum physics of the double-quantum-dot charge qubit and cryogenic testing. I am very grateful for the effective technology support from TSMC. My sincere gratitude also goes to all my doctoral committee members including Professor Kang Lung Wang, Professor Yuanxun Wang, Professor Wentai Liu, Professor Sudhakar Pamarti, Professor Chih-Kong Ken Yang, and Professor Miloš D. Ercegovac for their valuable advice and feedback.

The current members and alumni of the High-Speed Electronics Lab (HSEL) have contributed immensely to my research. I would like to give special thanks to Jhih-Wei Chen and Andy Zhong for their significant contribution to our research in quantum computing. I also want to express my gratitude to Dr. Adrian Tang, Professor Yanghyo Kim, Dr. Yan Zhang, Dr. Richard Al Hadi, Dr. Yan Zhao, Dr. I-Ning Ku, Professor Yen-Cheng Kuan, Dr. Ning-Yi Wang, Professor Jenny Yi-Chun Liu, Dr. Zuow-Zun Chen, Jia Zhou, Dr. Rulin Huang, Christopher Chen, Zong-Ru Lee, Dr. Weikang Qiao and Runzhou Chen for helping me tremendously during my graduate studies. I would like to thank our wonderful administrative assistants, Janet Lin and Juliet Pooler, for their timely and effective support on purchases and petitions. My gratitude also goes to staff members of the Graduate Student Affairs Office of our department led by Deeona Columbia for their support and guidance, and the team at the Center for High Frequency Electronics (CHFE) led by Minji Zhu for assembling our testing prototype and sharing insights on testing.

I would like to express my special appreciation to my mentors at Broadcom, Dr. Dongsoo Koh and Dr. James Y.C. Chang, for their support and guidance. I would also like to thank Dr. Young-Kai Chen for his great mentoring during my internship at Bell Labs.

Lastly, I would like to express my deepest gratitude towards my family: my parents, Te-Hui Wang and Li-Mei Wang, my wife, Hsiang-Yi, and my lovely daughter, Stella. I cannot be where I am without their endless love and companionship.

#### VITA

| 2008         | B.S., Electrical Engineering, National Taiwan University, Taiwan        |

|--------------|-------------------------------------------------------------------------|

| 2011         | M.S., Electrical Engineering, University of California, Los Angeles, CA |

| 2013-2016    | Technologies Incubation Scholarship, Ministry of Education, Taiwan      |

| 2014-2016    | High-Speed I/O Design Intern, Bell Labs, New Providence, NJ             |

| 2016-present | Mixed-signal IC Design Engineer, Broadcom Inc., Irvine, CA              |

#### **SELECTED PUBLICATIONS**

Wang, Y. H., Chen, J. W., ... & Chang, M. C. F. A scalable CMOS quantum state controller with >99% fidelity for universal single-qubit gates. Submitted to journal for publication.

Chiang, H. L., ..., Wang, Y. H., ... & Radu, I. P. (2023, June). How Fault-Tolerant Quantum Computing Benefits from Cryo-CMOS Technology. In 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) (pp. 1-2). IEEE.

Liu, C. C., Wang, Y. H., ... & Chang, M. C. F. (2016, June). A 2.2 GHz SRAM with high temperature variation immunity for deep learning application under 28nm. In Proceedings of the 53rd Annual Design Automation Conference (pp. 1-6).

Chen, Z. Z., Wang, Y. H., ... & Chang, M. C. F. (2015, February). 14.9 sub-sampling all-digital fractional-N frequency synthesizer with–111dBc/Hz in-band phase noise and an FOM of–242dB. In 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers (pp. 1-3). IEEE.

Tang, A., ..., Wang, Y. H., ... & Chang, M. C. F. (2012). A D-Band CMOS Transmitter With IF-Envelope Feed-Forward Pre-Distortion and Injection-Locked Frequency-Tripling Synthesizer. IEEE transactions on microwave theory and techniques, 60(12), 4129-4137.

Tang, A., ..., Wang, Y. H., ... & Chang, M. C. F. (2012, June). A CMOS 135–150 GHz 0.4 dBm

EIRP transmitter with 5.1 dB P1dB extension using IF envelope feed-forward gain compensation.

In 2012 IEEE/MTT-S International Microwave Symposium Digest (pp. 1-3). IEEE.

Tang, A., Virbila, G., Wang, Y. H., ... & Chang, M. C. F. (2012, June). A 200 GHz 16-pixel focal plane array imager using CMOS super regenerative receivers with quench synchronization. In 2012 IEEE/MTT-S International Microwave Symposium Digest (pp. 1-3). IEEE.

Tang, A., ..., Wang, Y. H., ... & Chang, M. C. F. (2012, February). A low-overhead self-healing embedded system for ensuring high yield and long-term sustainability of 60GHz 4Gb/s radio-ona-chip. In 2012 IEEE International Solid-State Circuits Conference (pp. 316-318). IEEE.

Tang, A., ..., Wang, Y. H., ... & Chang, M. C. F. (2012, February). A 144GHz 0.76 cm-resolution sub-carrier SAR phase radar for 3D imaging in 65nm CMOS. In 2012 IEEE International Solid-State Circuits Conference (pp. 264-266). IEEE.

Tang, A., ..., Wang, Y. H., ... & Chang, M. C. (2012). A Formula Not Shown-Band CMOS Transmitter With IF-Envelope Feed-Forward Pre-Distortion and Injection-Locked Frequency-Tripling Synthesizer. IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES MTT, 60(12), 4129-4137.

Ku, I. N., ..., Wang, Y. H., & Chang, M. C. F. (2011, September). A 40-mW 7-bit 2.2-GS/s timeinterleaved subranging ADC for low-power gigabit wireless communications in 65-nm CMOS. In 2011 IEEE Custom Integrated Circuits Conference (CICC) (pp. 1-4). IEEE.

# **Chapter 1** Introduction to quantum computing

# 1.1. Significance of quantum computing

Quantum computing can accelerate revolutionary breakthrough by solving complex problems intractable to classical counterparts. Key fundamental properties that distinguish quantum computers include the superposition of basis states and the entanglement between quantum bits (qubits). Unlike a classical bit which is either 0 or 1 at a given time, the state of a qubit,  $|\psi\rangle$ , is a superposition of the two computational basis states, e.g.,  $|0\rangle$  and  $|1\rangle$ . Mathematically it can be expressed as

$$|\psi\rangle = c_0|0\rangle + c_1|1\rangle$$

where  $c_0$  and  $c_1$  represent complex probability amplitudes, and  $c_0^2 + c_1^2 = 1$ . Entanglement between qubits further expands the information density of a quantum computer. A two-qubit system stores the superposition of  $2^2$  states at any given time, and can be written as

$$|\psi\rangle = c_{00}|00\rangle + c_{01}|01\rangle + c_{10}|10\rangle + c_{11}|11\rangle$$

where  $c_{00}^2 + c_{01}^2 + c_{10}^2 + c_{11}^2 = 1$ . In contrast, a two-bit classical computer still stores only one state at a time. Therefore, as the number of bits increases, the information density of a quantum computer is exponentially higher than that of a classical counterpart.

In an N-qubit system, the entanglement also causes the probability amplitude of all  $2^N$  states to change when the state of a single qubit changes. On the other hand, flipping a bit in an N-bit classical system only affects its current state. Above properties enable quantum computers to solve complex optimization problems with large data sets in a parallel fashion that is exponentially faster than classical computers. An example of computational advantage of quantum computers is

shown in Table 1-1. Applications of quantum computing include cryptography, searching, molecular formations, material science, artificial intelligence, etc.

| Table 1-1: Analysis | of computational | l advantage of q | uantum computers | (IBM        | Corporation 20 | 18). |

|---------------------|------------------|------------------|------------------|-------------|----------------|------|

| 2                   | 1                | 0 1              |                  | <pre></pre> | 1              |      |

| . Jpe er eeuing                                       |            |           |              |               |                        |  |

|-------------------------------------------------------|------------|-----------|--------------|---------------|------------------------|--|

| Classical<br>algorithm with<br>exponential<br>runtime | 10<br>secs | 2<br>mins | 330<br>years | 3300<br>years | Age of the<br>universe |  |

| Quantum<br>algorithm with<br>polynomial<br>runtime    | 1<br>min   | 2<br>mins | 10<br>mins   | 11<br>mins    | ~24<br>mins            |  |

Type of scaling Time to solve problem

# 1.2. Cornerstones for quantum computing

To harness the power of quantum computing, in a fault-tolerant quantum computer at least 1,000 almost-error-free logical qubits need to be integrated. With an error-tolerant quantum error correction (QEC) algorithm such as the surface code, each logical qubit will consist of at least 1,000 physical qubits with less than 1% error rate (Fowler, et al. 2012). Also, it must be capable of performing universal quantum gate operations. These requirements impose scalability, universality, and fidelity constraints on the quantum processor, the combination of physical qubits and their quantum controller.

### **1.2.1.** Scalability

To integrate over one million physical qubits (1,000 logical qubits times 1,000 physical qubits per logical qubit) in a fault-tolerant quantum computer, scalability of the quantum processor is crucial. Being able to leverage mature semiconductor fabrication processes and as a result easier

to be integrated with quantum controllers enhances the scalability of the qubit. Thus, in this work we focus on highly scalable, all-electrically-controlled, CMOS-compatible qubits.

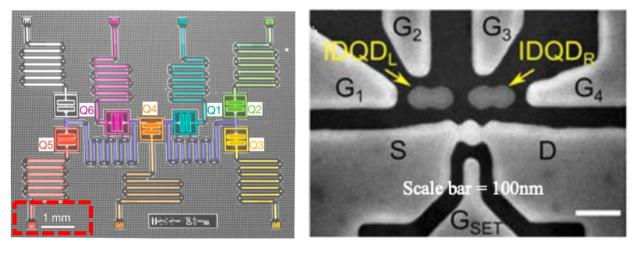

Popular types of qubits in this category can be divided into microwave-controlled and dcpulse-controlled. Microwave-controlled qubits include superconducting qubits and quantum-dot (QD) qubits utilizing the spin of charges. Their minimum layout pitch is limited to ~1mm due to the required high-Q LC resonant circuits and to alleviate crosstalk. On the contrary, the layout pitch of dc-pulse-controlled qubits such as the position-based double-quantum-dot (DQD) charge qubit is primarily limited by the resolution of lithography during fabrication, and it is on the order of 200nm. Examples are shown in Figure 1-1.

(a)

(b)

Figure 1-1: (a) 1mm-pitch superconducting qubits with resonant circuits (Kandala, et al. 2017).(b) 200nm-pitch position-based DQD charge qubits (Yang, et al. 2016).

## **1.2.2.** Universality

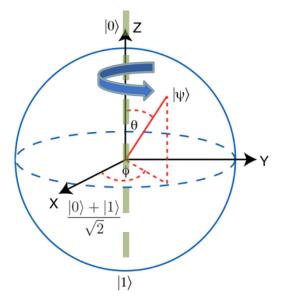

The state of a qubit can be visualized as a vector on the Bloch sphere as shown in Figure 1-2. Its mathematical expression in a spherical coordinate is

$$|\psi\rangle = cos(\theta/2)|0\rangle + e^{j\phi}sin(\theta/2)|1\rangle$$

where  $\theta$  represents the polar angle from the Z axis and  $\varphi$  is the azimuthal angle from the X axis. When the quantum system is at rest, the state vector of the qubit precesses around the axis of eigenstates, and the angular frequency  $\omega$  of this Larmor precession is related to the difference in energy of the eigenstates  $\Delta E$  through

$$\omega = \frac{\Delta E}{\hbar}$$

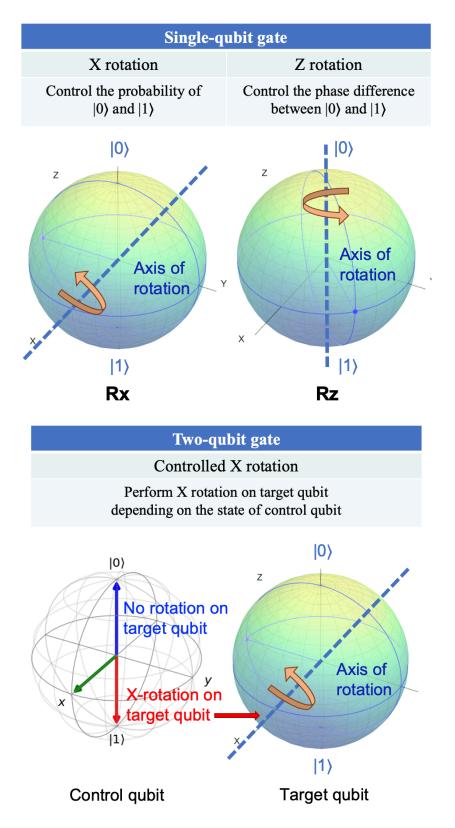

Universality mandates arbitrary manipulation of all  $2^{N}$  states in an N-qubit system, which can be broken down into a set of basic quantum gate operations called a universal quantum gate set. The constituents include single- and two-qubit gates. One example includes arbitrary X and Z rotation (Rx and Rz) for single-qubit gates and controlled X rotation for the two-qubit gate as illustrated in Figure 1-3. The combination of arbitrary X and Z rotation can rotate the state vector to any point on the Bloch sphere.

Figure 1-2: Representation of a qubit's state on the Bloch sphere.

Figure 1-3: An example of universal quantum gate set.

### 1.2.3. Fidelity

Nonideal control waveforms and noise lead to a finite error rate when operating physical qubits. Even with a small error rate of 0.1% per operation, the accumulated error rate after repeating the operation 1,000 times will reach 63%, which is intolerable for practical purposes. Thus, algorithms for QEC are necessary.

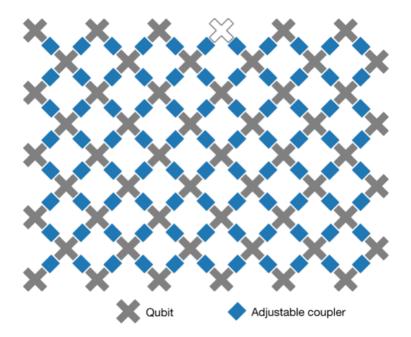

One of the most popular QEC algorithms for its high tolerable error rate of physical qubits is the surface code, which gets its name from the required two-dimensional placement of qubits. A sample placement of qubits compatible with the surface code from Google is shown in Figure 1-4. The error rate of the constructed logical qubit after error correction, P<sub>L</sub>, can be estimated from

$$P_L \approx 0.03 \times \left(\frac{P_{ph}}{P_{th}}\right)^{\sqrt{m/3}}$$

where  $P_{th}$  is the error threshold for each physical qubit set by the chosen QEC algorithm,  $P_{ph}$  is the actual error rate when operating a physical qubit, and m is the number of physical qubits required to achieve a certain  $P_L$  (Fowler, et al. 2012). Given the error rate of a logical qubit, as the error rate of constituting physical qubits increases towards the error threshold, more physical qubits will be needed to construct a logical qubit. For almost-error-free logical qubits utilizing surface-code QEC, the error threshold is 1%, and thus the error rate of a physical qubit needs to be below this threshold. Equivalently, the fidelity of operating a physical qubit must exceed 99%.

Figure 1-4: Surface-code-compatible qubit placement in the 54-qubit "Sycamore" quantum processor from Google (Arute, et al. 2019).

# 1.3. Cooling power constraints

To preserve the delicate quantum properties against thermal noise, the typical operating temperature of our qubit ranges from tens to hundreds of millikelvin. Maintaining at the desired temperature relies on sufficient cooling power of the refrigerator to overcome the heat generated within the cryogenic chamber. The available cooling power reduces exponentially as the target temperature drops, and this imposes a stringent requirement on the power consumption of the quantum processor. I/O cabling will also increase the thermal load to the chamber and reduce the available power budget. Therefore, in practical quantum systems, the quantum controller is placed as close to the qubit as possible with a minimum I/O count. The cooling power of various chambers in a commercial dilution refrigerator is shown in Figure 1-5. At 4K the cooling power is around

1W. It drops to 10mW at 1K, and only 10µW at 20mK. Further enhancement of the cooling power of refrigerators is another important area of research for scaled-up quantum computing.

Figure 1-5: Cooling power of a commercial dilution refrigerator in various chambers (Bonen

2020).

# **Chapter 2** Scalable quantum processors

### 2.1. Microwave-based versus dc-pulse-based quantum processors

#### Microwave-based quantum processors

The current mainstream microwave-based quantum processor is based on the superconductor qubit. In 2019, Google demonstrated quantum supremacy with a 54-qubit chip, which can encode an amount of information surpassing any classical computer. In 2022, IBM announced a quantum computer with 433 qubits and plans to achieve quantum advantage by 2030. However, as discussed in section 1.2.1, the 1mm pitch will hinder scaling up. This is limited by the dimension of the high-Q LC resonant circuits which is proportional to the carrier's wavelength. The typical carrier frequency of 4-8GHz sets the practical layout pitch. Surface-code-compatible qubit placement shown in Figure 2-1 further increases the equivalent pitch between qubits. On the quantum controller side, for spectral purity, similar high-Q resonant circuitry mandates large on-chip inductors and consumes high power. A 2-channel non-multiplexed quantum controller from IBM in 14nm FinFET is shown in Figure 2-1. Each channel occupied 0.8mm by 1.95mm.

#### • DC-pulse-based quantum processors

To address the scalability issue, we choose to work on the highly scalable, dc-pulsecontrolled position-based DQD charge qubit. The hard-wall-confined DQD shown in Figure 2-2 is of particular interest due to its long decoherence time on the order of tens of microseconds (Yang, et al. 2016) (Gorman, Hasko and Williams 2005). This allows many high-fidelity quantum gate operations as a typical  $2\pi$  X rotation only needs ~200ps. Aside from the ~200nm layout pitch, its quantum state can be fully controlled by dc pulses, and its capacitive terminals enable the adoption of low-power capacitive-digital-to-analog-converter-based (CDAC-based) output stage for the controller. Since the controller no longer needs on-chip inductors, its area will be drastically smaller than microwaved-based counterpart. The qubit's required voltage range is also compatible with advanced CMOS technologies. As shown in the Figure 2-2, the needed range of dc bias for state initialization is less than 1.8V, which is a common supply voltage for thick-oxide I/O FETs. Since an adiabatic process is desired during initialization to avoid unwanted excitation, thick-oxide FETs are the perfect candidate for these dc sampling switches. On the other hand, less-than-0.9V pulse height is needed for diabatic pulsing during quantum gate operations. Since this is a typical supply voltage for thin-oxide core FETs, they can be used to generate these fast pulses. Due to these promising properties, our CMOS quantum controller is designed for this type of qubit.

Figure 2-1: (a) Placement of superconducting qubits compatible with heavy hexagonal surfacecode (Chakraborty, et al. 2022). (b) A 2-channel non-multiplexed quantum controller in 14nmFinFET for superconducting qubits (Chakraborty, et al. 2022).

Figure 2-2: Hard-wall-confined position-based DQD charge qubit (Yang, et al. 2016) (Gorman, Hasko and Williams 2005).

### 2.2. Position-based DQD charge qubit

### 2.2.1. Universal single-qubit quantum gates

#### • Principle of operation

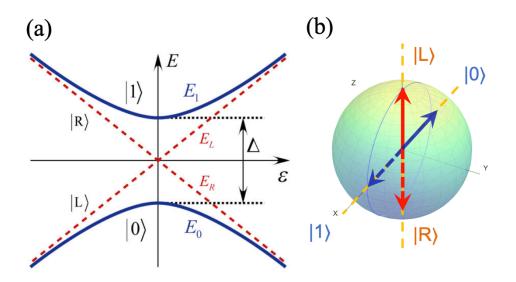

The position-based DQD charge qubit consists of a left and a right QD separated by a tunable tunneling barrier. As the size of the QD reduces thanks to advanced fabrication technologies, the required charging energy to add extra charges to the QD increases due to the stronger Coulomb repulsion (Rabouw and Donega 2017). This results in clearly discretized charge state of the QD. The position-based DQD charge qubit typically utilizes the location of the charge to encode its quantum state. Mathematically, the basis state  $|L\rangle$  denotes that the charge is on the left dot, and  $|R\rangle$  on the right dot. The energy diagram shown in Figure 2-4 changes with the interdot coupling related to the potential of the barrier. The general Hamiltonian is written as

$$H = \begin{pmatrix} \varepsilon/2 & \Delta/2 \\ \Delta/2 & -\varepsilon/2 \end{pmatrix}$$

where  $\varepsilon$  is the detuning energy between the two dots and  $\Delta$  is the interdot coupling energy at the anti-crossing in the energy diagram. The average energy of the two QDs only contributes to the global phase of the system, and thus it is irrelevant to the quantum gate operations. The Hamiltonian determines the eigenstates and their corresponding eigenenergy as expressed below.

$$E_{\pm} = \frac{1}{2}\sqrt{\Delta^2 + \varepsilon^2}$$

$$\begin{cases} |\psi_+\rangle = \cos(\theta_0/2) |L\rangle + \sin(\theta_0/2) |R\rangle \\ |\psi_-\rangle = \sin(\theta_0/2) |L\rangle - \cos(\theta_0/2) |R\rangle \\ \theta_0 = \tan^{-1}\frac{\Delta}{\varepsilon} \end{cases}$$

As described in section 1.2.2, universal single-qubit gates require arbitrary rotation around any two orthogonal axes on the Bloch sphere. Typically for our qubit, the two axes chosen are the X and Z axis since the eigenstates align with these axes as explained in following paragraphs and the qubit state naturally precesses around them.

When the barrier potential is high and thus makes the interdot coupling negligible, or  $\Delta \ll \varepsilon$ , resulting eigenstates are  $|L\rangle$  and  $|R\rangle$ . The corresponding eigenenergy for  $|L\rangle$  is  $\varepsilon/2$ , and for  $|R\rangle$  is  $-\varepsilon/2$ . Solving the time-dependent Schrödinger's equation yields a precession frequency of  $\varepsilon/h$ . Since  $|L\rangle$  and  $|R\rangle$  are aligned with the Z axis on the Bloch sphere as shown in Figure 2-4, setting a high barrier potential and introducing detuning between the dots result in a Z rotation.

On the other hand, when the barrier potential is lowered and thus the detuning is minimized, or  $\Delta \gg \varepsilon$ , resulting eigenstates become  $|0\rangle$  and  $|1\rangle$ . The corresponding eigenenergy for  $|0\rangle$  is  $-\Delta/2$ , and for  $|1\rangle$  is  $\Delta/2$ . Again, solving the time-dependent Schrödinger's equation yields a precession frequency of  $\Delta/h$ . Since  $|0\rangle$  and  $|1\rangle$  are aligned with the X axis on the Bloch sphere, lowering the barrier potential and nulling the detuning result in an X rotation.

Figure 2-3: (a) Discretized energy states of QD (Rabouw and Donega 2017). (b) Illustration of quantum states of a position-based DQD charge qubit.

Figure 2-4: (a) Energy diagram with (blue) and without (red) interdot coupling. (b) Eigenstates on the Bloch sphere with (blue) and without (red) interdot coupling.

### • Actual implementation of X rotation (Rabi oscillation)

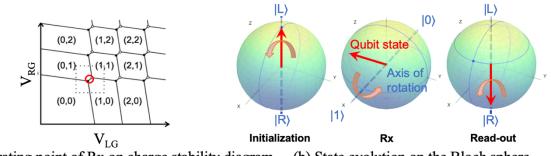

To initialize the qubit's state to  $|L\rangle$ , we minimize the interdot coupling and set the potential of the left and right gate based on the charge stability diagram of the DQD such that there is one charge on the left dot and none on the right. After initialization, the detuning energy is reduced to zero by equalizing the potential of both gates to minimized unintended Z rotation in subsequent phases. To initiate the X rotation, as described earlier in this section, we lower the barrier potential by sending a fast pulse to the barrier terminal. As derived in section 2.2.2, for high fidelity it is important to minimize the edge transition time relative to the Rabi oscillation period. Through this diabatic process, the initial state,  $|L\rangle$ , starts to rotate around the X axis and oscillate between  $|L\rangle$ and  $|R\rangle$ . The exponential relationship between barrier voltage and interdot coupling energy, and thus the Rabi oscillation frequency, can be explored through a highly programmable quantum controller with precise tuning in pulse width and height. To determine the state of the qubit after the X rotation, we raise the barrier potential to enter the hold phase and perform read-out through neighboring charge sensors. This series of actions need to be repeated periodically for a projective read-out to determine the probability amplitude of each basis state.

Critical requirements on control waveforms include the following.

- Low-noise and high-resolution pulse height tuning: On barrier, this enables accurate control of the Rabi frequency. On gates, this minimizes unintended Z rotation.

- High-resolution, high-linearity and low uncertainty pulse width tuning for barrier pulses: This enables accurate control of degree of rotation.

- Minimized edge transition time during pulsing: This minimizes unintended rotation during edge transitions due to the intermediate time-varying Hamiltonian.

(c) Timing diagram and corresponding terminals in intended CMOS-qubit integration

Figure 2-5: Principle and implementation of the X rotation, or Rabi oscillation.

#### • Actual implementation of Z rotation (Ramsey fringes)

For Z rotations, since the qubit state is initialized in the +Z direction ( $|L\rangle$ ) on the Bloch sphere, we need to perform a 90° X rotation prior to and after the intended Z rotation to observe its effect. After the hold phase following the first 90° X rotation, we increase the detuning by pulsing both gates in opposite direction to facilitate a Z rotation. Between the hold phase and the Z-rotation phase, since the energy eigenstates remain the same, the edge rate does not need to be fast, and only the total area under the pulse determines the degree of Z rotation.

Critical requirements on control waveforms include the following.

- High-resolution, high-linearity, and low-uncertainty pulse height and width tuning: This enables accurate control of the frequency and degree of rotation.

- High-fidelity 90° X rotation: This is needed for precise characterization of the Z rotation.

(c) Timing diagram and corresponding terminals in intended CMOS-qubit integration

Figure 2-6: Principle and implementation of the Z rotation, or Ramsey fringes.

# 2.2.2. Requirements on control waveforms for high fidelity

#### • Maximum error in pulse width

Nonideal pulse width results in error in the degree of rotation. For high fidelity, the achieved maximum error in pulse width should restrict this error to less than 1%. Assuming the qubit's state is initialized in |L), or

$$|\psi_0

angle = \begin{pmatrix} \mathbf{1} \\ \mathbf{0} \end{pmatrix}$$

at t=0 with nulled detuning, a pulse is applied to the barrier to facilitate the X rotation. The Hamiltonian with the interdot coupling can be written as

$$H = \begin{pmatrix} \mathbf{0} & \Delta/2 \\ \Delta/2 & \mathbf{0} \end{pmatrix}$$

By solving the time-dependent Schrödinger's equation, the time evolution of the qubit's state is

$$|\psi\rangle = U(t)|\psi_0\rangle = \begin{pmatrix} \cos\frac{\omega t}{2} & -i\sin\frac{\omega t}{2} \\ -i\sin\frac{\omega t}{2} & \cos\frac{\omega t}{2} \end{pmatrix} \times \begin{pmatrix} 1 \\ 0 \end{pmatrix} = \begin{pmatrix} \cos\frac{\omega t}{2} \\ e^{-i\pi/2}\sin\frac{\omega t}{2} \end{pmatrix}$$

The fidelity after the X rotation (Jozsa 1994) then is

$$\mathcal{F}(\rho,\sigma) = \left(tr\sqrt{\sqrt{\rho}\sigma\sqrt{\rho}}\right)^2 \approx \left|\langle\psi_\rho|\psi_\sigma\rangle\right|^2 = \left|\langle\psi_0|U(t_{final})U(t_{target})|\psi_0\rangle\right|^2$$

$$= \frac{1}{2} + \frac{1}{2}\cos(\omega t_{err})$$

The approximation holds due to the assumption of a decoherence time much longer than the time for the rotation. Finally, the error in pulse width

$$t_{err} = \frac{\cos^{-1}(2\mathcal{F} - 1)}{\omega}$$

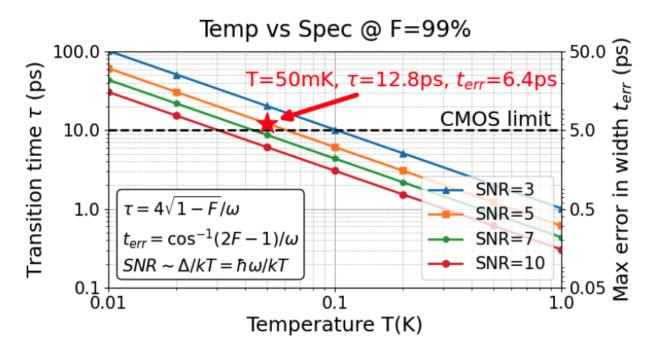

For  $\mathcal{F} > 99\%$ , the maximum error in pulse width can be calculated as a function of the Rabi frequency.

#### • Maximum edge transition time

During the edge transitions of the barrier pulse in an X rotation, non-zero edge transition time contributes to unintended rotation due to the intermediate time-varying Hamiltonian. After initializing the qubit's state to  $|L\rangle$  and minimizing the detuning, edge transition occurs from time t<sub>0</sub> to t<sub>1</sub>. The intermediate time-varying Hamiltonian and the time evolution matrix are

$$H = \begin{pmatrix} \varepsilon/2 & \Delta(t)/2 \\ \Delta(t)/2 & -\varepsilon/2 \end{pmatrix}$$

$$\widehat{U}(t_1, t_0) \approx 1 + \frac{\tau \overline{H}}{i\hbar}$$

where  $\overline{H}$  is the average Hamiltonian,  $\overline{\Delta(t)} \approx (\mathbf{0} + \hbar \omega)/2$ , and  $\tau$  is the edge transition time. The expression of  $\widehat{U}(t_1, t_0)$  is simplified via the perturbation approximation to the first order. This simplification is valid due to the short transition time,  $\frac{\tau \overline{H}}{t\hbar} \ll \mathbf{1}$ . The impact of finite detuning shows up in higher-order terms and is eliminated during the simplification due to its trivial quantity. After the edge transition at  $t_1$ , fidelity  $\mathcal{F} = \mathbf{1} - \zeta$ , where  $\zeta$  is the adiabaticity defined in Adiabatic Theorem.

$$\zeta = \mathbf{1} - \mathcal{F} = \mathbf{1} - |\langle \psi_{t0} | \psi_{t1} \rangle|^2 \approx \frac{\tau^2}{\hbar^2} \left( \left\langle L \right| \overline{H}^2 \left| L \right\rangle - \left\langle L \right| \overline{H} \left| L \right\rangle^2 \right) = \left( \frac{\tau \omega}{4} \right)^2$$

Therefore, the edge transition time

$$\tau = \frac{4\sqrt{1-\mathcal{F}}}{\omega}$$

For  $\mathcal{F} > 99\%$ , the maximum edge transition time can also be calculated based on the Rabi frequency. For advanced CMOS technologies, the practical minimum edge transition time is on the order of 10ps.

#### • Trade-off between waveform requirements and operating temperature of the qubit

Based on aforementioned requirements, we plot the maximum error in pulse width and maximum edge transition time for high fidelity versus the qubit's operating temperature in Figure 2-7 in various signal-to-noise ratio (SNR) scenarios. The SNR of our qubit is set by the ratio between the interdot coupling energy  $\Delta$  and the thermal noise kT. At a given temperature, larger interdot coupling energy increases the SNR, but it also leads to a higher Rabi frequency, which makes the waveform requirements harder to meet and increases the power and area of the quantum controller. Finally, considering the shortest practical transition time in advanced CMOS technologies, we choose to operate our qubit at 50mK with a 5GHz Rabi frequency and a reasonable SNR of 5. The corresponding maximum error in pulse width is 6.4ps, and the maximum edge transition time is 12.8ps.

Figure 2-7: Precision requirements on control waveforms versus qubit operating temperature.

## 2.2.3. Fidelity bottleneck in physics experiments

Stringent requirements derived in the previous section is only realizable with a minimized interconnect between the quantum controller and the qubit. Meter-long cabling from the arbitrary waveform generator (AWG) to the qubit in physics experiments largely limited the fidelity of single-qubit quantum gates due to nonideal waveforms (Cao, et al. 2013). To alleviate the transmission line effect arising from the long cabling, some form of low-pass filtering is needed to limit the voltage overshoot and the prolonged voltage ringing immediately after transition edges. The filtered narrow-band pulse therefore has long edge transition times. Combining with the pulse-height-dependent overshoot and insufficient precision in width control of the AWG, the fidelity then is limited. Our work addresses these issues by proposing to integrate the output stage of the quantum controller with the qubit chip through a low-parasitic packaging. Together with high-precision tuning in pulse width and height, it enables wide-band pulsing with sufficiently short edge transition time and precise waveforms to achieve high-fidelity arbitrary X and Z rotations.

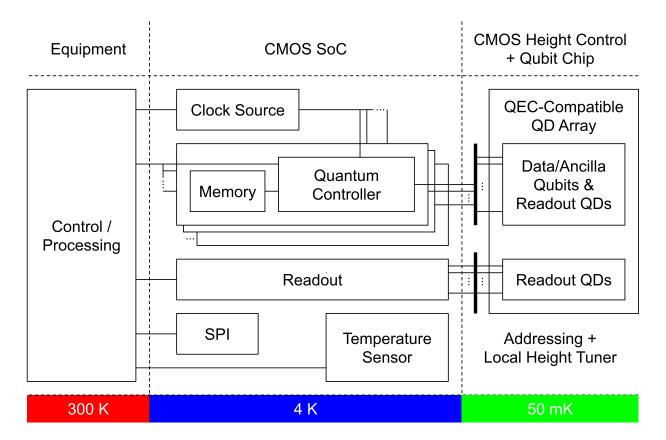

## 2.3. Proposed architecture for a scalable quantum processor

To achieve scalable quantum computing with high fidelity, we propose the architecture for the quantum processor illustrated in Figure 2-8. Aside from meeting stringent requirements on control waveforms, we envision that the quantum controller to be divided into two parts to be compatible with the available cooling power from the dilution refrigerator. Only the necessary low-power addressing and height control circuitry should be integrated with the qubit chip through a low-parasitic packaging inside the millikelvin chamber. The rest of the circuitry including the width control and the high-speed logic will be housed in a separate chamber at a higher temperature, e.g., 4K, for its higher cooling power. The number of interconnects between chambers should be minimized to limit the thermal load.

Figure 2-8: Proposed architecture of a scalable quantum processor.

# Chapter 3 Temperature-insensitive quantum controller for high-fidelity universal single-qubit gates

# 3.1. Temperature-insensitive design methodology

A major challenge in designing complex, high-performance circuits for cryogenic operations is the lack of device models at cryogenic temperatures for simulations. To guarantee the circuit's performance for high-fidelity quantum gates, we propose temperature-insensitive design methodologies based on changes of device characteristics from room temperature to cryogenic temperatures reported in existing literature.

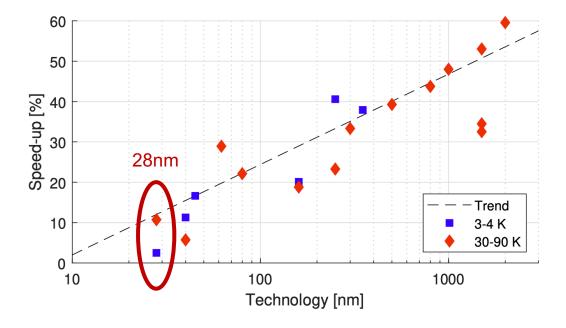

#### • Digital-centric architecture

A comparison of transistor characteristics at 300K and 4K is summarized in Table 3-1. Since our controller is designed with 28nm bulk CMOS technology, we focus on the measurement data from the 40nm CMOS samples. For analog circuits to main similar performances at cryogenic temperatures, the significantly increased threshold voltage (V<sub>th</sub>) and variation in charge mobility mandate wide-range programmability. Worsened matching of FETs (Van Dijk, et al. 2020) and increased 1/f noise (Chang, Abidi and Viswanathan 1994) at cryogenic temperatures result in significant area penalty. Thankfully, effects such as carrier freeze-out and kink effect are not found to occur in nanometer-scale technologies (Van Dijk, et al. 2020).

Digital circuits with fast edges, on the other hand, are less sensitive to changes in  $V_{th}$  and charge mobility due to rail-to-rail signaling. Shorter gate delay leads to faster logic, and steeper subthreshold slope lowers the leakage. A key design parameter for synthesized digital circuits is the hold time margin. Later in this section we propose a hold time margin at 300K to ensure robust functionality at cryogenic temperatures while maintaining efficiency in area and power.

From previous analysis, we propose a digital-centric implementation and strive to maximize its performance. For analog amplifiers, we incorporate sufficient programmability to cover the extreme variations in the I-V characteristics of devices.

Table 3-1: Comparison of transistor characteristics at 300K and 4K (Van Dijk, et al. 2020).

| Technology                           |                    | 0.16 μm                                 |                        | 40 nm                  |                        |

|--------------------------------------|--------------------|-----------------------------------------|------------------------|------------------------|------------------------|

| Temperature                          |                    | 4 K                                     | 300 K                  | 4 K                    | 300 K                  |

| Device W/L                           | $[\mu m/\mu m]$    | 2.32 / 0.16                             |                        | 1.2 / 0.04             |                        |

| $V_T$                                | [V]                | 0.55                                    | 0.40                   | 0.50                   | 0.38                   |

| SS                                   | [mV/dec]           | 22.8                                    | 87.0                   | 27.7                   | 88.2                   |

| n                                    | [-]                | 28.7                                    | 1.5                    | 34.9                   | 1.5                    |

| I <sub>on</sub>                      | [A]                | $2 \cdot 10^{-3}$                       | $1.5 \cdot 10^{-3}$    | $6 \cdot 10^{-4}$      | $5.3 \cdot 10^{-4}$    |

| I <sub>off</sub>                     | [A]                | $< 3 \cdot 10^{-11}$                    | $< 1.6 \cdot 10^{-10}$ | $< 1.5 \cdot 10^{-12}$ | $< 1.4 \cdot 10^{-10}$ |

| Ion/Ioff                             | [A/A]              | $> 6.7 \cdot 10^7$                      | $> 9.4 \cdot 10^6$     | $> 4.0 \cdot 10^{8}$   | $> 3.8 \cdot 10^{6}$   |

| Gate delay                           | [ps]               | 30.60                                   | 38.30                  | -                      | -                      |

| $\lambda$                            | [V <sup>-1</sup> ] | 3.3                                     | 0.6                    | 4.0                    | 1.3                    |

|                                      |                    | Weak Inversion                          |                        |                        |                        |

| $g_m/I_D$                            | [V <sup>-1</sup> ] | 70                                      | 27                     | 92                     | 27                     |

| Intrinsic gain = $g_m/(\lambda I_D)$ | [V/V]              | 21.2                                    | 45.0                   | 23.0                   | 20.8                   |

|                                      |                    | Strong Inversion (at $V_{ov} = 0.2 V$ ) |                        |                        |                        |

| $g_m/I_D$                            | [V <sup>-1</sup> ] | 6                                       | 9                      | 9                      | 10                     |

| Intrinsic gain = $g_m/(\lambda I_D)$ | [V/V]              | 1.8                                     | 15.0                   | 2.2                    | 7.7                    |

Figure 3-1: Speed-up of digital gates at cryogenic temperatures (Van Dijk, et al. 2020).

#### • Capacitor-matching-based linearity-sensitive circuits

As explained in section 2.2, precise control over the pulse shape is the key to achieve high fidelity. Thus, highly linear converters are indispensable. To fulfill required speed and resolution, current digital-to-analog converter (DAC) and capacitive DAC (CDAC) are two viable options.

Current DACs utilize matching of FETs for linearity. From ('t Hart, et al. 2018) it was reported that the matching property ( $\sigma/\mu$ ) of the drain current of long-channel FETs, suitable for implementing current sources, can deteriorate up to 20% from 300K to 4.2K, and this is mainly due to increased mismatches in V<sub>th</sub>. Due to the worsened matching, these FETs need to be sized 20% larger just to meet the same linearity at 4.2K.

CDACs, on the other hand, utilize matching of capacitors for linearity. To our best knowledge, there has not been any literature systematically characterizing matching of capacitors at cryogenic temperatures. However, since the matching solely depends on the ratio of geometry, it is not expected to degrade as temperatures drops (Van Dijk, et al. 2020). In this work, we report the indirectly measured matching property of metal-oxide-metal (MOM) capacitors at 300K and 77K. Another advantage of choosing CDAC-based width and height control is its drastically lower power consumption. All sub-circuits can be designed in the digital fashion and, excluding leakage, consume only dynamic power during switching activities. For the height control, the purely capacitive qubit terminal is also a perfect fit for the CDAC's charge-redistribution operating principle. Therefore, we propose to utilize capacitor matching for linearity-sensitive circuits.

Figure 3-2: Worsened matching in drain current as temperature drops (biased at a fixed  $g_m/I_D$  of  $10V^{-1}$  in saturation) ('t Hart, et al. 2018).

#### • 50ps hold time margin

During the design of synthesized sequential logic digital circuits, closing timing with proper setup and hold time margin is arguably the most important step. However, without modeling at cryogenic temperatures, it is impossible to predict the margin at those temperatures accurately. Insufficient setup or hold time leads to loss of circuit functionality. Setup time violation can be resolved during the chip testing by slowing down the clock rate and increasing the voltage supply to speed up the circuits. Hold time violation, however, cannot be fixed on silicon, and requires extra iterations of costly tape-out to correct. As illustrated in Figure 3-3, for the register REG2 to properly read the output of a combinational logic, the output must hold steady for at least T<sub>h</sub> after the arrival of clock. Proper hold time margin is reserved to guarantee positive hold slack in all cases. Hold time violation occurs when the hold slack becomes negative. Since the relative

timing between the combinational logic delay and T<sub>h</sub> has no dependency on the clock rate and the supply voltage, hold time violations cannot be resolved during testing.

To ensure robust functionality at cryogenic temperatures, we must reserve sufficient hold time margin in the design phase. Inserting buffers in the combinational logic can increase the margin. However, this comes with a cost of larger chip area and higher power consumption. Thus, the margin must be decided methodically.

Figure 3-3: Illustration of hold time requirement (Zhang 2016).

As temperature drops, the change in CMOS gate delay is dictated by competing factors such as increased  $V_{th}$  and variation in charge mobility. Depending on their changes relative to the voltage supply ( $V_{DD}$ ), different trends of gate delay have been observed. When the increase in  $V_{th}$  dominates, FETs turn on slower and the gate delay increases. From the delay per stage of a 101-stage ring oscillator in 28nm bulk CMOS (Ismail-zade, et al. 2020) shown in Figure 3-4, the increase in gate delay below 300K can be as high as 70%. On the other extreme, when the increase in charge mobility dominates, the "on" current increases. Assuming that the changes in parasitic capacitance of FETs is trivial, the input of the succeeding gate gets charged faster, which leads to reduced gate delay. From the measured "on" current versus temperature reported in (Beckers, et al. 2017) shown in Figure 3-5, the reduction in gate delay from 300K to 4.2K can be as high as 30%.

Figure 3-4: Delay per stage of a 101-stage ring oscillator in 28nm bulk CMOS versus temperature (Ismail-zade, et al. 2020).

Figure 3-5: "On" current versus temperature in 28nm bulk CMOS (Beckers, et al. 2017).

With the knowledge of extreme variations in the gate delay, we calculate the required hold time margin at 300K to ensure robust functionality at cryogenic temperatures. At room temperature,  $T_h$  in our 28nm standard cell is 5ps, and a typical hold time margin is 10ps. The worst scenario for the hold time constraint occurs when the  $T_h$  increases to the upper bound and  $T_{CQ} + T_{data}$  reduces to the lower bound. Here we assume that with the synthesized clock tree, clock arrives at each register at the same time and is insensitive to temperature changes. To have the same ratio of  $T_h$  and hold slack at cryogenic temperatures, the required hold time margin can be derived below.

$$(5p + Hold \, slack|_{300K}) \times 70\% = (5p + 10p) \times 170\%$$

$$\implies Hold \, slack|_{300K} = 31ps$$

To reserve more margin for millikelvin operations, we specify the hold time margin to be 50ps for all digital blocks, which should guarantee their functionalities at cryogenic temperatures.

- Summary of temperature-insensitive design methodologies

- Adopt digital-centric architecture with fast edge transitions.

- Incorporate sufficient programmability for analog circuitry.

- Utilize capacitor matching for linearity-sensitive circuits.

- Design with 50ps hold time margin at 300K for synthesized sequential digital circuits.

## **3.2.** Quantum controller design with temperature-insensitive performance

## 3.2.1. Limitation of state-of-art dc-pulse-based controllers

To enable high-fidelity universal single-qubit gates for our qubit, a maximum error in pulse width of 6.4ps is required. The major contributors to this error include the finite tuning resolution, maximum absolute value of differential nonlinearity (max |DNL|), and uncertainty in pulse width due to random noise. In state-of-art dc-pulse-based quantum controllers, the tuning resolution of pulse width in (Esmailiyan, et al. 2020) (Ekanayake, et al. 2008) was limited to one period of their input clock since digital counters triggered by the input clock were used to program the pulse width. This is too coarse since even with an input clock as fast as 6GHz (Esmailiyan, et al. 2020), the resolution was merely 166ps per step, which is 26 times larger than the required maximum error in pulse width. In (Pauka, et al. 2021), an on-chip free-running ring oscillator generated the master clock, and the linear width tuning was done through varying the number of stages in the oscillator. The tuning resolution could be as fine as two times the delay of an inverter, which is on the order of 20ps, but this delay could vary significantly since there was no PVT-compensation or calibration implemented. The shortest pulse width was also limited to one clock period due to the digital-counter tuning mechanism. The 166ps-wide pulse reported in (Esmailiyan, et al. 2020) is already

$\sim$ 300° of a 200ps Rabi period. Max |DNL| was not reported in any of the state-of-art controllers. Uncertainty in pulse width was only reported in (Ekanayake, et al. 2008), but it was on the order of hundreds of picoseconds, which is at least 15 times over our targeted maximum error in pulse width. Also, among all these works there was no calibration to ensure accuracy of the pulse width.

Precise pulse height tuning can enable accurate control of the rotation frequency, minimize unintended rotations, and reduce crosstalk between qubit terminals. In state-of-art controllers, only (Esmailiyan, et al. 2020) implemented on-chip control of pulse height. However, its linearity was limited to a max |DNL| of 10.4LSB with 8-bit programmability.

The concept of integrating a CDAC-based output stage with the qubit chip in the millikelvin chamber was demonstrated in (Pauka, et al. 2021). However, its maximum repetition rate of successive quantum gates was limited to around 10MHz to keep its power consumption lower than the cooling power of the 100mK chamber. This bottleneck can be broken by moving most of the controller to another chamber at a higher temperature while leaving only the output stage in the millikelvin chamber. (Esmailiyan, et al. 2020) integrated the controller with the qubit at 3.4K. Although switching activities in its CDAC were limited to only the enabled units, continuous clocking of those units by the master clock at 2GHz still incurred noticeable overhead in power consumption. This can be improved by replacing the continuous clocking scheme with a pulse-activated design.

Lastly, on-chip generation of all control waveforms needed for universal single-qubit gates is preferrable as it reduces the number of high-speed I/O needed for the cryogenic chamber. I/O interconnects with higher bandwidth result in larger thermal load, and thus further consume the already limited cooling power budget. Among the state-of-art controllers, only (Pauka, et al. 2021) was capable of generating arbitrary waveforms through on-chip memories.

### **3.2.2.** Proposed architecture for the quantum controller

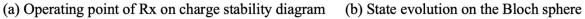

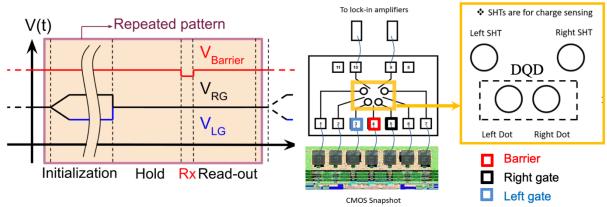

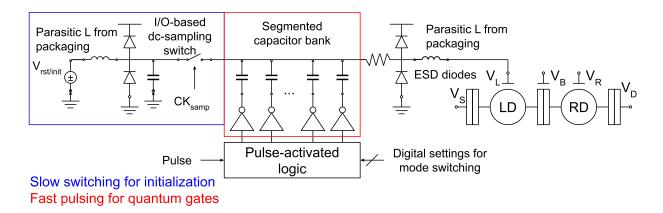

To support high-fidelity universal single-qubit gates for our qubit, we have implemented a temperature-insensitive quantum controller in 28nm bulk CMOS as shown in Figure 3-6. Figure 3-7 details the chip layout and the intended CMOS-qubit integration. This prototype is designed not only for high-fidelity operations, but also to explore the optimal operating point and to study the decoherence and relaxation behavior of the qubit. To do the latter, significant amount of extra circuitry is added to the design. Once the qubit is fully characterized, the extra circuitry can be removed without sacrificing the precision, and the controller can be further partitioned into two parts as described in section 2.3.

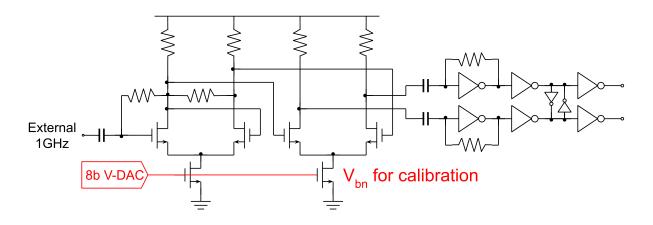

Illustrated in Figure 3-6 is the architecture and timing diagram of the proposed quantum controller. A 50Ω-terminated, highly programmable clock amplifier at the front end amplifies the external 1GHz sine wave to a rail-to-rail clock signal, and it is the only analog amplifier in the entire chip. This clock is then utilized by a 12-bit, 3.9ps/step width controller to generate pulses needed for quantum gates. It also drives the dual-edge-triggered core logic for all dynamic controls, pulse gating for power efficiency, and to generate all required waveforms for universal single-qubit gates. The linearity of the width tuning is calibrated by a 2ps/step pulse-swallowing cyclic TDC to ensure temperature-insensitive performance. After the width controller, the 9-bit, nominally 1mV/step, CDAC-based height controller fine tunes the pulse height and delivers final control waveforms to the left gate, barrier, and right gate of the DQD. DC biasing circuitry for the source and drain of the DQD is not shown. For synchronized lock-in read-out from charge sensors next to the DQD, our controller can also embed the lock-in pattern in all output waveforms.

Figure 3-6: Architecture and timing diagram of proposed quantum controller.

Figure 3-7: Chip layout and intended integration with the qubit.

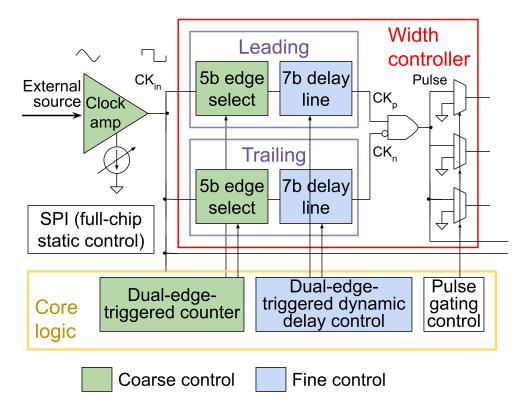

# 3.2.3. Temperature-insensitive width controller

#### • Tuning resolution

A two-step architecture is employed to implement the 12-bit width tuning. The pulse width is defined by a leading and a trailing 1GHz clock with different delays as shown in Figure 3-8. The 5-bit coarse tuning covers a 16ns range with a 500ps step. Then the 7-bit fine tuning further dissects the 500ps range with a 3.9ps step.

The coarse tuning is achieved by selecting two edges of the 1GHz input clock. Extensive simulations have been done to close the timing including the synthesized core logic and the edge

selection circuitry on the signal path. The duty cycle of the input clock can be distorted due to nonideal operating point of the clock amplifier and unbalanced rising and falling edge transition on the signal path. This introduces errors to the nominal step size of 500ps. The error is calibrated by the cyclic TDC and thus the tuning resolution is temperature-insensitive. During the calibration, the biasing voltage of the NFET current sources, V<sub>bn</sub>, in the clock amplifier is adjusted with an 8-bit voltage DAC (VDAC) as shown in Figure 3-9. All VDACs implemented in our controller has an output range from ground to its supply voltage to ensure coverage of extreme variations in transistor characteristics.

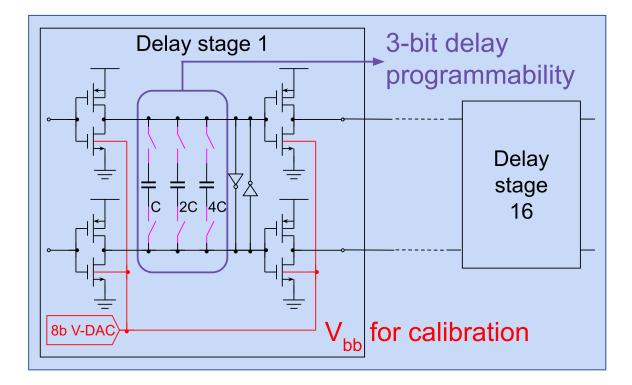

The fine tuning is achieved through varying the capacitive load in the 3-bit inverter-C delay stages in the 7-bit delay line. The step size of 3.9ps is also made temperature-insensitive thanks to the calibration by adjusting its supply and the bulk voltage of the NFETs in the delay stages,  $V_{bb}$ , through the 8-bit VDAC as shown in Figure 3-10.

Figure 3-8: Two-step architecture for width control.

Figure 3-9: Schematic of the programmable clock amplifier.

Figure 3-10: Schematic of inverter-C delay stage in the 7-bit delay line.

#### • Linearity

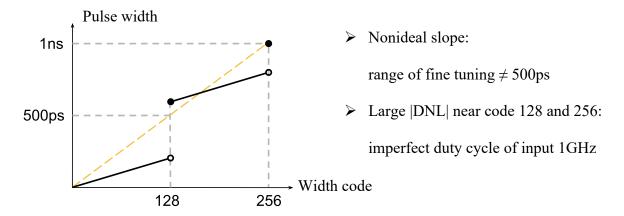

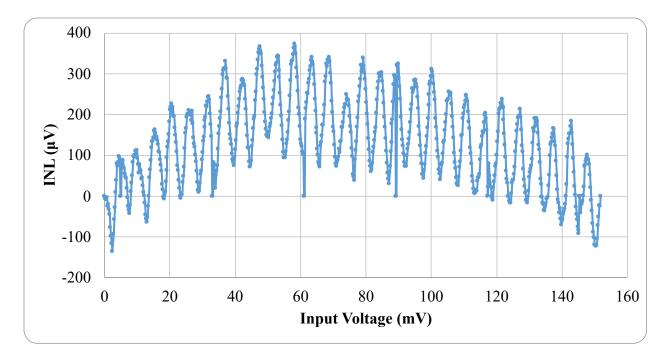

To minimize max |DNL|, we first analyze the major contributors to the nonlinearity in width tuning. In Figure 3-11, the deviation of the full scale of fine tuning from 500ps introduces gain error in its transfer curve. The nonideal duty cycle of the input clock further adds to the nonlinearity when the coarse tuning advances by one step, which is from code 127 to 128 and from code 255 to 256. Thanks to the well-matched inverter-C delay stages, the max |DNL| occurs either from code 127 to 128 or from code 255 to 256. Lastly, supply ripples due to transient current at transition edges also temporarily change the local supply voltage and introduce nonlinearity.

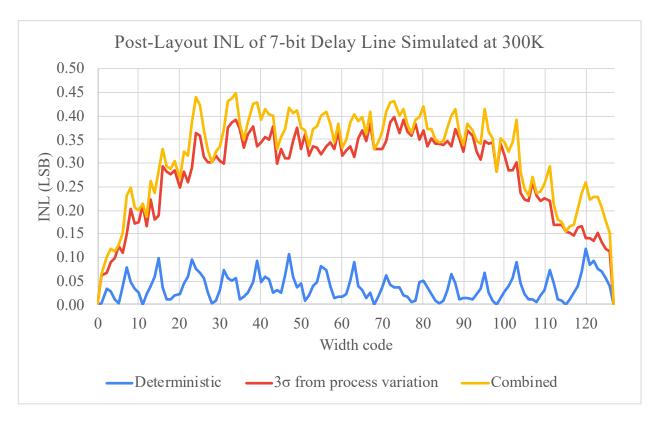

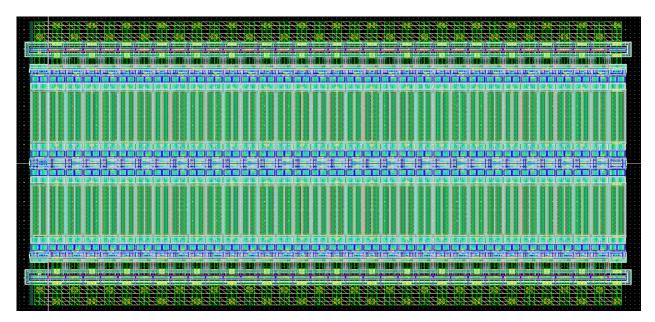

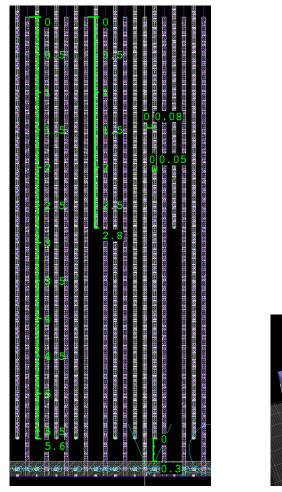

The max |DNL| is calibrated by the cyclic TDC through adjusting V<sub>bn</sub> and V<sub>bb</sub> as shown in Figure 3-9 and Figure 3-10, and thus made temperature-insensitive. For a linear fine tuning, we utilize the matching of MOM capacitors and adopt a segmented capacitor array (4-bit thermometer-coded MSBs + 3-bit binary-coded LSBs). The FETs in the inverter-C delay stage are sized for good matching such that the worst integral nonlinearity (INL) of the 7-bit delay line is around 0.45LSB (see Figure 3-12). To reduce supply ripple, we design a pseudo-differential, crosscoupled signal path with abundant bypass capacitors under the supply as shown in Figure 3-10. Illustrated in Figure 3-13 is the final compact, well-matched layout of the 7-bit delay line.

Figure 3-11: Major contributors to the nonlinearity of width control.

Figure 3-12: Post-layout simulated INL profile of the 7-bit delay line.

Figure 3-13: Layout of the 7-bit delay line for good linearity.

#### • Uncertainty in pulse width

We aim to minimize the uncertainty in pulse width for pulses shorter than 500ps. Since the expected Rabi period is 200ps, pulses up to 500ps long are sufficient to facilitate arbitrary X rotations. Pulses longer than 500ps are mainly used for decoherence and relaxation studies, and thus their accuracy requirement is not as stringent.

The rising and falling edge of pulses up to 500ps are generated from the same edge of the input clock. Therefore, noise from circuitry before the width controller is largely cancelled. Edge transitions throughout the entire signal path are designed to be fast to minimize the translation from noise to uncertainty in width. In the 7-bit delay line, the wider range covered in each delay stage will reduce the number of delay stages but result in slower edge transitions as the same inverter has to drive larger capacitive load, and this increases the width uncertainty. Therefore, through simulations we strike a balance between the number of bits per delay stage and the worst-case uncertainty in pulse width. At cryogenic temperatures, since the calibrated delay stages have a similar edge rate as that at 300K, lower thermal noise leads to smaller uncertainty. Signal path in the subsequent height control also benefits from lower temperature due to similar reasons.

#### • Calibration with pulse-swallowing cyclic TDC

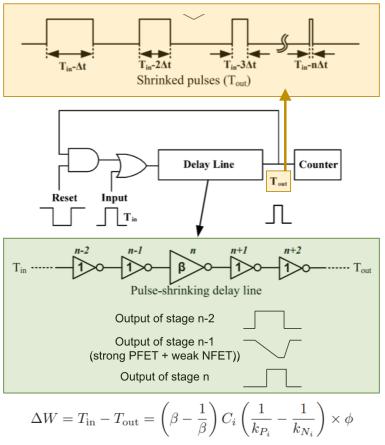

A 2ps/step pulse-swallowing cyclic TDC is developed to maximize the precision of width tuning as there is no oscilloscope with such high resolution in time. The TDC consists of a loop of skewed inverters, whose PFET and NFET have asymmetric driving strengths. Due to this asymmetry, the rising and falling edge at the input of the inverter experience different amount of delay, and this difference further depends linearly on the output load. Therefore, by sizing one of the inverters larger than the others, the pulse will be shrunk. Figure 3-14 illustrates the operating principle explained above and the governing equation for pulse shrinkage. Finally, the pulse width can be inferred simply by counting the number of times the pulse is shrunk before vanishing.

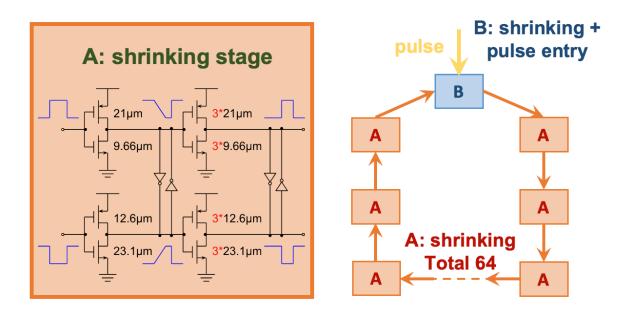

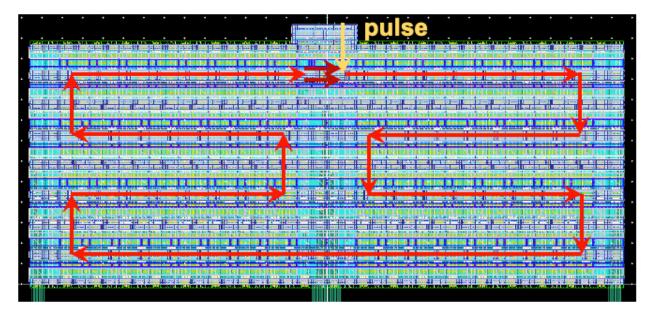

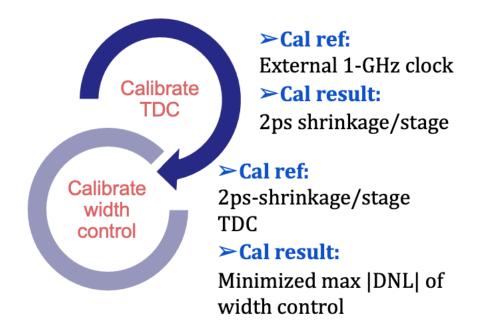

To realize 2ps shrinkage per stage with small uncertainty, we select a  $\beta$  of 3 under a 0.9V supply. A total of 64 shrinkage stages plus one pulse entry stage comprise the loop and exhibit a loop delay longer than 1ns. Since the loop delay must be longer than the maximum pulse width for proper functionality, the designed delay enables calibration of the TDC against the accurate 1ns period of the external clock. To enhance the linearity of the TDC, similar to the signal path, it is designed with a pseudo-differential, cross-coupled architecture to reduce supply ripple. The schematic and layout are shown in Figure 3-15 and Figure 3-16, respectively.

From the analysis in (Chen, Lin and Hwang 2014), we expect the resolution of the cyclic TDC to change as temperature drops. From testing, the shrinkage per stage reduces by 5% from 300K to 77K, which can be easily compensated by slightly lowering the supply voltage. Tuning the supply is a more desirable solution than adding circuits for temperature compensation, since the latter requires a much higher supply and thus significantly increases the power consumption.

During testing, the step size of the TDC will be first calibrated against the accurate 1ns period of the 1GHz input clock. Afterwards, the calibrated TDC will be used to optimize the precision of the width tuning.

Loop delay > max pulse width for proper functionality

Figure 3-14: Principle of pulse-swallowing cyclic TDC (Chen, Lin and Hwang 2014).

Figure 3-15: Schematic of our pulse-swallowing cyclic TDC.

Figure 3-16: Cyclic and matched layout of the TDC for good linearity.

Figure 3-17: Proposed calibration flow for optimal precision in width control.

### **3.2.4.** Temperature-insensitive height controller

The height controller is the output stage of our quantum controller, which directly interfaces with the qubit and charge sensors to perform initialization, manipulation, and read-out. Low-power CDAC-based design is adopted to take advantage of the purely capacitive terminals on the qubit chip. Each phase of operation has its own requirement on the control waveform. Therefore, aside from the precise CDAC, additional features supporting all phases of qubit operations are also incorporated to support high-fidelity quantum gates.

#### • Features for high-fidelity operations

During initialization, at the CMOS-qubit interface we need wide-range, low-speed sampling of dc voltages to properly bias the qubit at the desired charge regime and to avoid unintended excitation. These dc sampling switches are implemented with thick-oxide I/O FETs which also exhibit low leakage when they are turned off in other phases of operation. During manipulation and read-out, the fast pulses are generated by switching the CDAC to satisfy the transition time requirement as derived in section 2.2.2. A series pulse-shaping polysilicon-based resistor is added to the output to minimize the voltage overshoot, and its negligible leakage to the substrate is verified through simulations. In these phases we keep the impedance of the CMOS-qubit inface high to avoid significant voltage drooping which undermines the biasing of qubit and in turn shortens its decoherence time. The ESD diodes are sized just for sufficient protection. Perterminal hybrid DAC is implemented for independent pulsing to address potential crosstalk between qubit terminals. Lock-in pattern in the output waveforms can be enabled for lock-in read-out in low-SNR settings. All features mentioned above are shown in Figure 3-6 and Figure 3-18.

#### • Linearity and resolution

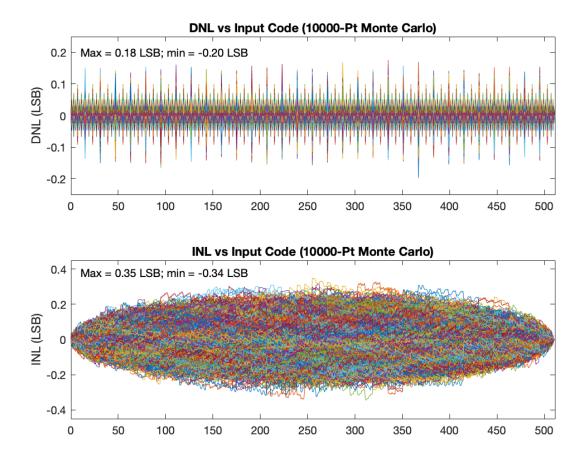

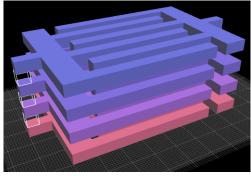

Requirements on the resolution, full scale, and linearity of the CDAC are dictated by the actual physical properties of the DQD. In this work we define the specifications according to the hard-wall-confined DQD (Yang, et al. 2016) (Gorman, Hasko and Williams 2005) mentioned in section 2.1. To cover a full scale of 500mV with output inverter drives powered by a 0.9V reference voltage, we co-design the 1pF total switchable capacitors in the CDAC with attenuation capacitors, extracted parasitic capacitance at the output, and the anticipated loading from the qubit. To determine the segmentation scheme of the capacitor bank and the sizing of the custom-made unit MOM capacitors for good linearity, we simulate the worst-case nonlinearity through 10,000-point Monte Carlo simulations in MATLAB. Figure 3-19 shows the DNL and INL profile with the final segmentation scheme and assuming conservative capacitor matching property. To reduce the layout size of the 9-bit CDAC, the capacitor with weighting of 1LSB is made of a 2fF unit capacitor while higher-weighting capacitors consist of 4fF unit capacitors. Figure 3-20 shows the mixedunit-capacitor implementation. The smaller capacitor banks also shorten the routing to qubit terminals and further reduce parasitic capacitance. The estimated matching of the 2fF unit capacitor is 0.7% (Tseng, et al. 2016) (Tsai, et al. 2015) (Saberi, et al. 2011), and the simulated max |DNL| is 0.2LSB.

To stabilize the reference voltage during full-scale pulsing, sufficient bypass capacitors are added to reduce the voltage drop at the pulse edges. The simulated integrated voltage noise at the output is negligible in comparison with 1LSB, and the thermal floor will be even lower at millikelvin temperature. Finally, the pulse-gating mechanism in the width controller in concert with the pulse-activated logic in the CDAC minimize switching activities and lower the power consumption for millikelvin operations.

Figure 3-18: Conceptual diagram of the height controller.

Figure 3-19: Linearity of the segmented CDAC (5 thermometer-coded MSBs + 4 binary-coded LSBs) with 0.7%  $\sigma_c/\mu_c$  of the 2fF unit capacitor.

Figure 3-20: Layout and conceptual diagram (Matthias 2022) of custom-made MOM capacitor using metal 2 to metal 5.

# 3.2.5. Core logic and SPI

The synthesized core logic and serial peripheral interface (SPI) are necessary for all dynamic controls and static programmability for the controller. The SPI is low-speed and relatively straightforward, while the core logic controls the width and height controller at 1GHz speed. To avoid glitches at its outputs which introduce unexpected distortion to the control waveform, the core logic is implemented as a Moore machine, which is a finite-state machine whose output only depends on its internal state. Also, the outputs are intentionally buffered such that the timing

analysis results are independent of the external load. The core logic defines synchronously the control waveforms for all terminals of the DQD and charge-sensors, lock-in read-out, triggering clock for the TDC's digital output, and digital settings for the whole controller.

To achieve low worst-case uncertainty in pulse width, we limit the full scale of the fine tuning to 500ps, which mandates a step size of 500ps in the coarse tuning. Since the coarse tuning is done through selecting edges of the 1GHz clock by the digital counter in the core logic, the counter needs to be dual-edge-triggered. As dual-edge-triggered flip-flops are not available in our 28nm standard-cell library, the counter design is separated into two parts, i.e., the rising- and falling-edge-triggered. To avoid glitches on the output edge selection signal sent to the signal path, we combine the output of both parts with an XOR gate, which is the simplest circuitry possible.

# Chapter 4 Liquid nitrogen dip testing