# **UC Irvine**

# **ICS Technical Reports**

# Title

Automatic synthesis of analog layout: a survey

# **Permalink**

https://escholarship.org/uc/item/8tg9c2ww

# **Author**

Rentmeesters, Mark J.

# **Publication Date**

1990-08-02

Peer reviewed

# Automatic Synthesis of Analog Layout: A Survey

Mark J. Rentmeesters

VLSI CAD Laboratory

Dept. of Information and Computer Science

University of California, Irvine

### ABSTRACT

A review of recent research in the automatic synthesis of physical geometry for analog integrated circuits is presented. On introduction, an explanation of the difficulties involved in analog layout as opposed to digital layout is covered. Review of the literature then follows. Emphasis is placed on the exposition of general methods for addressing problems specific to analog layout, with the details of specific systems only being given when they surve to illustrate these methods well. The conclusion discusses problems remaining and offers a prediction as to how technology will evolve to solve them. It is argued that although progress has been and will continue to be made in the automation of analog IC layout, due to fundamental differences in the nature of analog IC design as opposed to digital design, it should not be expected that the level of automation of the former will reach that of the latter any time soon.

August 2, 1990

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.)

UCI ICS TR 91 - 75

# Table of Contents

| 1. Introduction                               | 1  |

|-----------------------------------------------|----|

| 2. Analog ICs and Their Design                | 2  |

| 2.1 Characteristics of analog circuits        | 2  |

| 2.2 Analog IC Design                          | 4  |

| 2.2.1 Topology and component selection        | 4  |

| 2.2.2 Analog IC layout                        | 5  |

| 3. Automatic Analog Layout Synthesis          | 8  |

| 3.1 Module assembly and floorplanning         | 8  |

| 3.2 Module and device generation              | 14 |

| 3.2.1 Procedural methods                      | 15 |

| 3.2.2 Template based methods                  | 16 |

| 3.2.3 General approaches                      | 19 |

| 3.3 Layout optimization                       | 22 |

| 4. Analysis and Conclusion                    | 28 |

| 4.1 Summary                                   | 28 |

| 4.2 Analysis                                  | 30 |

| 4.3 Predictions                               | 33 |

| 4.3.1 Short term predictions                  | 33 |

| 4.3.1 Long term predictions                   | 35 |

| 4.4 Conclusion                                | 37 |

| Abbreviations used in bibliographic citations | 37 |

| References                                    | 38 |

# Automatic Synthesis of Analog Layout: A Survey

Mark J. Rentmeesters

VLSI CAD Laboratory

Dept. of Information and Computer Science

University of California, Irvine

#### 1. Introduction

So many integrated circuits designed today are digital devices that digital and integrated circuitry are often considered synonymous. This simplification however, overlooks the fact that the same advances in microminiaturization that have made digital integrated circuits possible can also be applied to the design of electronic systems that process information represented in a continuous, or analog form as well. Indeed, until very recently the demand for monolithic solutions to analog circuit needs has been quite small in comparison to digital ones. This however is changing as applications for integrated circuits expand. The increasing economy of microminiaturization has made possible new applications for this technology, many of them involving analog circuitry. In particular, with competitive demands forcing full systems to be placed on an ever shrinking number of chips, in an inherently analog world, it is becoming increasingly necessary to include at least some analog interface circuitry on many primarily digital ICs. For this reason, demand for analog circuitry has recently begun to catch up with that for digital. Today, analog and mixed analog-digital IC design starts represent a substantial and growing percentage of all integrated circuits under development.<sup>19</sup>

In fact, so fast has been the growth in demand for analog integrated circuitry in recent years that somewhat of a vacuum now exists in the availability of computer aided design tools for such circuit development. This situation does not represent the first time the integrated circuit design community has found itself in such a predicament, however. A similar situation existed in the late seventies, when the advent of VLSI levels of circuit integration left the mostly manual methods of IC design then in practice incapable of fully exploiting the technology's capabilities, even for digital applications. Since then many automatic design tools have come to the aid of the digital IC designer. The most powerful of these tools provide design synthesis, that is, they will gen-

erate designs or features of a design automatically without the need for detailed human direction. Unfortunately, few of the synthesis tools developed for digital IC design to date have proved applicable to the somewhat different task of developing analog ICs. Nevertheless, automation of analog integrated circuit design was never forgotten. It has merely been overshadowed by developments in the digital world. As will be seen in what follows, useful tools are already at hand, and prospects for continuing additions to their number look quit good.

This paper will review the state of the art in the automatic synthesis of the physical geometry or layout for analog integrated circuits. The layout, process, also called physical design, is a very influential part of the design of an analog integrated circuit. Layout deals with the geometric definition, i.e. construction and positioning, of electrical devices and their interconnections on the surface of the an IC chip. Although there are now several excellent reviews of automatic layout synthesis in general, 36, 45, 53, 62, 71, 80 for the most part these works describe only digital layout. What is and is not applicable to analog design is not made clear in these expositions. It is hoped that the present work will provide this information.

Although an effort has been made to make the present work self contained, to keep the development concise and focused, emphasis will often be placed on the differences between analog design tasks and their corresponding digital counterpart. This not only saves the need to describe the digital method or problem in extreme detail, but also emphasizes the difficulties unique to analog design automation that make it distinct from that of digital. Being primarily a survey of the literature in automatic analog IC layout synthesis, rather than of the technology itself or of its applications, this paper will be focused in several other ways as well. It will, for one, be concerned for the most part with analog circuit applications and fabrication processes already in widespread

use. That is, no coverage will be given to the automatic synthesis of experimental or as yet to be fully developed circuit technologies (e.g. neural networks), for which no publications describing specialized automated design aids currently exist. Likewise, the most heavily emphasized fabrication process will be CMOS. This is because it is for mixed analogdigital circuits that interest in alleviating analog circuitry design bottlenecks through automation is strongest, and CMOS is currently the technology of choice for mixed analog-digital IC design. Fortunately, the general principles of most of the automation techniques that will be described are not highly dependent upon the type fabrication technology employed. In addition, essentially no coverage will be given to so called bipolar array or masterslice analog IC development methodologies, as physical design in these processes is usually made very simple by intention, often requiring little or no automation. The reader interested in masterslice design techniques can consult (81).

It will be seen that the primary aim of most techniques described in this report is to provide an automated solution to some problem or group of problems in the design of high performance, full custom analog integrated circuits. Because these solutions are for full custom applications, they enjoy every design freedom that would be available to the human designer. But because the designs are for high performance circuits, their use cannot generally represent a substantial compromise over the results of human effort either.

The paper is organized as follows. In section two an overview of contemporary analog IC design and layout practices is presented. The background material presented in this section will allow the nonanalog IC design specialist to properly comprehend and appreciate the problems and challenges involved in analog IC design and its automation. The objective of section three, the main body of the review, is then to provide an unbiased and exhaustive summary of progress reported to date in the automation of analog IC layout synthesis. The ordering of subsections within section three arranges the problems in automatic analog layout synthesis roughly from the simpler to the more challenging. This organization is also roughly chronological, as the more demanding challenges have tended to resist attempts at automation longer. Unbiased exposition ends in the final section, number four, where a critical analysis of the strengths and weaknesses of current efforts in analog IC design automation is attempted. After identifying the apparent sources of these strengths and weaknesses, the chronological progression begun in

section three is projected into the future in section four with predictions of likely developments yet to come in the field of analog IC design automation in the next several years.

# 2. Analog ICs and Their Design<sup>27, 28</sup>

## 2.1. Characteristics of analog circuits

The variety of analog circuits in widespread use today is actually quite small. Application of electronics to signal and information processing began with the development of electronic telephony and radio nearly a hundred years ago. These early applications utilized a continuous waveform data representation, but since the advent of digital data processing techniques in the fourties, which have generally provided a much simpler design path for most signal and information processing applications, the uses of analog circuitry have for the most part remained unchanged. Thus, most analog circuits designed today can be classified as some form of signal amplifier, modulator, or demodulator, the principle classes of electronic circuits in existence when radio and telephone where the most extensive and demanding applications of electronics.

Today, the "amplifiers" are commonly referred to as linear electronics, and include the ubiquitous operational amplifier, or opamp, and many varieties of frequency selective amplifiers usually referred to as filters. Modulators and demodulators, which are in much less demand, are generally lumped together as nonlinear circuitry and include such devices as voltage controlled oscillators (VCOs -- the frequency of oscillation is controlled by an input voltage), waveform reshaping circuits (e.g. rectifiers), and waveform generators (that produce periodic patterns having various shapes, e.g. sinusoidal, square). Not surprisingly, the only analog circuit types to have effectively arisen since the advent of digital technologies have been analog-to-digital (A/D) and digitalto-analog (D/A) converters. Something that all these circuit forms share in common, at least when compared to modern digital electronics, is simplicity of function. Their output has a very direct relationship to their inputs. This is because a system having a complicated relationship between its input and its output, especially if this relationship requires long term information storage, quickly becomes very difficult to design as an entirely analog circuit.

The difficulting of design arises from the higher level of electrical detail utilized in analog circuits than in digital ones. The greater importance of pre-

cision in voltage levels, current rates, and so on in analog circuits means the electrical properties of their components, such as resistances and capacitances, have to be determined and specified more precisely. It also means more attention has to be paid to less influential device characterists and other physical phenomena than is necessary in digital design. For example, electromagnetic coupling between unconnected but adjacent wires can often be safely ignored in digital electronics but not in analog. For this reason, when assessing the design complexities of integrated circuits, the often low component count of analog circuits as compared to digital can be deceptive. Although few in number, the components in an analog circuit must often be specified at a much higher level of detail than do those in digital circuits. For example, at the waveform level of detail employed in analog circuitry, seemingly "simple" circuit modifications, such as alteration of a device characteristic (e.g. resistance) by a few percent, can significantly alter circuit behavior. Thus, analog circuits tend to be simple in structure but complex and precise in their detail.

Nothing better conveys the subtlety of detail present in seemingly simple analog circuits better than their performance specifications. Analog circuits are notorious for their apparently inexhaustible measures for characterization. A single example, that of an operational amplifier, will serve to illustrate this well.

An ideal operational amplifier is a voltage controlled voltage source extracting no energy from the controlling input circuit (having infinite input impedance), providing arbitrarily high output power (having zero output impedance), always responding without delay to any change in input, as well as being impervious to any other changes in its environment. Some of the parameters commonly used to describe how well any physically realizable op amp approximates this ideal are the following:29 Gain, a measure of the power produced on output for a given power on input; Offset voltage, the non-zero constant error voltage appearing on output when none should appear; Bandwidth, a measure of the range of input frequencies over which useful amplification can be expected -- generally, as input frequencies increase, amplification decreases; Slew rate, a measure of how fast the output responds to changes in input; Output resistance, a limiter of output power; Dynamic range, a measure of the minimum and maximum voltage levels between which the output can be expected to have a linear relation to the input; Power supply rejection ratio, a measure of the extend to which variation (noise) in power supply voltages will appear

in the output.

It should be pointed out that for any real circuit, most of these specifications are dependent upon many environmental and circumstantial conditions, so that, for instance, a single characteristic, such as maximum gain, can be considered at any one of a number of different frequencies, operating temperatures, output loadings, and so on. With such possibilities for qualifying any performance characteristic, it can truly be said that there is no limit to the variety, number, or uniqueness of specifications that can define the objectives of an analog IC design task.

There are many signal processing applications in which the input and output are both analog, suggesting that a completely analog design solution would be the most natural. Nevertheless no such design implementations are ever attempted. Instead, a partly analog, partly digital solution is chosen. The choice of a mixed analog-digital design alternative in situations in which an entirely analog one would seem more natural is usually justified on the basis of the shortcomings of analog circuit technology. The shortcoming most often cited is insufficient signal representation accuracy. However, quite often these shortcomings, especially representation accuracy, are not fundamental to the technology itself, but only describe limitations for the easily developed design possibilities.

For example, for many analog signal processing applications, the only inherent limitations deriving from representation accuracy are those associated with the original input or the output. These limitations would be experienced by any partially digital solution as well. A completely analog solution competitive with a partly digital one would therefore, in principle, be possible to design. However, designing the entirely analog solution would probably be woefully more difficult than designing a partly digital one. Designing the system as a completely analog circuit would require that its behavior be predictable and understandable at the continuous waveform level of detail through out. With a partly digital implementation, this need not be the case.

Thus, even though an analog circuit's function may be a simple one, this is typically the case because the complexity of the circuit's design has limited what could be accomplished using analog IC design methods alone.

## 2.2. Analog IC Design

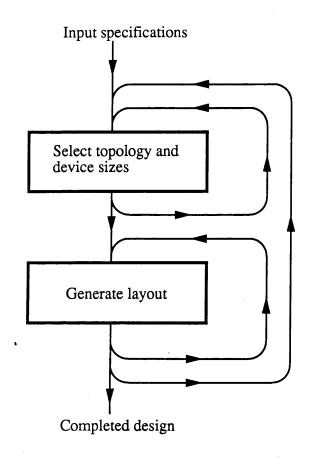

## 2.2.1. Topology and component selection

A circuit's topology is a specification for the connectivity of its components, that is, it defines what is connected to what. It should not be confused with the more geometric layout topology it may acquire if implemented monolithically. Together with a specification of the electrical properties of the components themselves, it very often is the only complete, electrically abstract, constructive definition of an analog IC's intended design. It does not include the arrangement of the components or any physical characteristics of these components that do not have direct electrical significance. For an integrated circuit, these properties would be determined later by the circuit's layout. Conceptually at least, topology and component selection precede layout specification, although in practice, for analog IC design, the two are usually developed in close concert.

Analog circuits intended for monolithic manufacture are more constrained in their design than are circuits that can be constructed from large, discretely fabricated components for several reasons.

First, the smallness of economically viable IC circuits puts limits on the types and values of components that can be utilized. For example, at micron dimensions and audio frequencies, no significant inductances are achievable, hence there can be no inductors in circuits for these applications unless connections are made for them to be provided off chip. Similarly, higher values of resistance and capacitance are generally achieved through larger component size. Thus there is a practical upper limit on the values of resistors and capacitors employable before the economic advantages of microfabrication are exhausted.

The second reason monolithic analog design is more constrained is that analog circuits, as has been noted, are generally very sensitive to the precise values of their components, yet contemporary integrated circuit manufacturing technology does not provide the precision necessary to achieve good value rendition. Where as it is possible to obtain discrete components such as resistors or capacitors with manufacturing tolerances on there electrical properties of as little as one percent, the techniques used to provide many electrical characteristics on an integrated circuit commonly provide tolerances of only about 20 - 30 percent, and sometimes worse.

The third difficulty with monolithic analog IC design is achieving sufficient component and signal

isolation. Although often so assumed in digital IC design, neither the silicon substrate nor even the vacuum above its surface is in reality an ideal insulator. For analog circuitry, components placed proximally often must be treated as electrically coupled, and since every component is of necessity close to the substrate, by extension, every component in a monolithic circuit is to some degree coupled to every other. This often forces the use of circuit topologies (e.g. "double ended" or "fully differential") that are relatively insensitive to some types of coupling. More will be said on component placement and coupling shortly.

Fortunately, because all components on an IC are manufactured simultaneously under identical conditions, monolithic manufacture of electrical components does have one redeeming virtue over discrete manufacture. Although the exact electrical parameters of individual, monolithically manufactured components may vary widely, all parameters of like kind on the same chip tend vary in concert, tracking one another closely. Thus ratios of parameters for devices manufactured monolithically, such as the ratio of capacitances of two capacitors, resistances of two resistors, or gains of two transistors, tend to exceed those that can be easily achieved with discrete components.

Exploiting this advantage while ameliorating the disadvantage of poor absolute tolerances means utilizing circuit topologies that rely less on absolute component values and more on component matching too achieve good performance. This, in fact, is a design practice that is now basic to all analog IC engineering. 18 Monolithic analog circuit topologies are generally chosen so as to be insensitive to individual component values, so long as these values properly track those of other components. Conversely, the ability to achieve precision component ratios is often what is exploited in monolithic analog IC design to achieve precision of operation. Thus, in monolithic analog circuit design, component matching plays a fundamental a role. It influences circuit topology selection and is often the principle limiter on many circuit performance specifications.

Since difficulty of understanding and predicting electrical circuit behavior at a continuous waveform level of detail is the limiting factor on analog circuit function complexity, it is also the principle challenge in analog circuit design. Unlike digital design, where boolean algebra and other simplifying abstractions can be applied with fairly high confidence to logical representations of circuit behavior, in analog circuit design, the models employed for circuit analysis are much more approximate and less encompassing. To

predict or explain the many and varied characteristics of interest in analog circuit design, it is often necessary to make simplifying assumptions that restrict the validity of the conclusions reached. Different models, employing different simplifying assumptions, and thereby having different ranges of validity, are used to predict or explain different characteristics of a circuit's behavior. Because of the limited applicability and reliability of circuit models for analog IC design, this design process is a much more experimental undertaking than is that for digital design.

Much more so in analog design than in digital, the only reliable arbiter of what a circuit will do is the actual circuit itself. Designers of discrete analog circuits rely very heavily on iterative experimentation through breadboarding to develop workable circuits. Due to the high cost and long delay involved in integrated circuit fabrication, monolithic analog designers must rely more on precise numerical simulation, but the methodology is nevertheless very much the same. A tentative design is put together and then tested. performance measures are taken, the design altered, and the cycle repeated until a suitable solution is found. In the end, what design models existed to systemize the search served only as guides, and the reasons for the circuit's exact, final behavior might have never been fully explained or understood.

The precision simulations employed in this search process are usually called SPICE or SPICE-level simulations after a commonly used circuit simulation tool. They are generally very computationally intensive. Thus this sort of cut-and-try development can be very time consuming, even for very small circuits, with only "a few" circuit parameters that must be determined experimentally. Note that this fairly explains the current de facto limitation on analog circuit complexity.

Besides being time consuming, it is also apparent that circuits designed in this way tend to be very fabrication process dependent. Of necessity, such empirical methodologies rely heavily on as many assumptions that can be identified and made as possible. This reduces the amount of search required and increases the likelihood that what is being observed in design is actually how the circuit will behave when manufactured. That is, an analog circuit is most often designed for a specific target fabrication process. Moreover, that one target process is generally characterized in much greater detail than it would be for designing digital circuits. The net result is a circuit that will perform properly when manufactured on the target fabrication process, and

very likely only on that process.

Although the iterative experimentation often continues into physical design and through fabrication as well, at least initially, the result of all these considerations an of all this effort is a specification for the circuit's topology and for each of the devices it contains. Usually the devices have a principle characteristic, for example, resistance for resistors, which is called their size. Transistors usually have two characterists, length and width, also referred to as sizes. Thus component selection is often referred to as device sizing. Similarly, a circuit topology together with component descriptions is often referred to as a sized schematic, even though this phrase more traditionally has referred to a graphical representation (i.e. a drawing) of a circuit topology that indicates device sizes.

# 2.2.2. Analog IC layout<sup>6, 29</sup>

The actual physical form of an integrated circuit is determined by its layout. The layout is a specification of the location, geometric construction, and physical composition (e.g. metal or silicon) of all the components of a circuit and of their interconnections. No more design detail is usually necessary given this geometric definition in order to manufacture the circuit save to indicate which fabrication facility to use. With the addition to the circuit specification of the layout level of design detail, the idealizations of any higher level design abstractions come face to face with the actual characteristics of the physical world. The goals of layout definition are to render the ideal intended behavior of a circuit with sufficient fidelity, and to do so as inexpensively as possible.

For layout purposes, a circuit's ideal behavior is usually defined by a sized schematic, while its cost is typically taken to be its total layout area. Unlike layout of digital circuits, the challenge in physical definition of analog ICs is typically not achieving minimum area, but in keeping the implementation sufficiently close in behavior to that of the specification. Most of the difficulties involved in maintaining adherence to specification can be classified as one of two types, those due to intrinsic discrepancies between the physical and ideal known as parasitics, and those due to uncontrollable operational and process variations.

The terms "parasitics" and "parasitic components" refer to any nonidealities of an electronic circuit's physical implementation that can be modeled as additional components inserted into the intended circuit topology to better approximate

actual behavior. Such additional components alter the circuit's behavior, usually adversely, and therefore they generally must be minimized. The parasitics of primary concern in layout are those due to interconnections or routing. This is because individual device parasitics tend to be more predictable and therefore their effects are usually addressed prior to layout. Whether due to routing or other layout features however, the parasitics influenced by layout are generally of two types, resistive or capacitive.

The nonzero resistance of some routing layers, such as polysilicon and diffusion, can make them unacceptable for use as interconnections in critical areas, even over short distances. For example, a short polysilicon bridge or jumper joining to metal wires separated by a third can hurt performance in some situations. Likewise the resistance of interlayer contacts can sometimes be of concern. Thus in analog layout, routing cannot be considered a matter of just providing the proper connectivity in as little space as possible, as it must also concern itself with the effects of inserting numerous additional resistive electrical "devices" in the form of contacts and poly bridges. Fortunately however, for the most part, resistive parasitics can be adequately avoided by routing primarily in metalization layers, for which resistive parasitics are often negligible.

Of much greater concern are capacitive parasitics, as they are more pervasive, harder to avoid, and frequently more influential, due to their inducement of internodal coupling. Circuit specifications in the form of a sized schematic often assume that each electrical equipotential, i.e. node or net, is electrically isolated from every other (except where indicated by desired component connections), yet in any physical circuit realization, such is not the case. Any two electrical equipotentials in close proximity to each other constitute a capacitor capable of transmitting a time varying electrical signal. The process of translating a sized schematic into a physical layout thus introduces numerous extraneous capacitors that unintentionally couple nets to each other even when they are not directly connected. Unfortunately, at the signal energies, circuit sensitivities, and spacing distances of contemporary analog ICs, the coupling induced by these parasitic capacitances can adversely effect circuit performance, and therefore cannot be neglected.

Controlling the undesirable couplings caused by these extraneous capacitors, which result in "crosstalk" between and "noise injection" within nets carrying time varying signals, is a major challenge in analog IC layout. Unacceptable coupling between nets can result from wires that cross over

one another or that run next to each other for an extended length, as in a routing channel. Signal carrying nets can also be indirectly coupled to each other through non-signal carrying nets. For example, two nodes, each coupled to the same power line by crossovers, can pass interference to each other through this intermediary shunt. The most notorious such intermediary shunt is that of the substrate. Due to the planar nature of IC layout, every electrical IC net is capacitively coupled to the region of the substrate over which it is laid out. The substrate, moreover, is usually a lightly doped semiconductor, not an insulator, and can thus pass signals, albeit with some attenuation, from any net to any other.

To obtain adequate levels of internodal isolation within analog ICs, crossovers of sensitive signal carrying nets must be avoided. Very often sensitive signal carrying nets must be "shielded" from other nets by adequate spacing that is much greater than the minimum possible, and/or by interposition of other less electrically active nets or material. The cumulative layout area of wiring that implements net connections must be monitored as this determines the extent of coupling to the substrate. Routing of far ranging, or extensive nets, such as power lines, must be carefully managed to avoid indirect coupling.

As will be seen in section 3, although not every net must be treated with such extreme care, in most analog IC applications, there are enough nets of such importance throughout the design that the overall layout organization and many layout details are determined by the desire to achieve adequate nodal isolation.

Just as influential, if not more so, in determining layout organization, is control of variations in electrical characteristics due to fluctuations in the manufacturing process and in circuit operation. As has already been described, the most important of these, especially at the layout design stage, is ensuring proper component matching. By the time an analog IC design is ready to be laid out, there are many devices whose matching properties critically influence circuit performance. In fact, circuit topologies for analog ICs are often chosen so that improved performance can be achieved if component matching is extended to parasitics as well. Thus whole subcircuits consisting of many components, interconnections and all their related parasitics may need to match those of other subcircuits for optimal overall circuit behavior.

Good matching, however, depends upon proper physical definition of the circuitry involved. Ulti-

mately, matching is always the result of uniformity in processing. Even within a single chip however, processing variations do exist from point to point. These variations are influenced by the kinds and types of devices being fabricated, and even by the local "environment" of structures close by. Because many of the causes of these variations are poorly understood, for the purpose of analog IC layout, controlling their effects pragmatically reduces, for the most part, to providing as much "sameness," or uniformity in geometric structure as possible. That is, components whose electrical properties should match are given similar if not identical geometric definitions, the same orientation, and placed as close to each other as possible, so as to share as nearly "the same" location as possible, and so on. The need to match parasitics and whole subcircuits results in a desire to achieve sameness in routing and intercomponent spacing as well, so that good analog IC layouts often have a remarkable degree of symmetry, and achieving such symmetry becomes a primary goal of the analog IC layout process.

Very often achieving proper matching is so valuable that it overrides the desire for minimum area or reduced parasitics. For example, extraneous parasitics, such as unnecessary crossovers or perfunctory routing, may be added to some parts of a circuit in order to achieve better matching with other parts where similar parasitics already exist and cannot be removed. It should be noted that although providing proper layout symmetry for matching purposes is usually not hard to achieve in practice, the layouts that display such symmetry are usually markedly different from those that would have resulted had no matching requirements been enforced. In particular, digital layout methodologies that do not consider matching are generally inappropriate for analog layout for this reason.

In addition to tolerances on matching, it is also necessary in laying out an analog circuit to consider variations in the actual values of each device. Although as has been mentioned, absolute tolerancing of monolithic device electrical characteristics is generally so poor that circuit topologies are usually selected to be relatively insensitive to them, no design is ever completely free from absolute device parameter values. Fortunately, absolute device tolerancing primarily involves devices individually, so that techniques for addressing this problem need only concern the relatively simple geometries of individual devices. For example, monolithic capacitors are generally laid out as square rather that oblong rectangles to minimize variations due to edge definition irregularities. Similarly, mask alignment errors can also

cause deviations in device characteristics that can be partially compensated by giving the device a rotationally symmetric layout that is thus insensitive to the direction of mask offset.

Variations in device characteristics due to temperature is an exception to the need to consider absolute device tolerances only individually. Temperature can very from point to point and from time to time across a chip as determined by the location and functioning of various heat producing components. Proper control of device characteristics that vary with temperature thus requires some consideration when laying out a circuit as a whole. Heat producing components, for example, should be placed away from others adversely affected by heat. Sometimes feedback controlled substrate "heaters" must be added to a layout to maintain nearby device temperatures at constant, predictable levels. Device matching is also influenced by temperature, so that thermal gradients often must be included in the symmetrical design of a circuit. Heat related concerns are less frequently mentioned in literature describing CMOS applications, presumably because CMOS circuits are less power hungry, and hence less heat producing, than bipolar circuits, for which concern about heat is more common.

Although process variations and device-tosubstrate parasitics can often be predicted prior to layout, routing and other inter-device parasitics can only be accurately ascertained once a layout has been defined. These, however, as has been noted, can be principle determiners of overall circuit performance, particularly for measures concerning noise. The importance of routing and inter-device parasitics, together with the need for good matching, is what makes layout so influential in the design of analog integrated circuits. Very often topology and component selection must go hand in hand with layout planning. For example, good analog IC designers may consider the actual physical requirements for crossovers or poly bridges when selecting a circuit topology. Or a circuit topology might be selected, and its layout begun when incompatibilities are identified between what can be accomplished physically and what was assumed, prompting modification of the original selection. The latter might occur, for example, after a detailed parasitic extraction of the layout revealed overly optimistic assessments of these quantities. The fact that physical design so extensively influences the overall design of analog circuits and of the design process as a whole often makes it a challenging job even for human designers to say nothing of its automation.

## 3. Automatic Analog Layout Synthesis

The many concerns that must be dealt with in producing a complete layout for an analog or analog-digital IC can be conceptually subdivided into on of five categories. Each category consists of interrelated problems, issues and tasks that are usually considered together or in close concert when a layout is developed. These categories are: chip or system level planning, module assembly, module generation, device generation, and design optimization.

System level planning encompasses problems having to do with the layout of the entire system as a whole, such as overall floorplanning. Although there are many difficulties involved in system level layout of analog ICs for which automation could be applied (see for example (64)), so little has yet been done in the way of automation on the problems in this area that it will prove most convenient to mention them only in passing. Most of the work in design automation concerning system wide issues has been done in conjunction with the more urgent needs of module assembly.

Module assembly and module generation both refer to the integration of geometric layout sections, or cells, into larger ones, but differ in the level of complexity of the subcells being combined. Module assembly deals with the arrangement and interconnection of relatively large, complete cells, usually into the floorplan of the system as a whole, while module generation has to do with the definition of the internal geometry of the more complex cells that are "assembled." As will be more clearly described in section 3.1, the distinction between these two types of component integration derives from a change in concerns as the level of complexity of the cells involved increases. As will be seen, module generation is generally more difficult than module assembly. By far, the greatest concentration of research and development in automatic analog IC layout synthesis has been and will most likely continue to be in module assembly and module generation, as these are the most difficult and time consuming jobs in analog layout synthesis. Accordingly, most of this survey will be devoted to work in these areas.

Device definition refers to the lowest level of electrically significant geometric organization, namely, the graphic design of the fundamental electrical components, such as transistors and capacitors. Like system level layout, device definition is most conveniently covered only in passing. Although proper layout of many varied and often circuit-specific devices found in analog ICs is as critical to correct layout synthesis as is any other part of the

design process, its automation is relatively simple, and is usually performed in conjunction with module generation. Hence an adequate review of the state of the art in automated device definition will result from proper coverage of module generation.

The category of design optimization is somewhat of a catch all. Within it we mean to include not only optimization of the layout by itself, but also that of the design as a whole. It encompasses all activities concerned with managing the operation of separately conducted design tasks so as to produce a design of as high a quality as possible. It therefore includes any type of system-wide design task coordination as well. Automatic optimization of analog IC layout is a relatively new and apparently growing field of development. Although young, due to its obvious value and probable greater extent in the future, an attempt will be made to ascertain the state of the art in this area as well.

Many automatic synthesis tools for analog IC layout address problems within several of these categories simultaneously. Although the issues addressed by any one tool may vary, the individual problems they solve do not. It will therefore prove most expedient to review what has been done in automatic analog IC layout synthesis on a category-by-category basis, rather than by individual tools that have so far been developed.

#### 3.1. Module assembly and floorplanning

Though the diversity of concerns in analog IC layout may be interrelated and complex, they do at least tend to be manageable locally. For instance, the number of components in a collection that must mutually match each other is usually small, and the components themselves usually common to a small subcircuit that can be laid out as a unit. Similarly, many critically sensitive nets connect only a few components, so that the routing of these nets need not be extensive nor difficult to isolate. Consequently; as larger and more complete subdivisions of an analog IC are integrated, the number and criticality of problems tends to decline. There are fewer and less critical sensitive nets to route, fewer matching requirements, and so on. Thermal gradients tend to be more uniform and hence less significant as module dimensions increase as well.

The level of integration at which matching demands have all been dealt with within the modules themselves is particularly significant. Once these demands have been met, the needs for layout symmetry are gone and hence module placement much

less constrained. Also, modules already consisting of several matching components or subcircuits tend to be more uniform in size, or at least more conformable to various uniform heights or widths. The most common modules of this kind are complete op amps and banks of matching devices like capacitors or resistors. Large individual capacitors or resistors that need not necessarily match anything can also be included in this category due to their lack of matching needs and similar size. The task of integrating analog modules having no mutual matching requirements will be called module assembly.

The predominant concern in module assembly is isolation, in all its forms: crosstalk between signal nets, indirect feed-through via power lines, and noise injection from the substrate. Capacitive and resistive parasitics can still be an issue at this integration level as well. The relative simplicity of module assembly makes its automation simpler, permitting, in particular, more general and comprehensive methods to be developed and applied. It also makes the task more like that of digital layout. In fact, as will be seen, most of the tools for automatic analog module assembly developed to date use methods originally devised for digital layout with little and in some cases no modification.

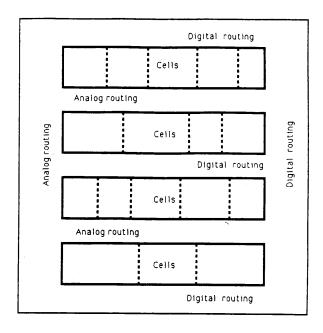

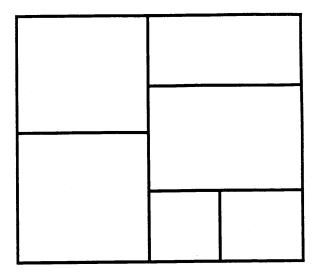

When more than ten or twenty modules are to be assembled, it is usually worth while to first impose some type of structure on their layout as a whole. For layouts involving tens of cells, the most common if not universal structure imposed is that of a "strip architecture." In a strip layout architecture, a common dimension, i.e. length or width, is imposed on the layout of each module (possibly in groups), so that they may be efficiently organized side-by-side into strips, and the strips then stacked into levels with space, "routing channels" being left between the levels for inter-cell connection (see figure 1). The strip architecture is indeed universal in standard cell design practices and there are many tools, primarily developed for standard cell layout, for automating the layout process given this architecture. Although use of fixed libraries of standard cells has been much less successful in analog design as it has in digital, the strip architecture itself is just as pervasive in analog layout as it is in digital.

This naturally has lead to efforts to employ standard cell automation tools and automation methodologies to analog layout. To obtain useful results however, some modifications to these tools have usually been necessary. With digital standard cell module assembly methods, placement of cells typically precedes all routing, with cell arrangement

Figure 1: A strip architecture for analog layout

usually chosen so as to minimize the total length of all interconnect wiring. During placement, cells typically may be flipped, rotated and arranged without regard for net isolation problems that would arise in analog circuitry when the cells were subsequently interconnected. To simplify the task of routing under constraints imposed by crosstalk concerns, for analog layout, two adaptations of digital standard cell floorplanning and placement methods have been tried.

First, the strip architecture has been augmented with the requirement that every other routing channel between strips of cells be exclusively devoted to routing "sensitive" nets, as shown in figure 1.12, 41 Thus each module has access to a channel dedicated to routing sensitive nets on one of its non-abutting sides, and access to a less exclusionary channel on its other side for noiser nets that should be separated from the sensitive ones. This channel segregation scheme is commonly used in manual layout of analog cells. It imposes an additional requirement on the layout of each module in that all external connections to sensitive nets must be made on one and the same side, and all connections to particularly noisy nets must be accessible from the other side. It does not however, restrain the overall cell assembly problem, as all cell arrangements are still routable. Within this structure, extensive power lines are usually routed as noisy nets in the "insensitive" routing channels, or along the edges of either channel as an integral part of the cells themselves.

Net isolation via an alternating channels separation scheme is usually insufficient by itself to guarantee workable analog layout when the modules themselves are only just large enough to address matching concerns as defined above. Current routing algorithms employed within either type of channel are as yet adaptations of relatively simple digital techniques, and there are usually still many intermodule sensitive nets with parasitic and isolation constraints that these routers cannot properly handle. To retain the ability to use simpler (and faster) routing tools where they can be employed, while still ensuring proper treatment of nets that these tools cannot handle, the alternating-channel adaptation is often accompanied by a second adaptation to conventional digital standard cell placement methods. This adaptation is to perform cell placement in an hierarchical fashion. Recall that the more sensitive nets tend to be local to specific subcircuits. Subcircuits containing nets with tight parasitic or isolation tolerances can thus often be clustered together into "polycells" or "macromodules" that can then be placed and routed as a whole. The critical nets internalized by this clustering process need never be seen by the routing or placement mechanisms determining the location and external connections of the cluster as a whole. Thus the higher level placement and routing algorithms can remain relatively simple, while the more arduous inter-cluster placement and routing has been localized and can be accomplished through other means.

When a hierarchical layout strategy is employed, many possibilities for inter-cell placement and routing, as well as for cluster generation itself, are possible. Inter-cluster layout can be performed manually (creating new cells in an analog "standard" cell library), by some modification of a conventional, general automation technique, or by automatic routines specialized for each type of cluster.

As an example of a more general automatic technique, Kimble et al.<sup>42</sup> constrain each cluster to occupy one strip, retain the global cell placement algorithm for inter-cluster cell ordering, and provide additional routing channels within the analog cells themselves for critically sensitive routing. (How inter-cluster routing is accomplished is not described.) They identify the clusters themselves through an analysis of the circuit's net list specification, which hierarchically describes the circuit in terms of subcircuits of various kinds, both analog and digital.

As another example, Winner et al.<sup>85</sup> attempt a completely automated method of both cluster generation and inter-cell placement. They group cells

based on an analysis of net connectivities. Sensitive "summing" nodes are identified in the circuit's schematic and a tree of nets and components emanating from each of these nodes traced out in the net list until all remaining free terminals of each tree connect to insensitive nets. Each tree then constitutes a cluster. A cluster is then laid out in a single strip and routed within a routing channel internal to and dedicated for the cluster. This routing is accomplished by a special purpose algorithm.

As for the use of algorithms specialized for each type of cluster, note that this constitutes module generation. Hence, the hierarchical, poly-cell approach to cell assembly is as much an adaptation of conventional digital place and route methodologies to analog layout where they might not otherwise be applicable as it is an extension of these techniques into the realm of module generation, the topic of section 3.2.

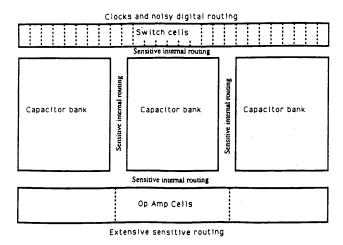

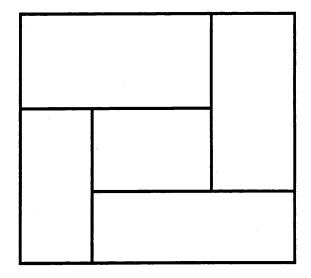

Figure 2 shows an elaboration of the strip architecture of figure 1 that is very commonly used in both manual and automatic layout of switched capacitor circuits. 7-9, 69, 70, 87 Switched capacitor analog circuitry, especially switched capacitor filters, are unusually regular in construction, utilizing somewhat predictable ratios of three types of modules: op amps, banks of matching capacitors, and clock-controlled analog signal switches. This circuit regularity can be exploited to simplify layout with an overall floorplan that is more structured. With the scheme shown in figure 2, a dedicated routing channel for extensive but sensitive nets is placed below a strip exclusively containing op amps cells. This channel corresponds to the "sensitive" routing channel of the more general strip architecture. A routing channel for noisy digital nets corresponding to the earlier "insensitive," channel appears above a strip containing only switches controlled by clocks and other noisy digital nets. Between these two "global" routing channels are two "local" routing channels, one on either side of a median strip of capacitor cells. There are thus three types of strips: those for opamps, those for capacitor banks, and those for switches. Layouts consisting of multiple replications of this three-striptype sequence are built up by alternating the order of the strips, so that outer digital routing channels and outer sensitive routing channels always coincide with their like kind, just as in the general strip architecture.

For this floorplan structure, again, clustering is generally employed and can be derived, just as before, from the circuit's hierarchical definition or from its connectivity. Both of these methods are

Figure 2: A common floorplan for switched capacitor circuits.

usually quite easy to apply for filtering applications. For such applications, typically, each op amp has associated with it a single capacitor bank, and a small collection of switches. These op ampdetermined strip segment triplicates form natural clusters. Additional routing channels are generally placed between each such cluster for its own internal and other routing.87 Such macromodule triplicates are usually treated as a whole in global placement strategies. These strategies may attempt to optimize the circuit by moving the triplicates around driven by traditional optimization criteria, e.g. minimization of total interconnect length. However, for switched capacitor filters, each of these triplicates typically corresponds to one of an ordered series of filter "stages," making their relative placement fairly obvious. Within an individual macromodule triplicate, ordering of switch cells within the switch strip, and arrangement of capacitors within the capacitor bank, is typically driven by routing considerations as will be described shortly. For the specialized but common forms of analog circuitry that can use this second, more specialized strip architecture, these being primarily switched capacitor circuits of various kinds, the difficulties in layout lie mainly in intrastage routing and in low level (e.g. op amp) module synthesis.

The tools for global floorplanning and placement that employ the second, more specific strip architecture are usually themselves particularized for the unusually regular type of circuits that fit this layout structure. As was just noted, they are generally so simple, e.g. being guided by the ordering of stages in a filter's definition, that they gain little attention in the literature. On the other hand, with the more

general first architecture, digital placement tools are often employed for global cell and polycell arrangement. Very often this is the case because the circuit as a whole consists of digital as well as analog cells, and the digital cells are standard cells. It is most convenient in this situation to simply employ a conventional digital standard cell placement tool to arrange all cells, both digital and analog. (The analog cells being preconfigured polycells where necessary.) Smith et al.77 and Gruver et al.51 describe a digital standard cell layout system adapted to accommodate analog cells in this way. Kim et al.41 on the other hand, describes a cell placement algorithm specialized for analog layout. However, except for its use of the first, more general alternatingchannels strip architecture adaptation, it is not materially different from a conventional digital placement tool. The recent review of Berkcan et al., (13), briefly surveys work in floorplanning and placement at the cell assembly level, including a few references to the European literature not covered here.

It is not surprising that simple techniques, either ad hoc or digital, are sufficient for cell placement at the cell assembly level of circuit integration, as this level is generally identified by its suitability for simple placement methods. As was noted in the introduction to this section however, analog cell assembly is not entirely as carefree as that of digital. In analog work, net isolation is still a major concern even for cell assembly. This generally complicates routing. As most crosstalk and parasitics, especially those that are hard to predict prior to layout, are the result of interconnections, net routing is very influential in determining and hence controlling these undesirable side effects of physical circuit realization. Hence routing between even large analog macro or polycells must generally still be carried out somewhat more carefully than it is for digital circuitry.

Routing is affected in several ways by the additional concerns of analog layout at the cell assembly level. To begin, for analog layout, minimization of fundamental capacitive and resistive interconnect parasitics entails reducing the lengths of interconnects. This is much the same as for digital routing. However, for analog layout, this reduction must generally be addressed on a per-net basis rather than for a circuit as a whole. That is, minimizing the sum total interconnect length of all nets as a whole is not a good strategy for optimization in analog layout. Parasitics on some nets are more critical than others, and can vary in importance depending upon their values. For example, a .01 pf increase in a parasitic capacitance may be negligible at some values of the total parasitic, but significant at others, even for the

same net. Also unlike digital routing, sensitivity of some interconnects to resistive parasitics may entirely preclude use of some high-resistivity interconnect layers from routing of some nets. The most important complication of analog interconnect routing, when matching is not required, however, is internet coupling. Ensuring adequate internodal isolation is generally accomplished by arranging for sufficient separation to exist between the nets involved. The separation distances required are generally larger than the minimum spacing rules employed for digital routing. In some cases, a few multiples of a minimum wire width may be entirely adequate, while in others it may be desirable to have the interconnects involved spaced as far apart as possible. Interconnect crossovers are especially notorious for inducing internodal coupling. They must be avoided entirely on some nets while being tolerable but undesirable on many others. All of these concerns make routing of analog macrocells a job distinctly different from that for digital cells.

The first step in automating an analog routing task is usually to impose the restriction that all routing be channel routing, that is, that no routing be permitted over already-occupied areas, even if allowed by the fabrication process. An interconnect placed over existing circuitry of any kind will be capacitively coupled to it. Thus over-module routing is generally avoided in analog layout. Although good analog layout professionals sometimes effectively take advantage of occasional opportunities in analog layout for over-cell routing, due to the difficulty in identifying these opportunities, they have in general not been exploited in automated analog routing. (However, see (22).)

Automatic channel routing is a highly developed technology in digital layout. Although some have attempted to employ automatic unaltered digital channel routing methods for analog layout, 7, 10, 25 for many analog designs, just keeping interconnect off existing layout is generally insufficient to control parasitics and crosstalk at acceptable levels. Therefore, the next step in automating analog routing typically is to impose a classification system on the circuit's nets that will facilitate a more refined treatment of the problem. These classification systems consist of a discrete, finite set of net "types" simple enough to be manipulated automatically, but expressive enough to capture the variety of special nodal uses, treatments, and privileges required for good analog layout. In general, they merely formalize informal net stereotypes commonly used in manual layout. In addition to "sensitive" nets requiring extreme isolation, and "noisy" nets which are particularly harmful, such a classification system may also include "neutral" nets of varies kinds, such as "power" nets (extensive and high current carrying), and "bias" nets (less extensive and/or having lower currents). Any or all of these primary net types are sometimes further appended with such designations as "critical" or "non-critical" (e.g. on sensitive nets), or "digital" or "analog" (e.g. on power nets, which are often segregated as such). A net's type must be assigned prior to layout. Usually this is done manually. (However, see section 3.3.) The purpose of net classification is to provide additional information to an automatic router or other layout tool so that it may better respect internodal isolation concerns where they are important, while at the same time exploiting available layout freedoms where they exist.

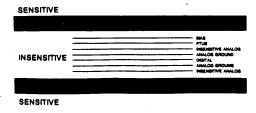

The additional information provided by net typing can be used in a number of ways to effect better analog layout. Its use in channel segregation, that is, assigning specific channels to specific types of nets, has already been discussed, as has its use in module clustering. Kimble et al.,<sup>42</sup> further utilize net typing to segregate tracks within their nonsensitive channels as shown in figure 3.

#### SHIELDING IN INSENSITIVE ROUTING CHANNELS

Figure 3: Net segregation within a channel by type (from (42)).

This scheme takes advantage of the ability of neutral bias and power lines to shield various signal net classes from each other. Another obvious application of net typing is prioritizing the routing process. In its simplest form, prioritization merely determines the order in which nets are considered for routing. Nets routed earlier generally enjoy less restricted routing conditions and can obtain more desirable tracks in the routing channel. Kimble et al.<sup>42</sup> for example, route nets from the edges of the channel inward toward its middle. The higher priority sensitive nets in this system thus experience fewer crossovers, as later through-channel routing is able to avoid them completely by utilizing only the as yet unoccupied portion of the channel near its center.

A higher priority can also mean that a net will be more influential in determining cell placement. Recall that, when employed, module clustering techniques aim to internalize sensitive and/or critical nets. Many systems that employ a clustering technique for net isolation also use routing concerns in defining more specific cell arrangement details within clusters as well. Under the classical switched capacitor floorplan of figure 2, for example, Yaghutiel et al. 87, 88 determine the order of switches within a switch cluster, and the order of capacitors within a capacitor bank, so as to minimize crossovers. Here, net type is used to give crossovers of sensitive nets priority for removal. Barlow et al.8,9 go a step further and classify some sensitive nets as critical. They then identify subclusters of capacitors and switches connected to these critical nets and place them together within their respective strips. Routing within each subcluster, in particular, routing of each subcluster's defining critical net, takes precedence over inter-subcluster routing and is performed first. This method, they claim, nearly always guarantees that the identified critical nets will experience no crossovers.

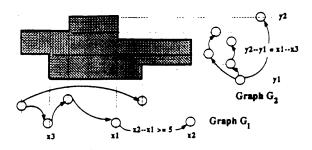

All of the techniques for analog routing described so far have been fairly ad hoc -- they do not make use of any widely recognized, general problem formulation or solution method. The next example represents a departure from this rule. It also anticipates a much larger body of work to be covered in section 3.2 on module generation. This technique makes use of a constraint graph to represent analog related routing restrictions, a structure, as will be seen, that has many uses outside of routing as well.

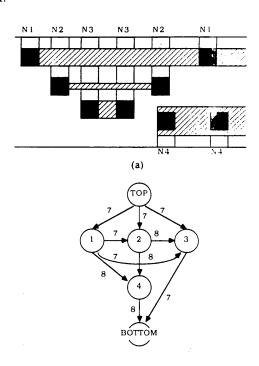

This example is a method of performing detailed channel routing for analog layout. Detailed channel routing concerns the selection of tracks for interconnections within (usually individual  $\mathbf{a}$ elongated) rectangular channel having component connection points along it boundary. Detailed channel routing can be accomplished by applying a standard optimization paradigm in which a constraint graph representing all interconnect restrictions is first constructed and then solved. In this particular application, constraint graph solution means finding an assignment of terminal-to-terminal interconnect segments to channel tracks in such a way as to minimize channel width while at the same time respecting all restrictions represented by and contained within the constraint graph.

Chen and Kuh<sup>20</sup> describe a constraint representation and graph solution method for channel routing of digital circuits. In this scheme, graph nodes represent terminal-to-terminal interconnect segments,

and an edge is placed between two nodes if the corresponding segments must share a common stretch of channel (and hence may influence each others placement). A directed edge between two nodes indicates that one of the corresponding segments must be either above or below the other (as indicated by edge direction). Undirected edges simply convey that the segments cannot coincide. The edges are weighted, with the weight indicating the minimum distance by which the segments must be separated. (See figure 4.) The kinds of routing restrictions that can be represented by constraint graph edges in this way are inherent to all channel routing problems whether analog or digital, as they are a natural result of the overlapping extents of interconnect segments that must be placed within the channel.

Figure 4: A detailed channel routing and its constraint graph (from (30)).

Gyurcsik et al., 30, 38 recognized that net crossovers, layer restrictions and proximity limitations, all important concerns for analog layout, can all be enforced by imposing these simple ordering and spacing constraints on the wires connecting terminals along the edges of a routing channel. What they have done is to add additional edges to the constraint graph, before it is solved, represent these analog layout restrictions. Crossovers are excluded by requiring one of the involved segments to lie above or below the other. To avoid high resistivity routing layers and/or inter-layer contacts along a given interconnect segment, the segment can be constrained to lie on just one layer. This can be accomplished by forcing all other proximal interconnects to either lie above or below the constrained one. Proximity limitations are enforced through proper definition of the weights. Thus by the simple addition of more specific constraints, the same technique described by Chen and Kuh can be used to generate a channel routing plan that minimizes channel width without violating any indicated net crossover or proximity restrictions.

Because this technique does not attempt to reorder the terminals along the channel's boundary, and can space any two nets according to any isolation criteria, it can be applied without the use of a channel segregation or module reordering mechanism. However, it cannot entirely replace them, as for some module placements the constraint graph may not be solvable. If this were the case, some module reordering would be required. Additionally, much waisted area could result if nets requiring substantial separation distances were required to share the same channel rather than being allowed to occupy two widely ones. Nevertheless,  $_{

m this}$ technique represents a definite advance in the application of systematic methods to the often perplexing plethora of concerns in analog routing. Several more examples of methods based on the use of a constraint graph to represent analog layout concerns will be presented in section 3.2.

This last, more elaborate constraint-based analog routing method has apparently not yet been used in any actual design tools or design applications. However, two of the techniques mentioned before it are in fact either in commercial use or competitive with systems that are in such use. The system described by Kimble et al. has been in production use since 1983,42 while Barlow et al. report that their system consistently produces area densities within fifteen percent of intensive hand-packed layout.9 From these reports, one can conclude that sequentially prioritized net routing and routing directed placement schemes, the techniques these systems use, when properly applied, are apparently adequate, at the module assembly level of integration, for many analog IC layout tasks. It can also be observed that all of the routing methods described in this section are based on some digital technique which has been augmented to take into consideration analog routing concerns through use of a simple net classification scheme.

# 3.2. Module and device generation

Although assembly of large fairly complete analog building blocks can be difficult, as was seen in section 3.1, the real challenge in automating analog IC layout is in integration at and just above the device level of component complexity, that is, in properly arranging and interconnecting no more than ten or twenty electrical devices in a compact, performance maximizing way.

There are several reasons why layout at this level of complexity can be difficult. First, it is, of course, still necessary to worry about parasitics and isolation. In fact, a larger proportion of the nets involved usually must be watched for proper isolation. Moreover, because there are fewer components per net, there are more opportunities to implement connections through direct abutment or short, twoterminal routing segments. This makes the difference between good and bad component placements more extreme when it comes to minimizing net parasitics and crosstalk, and thereby puts a premium on proper placement in controlling these adversities. Secondly, placement is complicated by the fact that the components to be integrated, individual devices or small subcircuits, do not, in general, have geometries amenable to any simple layout plan, such as a strip architecture. For individual devices, it is much more the case that form is determined by function. For instance, for small devices, terminal locations and aspect ratios, the ratio of a cell's length to width, can be restricted by performance limitations. A more significant restriction however, is that the area of a cell for a device is usually determined by its electrical specifications. This results in a third complication, as the areas of cells often vary substantially, sometimes by as much as two orders of magnitude or more. This size variation can make efficient utilization of area difficult. Lastly, there is, of course, often the need for symmetrical layout.

The needs for symmetrical layout and the large variations in device sizes virtually preclude adaptation of established general purpose digital synthesis methods to this type of analog layout. Digital layout systems never attempt to match wire dimensions when routing, as would be required for symmetrical layout, and for placement purposes, these methods often idealize all components as being of equal size. Thus analog layout at small levels of integration is fundamentally different from both analog layout at larger levels of module complexity, and digital layout at all levels. In general, it is more difficult than any of these other layout tasks.

Due to the extreme difficulty of low level analog layout, most early attempts at automatic analog layout synthesis concentrated on module assembly, leaving the more exacting internal layout of the cells were to be assembled to manual methods. 42, 51, 77 However, this still left a substantial amount of layout to human effort, as every new analog IC design still required many new analog modules to be laid out. Repeated attempts to develop libraries of widely applicable, general purpose standard cells for analog design, akin to those so successfully employed in digital IC layout, 40, 47, 50, 82 have generally failed. 15, 17 The libraries never seemed to contain a cell close enough to what was required to meet specification. Instead, each new analog circuit design generally entailed adding new "standard" cells to the library, cells that would inevitably end up only being used within that original application.<sup>17</sup> It is not hard to see why this might be the case. The most important details distinguishing any two analog circuits are at the device and small subcircuit level. Indeed, the use of general purpose circuit topologies that can be easily adapted to different uses through device sizing alone is, in fact, a common practice in filter design. 27, 54 Thus it is not uncommon for analog circuitry of considerable functional diversity to differ in construction only in the specifications for the devices used. Hence, the only fixed cells that have found truly wide application in analog layout have been those whose internal device sizes do not significantly determine circuit function, such as digitally controlled analog signal switches.

#### 3.2.1. Procedural methods

What has proved much more successful at accelerating low level analog layout than attempting to maintain libraries of reusable but individually designed standard cells, has been the use of parameterized cell generators. These are computer programs or subroutines that accept a handful of circuit specifications as input and produce as output a layout for a specific device or circuit that meets the given specifications. Because it relies on conventional procedural programming practices, use of parameterized cell generators is also referred to as procedural specification. Usually, the input parameters of a cell generator correspond very closely to geometric characteristics of the desired layout, such as device sizes. If the generator is to produce a multi-device circuit, usually the circuit's topology and floorplan are largely fixed.

Although developing a computer procedure for generating a certain class of layouts is generally more

difficult than directly implementing any one of its possible outputs by hand, unlike analog "standard" cells, analog "standard generators" have proven genuinely reusable. In fact, due to the importance of precise device sizing in analog IC design, as well as to the relative simplicity of device geometric forms, cell generators for individual circuit devices have been employed in analog layout for years and are now quite common.

Allen et al.2-5, 75 pioneered the use of direct procedural layout specification for multi-device analog layout, but writing computer procedures to automatically generate complex circuit layout did not become popular in analog design until this layout description method had become more widely used in IC design automation in general, particularly, not until digital IC layout had become so complex that procedural methods were needed for its automation as well. Once this occurred, many programming tools specialized for IC layout became available that could be used or easily adapted for analog layout. In particular, compilers for special purpose programming languages were developed specifically for procedural layout specification. These languages, for instance, made recurring operations in layout specification, such as component placement by relative positioning (e.g. above, right-of) and interconnect path definition easier and simpler to describe. Kuhn<sup>46</sup> describes the use of a special purpose layout language for analog layout. (See figure 5.)

Figure 5: A sample layout and its procedural specification (from (46)).

Since parameterized cell definition is based on contemporary computer programming methodology, it is in principle completely general and capable of being applied to any layout task large or small. Automatic generation of layout from procedural specification is often referred to as silicon compilation. Use of such methods is in fact growing in both digital and analog layout automation. Both Kuhn, 46 and Helms and Russel<sup>32</sup> describe very highly developed silicon compiler systems for analog layout. The Concorde system<sup>32, 33</sup> for example, contains a library of generators for complete A/D and D/A converters, for switched capacitor filters, and for all the principle components of these circuits, such as op amps. It is claimed that these systems produce modules with performance comparable to hand crafted design.34

Procedural layout specification has not proved to be a panacea for analog layout however, as it merely trades one type of complexity for another. Programs for generating special purpose cells are many times more difficult to develop than any one of the circuits they produce would be. Moreover, the disparity between the two levels of development difficulty grows exponentially with the complexity of the circuit under consideration. Hence, in general, it is only economically justifiable to develop procedural specifications for very simple layouts, such as those for individual devices, for highly regular layouts, such as those often found in switched capacitor filter designs, 7, 69, 70 and for other complex circuitry only when it is expected that the generators developed will be very highly used.

### 3.2.2. Template based methods

of the reasons procedural layout specification is so difficult is that it requires the layout to be described in every detail all at once. It is difficult with procedural specification, as with any other programming task, to operationally describe a high level or abstract general plan without including along with it many of the incidental low level particulars that would make the plan into a complete design. It is also not possible with conventional programming methods to describe the details without specifying an often irrelevant order for their addition to the design. Thus for IC layout, detailed, sequential, step-by-step construction commands can be an awkward, inefficient way to declare what is in fact a static object. This is especially true when the design conforms to a large number of uniformly applicable constraints, that would thus have to be repetitively checked or enforced throughout the specification. Yet integrated circuits, do conform to a large number