# UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

### Title

Performance-driven Analysis and Optimization in the Emerging System Architecture Communication Paradigms

**Permalink** https://escholarship.org/uc/item/8vb1s8zz

**Author** Zhang, Zhizhou

Publication Date 2022

Peer reviewed|Thesis/dissertation

University of California Santa Barbara

# Performance-driven Analysis and Optimization in the Emerging System Architecture Communication Paradigms

A dissertation submitted in partial satisfaction of the requirements for the degree

> Doctor of Philosophy in Computer Science

> > by

#### Zhizhou Zhang

Committee in charge:

Professor Timothy Sherwood, Chair Professor Jonathan Balkind Professor Yu Feng Milind Chabbi, Ph.D., Uber

December 2022

The Dissertation of Zhizhou Zhang is approved.

Professor Jonathan Balkind

Professor Yu Feng

Milind Chabbi, Ph.D., Uber

Professor Timothy Sherwood, Committee Chair

December 2022

# Performance-driven Analysis and Optimization in the Emerging System Architecture Communication Paradigms

Copyright  $\bigodot$  2022

by

Zhizhou Zhang

To my family.

#### Acknowledgements

I would like to express my deepest gratitude to my advisor, Professor Timothy Sherwood, for providing me with guidance, encouragement, and support throughout my Ph.D. journey. His unwavering support, encouragement, and insights have been invaluable in the completion of this dissertation. I learned tremendously from him in both academic research and beyond.

I would also like to thank the committee members, Professor Jonathan Balkind, Professor Yu Feng, and Dr. Milind Chabbi, for their time, expertise, and constructive feedback throughout my research. I enjoy and appreciate collaboration and discussion with Jon, teaching and feedback from Yu, and mentoring from Milind.

In addition, I would like to extend my sincere thanks to the following:

To all labmates and friends in UCSB ArchLab, CS Department, my collaborators at Uber, and my coauthors at the University of Rochester. Special thanks to Jeremy Lau, Deeksha Dangwal, Georgios Tzimpragos, Alvin Glova, Jennifer Volk, and Rhys Gretsch of ArchLab for the amazing experience. To Professor Yufei Ding, Yuke Wang, and Boyuan Feng of UCSB for the warm welcome and inspiring learning. To Adam Welc, Murali Krishna Ramanathan, Prithvi Raj, and Abhishek Parwal of Uber for the great collaboration. To Chen Ding, Sandhya Dwarkadas, Chencheng Ye, Sayak Chakraborti, and Noah Bertram of the University of Rochester for your fascinating cooperation. Special thanks to Chen, who inspires me in the research and Ph.D. program and is always willing to help. To my parents Minxing Zhang and Xiaoyuan Zhang for the enormous help to achieve this milestone.

Last, to my beloved partner, Wei Jin, for the continuous support, encouragement, and tutoring along this journey.

Thank you all.

### Curriculum Vitæ Zhizhou Zhang

#### Education

| 2022 | Ph.D. in Computer Science, University of California, Santa Barbara. |

|------|---------------------------------------------------------------------|

| 2021 | M.S in Computer Science, University of California, Santa Barbara.   |

| 2018 | B.S. in Computer Science, University of Rochester.                  |

#### Publications

[6] **Zhizhou Zhang**, Alvin Glova, Timothy Sherwood, and Jonathan Balkind. A Prediction System Service. ASPLOS 2023.

[5] Alvin Oliver Glova, Yukai Yang, Yiyao Wan, **Zhizhou Zhang**, George Michelogiannakis, Jonathan Balkind, and Timothy Sherwood. Establishing Cooperative Computation with Hardware Embassies. SEED 2022.

[4] **Zhizhou Zhang**, Murali Krishna Ramanathan, Prithvi Raj, Abhishek Parwal, Timothy Sherwood, and Milind Chabbi. Critical Path Analysis of Large-scale Microservice Architectures. ATC 2022.

[3] Deeksha Dangwal, **Zhizhou Zhang**, Jedidiah R Crandall, and Timothy Sherwood. Context-Aware Privacy-Optimizing Address Tracing. SEED 2021.

[2] **Zhizhou Zhang**, Milind Chabbi, Adam Welc, and Timothy Sherwood. Optimistic Concurrency Control for Real-world Go Programs. ATC 2021.

[1] **Zhizhou Zhang**, Chencheng Ye, Rahman Lavaee, Ning Gu, and Chen Ding. Finegrained data usage analysis by access sampling: seeing the data that is not there. MEM-SYS 2018.

#### Abstract

## Performance-driven Analysis and Optimization in the Emerging System Architecture Communication Paradigms

by

#### Zhizhou Zhang

Computation is increasingly complex, and our languages, systems, and design practices are changing to meet that shifting reality. That shift comes also with new challenges in debugging and optimization. In this thesis, we demonstrate that by adopting performance-driven analysis and optimization around communication paradigms, we are able to facilitate the development process and improve the performance of the programs. Specifically, we show such improvements in improving the synchronization mechanism in Golang by Hardware Transactional Memory (HTM), Critical Path Analysis (CPA) of Remote Procedure Call (RPC), and optimizing programs by novel service of prediction at Operating System (OS) level.

# Contents

| Cι  | ırriculum Vitae                                                                                                                                                                | vi                                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Ał  | ostract                                                                                                                                                                        | vii                                                 |

| Li  | st of Figures                                                                                                                                                                  | x                                                   |

| Lis | st of Tables                                                                                                                                                                   | xii                                                 |

| 1   | Introduction                                                                                                                                                                   | 1                                                   |

| 2   | Optimistic Concurrency Control for Real-world Go Programs<br>2.1 Introduction                                                                                                  | <b>10</b><br>10                                     |

|     | 2.2       Challenges                                                                                                                                                           | 13<br>16                                            |

|     | 2.4Gocc Overview                                                                                                                                                               | 17<br>19<br>43                                      |

|     | 2.7 Conclusions                                                                                                                                                                | 49                                                  |

| 3   | A Prediction System Service3.1 Introduction3.2 Prediction as a Service3.3 Design and Implementation of a PSS3.4 Use-Case Scenarios3.5 Evaluation3.6 Related Work3.7 Conclusion | <b>52</b><br>55<br>55<br>57<br>62<br>70<br>77<br>79 |

| 4   | CRISP: Critical Path Analysis of Large-Scale Microservice Architec-                                                                                                            | -<br>81                                             |

|     | tures         4.1 Introduction         4.2 Motivating Example for CRISP                                                                                                        | 81<br>81<br>85                                      |

|          | 4.3            | Background                  | 87  |  |  |

|----------|----------------|-----------------------------|-----|--|--|

|          | 4.4            | CRISP Methodology           | 90  |  |  |

|          | 4.5            | Critical Path Analysis      | 92  |  |  |

|          | 4.6            | CRISP Features              | 100 |  |  |

|          | 4.7            | Experience and Evaluation   | 106 |  |  |

|          | 4.8            | Related Work                | 116 |  |  |

|          | 4.9            | Conclusions and Future Work | 118 |  |  |

| <b>5</b> | Con            | clusion                     | 119 |  |  |

| Bi       | Bibliography 1 |                             |     |  |  |

# List of Figures

| 2.1 GOCC schematic diagram.                                                                                                                         | 14 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 Lock examples. $\ldots$                                                                                                                         | 24 |

| 2.3 a.Lock() is Downward Exposed                                                                                                                    | 25 |

| 2.4 c.Unlock() is not Upward Exposed.                                                                                                               | 25 |

| 2.5 Region dominated by lock and post-dominated by unlock.                                                                                          | 25 |

| 2.6 Example of AST transformation                                                                                                                   | 36 |

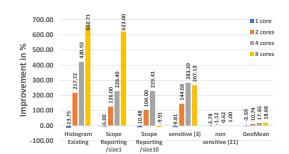

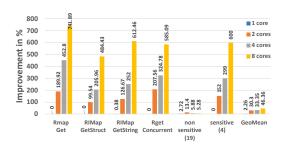

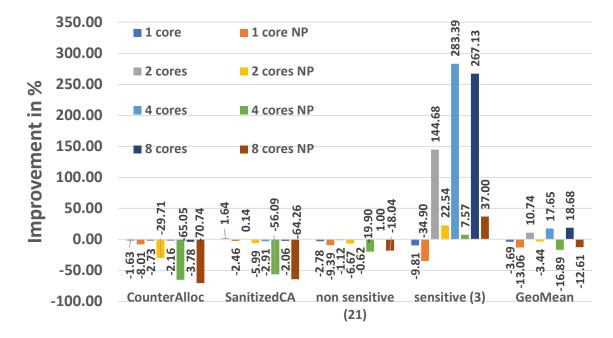

| 2.7 Results on Tally with different core numbers                                                                                                    | 45 |

| 2.8 Results on go-cache                                                                                                                             | 45 |

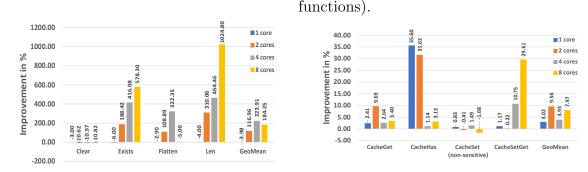

| 2.9 Results on concurrent set                                                                                                                       | 45 |

| 2.10 Results on fastcache                                                                                                                           | 45 |

| 2.11 Results on Tally                                                                                                                               | 50 |

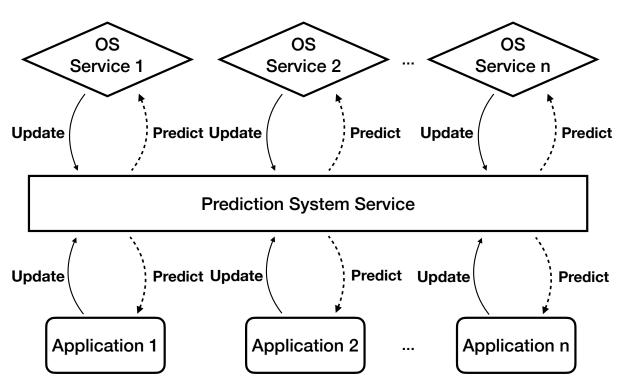

| 3.1 Design of Prediction System Service                                                                                                             | 58 |

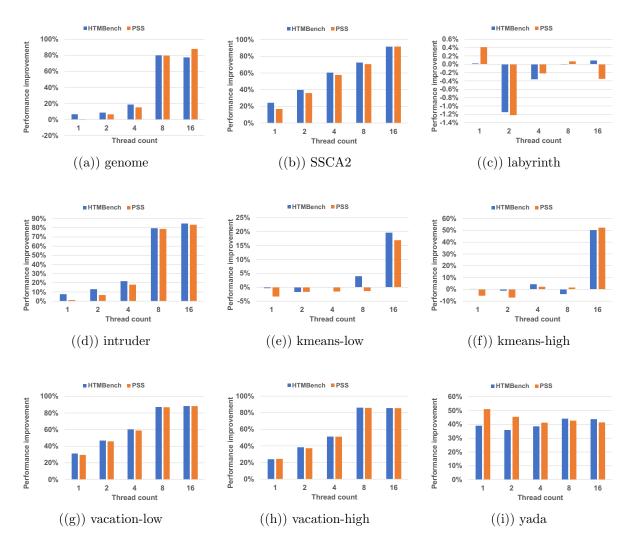

| 3.2 Performance of HTMBench and PSS HLE normalised to vanilla STAMP.                                                                                | 71 |

| $((a)) genome \ldots \ldots$ | 71 |

| $((b)) SSCA2 \ldots \ldots$  | 71 |

| $((c))$ labyrinth $\ldots$                                                                                                                          | 71 |

| $((d))$ intruder $\ldots$                                          | 71 |

| $((e))$ kmeans-low $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                     | 71 |

| $((f))$ kmeans-high $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                           | 71 |

| $((g))$ vacation-low $\ldots \ldots \ldots$       | 71 |

| $((h))$ vacation-high $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                | 71 |

| $((i))$ yada $\ldots$                                              | 71 |

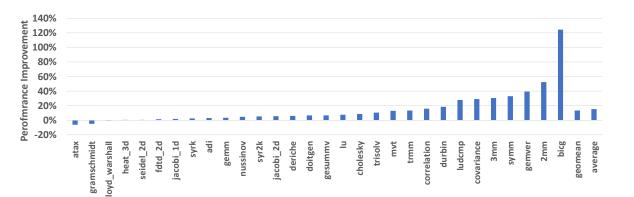

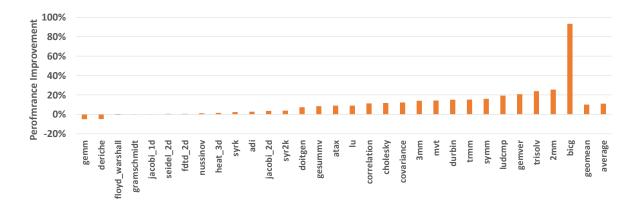

| 3.3 Performance improvement of PSS with 20 iterations on PolyBenchPython                                                                            | 72 |

| 3.4 Performance improvement of PSS with 50 iterations on PolyBenchPython                                                                            | 73 |

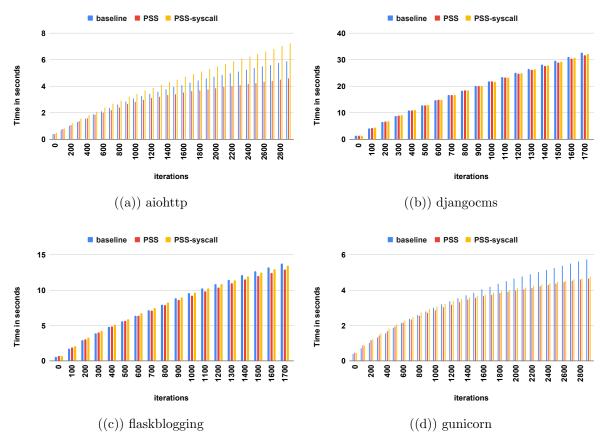

| 3.5 Result of macrobenchmarks                                                                                                                       | 74 |

| $((a))$ aiohttp $\ldots$                                           | 74 |

| ((b)) djangocms                                                                                                                                     | 74 |

| ((c)) flaskblogging                                                                                                                                 | 74 |

| ((d)) gunicorn                                                                                                                                      | 74 |

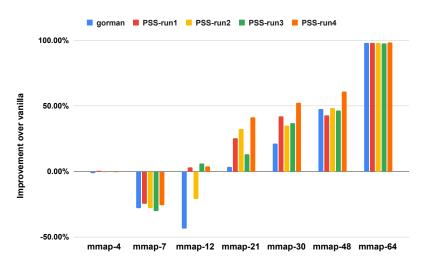

| 3.6 Average latency of MMTests                                                                                                                      | 76 |

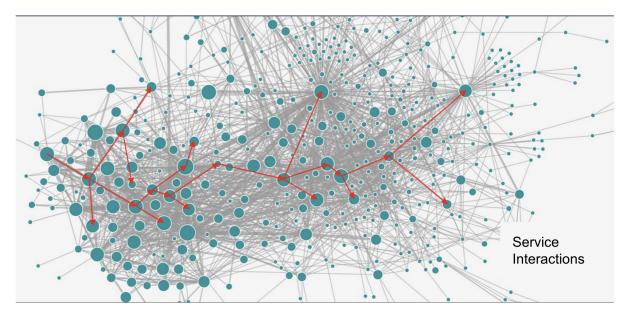

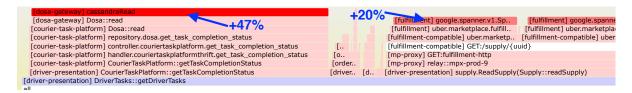

| Complex microservice RPC call graph at Uber collected via Jaeger tracing.   | 82                                       |

|-----------------------------------------------------------------------------|------------------------------------------|

| Critical path(s) of createOrder endpoint                                    | 84                                       |

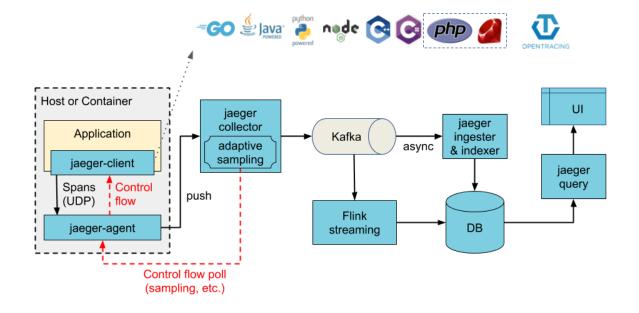

| Jaeger deployment at Uber.                                                  | 89                                       |

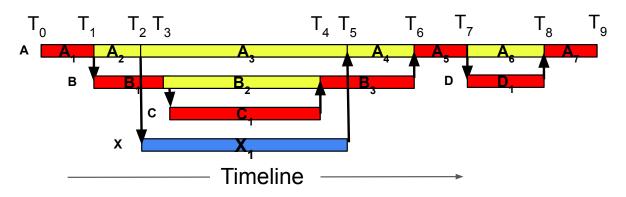

| Critical path on example spans and trace                                    | 94                                       |

| Data representation conversion                                              | 95                                       |

| Normal trace                                                                | 96                                       |

| Clock-skewed trace                                                          | 96                                       |

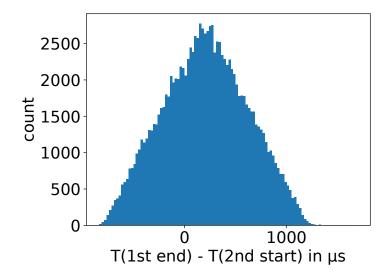

| Distribution of time-skew on real traces                                    | 97                                       |

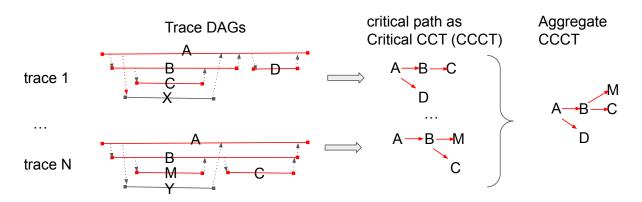

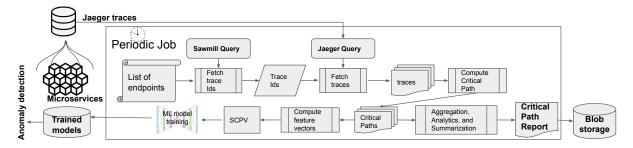

| Schematic diagram of CPA over Jaeger traces                                 | 99                                       |

| Example heat map from 1000 traces.                                          | 101                                      |

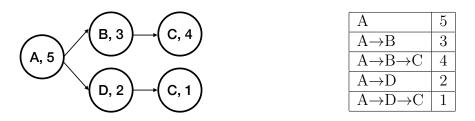

| An example CCCT                                                             | 103                                      |

| Differential flame graph for the getDriverTask                              | 104                                      |

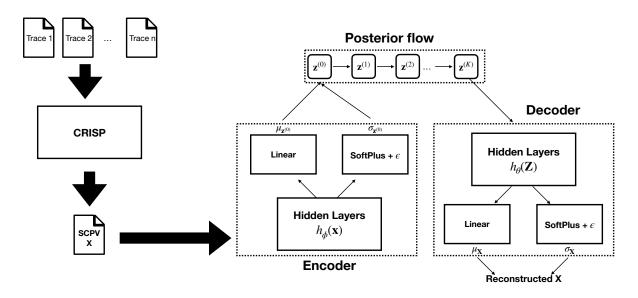

| Architecture of neural network for anomaly detection                        | 104                                      |

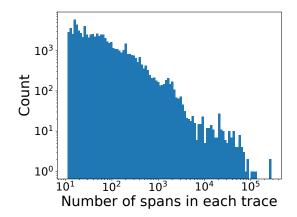

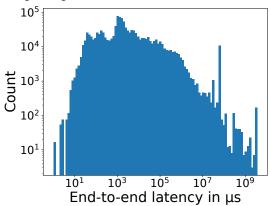

| Histogram of the number of spans per trace                                  | 108                                      |

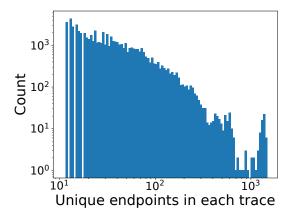

| Histogram of number of unique endpoints per trace                           | 108                                      |

| Distribution of latency among all traces.                                   | 108                                      |

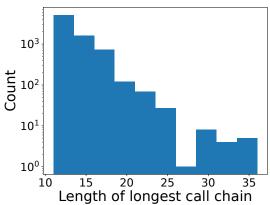

| Histogram of longest call chain per trace                                   | 108                                      |

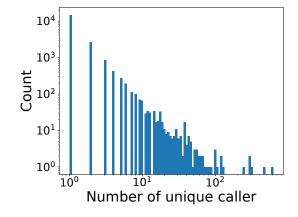

| Histogram of the number of unique caller for each endpoint                  | 109                                      |

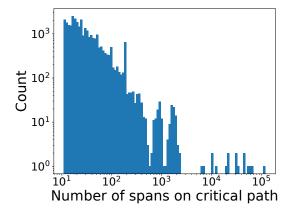

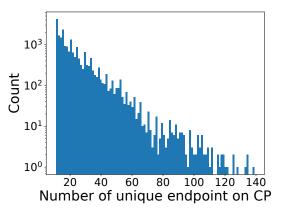

| Histogram of the number of spans on the critical path per trace             | 109                                      |

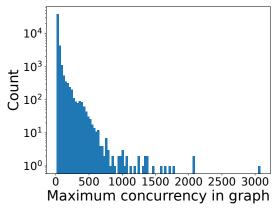

| Histogram of the degree of the concurrency per trace                        | 109                                      |

| Histogram of the number of unique endpoints on the critical path per trace. | 109                                      |

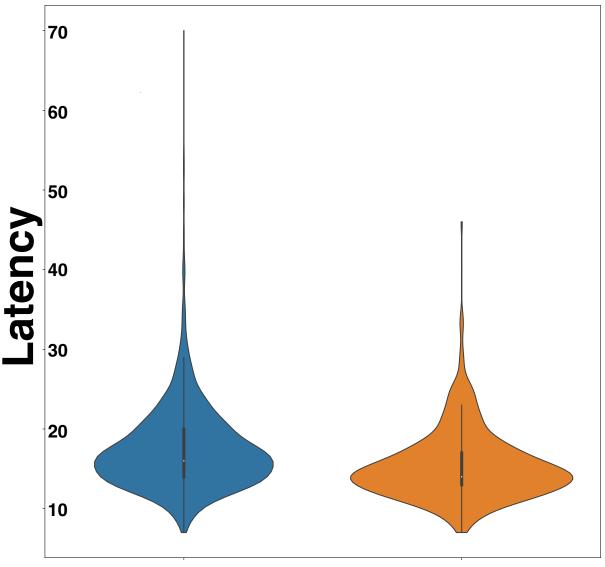

| Violin plot                                                                 | 115                                      |

|                                                                             | Critical path(s) of createOrder endpoint |

# List of Tables

| 2.1 | Go package characteristics and their behavior using GOCC | 41 |

|-----|----------------------------------------------------------|----|

|     | List of selected PyPy JIT parameters                     |    |

|     | Overhead of top-down analysis of getDriverTasks          |    |

# Chapter 1

# Introduction

There are increasing amounts of data generated every year and more computing power is needed to process the data. To meet the raising requirement of the computation, simply stacking more cores or machines is not enough. Each machine has physical limitations and many of the computations are not easily scalable. Instead, more novel programming languages, specialized tools and libraries, and new system architectures designs have been developed to provide fast and effective support for demanding computation.

For instance, new programming languages like Rust, Go, and Swift are developed since they can provide better support for concurrent programming, garbage collection, modularity, and scalability. Such new features help programmers develop, debug, and maintain more complex applications dramatically. At the same time, machine learning is more widely applied to optimize the performance of complicated programs. The strong capability of machine learning is able to find out solutions that easily outperform human experts in many scenarios. For application development, microservice designs are gradually more popular in the industry and the modern data center. Compared with the traditional monolithic design, microservices are noticeably superior in modularity, scalability, and deployability. However, the shift comes also with new challenges because of the complexity. Specifically many of the features like concurrent programming are error-prone, machine learning methods are known for their indescribability, and microservices architecture is infamous to debug and optimize due to the extreme complexity. We will break down the detailed challenges of the new systems and tools below.

#### 1.0.1 Concurrent programming

Golang [1] is one of the most representative new programming languages that has gained substantial popularity recently. It has a wide application range including both enterprise software [2] and open-source applications including Kubernetes [3] and libraries [4]. One of the reasons Go is popular is that Go has many syntax similarities to C, which is prevalent to many developers already. But unlike C, Go supports concurrency as a first-class language component. Specifically, Go provides straightforward and easy-to-use features for concurrent programming — any functions in Go can be scheduled to run concurrently by simply prefixing the function call with the **go** keyword.

Although such a feature makes writing concurrent programs much easier in Go, programmers still need to explicitly manage the interaction between concurrently running code. Normally there are two ways for the management: via passing messages through channels [1] or explicitly synchronization control to the shared memory. In reality, the latter approach is more widely used by developers. Among different synchronization access control mechanisms, mutual exclusion via lock [5] is still the most prevalent way by developers due to its simplicity [6].

However, it is well-known that locks can slow down the program by unnecessarily serializing the concurrent execution, even if there is no shared memory accessed by concurrently running code. There are many studies from the past in order to boost the lock-based program execution. One of the noticeable solutions to locks is *transactional* memory (TM) [7]. Unlike lock, TM allows multiple pieces of code to be executed concurrently and speculatively. If there is a *conflict* [8] detected, i.e. more than two pieces of code touch the same memory and at least one of them is a memory write, at least one piece of code will be *rolled back* and restart the computation. Otherwise, all executions can proceed in parallel if no conflict has been detected.

TM is originally supported in software as STM [9, 10, 11, 12] and later available in commodity hardware as Hardware Transactional Memory (HTM), including IBM, Intel, and Arm [13, 14, 15]. However, despite the invention and research of TM over three decades, the real-world application of TM to accelerate software has not gone too far. There are several reasons that can potentially cause the gap.

One possible reason is that a lot of TM works from the past focused on designing and implementing TM algorithms but only measuring the performance on synthetic benchmarks (e.g., STMBench [16]) or evaluating selected concurrent data structures. When it comes to the real-life applications [9, 17], TM was not able to generate convincing performance.

Therefore, how to utilize the existing HTM techniques to boost real-world programs, specifically in Go because of its concurrency-first philosophy, is an unsolved but worthwhile challenge.

#### **1.0.2** Runtime Optimization

The runtime optimization problem is a set of challenges faced by developers frequently. Consider when capable performance programmers find out the business-critical application is running slowly but there is no obvious cause, normally they need to navigate the potential optimization spaces for the trade-offs. However, the potential optimization spaces can be huge, and quite often it is difficult to make the decisions right away. For instance, is it faster to run the code with Mutex lock as explicit synchronization control than wrapping it optimistically in a transaction via TM? Should certain functions be inlined or compiled with different optimization levels? To answer the questions mentioned above needs to balance a set of constraints. As our applications, system, and hardware grow complicated, it is harder to characterize and understand all potential parameters in the decision-making process, and even more difficult to find out an ideal solution using ad-hoc heuristics.

Luckily, machine learning has proved a good fit to navigate the complex optimization space and find out a good solution. The use case of machine learning approaches is not limited to optimizing data structures [18], implementing state-of-the-art recommendation systems [19], learning the structure and optimal access of the database [20], and improving anomaly detection [21]. For another case of TVM [22], machine learning is able to produce computing kernels that significantly outperform the design from human optimizers'.

Such a style of optimization is becoming more and more common in the past several years and it makes little sense for each application to use its own internal ML framework for parameter runtime optimization, where it elides the opportunities for sharing of memory or exploiting common hardware resources.

On the other hand, many of the works mentioned above utilize complex machinelearning models. Although they are capable to generate performant solutions, the high cost of the training and inference hinders a broader application, especially when the target itself is relatively simple. An ideal model should be able to generate accurate results with relatively low latency.

Therefore, it is time to consider what type of new *abstractions* is necessary to facilitate broader use of this important style of the runtime optimization problem and how to provide low-cost but good quality results for runtime optimization.

#### 1.0.3 Microservices

Microservice architectures [23, 24, 25, 26, 27, 28, 29] have become the cornerstone of modern service-oriented software systems. Unlike monolithic software development and deployment, the microservice environment breaks down the business logic into individually deployable programs. Such an approach allows fast development and scalable deployment. Between the microservices, individual *instances* interact with each other via remote procedure calls (RPCs). As the business grows larger, microservices increase in number, and the interaction becomes much more complex. In addition, the RPCs are often deeply nested, asynchronous, and hierarchical, which makes it extremely difficult to identify the source of the problems. However, understanding microservices of the business-critical request and how to optimize them is very important for developers.

We can consider Uber's backend as an example of microservice architecture. There are around  $\sim 4,000$  microservices interacting with each other via RPCs. What is more, each microservice hosts several APIs. In total, there are more than 40,000 unique RPC endpoints that can call each other in complex ways.

When a service request arrives at an entry point API to the backend system, it needs multiple "hops" through many RPCs before being fully serviced. The interactions are also asynchronous, deeply nested, and can invoke multiple other downstream APIs. As a result, it is extremely hard to identify which service(s) contribute to the overall end-toend latency when top-level request performance degradation is detected [30, 31, 32, 33, 34, 35, 36]. The answer to the question is very important in many scenarios, including

- Identifying potential opportunities to optimize top-level microservice

- Spotting bottleneck APIs that affect other endpoints

- Setting appropriate time-to-live threshold for RPCs

- Diagnosing error and outages conditions

• Advising for computing and other datacenter management

Therefore, certain analysis is needed for better microservice architecture at the datacenter scale.

#### **1.0.4** Commonality of the Challenges

Although the three cases mentioned above are quite different in terms of the exact reasons for the challenge, they share certain commonalities if we examine them carefully.

The fundamental challenge for the three cases is around communication paradigms. Hardware lock elision (HLE) is focused on the synchronization mechanism between different cores or threads. How to utilize different communication schemes including transactions and Mutex locks is the region of interest. Meanwhile, the key to solving runtime optimization problems using machine learning is to find the proper abstraction of the fundamental machine learning services and provide efficient implementation at the right location accordingly. The communication paradigm is crucial to consider when we need to design a component that allows Operating System (OS) to communicate with user-level applications efficiently. Last but not least, communication paradigms are the cornerstone of Remote Procedure Calls (RPCs), which implement the microservices at the datacenter. In order to analyze the microservices well, it is required to understand the nature of the RPCs and come up with appropriate tools.

In terms of how to solve these challenges, we propose to use performance-driven analysis and optimization. The challenges are from real-world applications with specific performance requirements. They are also complex and dynamic in nature, hence performance-driven analysis and optimization is one of the best-fitting methodologies.

Therefore, we present the thesis statement below after observing those commonalities.

#### Thesis Statement

In this thesis, we demonstrate that by adopting performance-driven analysis and optimization around communication paradigms, we are able to facilitate the development process and improve the performance of the programs. Specifically, we show such techniques in improving the synchronization mechanism in Golang by Hardware Transactional Memory (HTM), optimizing programs by novel service of prediction at the Operating System (OS) level, and analyzing the complex system within a datacenter by Critical Path Analysis (CPA) of Remote Procedure Call (RPC).

For synchronization mechanism improvement in Golang, we propose a framework, named GoCC, to utilize Hardware Transactional Memory to speed up certain Mutex locks. The framework identifies Mutex locks from the source file, analyzes the valid replacement candidates, rewrites the code with HTM automatically, and provides an efficient runtime library. The analysis includes detailed and thorough static analysis at the intermediate representation (IR) level so that the transformation from Mutex locks to HTM is always safe and valid. The runtime library contains a lightweight controller that can choose HTM or Mutex locks efficiently and effectively at runtime.

For prediction system service (PSS), we propose a new system-level service that can provide a simple but effective prediction inspired by GoCC. The prediction can be shared among different applications and tasks at both the user level and kernel level. The prediction-based mechanism is particularly helpful for certain types of runtime optimization problems. By effectively and efficiently guiding the decision at the runtime, PSS is able to improve the performance of applications in different fields.

For microservices at datacenter scale, we adopt critical path analysis (CPA) on the sampled trace to pinpoint the top contributor to the end-to-end latency. We built a tool named CRISP to extract the critical path from the collected trace at Uber and developed tools to help programmers debug the service. CRISP also enhances anomaly detection by reducing training and inferencing time and improving model accuracy.

In summary, we adopted performance-driven analysis and optimization around communication paradigms for emerging programs and systems. We believe such an approach is able to further help developers optimize and debug complex applications.

The structure of the rest of the thesis follows:

- In Chapter 2, we study on how to accelerate Mutex lock with Hardware Transactional Memory (HTM) in Golang. We propose a framework named GoCC that is able to identify, analyze, and replace the Mutex with HTM in the given Golang source code. The procedure in the framework is sound, automatic, and efficient. With the help of a newly designed runtime controller, GoCC is able to speed up Golang programs with limited downside.

- In Chapter 3, we show how to solve several dynamic optimization problems with a novel prediction system service (PSS). PSS is able to provide a cheap but efficient prediction mechanism for a variety of tasks at both user-level and kernel-level and allows model updates based on the correctness of the prediction. To validate the broad applicability of PSS, we apply it in three different scenarios: Hardware Lock Elision (HLE), parameter tuning for Just-In-Time (JIT) compiler, and page reclaim of memory management in Operating System.

- In Chapter 4, we illustrate how to perform critical path analysis (CPA) on the microservice traces and enable better debugging and optimization abilities for the developers. We build a tool named CRISP, which is able to provide several popular tools for debugging, including flamegraph and heatmap. CRISP can also offer significant speedup for anomaly detection and improve prediction accuracy notice-ably. Besides, CRISP can also guide the hardware selection given the emerging

microservice workload.

# Chapter 2

# Optimistic Concurrency Control for Real-world Go Programs

## 2.1 Introduction

Golang [1] (or simply Go) is a modern programming language that has gained significant popularity over the last decade. It is being used to write enterprise software [2] (e.g., to implement backend services) in some of the largest technology companies as well as to develop large and widely used open-source applications (e.g., Kubernetes [3]) and libraries (e.g., Tally [4]). The design of Go is inspired by C, but unlike C, it supports concurrency as a first-class language construct. Even more importantly, and unlike other popular languages with first-class concurrency support (e.g., Java), the Go language goes to great lengths to simplify concurrent programming by making concurrency easy to use (and thus frequently used) by the developers [6] — any function in Go can be scheduled to execute concurrently with the rest of the code as a *goroutine* [1] by simply prefixing its call with the **go** keyword.

Although Go makes writing concurrent programs easier, it still requires programmers

to manage interactions between concurrently executing code — this can be accomplished either via passing messages through channels [1] or explicitly synchronizing accesses to shared memory. Shared memory is used more often than message passing by Go developers, and mutual exclusion via locks [5] remains the most widely-used synchronization mechanism across several applications [6]. It is, therefore, the focus of our work.

Locks may unnecessarily serialize concurrent execution, even if the code operates on disjoint data. Our work aims to improve the performance of concurrent Go code, particularly code hiding behind needlessly held locks. Our goal is to accomplish this while retaining the correctness of concurrent execution. We utilize the concept of *transactional memory* (TM) [7] to achieve this goal. The general idea behind TM is to decide on whether two (or more) pieces of code can be executed concurrently based on whether their accesses to the underlying data are *conflicting* [8] or not, that is, if at least one of the accesses is a write. Conflict-free executions are allowed to proceed in parallel. On the other hand, upon encountering a data access conflict, execution effects of at least one piece of code have to be *rolled back* (i.e., undone), and the computation must be restarted. TM machinery, which originally started in software (STM) [9, 10, 11, 12], is now available in commodity hardware as Hardware Transactional Memory (HTM) [13, 14, 15]. However, despite almost three decades of work in this area, TM's promise of accelerating concurrent computations for real-life software has not been quite fulfilled. We speculate that there are two reasons why this is the case.

The first reason is that TM while being a single concept, may have different realizations in terms of algorithms and implementations (e.g., eager vs. lazy versioning [37]) and different integration strategies at the language level (e.g., API-level solutions [12] or the compiler-assisted **atomic** construct used to demarcate TM-managed concurrent code [38]), resulting in different behavior from the programmer's perspective. Consequently, attempts to introduce TM as a separate language-level mechanism lead to significant semantic dissonance with respect to existing concurrency-related mechanisms [39, 40].

The second reason is that a lot of TM (particularly STM) work was focusing on designing and implementing TM algorithms but limiting empirical evaluation to synthetic benchmarks (e.g., STMBench7 [16]) or measuring the performance of only selected concurrent data structures. Unfortunately, unlike what was expected, TM techniques did not easily generalize to real-life applications [9]. A few attempts to apply TM to production code were unsuccessful (e.g., an attempt to rewrite the Quake game server to use TM [17]).

In this work, we attempt to rectify some of these limitations and show that TM can be effective in accelerating real-life concurrent code. We focus less on the algorithmic side of TM (we use state-of-the-art off-the-shelf HTM implementation from Intel), and more on how and when to apply the TM machinery to maximize the benefit. Additionally, we replace Go locks with HTM constructs without changing the code's behavior in any way, which allows us to completely bypass complications related to transactional memory semantics. More specifically, we employ *transactional lock elision* (TLE) [41] — a wellknown technique that attempts to execute a lock-protected critical section as an atomic hardware transaction, reverting to using the lock if these attempts fail.

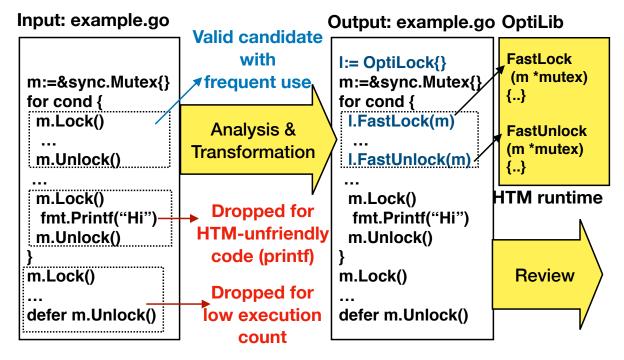

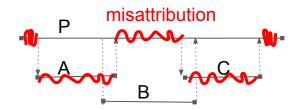

Figure 4.9 depicts our solution. At a high level, our solution starts with using static analysis to identify candidate lock-protected critical sections to be instead protected by the HTM. Then we filter out non-desirable candidates using both static analyses (e.g., to eliminate regions containing I/O operations) and dynamic analysis (to eliminate regions where the application of the HTM would not be beneficial based on profile data collected at runtime). Finally, we rewrite the code to have candidate regions use HTM constructs provided by the HTM library we developed instead of Go locks [5]. GOCC transformations are guaranteed to be safe; developer involvement is optional but highly recommended to let developers ultimately decide whether or not they want to use HTM.

In summary, this work makes the following contributions:

- We present the design and implementation of a framework for identifying lock-protected critical sections and select the best candidates for lock elision based on static analysis and execution profiles of Go programs.

- 2. We describe the source-to-source code transformation to replace mutual-exclusion locks in Go programs with HTM concurrency control constructs.

- 3. We introduce a library extending vendor-provided HTM primitives with intelligent features such as runtime contention management. Specifically, we devise a lightweight perceptron [42, 43] that learns whether eliding a lock via HTM at a call site [44] is beneficial at runtime.

- 4. We demonstrate the effectiveness of GOCC for improving performance of real-life concurrent Go code by up to  $10 \times$ .

### 2.2 Challenges

Locks are widely used in the real-world Go code and a significant amount of execution time can be spent waiting to acquire them [6, 45, 46, 47, 48, 49, 50]<sup>1</sup>. It is possible to replace a lock with a transaction that enables a critical section to be speculatively executed without actually holding the guarding lock. With the support of the HTM, such replacements can result in significant speedups. However, there are several challenges in performing these replacements correctly and robustly and ensuring that they deliver high performance reliably.

First, automatically and accurately matching a lock with its corresponding unlock op-

<sup>&</sup>lt;sup>1</sup>A limited study we performed in a large-scale industrial setting using thousands of different Go services showed up to 30% execution time being spent in lock-related code in certain Go programs; 5-10% was quite common.

Figure 2.1: GOCC schematic diagram. Static analysis detects three legal lock-unlock pairs in the input file example.go. The top one is a valid replacement candidate. The middle one is filtered since it contains I/O operations in its critical section. The bottom one is dropped due to the infrequent use via the information provided by profiles. The transformed code calls optiLib, which executes the critical section via HTM. The resulting diff is given to the developer for review.

eration to precisely identify critical sections is a complex problem. Real-world programs can use locks with nesting intra- or inter-procedurally, which makes it significantly more involved. Additionally, certain lock-compatible instructions (e.g., IO and privileged instructions) will not work with HTM. A critical section including such instructions will not benefit from HTM.

Furthermore, Go provides a keyword that enables delaying lock release operation to all exit points of a function by prefixing the Unlock() operation with the defer [51] keyword<sup>2</sup>. It not only complicates matching an unlock with a lock operation, it may unnecessarily lengthen a critical section, which according to a synthetic benchmark we

<sup>&</sup>lt;sup>2</sup>Any function can be deferred in Go.

wrote shows performance degradation. A scan of 21 million lines of industrial Go code, which includes about 8000 Unlock() operations, shows that about 76% are prefixed with the defer keyword. This indicates that handling defer statements is important.

Second, the Go language nuances [1] (e.g., pointer vs. value syntax, anonymous Mutex fields, lambda functions, etc.) make it non-trivial to transform lock-based code to HTM-based code.

Third, HTM has startup and commit overheads. Even in non-concurrent code, where data-access conflicts do not happen, HTM can fail [52], and locks may outperform HTM, particularly on tiny critical sections [53].

Fourth, the critical section size can be hard to estimate in general. If we make the conservative design choice and do not replace the lock if the critical section size is unknown, we can miss the opportunity to generate significant performance improvement. Thus, we need some runtime mechanism that can handle critical sections of arbitrary sizes with low overhead.

Fifth, when HTM aborts for a genuine data-access conflict, naively falling back to using a lock can be detrimental to performance [54, 55]. Deciding when and how to retry HTM-based executions or fall back to using fine-grained locks must be handled very carefully to avoid pathologies [54, 55, 56].

Our tool, GOCC, attempts to solve the above challenges. GOCC is an end-to-end system for improving the performance of lock-based Go code using HTM. We devise a sophisticated program analysis to identify lock-protected critical sections (§ 2.5.2), support lock-to-HTM code transformation including non-trivial Go features (§ 2.5.3), and develop an efficient HTM library to handle issues manifested at runtime (§ 2.5.4).

### 2.3 Related Work

Herlihy and Moss proposed transactional Memory (TM) [7] in 1993 as an alternative to locks. While locks proactively prevent two or more threads from concurrently accessing shared data, TM takes the opposite approach — concurrent accesses are allowed as long as they do not conflict. A lot of work has been done around both software and hardware implementations of transactional memory [10, 11, 12, 13, 14, 15, 57], but only a few [9, 17, 58, 59] focused on evaluating the approach with real-life workloads, and none have done this for Go.

Intel's TSX extension of x86 instructions set [60] implementing HTM is of specific interest here as it underlies parts of our implementation. It is widely available in modern Intel CPUs and offers software interfaces providing subtly different functionality. The RTM (Restricted Transactional Memory) interface allows programmers to execute arbitrary code as a hardware transaction. All operations within a transaction have atomic execution behavior — they all either appear to happen instantaneously or the entire transaction aborts and reverts the architectural state to before it was started. This can be trivially used to emulate the behavior of mutual-exclusion locks. In fact, this is precisely the kind of functionality that the HLE (Hardware Lock Elision) interface provides. However, HLE has been introduced mainly for backward compatibility with architectures that are not TSX-enabled and is not only very simplistic (e.g., with respect to contention management) but has also been shown to perform poorly compared to RTM [61]. Consequently, our solution uses the RTM interface as the low-level implementation mechanism to build a comprehensive TM-based alternative for mutual-exclusion locks.

Lock elision, whether in software or hardware or a hybrid fashion, including gaining insights into them, has been extensively studied [62, 56, 63, 57, 64, 65, 66, 67, 68, 69, 57, 70, 14, 71, 72, 73, 74, 75, 76, 77]. Our work uses many of those techniques; for example,

the basic design of our runtime controller was inspired by Wang et al. [75]. Additional possibilities to bring more solutions from the literature to the design and implementation of both our static analysis tool and runtime controller also exist. Other attempts to use transactional memory for emulating mutual-exclusion locks exist as well [78, 79], but they have to cope with higher overheads and semantics-related complications due to using the STM, they target the Java language whose synchronization lock-like primitives (i.e., *monitors*) are easier to handle due to their lexical scoping and, most importantly, their evaluation is based exclusively on synthetic benchmarks.

### 2.4 Gocc Overview

A Go Mutex is a runtime object with Lock() and Unlock() operations on it. Two (or more) critical sections guarded by the same Mutex will not execute concurrently. When transforming locks into HTM, there are two possibilities.

- A given Mutex guarding a set of critical sections is replaced with another object supporting operations analogous to Lock()/Unlock() but provided by the HTM. As a result, all critical sections previously guarded by the Mutex are now executed under HTM's control.

- 2. Lock()/Unlock() operations of the Mutex are replaced with their HTM equivalents on a per critical section basis. As a result, some critical sections for a given Mutex are still guarded by the same Mutex, while the others execute under HTM's control.

The former is doable only if it is beneficial to transform all Lock()/Unlock() operations using a given Mutex, and the Mutex object is defined in the code that we are rewriting. Assessing the benefit of transforming the Mutex object would require inspecting every critical section it protects. A "may alias" pointer analysis [80, 81] can answer such a question. The "all-or-none" coarse-granularity of this approach makes it unattractive because the imprecision of pointer analysis overapproximates the critical sections protected by a Mutex, disqualifying too many Mutexes from transformation.

This work adopts the latter approach, where we consider pairs of Lock()/Unlock() operations in the code for transformation, which provides fine-grained control over transformation. This approach has to handle pairing a lock with its corresponding unlock and support interoperability of HTM (where the code is transformed) with locks (where the code is not transformed). This kind of interoperability is well-studied in the literature [82, 83, 13, 84, 55] and is handled by our library.

Recall, from Figure 4.9, that input to GOCC is the source code for a Go package along with its execution profiles. The output is a source code patch, where candidate Lock()/Unlock() operations are replaced with calls to a custom HTM library. GOCC consists of the following key components:

- Analyzer: performs static analysis on the input program and collects lock-unlock pairs for transformation (§ 2.5.2).

- Transformer: rewrites the program by replacing Lock()/Unlock() with HTM, i.e. FastLock()/FastUnlock(), which elide the lock (§ 2.5.3).

- Adaptive runtime (optiLib): implements HTM in Go and provides required runtime mechanisms including retry and rollback (§ 2.5.4).

The source code patch choice, rather than a compiler transformation, is motivated by the desire to keep the developers in the loop. Using HTM without developers' knowledge can prove unwelcome because developers often demand full visibility into their programs. Developers are becoming performance and variance sensitive [85, 86, 87], and an accidental regression can become hard to diagnose. As a side effect, the choice of source-code patch demands us to be surgical — injecting large, complicated HTM-handling boilerplate code is a non-starter. Consequently, we perform Lock()/Unlock() operations replacements with API calls to HTM logic hidden in the optiLib open-source library and do so only in places where benefits of HTM are likely (e.g., we minimize the number of modified code locations using execution profiles).

#### 2.4.1 Gocc Guarantees and Limitations

- GOCC will transform properly synchronized code (i.e., where every lock operation will have a corresponding unlock operation) into the equivalent code without changing the code's behavior. Code not meeting this criterion will be either not transformed or transformed and its runtime behavior will be unchanged.

- GOCC considers only those lock-unlock pairs that seem to operate on the same lock within the same function inter-procedural Lock()/Unlock() operations are disregarded. Note, however, that in a critical section protected by GOCC transformed lock can make arbitrary function calls. The requirement to have both Lock() and its matching Unlock() operation be present in the same procedure scope is only our implementation choice and pragmatic in nature. Over 70% of the locks, we inspected met this criterion.

- GOCC makes no effort to identify critical sections or code reachability in the presence of reflection [88].

- GOCC, as implemented, does not *statically* detect HTM conflicts or capacity limitations (see § 2.5.2 for the details).

### 2.5 Gocc Design and Implementation

Before diving into the details of GOCCs design and implementation, we define some common terminology.

#### 2.5.1 Terminology

Go's sync package provides two kinds of shared memory objects: Mutex and RWMutex. GOCC handles them both, but in the following sections, without the loss of generality, we will only use the term Mutex for simplicity. From an HTM transformation viewpoint, an RWMutex is no different from a Mutex, except RWMutex offers additional APIs for read-only accesses.

A critical section **CS** is all code regions protected by a pair of lock and unlock operations on the same mutex object m — the notation for calling lock/unlock operations on m is m.Lock()/m.Unlock() where m is referred to as a receiver. Lock-point, abbreviated with letter L (Unlock-point abbreviated with letter U), is a static location in the code where the Lock() (Unlock()) function is invoked on a Mutex. LU-points is a set of L and U points. LU-pair is a candidate pair of one lock-point paired with an unlock-point. In the runtime context, fastpath/HTM-path means the use of HTM, and slowpath/fallback-path means the use of the original lock.

We utilize the Abstract Syntax Tree (AST), program Control Flow Graph [89] (CFG), and Static Single Assignment (SSA) [90] form of program representation prevalent in the compiler literature. In a CFG, nodes are basic blocks [89] of straight-line code, and edges are control flow relationships among them. GOCC first transforms the source code to the AST form (which is also used for code transformation as described in § 2.5.3) and then to the SSA form for CFG construction.

#### 2.5.2 Analyzer

The goal of the analyzer is to find as many LU-pairs as possible. The LU-pairs that protect HTM-incompatible critical sections (e.g., those including IO operations) must be pruned. This filtering serves two purposes: it reduces the number of code changes and non-beneficial HTM transformations. Complicated lock usage patterns, several Go language quirks, and pointer imprecision complicate the static analysis. A comprehensive call-graph analysis is vital because critical sections often contain function calls.

**Conflicts:** A sophisticated static analysis may detect whether transactions conflict. Answering this question, however, is unlikely to be valuable because developers typically do not use a lock if a conflict is impossible. Assuming conflicts happen, there is no easy way to statically determine whether transactions do not "typically" conflict. We do not try to solve this problem and leave conflict resolution to optiLib.

**Capacity:** Although one can perform static analysis to estimate the memory footprint of a critical section, it may not be possible if the bounds of a loop are unknown. Also, without knowing the target architecture's HTM capacity, it would be premature to filter out candidate critical sections this way. We leave the capacity-related decisions also to optiLib.

In the rest of this section, we, first, define the scope of our transformation (§ 2.5.2); then, describe the process of matching a lock with an unlock operation within a code region assuming no lock nesting and no function calls in a **CS**; extend our analysis to include nested locks (§ 2.5.2); expand the analysis scope to **CS**s that may contain function calls (§ 2.5.2); detail special case of Go's **defer** statement (§ 2.5.2); and finally discuss profile-based filtering (§ 2.5.2).

#### Scope of Transformation

To simplify the analysis, if a Lock()/Unlock() operation is executed in the middle of a basic block, we break such basic blocks in the CFG so that each lock-point begins a new basic block and each unlock-point ends a basic block. A single-entry single-exit (SESE) region [91] (simply *region*) of a CFG is our smallest granularity of lock transformation. A region is a subgraph of a CFG. Control reaching any basic block in a region is guaranteed to have already executed a designated entry basic block; control leaving from any basic block in the region is guaranteed to eventually pass through a designated exit basic block.

A function is the largest granularity of our lock transformation; a function always forms a region because all exits from a function are considered to go through a dummy basic block. This choice is pragmatic in nature since LU-pairs spanning multiple functions are uncommon.

Regions can be nested within one another. A Program Structure Tree (PST) organizes regions into a hierarchical tree [91]. We visit regions inside out from most-nested to leastnested. Section 2.5.2 describes the region identification and visiting strategies, which are not central to this work.

#### Splicing SESE regions for maximal LU-pairing

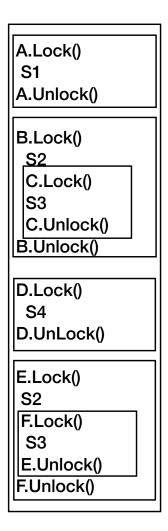

Although the classic definition of a program structure tree PST [91] provides hierarchical access to SESE regions, one may miss certain lock matching opportunities if multiple lock and unlock statements happen in a straight-line sequence, as shown in Figure 2.2. In this example, there is no conditional execution or loops from the first statement to the last hence, even though LU-points split the basic blocks, the standard SESE would place all such basic blocks in a single innermost region without further nesting. This would complicate which lock to pair with which unlock since the region has more than one LU-pair.

We solve the pairing problem in such straight-line code sections by performing additional processing to splice a region further based on LU-points. The idea is simple; we utilize the dominator and post-dominator trees [89] for the region. Only the nodes that contain a lock-point are of interest in the dominator tree (DomTree). Only the nodes that contain an unlock-point are of interest in the post-dominator tree (PDomTree).

We perform a post-order traversal of the DomTree. For each lock-point L in this

traversal in DomTree, we look up L's immediate post-dominator in the PDomTree, which is an unlock-point U. We then perform the reverse test, we look up the immediate dominator of U in the DomTree that is a lock-point, say,  $\hat{L}$ . If  $L = \hat{L}$ , we have the innermost matching of a candidate LU-pair. We also check that their points-to sets intersect. If no matches are found, we traverse up in the DomTree till a match is found and drop the candidate L if none is found.

Matched pairs are no longer considered when matching other lock-points or unlockpoints during the rest of the post-order traversal of nodes higher-up in the *DomTree*. This strategy breaks a straight-line sequence into the maximum number of LU-pairs, as shown with demarcated SESE-regions in Figure 2.2.

#### Matching LU-pair in the Absence of Nested Locks

This subsection discusses analyzing a candidate region R.

LU-points in R may be operating on different locks, which should be pruned. Some lock (unlock) operations may escape R, without a corresponding unlock (lock) operation in R, which should also be pruned. Below, we formalize these aspects.

**Definition 2.5.1** (Points-to set  $\mathcal{M}(L)$  of a Lock point L). Every lock-point (L) operates on some receiver mutex pointer  $\mathbf{p}$ .<sup>3</sup> Such a mutex pointer may point to one or more mutex objects allocated in the program. The set of all possible **Mutex** objects that  $\mathbf{p}$  may point to in the program is the Points-to Set of L, denoted by  $\mathcal{M}(L)$ .

Similarly, the Points-to set of an Unlock point U is  $\mathcal{M}(U)$ . We employ Anderson's flow-insensitive may-alias analysis [92] to obtain  $\mathcal{M}(L)$  and  $\mathcal{M}(U)$  on the whole program.

<sup>&</sup>lt;sup>3</sup>At the source level p can be either a pointer or an actual object value, but at the SSA level it is always a pointer.

Figure 2.2: A straight-line sequence of statements that fall into a single region are further spliced into regions based on matching a lock-point with the nearest post-dominating unlock-point and unlock-point with the nearest dominating lock-point.

| 2 m := &sync.Mutex{} 2<br>3 m.Lock() 3 | <pre>l := OptiLock{} m := &amp;sync.Mutex{} l.FastLock(m) l.FastUnock(m)</pre> |

|----------------------------------------|--------------------------------------------------------------------------------|

|----------------------------------------|--------------------------------------------------------------------------------|

Listing 2.1: Original lock-based code. Listing 2.2: Transformed HTM code.

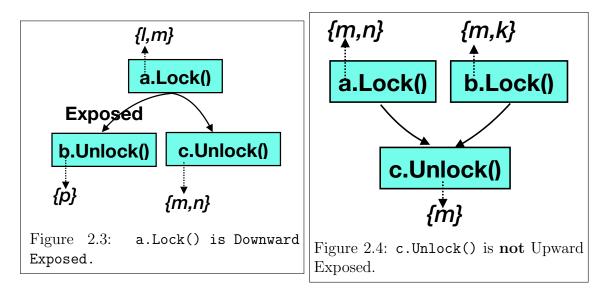

**Definition 2.5.2** (Downward Exposed Lock-point (**DELock**)). A lock-point, L, with points-to set  $\mathcal{M}(L)$ , is downward exposed in the region R, if there exists at least one path from L to R's exit without any unlock-point on any mutex in  $\mathcal{M}(L)$ .

**Definition 2.5.3** (Upward Exposed Unlock-point (**UEUnlock**)). An unlock-point, U, with points-to set  $\mathcal{M}(U)$ , is upward exposed in the region R if there exists at least one path from R's entry to U without a lock-point on any mutex in  $\mathcal{M}(U)$ .

DELock identifies lock-points that *definitely* do not have any corresponding unlockpoints in some execution paths in R; and UEUnlock identifies unlock-points that *definitely* do not have corresponding lock-points in some execution paths in R.

Figure 2.3 exemplifies a downward exposed lock-point. Mutex pointer a's points-to set  $\{l, m\}$ , has an empty intersection with b's points to set  $\{p\}$ ; although it has a non-empty

intersection with c's points-to set  $\{m, n\}$ . Figure 2.4 exemplifies an unlock-point that is *not* upward exposed. Mutex pointer c's points-to set  $\{m\}$ , has non-empty intersection with a's points-to set  $\{m, n\}$  and b's points-to set  $\{m, k\}$ .

We eliminate all DELock(R) and UEUnlock(R) from the transformation in R. The remaining lock-points in R are the complement of DELock(R), which is denoted by  $\overline{DELock(R)}$ . Similarly, the remaining unlock-points in R are the complement of UEUnlock(R), which is denoted by  $\overline{UEUnlock(R)}$ .

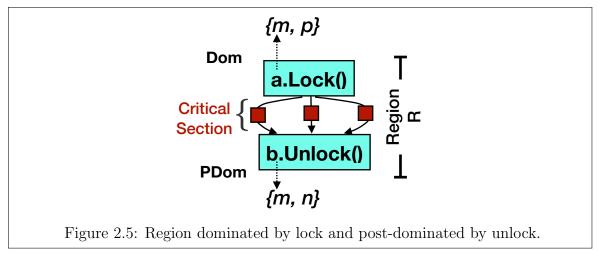

**Definition 2.5.4** (Feasible-HTM-Pair). Let  $L \in \overline{DELock(R)}$ . Let  $U \in \overline{UEUnock(R)}$ . L and U form a feasible HTM pair if all of the following conditions are true,

(1)  $\mathcal{M}(L) \cap \mathcal{M}(U) \neq \phi$ ,

(2)  $(L \text{ Dom } U) \wedge (U \text{ PDom } L),$

(3) The critical section  $C \subseteq R$  guarded by L and U contains no LU-point X such that  $\mathcal{M}(X) \cap (\mathcal{M}(L) \cup \mathcal{M}(U)) \neq \phi$ , and

(4) C contains no HTM-unfriendly instructions.

Condition (1) filters out those LU-points that are guaranteed to be operating on different Mutexes.

Condition (2) filters out infeasible control flows where unlock happens before lock and vice-versa. DOM and PDOM respectively represent dominator [89] and postdominator [89] relationships in a CFG. Figure 2.5 shows an example, where all paths from lock-point a.Lock() are post-dominated by unlock-point b.Unlock(), whose all incoming paths are dominated by a.Lock(). Additionally, the set-intersection of the points-to set of mutex pointers  $a = \{m, p\}$  and  $b = \{m, n\}$  is non-empty. Any Feasible-HTM-Pair on L and U, forms an SESE-region by itself, where the entry basic block has L as its first instruction and the exit basic block has U as its last instruction. Condition (2) intuitively finds correct candidate LU-pairs in the absence of nested locks because if a lock operation L is performed on every path reaching any code in C and an unlock operation U is performed on every path exiting C, then LU must be operating on the same Mutex. Section 2.5.2 justifies our choice of DOM/PDOM relationships.

Condition (3) ensures that if we match an L with a U, there does not exist another lock-point or unlock-point in the same region that *may* operate on a Mutex in the same points-to set as that of L or U. The next subsection elaborates on lock nesting.

Condition (4) is an obvious requirement to ensure HTM does not abort. A region is unsafe if it contains any IO instructions.

Since we use "may alias" to match a lock-point with unlock-point, it is possible (but less likely) for our transformation to pair a lock with an unlock that may be operating on two different mutex objects at runtime. However, at runtime, we can obtain and memorize the address of the mutex object used at the lock-point, and compare it against the mutex object offered to the runtime at the unlock-point. In case of an address mismatch of the mutex objects used in the same LU-pair, we can abort the transaction and revert to a safe state and fall back to using the locks. A mismatch is impossible without nested locks because of the dominance and post-dominance relationship between the lock and unlock in an LU-pair.

#### Justification for using the dominance and post-dominance relationship

The DOM and PDOM requirements proposed in Definition 2.5.4: Condition(2) may seem rather too strong. In a more complex control flow shown in Listing 2.3, Condition (2) does not hold good because neither lock-point dominates any unlock-point; however, both lock-points taken together guarantee a lock-point execution before executing an unlock-point and similarly, both unlock-point taken together ensure that after executing any lock-point, one unlock-point is guaranteed to execute. Thus, it would be valid to transform all LU-points with HTM here.

```

1 if cond1 {

2 m.Lock()

3 } else {

4 m.Lock()

5 }

6 if cond2 {

7 m.Unlock()

8 } else {

9 m.Unlock()

10 }

```

Listing 2.3: Complex locking control flow amenable for HTM.

```

1 if cond1 {

2 m.Lock()

3 // in critical section

4 }

5 // may be critical section

6

7 if cond2 {

8 // in critical section

9 m.Unlock()

10 }

```

Listing 2.4: Complex locking control flow unsuitable for HTM.

A slightly different control flow in Listing 2.4, however, shows that the lack of DOM and PDOM relationship is not easy to handle. In this case, the execution of the lock-point does not ensure the execution of unlock-point also or vice versa. Hence, transforming both LU-points does not provide any guarantee.

Any "umbrella covering" analysis may artificially drag non-critical sections into critical sections. With this observation, we enforce condition (2).

#### Lock Nesting

Go supports nested locks, but reentrant [93] locks are not allowed. Condition (3) in Definition 2.5.4 allows nested locks but demands that they operate on disjoint Mutex objects.

HTM via Intel TSX allows nesting: if a nested transaction succeeds, hardware does not commit it until the outermost transaction commits. If a nested transaction fails, the control jumps to the starting code address of the nested transaction. This facility allows us to safely transform locks into HTM even when they are nested.

Condition (3) in Definition 2.5.4 disqualifies a candidate LU-pair from the transfor-

| a.Lock() //outer region start                                                  | 1 a.Lock()                                                |

|--------------------------------------------------------------------------------|-----------------------------------------------------------|

| 2<br>3<br>4 b.Lock() // inner region start<br>5 b.Unlock() // inner region end | 3 l := OptiLock{}<br>4 l.FastLock(b)<br>5 l.FastUnlock(b) |

| $^6$ a.Unlock() //outer region end                                             | 6<br>7 a.Unlock()                                         |

| Listing 2.5: Nested Locks.                                                     | Listing 2.6: HTMized.                                     |

mation in the region R if there exists any other lock or unlock point whose lock/unlock operation *may be* operating on the same mutex as those in the LU-pair.

As an example, in Listing 2.5, assume the mutex pointers a and b point to the same points-to set. When inspecting the "inner region", we find only one LU-pair, which obeys all Feasible-HTM-Pair conditions in Definition 2.5.4. Consequently, the lock usage on bin the inner region can be transformed to HTM. When inspecting the "outer region", however, we see conflicting LU-points, and hence the locking operations on a will not be transformed. The resulting transformed code is shown in Listing 2.6, which is correct.

This approach complicates hand-over-hand locking [94, 95], sometimes used in the concurrent linked-list traversal, shown in Listing 2.7. As before, assume all four LU-points have a non-empty intersection of their points-to sets. When inspecting the inner region, the LU-pair b.Lock() and a.Unlock() passes all tests in Definition 2.5.4. Hence, they will be, incorrectly, paired and transformed to use HTM, as shown in Listing 2.8. This transformation violates the programmer's intention. Subsequently, when visiting the outer region, condition (3) is violated, and hence the outer LU-pair will not be transformed. One could have discarded the transformation of the inner region when the conflict is visible in the enclosing region. However, we cannot distinguish this incorrect pairing from the correct pairing in the previous case. Our solution is to always apply the transformations on the candidates found in inner regions, and handle mismatches at runtime via HTM aborts iff executing on the fastpath. As mentioned at the end of § 2.5.2, a mismatch is easy to recognize at runtime by, first, making FastLock() store the address

| 1 | a.Lock() //outer region start     | 1 | a.Lock()              |

|---|-----------------------------------|---|-----------------------|

| 2 |                                   | 2 |                       |

| 3 |                                   | 3 | l := OptiLock{}       |

| 4 | b.Lock() // inner region start    | 4 | l.FastĹock(b)         |

|   | a.Unlock() // inner region end    |   | l.FastUnlock(a)       |

| 6 |                                   | 6 |                       |

| 7 | b.Unlock() //outer region end     | 7 | b.Unlock()            |

|   | Listing 2.7: Hand-over-hand lock. |   | Listing 2.8: HTMized. |

| 1 | a.Lock()   |

|---|------------|

| 2 | b.Lock()   |

| 3 | b.Unlock() |

| 4 | a.Unlock() |

| 1        | a.Lock()   |  |

|----------|------------|--|

| <b>2</b> | b.Lock()   |  |

| 3        | a.Unlock() |  |

| 4        | b.Unlock() |  |

Listing 2.10: imperfectly nested locks.

of the Mutex used at the lock-point in a field in OptiLock and, second, checking whether the Mutex passed to FastUnlock() is the one present in OptiLock. The transactional abort is needed (and possible) only on the fastpath. Section 2.5.2 details the correctness of transforming nested locks into HTM via Gocc.

## Interoperability of lock-nesting with HTM

Programs may use perfect nesting as shown in Listing 2.9 or imperfect nesting as shown in Listing 2.10 (aka hand-over-hand locks [94, 95]).

The following cases arise depending on the kind of lock nesting and whether or not the LU-pair is converted into HTM.

- Neither the inner nor the outer lock is transformed to HTM. This is always safe because the behavior is the same as the original code in both perfect and imperfect nesting.

- Both the inner and outer locks are transformed to HTM. If both inner and the outer locks use the fast path and the transaction commits successfully, it ensures

mutual exclusion and atomicity of both critical sections, and hence it is safe; it also ensures that the entire transaction did not conflict with any other concurrent operation. If both inner and outer locks use the respective slow paths, the behavior is the same as the locks being untransformed (previous case) and hence obviously safe. These two are true whether perfect or imperfect nesting. If one of the inner or outer HTM falls back to its slowpath, the behavior becomes the same as one of the following cases.

## • Perfectly nested locks

- Only the inner lock is transformed to HTM. This is safe because all instructions inside the HTM will appear to execute atomically and mutually exclusive to the external observer. While performing the inner (and the only) transaction, if the inner lock gets acquired by another thread, the transaction will abort, and none of its state changes will be visible to the external world; the outer lock will continue to be held. The inner transaction may be retried or fall back on its slowpath. Falling back to the slowpath is the same as both inner and outer locks not being transformed.

- Only the outer lock is transformed to HTM. This is safe because the inner lock operation, including lock acquisition and release, will be done transactionally. If another thread acquires either the inner or the outer lock while the transaction is in flight, the outer transaction will be aborted, and the inner lock acquisition (if already done) will be rolled back, ensuring mutual exclusion and atomicity of the entire region and the availability of the inner and outer locks to others. If the transaction commits, mutual exclusion and atomicity of the entire region are assured.

- Imperfectly nested locks

- Only the inner lock is transformed to HTM. This is represented by transforming b.Lock() and a.Unlock() in Listing 2.10. If at runtime, fallback path is taken at b.Lock(), a.Unlock() will also use the fallback lock because our implementation recognizes mismatched mutexes from FastLock() to FastUnlock() on the same OptiLock object; hence, the behavior is as if we did no transformation; and hence it is functionally same as the original code. If at runtime the fastpath is taken at b.Lock(), at a.Unlock() we recognize a mismatched mutex a vs. b and abort the transaction. The abort rolls back all changes done between b.Lock() till a.Unlock() and falls back to the slowpath. As stated before, slowpath is always correct, and hence the entire behavior is the same as the original untransformed code.

- Only the outer lock is transformed to HTM. This is represented by transforming a.Lock() and b.Unlock() in Listing 2.10. If at runtime, the fallback path is taken at a.Lock(), b.Unlock() will also use the fallback lock because our implementation recognizes mismatched mutexes from FastLock() to FastUnlock() on the same OptiLock object; hence, the behavior is as if we did no transformation; and hence the behavior is functionally same as the original code. If at runtime, the fastpath is taken, at unlock time in b.Unlock() we recognize a mismatched mutex a vs. b and abort the transaction. The abort rolls back all changes done between a.Lock() till b.Unlock() including the inner b.Lock() and a.Unlock(), thus discarding all changes in the entire region. Subsequently, we'll always take the slowpath route due to mismatched mutexes, and hence the effect is the same as both inner and outer locks not being transformed, which is always safe.

It is straightforward to extend the argument to any depth of nesting using an inductive argument that assumes that N-level nesting works (because 2-level nesting works) and uses the same argument as above to prove that N + 1-level nesting is also correct.

#### Critical Sections with Function Calls

When the critical section protected by a candidate LU-pair contains function calls, we need to extend the analysis beyond the current function. Conditions (1) and (2) in Definition 2.5.4 are local to R. Conditions (3) and (4) require inter-procedural analysis.

We need to ensure that the transitive-closure of all code regions protected by a candidate LU-pair, including the blocks reachable via function calls, neither contains any HTM-unfriendly instructions nor contains any LU-points whose points-to set may overlap with the points-to sets of L or U. Otherwise, we discard the candidate LU-pair.

To accomplish this, we first build a static call graph using rapid type analysis [96, 97]. Next, we precompute summary information for each function on its own without its transitive closure of function calls; the summary contains (a) the fit of the function for HTM based-execution (i.e., no HTM-unfriendly instructions), and (b) the union of all points-to sets of all LU-points in the function, denoted by  $\mathcal{P}$ .

For a candidate LU-pair meeting all the conditions in Definition 2.5.4 within the region R, we proceed to do inter-procedural analysis. Let  $F^*$  be the transitive closure of all the function calls invoked inside the critical section  $C \subseteq R$  protected by a candidate LU-pair. LU-pair is discarded if (a)  $\exists F \in F^*s.t. F$ 's summary contains HTM-unfriendly instructions or (b)  $\exists F \in F^*s.t. \mathcal{P} \cup (\mathcal{M}(L) \cup \mathcal{M}(U)) \neq \phi$ . The former is simply condition (4) expanded to all functions, and the latter is condition (4) expanded to all functions. We note that nested locks discussed in § 2.5.2 can be in different functions.

#### The defer Statement

The defer [51] statement in Go, introduced in § 2.2, needs special attention. Go defers the execution of functions prefixed with the defer keyword to the calling function's return point. The presence of defer Unlock() complicates our CFG-based dominance/postdominance analysis. Deferred unlocks extend the critical sections till function exit points. Listing 2.11 shows a legal Go code, where the defer m.Unlock() appears even before the call to m.Lock(). Condition (2) in Feasible-HTM-Pair will treat this pair as an invalid candidate for transformation because the lock-point does not dominate the unlock-point.

We address this case by interpreting defer m.Unlock() in a CFG by (a) introducing a synthetic m.Unlock() statement at the end of each basic block that returns control from the function, and (b) discarding the presence of m.Unlock() in its original position during the analysis. This allows us to reuse the previously described dominance relationship. During transformation, however, GOCC simply replaces a defer Unlock() with a defer FastUnlock() in its original place, as shown in Listing 2.12.

Multiple defer calls are executed in a last-in-first-out (LIFO) order of encountering the defer statement at runtime. This complicates the dominance and post-dominance relationship; for simplicity, we discard any function that contains multiple defer Unlock() statements. We found none in the packages used in our evaluation.

## **Profiles to Filter Hot Critical Sections**

Profiling is a built-in feature in Go, which takes callstack samples via timer [98] or hardware performance counter [99] interrupts. One can take CPU profiles of a go program either at launch time by simply passing a -cpuprofile flag or from an already running program, for a specified duration, by accessing an exposed profiling port.

Go profiles are in the pprof format.

```

1 func DeferExample() {

1 func DeferExample()

{

l := OptiLock{}

2

:= &sync.Mutex{}

3

m := &sync.Mutex{}

3

m

defer m.Unlock()

defer 1.FastUnlock(m)

\mathbf{4}

4

m.Lock()

1.FastLock(m)

\mathbf{5}

\mathbf{5}

6

// critical section

6

// inside HTM

7 }

```

```

Listing 2.11: defer Unlock.

```

Listing 2.12: HTMized.

The pprof Go package [98] allows us to programmatically navigate the callstack samples presented as weighted call graphs, where the nodes represent functions and edges represent caller-callee relationships. The functions are annotated with their inclusive and exclusive execution times.

When profiles are available, we use them to filter the regions where negligible execution time is spent, even before applying the static analysis. In fact, this is the first filtering step we perform before making the aforementioned LU-pair identification. We treat any critical section (including the entry and exit) where the aggregated execution time is less than 1% of the total execution time as insignificant.

## 2.5.3 Transformer

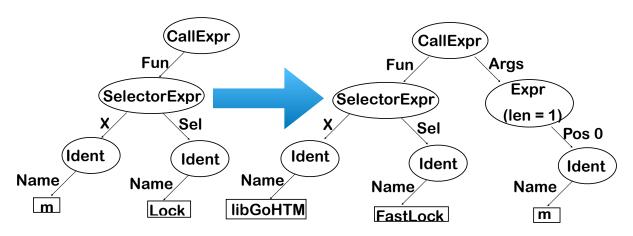

Since our end product is a code patch, we perform the transformation on the AST form of the program. Go AST can be serialized into source code via Go format [100] package. To this end, the transformer maps the candidate set of LU-pair operations found during the SSA-based analysis phase (described in § 2.5.2) to AST nodes [101]. It then replaces the LU-pair operations with calls to FastLock()/FastUnlock() in optiLib. It also passes the original Mutex object as a pointer to the calls to FastLock()/FastUnlock() since the underlying lock object is necessary for lock elision (fastpath) as well as for slowpath. Figure 2.6 shows an example AST transformation. The transformation itself is mechanical but challenging. In the following sections, we discuss several Go features that pose special challenges in transforming the AST.

Figure 2.6: Example of AST transformation from m.Lock() to optiLib.FastLock(m). Some AST nodes are omitted for brevity.

| 1                              | <pre>11 := Optilock{}</pre>    |       |

|--------------------------------|--------------------------------|-------|

| 2// pointer form               | 2// pointer form               |       |

| 3 m := &sync.Mutex{}           | 3 m := &sync.Mutex{}           |       |

| 4 m.Lock()                     | 41.FastLock(m)                 |       |

| 5 m.Unlock()                   | 5l.FastUnlock(m)               |       |