### **UC Santa Barbara**

### **UC Santa Barbara Electronic Theses and Dissertations**

#### **Title**

Learning from Production Test Data: From Statistical Characterization to Modeling for Anomaly Detection

### **Permalink**

https://escholarship.org/uc/item/8vx9t7qj

#### **Author**

Lin, Fan

#### **Publication Date**

2016

Peer reviewed|Thesis/dissertation

### University of California Santa Barbara

# Learning from Production Test Data: From Statistical Characterization to Modeling for Anomaly Detection

A dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor\ of\ Philosophy}\\ {\rm in} \\ {\rm Electrical\ and\ Computer\ Engineering} \end{array}$

by

Fan Lin

#### Committee in charge:

Professor Kwang-Ting Tim Cheng, Chair Professor Malgorzata Marek-Sadowska Professor Alberto Giovanni Busetto Professor XiFeng Yan

June 2016

| The Dissertation of Fan Lin is approved.        |

|-------------------------------------------------|

|                                                 |

|                                                 |

| Professor Malgorzata Marek-Sadowska             |

|                                                 |

| Professor Alberto Giovanni Busetto              |

|                                                 |

| Professor XiFeng Yan                            |

|                                                 |

| Professor Kwang-Ting Tim Cheng, Committee Chair |

# Learning from Production Test Data: From Statistical Characterization to ${\it Modeling~for~Anomaly~Detection}$

Copyright © 2016

by

Fan Lin

### Acknowledgements

I deeply appreciate the guidance of Prof. Tim Cheng through the years. I have been lucky to have learned and changed so much during the PhD study. I would also like to acknowledge my committee, Prof. Malgorzata Marek-Sadowska, Prof. Alberto Giovanni Busetto, and Prof. XiFeng Yan for their input. Thanks to Chun-Kai Hsu for the collaborative work on the project, and all my labmates and friends for simply being there. I appreciate the inspiring discussions with Chieh-Chi Kao, Kuo-Chin Lien, and the other members of our image processing study group. Finally, thanks for the support from my parents and my girl friend Stephanie.

# $\begin{array}{c} \mathbf{Curriculum} \ \mathbf{Vitæ} \\ \mathbf{Fan} \ \mathbf{Lin} \end{array}$

### Education

| 2016 | Ph.D. in Electrical and Computer Engineering,           |

|------|---------------------------------------------------------|

|      | University of California, Santa Barbara, United States. |

| 2014 | M.S. in Electrical and Computer Engineering,            |

|      | University of California, Santa Barbara, United States. |

| 2010 | B.S. in Electrical Engineering,                         |

|      | National Taiwan University, Taipei, Taiwan.             |

# Experience

| 2011 - 2016 | ${\it Graduate Research Assistant, University of California, Santa}$ |

|-------------|----------------------------------------------------------------------|

|             | Barbara, United States.                                              |

| 2015        | Test Engineer Intern, Oracle, Santa Clara CA, United States.         |

| 2013        | Test Engineer Intern, Broadcom, Irvine CA, United states.            |

| 2012        | Test Engineer Inter, Taiwan Semiconductor Manufacturing              |

|             | Company (TSMC), Taiwan.                                              |

| 2012 - 2014 | Teaching Assistant, University of California, Santa Barbara,         |

|             | United States.                                                       |

### Honors and Awards

2016 Dissertation Fellowship, University of California, Santa Barbara.

| 2015 | Studying Abroad Scholarship, Ministry of Education, Tai-   |

|------|------------------------------------------------------------|

|      | wan.                                                       |

| 2010 | Research Award, Lam Research Corp., Taiwan.                |

| 2010 | Valedictorian Speech, National Taiwan University, Taiwan.  |

| 2010 | Presidential Award, National Taiwan University, Taiwan.    |

| 2010 | Innovation Award, National Taiwan University, Taiwan.      |

| 2010 | Special Project Award, National Taiwan University, Taiwan. |

### **Publications**

- **F. Lin** and K.-T. Cheng, "An Artificial Neural Network Approach for Screening Test Escapes," submitted to *International Test Conference (ITC)*, 2016.

- **F. Lin**, C.-K. Hsu, and K.-T. Cheng, "Pairwise Proximity-Based Features for Test Escape Screening," in *International Conference on Computer-Aided Design* (ICCAD), 2015.

- **F. Lin**, C.-K. Hsu, and K.-T. Cheng, "AdaTest: an Efficient Statistical Test Framework for Test Escape Screening," in *International Test Conference (ITC)*, 2015.

- **F. Lin**, C.-K. Hsu, and K.-T. Cheng, "Learning from Production Test Data: Correlation Exploration and Feature Engineering," in *Asian Test Symposium (ATS)*, 2014.

- **F. Lin**, C.-K. Hsu, and K.-T. Cheng, "Feature Engineering with Canonical Analysis for Effective Statistical Tests Screening Test Escapes," in *International Test Conference (ITC)*, 2014.

- S. Zhang, **F. Lin**, C.-K. Hsu, K.-T. Cheng, and H. Wang, "Feature Engineering with Canonical Analysis for Effective Statistical Tests Screening Test Escapes," in *International Test Conference (ITC)*, 2014.

- C.-K. Hsu, **F. Lin**, K.-T. Cheng, W. Zhang, X. Li, J. M. Carulli, and K. M. Butler, "Test Data Analytics: Exploring Spatial and Test-Item Correlations in Production Test Data," in *International Test Conference (ITC)*, 2013.

#### Abstract

Learning from Production Test Data: From Statistical Characterization to

Modeling for Anomaly Detection

by

#### Fan Lin

Modern test programs for post-silicon testing include a large number of test measurements applied in multiple settings such as different temperatures, supply voltages, and operation modes to meet the demanding quality requirements of the products. In addition to the pass/fail results of each test item, there exist multiple types of correlations in the huge amount of production test data. Identifying and modeling the hidden correlations in the test data could help screen test escapes, which are chips that pass all test items but fail in system-level application.

This thesis focuses on developing revealing features and machine learning algorithms for classifying test escapes based on production test data. In terms of feature engineering, three types of feature sets that represent different aspects of how a chip deviates from the normal population are proposed. In addition, a linear transformation that compacts the critical information for feature reduction and a collection of nonlinear transformations that reveal additional abnormalities of the test escapes are proposed to effectively expose the test escapes as outliers in certain perspectives. We have also developed frameworks exploiting state-of-the-art machine learning algorithms including a support vector machine (SVM), a cascade of AdaBoost classifiers, and an artificial neural network.

# Contents

| $\mathbf{C}_1$ | urricı   | um Vitae                                    | $\mathbf{v}$ |  |

|----------------|----------|---------------------------------------------|--------------|--|

| A              | Abstract |                                             |              |  |

| Li             | st of    | igures                                      | xii          |  |

| Li             | st of    | Cables                                      | XV           |  |

| 1              | Intr     | duction                                     | 1            |  |

|                | 1.1      | Correlations in Production Test Data        | 1            |  |

|                | 1.2      | Machine Learning for Detecting Test Escapes | 3            |  |

|                | 1.3      | Proposed Methods                            | 5            |  |

| <b>2</b>       | Can      | nical Analysis and SVM                      | 8            |  |

|                | 2.1      | ntroduction                                 | 8            |  |

|                | 2.2      | Feature Development                         | 11           |  |

|                |          | 2.2.1 Measurement Mean                      | 12           |  |

|                |          | 2.2.2 Spatial Pattern                       | 12           |  |

|                | 2.3      | Feature Transformation                      | 15           |  |

|                | 2.4      | Test Methodology                            | 21           |  |

|                |          | 2.4.1 Classifier                            | 23           |  |

|                |          | 2.4.2 Pre-test Analysis                     | 23           |  |

|                |          | 2.4.3 Test Application                      | 24           |  |

|                | 2.5      | Experimental Result                         | 26           |  |

|                |          | 2.5.1 Data Setup                            | 26           |  |

|                |          | 2.5.2 Sequential Rejectors                  | 27           |  |

|                |          | 2.5.3 Comprehensive Test                    | 32           |  |

|                |          | 2.5.4 Test Application                      | 34           |  |

|                |          | 2.5.5 Another Experimental Scenario         | 37           |  |

|                |          |                                             | ~ •          |  |

|   | 2.6                    | Summary                                                       |

|---|------------------------|---------------------------------------------------------------|

| 3 | Ada                    | aTest 41                                                      |

|   | 3.1                    | Introduction                                                  |

|   | 3.2                    | AdaTest                                                       |

|   | 0.2                    | 3.2.1 AdaBoost                                                |

|   |                        | 3.2.2 Cascaded AdaBoost Classifiers                           |

|   | 3.3                    | Data Preparation and Feature                                  |

|   | 0.0                    | Generation                                                    |

|   |                        | 3.3.1 Data Standardization                                    |

|   |                        | 3.3.2 Features for Classification                             |

|   | 3.4                    | Experimental Result                                           |

|   | 0.4                    | 3.4.1 Emulating Test Escapes                                  |

|   |                        | 3.4.2 Classification Accuracy                                 |

|   |                        | 3.4.3 Application Runtime and Memory Usage                    |

|   |                        | 3.4.4 Feature Selection                                       |

|   | 3.5                    |                                                               |

|   | 5.5                    | Summary                                                       |

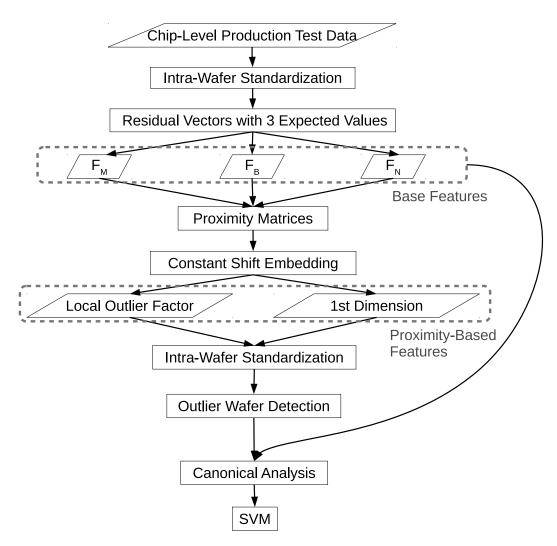

| 4 | $\operatorname{Pro}$   | ximity-Based Features 65                                      |

|   | 4.1                    | Introduction                                                  |

|   | 4.2                    | Pairwise Proximity 6                                          |

|   | 4.3                    | Constant Shift Embedding                                      |

|   |                        | 4.3.1 Concepts and Properties                                 |

|   |                        | 4.3.2 Distribution in the Embedded Space                      |

|   | 4.4                    | Data Preparation and Feature                                  |

|   |                        | Processing                                                    |

|   |                        | 4.4.1 Data Standardization                                    |

|   |                        | 4.4.2 Feature Generation                                      |

|   |                        | 4.4.3 Feature Standardization and Outlying Wafer Detection 80 |

|   |                        | 4.4.4 Feature Transformation and Classification 82            |

|   | 4.5                    | Experimental Results                                          |

|   |                        | 4.5.1 Classification Accuracy                                 |

|   |                        | 4.5.2 Performance Overhead                                    |

|   | 4.6                    | Summary                                                       |

|   | 1.0                    |                                                               |

| 5 | $\mathbf{A}\mathbf{n}$ | Artificial Neural Network Approach 90                         |

|   | 5.1                    | Introduction                                                  |

|   | 5.2                    | Artificial Neural Networks                                    |

|   | 5.3                    | The Proposed Structure                                        |

|   | 5.4                    | Feature Processing 98                                         |

| Bi         | Bibliography 1 |        |                                 | 115 |

|------------|----------------|--------|---------------------------------|-----|

| 6          | Con            | clusio | n                               | 113 |

|            | 5.6            | Summ   | nary                            | 110 |

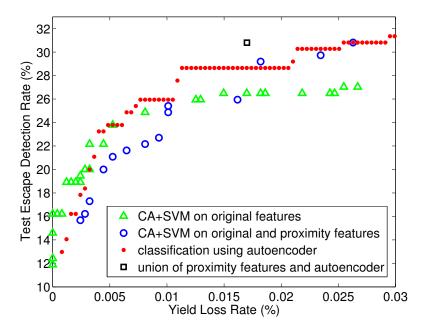

|            |                | 5.5.4  | Performance Comparison          | 109 |

|            |                |        | Trained Parameters in the Model |     |

|            |                | 5.5.2  | Classification Accuracy         | 104 |

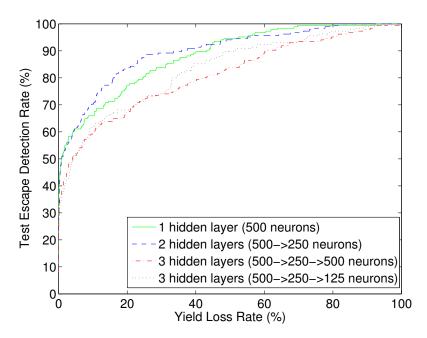

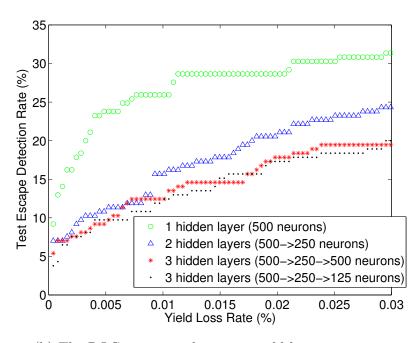

|            |                | 5.5.1  | Impact of Structure Design      | 101 |

| 5.5 Experi |                | Exper  | imental Results                 | 100 |

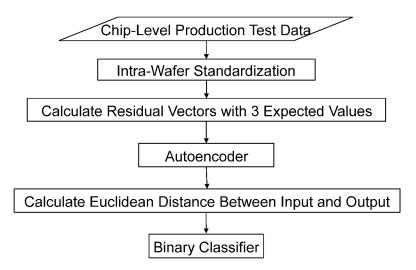

|            |                | 5.4.3  | Proposed Test Flow              | 99  |

|            |                | 5.4.2  | Feature Generation              | 99  |

|            |                | 5.4.1  | Data Standardization            | 98  |

# List of Figures

| 2.1  | Examples of test escapes which are considered abnormal with re-         |    |

|------|-------------------------------------------------------------------------|----|

|      | spect to different estimated values                                     | 13 |

| 2.2  | An example of residuals with respect to different estimated values      |    |

|      | of one test item                                                        | 16 |

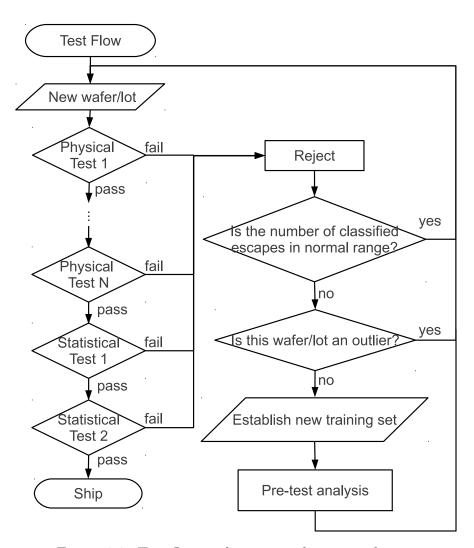

| 2.3  | Test flow with sequential statistical tests                             | 22 |

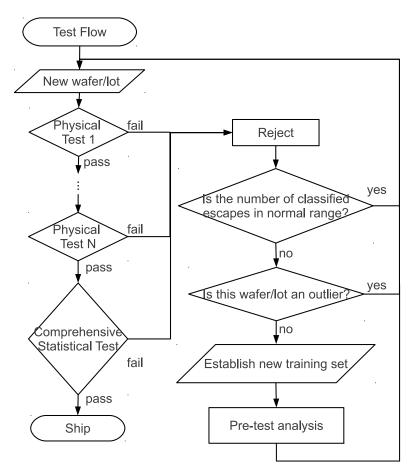

| 2.4  | Test flow with a comprehensive statistical test                         | 24 |

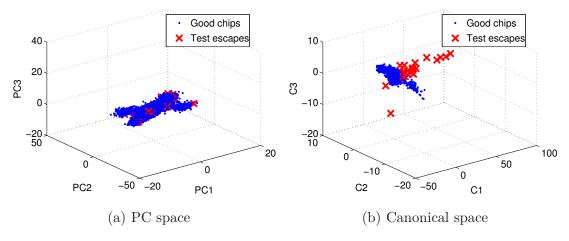

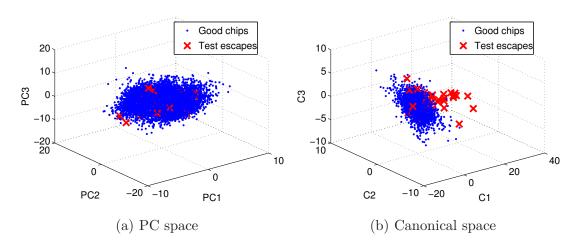

| 2.5  | The distributions of good chips/test escapes in different feature       |    |

|      | spaces of $F_m$                                                         | 29 |

| 2.6  | The distributions of good chips/test escapes in different feature       |    |

|      | spaces of $F_s$                                                         | 29 |

| 2.7  | The ROC diagram for C-SVC based on $F_m$ and $F_s$ in three different   |    |

|      | spaces                                                                  | 31 |

| 2.8  | The distributions of good chips and test escapes detected by the        |    |

|      | two sets of features in the canonical space of $F_m$                    | 33 |

| 2.9  | The distributions of good chips/test escapes in the canonical space     |    |

|      | derived from $F_m \cup F_s$                                             | 34 |

| 2.10 | The ROC diagram for C-SVC in canonical space with 3 features            |    |

|      | derived from different feature sets                                     | 35 |

| 2.11 | The ROC diagram for C-SVC based on $F_m \cup F_s$ in the original space |    |

|      | and in the canonical space                                              | 38 |

| 2.12 | The ROC diagram for C-SVC in canonical space with 3 features de-        |    |

|      | rived from different feature sets, based on a data set with a reduced   |    |

|      | number of test escapes described in Section 2.5.5                       | 39 |

| 3.1  | The cascade of classifiers for test escape screening which is applied   |    |

| 0.1  |                                                                         | 47 |

| 3.2  | after the physical test program for all chips in a wafer is completed.  | 41 |

| ა.⊿  | The median among the measurements of eight neighbors is used as         | 52 |

|      | the expected value for the target chip $t$ in the middle                | 02 |

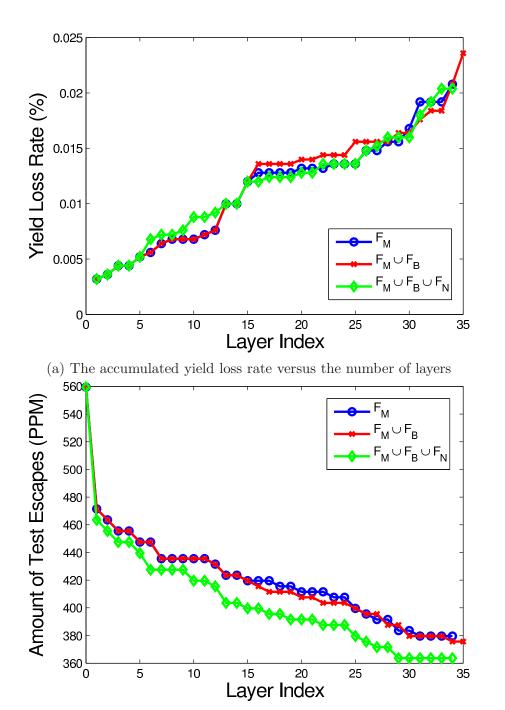

| 3.3 | The accumulated yield loss rate and the amount of remaining undetected test escapes versus the number of layers in the cascade of                                                                                                                            |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4 | classifiers                                                                                                                                                                                                                                                  |

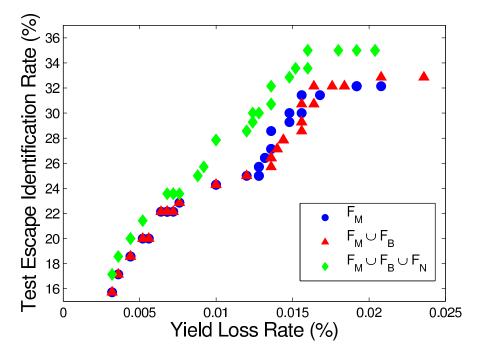

| 0.4 | features                                                                                                                                                                                                                                                     |

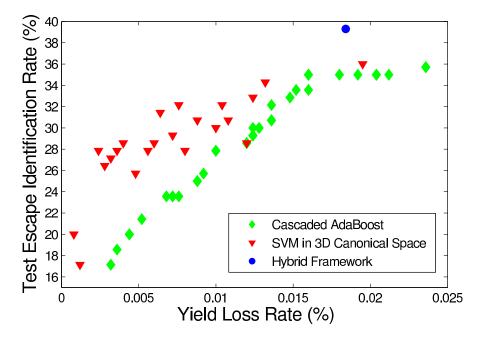

| 3.5 | The ROC curves of classifications based on cascaded AdaBoost and SVM in 3-dimensional canonical space                                                                                                                                                        |

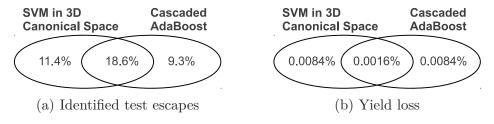

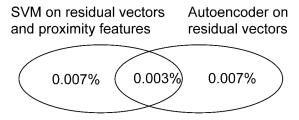

| 3.6 | The Venn diagram of the populations of identified test escapes and yield loss for the SVM-based framework and AdaTest                                                                                                                                        |

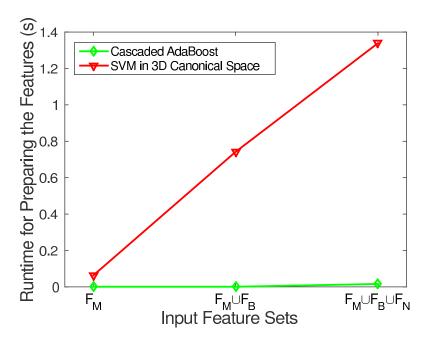

| 3.7 | The runtime for generating and transforming the features before classification                                                                                                                                                                               |

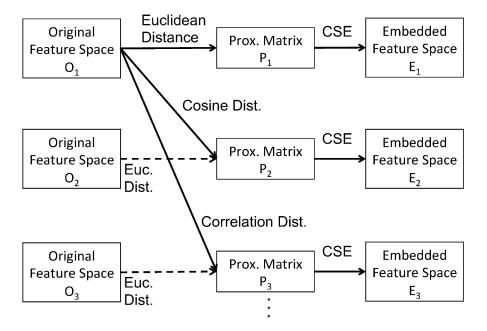

| 4.1 | The conversion between proximity matrices and Euclidean spaces. CSE preserves the cluster structure through the conversion from a                                                                                                                            |

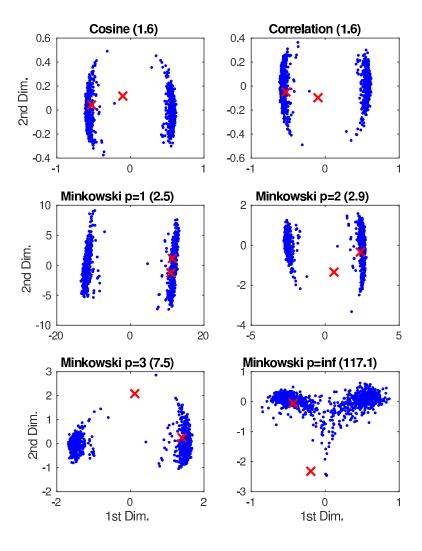

| 4.2 | proximity matrix $P_i$ to an embedded Euclidean space $E_i$ The distributions of the chips on a wafer in the first two dimensions of the CSE embedded spaces based on six different proximity/distance functions. Blue dots represent the good chips and red |

|     | crosses mark the positions of test escapes. The numbers of effective dimensions are shown above each figure.                                                                                                                                                 |

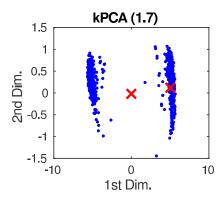

| 4.3 | The distribution in the first two dimensions of the embedded space constructed based on kPCA with RBF kernel.                                                                                                                                                |

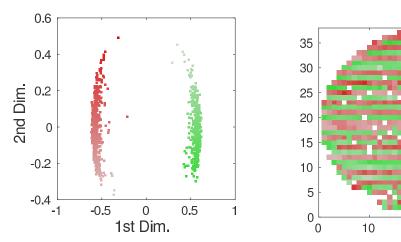

| 4.4 | Color-coded distributions of good chips showing the correspondence of chips in the embedded space and on the wafer. Chips are colored                                                                                                                        |

| 4.5 | to show their corresponding positions                                                                                                                                                                                                                        |

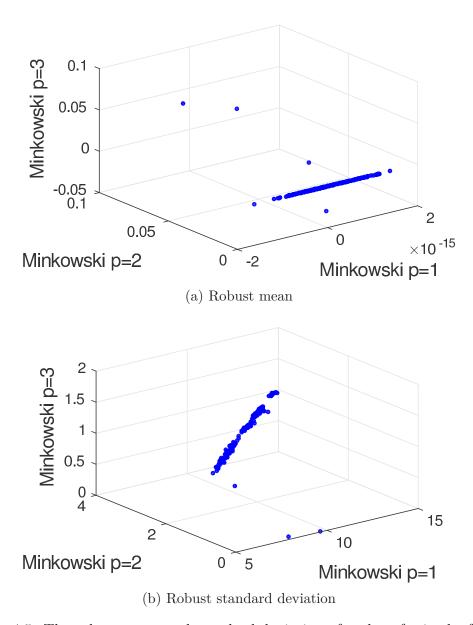

| 4.6 | ture space of three proximity-based features                                                                                                                                                                                                                 |

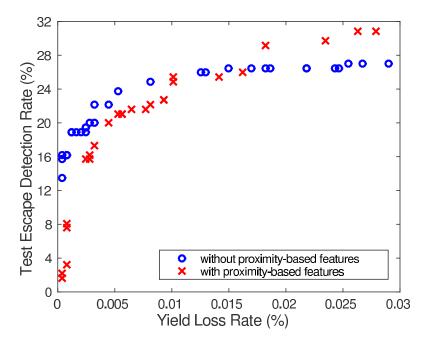

| 4.7 | The ROC curves of classification based on the base features with and without the proximity-based features.                                                                                                                                                   |

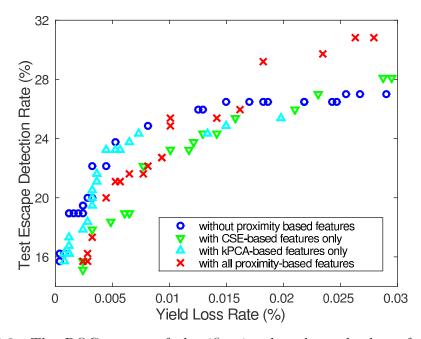

| 4.8 | The ROC curves of classification based on the base features plus different subsets of the proximity-based features                                                                                                                                           |

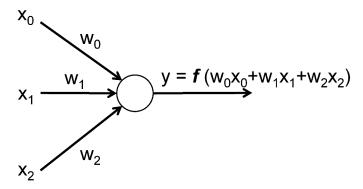

| 5.1 | An artificial neuron with three inputs and one output. The output of a neuron is the activation result of the weighted sum of the                                                                                                                            |

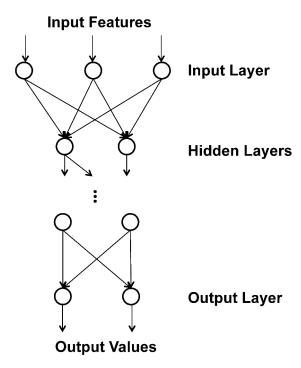

| 5.2 | neuron's inputs                                                                                                                                                                                                                                              |

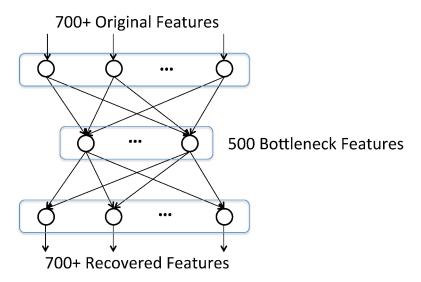

| 53  | The proposed suppercoder structure                                                                                                                                                                                                                           |

| 5.4  | The flow of using the proposed autoencoder for test escape screening | .100 |

|------|----------------------------------------------------------------------|------|

| 5.5  | The ROC curves demonstrate the classification accuracy for differ-   |      |

|      | ent structure designs of the autoencoder                             | 103  |

| 5.6  | The ROC curves of three frameworks                                   | 105  |

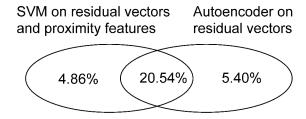

| 5.7  | The Venn diagrams of the test escape and yield loss populations      |      |

|      | resulted from the SVM on proximity features and residual vectors     |      |

|      | (the method in Chapter 4) and from the proposed autoencoder          | 106  |

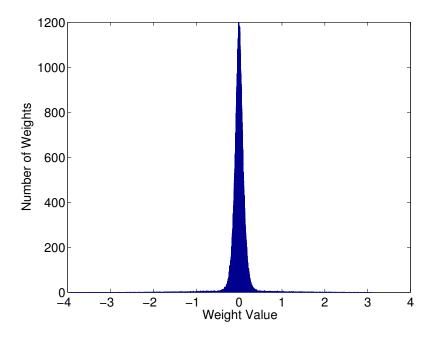

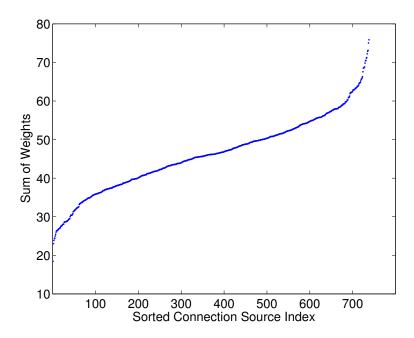

| 5.8  | The histogram of the trained weights in the hidden layer             | 107  |

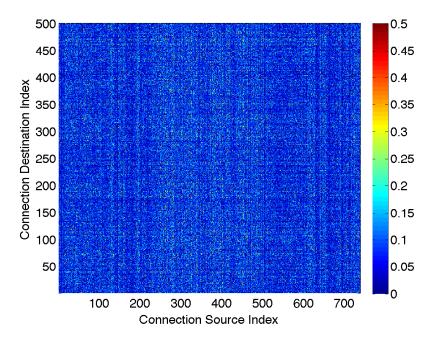

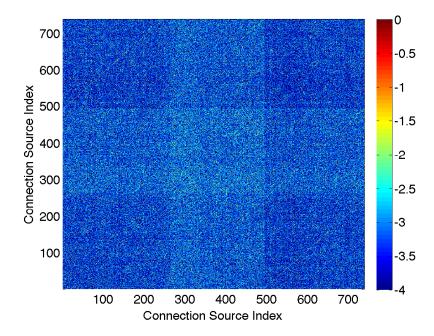

| 5.9  | The absolute values of the weights in the hidden layer as a color-   |      |

|      | coded map                                                            | 109  |

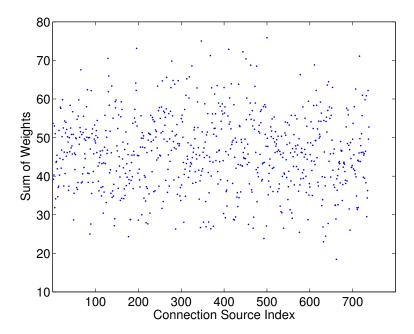

| 5.10 | The vertical sum of the absolute values of the weights in the hidden |      |

|      | layer                                                                | 110  |

| 5.11 | The sorted sum of the absolute values of the weights in the hidden   |      |

|      | layer                                                                | 111  |

| 5.12 | The correlation between each two columns of absolute values of the   |      |

|      | weights. Note that the values are in logarithmic scale               | 112  |

# List of Tables

| 2.1 | Percentage of Test Escapes Detected by C-SVC in Three Different            |    |

|-----|----------------------------------------------------------------------------|----|

|     | Spaces Based on the Validation Set                                         | 32 |

| 2.2 | Percentage of Test Escapes Detected by C-SVC in Three Different            |    |

|     | Spaces Based on the Testing Set                                            | 35 |

| 2.3 | Runtime of Deriving/Applying Transform Matrix for Canonical                |    |

|     | Transform and PCA Based on Training/Testing Set                            | 36 |

| 2.4 | Runtime of Training/Applying C-SVC Model in Three Different                |    |

|     | Spaces Based on Training/Testing Set                                       | 37 |

| 2.5 | Test Escape Identification Rate and Runtime for Applying the               |    |

|     | Models with the Yield Loss Rate Limited to 0.001%, based on $F_m \cup F_s$ | 39 |

| 3.1 | Runtime Per Wafer for Generating Each Feature Set From the Test            |    |

|     | Data                                                                       | 60 |

| 3.2 | Runtime Per Wafer for Each Step in the Statistical Test Frame-             |    |

|     | works Given $F_M \cup F_B \cup F_N$ as Input Features                      | 61 |

# Chapter 1

# Introduction

With the growing complexity and the shrinking size of modern chips, more tests have been added to the test program to assure the quality of a product, and tests are often applied multiple times under different environment settings to cover design corners. The increasing amount of tests has resulted in excessive test time and massive test data. With the help of effective data analytics, such test data has been transformed from a by-product of little value to a great source of information for better understanding the device under test (DUT). This dissertation explores and develops machine learning techniques for detecting test escapes, which are chips that pass the entire test program but fail at system-level applications, based on semiconductor production test data.

# 1.1 Correlations in Production Test Data

There exist meaningful correlations in the test data. In general, test data correlations can be classified into three types: spatial correlations, inter-test-item

correlations, and temporal correlations. Spatial patterns on a wafer have been commonly observed for various test measurements. The existence of a pattern implies that the measurement of a die is somehow correlated to the measurements of the other dies on the same wafer. The cause of spatial patterns could range from manufacturing processes, equipment settings, to test configurations such as a multi-site configuration.

There often exist correlations among measurements of multiple test items in a test program. Examples of strong inter-test-item correlations include the same test applied multiple times under different electrical and/or environmental settings and different tests testing the same functionality of the chip. Once inter-test-item correlations are identified, test items in the test program can be reordered for more efficient defect screening, some redundant test items can be removed for test time reduction, and multivariate models can be constructed for outlier detection.

Measurements of the same test item for dies in different wafers intuitively should exhibit similar patterns if the manufacturing process is stable. Such temporal correlations, across wafers and lots for measurements at the same die location, can be used to model the variation over time and manufacture/test equipment. Monitoring the temporal correlations often reveals the stability, integrity, and robustness of the manufacturing and test processes and thus is very useful for debugging.

## 1.2 Machine Learning for Detecting Test Escapes

Even with the ever growing number of tests and a test often being applied multiple times under different electrical/environmental conditions, there still exist test escapes, because system-level tests are usually not applied to all of the chips before shipment. Test escapes often have various root causes and therefore are hard to be detected with a single test. Additionally, the amount of test escapes in a mature manufacture process are typically within the range of hundreds or tens of Parts Per Million (PPM), so there are only a limited number of samples to be learned from for detecting future test escapes.

In a machine learning process, the sample data set is first split into three sets: a training set, a testing set, and an optional validation set. A training set is used for the machine learning to build a model based on, and therefore, must be statistically representative of the entire sample space, i.e. the statistical characteristics the training set possesses should accurately reflect the statistical characteristics of the entire sample set. If the training set possesses some unique characteristics that do not generalize to the rest of the samples, the learned model will not apply to the rest of the model accurately. After the learning phase, the learned model is applied to the testing set for evaluation of the performance such as prediction accuracy in a regression task or the true positive rate and the false positive rate in a classification task. In some algorithms, e.g. a support vector machine (SVM), multiple models are built based on a search of optimal values for some parameters, and a validation set is used for evaluating the models for selecting the best one.

There are, however, some challenges when applying the abovementioned ma-

chine learning framework in semiconductor production test data. First, process variation exists and could accumulate over time. That is, the training dataset created based on a certain collection of existing samples may not represent samples that are manufactured later because the manufacturing process has induced variation in the product characteristics over time. Therefore, a model learned based on the early training dataset could not be applied to the later query products. To address this problem, we need to carefully remove the wafer-to-wafer and lot-to-lot variations and have the machine learning algorithm learn only the characteristics of the chips that are immune from process variations. The developed machine learning framework must also constantly monitor how the learned model fit the newly manufactured data, and if there is a significant difference in the performance, e.g. a sudden drop of prediction accuracy, the newly manufactured samples should be checked if they are anomalies. If not, a new training set should be created to represent the new characteristics of the manufactured samples and a new model should be built based on the new training set.

When using machine learning algorithms to detect test escapes, another problem is that there are typically only a very small amount of test escapes in millions of chips. Additionally, test escapes could result from very different root causes. Therefore, it is difficult to find a universal test for detecting all test escapes. Instead, a general strategy in this dissertation is to explore multiple perspectives which could potentially reveal some abnormalities of the test escapes, and let the machine learning algorithm automatically extract the most critical information from the many perspectives to expose test escapes as anomalies.

# 1.3 Proposed Methods

It has been demonstrated that statistical analysis based on production test data, also known as *statistical tests* [1], could detect test escapes as anomalies. This dissertation further explores various state-of-the-art machine learning techniques and develops effective statistical tests.

In Chapter 2, we propose using a residual vector, which is the difference between the measured test values and some expected values, as the features for classification. Different expected values would result in different types of residual vectors, and potentially reveal different aspects of the chips under test. Therefore, our strategy is to include as many potentially useful residual vectors as possible. However, having too many features may not only increase the runtime but also deteriorate the accuracy for a machine learning classifier. To address this problem, a linear transformation called canonical analysis is proposed. Canonical analysis could compact the separation between classes of samples in a high-dimensional feature space into the first few dimensions in a transformed feature space, therefore it is used for feature reduction, followed by a classic SVM classification. The experimental results show that canonical analysis could significantly reduce the runtime of SVM and in some cases, improve the accuracy of SVM for classifying test escapes.

The framework incorporating canonical analysis and SVM, however, requires all potentially useful features (multiple types of residual vectors) to be generated first before canonical analysis can be applied during test application, which results in significant runtime and memory usage. Chapter 3 proposes using a popular framework in real-time face recognition called the *Viola-Jones* framework for

detecting test escapes. Named AdaTest, this framework is composed of a cascade of adaptive boosting (AdaBoost) classifiers. AdaBoost is an algorithm that combines multiple classifiers, referred to as the weak classifiers, into a final classifier, referred to as the strong classifier. In this framework, each weak classifier is a decision stump, which is simply a threshold set on a single feature. As a result, AdaTest would select only the most critical features without any transformation in the training phase for classification, and only these selected features need to be produced during test application. Therefore, AdaTest is significantly faster than the previous framework utilizing canonical analysis and SVM, and since there is no feature transformation in the process of learning a model, the selected features could be directly interpreted for the diagnosis of the test escapes.

In addition to canonical analysis, a collection of nonlinear transformations are introduced in Chapter 4 to reveal more abnormalities of test escapes. We calculate the pairwise proximity between each pair of samples on a wafer and include this information as the features for our analysis. To include as much potentially useful information as possible, we included seven proximity/distance functions as the nonlinear transformations that characterize the relation between of samples. For a wafer with N chips, each nonlinear transformation would result in one N by N symmetrical proximity matrix, whose elements represent the proximity of two corresponding samples. A technique called *constant shift embedding* is then applied to transform this proximity matrix back into a Euclidean vector representation so that traditional machine learning algorithms could be applied.

Chapter 5 introduces an artificial neural network (ANN) approach for detecting test escapes. Artificial neural networks have demonstrated great potential

recently in many applications such as image processing and voice recognition. For detecting test escapes, we design an autoencoder structure that is trained using only the good chip population in the training set, which is referred to as unsupervised learning. An autoencoder is an artificial neural network with the input and output layers both representing the original input features, and a bottleneck layer in which the number of neurons is smaller than that of the input/output layer. The bottleneck layer therefore contains information that is critical for representing the dataset. With the unsupervised learning process, the autoencoder fits only the good chip population and any query chip that the autoencoder model does not fit could be identified as an anomaly, which is likely a test escape.

# Chapter 2

# Canonical Analysis and SVM

### 2.1 Introduction

For many applications, the requirements of the defective parts per million (DPPM) of integrated circuits have to be extremely close to zero. Each field return found at the customer side incurs significant cost and requires thorough analysis of the cause. It has been shown that a good fraction of field returns are test escapes that pass the complete test program, but fail at system level due to their intrinsic defects [2, 3]. Applying system level tests to each chip prior to shipment, however, is undesired because it often results in high test time and cost.

This dissertation addresses the problem of identifying as many test escapes as possible by statistical analysis of the test data produced by a given test program, without taking any additional physical measurements. Such an approach can be viewed as adding statistical tests to the original test program [1]. Our main focus is on engineering novel features for statistical tests and demonstrating the

importance of feature engineering for effectively capturing test escapes by statistical tests. Specifically, we develop features based on how a chip's measurements deviate from the means of a set of normal chips and how a chip's measurements deviate from the spatial patterns on a wafer. We then transform the features to a canonical space in which the separation between normal chips and test escapes of the projected data is maximized. The multivariate statistical approach based on these features incorporates both the inter-test-item correlations and the spatial correlations, and applying statistical tests based on the transformed features achieves significant runtime reduction based on standard classification algorithms. The proposed flow can be easily extended to include more sets of features and applied to a wide range of products.

To screen potential test escapes, one technique proposed by the Automotive Electronics Council is the part average testing (PAT) [4]. For some suggested electrical tests, PAT compares the measurement of a query chip with the mean of a set of normal chips and discard the query chip if it is more than  $6-\sigma$  away from the mean. To address PAT's limitation of evaluating individual test item only and ignoring the multivariate relation among test items, several other studies proposed multivariate screening approaches that incorporate the inter-test-item correlations.

O'Neill [5] applied outlier analysis with principal component analysis (PCA) on sets of correlated test items. Sumikawa et al. [2] extended O'Neill's work with sophisticated model and test selection schemes and developed a preemptive and a reactive approach, depending on whether known field returns were given. Butler et al. [6] successfully demonstrated burn-in minimization by a collection of

multivariate analysis. Chen et al. [3] showed various data mining techniques on final test data to predict system level test (SLT) failures.

In addition to inter-test-item correlations, there exist spatial correlations among dies on the same wafer. Stine et al. [7] modeled and decomposed spatial variations into four components: wafer-level variation, die-level variation, wafer-die interactions, and residuals. In capturing the spatial patterns with only a small amount of samples, Li et al. [8] proposed a virtual probe (VP) technique and Kupp et al. [9] proposed an estimation with a Gaussian process model. Nahar et al. [10] and Riordan et al. [11] used the spatial correlation of neighboring dies for defect prediction. Sumikawa et al. [12] identified abnormal wafers based on the spatial patterns of tests.

Taking into account the multiple correlations in test data, we also investigate a data transformation technique based on multivariate analysis of variance (MANOVA). MANOVA has been used in various fields to analyze the difference in the means of features between populations of samples [13, 14]. Based on MANOVA, a canonical analysis can be applied on the samples to form a set of canonical variables which are linear combinations of the original test measurements. The linear combinations are chosen such that the first canonical variable achieves the maximum separation between populations, the second canonical variable achieves the maximum separation between populations subject to it being orthogonal to the first canonical variable, and so on. Essentially MANOVA shows if there is a significant difference in the means between populations, and the canonical analysis could identify combinations of the variables to maximize the separation between populations. In this chapter we utilize the canonical analysis

to project the features into a canonical space for further statistical tests, which can more easily screen out test escapes with standard classification methods.

The rest of the chapter is organized as the following: Section 2.2 illustrates how we develop features that represent different characteristics of a chip. Section 2.3 introduces the canonical analysis to further transform the features. The application of the proposed statistical tests is described in Section 2.4, and Section 2.5 shows experimental results on production test data. Section ?? concludes the chapter.

## 2.2 Feature Development

In our research, we use the *residual vector* of each chip as the base of input features for statistical analysis. In general, each chip with N test measurements can be characterized by an  $N \times 1$  residual vector  $\boldsymbol{r}$ :

$$r = x_m - x_e \tag{2.1}$$

where  $x_m$  is an  $N \times 1$  vector of the measured values and  $x_e$  is an  $N \times 1$  vector of the estimated values.

The residual vector represents how the measurement values of a chip deviate from its estimated values. There are two aspects we can engineer such feature. Choosing different estimated values to calculate the residual vector may reveal different test escapes, and transforming the residual vector to another space may enhance the performance of the classifier.

We first explore the choices of estimated values for calculating the residual

vector. The transformation of test data to another space will be discussed in Section 2.3.

#### 2.2.1 Measurement Mean

It has been shown that some test escapes differ from normal chips in their test measurement values relative to the measurement means [3]. Fig. 2.1 shows two wafer maps whose measurement values are standardized to the z-score by

$$z = \frac{x - \mu}{\sigma} \tag{2.2}$$

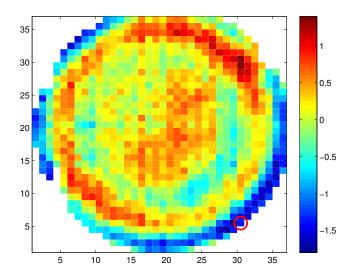

where x is the measurement value, and  $\mu$  and  $\sigma$  are the mean and standard deviation of the measurements for chips on the same wafer, respectively. In Fig. 2.1a the circled chip is a test escape with a relatively abnormal feature value based on the difference between its measurement value and the measurement mean of the entire wafer. Note that Fig. 2.1a shows only one test item and thus only one out of N features of the chips. There are other chips in the same dark blue region, which are as outlying as the circled chip is for this test item, but in the multivariate analysis they will not necessarily be classified as escapes.

## 2.2.2 Spatial Pattern

Spatial patterns have been observed on wafers in many test items [7, 15, 16, 17, 12]. Fig. 2.1b shows a test escape which would be considered abnormal based on spatial pattern analysis. A wafer's spatial patterns for some test items are the results of systematic variations which exist even without any additional man-

(a) A test escape that is abnormal with respect to measurement mean

(b) A test escape that is abnormal with respect to spatial pattern

Figure 2.1: Examples of test escapes which are considered abnormal with respect to different estimated values.

using the unique predicted value at each die location (derived from the test item's learned spatial pattern) as the estimated value, we effectively eliminate the systematic variations and incorporate only the effects of other variations (including random variations) in the residual vector. In other words, with this revised residual vector which takes into account test items' spatial patterns, we more accurately capture the noises in the wafer map images. We employ bilateral filtering, a well-developed filtering technique in image processing, to denoise a wafer map and retrieve a systematic spatial pattern of a test item.

Bilateral filtering [18] is a non-linear filtering technique which extends the concept of Gaussian filtering to weight coefficients based on both relative spatial distance and pixel intensity difference. Pixels that are spatially close but have significant difference in intensity will have smaller weights, while pixels that are a bit farther apart but very similar in intensity will have larger weights. Therefore, the sharp edges of an image can be preserved and the noises are more likely to be filtered. There are two kernels for evaluating the weights of the neighboring pixels. The domain kernel  $K_d$  evaluates the weights based on the spatial distance of pixels. The range kernel  $K_r$  evaluates the weights based on the pixel intensity difference.

Given the original image I, pixel coordinates x, and the filter window  $\Omega$ , the filtered image  $I_f$  is defined as

$$I_f(x) = \frac{1}{W_p} \sum_{x_i \in \Omega} I(x_i) K_r(\|I(x_i) - I(x)\|) K_d(\|x_i - x\|)$$

(2.3)

where

$$W_p = \sum_{x_i \in \Omega} K_r(\|I(x_i) - I(x)\|) K_d(\|x_i - x\|)$$

(2.4)

For a  $P \times Q$  wafer map with values ranging from  $v_{min}$  to  $v_{max}$ , we choose a Gaussian function with  $\sigma = min(P,Q)/16$  for  $K_d$ , a Gaussian function with  $\sigma = (v_{max} - v_{min})/10$  for  $K_r$ , and the whole wafer map as the filter window  $\Omega$ .

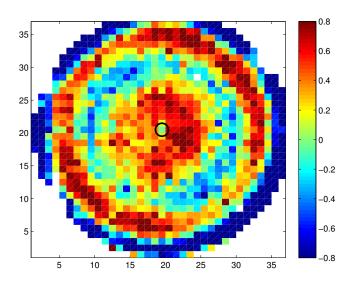

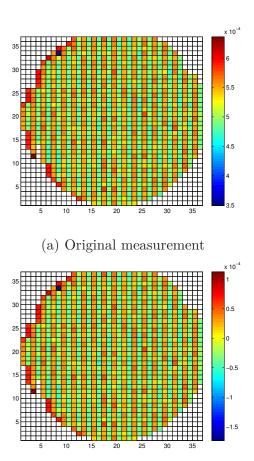

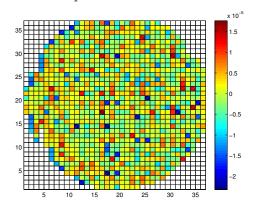

Fig. 2.2 shows the result of applying bilateral filter to one test item on a wafer map. Fig. 2.2a shows the original measurement of the test item. The residual of the measurement with respect to the wafer mean is shown in Fig. 2.2b, in which the spatial pattern is preserved. The residual of the measurement with respect to the bilateral filtered wafer map is shown in Fig. 2.2c, in which the spatial pattern in the original measurement is eliminated and the residuals better represent abnormality with respect to the spatial pattern.

Note that the circled test escape in Fig. 2.1a is abnormal considering its relatively large measurement value, but it is perfectly normal if we take into account the overall spatial pattern. The circled test escape in Fig. 2.1b is abnormal in the spatial pattern, but its measurement value is actually very close to the mean of the wafer. Therefore, each of the two test escapes shown in Fig. 2.1 can only be uniquely identified as abnormal, or potential test escape, by one of the two choices in selecting the estimated values for calculating residual vectors.

### 2.3 Feature Transformation

Besides exploring two different choices of the estimated values for calculating the residual vectors to enrich the input features, projecting these features into

(b) Residual with respect to the mean of the measurement

(c) Residual with respect to the bilateral filtered measurement

Figure 2.2: An example of residuals with respect to different estimated values of one test item.

different spaces before applying statistical tests may help improve the performance of classifiers. We introduce canonical analysis based on multivariate analysis of variance (MANOVA) to transform data into a canonical space in which the data of test escapes and normal chips are maximally separated in the first few dimensions.

Multivariate analysis of variance (MANOVA) [13] is a technique that, given g populations of samples in an N-dimensional space, compares the mean vectors of the populations and investigates which mean components differ significantly. Given the populations of samples:

Population

$$1: \boldsymbol{x}_{11}, \boldsymbol{x}_{12}, ... \boldsymbol{x}_{1n_1}$$

Population  $2: \boldsymbol{x}_{21}, \boldsymbol{x}_{22}, ... \boldsymbol{x}_{2n_2}$

$$\vdots$$

Population  $g: \boldsymbol{x}_{g1}, \boldsymbol{x}_{g2}, ... \boldsymbol{x}_{gn_q}$

$$(2.5)$$

where  $x_{ij}$  is an  $N \times 1$  vector of the jth sample in the ith population, and  $n_i$  is the number of samples in the ith population.

Each observation  $x_{ij}$  can be decomposed into three components: overall sample mean  $\bar{x}$ , the population effect  $(\bar{x}_i - \bar{x})$ , and the residual  $(x_{ij} - \bar{x}_i)$ , and

$$x_{ij} = \bar{x} + (\bar{x}_i - \bar{x}) + (x_{ij} - \bar{x}_i)$$

(2.6)

Subtracting  $\bar{x}$  from both sides of (2.6) and summing the cross products over i and

j yields

$$\sum_{i=1}^{g} \sum_{j=1}^{n_i} (\boldsymbol{x}_{ij} - \bar{\boldsymbol{x}}) (\boldsymbol{x}_{ij} - \bar{\boldsymbol{x}})'$$

$$= \sum_{i=1}^{g} n_i (\bar{\boldsymbol{x}}_i - \bar{\boldsymbol{x}}) (\bar{\boldsymbol{x}}_i - \bar{\boldsymbol{x}})' + \sum_{i=1}^{g} \sum_{j=1}^{n_i} (\boldsymbol{x}_{ij} - \bar{\boldsymbol{x}}_i) (\boldsymbol{x}_{ij} - \bar{\boldsymbol{x}}_i)'$$

(2.7)

or expressing it as:

$$S = B + W \tag{2.8}$$

where

$$S = \sum_{i=1}^{g} \sum_{j=1}^{n_i} (\mathbf{x}_{ij} - \bar{\mathbf{x}}) (\mathbf{x}_{ij} - \bar{\mathbf{x}})'$$

$$B = \sum_{i=1}^{g} n_i (\bar{\mathbf{x}}_i - \bar{\mathbf{x}}) (\bar{\mathbf{x}}_i - \bar{\mathbf{x}})'$$

$$W = \sum_{i=1}^{g} \sum_{j=1}^{n_i} (\mathbf{x}_{ij} - \bar{\mathbf{x}}_i) (\mathbf{x}_{ij} - \bar{\mathbf{x}}_i)'$$

(2.9)

Eq. (2.8) shows that the total variance  $\mathbf{S}$  is the sum of the between-population variance  $\mathbf{B}$  and the within-population variance  $\mathbf{W}$ . After such decomposition, MANOVA investigates if there exists significant difference between the population mean vectors using metrics based on  $\mathbf{B}$  and  $\mathbf{W}$ . For example, if the Wilks' lambda

$$\Lambda = \frac{|\boldsymbol{W}|}{|\boldsymbol{B} + \boldsymbol{W}|} \tag{2.10}$$

is too small, we can conclude that there exists significant difference between the populations.

After MANOVA, the canonical analysis suggested in [14] could be used to create a set of canonical variables which are the linear combinations of the original variables. The criteria for choosing the linear combinations are that the first canonical variable should exhibit the maximum separation between the populations, the second canonical variable should be orthogonal to the first canonical variable while also exhibit maximum separation between the populations, and so on.

The process of generating the canonical variables in canonical analysis is similar to generating the principal components (PCs) in principal component analysis (PCA) [13]. PCA is a feature reduction technique that generates a set of new features, named principal components, which are mutually orthogonal and are ordered by the amount of variability in the data each PC explains. Given a set of data in matrix X, where rows of X represent observations, and columns of Xrepresent variables, PCA creates the first PC, the linear combination of variables that can maximally explain the multivariate variability in X, using the eigenvector of the covariance matrix X'X with the largest eigenvalue. The second PC is the eigenvector of X'X with the second largest eigenvalue, which explains the maximum variability of X subject to it being orthogonal to the first PC. In canonical analysis, canonical variables are chosen based on the ability of explaining the ratio of the between-population variance B over the within-population variance W, so that in the first canonical variable the populations are maximally separated. Therefore, the first canonical variable is derived as the eigenvector of  $oldsymbol{W}^{-1}oldsymbol{B}$  with the largest eigenvalue, the second canonical variable is chosen as the eigenvector of  $W^{-1}B$  with the second largest eigenvalue, and so on.

Let E be the matrix whose first column is the first eigenvector of  $W^{-1}B$ , the second column is the second eigenvector, and so on, and each eigenvector is scaled such that the within-population variance of the canonical variable is 1. A new data set Y can be projected to the canonical space by

$$Y_p = Y_c E \tag{2.11}$$

where  $Y_c$  is Y with columns centered by subtracting their means and  $Y_p$  is the projected data set.

Both PCA and canonical analysis project data to another space by linear transformation, but the objectives of the transformations are quite different. PCA orders the created variables according to the amount of the variability in the data the variables can explain, while canonical analysis orders the created variables according to the amount of the between-population variance over the within-population variance the variables can explain. Both PCA and canonical analysis can be used for feature reduction. With a limited number of created variables which is smaller than the dimension of the original data, PCA preserves the variability of the data and canonical analysis preserves the separation between the populations of the data. Because the separation between populations is compacted into a small number of variables, the populations of data will be maximally separated in the space formed by the first few canonical variables, and a standard classification algorithm can much more easily classify the samples.

In multivariate statistical analysis, the canonical analysis can be regarded as canonical correlation analysis [14, 19, 20] between the dependent variables and some dummy variables. The description above for the process of deriving the canonical variables is similar to Fisher's linear discriminant analysis (LDA) [21], in which the canonical variables are known as discriminants. Applying the canonical analysis to our application, we categorize the normal chips as one population and the test escapes as the second population, and create the canonical variables by linear combinations of the test items.

# 2.4 Test Methodology

Based on the feature engineering scheme discussed in Sections 2.2 and 2.3, we propose to use two distinct sets of features. The first set of features are the residual vectors with measurement means as the estimated values, followed by the transformation to the canonical space. The second set of features are the residual vectors which use predicted values from the learned spatial patterns as the estimated values, followed by the transformation to the canonical space.

The two sets of features can be utilized in two ways. First, each set of features is used as the input features for one classifier - determining if the chip under test belongs to the normal population or test escape population, and the classifiers together form a series of statistical tests. A second possible way of utilizing the features is to include all sets of features to form a single comprehensive statistical test. The exemplar test flows are demonstrated in this section.

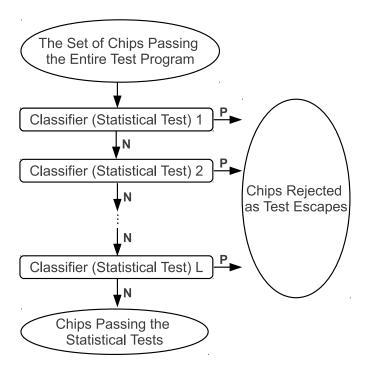

Figure 2.3: Test flow with sequential statistical tests

#### 2.4.1 Classifier

We use the *C-support vector classification (C-SVC)* algorithm provided by the SVM library LIBSVM [22] as our classifier for separating test escapes and good chips. Given the fact that the two classes of samples are very imbalanced (i.e. the number of good chips is much greater than the number of test escapes) in a practical training set, one can set a much higher weight for the class of test escapes to force the algorithm to always find a model that correctly identifies escapes [23]. The guideline for our classification, however, is to screen out as many escapes as possible subject to the constraint of limiting the yield loss to a very small number (say, less than 0.001%). Based on this guideline, each class in the C-SVC is given the same weight in our experiment to allow a thorough search for a model with the maximum number of correctly identified escapes while minimizing the yield loss to a level very close to 0.

# 2.4.2 Pre-test Analysis

To start the proposed statistical tests, the canonical variables and the C-SVC models based on the search for the optimal combination of parameters [22] need to be generated based on a set of training chips, and the optimal C-SVC model needs to be selected based on a set of validation chips. The training/validation set of good chips should be sampled across several lots and wafers, and the distribution of measurements in each lot should be checked for uniformity to validate that the training/validation set indeed properly represents a good-chip population. Some field returns (or known test escapes that pass the test program) are also required for finding the canonical variables and the classification models. Section 2.5 will

show that only a very small ratio of returns/known test escapes is required in order to find a canonical space for achieving significant runtime reduction while preserving the discriminating power between the test escapes and the normal population.

Figure 2.4: Test flow with a comprehensive statistical test

## 2.4.3 Test Application

An exemplar test flow of the proposed statistical tests, applied to each wafer/lot, is shown in Fig. 2.3. These statistical tests are performed after all physical tests

are executed, and serve as additional *rejectors* which reject some of the bad chips that escape all physical tests. While in this chapter we suggest two specific statistical tests only, additional statistical tests can be developed and applied based on more new features.

A modification from Fig. 2.3 is shown in Fig. 2.4, in which the sequential statistical tests are replaced with one single comprehensive statistical test. With the application of canonical transform, the useful information in separating the test escapes and the normal population in all generated features is incorporated into the comprehensive test. An experimental comparison on the two exemplar flows will be made in Section 2.5.

Given any training set, it is possible that the manufacturing process drifts over time such that the training set is no longer sufficiently representative for the later data. Therefore, if the proposed statistical tests report an abnormally large number of test escapes for a wafer/lot under test, it could be due to such temporal process variation and thus the wafer/lot should be analyzed for the actual cause. If the wafer/lot is diagnosed as an outlier wafer/lot, we can conclude that the training set still effectively represents the population of good chips, and the test flow can continue to the next wafer/lot without a new training set. Otherwise, a new training set should be established and the corresponding canonical variables and C-SVC models should in turn be derived.

# 2.5 Experimental Result

To validate the proposed methods, the continue-on-fail production test data of a high volume commercial product was first preprocessed to remove confidential information while accurately preserving the information critical to the evaluation. The data set contains more than 1200 wafers with more than 200 parametric test measurements captured by the production test program for each die, and have more than 700 dies per wafer. In the following discussion we use N to denote the number of parametric test measurements.

Since there is no actual test escape information in this data set, we first introduce how to *emulate* test escapes for our evaluation, and then validate our proposed methodology based on the data set.

## 2.5.1 Data Setup

In a test program, chips with measurements beyond the test limits are rejected as faulty chips, and those pass the test program but fail later at the system level or in the field (field returns) are test escapes. Without actual test escape information, we identified a set of bad chips as *emulated* test escapes which meet the following criterion: among the over 200 measurements, only one measurement did not fall within its test limits and its violation to the spec was marginal. We therefore *hid* this failing measurement which rejected these faulty chips - pretending that each of these bad chips still passed all physical tests in the test program and is treated as a test escape. To hide this measurement which failed a chip, we replaced its value by a normal value well within the test limits such that the resulting

feature value (i.e. an element of the chip's residual vector) is equal to the median of all good chips. After such manipulation, these faulty chips now have similar characteristics as test escapes: passing the complete test program, but with some intrinsic defects. We can then evaluate if the measurements of all-but-one test items which did not violate the test limits can expose those *emulated* test escapes in the proposed statistical tests.

The goal of our analysis is to screen test escapes based on the subtle differences in the non-failing measurements, so we only considered those faulty chips with a very small number of failing measurements and insignificant violations to the test specs as emulated test escapes. Faulty chips which fail many test items and/or have significant violations to the test specs are more likely to be catastrophic failures. Such catastrophic failures should have very revealing and differentiable features derived from the non-failing measurements, and including those catastrophic failures could result in an overly optimistic conclusion of the experiment. Therefore, we excluded faulty chips with more than one failing measurements or with only one failing measurement but its violation to the spec is significant from our analysis.

## 2.5.2 Sequential Rejectors

In pre-test analysis, test data from 200 wafers were used as the training set for finding the canonical variables and generating C-SVC models based on the search for the best combination parameters. Test data from another 300 wafers were used as the validation set for selecting the best C-SVC model with an acceptable level of yield loss.

For simplicity and clarity, we use the following notations for the different residual vectors:

- Feature Set  $F_m$ : Residual vectors derived using measurement means as the estimated values

- Feature Set  $F_s$ : Residual vectors derived using predicted values based on the learned spatial patterns as the estimated values

After the canonical space is found based on the training set, the residual vectors of the validation set are transformed into the canonical space by Eq. (2.11). For comparison, we also transform these residual vectors into the PC space by PCA. Fig. 2.5 illustrates the feature set  $F_m$  transformed into the PC space and the canonical space respectively (with respect to the first three variables created in each of these two analyses). Fig. 2.6 shows feature set  $F_s$  transformed into the PC space and the canonical space respectively. For better visualization, Fig. 2.5 and Fig. 2.6 show only a subset of good chips and emulated test escapes (they were randomly sampled from the validation set while maintaining the original ratio of good chips vs. test escapes). It is very clear that the test escapes are much more separable from the normal population in the canonical space than in the PC space for both  $F_m$  and  $F_s$ .

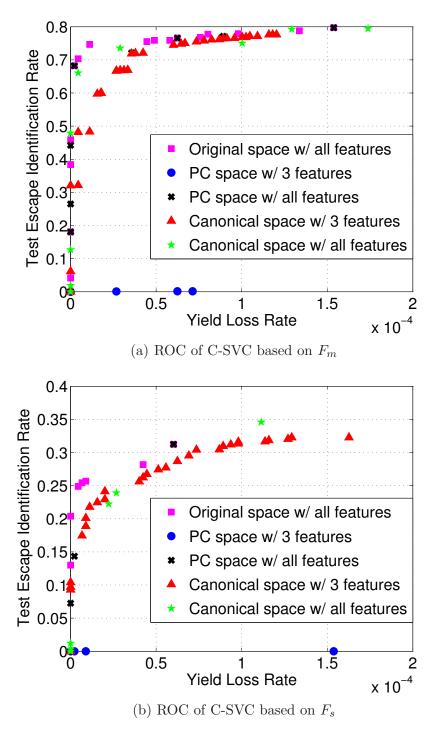

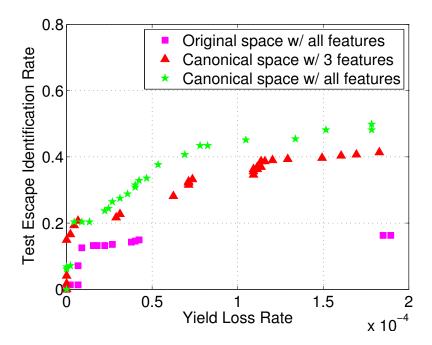

Fig. 2.7 shows the relative operating characteristics (ROC) diagram of C-SVC's performance based on  $F_m$  and  $F_s$  in the original space, the PC space, and the canonical space. The horizontal axis shows the yield loss rate and the vertical axis shows the test escape identification rate, which are the *false positive rate* and the *true positive rate* respectively in our classification problem. Using all

Figure 2.5: The distributions of good chips/test escapes in different feature spaces of  $F_m$ .

Figure 2.6: The distributions of good chips/test escapes in different feature spaces of  $F_s$ .

features in the three spaces results in similar classification performances because the discriminating information is preserved in the linear transformation to a new space. When only three features are used for the purpose of feature reduction, using the first three canonical variables as input features results in significantly greater classification accuracy than using the first three PCs, which explain only 25% and 21% of the variability in  $F_m$  and  $F_s$  respectively.

Table 2.1 shows the ratio of test escapes identified by C-SVC in the N-dimensional original feature space, 3-dimensional PC space, and 3-dimensional canonical space, with a limit of 0.001% yield loss for all three cases. The first column shows the ratio of test escapes identified only by  $F_m$  and not detectable by  $F_s$ . The second column shows the ratio of test escapes identified only by  $F_s$  and not detectable by  $F_m$ , and the third column shows the ratio of the union of the test escapes identified by  $F_m$  and  $F_s$ . C-SVC in the 3-dimensional PC space cannot identify any of the test escapes given the very low yield loss rate limit, while C-SVC in the 3-dimensional canonical space achieves a lower but still significant ratio of identified test escapes than C-SVC with all the features in the original space.

For a fixed yield loss budget (0.001% in this experiment), the learned C-SVC models based on different sets of features can identify unique sets of escapes. In the canonical space, there are 11.0% of the escapes that can be identified based on both  $F_m$  and  $F_s$ , while the classifications based on  $F_m$  and  $F_s$  identify unique sets of 37.2% and 9.1% of the escapes, respectively.

To better visualize a feature set's ability of uniquely identifying test escapes, Fig. 2.8 shows the distribution of identified test escapes in the canonical space of

Figure 2.7: The ROC diagram for C-SVC based on  $F_m$  and  $F_s$  in three different spaces.

Table 2.1: Percentage of Test Escapes Detected by C-SVC in Three Different Spaces Based on the Validation Set

|                                                          | Detected by Feature Set |            |                |

|----------------------------------------------------------|-------------------------|------------|----------------|

|                                                          | $F_m$ only              | $F_s$ only | $F_m$ or $F_s$ |

| C-SVC in $N$ -D original space <sup><math>a</math></sup> | 45.7%                   | 3.2%       | 71.4%          |

| C-SVC in 3-D PC space                                    | 0%                      | 0%         | 0%             |

| C-SVC in 3-D canonical space                             | 37.2%                   | 9.1%       | 57.3%          |

<sup>&</sup>lt;sup>a</sup>N: Number of Test Measurements (> 200)

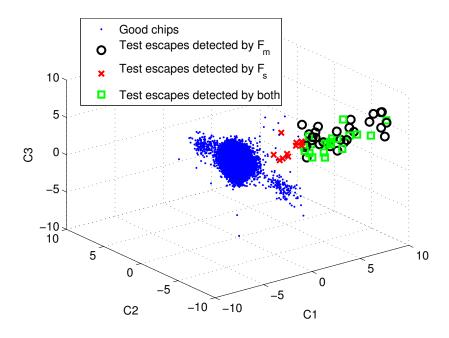

$F_m$ . It is clear that  $F_s$  reveals some test escapes that are close to the normal population in the canonical space derived from  $F_m$ , which C-SVC in this space cannot correctly classify without incurring additional yield loss. Therefore, it is important to incorporate both sets of features to screen test escapes more effectively.

## 2.5.3 Comprehensive Test

In addition to applying canonical transform to  $F_m$  and  $F_s$  separately, we can apply canonical transform to  $F_m$  and  $F_s$  together, considering them as a single feature set for the classification problem. In this case, the proposed framework becomes even more extensible as one can generate many possible features and input them all into the canonical transform without knowing which sets of features are more suitable for which product. A general feature set can be developed and applied to different products efficiently since canonical transform automatically generates the most discriminating features out of all possible features for each product. The test flow is shown in Fig. 2.4 in Section 2.4.

Fig. 2.9 shows the distribution of good chips and test escapes in the canonical space derived from  $F_m \cup F_s$ , i.e. a canonical variable is a linear combination of all

Figure 2.8: The distributions of good chips and test escapes detected by the two sets of features in the canonical space of  $F_m$ .

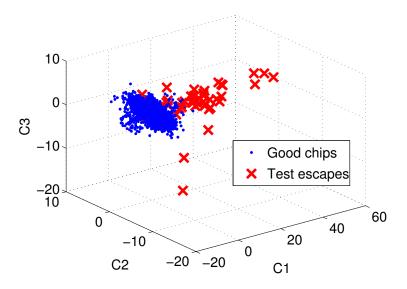

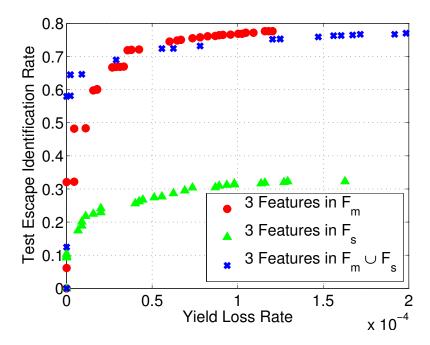

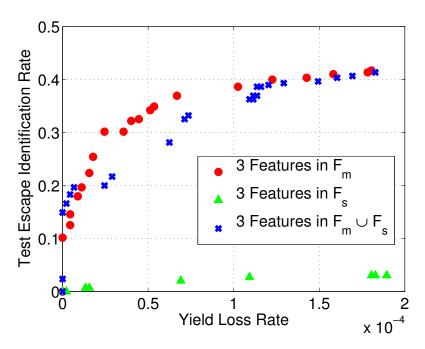

features in  $F_m$  and all features in  $F_s$ . There is a clear separation between the good chips and the test escapes. Fig. 2.10 shows the ROC curves of using 3 canonical variables derived from  $F_m$ ,  $F_s$ , and  $F_m \cup F_s$ , as the input features for C-SVC. When the yield loss rate is very low (< 0.001%), using the canonical variables derived from  $F_m \cup F_s$  identifies 64.6% of the test escapes, which is higher than using the canonical variables derived from  $F_m$  or  $F_s$  alone. Compared with the results in Table 2.1, using canonical variables derived from  $F_m \cup F_s$  identifies more test escapes than the union of the test escapes identified using the canonical variables derived from  $F_m$  and the canonical variables derived from  $F_s$ . In other words, using a single comprehensive test derived from all generated features achieves greater accuracy than using a sequence of rejectors, each of which is derived from

a unique set of features.

Figure 2.9: The distributions of good chips/test escapes in the canonical space derived from  $F_m \cup F_s$ .

## 2.5.4 Test Application

The testing set of our data includes more than 700 wafers containing more than 500K chips. The percentage of detected test escapes based on the testing set, given a yield loss budget of 0.001%, is shown in Table 2.2. The classification performance is greatly enhanced in the canonical space than that in the PC space. Using the canonical variables derived from  $F_m \cup F_s$  also results in much better accuracy than using the canonical variables derived from  $F_m$  or  $F_s$  alone. Note that in the original space there are N dimensions in  $F_m$  and  $F_s$ , 2N dimensions in  $F_m \cup F_s$ , where N is the number of test measurements.

The following two tables show the runtimes executed on an Intel Xeon Quad-

Figure 2.10: The ROC diagram for C-SVC in canonical space with 3 features derived from different feature sets.

Table 2.2: Percentage of Test Escapes Detected by C-SVC in Three Different Spaces Based on the Testing Set

|                              | Feature Set |       |                |

|------------------------------|-------------|-------|----------------|

|                              | $F_m$       | $F_s$ | $F_m \cup F_s$ |

| C-SVC in original space      | 64.4%       | 23.6% | 67.1%          |

| C-SVC in 3-D PC space        | 0%          | 0%    | 0.07%          |

| C-SVC in 3-D canonical space | 43.4%       | 17.1% | 61.9%          |

core 3.6GHz system. The data is based on the comprehensive test, in which the canonical variables are derived from  $F_m \cup F_s$ .

The runtime for canonical transform and PCA to derive the transform matrix based on the training set and to apply the transform on the testing set is shown in Table 2.3. While it takes slightly longer to derive the transform matrix for canonical transform during the training process, the time for applying the transform is very close for both transforms.

Table 2.3: Runtime of Deriving/Applying Transform Matrix for Canonical Transform and PCA Based on Training/Testing Set

|                     | Transform           |                     |  |

|---------------------|---------------------|---------------------|--|

| Canonical Transform |                     | PCA                 |  |

| Derivation          | $5.55 \mathrm{\ s}$ | $3.56 \mathrm{\ s}$ |  |

| Application         | $0.75 \mathrm{\ s}$ | $0.78 \; s$         |  |

Table 2.4 shows the runtime of training the C-SVC model based on the training set and applying the C-SVC model to the testing set. Training in the canonical space is much easier because most of the separating power in the data is compacted into the 3 input features for C-SVC. A runtime reduction of 63X and 29X is achieved for training and applying the model in the canonical space. In application of the proposed statistical test to the test flow, it takes 0.75s + 8.41s to transform the features and apply the model to more than 700 wafers, resulting in less than 0.013s additional test time per wafer.

Table 2.4: Runtime of Training/Applying C-SVC Model in Three Different Spaces Based on Training/Testing Set

|             | Feature Space |                  |                     |

|-------------|---------------|------------------|---------------------|

|             | 2N-D Original | 3-D Canonical    | 3-D PC              |

| Training    | 31.27  s      | $0.50 \; { m s}$ | $3.42 \mathrm{\ s}$ |

| Application | 242.16 s      | 8.41 s           | 74.87 s             |

#### 2.5.5 Another Experimental Scenario

The emulated data set based on the previous description contains 3500PPM of test escapes, a good fraction of which are detected by a very small number of test items. In order to capture a more realistic scenario for which each test item detects only a small number of emulated test escapes, we removed some escapes from the original emulated test escape population (of 3500PPM) so that each test item only detects a limited number of escapes in the resulting test escape population. Specifically, we identified those test items that hiding each of them would result in greater than 50PPM in the original test escape population. We then removed those emulated escapes detected by these test items, resulting in a reduced emulated test escape population of 600PPM.

Based on the data set with a reduced number of test escapes, the ROC curves for C-SVC with  $F_m \cup F_s$  as the input features are shown in Fig. 2.11. Note that in this case, C-SVC in the canonical space, even with only the first 3 dimensions, achieves greater classification accuracy than C-SVC in the original space with all 2N features. For a yield loss rate limited to 0.001%, Table 2.5 shows the test escape identification rate and the corresponding runtime for applying the model. In this data set, effectively compacting the separation between classes into the

very few dimensions allows more effective and efficient classification for C-SVC than that in the original space with much more dimensions.

Figure 2.11: The ROC diagram for C-SVC based on  $F_m \cup F_s$  in the original space and in the canonical space.

Fig. 2.12 shows the ROC diagram of classification based on 3 canonical variables derived from  $F_m$ ,  $F_s$ , and  $F_m \cup F_s$ . Given the yield loss rate limited to 0.001%, the ratio of identified test escapes are 14.6%, 0.7%, and 16.3%, respectively. While the identification rate drops for the three cases compared with that in the original data set, classification based on the canonical variables derived from  $F_m \cup F_s$  still achieves better accuracy than using the canonical variables derived from  $F_m$  or  $F_s$  alone, and the identification rate of test escapes is still significant under the constraint of a close-to-zero limit on yield loss rate.

Table 2.5: Test Escape Identification Rate and Runtime for Applying the Models with the Yield Loss Rate Limited to 0.001%, based on  $F_m \cup F_s$

|                                    | Feature Space |               |                |

|------------------------------------|---------------|---------------|----------------|

|                                    | 2N-D Original | 3-D Canonical | 2N-D Canonical |

| Test Escape<br>Identification rate | 12.5%         | 19.7%         | 20.3%          |

| Application<br>Runtime             | 176.19 s      | 4.63 s        | 19.44 s        |

Figure 2.12: The ROC diagram for C-SVC in canonical space with 3 features derived from different feature sets, based on a data set with a reduced number of test escapes described in Section 2.5.5.

# 2.6 Summary

Through feature engineering, we propose two sets of features to characterize the health of chips. We demonstrate that statistical tests based on each set of features could uniquely identify some test escapes that the other set of features cannot reveal. As adding more features may reveal more test escapes, we further propose to transform these features into a canonical space for feature reduction. Classification performed by the statistical tests on the reduced dimensions in canonical space achieves 29X runtime reduction while achieving a significantly higher accuracy than PCA in our experiment. We can expect further improvement if more types of features are added into the framework, followed by feature reduction through canonical analysis. Using our data set with emulated test escapes, we demonstrated that classification in a 3-dimensional canonical space can achieve greater accuracy than that in the original space with 200+ dimensions.

While C-SVC is used as the classification engine to evaluate various aspects of feature engineering proposed in the chapter, other classifiers can also be used. The scheme to utilize statistical tests containing the proposed features is flexible and can be easily extended to accommodate more types of statistical tests.

# Chapter 3

# AdaTest

# 3.1 Introduction

Statistical tests [1], which are statistical analyses following the physical test program, could help screen test escapes and outliers utilizing the hidden correlations in test data without additional physical measurements. In recent studies for outlier screening, O'Neill [5] and Sumikawa et al. [2] investigated the distribution of the population under test using principal component analysis (PCA) on correlated test items, and Krishnan and Kerkhoff [24] explored multiple Mahalanobis distances as the metric for screening. Chen et al. [3] also demonstrated various data mining techniques in predicting system-level test (SLT) failures.

Daasch et al. [25] proposed a concept of residual for outlier screening and demonstrated its applications considering the neighboring chips as the reference for deriving the residual, called nearest neighbor residual (NNR), in [26, 27, 28, 29]. In Chapter 2, we proposed a feature engineering framework which utilizes two