## **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

High-Performance Grid-Tied Single-Phase Power Converter Design with Applications in Electric Vehicle Charging and Residential Photovoltaic Systems

#### **Permalink**

https://escholarship.org/uc/item/91k9s53m

#### **Author**

Fernandez, Kelly

#### **Publication Date**

2023

Peer reviewed|Thesis/dissertation

# High-Performance Grid-Tied Single-Phase Power Converter Design with Applications in Electric Vehicle Charging and Residential Photovoltaic Systems

By

Kelly M. Fernandez

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Robert Pilawa-Podgurski, Chair Professor Kristofer Pister Associate Professor Duncan Callaway

Fall 2023

# High-Performance Grid-Tied Single-Phase Power Converter Design with Applications in Electric Vehicle Charging and Residential Photovoltaic Systems

Copyright 2023 By Kelly M. Fernandez

#### Abstract

High-Performance Grid-Tied Single-Phase Power Converter Design with Applications in Electric Vehicle Charging and Residential Photovoltaic Systems

By

#### Kelly M. Fernandez

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Associate Professor Robert Pilawa-Podgurski, Chair

Single-phase power converters enable people to connect any electronic device to the ac grid. As the electricity demand of our world continues to grow, it is crucial to continually research and develop novel power electronic technologies that have improved performance. Specifically, traits of minimal power loss, high volumetric power density, high gravimetric power density, high levels of reliability, and long lifetimes are desired.

In the first part of this thesis, a novel two-stage power converter design is proposed for the application of level-2 electric vehicle on-board charging. For the ac-to-dc rectification stage, a hybrid-switched capacitor converter, which utilizes the ultra-high energy densities of class two ceramic capacitors to minimize the passive component sizing of the converter, is proposed. For the energy buffer stage of the on-board charger, an active buffer topology that minimizes the system's physical volume and weight without compromising efficiency is presented. The active buffer topology in the electric vehicle charger is further investigated, with a novel control and circuit topology introduced that significantly reduces any voltage and current ripple along the dc-link.

In the second part of this thesis, a novel two-stage inverter solution is proposed for a residential microinverter. The inverting stage of the microinverter is divided into two parts: a step-up stage and an inverting stage. Both parts are implemented with hybrid switched-capacitor converter topologies to (1) reduce system volume through leveraging the high energy densities of capacitors and (2) increase system efficiency by utilizing lower voltage switches with high figures of merit and soft-switching techniques. The passive component volume and switching stress of the step-up stage are theoretically analyzed and compared to other converter topologies, showcasing it as a practical converter choice for the microinverter application space. This two-part inverting stage creates a high voltage dc bus where the energy buffer can be placed in the system. This reduces the required buffer capacitance,

enabling the engineer to have a broader range of capacitor choices to design a more reliable and energy-dense system.

Overall, this thesis showcases the design and utilization of several hybrid switched-capacitor converters, active buffer topologies, and control in the single-phase application area. Modeling and theoretical analysis techniques of power converter volume and power stress are explained in detail. High-performance hardware prototypes, experimental results, and test setup designs are included.

To my family and friends.

A mi familia y amigos.

# Contents

| $\mathbf{C}$ | Contents                                                                                       | ii                               |

|--------------|------------------------------------------------------------------------------------------------|----------------------------------|

| Li           | ist of Figures                                                                                 | iv                               |

| Li           | ist of Tables                                                                                  | xi                               |

| 1            | Introduction 1.1 Introduction                                                                  | 1<br>1<br>1                      |

| 2            | Fundamentals of Power Converters in Single-Phase Systems  2.1 Single-Phase System Architecture | 4<br>4<br>6<br>8                 |

| Ι            | Single-Phase Power Conversion for Electric Vehicle Charging Applications                       | 12                               |

| 3            | Electric Vehicle On-Board Charger  3.1 Introduction                                            | 13<br>13<br>15<br>17<br>27<br>31 |

| 4            | Series-Stacked Buffer with and without the Charge Injection Method 4.1 Introduction            | 33<br>33<br>35<br>38<br>45       |

| II |       | ulti-Level Power Converters for Residential Solar Panel croinverter Applications | <b>52</b> |

|----|-------|----------------------------------------------------------------------------------|-----------|

| 5  | Res   | idential Solar Panel Survey                                                      | 53        |

|    | 5.1   | Motivation for a Residential Solar Panel Survey                                  | 53        |

|    | 5.2   | Overview of Solar Panel Survey                                                   | 53        |

|    | 5.3   | Findings of Solar Panel Survey                                                   | 54        |

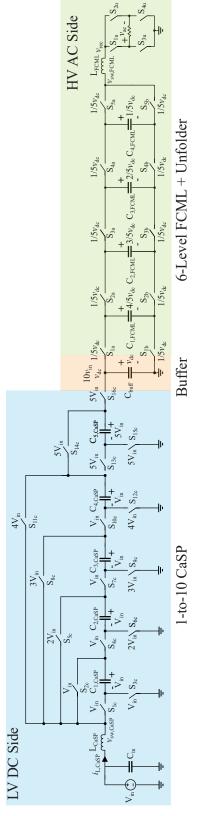

| 6  | A 1   | -to-10 Cascaded Series-Parallel Converter                                        | 57        |

|    | 6.1   | Introduction                                                                     | 57        |

|    | 6.2   | Cascaded Series-Parallel (CaSP) Passive Component Volume and Switch              |           |

|    |       | Stress Analysis                                                                  | 58        |

|    | 6.3   | 1-to-10 CaSP Principles of Operation                                             | 69        |

|    | 6.4   | Hardware Validation and Experimental Results                                     | 72        |

|    | 6.5   | Conclusion                                                                       | 78        |

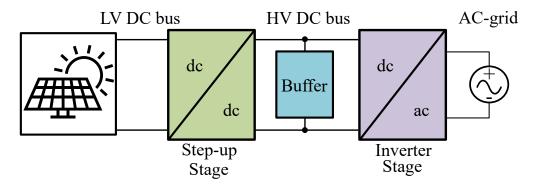

| 7  | АТ    | Wo-Stage Multi-level Hybrid Switched-Capacitor Microinverter                     | 79        |

|    | 7.1   | Introduction                                                                     | 79        |

|    | 7.2   | System Architecture                                                              | 83        |

|    | 7.3   | Hardware Implementation and Experimental Results                                 | 90        |

|    | 7.4   | Conclusion                                                                       | 98        |

| 8  | Cor   | nclusion                                                                         | 99        |

|    | 8.1   | Concluding Remarks                                                               | 99        |

| Bi | blios | graphy                                                                           | 102       |

# List of Figures

| 2.1 | A bidirectional single-phase power conversion system. The power converter must<br>either rectify the ac power waveforms to meet the demands of the corresponding |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | dc load or invert the dc energy from the dc source to required levels for the ac                                                                                 |    |

|     | distribution grid                                                                                                                                                | 4  |

| 2.2 | A single-phase power conversion system that rectifies the ac power waveform                                                                                      |    |

|     | that is supplied by the ac grid to a dc power waveform that meets the electrical                                                                                 |    |

|     | specifications of the dc load. The system is encompassed by a power factor                                                                                       |    |

|     | correction (PFC) stage that performs the power rectification and a buffering                                                                                     |    |

|     | stage that regulates the twice-line frequency power pulsation on the dc port to                                                                                  |    |

|     | minimize dc-link voltage and current ripple                                                                                                                      | 5  |

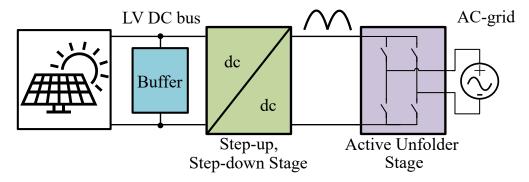

| 2.3 | A single-phase power conversion system that inverts the dc power waveform that                                                                                   |    |

|     | is supplied by a dc source to an ac power waveform that meets the electrical                                                                                     |    |

|     | specifications of the local ac distribution grid. The system is encompassed by                                                                                   |    |

|     | an inverting stage that performs the power inversion and a buffering stage that                                                                                  |    |

|     | regulates the twice-line frequency power pulsation on the dc port to minimize                                                                                    | _  |

| 2.4 | dc-link voltage and current ripple                                                                                                                               | ٦  |

| 2.4 | A two-level step-up power converter used as the power factor correction and                                                                                      | _  |

| 2 - | inverting stage in a single-phase system.                                                                                                                        | 1  |

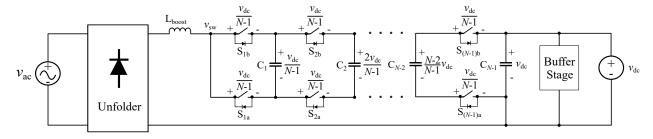

| 2.5 | An N-level step-up power converter used as the power factor correction and in-                                                                                   |    |

| 0.0 | verting stage in a single-phase system.                                                                                                                          | ć  |

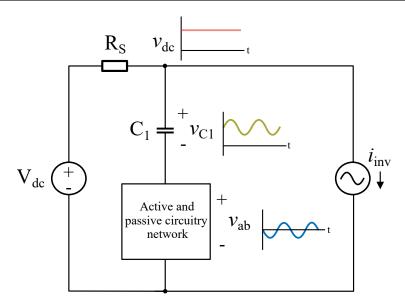

| 2.6 | An example of an active buffer topology that reduces the capacitance requirement                                                                                 |    |

|     | of the buffer stage by utilizing a network of active and passive circuitry in series                                                                             | (  |

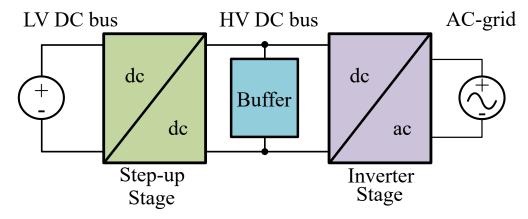

| 2.7 | with $C_1$                                                                                                                                                       | 6  |

| 2.1 | can now place the energy buffer across the HV dc bus for low-voltage dc systems,                                                                                 |    |

|     | such as residential microinverters, decreasing the capacitance requirement                                                                                       | 10 |

|     | such as residential interoffiveriers, decreasing the capacitance requirement                                                                                     | 10 |

| 3.1 | A conventional non-isolated two-level boost converter used for electric vehicle                                                                                  |    |

|     | on-board charging.                                                                                                                                               | 14 |

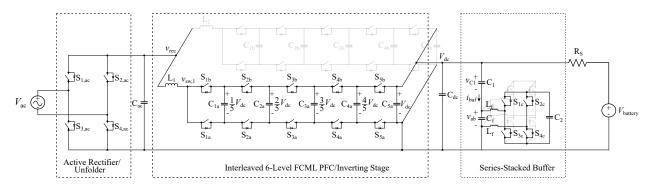

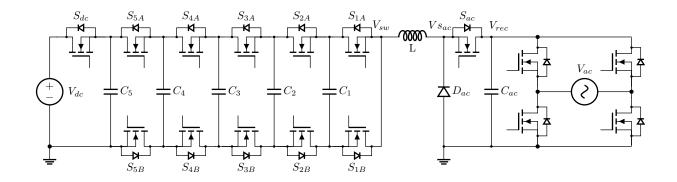

| 3.2 | Schematic of the overall system with active rectifier (unfolder), interleaved FCML,                                                                              |    |

|     | and SSB                                                                                                                                                          | 14 |

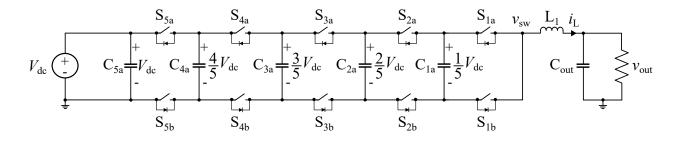

| 3.3 | A 6-level FCML converter configured for a dc-dc step-down conversion                                                                                             | 16 |

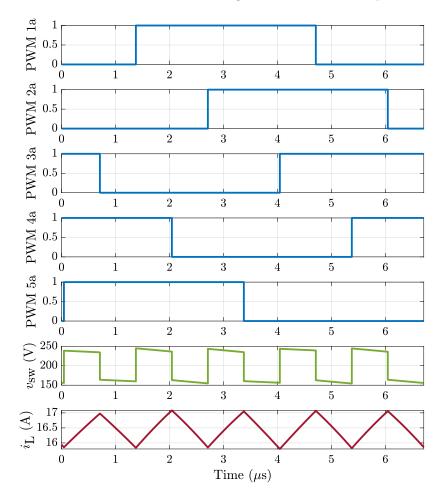

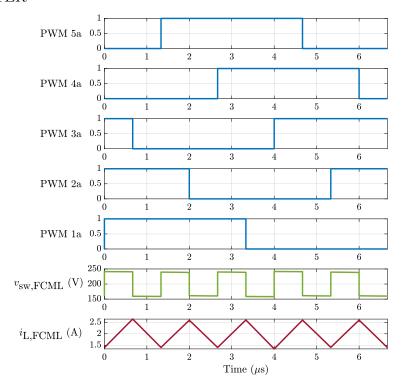

| 3.4  | The inductor current $i_{\rm L}$ and switched-node voltage $v_{\rm sw}$ during one switching period for the 6-level FCML shown in Fig. 3.3. The input voltage, output |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | power, switching frequency, and duty cycle of the topology are $V_{\rm dc} = 400$ V,                                                                                  |     |

|      | $P_{\text{out}} = 3.3 \text{ kW}, f_{\text{sw}} = 150 \text{ kHz}, \text{ and d} = 0.5, \text{ respectively.} \dots \dots \dots \dots$                                | 16  |

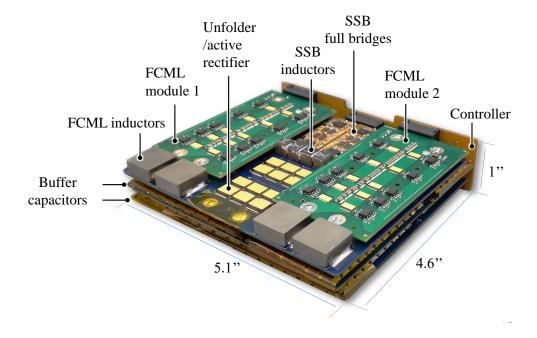

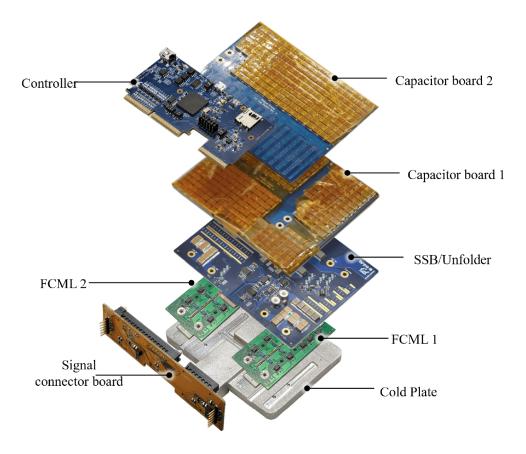

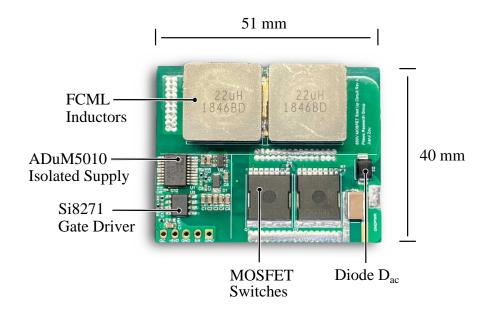

| 3.5  | The first revision of the EV charger assembly, excluding the thermal management,                                                                                      |     |

|      | with key subsystems labeled. In this depiction, the first revision of the FCML is                                                                                     |     |

|      | shown. (Figure was created in collaboration with Sophia Chou and Zitao Liao.)                                                                                         | 18  |

| 3.6  | A stack-up of the second revision of the EV charger assembly, showing the mod-                                                                                        |     |

|      | ular hardware design. In this assembly depiction, the second revision of the                                                                                          |     |

|      | FCMLs is shown and interfaces with the custom additively manufactured cold                                                                                            |     |

|      | plate. (Figure created in collaboration with Sophia Chou, Rahul Iyer, Ting Ge,                                                                                        |     |

|      | and Zitao Liao.)                                                                                                                                                      | 19  |

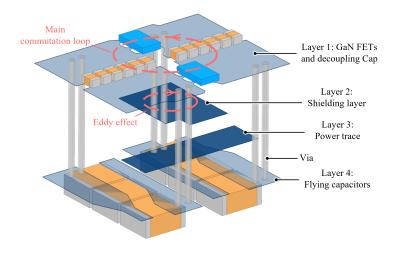

| 3.7  | PCB design of FCML module power stage that uses copper shield planes to reduce                                                                                        |     |

|      | the parasitic loop inductance. (Figure created in collaboration with Ting Ge and                                                                                      |     |

|      | Rahul Iyer.)                                                                                                                                                          | 21  |

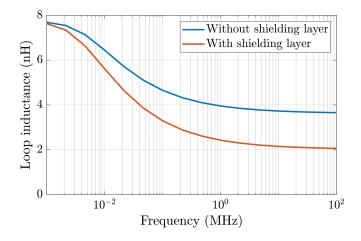

| 3.8  | Commutation loop inductance simulated in ANSYS Q3D for lateral commutation                                                                                            |     |

|      | loop with and without shielding layer. (Figure created in collaboration with Ting                                                                                     |     |

|      | Ge and Rahul Iyer.)                                                                                                                                                   | 21  |

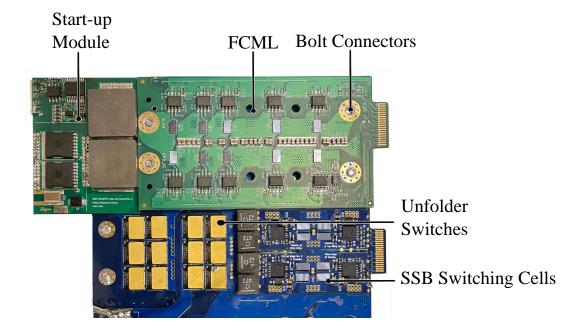

| 3.9  | Assembly of the EV charger system showing the SSB switching cells, which are                                                                                          |     |

|      | mounted on to the SSB/Unfolder board depicted in Fig. 3.6, and the start-up                                                                                           |     |

|      | PCB daughter-board, which is mounted on to the FCML converter PCB. (Figure                                                                                            |     |

|      | created in collaboration with Ting Ge, Rahul Iyer, and Jiarui Zou.)                                                                                                   | 22  |

| 3.10 | Modular start-up PCB daughter-board that is mechanically and electrically fitted                                                                                      |     |

|      | to the EV charger system. (Figure created in collaboration with Ting Ge, Rahul                                                                                        |     |

|      | Iyer, and Jiarui Zou.)                                                                                                                                                | 23  |

| 3.11 | Schematic of the EV charger FCML equipped with start-up components $S_{ac}$ and                                                                                       |     |

|      | D <sub>ac</sub> . (Figure made in collaboration with Sophia Chou.)                                                                                                    | 24  |

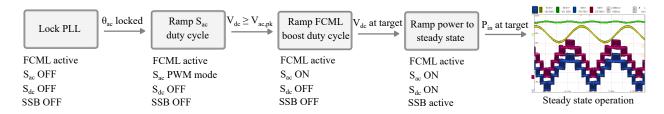

| 3.12 | Flow diagram of the EV charger start-up control procedure adapted from [48].                                                                                          |     |

|      | (Figure made in collaboration with Sophia Chou.)                                                                                                                      | 24  |

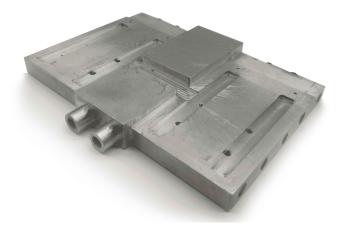

| 3.13 | The machine-drilled manufactured cold plate, showing the side that interfaces                                                                                         |     |

|      | with the electrical system. (Figure made in collaboration with Sophia Chou and                                                                                        |     |

|      | Zitao Liao.)                                                                                                                                                          | 25  |

| 3.14 | Custom additively manufactured cold plate, showing the side that interfaces with                                                                                      |     |

|      | the electrical system. (Figure made in collaboration with Ting Ge and Rahul Iyer.)                                                                                    | 25  |

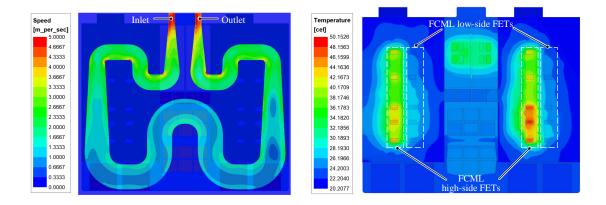

| 3.15 | Simulated velocity magnitude of the coolant in the AM cold plate with a 3.3                                                                                           |     |

|      | LPM flow and corresponding temperature on the power stage operating at 4 kW.                                                                                          |     |

|      | (Figure made in collaboration with Ting Ge and Rahul Iyer.)                                                                                                           | 26  |

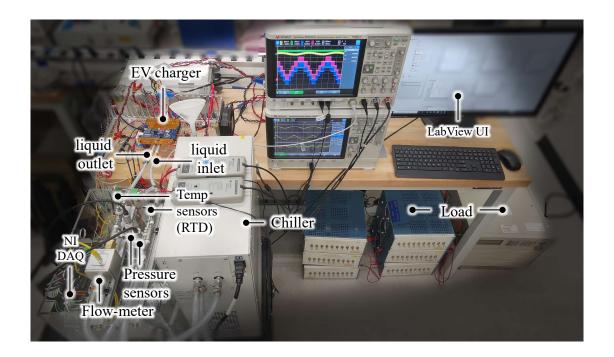

| 3.16 | System test setup for high power inverter testing. (Figure made in collaboration                                                                                      | 2.0 |

| 0.1= | with Sophia Chou and Zitao Liao.)                                                                                                                                     | 26  |

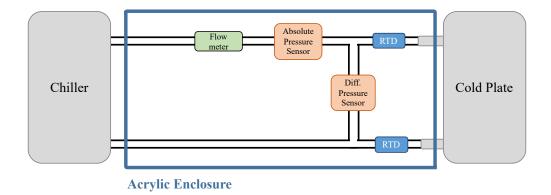

| 3.17 | Diagram of liquid cooling loop used in high power inverter testing. Table 3.2 lists                                                                                   | 27  |

|      | the equipment used for data measurement and acquisition of the cooling loop                                                                                           | 27  |

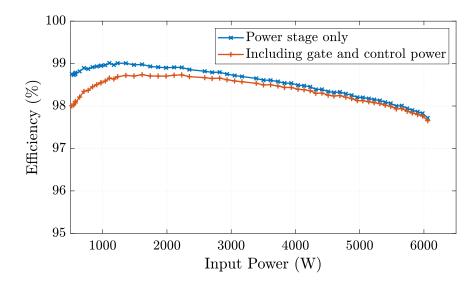

| 3.18       | The efficiency of the 6.1 kW inverter test, $400 V_{dc}$ to $240 V_{ac}$ for the first revision of the EV charger system. (Figure made in collaboration with Sophia Chou and                                                                                                                                                                                                  |    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.19       | Zitao Liao.)                                                                                                                                                                                                                                                                                                                                                                  | 28 |

| 0.20       | ages from 400 $V_{\rm dc}$ to 240 $V_{\rm ac}$ , 6.1 kW for the <b>first</b> revision of the EV charger system. (Figure made in collaboration with Sophia Chou and Zitao Liao.)                                                                                                                                                                                               | 29 |

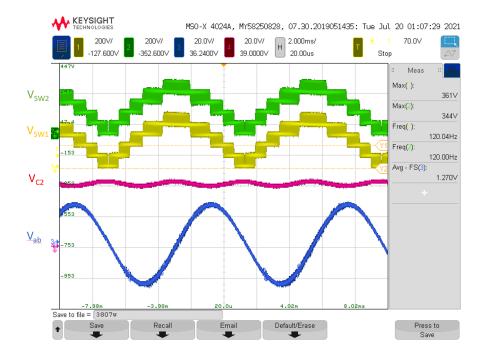

| 3.20       | The efficiency of the <b>second</b> revision of the EV charger system in inverter mode from $400 \text{ V}_{dc}$ to $240 \text{ V}_{ac}$ . (Figure made in collaboration with Ting Ge and Rahul                                                                                                                                                                               | 20 |

| 3.21       | FCML switching waveforms measured at peak tested power (3.8 kW) for the <b>second</b> revision of the EV charger system. The measured switched-node waveforms indicate the natural balancing of the flying capacitor voltages. (Figure made in                                                                                                                                | 30 |

| 3.22       | collaboration with Ting Ge and Rahul Iyer.)                                                                                                                                                                                                                                                                                                                                   | 30 |

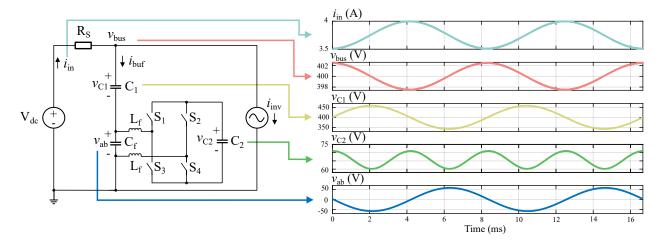

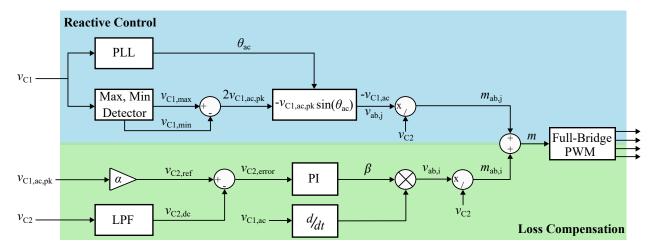

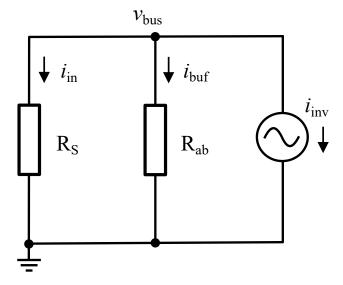

| 4.1        | Schematic of a traditional Series-Stacked Buffer connected to a dc voltage source $V_{dc}$ and an inverter modeled as a current load $i_{inv}$ . Voltage and current waveforms of the system are displayed for a 1.5 kW system operation where $v_{bus, dc} = 400 \text{ V}$ ,                                                                                                |    |

| 4.0        | $i_{\rm dc} = 3.75 \text{ A}, C_1 = 80 \ \mu\text{F}, C_2 = 204 \ \mu\text{F}, \text{ and } R_{\rm s} = 10 \ \Omega.$                                                                                                                                                                                                                                                         | 34 |

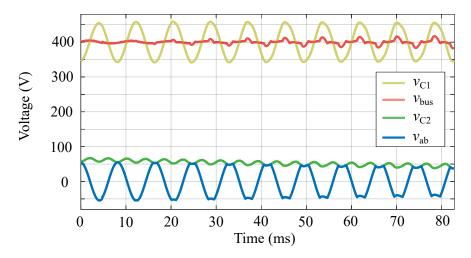

| 4.2<br>4.3 | The reactive and loss compensation control blocks for a traditional SSB Voltage waveforms for a SSB when no loss compensation control is implemented. Before time $t = 0$ , capacitors $C_1$ and $C_2$ are charged to nominal amounts for a                                                                                                                                   | 36 |

|            | 1.5 kW, 400 V system operation                                                                                                                                                                                                                                                                                                                                                | 36 |

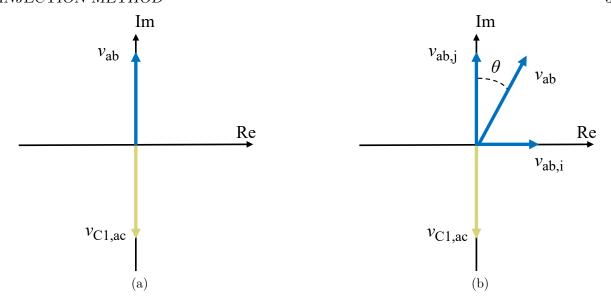

| 4.4        | Phasor diagram of the voltages $v_{\rm ab}$ and $v_{\rm C1}$ based on (a) solely the reactive control diagram in Fig. 4.2 for a lossless SSB and (b) the combined reactive and loss                                                                                                                                                                                           |    |

| 15         | compensation controls in Fig. 4.2                                                                                                                                                                                                                                                                                                                                             | 37 |

| 4.5        | current ripple coupled to the dc-link current                                                                                                                                                                                                                                                                                                                                 | 38 |

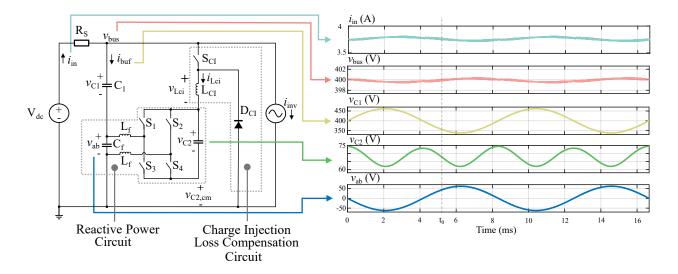

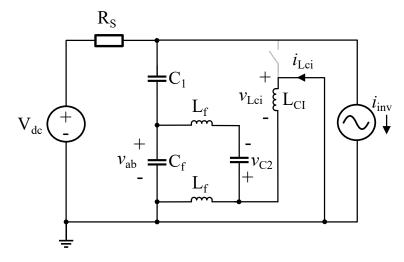

| 4.6        | Schematic of a SSB with charge injection circuit connected to a dc voltage source and a modeled inverter current load. Voltage and current waveforms of the system are displayed for a 1.5 kW system operation where $v_{\rm bus,dc}=400$ V, $i_{\rm dc}=3.75$ A, $C_1=80~\mu{\rm F},~C_2=204~\mu{\rm F},$ and $R_{\rm s}=10~\Omega.$ Time $t_0$ is labeled for the switching |    |

|            | period example of the SSB with charge injection converter explained in Section 4.3.                                                                                                                                                                                                                                                                                           | 39 |

| 4.7        | Reactive and loss compensation control diagrams for a SSB implemented with charge injection loss compensation control                                                                                                                                                                                                                                                         | 39 |

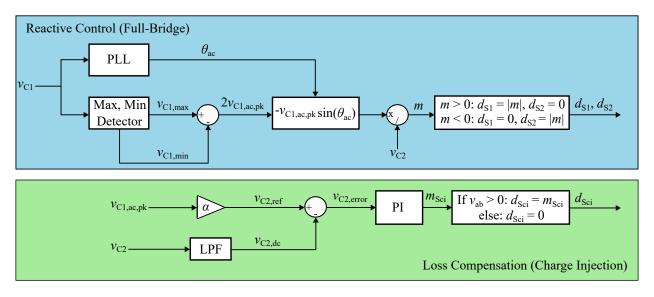

| 4.8        | Simulated operation of the SSB with charge injection method during one switching period. Both the charge injection and full-bridge circuits are operated at 160 kHz where the PWM for $S_{CI}$ is delayed by time $t_2$ . The circuit states shown in this example are described in Table 4.1. Fig. 4.6 shows where time $t_0$ occurs in                                      | 99 |

|            | the twice-line frequency period                                                                                                                                                                                                                                                                                                                                               | 43 |

| 4.9<br>4.10 | State X of the SSB and charge injection combined circuit                                                                                                                                                                                                                                                                                                                                                          | 46       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|             | voltage $v_{\text{Lci}}$ in circuit state X                                                                                                                                                                                                                                                                                                                                                                       | 46<br>47 |

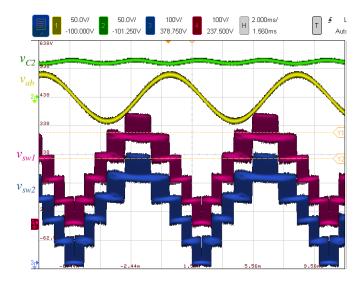

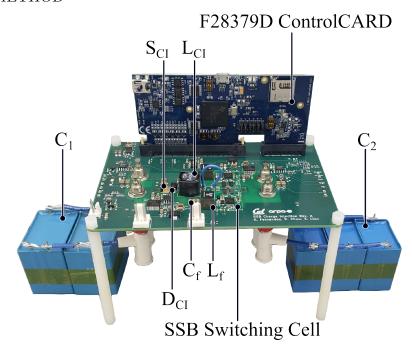

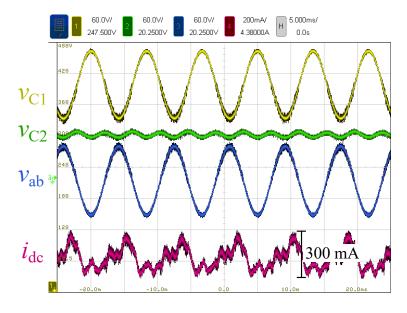

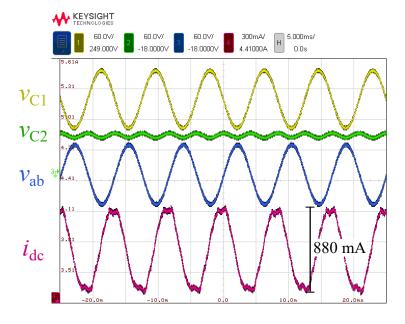

| 4.12        | Steady state waveforms of $v_{\rm C1}$ (yellow), $v_{\rm C2}$ (green). $v_{\rm ab}$ (blue) and $i_{\rm in}$ (pink) for the SSB implemented with the charge injection loss compensation control at 1.5 kW with $v_{\rm bus,dc} = 400 \text{ V}$                                                                                                                                                                    | 48       |

| 4.13        | Steady state waveforms of $v_{\text{C1}}$ (yellow), $v_{\text{C2}}$ (green). $v_{\text{ab}}$ (blue) and $i_{\text{in}}$ (pink) of the SSB implemented with the traditional control proposed in [72] at 1.5 kW with $v_{\text{bus,dc}} = 400 \text{ V}. \dots \dots$                                                     | 48       |

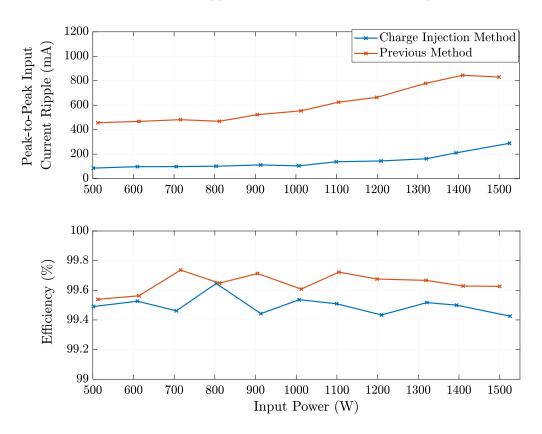

| 4.14        | The peak-to-peak dc input current ripple and efficiency comparisons between the traditional loss compensation method highlighted in Section 4.2, and the charge injection method. Note, the efficiency curve does not include gate drive losses since they are negligible, as shown in Fig. 4.16.                                                                                                                 | 49       |

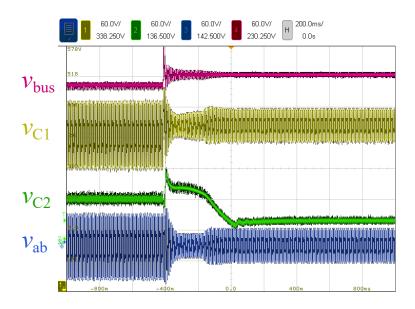

|             | Waveforms of the SSB with charge injection method captured during a load step from 1.5 kW ( $v_{\text{bus,dc}} = 400 \text{ V}$ ) to 750 W                                                                                                                                                                                                                                                                        | 50<br>51 |

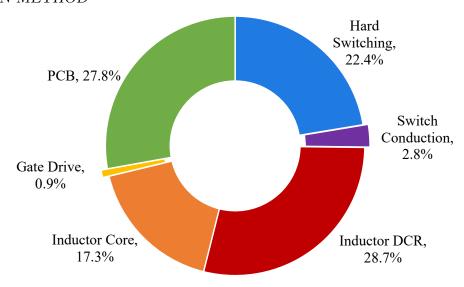

| 4.10        | Estimated loss breakdown of SSB with charge injection circuit at 1.5 kW                                                                                                                                                                                                                                                                                                                                           | 91       |

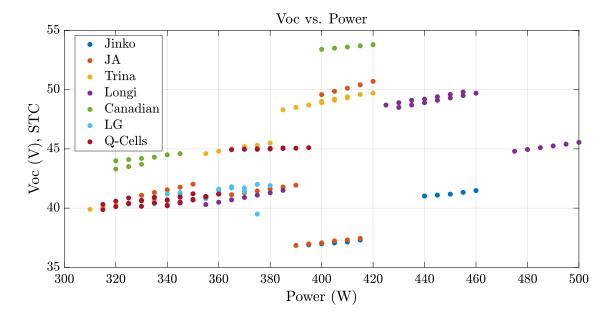

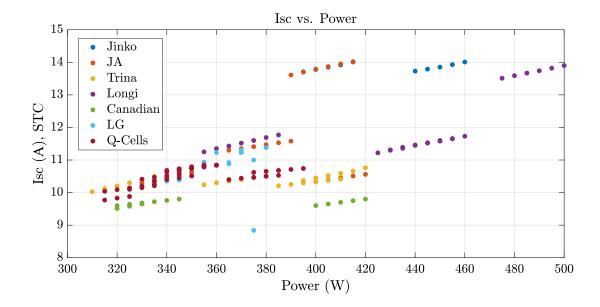

| 5.1         | The open circuit voltage $V_{oc}$ of various residential solar panels versus the rated power of the solar panel for standard testing conditions (STC). (Figure made in                                                                                                                                                                                                                                            |          |

| 5.2         | collaboration with Francesca Giardine.)                                                                                                                                                                                                                                                                                                                                                                           | 55       |

| 5.3         | collaboration with Francesca Giardine.)                                                                                                                                                                                                                                                                                                                                                                           | 55<br>56 |

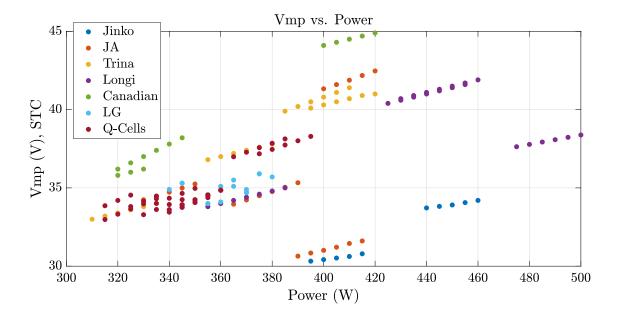

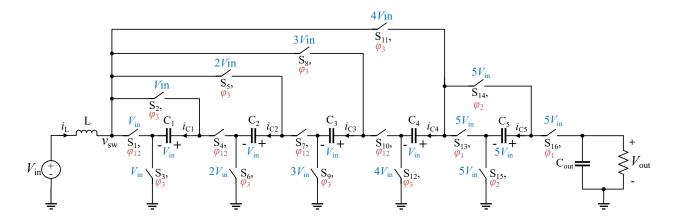

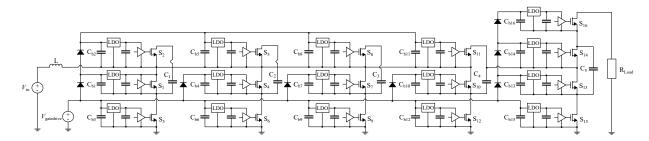

| 6.1         | Schematic drawings of the various $N$ -to-1 ReSC converter topologies considered for comparison in this analysis. Subscripts $n_c$ and $n_l$ denote the number of capacitors or inductors per topology, respectively, which are unique values per topology to achieve an $N$ -to-1 conversion ratio. The gating signal for each switch is denoted                                                                 | e.c.     |

| 6.2         | by $\varphi$                                                                                                                                                                                                                                                                                                                                                                                                      | 60       |

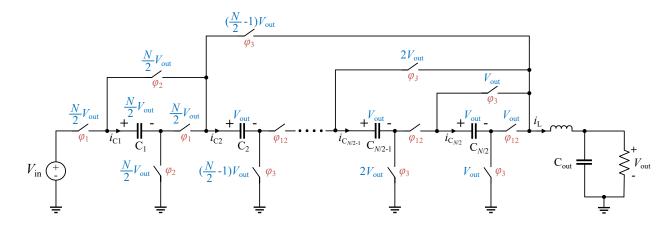

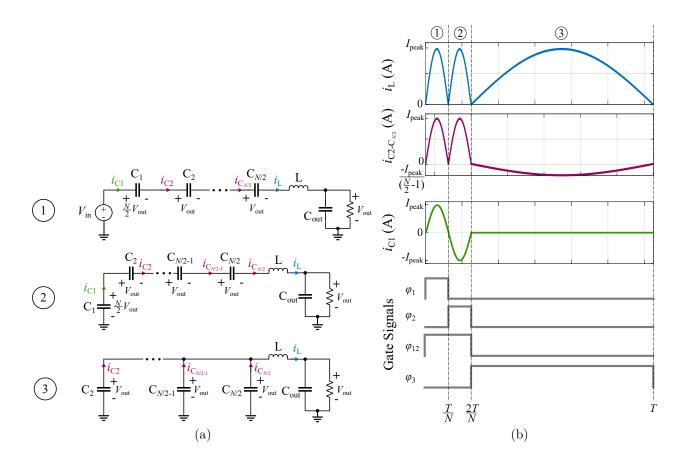

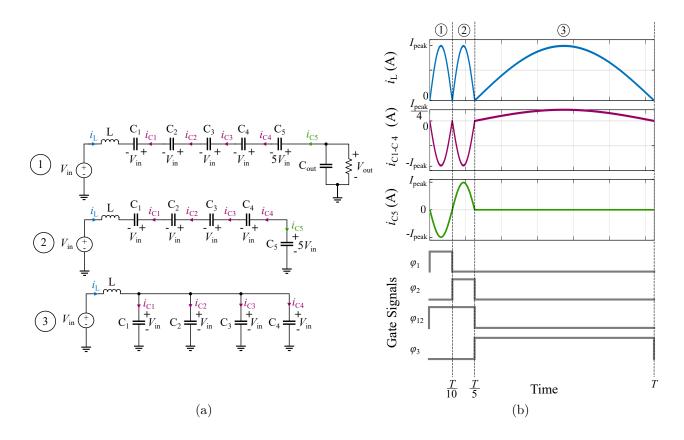

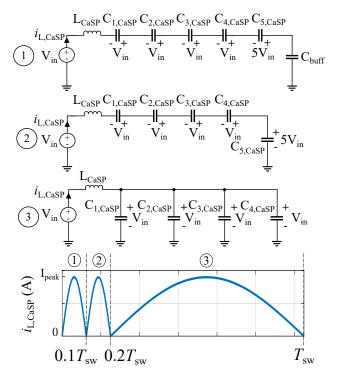

| 6.3         | capacitors, and the gate signals of the switches are provided The $N$ -to-1 CaSP: (a) The circuit states for each of the three sub-periods of the $N$ -to-1 CaSP. (b) The inductor and flying capacitor current waveforms, along with gate signals for the $N$ -to-1 CaSP during the entire switching period. Note that the average inductor current is equal to $I_{\rm out}$ for each of the three sub-periods, | 61       |

|             | and thus for the entire switching period, leaving $I_{\text{peak}} = \frac{\pi}{2}I_{\text{out}}$                                                                                                                                                                                                                                                                                                                 | 62       |

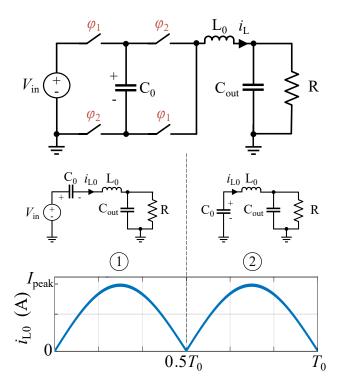

| 6.4        | A schematic and principle functionality of a 2-to-1 ReSC converter. Inductor $L_0$ shares the same inductance $L_0$ as inductor L in the N-to-1 CaSP shown in                                                       |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | Fig. 6.2. Similar to the CaSP, the average inductor current is equal to the output current $I_{\text{out}}$ and therefore the peak inductor current is $I_{\text{peak}} = \frac{\pi}{2}I_{\text{out}}$ . Noted, the |    |

|            | switching period duration $T_0$ is not equal to the switching period $T$ for the CaSP.                                                                                                                              | 65 |

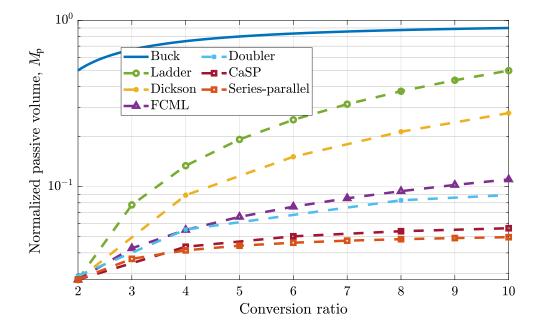

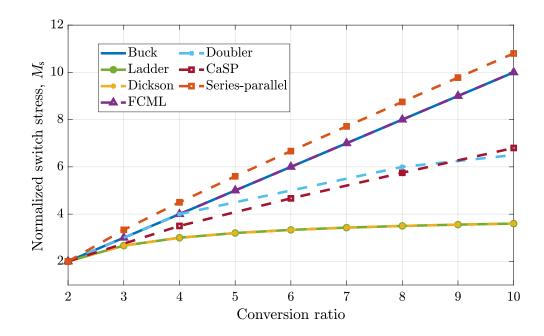

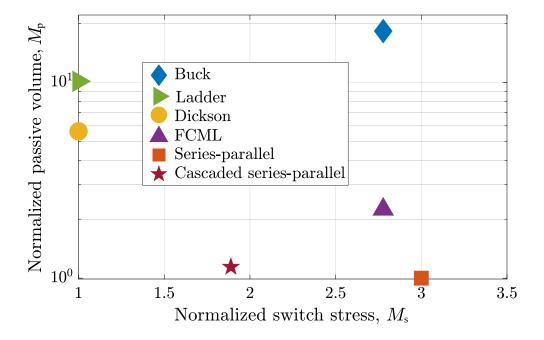

| 6.5        | Normalized passive volume $M_p$ for the buck converter and the ReSC topologies illustrated in Fig. 6.1, from a 2:1 to a 10:1 conversion ratio                                                                       | 68 |

| 6.6        | Normalized switch stress $M_{\rm s}$ for the buck converter and the ReSC topologies                                                                                                                                 |    |

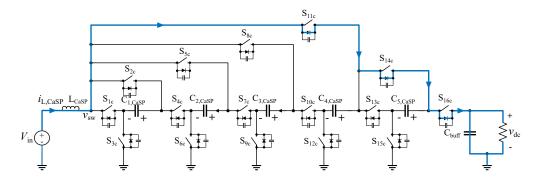

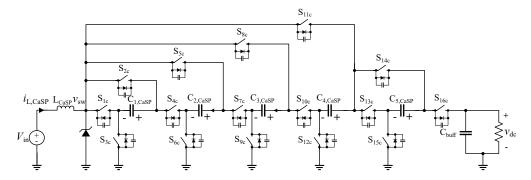

| 6.7        | illustrated in Fig. 6.1, from a 2:1 to a 10:1 conversion ratio                                                                                                                                                      | 69 |

| 0.1        | considered in this analysis for a 10-to-1 (or 1-to-10) conversion ratio                                                                                                                                             | 70 |

| 6.8        | Schematic drawing of a 1-to-10 CaSP with switch and capacitor dc voltage ratings                                                                                                                                    |    |

| 6.9        | provided                                                                                                                                                                                                            | 71 |

|            | pacitor current waveforms for the 1-to-10 CaSP during the entire switching period.  (b) The circuit states for each of the three sub-periods of the 1-to-10 CaSP                                                    | 71 |

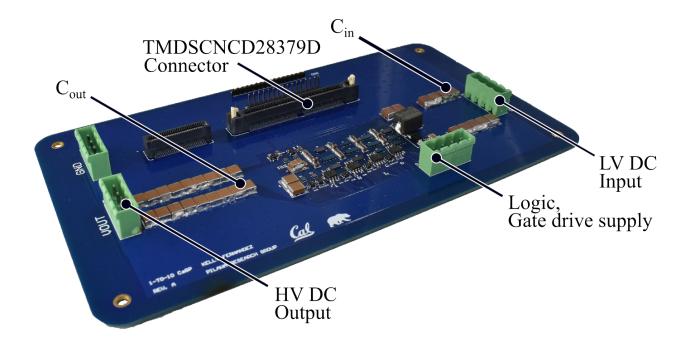

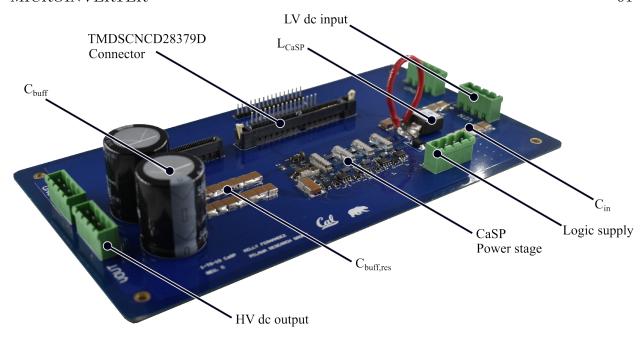

| 6.10       | The CaSP hardware prototype rated for 300 W and a 35 V-to-350 V step-up                                                                                                                                             |    |

|            | ratio. Fig. 6.11 shows a detailed look of the power stage of the hardware, and                                                                                                                                      | 70 |

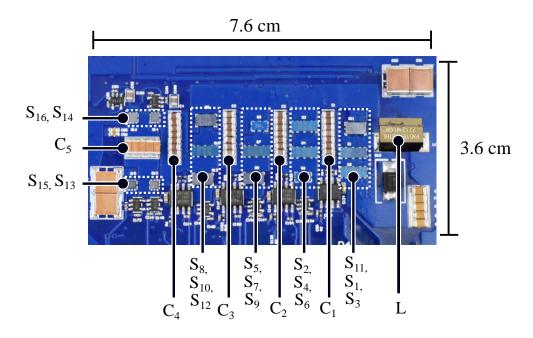

| 6.11       | Table 6.1 explains the detailed parameters for the annotated components Power stage of the hardware prototype with passive storage elements and active                                                              | 73 |

|            | devices labeled. Table 6.1 provides the detailed parameters for the annotated                                                                                                                                       |    |

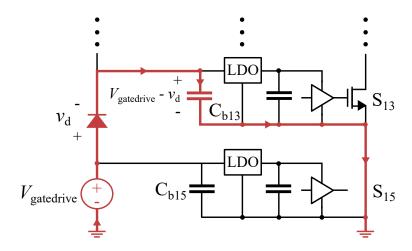

| 6 12       | components                                                                                                                                                                                                          | 74 |

| 0.12       | bootstrap methodology is used to deliver power to the switch side of the gate                                                                                                                                       |    |

| 6 12       | An example of the assessed bootstrap singuit method for the 1 to 10 CoSP hard                                                                                                                                       | 74 |

| 6.13       | An example of the cascaded bootstrap circuit method for the 1-to-10 CaSP hardware prototype                                                                                                                         | 75 |

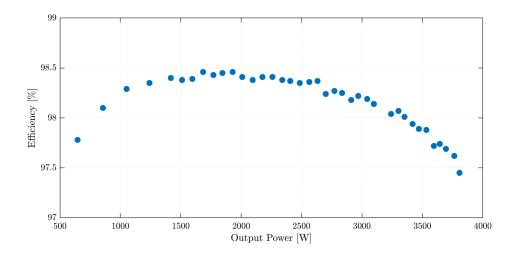

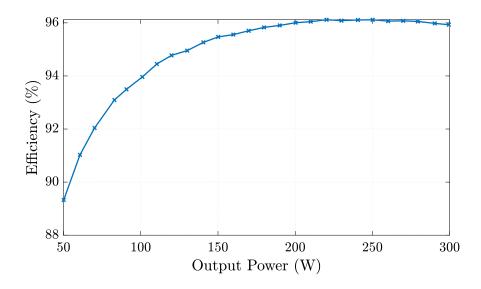

|            | Efficiency vs. output power for the CaSP performing a 35-to-350 V step-up. $$                                                                                                                                       | 76 |

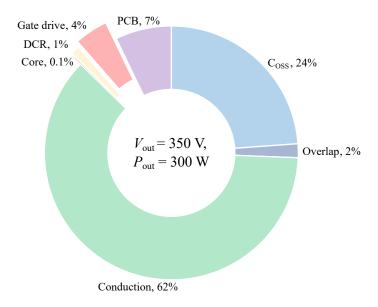

| 6.15       | Loss breakdown of the 1-to-10 CaSP hardware prototype for a 35-to-350 V step-up operation with 300 W output power                                                                                                   | 76 |

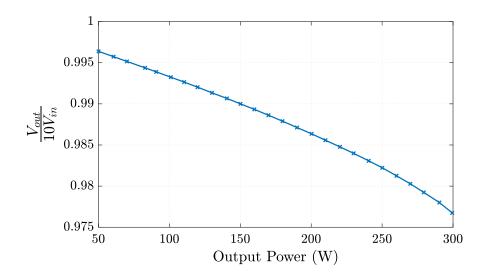

| 6.16       | Load regulation of the CaSP performing a 35-to-350 V step-up.                                                                                                                                                       | 77 |

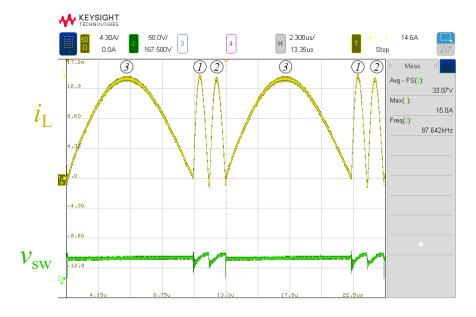

|            | Inductor current and switch node waveforms validating the ZCS operation of the                                                                                                                                      |    |

|            | 1-to-10 CaSP for a 35-to-350 V step-up at 300 W of output power                                                                                                                                                     | 77 |

| 7.1        | Diagram of a single-stage microinverter                                                                                                                                                                             | 80 |

| 7.2<br>7.3 | Diagram of a double-stage microinverter                                                                                                                                                                             | 80 |

|            | verter is used to step up the LV dc input to a HV dc bus. A dc-link capacitor buffers the twice-line frequency power pulsation. A 6-level FCML converter with                                                       |    |

|            | an active unfolder acts as the inverting stage                                                                                                                                                                      | 81 |

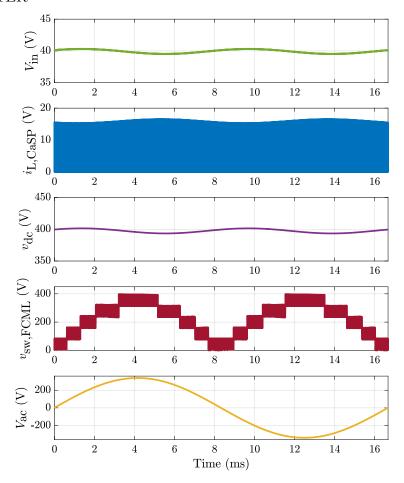

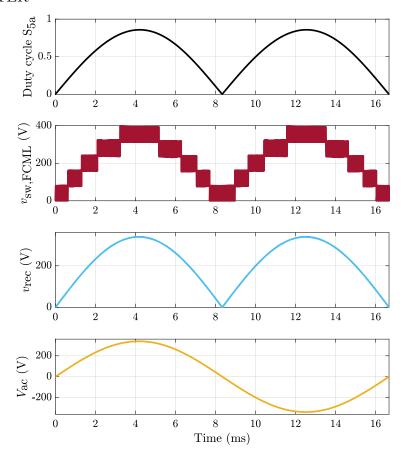

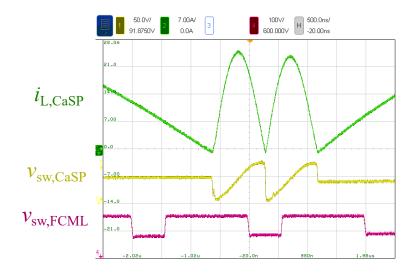

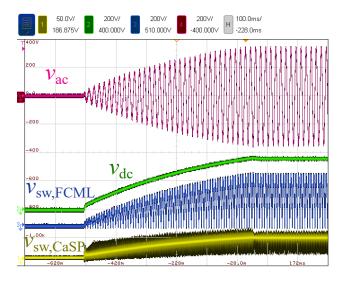

| 7.4  | Exemplary waveforms of the low voltage dc bus $V_{\rm in}$ (which is internally modeled with some source impedance), the CaSP inductor current $i_{\rm L.CaSP}$ , the high voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | dc bus $v_{\rm dc}$ , the FCML switched-node voltage $v_{\rm sw,FCML}$ , and the ac output voltage $v_{\rm ac}$ during a 40 V to 240 V <sub>ac</sub> conversion rated at 400 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84  |

| 7.5  | The three sub-period circuit states of the CaSP stage. Inductor current $i_{L,CaSP}$ is shown for each sub-period for a given switching period $T_{sw}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 85  |

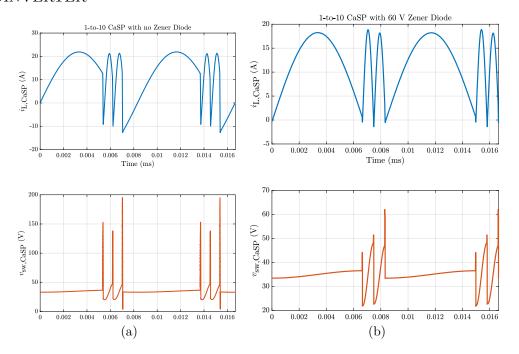

| 7.6  | Direction of current flow when the $i_{L,CaSP}$ is not fully discharged to 0 A and the converter experiences a switching transition. The output capacitance in some switches will discharge, allowing some switches to reverse conduct and connect the switched-node to the HV dc bus $v_{dc}$                                                                                                                                                                                                                                                                                                                                                                | 85  |

| 7.7  | Exemplary waveforms of the inductor current $i_{L,CaSP}$ and switched-node voltage $v_{sw,CaSP}$ without and with a clamping circuit on the switched-node of the CaSP: (a) when there is no clamping mechanism in the CaSP circuit. The voltage transient along the switched-node can cause the voltage across some of the switches in the CaSP to exceed their blocking voltage, potentially causing catastrophic damage to the microinverter system. (b) When a 60 V Zener diode is placed along the switched-node in the CaSP circuit as a clamping mechanism. The voltage across the switched-node is clamped to prevent any switches in the circuit from |     |

|      | experiencing an over-voltage condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86  |

| 7.8  | Circuit of the 1-to-10 CaSP with a Zener diode placed across the switched-node to prevent high voltage transients during switching transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87  |

| 7.9  | The inductor current $i_{\rm L}$ and switched-node voltage $v_{\rm sw}$ during one switching period for a 6-level FCML shown in the microinverter system topology in Fig. 7.3. The input voltage, output power, switching frequency, and duty cycle of the                                                                                                                                                                                                                                                                                                                                                                                                    | 00  |

| 7.10 | topology are $V_{\rm dc} = 400$ V, $P_{\rm out} = 400$ W, $f_{\rm sw} = 150$ kHz, and $d = 0.5$ , respectively. Exemplary waveforms of the duty cycle for switch $S_{5a}$ (placement shown in Fig. 7.3), the FCML switched-node voltage $v_{\rm sw,FCML}$ , the voltage output of the low pass filter in the FCML $v_{\rm rec}$ , and the ac output voltage $v_{\rm ac}$                                                                                                                                                                                                                                                                                      | 89  |

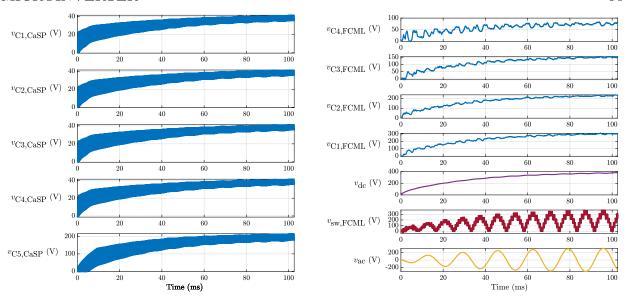

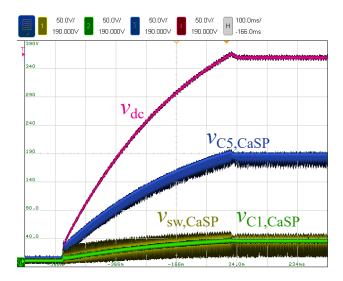

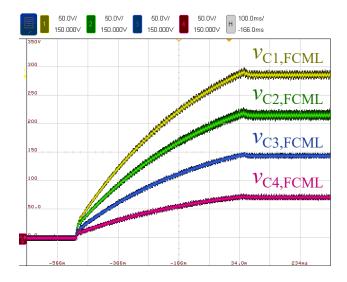

| 7.11 | Exemplary voltage waveforms of the capacitors $C_{1,CaSP}$ through $C_{5,CaSP}$ in the CaSP stage, $C_{1,FCML}$ through $C_{4,FCML}$ in the FCML stage, the voltage across the HV energy buffer $v_{dc}$ , the FCML switched-node voltage $v_{sw,FCML}$ , and the ac output $v_{ac}$ , during a system hard start-up from $V_{in} = 0$ V to 40 V at a rated power of $P_{in} = 400$ W                                                                                                                                                                                                                                                                         | 90  |

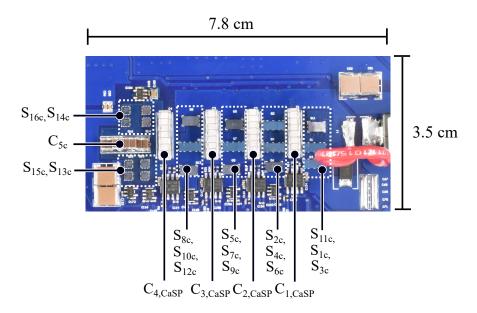

| 7.12 | Developmental prototype of 1-to-10 CaSP stage for the proposed step-up inverter.  Table 7.2 lists the part numbers and parameters of the major components of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 7 19 | full system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91  |

|      | Annotated photograph of the power stage for the CaSP. Table 7.2 lists the part numbers and parameters of the major components of the full system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91  |

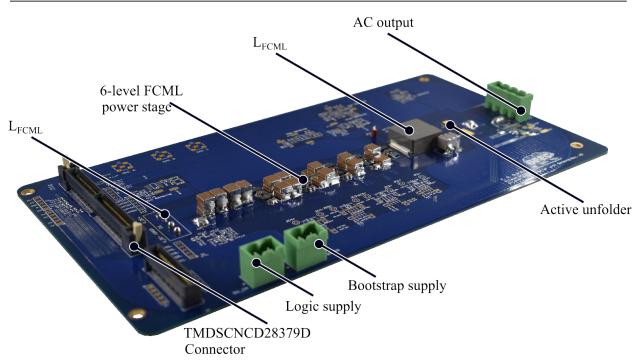

| 7.14 | Developmental prototype of the inverting FCML stage for the proposed microinverter. Table 7.2 lists the part numbers and parameters of the major components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.0 |

|      | of the full system. (Figure made in collaboration with Francesca Giardine.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 92  |

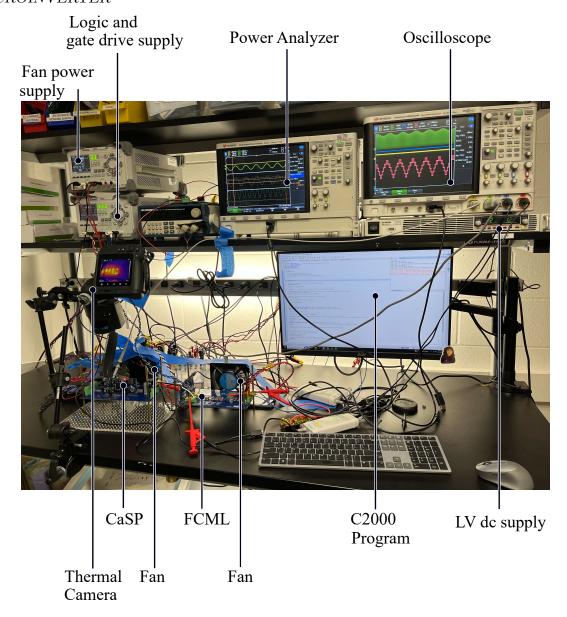

| 7.15        | Test setup for the microinverter system prototype verification. The resistive load sits below the table of the shown test setup. (Figure made in collaboration with                                                                                                                           |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | Francesca Giardine.)                                                                                                                                                                                                                                                                          | 93 |

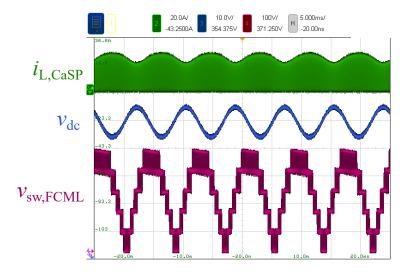

| 7.16        | Experimental waveforms of CaSP inductor current $i_{\rm L,CaSP}$ , the HV dc bus voltage $v_{\rm dc}$ , and the FCML switched-node voltage $v_{\rm sw,FCML}$ for a 38 V to 240 V <sub>ac</sub> conversion at full load P <sub>out</sub> = 500 W. (Figure made in collaboration with Francesca |    |

| 7.17        | Giardine.)                                                                                                                                                                                                                                                                                    | 95 |

|             | collaboration with Francesca Giardine.)                                                                                                                                                                                                                                                       | 95 |

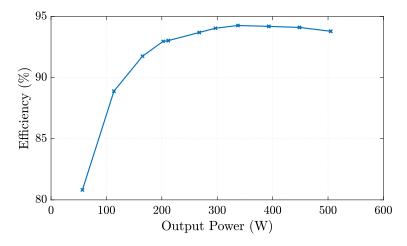

| 7.18        | Efficiency of full system over an output power range from 50 W to 500 W for a 35 V to 240 $V_{\rm ac}$ system conversion. (Figure made in collaboration with Francesca                                                                                                                        |    |

| <b>7</b> 10 | Giardine.)                                                                                                                                                                                                                                                                                    | 96 |

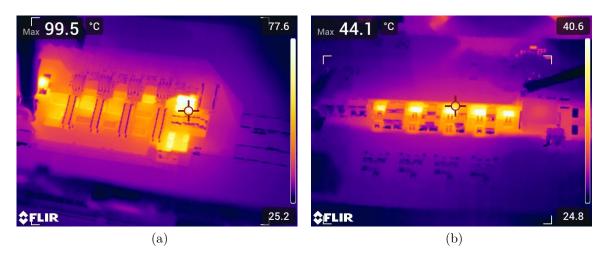

| 7.19        | = 500 W: (a) the step-up CaSP stage; (b) the inverting FCML stage. (Figures                                                                                                                                                                                                                   |    |

| 7.20        | made in collaboration with Francesca Giardine.)                                                                                                                                                                                                                                               | 96 |

| 7.21        | $C_5$ capacitor voltage $v_{C5,CaSP}$ , and HV dc bus $v_{dc}$                                                                                                                                                                                                                                | 97 |

|             | $v_{	ext{C4.CaSp.}} \dots $                                                                                                                                                             | 97 |

| 7.22        | - /                                                                                                                                                                                                                                                                                           | 98 |

# List of Tables

| 2.1        | Energy density differences between a 40 V and a 400 V aluminum electrolytic capacitor                                                                | 9<br>11  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1<br>3.2 | Component listing of both revisions of the EV charger system                                                                                         | 20       |

| 3.3        | testing                                                                                                                                              | 27<br>29 |

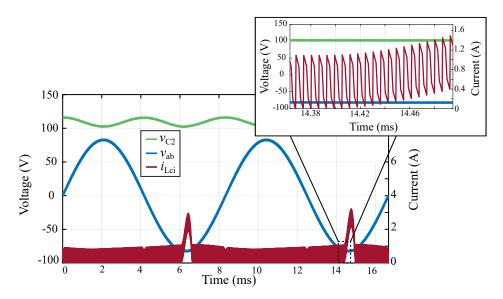

| 4.1<br>4.2 | Series-Stacked Buffer with charge injection method circuit states of operation Component listing of the SSB with Charge Injection hardware prototype | 42<br>47 |

| 6.1<br>6.2 | Components used in the 1-to-10 CaSP hardware prototype                                                                                               | 73<br>75 |

| 7.1<br>7.2 | Volume difference in the buffer stage between a single-stage and a double-stage microinverter solution                                               | 83<br>92 |

#### Acknowledgments

I would like first to say thank you to my advisor, Prof. Robert Pilawa-Podgurski. I am very grateful to have joined your research group in my second year of graduate school. Under your guidance, I have learned way more than I could have ever imagined during graduate school, both in my career and personal life. You have a remarkable ability to find not only brilliant power electronics students but also kind-hearted, selfless people to become members of your research group.

I thank my dissertation and qualifying committees, Robert, Prof. Duncan Callaway, Prof. Kristofer Pister, and Prof. Sascha von Meier. I have appreciated your feedback and suggestions before and while writing this dissertation. Thank you additionally to Prof. Seth Sanders. As my original advisor when I started my PhD at Berkeley, you instilled in me how fun learning can be and helped guide me at the beginning of my research journey.

When I first started in the Pilawa research group, I was mentored by Sophia Chou and Zitao Liao. You both are incredibly patient, kind, knowledgeable, and resourceful. Thank you for planting the various seeds of power electronics in my little brain. Thank you also to Raya, who came aboard the EV charger project towards the end. You are also a delight to work with and made me realize how much younger students are capable of at the beginning of their careers (which is a lot!). I cannot imagine starting this PhD with any other mentors, mentees, and any other project other than EV charger. Thank you all so much.

When Sophia, Zitao, and Raya left, we adopted a new team of EV charger members - Ting, Rahul, Jiarui, and Joseph Schaadt. Although none of you had prior knowledge of the EV charger system beforehand, each of you learned very quickly. I appreciate your help in this project and your adaptability in making a block of various PCBs, connecting them, and helping me explode them at high voltage and power. You helped me learn a lot during the second revision of testing, and I am very grateful for your assistance and hard work.

Aside from team EV charger, I had the pleasure of working with a small, relatively isolated team in our research group, the "Rougher and Tougher Buffers" team - Finn and Nathan Brooks. I appreciate your help in lab debugging and discussing all things buffer-related; we created quite a fun learning community. Series-stacked buffer for life!

I have had the pleasure of mentoring several students over the career of my PhD. However, none of them had such an impact on me as Finn. We had quite an interesting start together, with me being your GSI for 213A during the worst bits of the pandemic. Thus, who would have thought we would later become both a mentor-mentee pair and such great friends. Thank you for being there for me through work and my personal life; you have taught me quite a lot about being a better mentor and friend. You are the Luigi to my Mario! Thank you as well to Jessica Keast. I have enjoyed and appreciated all of your dinners, support, and hosting of board game nights throughout my PhD.

Here comes the big one - thank you all in the Pilawa Research group. You have all made this journey such a joyful and fun experience. To the older students in the group from when I first joined - Pourya, Joseph, Zichao, Nathan Pallo, Sophia, Zitao, and Nathan Brooks. Since I first joined, you have all been very welcoming and willing to put down whatever you

are doing to help others. Thank you. Thanks additionally to Nate Pallo for assisting me with GSI'ing 113A/213A. You are a role model for what a good instructor looks like, which helped me when I was the sole GSI the following year. Thank you as well to Sam, Maggie, and Rose. We started around the same time in the group, and I value your friendship and assistance in research for the past six years! Thank you to Ivan, Ting, Nathan Ellis, Logan, Finn, Rod, Yicheng, Rahul, Amanda, Ben, Marrin, Sahana, Haifah, Jiarui, Nathan Biesterfeld, Elisa, Tahmid, and Joseph Schaadt. Not only have you passed the torch in creating a positive lab culture, but you are also so brilliant and have taught me a lot about power electronics! Thank you additionally to my cubicle - Haifah, Elisa, and Nathan Biesterfeld, you have been great work neighbors, and I appreciate you putting up with all of my distractions; the 145B crew - Maggie, Sahana, and Finn, thanks for making that room bright in conversation and in laughter despite its small size and dungeoneous location; the fun run crew - Finn, Sam, Elisa, Nathan Biesterfeld, Yicheng, Amanda, and Rod, thank you for the fun after-work workouts and treats; and lastly, but certainly not the least, the trivia crew - Nathan Brooks, Ivan, Rod, Elisa, Nathan Biesterfeld, and Nagesh, thank you for always showing up to trivia nights so we can learn useless fun facts and continuously not place in the top 3. We'll win one of these days!

I've been blessed with such a great community not only within work but also outside of work. Life cannot always be work, and my friends have helped me maintain a healthy and fun work-life balance. Specifically, my workout buddies turned movie night buddies turned life buddies - Ryan, David, Josh, Mauricio, Arya, Abe, Gabe, and Hani. Thank you for keeping me sane through our runs, bike rides, climbs, movie nights, and bonfires together. You have always been there to hear me vent, offer advice, and push me to improve myself. I appreciate you and look forward to continuing our workouts, bonfires, movie nights, and bar nights! To Team Banana - Cameron, Scott, Cole, Meghan, Luke, and Mohammed, thank you for getting me into cycling and dragging my butt to South Bay for some beautiful long-ride excursions! Specifically, thank you to Cameron - I will always remember our backpacking excursions from the JMT to eating Safeway sandwiches while backpacking on Thanksgiving day; thank you for being there for me and helping me get my butt outside. Thank you to Sonali and Jess; despite being buried in work and silent to the world, I have always appreciated you texting me asking me to go climbing and grab food. I'd also like to thank Peyton, Sam Holladay, Tyler, Mauricio, Esther, and Alyssa. You also have helped me stay sane by reminding me of the need to step away from electronics and my work to enjoy life outside in the mountains! My housing roommate - Gabriel Matute, thank you for being there for the last two years of my PhD. I've appreciated having a friend so close by to laugh about things with, both within and outside the PhD, and always to have your moral support. To Paul Kim and Julia Mahler, my dear undergrad friends who have never hesitated to call me to check in with me and have let me crash at their homes in Colorado to go hiking while visiting for conferences, thank you! Thank you to Anya, Danielle, and Pierre for being there for me for all matters tied to my PhD and personal life over the last six years. To one of my dearest friends on my journey, Alex Keller. You have been there with me since day one of my Ph.D. I appreciate your help through all of these years! To summarize, I could not

#### ask for a better group of friends in this world. Thank you all!

Lastly, I want to say thank you to my family. Despite not understanding why I took this direction in life and moved far from home, you have always been beside me and helped me along the way. Mom and Dad, thank you for always answering my phone calls, guiding me through my personal life and career, and being there with me through all the rough and beautiful times these past six years. Molly and Amber, thank you for your advice, love, and unconditional support. I love you all and am blessed to have you as my family. This thesis is for you.

## Chapter 1

## Introduction

#### 1.1 Introduction

This thesis focuses on two specific applications of single-phase converters. In the first part, level-2 electric vehicle charging is examined. A novel hybrid switched-capacitor converter is proposed for the power factor correction stage, and an active buffer solution is offered for the energy buffer stage. Following this section, suggestions for improvement of the energy buffer stage, which reduces any current and voltage ripple along the dc-link, are given. In the second part of this thesis, a novel two-stage inverting system is proposed for the application area of microinverters. A passive component and switching stress analysis is completed to motivate the selection of the converter topology of the first stage, followed by a detailed description of the entire system solution. High-performance hardware prototypes and experimental results are showcased in this manuscript.

## 1.2 Organization of Thesis

#### Chapter 2: Fundamentals of Power Converters in Single-Phase Systems

Single-phase power conversion systems require a power converter to rectify the ac power sourced by the ac grid to a dc power waveform that is processed by the dc port. This process can also occur by an inverting means, where the power converter must invert the dc power sourced by the dc port to an ac power that meets ac grid regulations. Conventional single-phase power conversion systems have two stages: a power factor correction/inverting stage and a buffer stage that regulates the twice-line frequency power pulsation ripple along the dc bus. Conventional designs for both stages of the single-phase power conversion system are discussed. Suggestions for improvements in their design that offer increased volumetric and gravimetric power densities, increased efficiency, and improved reliability and lifetimes are given.

## Part I: Single-Phase Power Conversion for Electric Vehicle Charging Applications

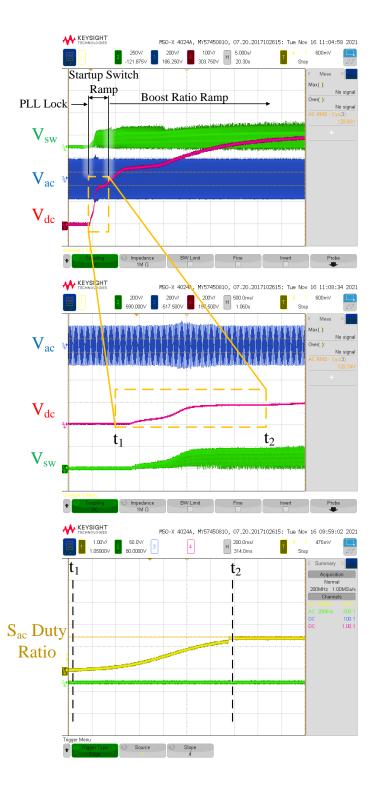

#### Chapter 3: Electric Vehicle On-Board Charger

Level II electric vehicle (EV) on-board chargers provide ac-dc conversion capability to charge on-board high-voltage (HV) batteries. Bidirectional EV chargers can also allow the EV to act as an ac source in vehicle-to-grid services. Chargers should have high power density, high power-handling capability, and low weight in charging and inverter applications. This chapter showcases the architecture of an optimized bidirectional EV charger system that can convert from both low-line (120  $V_{ac}$ ) and high-line (240  $V_{ac}$ ) ac voltages to a 400  $V_{dc}$  output. The operation and control of the complete system, thermal management, enhanced power stage design, and start-up procedure are discussed. Experimental results demonstrating dc-ac high power operation and system start-up are reported.

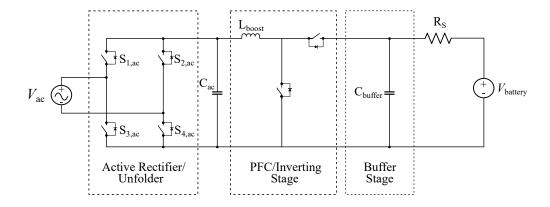

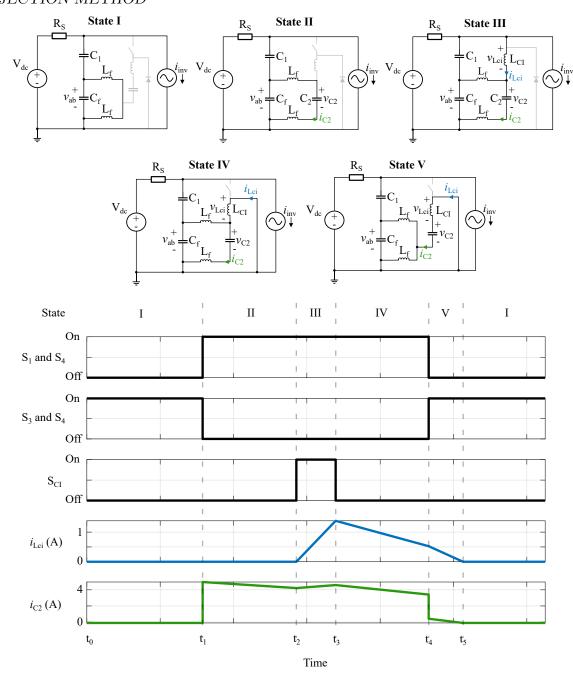

# Chapter 4: Series-Stacked Buffer with and without the Charge Injection Method

Single-phase power converter systems require a reactive circuit branch tied to the dc-link. The reactive branch buffers the twice-line frequency power pulsation that couples to the dc bus due to the mismatch in instantaneous power between the dc and ac ports. The Series-Stacked Buffer (SSB) has been presented as an active buffer topology that moderates this reactive power while maintaining a low physical volume and high efficiency. However, the SSB requires additional loss compensation control, producing a residual twice-line frequency ac current and voltage ripple coupled to the dc-link. This chapter proposes hardware and corresponding control that injects charge into the SSB to compensate for losses. This eliminates the twice-line frequency ripple from the dc-link through decoupling the reactive and real power handling. The charge injection technique is verified with an SSB hardware prototype rated for 1.5 kW and 400 V operation.

## Part II: Multi-Level Power Converters for Residential Solar Panel Microinverter Applications

#### Chapter 5: Residential Solar Panel Survey

This chapter presents a survey that examines the open circuit voltage  $(V_{oc})$ , the maximum power voltage  $(V_{mp})$ , and the rated power levels of many residential solar panels. Basic terminologies for key electrical characteristics in solar panel datasheets used in this survey are defined. The findings of the surveyed material provide voltage and power design requirements for any nominal microinverter system.

#### Chapter 6: A 1-to-10 Cascaded Series-Parallel Converter

Resonant hybrid switched-capacitor converters (ReSCs) can achieve high efficiency, power density, and power-handling capabilities. However, ReSCs have yet to be widely explored in high-voltage (HV) step-up application areas. This chapter attempts to bridge the gap between ReSCs and the HV step-up application space by proposing a 1-to-10 step-up cascaded series-parallel (CaSP) converter. The principles of operation and functionality of the circuit are discussed and are validated with a hardware prototype. Experimental results are provided up to 300 W and 350 V output, including efficiency and load regulation measurements and zero-current switching (ZCS) demonstration.

#### Chapter 7: A Two-Stage Multi-level Hybrid Switched-Capacitor Microinverter

This chapter explores using a two-stage architecture for a photovoltaic microinverter that utilizes efficient and compact hybrid switched-capacitor topologies. The first stage is a 1-to-10 step-up Cascaded Series Parallel (CaSP) dc-dc converter. The CaSP stage demonstrates the feasibility of using a fixed-ratio resonant switched-capacitor converter in the microinverter application space. Instead of advanced startup circuitry, the CaSP converter provides a startup sequence for the overall system architecture. The second stage offers voltage regulation and inversion: a flying capacitor multilevel (FCML) converter that converts the intermediate high voltage dc bus that is between 350 V to 400 V, to a 240  $V_{\rm rms}$  ac output. Experimental results validate the system architecture's functionality, highlighting the possibilities of using the CaSP converter in renewable applications.

#### Chapter 8: Conclusion

This chapter concludes this thesis. Conventional power converter designs for electric vehicle converters and microinverters are discussed, followed by a brief discussion of how system improvements can be made. The proposed power converter systems for these two applications in this thesis are summarized, with experimental and hardware results noted.

## Chapter 2

# Fundamentals of Power Converters in Single-Phase Systems

## 2.1 Single-Phase System Architecture

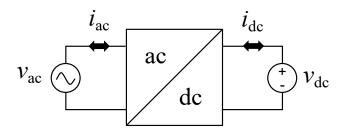

In single-phase power conversion systems, a power converter (shown in Fig. 2.1) is required to convert the ac power waveform provided from the ac grid to a dc power waveform, where the dc load determines the power and dc voltage requirements. In single-phase inverting applications, the power converter operates as an inverting topology, where it inverts the dc power provided by its dc source to required levels for the ac distribution grid [1], [2]. In the United States, the ac voltage supplied by the grid is conventionally either 120  $V_{\rm ac}$  or 240  $V_{\rm ac}$  [3]. There is an abundance of single-phase applications that have strict specifications for the dc port voltage and power levels. For example, in single-phase electric vehicle (EV) charging, the dc load is the car's dc battery, which is typically rated between 400  $V_{\rm dc}$  to 800  $V_{\rm dc}$  and must be charged by power levels rated in the kilowatts [4]–[6]. Another example is residential solar panel inverters, which are commonly referred to as "microinverters," where the low voltage (LV) dc solar panel can be rated up to 60  $V_{\rm dc}$  and can be connected to a

Figure 2.1: A bidirectional single-phase power conversion system. The power converter must either rectify the ac power waveforms to meet the demands of the corresponding dc load or invert the dc energy from the dc source to required levels for the ac distribution grid.

240 V<sub>ac</sub> grid [7], [8].

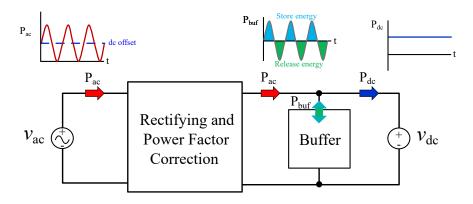

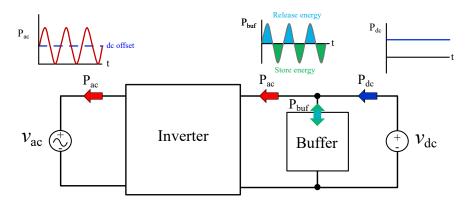

A conventional power conversion system has two stages. The first is an ac-to-dc power conversion stage, which handles the power factor correction, or a dc-to-ac inversion stage, pending on the desired application. The second stage is the twice-line frequency energy buffer, which is required to store and release the twice-line frequency power pulsation along the dc-link of the system caused by the instantaneous power mismatch between the ac and dc ports. Figs. 2.2 and 2.3 display the placement of the two stages in a single-phase power

Figure 2.2: A single-phase power conversion system that rectifies the ac power waveform that is supplied by the ac grid to a dc power waveform that meets the electrical specifications of the dc load. The system is encompassed by a power factor correction (PFC) stage that performs the power rectification and a buffering stage that regulates the twice-line frequency power pulsation on the dc port to minimize dc-link voltage and current ripple.

Figure 2.3: A single-phase power conversion system that inverts the dc power waveform that is supplied by a dc source to an ac power waveform that meets the electrical specifications of the local ac distribution grid. The system is encompassed by an inverting stage that performs the power inversion and a buffering stage that regulates the twice-line frequency power pulsation on the dc port to minimize dc-link voltage and current ripple.

conversion system for rectification and inversion systems, respectively, along with the power waveforms that are processed by each port and stage in the system.

Assuming the voltage and current waveforms along the ac port of the system are in phase with one another, the power processed by the ac port can be derived as

$$P_{\rm ac} = V_{\rm ac} \sin(\omega_{\rm L} t) \cdot I_{\rm ac} \sin(\omega_{\rm L} t), \tag{2.1}$$

where  $V_{\rm ac}$  and  $I_{\rm ac}$  are the magnitudes of the ac voltage and current waveforms, respectively, and  $\omega_{\rm L}$  is the angular frequency of the rated line frequency  $f_L$ , which is a rated 60 Hz frequency in the United States. The product in (2.1) can be simplified to

$$P_{\rm ac} = P_0 - P_0 \cos(2\pi f_{2L} t), \tag{2.2}$$

where  $P_0$  is equal to  $\frac{V_{\rm ac}I_{\rm ac}}{2}$  and  $f_{\rm 2L}$  is  $2\times$  the rated lines frequency, which is equal to 120 Hz in the United States.

# 2.2 Conventional Single-Phase Power Converter Solutions

#### Power Factor Correction and Inverting Stage

Single-phase power converters can be broken into two separate categories: isolated designs, which utilize a transformer in the PFC/inverting stage that provides galvanic isolation in the system, and non-isolated designs, which have no transformer in the PFC/inverting stage. Noted, for the non-isolated designs, an isolation transformer must be placed elsewhere in the system if required by regulation in the intended application area. This thesis only examines non-isolated designs since they offer higher volumetric and gravimetric energy densities.

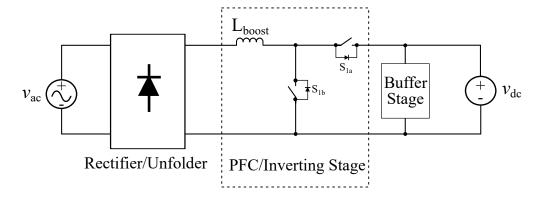

In a non-isolated PFC design, there is no transformer. Commonly, the output-to-input voltage gain depends on the converter's duty cycle. In applications where the voltage must be stepped up from the grid, such as in EV charging applications, a two-level boost converter is used as a conventional solution [9]. Similarly, in step-down and step-up-down applications, a two-level buck converter and two-level buck-boost can be used, respectively. Fig. 2.4 shows a two-level step-up power converter utilized in a single-phase power converter application. In this solution, the duty cycle of switch  $S_{1b}$  determines the gain of the power converter. Unlike a conventional isolated solution, such as the LLC converter [10], [11], the two-level solution utilizes only one magnetic component ( $L_{boost}$ , as shown in Fig 2.4) to handle the energy storage and transfer as well as the power factor correction.

### Twice-Line Frequency Buffering Stage

Conventionally, a bank of capacitors is used to buffer the twice-line frequency power pulsation along the dc-link of the system. The capacitance requirement is determined by the engineer's

Figure 2.4: A two-level step-up power converter used as the power factor correction and inverting stage in a single-phase system.

desired voltage ripple along the dc-link, as well as the rated power of the system:

$$C_{\text{buffer}} = \frac{P_{\text{sys}}}{2\pi f_{2\text{L}} \cdot v_{\text{dc}} \cdot \Delta v_{\text{dc}}},\tag{2.3}$$

where  $P_{\rm sys}$  is the rated power of the system,  $v_{\rm dc}$  is the dc voltage of the dc port, and  $\Delta v_{\rm dc}$  is the desired peak-to-peak voltage ripple of the dc-link [12], [13]. There are several capacitive solutions, and each offers its benefits:

- Multi-layer ceramic capacitors (MLCCs) Offer low values of ESR and ESL, further improving the system efficiency. Class 2 MLCCs offer high energy density levels [14], [15] but suffer from capacitance derating such that the capacitance decreases with higher dc voltages. Class 1 MLCCs do not experience this derating but offer poorer power density metrics. Ceramic capacitors overall have high reliability and long lifetimes.

- Film capacitors Offer high precision capacitance, high reliability, long lifetimes, low values of ESR, and can withstand highly rated voltages and currents. However, film capacitors suffer from larger physical volumes and weights than other capacitive solutions.