## University of California Los Angeles

## Energy Efficient Computing Using Static-Dynamic Co-optimizations

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Karthik Gururaj

#### Abstract of the Dissertation

## Energy Efficient Computing Using Static-Dynamic Co-optimizations

by

#### Karthik Gururaj

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2013 Professor Jason Cong, Chair

Energy consumption is a primary concern of current day computing systems – from handheld battery operated systems to servers in data centers connected to wall power. Research in academia as well as industry has focused on a variety of techniques for minimizing energy consumption while maintaining a good level of performance. The most effective techniques combine the best of static (or offline) and dynamic (or online/runtime) optimizations to obtain the best solution. Static optimizations can be more complex and can afford to take a global view of the application/computation being executed on the system – however, such optimizations have to be conservative in nature because they cannot anticipate all the different scenarios that can appear at runtime. Dynamic optimizations have more information about the application/computation for the given input – however, since such optimizations have to have low overhead, they can afford to have only a local view of the computation/application and the complexity of the optimization has to be relatively low. An additional direction that needs to be considered is to determine whether dynamic optimizations should be implemented in software or hardware. In this thesis, I present a study of three aspects of energy efficient computing that use a combination of static and dynamic optimizations to minimize energy consumption. The first aspect is to consider variability in the execution time of applications during scheduling for dynamic voltage frequency scaling (DVFS) capable systems to minimize energy consumption and yet maintain a desired level of performance. The main idea is to construct a schedule table offline and perform a simple table look-up at runtime. The second aspect is to consider application-level reliability for applications that can tolerate certain error in the outputs. I present the study of a profile-guided offline compilation strategy to identify critical instructions and a monitoring technique in software to handle corner cases at runtime. Finally, the third aspect of energy efficient computing I investigate is flexibility – customizing the instruction sets of processors to improve energy efficiency. I study the benefits of compiler directed optimizations for generating custom instructions which are executed within a modified processor pipeline and an architecture mechanism for detecting corner cases and to roll-back to a safe state. Additionally, I investigate the benefits of customizing the instruction set dynamically in hardware.

The dissertation of Karthik Gururaj is approved.

Yuval Tamir

Glenn Reinman

Lei He

Jason Cong, Committee Chair

University of California, Los Angeles 2013

To my family who have supported me at every step.

### Table of Contents

| 1  | Intr  | roduct | ion                                                              | 1  |

|----|-------|--------|------------------------------------------------------------------|----|

|    | 1.1   | Energ  | y efficient multiprocessor task scheduling under input-dependent |    |

|    |       | variat | ion                                                              | 2  |

|    | 1.2   | Assur  | ing application-level correctness in programs                    | 2  |

|    | 1.3   | Archit | tecture support for custom instructions with memory operations   | 2  |

|    | 1.4   | Archit | secture support for dynamic instruction set customization        | 3  |

| 2  | Ene   | ergy E | fficient Multiprocessor Task Scheduling under Input-             |    |

| d€ | epend | dent V | ariation                                                         | 4  |

|    | 2.1   | Introd | luction                                                          | 4  |

|    |       | 2.1.1  | Workload agnostic techniques                                     | 4  |

|    |       | 2.1.2  | Workload aware techniques                                        | 5  |

|    |       | 2.1.3  | Exploiting variation in execution time                           | 7  |

|    |       | 2.1.4  | Uni-processor Systems                                            | 7  |

|    |       | 2.1.5  | Multiprocessor Systems                                           | 7  |

|    | 2.2   | Prelin | ninaries and problem statement                                   | 9  |

|    |       | 2.2.1  | Processor Model                                                  | 9  |

|    |       | 2.2.2  | Application Model                                                | 10 |

|    |       | 2.2.3  | Problem Statement                                                | 12 |

|    | 2.3   | VAR-   | $\Gamma B$ – Variation-aware Time Budgeting                      | 12 |

|    |       | 2.3.1  | Task assignment heuristic                                        | 12 |

|    |       | 2.3.2  | Task scheduling and voltage assignment                           | 13 |

|    |       | 2 3 3  | Mathematical formulation of VAR-TB                               | 13 |

|   | 2.4 | Improving the scheduling algorithm |                                                     |    |  |

|---|-----|------------------------------------|-----------------------------------------------------|----|--|

|   |     | 2.4.1                              | Restricting the number of $SCE(v)$ entries per task | 17 |  |

|   |     | 2.4.2                              | Time complexity                                     | 18 |  |

|   |     | 2.4.3                              | Online algorithm                                    | 19 |  |

|   |     | 2.4.4                              | Voltage switching overhead                          | 19 |  |

|   |     | 2.4.5                              | Discrete voltages                                   | 20 |  |

|   | 2.5 | Exper                              | imental Results                                     | 21 |  |

|   |     | 2.5.1                              | Random task-graphs                                  | 22 |  |

|   |     | 2.5.2                              | Real-world Benchmarks                               | 24 |  |

|   | 2.6 | Concl                              | usions                                              | 28 |  |

| 3 | Ass | uring .                            | Application-level Correctness Against Soft Errors   | 31 |  |

|   | 3.1 | Introd                             | luction                                             | 31 |  |

|   | 3.2 | Relate                             | ed work and our contributions                       | 33 |  |

|   |     | 3.2.1                              | Monte-Carlo based techniques:                       | 33 |  |

|   |     | 3.2.2                              | Program analysis techniques                         | 33 |  |

|   |     | 3.2.3                              | Using program invariants and patterns               | 34 |  |

|   | 3.3 | Progra                             | am Representation                                   | 36 |  |

|   |     | 3.3.1                              | Preliminaries                                       | 36 |  |

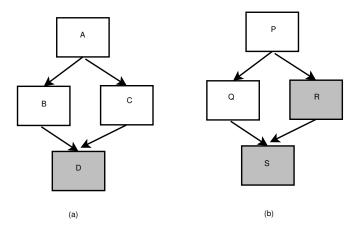

|   |     | 3.3.2                              | Program representation                              | 39 |  |

|   | 3.4 | Overv                              | iew of the proposed method                          | 41 |  |

|   |     | 3.4.1                              | Constructing PDG and computing edge weights         | 41 |  |

|   |     | 3.4.2                              | Constructing PDG                                    | 42 |  |

|   |     | 3.4.3                              | Computing edge weights - Static method              | 43 |  |

|   | 3 5 |                                    | uting o-AFFECTER from weighted PDC                  | 15 |  |

|    |       | 3.5.1   | Acyclic PDG                                                    | 45 |

|----|-------|---------|----------------------------------------------------------------|----|

|    |       | 3.5.2   | PDG with cycles                                                | 46 |

|    |       | 3.5.3   | Identification of critical instructions                        | 47 |

|    |       | 3.5.4   | Control flow optimization                                      | 47 |

|    | 3.6   | Assuri  | ing application-level correctness - profiling and runtime mon- |    |

|    |       | itoring | g                                                              | 50 |

|    |       | 3.6.1   | Profiling edge weights                                         | 50 |

|    |       | 3.6.2   | Runtime monitoring of edge weights                             | 51 |

|    |       | 3.6.3   | Ensuring application-level correctness                         | 53 |

|    | 3.7   | Exper   | iments and Results                                             | 53 |

|    |       | 3.7.1   | Error injection methodology                                    | 54 |

|    |       | 3.7.2   | Illegal memory accesses                                        | 54 |

|    |       | 3.7.3   | Analysis of results                                            | 60 |

|    | 3.8   | Concl   | usion                                                          | 61 |

|    |       |         |                                                                |    |

| 4  | Arc   | hitectı | are support for custom instructions with memory op-            |    |

| er | ation | ıs      |                                                                | 62 |

|    | 4.1   | Introd  | luction                                                        | 62 |

|    | 4.2   | Relate  | ed work and our contributions                                  | 63 |

|    |       | 4.2.1   | ALU-like CFUs                                                  | 63 |

|    |       | 4.2.2   | CFUs with memory operations                                    | 64 |

|    |       | 4.2.3   | CFUs with Architecturally Visible Storage (AVS)                | 64 |

|    |       | 4.2.4   | Context-full CFUs                                              | 65 |

|    |       | 4.2.5   | Our contributions                                              | 65 |

| 4.3 | Challenges and our proposed solution for supporting memory op- |                                                               |    |  |  |

|-----|----------------------------------------------------------------|---------------------------------------------------------------|----|--|--|

|     | eratio                                                         | ns in CFUs                                                    | 67 |  |  |

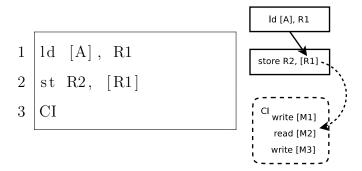

|     | 4.3.1                                                          | Issue 1: Maintaining program order for memory operations      | 68 |  |  |

|     | 4.3.2                                                          | Issue 2: Ordering of memory operations within a CI $\ldots$ . | 70 |  |  |

|     | 4.3.3                                                          | Issue 3: Possible partial commit to memory                    | 70 |  |  |

|     | 4.3.4                                                          | Issue 4: Handling TLB faults                                  | 71 |  |  |

|     | 4.3.5                                                          | Issue 5: Handling variable number of memory operations .      | 71 |  |  |

|     | 4.3.6                                                          | Scenarios where our architecture would beat a system with     |    |  |  |

|     |                                                                | compiler inserted synchronization                             | 72 |  |  |

|     | 4.3.7                                                          | Difference with CISC ISAs                                     | 73 |  |  |

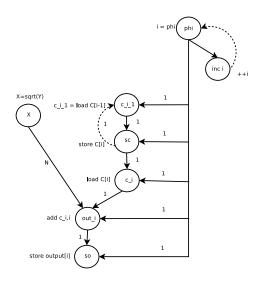

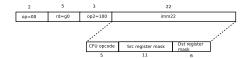

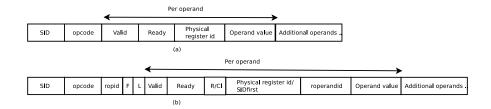

| 4.4 | Custo                                                          | m instruction operation and representation                    | 74 |  |  |

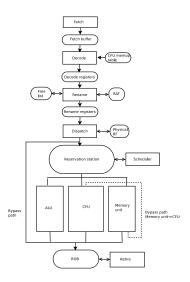

| 4.5 | Detail                                                         | s of proposed architecture                                    | 76 |  |  |

|     | 4.5.1                                                          | Fetch stage                                                   | 77 |  |  |

|     | 4.5.2                                                          | Decode stage                                                  | 77 |  |  |

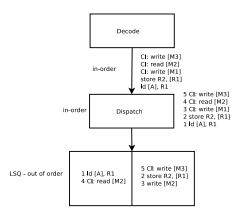

|     | 4.5.3                                                          | Rename stage                                                  | 79 |  |  |

|     | 4.5.4                                                          | Dispatch stage                                                | 79 |  |  |

|     | 4.5.5                                                          | Scheduler and execute stage                                   | 82 |  |  |

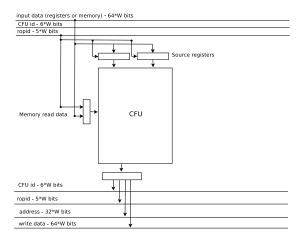

|     | 4.5.6                                                          | Communication with CFUs                                       | 83 |  |  |

|     | 4.5.7                                                          | Retire stage                                                  | 84 |  |  |

| 4.6 | Comp                                                           | iler flow for creating CIs                                    | 87 |  |  |

| 4.7 | Result                                                         | ts                                                            | 88 |  |  |

|     | 4.7.1                                                          | Evaluation setup                                              | 88 |  |  |

|     | 4.7.2                                                          | Comparison with baseline                                      | 89 |  |  |

|     | 473                                                            | Comparison with restricted CIs                                | 91 |  |  |

|   |     | 4.7.4   | Sensitivity with respect to FPGA resource availability     | 93  |

|---|-----|---------|------------------------------------------------------------|-----|

|   |     | 4.7.5   | Comparison under equal area constraint                     | 93  |

|   | 4.8 | Conclu  | isions                                                     | 95  |

| 5 | Arc | hitectu | are support for dynamic instruction set customization      | 98  |

|   | 5.1 | Introd  | uction                                                     | 98  |

|   | 5.2 | Relate  | d work                                                     | 100 |

|   |     | 5.2.1   | Static instruction set customization                       | 100 |

|   |     | 5.2.2   | Dynamically configurable functional units                  | 101 |

|   |     | 5.2.3   | Dynamic instruction stream customization                   | 102 |

|   |     | 5.2.4   | Trace cache based methods                                  | 102 |

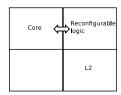

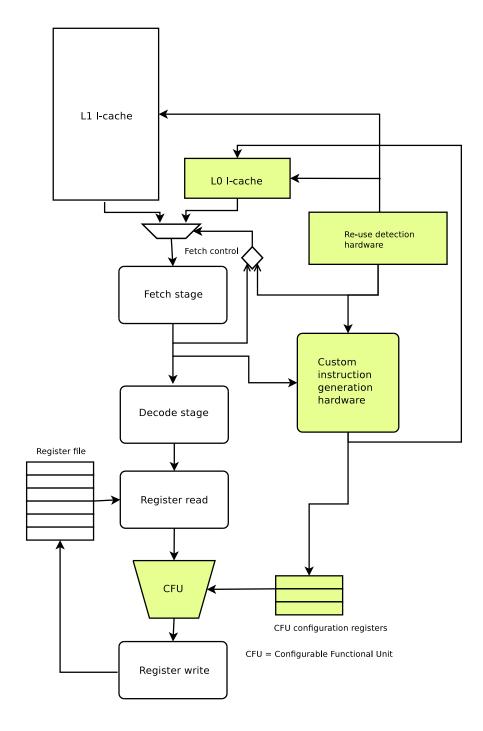

|   | 5.3 | System  | n overview                                                 | 103 |

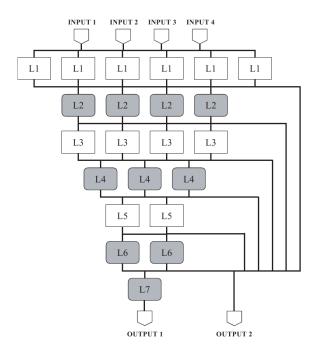

|   | 5.4 | CFU a   | architecture                                               | 105 |

|   | 5.5 | Identif | ying frequently executed parts of an application           | 107 |

|   | 5.6 | Challe  | nges in generating CIs and optimized instruction stream    | 108 |

|   |     | 5.6.1   | Generating correct CIs                                     | 108 |

|   |     | 5.6.2   | Generating correct optimized instruction stream            | 109 |

|   | 5.7 | Hardw   | rare support for CI construction and optimized instruction |     |

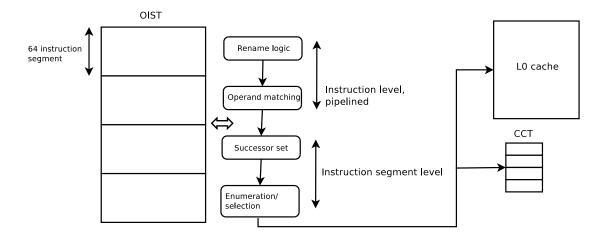

|   |     | stream  | generation                                                 | 112 |

|   |     | 5.7.1   | Determining instruction dependences                        | 112 |

|   |     | 5.7.2   | Subgraph enumeration                                       | 113 |

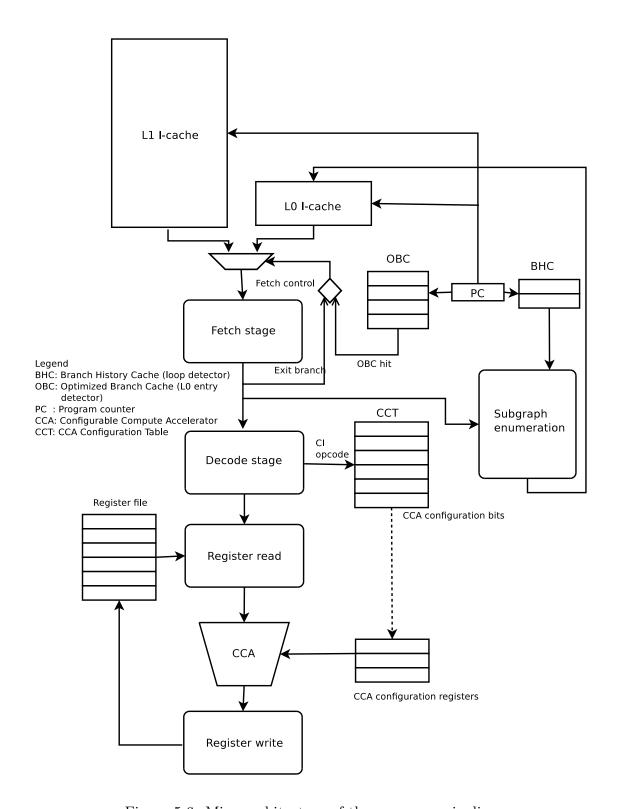

|   | 5.8 | Puttin  | g it all together                                          | 115 |

|   |     | 5.8.1   | Fetch stage                                                | 115 |

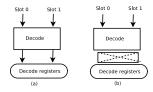

|   |     | 5.8.2   | Decode stage                                               | 117 |

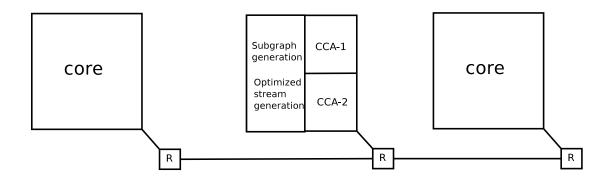

|   |     | 5.8.3   | Extension to CMP systems                                   | 119 |

| R | efere | nces   |                                                         | 138 |

|---|-------|--------|---------------------------------------------------------|-----|

| 6 | Con   | clusio | ns and Future Directions                                | 136 |

|   | 5.10  | Conclu | usions                                                  | 135 |

|   |       | 5.9.4  | Studying the impact of sharing hardware structures      | 130 |

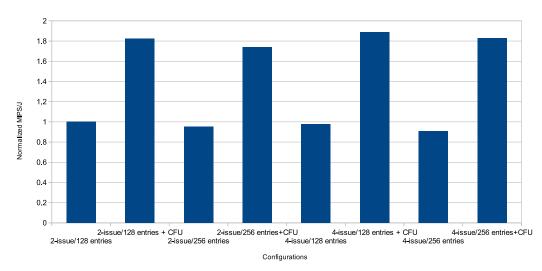

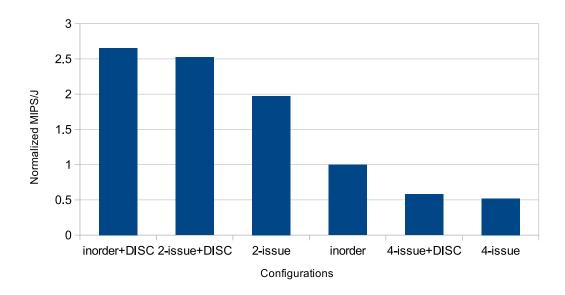

|   |       | 5.9.3  | Comparison with baseline and previous work              | 123 |

|   |       |        | structures                                              | 121 |

|   |       | 5.9.2  | Evaluating the impact of sizes of the proposed hardware |     |

|   |       | 5.9.1  | Evaluation framework                                    | 120 |

|   | 5.9   | Result | SS                                                      | 120 |

## LIST OF TABLES

| 2.1 | Sample schedule table                                               | 11 |

|-----|---------------------------------------------------------------------|----|

| 2.2 | Processor characteristics                                           | 21 |

| 3.1 | Simulation parameters                                               | 54 |

| 3.3 | Comparison with [83]: columns under 'Error-free' and 'Errors in-    |    |

|     | serted' show the $\#$ instructions executed without and with errors |    |

|     | at runtime respectively, column titled 'Energy reduction' shows the |    |

|     | energy reduction relative to [83]                                   | 55 |

| 3.3 | Comparison with [83]: columns under 'Error-free' and 'Errors in-    |    |

|     | serted' show the $\#$ instructions executed without and with errors |    |

|     | at runtime respectively, column titled 'Energy reduction' shows the |    |

|     | energy reduction relative to [83]                                   | 56 |

| 3.2 | Static instruction classification                                   | 57 |

| 3.4 | Comparison with [103]: columns under 'Error-free' and 'Errors in-   |    |

|     | serted' show the # instructions executed without and with errors    |    |

|     | at runtime respectively, column titled 'Energy reduction' shows the |    |

|     | energy reduction relative to [103]                                  | 58 |

| 3.4 | Comparison with [103]: columns under 'Error-free' and 'Errors in-   |    |

|     | serted' show the $\#$ instructions executed without and with errors |    |

|     | at runtime respectively, column titled 'Energy reduction' shows the |    |

|     | energy reduction relative to [103]                                  | 59 |

| 3.5 | Overhead associated with runtime monitoring                         | 61 |

| 4.1  | Alias information for benchmarks – columns titled 0-10 show the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

|      | fraction (as percentages) of memory dependences sorted by itera-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

|      | tion distance. The last column shows the ratio of dynamic/static                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

|      | memory dependences (expressed as percentage)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 72  |  |  |

| 4.2  | CI statistics – average over largest CIs per loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84  |  |  |

| 4.3  | Simulation processor parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85  |  |  |

| 4.4  | Normalized performance (#cycles elapsed) with non-pipelined CFUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

|      | on FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85  |  |  |

| 4.5  | Normalized performance (#cycles elapsed) with pipelined CFUs on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |  |  |

|      | FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86  |  |  |

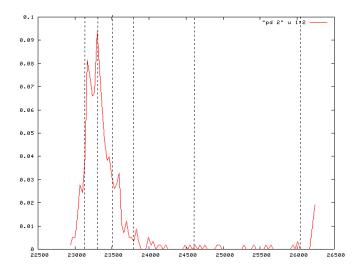

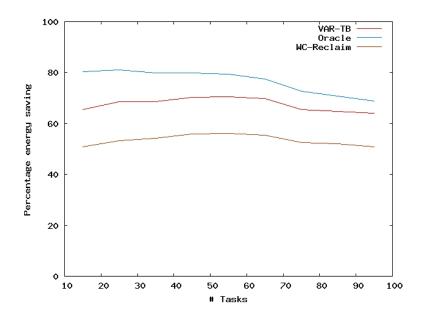

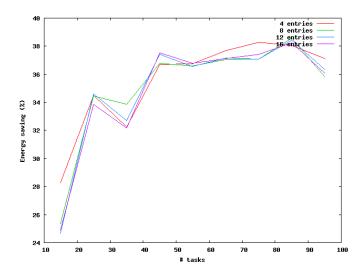

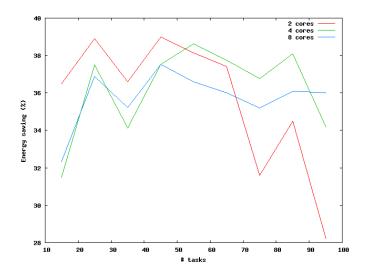

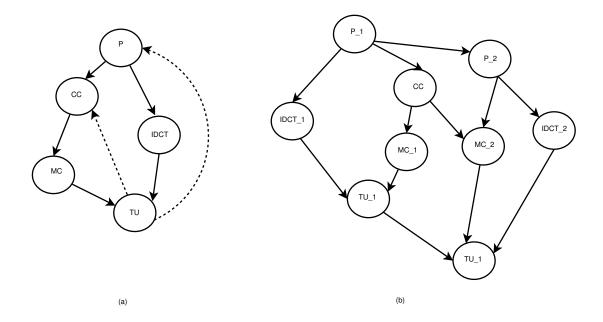

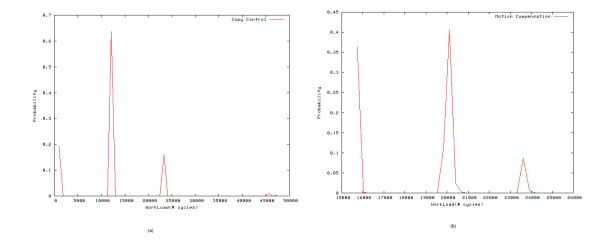

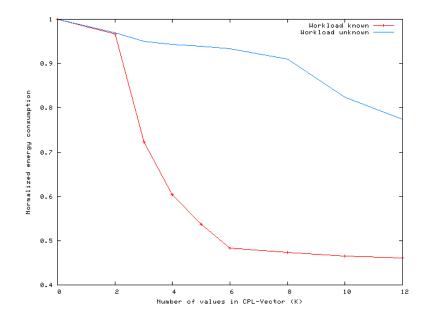

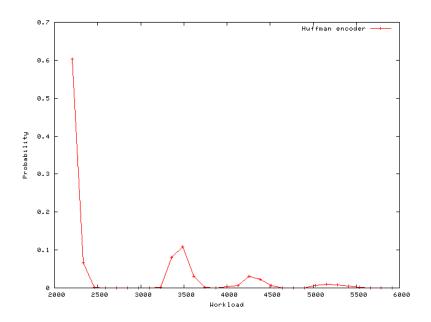

| 4.6  | Normalized total energy consumption with pipelined CFUs on FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 86  |  |  |