# **UC Irvine**

# **UC Irvine Electronic Theses and Dissertations**

### **Title**

Graph Learning for Robust Embedded and Cyber-Physical Systems

### **Permalink**

https://escholarship.org/uc/item/95h5694g

### **Author**

YU, SHIH-YUAN

# **Publication Date**

2023

Peer reviewed|Thesis/dissertation

# $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

# Graph Learning for Robust Embedded and Cyber-Physical Systems ${\bf DISSERTATION}$

submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in Computer Engineering

by

Shih-Yuan Yu

Dissertation Committee: Professor Mohammad Al Faruque, Chair Professor Pramod P. Khargonekar Assistant Professor Yanning Shen

Chapter 2 © 2021 IEEE. Reprinted, with permission, from Shih-Yuan Yu, HW2VEC: a Graph Learning Tool for Automating Hardware Security, 2021 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), December 2021. Chapter 3 is adapted from the Arxiv version of the paper submitted to ICSE SEIP 2023. The work involved in Chapter 3 is supported by the Defense Advanced Research Projects Agency (DARPA) and Naval Information Warfare Center Pacific (NIWC Pacific) under Contract Number N66001-20-C-4024.

Chapter 4 © 2022 IEEE. Reprinted, with permission, from Shih-Yuan Yu, Scene-Graph Augmented Data-Driven Risk Assessment of Autonomous Vehicle Decisions, IEEE Transactions on Intelligent Transportation Systems, July 2022.

Chapter 4  $\odot$  2022 IEEE. Reprinted, with permission, from Arnav Vaibhav Malawade, Spatiotemporal Scene-Graph Embedding for Autonomous Vehicle Collision Prediction, IEEE Internet of Things Journal, June 2022.

All other materials © 2023 Shih-Yuan Yu

# TABLE OF CONTENTS

|              |       |        |                                                                | Page         |

|--------------|-------|--------|----------------------------------------------------------------|--------------|

| LI           | IST ( | OF FIC | GURES                                                          | $\mathbf{v}$ |

| LJ           | IST ( | OF TA  | BLES                                                           | vii          |

| $\mathbf{A}$ | CKN   | OWLI   | EDGMENTS                                                       | viii         |

| $\mathbf{V}$ | ITA   |        |                                                                | ix           |

| $\mathbf{A}$ | BST   | RACT   | OF THE DISSERTATION                                            | xi           |

| 1            | Intr  | oducti | ion and Background                                             | 1            |

|              | 1.1   |        | dded System                                                    |              |

|              | 1.2   |        | -Physical System and Robustness                                |              |

|              | 1.3   |        | Graph Learning?                                                |              |

|              | 1.4   |        | rch Scope                                                      |              |

| 2            | Gra   | ph Lea | arning for Enhancing the Security of Hardware Designs          | 7            |

|              | 2.1   |        | luction                                                        |              |

|              | 2.2   |        | ed Works                                                       |              |

|              |       | 2.2.1  | Hardware Security Threats in IC Supply Chain                   |              |

|              |       | 2.2.2  | The Countermeasures Against Hardware Security Threats          |              |

|              |       | 2.2.3  | Machine Learning for Hardware Security                         |              |

|              |       | 2.2.4  | Graph Learning for Hardware Design and Security                |              |

|              | 2.3   |        | VEC Architecture Introduction                                  |              |

|              |       | 2.3.1  | HW2GRAPH: from hardware design to graph                        |              |

|              |       | 2.3.2  | GRAPH2VEC: from graph to graph embedding                       |              |

|              | 2.4   |        | VEC Use-cases                                                  |              |

|              |       | 2.4.1  | Use-case 1: Converting a Hardware Design to a Graph Embedding. |              |

|              |       | 2.4.2  | Use-case 2: Hardware Trojan Detection (GNN4TJ)                 |              |

|              |       | 2.4.3  | Use-case 3: Hardware IP Piracy Detection (GNN4IP)              |              |

|              | 2.5   | 1      | imental Results                                                |              |

|              |       | 2.5.1  | Dataset Preparation                                            |              |

|              |       | 2.5.2  | The Evaluation of Hardware Trojan Detection (GNN4TJ)           |              |

|              |       | 2.5.3  | The Evaluation of Hardware IP Piracy Detection (GNN4TP)        |              |

|              |       | 2.5.4  | The Evaluation of HW2VEC Tool Timing                           | . 31         |

|   | 2.6 | 2.5.5 The Evaluation of HW2VEC Applicability                     |   |

|---|-----|------------------------------------------------------------------|---|

| 3 |     | ph Learning for Embedded Software Analysis 3                     |   |

| • | 3.1 | Introduction                                                     |   |

|   | 3.2 | Related Works                                                    |   |

|   | 0.2 | 3.2.1 Software Reverse Engineering                               |   |

|   |     | 3.2.2 Machine Learning for Reverse Engineering                   |   |

|   |     | 3.2.3 Graph Learning for Binary Analysis                         |   |

|   | 3.3 | CFG2VEC Architecture                                             |   |

|   | 0.0 | 3.3.1 Problem Formulation                                        |   |

|   |     | 3.3.2 Ghidra Data ToolKit for Graph Extraction                   |   |

|   |     | 3.3.3 Hierarchical Graph Neural Network                          |   |

|   | 3.4 | Experimental Results                                             |   |

|   | 0.4 | 3.4.1 Dataset Preparation                                        |   |

|   |     | 3.4.1 Dataset Freparation                                        |   |

|   |     |                                                                  |   |

|   |     | $\mathbf{e}$                                                     |   |

|   | 2 5 | 3.4.4 The Practical Usage of CFG2VEC                             |   |

|   | 3.5 | Conclusion                                                       | 3 |

| 4 |     | ph Learning for Autonomous Driving Systems 6-                    |   |

|   | 4.1 | Introduction                                                     |   |

|   | 4.2 | Related Works                                                    |   |

|   |     | 4.2.1 ADS Design Philosophies                                    |   |

|   |     | 4.2.2 AV Scene-Graphs and Optimization Techniques 6              |   |

|   |     | 4.2.3 Risk Assessment                                            |   |

|   |     | 4.2.4 Early Collision Prediction                                 | 1 |

|   | 4.3 | SG2VEC: Scene-Graph Augmented Methodology                        | 3 |

|   |     | 4.3.1 Problem Formulation                                        | 3 |

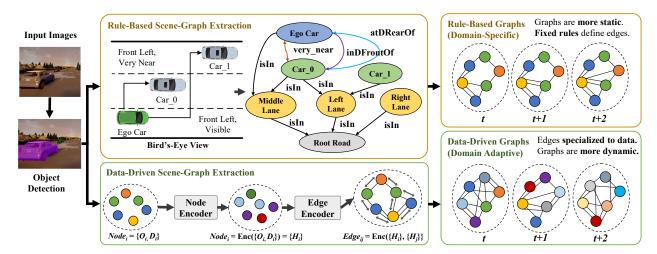

|   |     | 4.3.2 Scene-Graph Extraction                                     | 4 |

|   |     | 4.3.3 Scene-Graph Sequence Model Architecture                    | 6 |

|   |     | 4.3.4 Risk Inference                                             | 0 |

|   | 4.4 | Spatiotemporal Scene-Graph Embedding for collision prediction 8  | 1 |

|   |     | 4.4.1 Problem Formulation                                        | 1 |

|   |     | 4.4.2 Scene-Graph Extraction                                     | 2 |

|   |     | 4.4.3 Early Collision Prediction                                 | 4 |

|   | 4.5 | Experimental Results for Risk Assessment                         | 6 |

|   |     | 4.5.1 Experimental Preparation                                   |   |

|   |     | 4.5.2 The Evaluation of Subjective Risk Assessment               |   |

|   |     | 4.5.3 The Impact of Attention Mechanisms on Risk Assessment 9    |   |

|   |     | 4.5.4 Evaluating Transferability: From Virtual To Real-Driving 9 |   |

|   |     | 4.5.5 Evaluating Risk Assessment for Other Driving Maneuvers 9   |   |

|   | 4.6 | Experimental Results for Early Collision Prediction              |   |

|   |     | 4.6.1 Experimental Preparation                                   |   |

|   |     | 4.6.2 The evaluation of SG2VEC on Collision Prediction           |   |

|                           | 4.6.3      | The evaluation of SG2VEC's Transferability for Collision Prediction | 105 |

|---------------------------|------------|---------------------------------------------------------------------|-----|

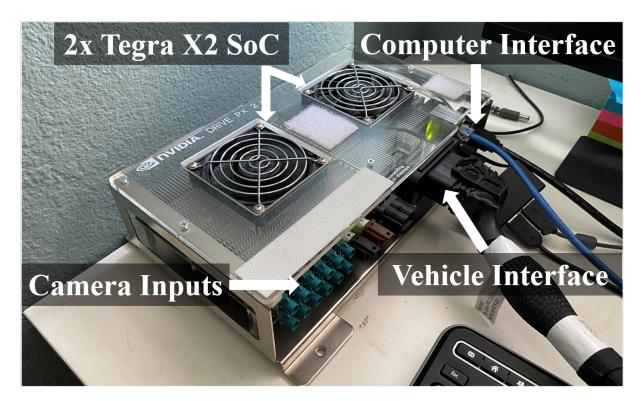

|                           | 4.6.4      | Experimental Results: Evaluation on Industry-Standard AV Hardware   | 106 |

|                           | 4.7 Sum    | mary                                                                | 108 |

| 5                         | Conclusi   | on                                                                  | 111 |

| $\mathbf{B}^{\mathbf{i}}$ | ibliograph | y                                                                   | 114 |

| $\mathbf{A}_{]}$          | ppendix A  | A Other Research Areas                                              | 129 |

# LIST OF FIGURES

|            | I                                                                                                                                                                                                                                                                                                                                                                                                                                                               | age      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

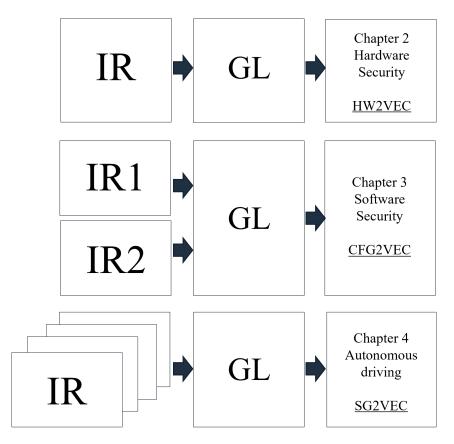

| 1.1        | The illustration of the research scope in this dissertation                                                                                                                                                                                                                                                                                                                                                                                                     | 6        |

| 2.1<br>2.2 | The illustration of the process that extracts features for hardware analysis The illustration of the IC supply chain demonstrating the hardware design flow from a specification to the behavioral description (RTL), logic implementation                                                                                                                                                                                                                      | 9        |

| 2.3        | (GLN), physical implementation (GDSII), and the actual chip (Bare Die or IC) The architecture of <i>HW2VEC</i> . Beginning with hardware design objects (RTL or GLN), the HW2GRAPH leverages PRE_PROC, GRAPH_GEN, and POST_PROC to extract graph representations from hardware designs in the form of node embedding matrix ( <b>X</b> ) and adjacency matrix ( <b>A</b> ). These graphs are then passed to GRAPH2VEC to acquire the graph embeddings for graph | . 12     |

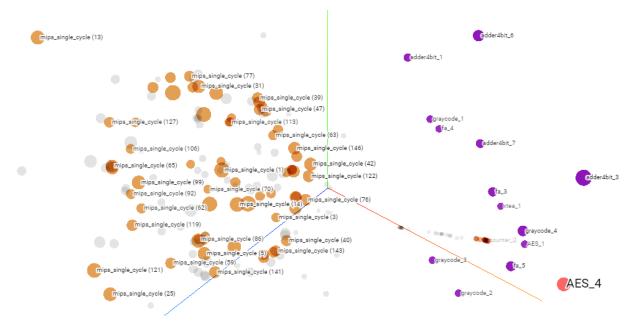

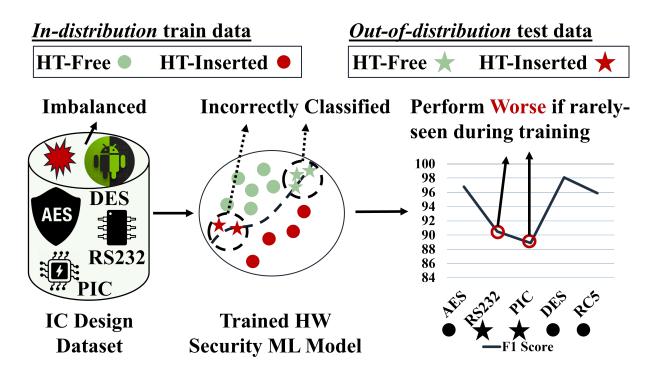

| 2.4<br>2.5 | learning tasks of hardware security                                                                                                                                                                                                                                                                                                                                                                                                                             | 18<br>31 |

|            | generalizing to OOD IC designs                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35       |

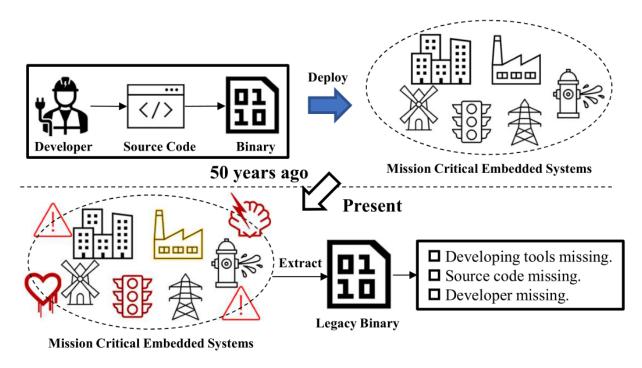

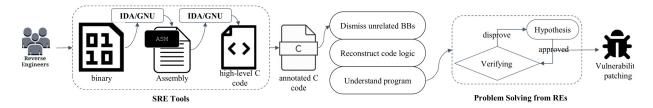

| 3.1<br>3.2 | Legacy software life cycle                                                                                                                                                                                                                                                                                                                                                                                                                                      | 39<br>41 |

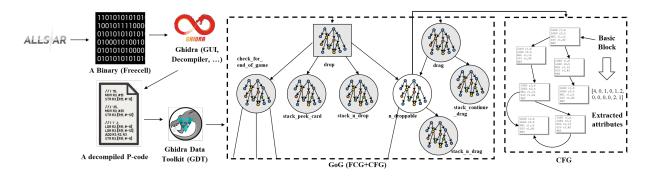

| 3.3        | An example of a <i>Graph-of-Graph</i> (GoG) of a binary compiled from a package Freecell with amd64 CPU architecture.                                                                                                                                                                                                                                                                                                                                           | 45       |

| 3.4        | The architecture of <i>CFG2VEC</i> with a supervised hierarchical graph neural network approach.                                                                                                                                                                                                                                                                                                                                                                | 49       |

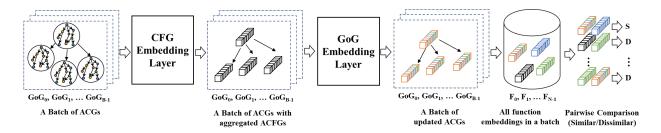

| 3.5        | The plugin screenshot integrated into Ghidra                                                                                                                                                                                                                                                                                                                                                                                                                    | 61       |

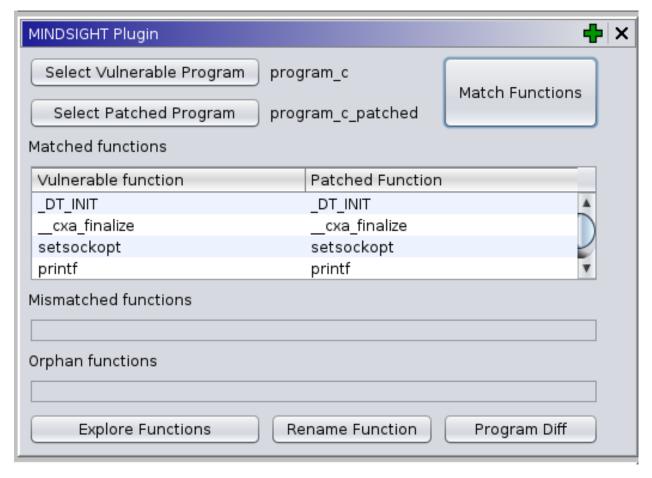

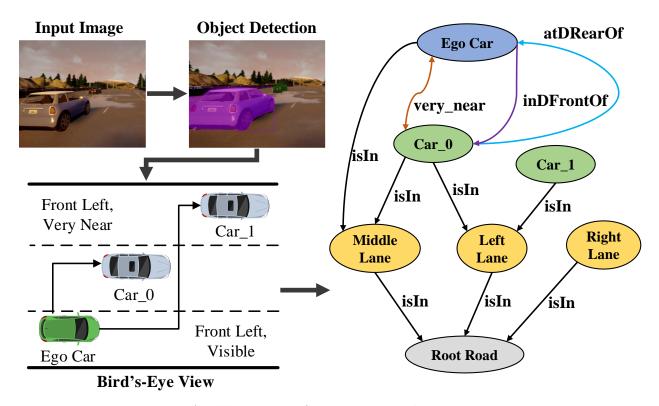

| 4.1        | An illustration of <i>scene-graph</i> extraction using the <i>Real Image Pipeline</i> . In this process, the first step is to detect a list of objects on each clip frame. Then, we project each frame to its bird's-eye view to better approximate the spatial relations between objects. Finally, we construct a <i>scene-graph</i> using the list of detected objects and their attributes                                                                   | 65       |

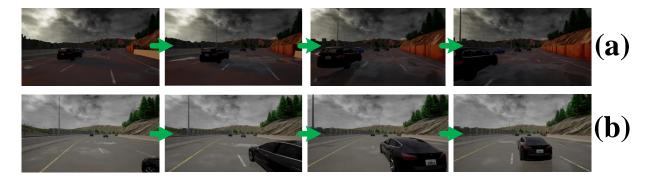

| 4.2        | An example of (a) a lane change that is both <i>subjectively</i> and <i>objectively</i> risky as well as (b) a <i>subjectively safe</i> but <i>objectively risky</i> lane change from our driving dataset. In (a), the ego car starts a safe lane change, but a high-speed vehicle suddenly appears in its blind spot and nearly collides with it. In (b), the ego car appears to drive directly toward the adjacent vehicle but is making                      | 69       |

|            | a safe lane change on a curved road                                                                                                                                                                                                                                                                                                                                                                                                                             | 71       |

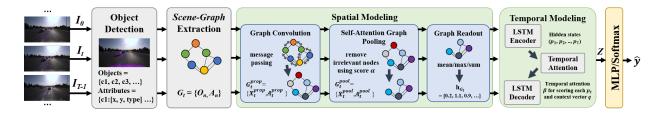

| 4.3   | An illustration of our model's architecture. First, each image $I_t \in \mathbf{I}$ is converted to a scene-graph $G_t$ via the Scene-Graph Extraction Pipeline. Next, |     |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | each scene-graph $G_t$ is converted to its corresponding scene-graph embedding                                                                                         |     |

|       | $\mathbf{h}_{G_t}$ via the graph convolution, pooling, and readout operations in the Spatial                                                                           |     |

|       | Modeling block. Then, the resulting $scene-graph$ embeddings are sequentially                                                                                          |     |

|       | processed by LSTM and temporal attention layers to acquire the spatiotem-                                                                                              |     |

|       | poral representation <b>Z</b> for a scene-graph sequence. Finally, the risk inference $\hat{y}$                                                                        |     |

|       |                                                                                                                                                                        |     |

|       | of the sequence is calculated from <b>Z</b> using an MLP with a <i>Softmax</i> activation                                                                              | 71  |

| 1 1   | function.                                                                                                                                                              | 74  |

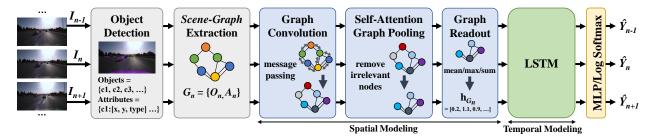

| 4.4   | An illustration of sg2vec's architecture                                                                                                                               | 81  |

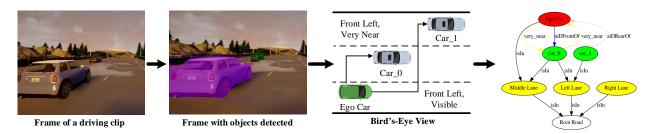

| 4.5   | An illustration of our <i>scene-graph</i> extraction process                                                                                                           | 86  |

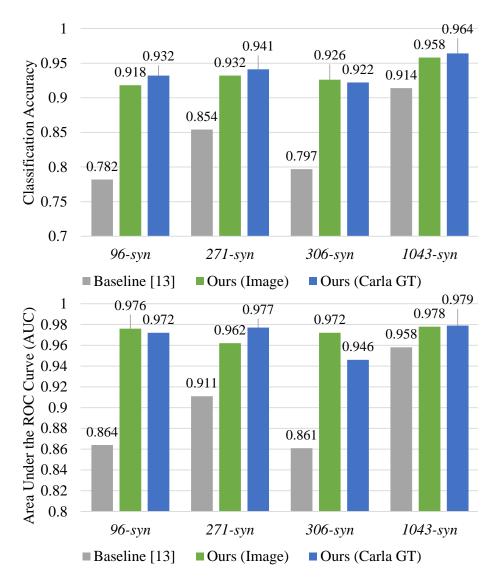

| 4.6   | Accuracy and AUC comparison between our approaches (Real Image and                                                                                                     | 00  |

|       | Carla GT) and [195] on different datasets.                                                                                                                             | 89  |

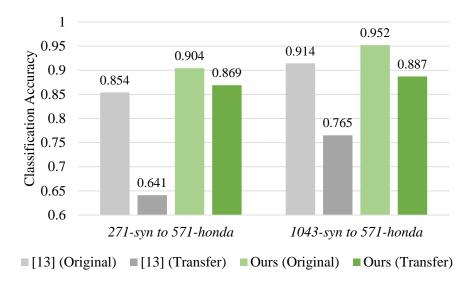

| 4.7   | The results of comparing transferability between our Real Image model and                                                                                              |     |

|       | [195]. In this experiment, we trained our model using our best hyper-parameters                                                                                        |     |

|       | on both 271-syn dataset and 1043-syn dataset. Then we tested the accuracy                                                                                              |     |

|       | of our approach on both the original dataset and 571-honda dataset. We                                                                                                 |     |

|       | followed the same procedure to train and test [195]                                                                                                                    | 93  |

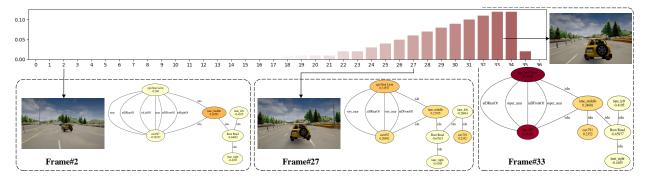

| 4.8   | The visualization of attention weights in both spatial $(\alpha)$ and temporal $(\beta)$                                                                               |     |

|       | domains using a risky lane-changing clip as an example. We used a gradient                                                                                             |     |

|       | color from light yellow to red for visualizing each node's projection score that                                                                                       |     |

|       | indicates its importance in calculating a <i>scene-graph</i> embedding. We also used                                                                                   |     |

|       | a gradient colored (white to red) bar chart to visualize the temporal attention                                                                                        |     |

|       | coefficients $\beta_1, \beta_2, \beta_{36}$ used for calculating the context vector $c$                                                                                | 95  |

| 4.9   | Examples of driving scenes from our a) synthetic datasets, b) typical real-                                                                                            |     |

|       | world dataset, and c) complex real-world dataset. In a), all driving scenes                                                                                            |     |

|       | occur on highways with the same camera position and clearly defined road                                                                                               |     |

|       | markings; lighting and weather are dynamically simulated in CARLA. In b)                                                                                               |     |

|       | driving scenes occur on multiple types of clearly marked roads but lighting,                                                                                           |     |

|       | camera angle, and weather are consistent across scenes. c) contains a much                                                                                             |     |

|       | broader range of camera angles as well as more diverse weather and lighting                                                                                            |     |

|       | conditions, including rain, snow, and night-time driving; it also contains a                                                                                           |     |

|       | large number of clips on unpaved or unmarked roadways, as shown                                                                                                        | 98  |

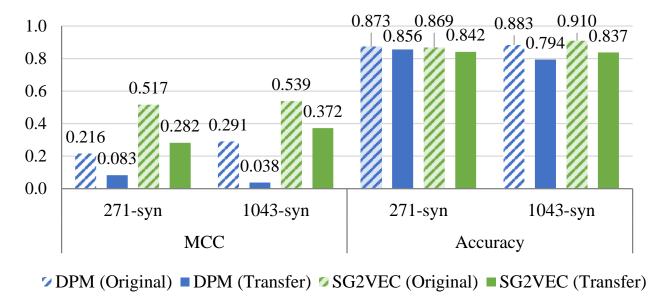

| 4.10  | Performance after transferring the models trained on synthetic 271-syn and                                                                                             |     |

|       | 1043-syn datasets to the real-world 571-honda dataset                                                                                                                  | 105 |

| 4.11  | Our experimental setup for evaluating SG2VEC and DPM on the industry-                                                                                                  | 465 |

| 4 4 0 | standard Nvidia DRIVE PX 2 hardware                                                                                                                                    | 107 |

| 4.12  | The differences between the scene-graphs generated by $RS2G$ and those ex-                                                                                             | 465 |

|       | tracted with a rule-based method for a driving scene                                                                                                                   | 109 |

# LIST OF TABLES

|     |                                                                                                                                                           | Page   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2.1 | The performance of HT detection using HW2VEC                                                                                                              | 29     |

| 2.2 | The results of detecting IP piracy with $HW2VEC$                                                                                                          | 31     |

| 2.3 | The time profiling for training/inference                                                                                                                 | 32     |

| 2.4 | The graph extraction time profiling. For <i>TJ-DFG-RTL</i> , the hardware AES and DES jointly take 472.46 seconds on average for DFG extraction while the |        |

|     | rest of the data instances take 16.7 seconds on average                                                                                                   | 33     |

| 3.1 | The statistics of datasets used in our experiments                                                                                                        | 54     |

| 3.2 | The performance evaluation of cfg2vec for function name prediction against                                                                                |        |

|     | $[79].  \ldots $                   | 54     |

| 3.3 | The comparison between $CFG2VEC$ and its ablated variations                                                                                               | 56     |

| 3.4 | The cross-architectural comparison between cfg2vec and [79]                                                                                               | 59     |

| 4.1 | The results of the Carla GT approach on 1043-syn dataset with various spatial and temporal modeling settings. In these experiments, we used MR-GCN        |        |

|     | layers with $64$ hidden units and $sum$ -pooling as the graph readout operation.                                                                          | 92     |

| 4.2 | The breakdown of risk assessment performance by driver action types (Lane-                                                                                |        |

|     | Changing, Merging, Branching, and Turning) evaluated on 1361-Honda dataset                                                                                | et. 97 |

| 4.3 | Classification accuracy, AUC, and MCC for SG2VEC (Ours) and DPM                                                                                           | 101    |

| 4.4 | SG2VEC ablation study on the $1043$ -syn dataset                                                                                                          | 102    |

| 4.5 | Average time of prediction (ATP) for collisions                                                                                                           | 104    |

| 4.6 | Performance evaluation of inference on 271-syn on the Nvidia DRIVE PX 2.                                                                                  | 107    |

### ACKNOWLEDGMENTS

I first want to thank my committee chair, Professor Mohammad Abdullah Al Faruque, for allowing me to return from industry to academia and pursue my Ph.D. There were ups and downs; however, Professor Al Faruque constantly guided me through the research and gave me valuable insights. Without his excellent supervision and persistent mentoring, I would not have been able to complete this thesis. I also want to thank my Ph.D. committee members: Professor Pramod Khargonekar and Assistant Professor Yanning Shen, for sparing precious time from their hectic schedules to provide supervision, support, and insightful comments for the thesis. Besides, I appreciate the help from Assistant Professor Zhou Li and Alfred Chen during my qualification examination.

I thank Dr. Sujit Rokka Chhetri for engaging and inspiring me to get involved in novel research ideas. Without his mentorship, I would not have gained this many achievements throughout my Ph.D. I thank my fellow lab-mates for engaging me in stimulating discussions. I particularly want to appreciate the precious time and efforts spared by Arnav Malawade and Rozhin Yasaei. Together, we have made some marks in the research communities. My sincere thanks go to my fellow collaborators, Dr. Deepan Muthirayan, Dr. Gustavo Quirós, Dr. Arquimedes Canedo, and Adjunct Professor Lawrence Kulinsky; they gave me opportunities to widen my vision and the scope of my research. Besides, I want to thank the principal investigators and leaders in Siemens Technologies, Dr. Nemeth Laszlo, Assistant Professor Sharma Tushar, Dr. Ramamurthy Arun, Dr. Akrotirianakis Ioannis, Dr. Amar Viswanathan for allowing me to collaborate with their research groups and broaden my horizons. I wish everyone the best in enjoying their following research journeys.

I also thank my fellow colleagues from the Autonomous and Intelligent Cyber-Physical Systems (AICPS) laboratory, Mohanad Odema, Luke Chen, Yonatan Gizachew, Ahmet Aksakal, Trier Mortlock, Nafiul Rashid, and Anomadarshi Barua for collaborating in various research endeavors. I want to thank many of my undergraduate students, Aung Myat Thu, Tommy Nguyen, Emily Lam, Yasamin Moghaddas, FangZhou Du, George Chin-Yuan Ting, Qingrong Zhou, Chonghan Wang, and Lelin Pan, for making contributions to my research works. I wish everyone the best in their lives.

Last but not least, I would like to thank my beloved mother and father-like brother for their unconditional love and belief in me. I want to appreciate the social support from my miscellaneous friends for making these difficult times relaxing. Particularly, I want to express my since gratitude to my wife, *Pin-Chun Chen*, for the much-needed love and support that helped me carry on through my Ph.D. during the unfortunate pandemic.

# **VITA**

# Shih-Yuan Yu

### **EDUCATION**

| Doctor of Philosophy in Computer Engineering                                                                                 | 2023 |

|------------------------------------------------------------------------------------------------------------------------------|------|

| University of California, Irvine (UCI), Irvine, California                                                                   |      |

| Master of Science in Computer Science and Information Engineering<br>National Taiwan University (NTU), <i>Taipei, Taiwan</i> | 2014 |

| Bachelor of Science in Computer Science and Information Engineer-                                                            | 2012 |

| ing                                                                                                                          |      |

| National Taiwan University (NTU) Taipei, Taiwan                                                                              |      |

# RESEARCH EXPERIENCE

| Graduate Research Assistant                      | Sep. 2018 - Jun. 2023 |

|--------------------------------------------------|-----------------------|

| University of California, Irvine (UCI)           | Irvine, California    |

| Compute Systems Performance & Reliability Intern | JunSep. 2022          |

| TuSimple Inc.                                    | San Diego, California |

| Automation Runtime Systems Internship            | JunSep. 2021          |

| Siemens Technology                               | Princeton, New Jersey |

| Research Assistant                               | Jul. 2012 - Jun. 2014 |

| National Taiwan University (NTU)                 | Taipei, Taiwan        |

### TEACHING EXPERIENCE

| Teaching Assistant for EECS 111         | 2023 Spring        |

|-----------------------------------------|--------------------|

| System Software                         | Irvine, California |

| Teaching Assistant for EECS 118         | 2023 Winter        |

| Introduction to Artificial Intelligence | Irvine, California |

| Teaching Assistant for EECS 111         | 2022 Spring        |

| System Software                         | Irvine, California |

### REFERRED JOURNAL AND CONFERENCE PUBLICATIONS

| CFG2VEC:                                                                         | Hierarchical   | Graph     | Neural    | ${\bf Network}$ | for | Cross- | 2023 |

|----------------------------------------------------------------------------------|----------------|-----------|-----------|-----------------|-----|--------|------|

| Architectural                                                                    | l Software Rev | verse Eng | gineering |                 |     |        |      |

| International Conference on Software Engineering / Software Engineering in Prac- |                |           |           |                 |     |        |      |

| tice                                                                             |                |           |           |                 |     |        |      |

Hardware Trojan Detection Using Graph Neural Networks

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

| Roadscene2vec: A Tool for Extracting and Embedding Road Scene-Graphs Knowledge-Based Systems 242, 108245                                                                                                              | 2022 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Artificial Intelligence Algorithms Enable Automated Characterization of The Positive and Negative Dielectrophoretic Ranges of Applied Frequency Micromachines 13 (3), 399                                             | 2022 |

| Spatiotemporal Scene-Graph Embedding for Autonomous Vehicle<br>Collision Prediction<br>IEEE Internet of Things Journal 9 (12), 9379-9388                                                                              | 2022 |

| HW2VEC: A Graph Learning Tool for Automating Hardware Security IEEE International Symposium on Hardware Oriented Security and Trust                                                                                   | 2021 |

| Graph Learning for Cognitive Digital Twins in Manufacturing Systems IEEE Transactions on Emerging Topics in Computing 10 (1), 34-45                                                                                   | 2021 |

| Establishing Digital Recognition and Identification of Microscopic Objects for Implementation of Artificial Intelligence (AI) Guided Microassembly Proceedings of World Congress on Micro and Nano Manufacturing 2021 | 2021 |

| Scene-Graph Augmented Data-Driven Risk Assessment of Autonomous Vehicle Decisions IEEE Transactions on Intelligent Transportation Systems                                                                             | 2021 |

| Cognitive Digital Twin for Manufacturing Systems IEEE/ACM Design Automation and Test in Europe Conference (DATE'21)                                                                                                   | 2021 |

| GNN4TJ: Graph Neural Networks for Hardware Trojan Detection at Register Transfer Level IEEE/ACM Design Automation and Test in Europe Conference (DATE'21)                                                             | 2021 |

| GNN4IP: Graph Neural Network for Hardware Intellectual Property Piracy Detection Design automation Conference (DAC)                                                                                                   | 2021 |

| Pykg2vec: A python library for knowledge graph embedding<br>The Journal of Machine Learning Research 22 (1), 754-759                                                                                                  | 2021 |

| Multimodal Knowledge Graph for Deep Learning Papers and Code<br>Conference on Information and Knowledge Management (CIKM)                                                                                             | 2020 |

| Sabotage Attack Detection for Additive Manufacturing Systems IEEE Access                                                                                                                                              | 2020 |

# ABSTRACT OF THE DISSERTATION

Graph Learning for Robust Embedded and Cyber-Physical Systems

By

Shih-Yuan Yu

Doctor of Philosophy in Computer Engineering

University of California, Irvine, 2023

Professor Mohammad Al Faruque, Chair

Since the appearance of microprocessors, miscellaneous categories of computer systems, including Embedded and Cyber-Physical Systems (ECPS), have become an integral part of our modern society. In contrast to general-purpose computers, an ECPS is a computing system designed to perform a dedicated or narrow range of functions with minimal human intervention. Today, the advanced standards in device networking, ubiquitous access to the Internet, miniaturization of processors, and reduced power consumption have taken this field to the next level. However, despite these technological growths, designing a robust ECPS remains an open research challenge where the goal is to achieve better functionalities, encompass complex, uncertain, and changing environments, and ensure system security. Minor failures on ECPS may cause severe collapses or cyberattacks, impeding progress toward increasing automation and modernizing our computing environments.

To achieve robustness, this dissertation studies the embedding of Computational Intelligence (CI) into emerging Graph Learning (GL) technologies. The CI paradigms mimic the nature of humans, aiming at solving complex problems and exhibiting a cognitive ability to learn or adapt to new situations to generalize, abstract, discover, and associate. As a prerequisite of this research direction, Machine Learning (ML) has become increasingly ubiquitous, with existing works exploring various fields, from self-driving vehicles, facial recognition systems,

and real-time language translation to security surveillance, innovative home applications, and health monitoring. However, conventional ML algorithms typically require appropriate vectorized representations crafted by domain experts to accomplish the desired goals. Graph-structured data have imposed unprecedented challenges on ML due to their inherent complexity. Unlike text, audio, and images, graphs are embedded in an irregular dimension, making some essential operations of ML inapplicable. GL has attracted much attention to new research ideas in several fields. To date, many researchers have proven the usefulness of GL in social computing, information retrieval, computer vision, bioinformatics, economics, and e-commerce. However, its applications in the subfields of ECPS still need to be explored.

In this dissertation, we will cover GL applications for ECPS in robust Integrated Circuit (IC) design analysis for hardware security, robust binary analysis for enabling software security, and ultimately how GL brings the scene-understanding capabilities of autonomous driving systems to the next level. In IC design analysis (Chapter 2), we explore how GL can be leveraged to resolve challenging problems in hardware security. We propose HW2VEC and demonstrate how it can be utilized for  $Hardware\ Trojan\ (HT)$  detection and  $Intellectual\ Property\ (IP)$  piracy detection. Next, in the binary analysis (Chapter 3), we demonstrate how a more advanced GL methodology, called CFG2VEC, can reverse-engineer the semantic source-level information lost during the compilation process, thus making the binary software patching tasks more efficient. Then, we describe our novel methodology, SG2VEC, to enhance autonomous driving systems' scene understanding capabilities (Chapter 4). To enable this cognitive capability, we propose to use scene-graph to encode the surrounding traffic participants and a pipeline of spatiotemporal scene-graph embedding networks to process scene-graphs and learn toward goals.

# Chapter 1

# Introduction and Background

# 1.1 Embedded System

An Embedded System (ES) can be broadly defined as a device that contains tightly coupled hardware and software components to perform a single function [94]. Since the decade 1970, this term has been widely used as we have witnessed the development of the first microprocessor design, TMS1000, which was used in calculators. Typically, an ES forms a part of a larger computer system and is designed not to be independently programmable by the user. Most ES directly interacts with the environments, making decisions in real-time based on their inputs. Therefore, it has to be reactive, consuming inputs in real-time and ensuring proper operations given their outputs. Regardless of the function performed, an ES comprises two components, hardware components (e.g., microcontroller) and software components (e.g., firmware). The ES takes the system inputs and coordinates the hardware component and the software component, eventually determining the system outputs sent back to the human or environment. As time goes on, the complexity of ES grows significantly, and it has been for a more complicated application purpose where the system has to be broken

into several interacting ESs. For example, for a multimedia player, the system includes audio input/output, a digital camera, a video processing system, a hard drive, a user interface (keys, a touchscreen, and a graphic display), power management, and digital communication components where each of these components is supported individually by an ES integrated into the application system. Modern ES has become ubiquitous in almost every aspect of our modern lives, including cellular phones, televisions, and automobiles, and even hidden in some safety-critical systems such as anti-lock brakes, electronic surveillance, and defense systems.

# 1.2 Cyber-Physical System and Robustness

More recently, around 2006, the terminology Cyber-Physical System (CPS) emerged, coined by Helen Gill at the National Science Foundation (NSF). As an advanced version of ES, a full-fledged CPS is typically designed as a "network" of interacting elements with physical input and output instead of as standalone devices [87]. CPS consists of a complex interaction between heterogeneous (different types of computation and communication platforms) and hybrid (discrete and continuous) components. The goal of CPS is to bridge the cyberdomain with physical processes where sensing, actuation, computation, and communication functions are deeply integrated to improve the overall performance, security, and reliability of physical systems. This deep integration has broadened the potential of CPSs in several directions, including intervention (e.g., collision avoidance); precision (e.g., robotic surgery and nano-level manufacturing); operation in dangerous or inaccessible environments (e.g., search and rescue, firefighting, and deep-sea exploration); coordination (e.g., air traffic control, war-fighting); efficiency (e.g., zero-net energy buildings); and augmentation of human capabilities (e.g., in healthcare monitoring and delivery). Today, the advanced standards in device networking, ubiquitous access to the Internet, miniaturization of processors, reduc-

tion in power consumption, and availability of Simulators and Emulators for system design have taken this field to a new generation which is called *Intelligent Cyber-Physical Systems* (iCPS) [47]. The growing demand for autonomy and the need to reduce both the decision-making time and the transmission bandwidth are pushing designers to integrate CPSs with intelligent mechanisms, ultimately reaching real Automation and improving the quality of human life. However, despite these technological growths, designing an iCPS is challenging as it has to be robust against complex, uncertain, and changing environments. Minor system failures may cause severe collapses or cyberattacks, impeding progress toward increasing automation and modernizing our computing environments.

As shown in the literature, a robust design of CPS design includes three features (3S) [86], which stability, security and systematicness. For stability, the CPS system should always reach a stable decision result eventually, regardless of how the environment generates noise and uncertain factors. For security, CPSs should be able to detect and countermeasure the cyber-physical interaction attacks. Lastly, systematicness refers to the fact that the cyber and physical components should be seamlessly integrated together into a systematic design. In the past decade, it has been seen that Artificial Intelligence has become increasingly ubiquitous in everyday life, such as self-driving vehicles, facial recognition systems, and real-time interpretation of different languages to security surveillance, innovative home applications, and health monitoring. Particularly, Machine Learning has been explored in making CPS intelligent, aiming at automating the processes as far as possible and achieving autonomy. One example of such a vision is Industry 4.0, in which emerging technologies such as collaborative robotics, big data, internet of things, artificial intelligence, and virtual and augmented reality jointly create a new paradigm, offering a more automated and efficient system [103]. In this case, self-X properties are of paramount importance in making these CPSs self-adapt or self-organize to cope with high dynamism and high changing environments [56], and such a capability relies on a proper cognition level of the system.

# 1.3 Why Graph Learning?

To date, many intelligent systems generally rely on ML algorithms handling various types of data. However, despite their ubiquity, graph data have imposed unprecedented challenges on ML due to their inherent complexity. Unlike text, audio, and images, graph data are embedded in an irregular domain, making some essential operations of existing ML algorithms inapplicable. For this, many research works have focused on this new field of study, Graph Learning (GL) [176]. Graphs, also called networks, can represent many real-world relations among various entities. A graph is often defined by two sets, i.e., node set and edge set, where the node represents the entity in a graph, and the edge stands for the relationship between a pair of entities. GL refers to ML on graphs where the methods of GL can map the features of a graph to feature vector(s) with the same dimensions in the embedding space. The goal of GL models is to extract the desired features of a graph and the output can be easily used by downstream tasks such as node classification, link prediction, and graph classification without an explicitly embedding process or feature engineering process. Many researchers and practitioners have proven the usefulness of GL in different areas, such as social computing, information retrieval, computer vision, bioinformatics, economics, and e-commerce.

To increase the robustness of ESs and CPSs, this dissertation studies the embedding of Computational Intelligence (CI) with the emerging Graph Learning (GL) technologies. Computational Intelligence (CI) paradigms involve adaptive mechanisms to facilitate intelligent behavior in a complex, uncertain, and changing environment. These paradigms mimic the nature of solving complex problems and exhibit an ability to learn or adapt to new situations to generalize, abstract, discover, and associate. Recently, cognitive intelligence (a.k.a. cognitive computing) [33]has attracted much research attention in various fields originating from neuroscience. One key in cognitive computing is that the human brain consists of two parts: the first relates to distinguishment and determination (perception), and the second

relates to reasoning and explanation. Generally speaking, it aims at understanding the presented information, interpreting its contextual meaning, and drawing deductions through correlation analysis or casual analysis. This derives an idea of *Intermediate Representation* (IR) where a human also adopts a similar mechanism during the cognitive process as it has a computational advantage for only considering a modest number of primitives and their relations and perceptual advantage in viewpoint invariance and robustness to noise based on qualitative discriminations [21]. However, most of the ML-based approaches implicitly assume the existence of the first part (in vectorized form) through the proper manual feature engineering by domain experts, only automating the second part through various types of ML models and learning processes.

# 1.4 Research Scope

In this dissertation, we will explore how to utilize GL to automate the first part (e.g., perception) and make the system more robust regarding performance, generalization, and explainability. As shown in Figure 1.1, specifically, we will cover GL applications for ES and CPS in robust Integrated Circuit (IC) design analysis for hardware security, robust binary analysis for enabling software security, and ultimately how GL brings the scene-understanding capabilities of autonomous driving systems to the next level. In IC design analysis (Chapter 2), we explore how GL can be leveraged to resolve challenging problems in hardware security. We propose HW2VEC and demonstrate how it can be utilized for  $Hardware\ Trojan\ (HT)$  detection and  $Intellectual\ Property\ (IP)$  piracy detection. Next, in the binary analysis (Chapter 3), we demonstrate how a more advanced GL methodology, called CFG2VEC, can reverse-engineer the semantic source-level information lost during the compilation process, thus making the binary software patching tasks more efficient. Then, we describe our novel methodology, SG2VEC, to enhance autonomous driving systems' scene

understanding capabilities (Chapter 4). To enable this cognitive capability, we propose to use scene-graph to encode the surrounding traffic participants and a pipeline of spatiotemporal scene-graph embedding networks to process *scene-graphs* and learn toward goals. During the courses of these projects, we have developed many research tools to confront the technical challenges (mentioned in Appendices). Lastly, we conclude the thesis with key findings and future steps in Chapter 5.

Figure 1.1: The illustration of the research scope in this dissertation.

# Chapter 2

# Graph Learning for Enhancing the Security of Hardware Designs

The globalized Integrated Circuit (IC) supply chain has brought various security threats in each phase of the chain. Although the counteracting solutions based on Machine Learning (ML) exist, most can only achieve the desired performance when security experts define a robust feature extraction process for IC designs. As the hardware designs are non-Euclidean data, designing a robust feature extraction process is challenging and requires manual effort. In this chapter, as a result, I will discuss my proposed research tool HW2VEC that models these IC designs using Graph Learning to enhance the early phases of the IC supply chain.

# 2.1 Introduction

In past decades, the growing design complexity and the time-to-market pressure have jointly contributed to the globalization of the *Integrated Circuit* (IC) supply chain [146]. Along this globalized supply chain, IC designers tend to leverage third-party *Electronic Design*

Automation (EDA) tools and Intellectual Property (IP) cores or outsource costly services to reduce their overall expense. This results in a worldwide distribution of IC design, fabrication, assembly, deployment, and testing [24, 95, 139]. However, such globalization can also make the IC supply chain vulnerable to various hardware security threats such as Hardware Trojan Insertion, IP Theft, Overbuilding, Counterfeiting, Reverse Engineering, and Covert & Side Channel Attacks [143?].

As the consequences of not promptly addressing these security threats can be severe, countermeasures and tools have been proposed to mitigate, prevent, or detect security threats [88]. For example, hardware-based primitives, physical unclonable functions (PUFs) [82], true random number generator (TRNG) [128], and cryptographic hardware can all intrinsically enhance architectural security. The countermeasures built into hardware design tools are also critical for securing the hardware in the early phases of the IC supply chain. Some Machine Learning (ML) based approaches have been proven effective for detecting *Hardware Trojans* (HT) from hardware designs in both Register Transfer Level (RTL) and Gate-Level Netlist (GLN) [73, 77]. Besides, [90] automates the process of identifying the counterfeited ICs by leveraging Support Vector Machine (SVM) to analyze the sensor readings from on-chip hardware performance counters (HPCs). However, as indicated in [159], effectively applying ML models is a non-trivial task as the defenders must first identify an appropriate input representation based on hardware domain knowledge. Therefore, ML-based approaches can only achieve the desired performance with a robust feature representation of a circuit (non-Euclidean data) which is more challenging to acquire than finding the one for Euclidean data such as images, texts, or signals.

In IC design flow, many fundamental objects such as netlists or layouts are natural graph representations [110]. These graphs are non-Euclidean data with irregular structures, thus making it hard to generalize basic mathematical operations and apply them to conventional Deep Learning (DL) approaches [30]. Also, extracting a feature that captures structural

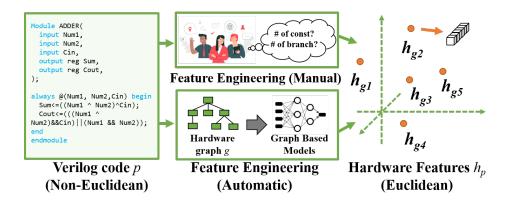

Figure 2.1: The illustration of the process that extracts features for hardware analysis.

information requires a non-trivial effort to achieve the desired performance. To overcome these challenges, many graph learning approaches such as Graph Convolutional Networks (GCN), Graph Neural Networks (GNN), or Graph Autoencoder (GAE) have been proposed and applied in various applications such as computer vision, natural language processing, and program analysis [98, 175]. In the EDA field, some works tackle netlists with GCNs for test point insertion [111] or with GNNs for fast and accurate power estimation in pre-silicon simulation [198]. As Figure 2.1 shows, these approaches typically begin with extracting the graph representation (g) from a hardware design p, then use the graph-based models as an alternative to the manual feature engineering process. Lastly, by projecting each hardware design onto the Euclidean space  $(h_g)$ , these designs can be passed to ML models for learning tasks. However, only a few works have applied GNN-based approaches for securing hardware during IC design phases due to the lack of supporting tools [187, 188].

To attract more research attention to this field, we propose HW2VEC, an open-source graph learning tool for enhancing hardware security. HW2VEC provides automated pipelines for extracting graph representations from hardware designs and leveraging graph learning to secure hardware in design phases. Besides, HW2VEC automates the processes of engineering features and modeling hardware designs. To the best of our knowledge, HW2VEC is the first open-source research tool that supports applying graph learning methods to hardware designs in different abstraction levels for hardware security. In addition, HW2VEC supports

transforming hardware designs into various graph representations such as the *Data-Flow Graph* (DFG), or the *Abstract Syntax Tree* (AST). In this paper, we also demonstrate that *HW2VEC* can be utilized in resolving two hardware security applications: *Hardware Trojan Detection* and *IP Piracy Detection* and can perform as good as the state-of-the-art GNN-based approaches.

Research Contribution: for the hardware security research community,

- We propose an automated pipeline to convert a hardware design in RTL or GLN into various graph representations.

- We propose a GNN-based tool to generate vectorized embeddings that capture the behavioral features of hardware designs from their graph representations.

- We demonstrate HW2VEC's effectiveness by showing that it can perform similarly compared to state-of-the-art GNN-based approaches for various real-world hardware security problems, including  $Hardware\ Trojan\ Detection$  and  $IP\ Piracy\ Detection$ .

- $\bullet$  We open-source HW2VEC as a Python library 1 to contribute to the hardware security research community.

# 2.2 Related Works

This section depicts hardware security problems in the IC supply chain and countermeasures against these security threats. Then, it covers the research works related to ML-based approaches for hardware security. Lastly, we introduce the works that utilize graph learning methods in both EDA and hardware security.

<sup>&</sup>lt;sup>1</sup>The HW2VEC is publicly available at https://github.com/AICPS/hw2vec/. Our readers can refer to [114] for more information about implementation.

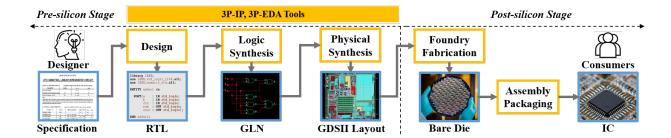

## 2.2.1 Hardware Security Threats in IC Supply Chain

In the Integrated Circuit (IC) supply chain, each IC is passed through multiple processes, as shown in Figure 2.2. First, the specification of a hardware design is turned into a behavioral description written in a Hardware Design Language (HDL) such as Verilog or VHDL. Then, it is transformed into a design implementation in terms of logic gates (i.e., netlist) with Logic Synthesis. Physical Synthesis implements the netlist as a layout design (e.g., a GDSII file). Lastly, the resulting GDSII file is handed to a foundry to fabricate the actual IC. Once a foundry produces the IC (Bare Die), several tests are performed to guarantee its correct behavior. The verified IC is then packaged by the assembly and sent to the market to be deployed in systems.

For a System-on-Chip (SoC) company, all of the mentioned stages of the IC supply chain require a vast investment of money and effort. For example, it costs \$5 billion in 2015 to develop a new foundry [189]. Therefore, to lower R&D costs and catch up with the competitive development cycle, an SoC company may choose to outsource the fabrication to a third-party foundry, purchase third-party IP cores, and use third-party EDA tools. The use of worldwide distributed third parties makes the IC supply chain susceptible to various security threats [177] such as Hardware Trojan Insertion, IP Theft, Overbuilding, Counterfeiting, Reverse Engineering, and Covert & Side Channel Attacks, etc. Not detecting or preventing these threats can lead to severe outcomes. For example, in 2008, a suspected nuclear installation in Syria was bombed by Israeli jets because a backdoor in its commercial off-the-shelf microprocessors disabled Syrian radar [3]. In another instance, the IP-intensive industries of the USA lose between \$225 to \$600 billion annually as the companies from China steal American IPs, mainly in the semiconductor industry [152].

Among the mentioned security threats, the insertion of *Hardware Trojan* (HT) can cause the infected hardware to leak sensitive information, degrade its performance, or even trigger

Figure 2.2: The illustration of the IC supply chain demonstrating the hardware design flow from a specification to the behavioral description (RTL), logic implementation (GLN), physical implementation (GDSII), and the actual chip (Bare Die or IC).

a Denial-of-Service (DoS) attack. In SoC or IC designs, *IP Theft*, the illegal usage and distribution of an IP core can occur. The third-party foundries responsible for outsourced fabrication can *overbuild* extra chips for their benefits without the designer's permission. Moreover, selling the *Counterfeited* designs in the name of its original supplier leads to financial or safety damage to its producer or even the national security if the target is within essential infrastructures or military systems. *Reverse engineering* (RE) recovers the high-level information from a circuit available in its lower-level abstraction. Although RE can be helpful in the design and verification process, an attacker can misuse the reconstructed IC designs for malicious intentions. *Covert Channel* uses non-traditional communication (e.g., shared cache) to leak critical information about a circuit. In contrast, *Side Channel* exists among the hardware components that are physically isolated or not even in proximity (e.g., power or electromagnetic channel) [199, 17, 5, 60, 40, 36, 39, 38, 35, 42, 44].

# 2.2.2 The Countermeasures Against Hardware Security Threats

Due to the globalization of the IC supply chain, hardware is susceptible to security threats such as IP piracy (unlicensed usage of IP), overbuilding (unauthorized manufacturing of the circuit), counterfeiting (producing a faithful copy of the circuit), reverse engineering, hardware Trojan (malicious modification of circuit), and side-channel attacks [11]. In the literature, countermeasures and tools have been proposed to mitigate, prevent, or detect

security threats [88]. For example, a cryptographic accelerator is a hardware-based countermeasure that can reinforce the build-in instead of the add-on defense against security threats.

True Random Number Generator (TRNG) and Physical Unclonable Function (PUF) are two

other effective security primitives [82, 128]. These solutions are critical for security protocols and unique IC identification, and they rely on the physical phenomena for randomness,

stability, and uniqueness, such as process variations during fabrication [159]. In addition to

hardware-based solutions, countermeasures enhancing security during the hardware design

process are also present in the literature. For example, side-channel analysis for HT detection

using various models such as hierarchical temporal memory [59, 18] and DL [58] has grabbed

lots of attention recently. However, they postpone the detection to post-silicon stage.

To defend the HT earlier in the pre-silicon stage, most existing detection techniques fall into one of the following categories. First, as HT typically remains inconspicuous during testing and only gets triggered by a particular event, the authors of [142] attempt to propose an automated Test Pattern Generation method to generate effective test vectors and increase the probability of triggering the HT. However, it is infeasible to cover all the possible testing scenarios. Secondly, Formal Verification (FV) is a pre-silicon algorithmic method that converts the 3PIP to a proof checking format and checks if the IP satisfies some predefined security properties [93, 156]. Although FV leverages the predefined security properties in IP for HT detection, its detection scope is limited to certain types of HTs because they are not comprehensive enough to cover all kinds of malicious behaviors [132]. Some works employ model checking but are not scalable to large designs as model checking is NP-complete and can suffer from state explosion [133]. The third existing category is Code Analysis (CA), which analyzes the hardware design programs using metrics such as line, statement, finite state machine, and toggle coverage to ascertain the suspicious signals that imitate the HT [169, 201]. However, CA requires the designer to manually inspect the suspicious code regions and localize the HTs. Finally, the last category is the graph-based analysis methods as the graph is an intuitive representation of a hardware design. The authors of [125] propose analyzing the data/control flow graph of the IC design to pinpoint the HTs by referencing a library of known HTs graphs and searching for the graph using sub-graph matching. However, sub-graph matching is NP-complete and thus incapable of applying to large designs. In more recent research, [65] proposes a new graph similarity heuristic customized for hardware security to improve accuracy and computation time. However, once again, it can only detect the HTs with the same graph representation as known HTs in their library, while in practice, attackers design a variety of HTs.

As for IP theft prevention, watermarking and fingerprinting are two approaches that embed the IP owner and legal IP user's signatures into a circuit to prevent infringement [127, 129]. Hardware metering is an IP protection method in which the designer assigns a unique tag to each chip for chip identification (passive tag) or enabling/disabling the chip (active tag) [100]. Obfuscation is another countermeasure for IP theft [34] which comprises two main approach; Logic Locking and Camouflaging. In Logic Locking, the designer inserts additional gates such as XOR into non-critical wires. The circuit will only be functional if the correct key is presented in a secure memory out of reach of the attacker [178]. Camouflaging modifies the design such that cells with different functionalities look similar to the attacker and confuses the reverse engineering process [131]. Lastly, another countermeasure is to split the design into separate ICs and have them fabricated in different foundries (e.g., Split Manufacturing) so that none of them can access the whole design to perform malicious activities [124, 200].

In [88], several academic and commercial tools have been proposed to secure hardware. For example, VeriSketch, SecVerilog, etc., are open-source academia verification tools for securing hardware. SecureCheck from Mentor Graphics, JasperGold Formal Verification Platform from Cadence, and Prospect from Tortuga Logic are all commercial verification tools ready in the market. PyVerilog [157] is a hardware design tool that allows users to parse HDL code and perform pre-silicon formal verification side-by-side with functional verification. In short, though many approaches have been proposed to counteract security threats, security

is still an afterthought in hardware design. Therefore, new countermeasures will be needed against new security threats.

# 2.2.3 Machine Learning for Hardware Security

In the last few decades, advancements in Machine Learning (ML) have revolutionized the conventional methods and models in numerous applications throughout the design flow. Defenders can use ML with hardware-based observations for detecting attacks, while attackers can also use ML to steal sensitive information from an IC, breaching hardware security [159]. Some ML-based countermeasures have been proven effective for detecting HT from hardware designs in both Register Transfer Level (RTL) or gate-level netlists (GLN) [73, 77]. In [73], the circuit features are extracted from the Abstract Syntax Tree (AST) representations of RTL codes and fed to a gradient boosting algorithm to train the ML model to construct an HT library. [77] extracts 11 Trojan-net feature values from GLNs and then trains a Multi-Layer Neural Network on them to classify each net in a netlist as a normal netlist or Trojan. Similarly, researchers have applied ML to automate the process of detecting other threats. For instance, SVM can be used to analyze the on-chip sensor readings (e.g., HPCs) to identify counterfeited ICs and detect HT in real-time [90, 101]. However, as indicated in [159], effectively applying ML models is not a trivial task, as the defenders must first identify an appropriate input representation for a hardware design. Unlike Euclidean data such as images, texts, or signals, finding a robust feature representation for a circuit (Non-Euclidean data) is more challenging as it requires domain knowledge in both hardware and ML. To overcome this challenge, HW2VEC provides more effective graph learning methods to automatically find a robust feature representation for a non-Euclidean hardware design.

# 2.2.4 Graph Learning for Hardware Design and Security

Although conventional ML and DL approaches can effectively capture the features hidden in Euclidean data, such as images, text, or videos, there are still various applications where the data is graph-structured. As graphs can be irregular, a graph can have a variable size of unordered nodes, and nodes can have a different number of neighbors, thus making mathematical operations used in deep learning (e.g., 2D Convolution) challenging to be applied [30]. Also, extracting a feature that captures structural information requires challenging efforts to achieve the desired performance. To address these challenges, recently, many graph learning approaches such as Graph Convolutional Networks (GCN), Graph Neural Networks (GNN), or Graph Autoencoder (GAE) have been proposed and applied in various applications [98, 175]. Only by projecting non-Euclidean data into low-dimensional embedding space can the operations in ML methods be applied.

In EDA applications, many fundamental objects such as Boolean functions, netlists, or layouts are natural graph representations [110]. Some works tackle netlists with GCNs for test point insertion [111] or with GNNs for fast and accurate power estimation in *pre-silicon* simulation [198]. [198] uses a GNN-based model to infer the toggle rate of each logic gate from a netlist graph for fast and accurate average power estimation without gate-level simulations, which is a slower way to acquire toggle rates compared to RTL simulation. They use GLNs, corresponding input port, and register toggle rates as input features and logic gate toggle rates as ground-truth to train the model. The model can infer the toggle rate of a logic gate from input features acquired from RTL simulation for average power analysis computed by other power analysis tools.

As for hardware security, only a few works utilizing GNN-based approaches against security threats exist [187, 188, 185]. [188] utilizes a GNN-based approach for detecting HT in *pre-silicon* design phases without the need for golden HT-free reference. Besides, using the GNN-

based approach allows the extraction of features from Data-Flow graphs to be automated. In [187], the proposed GNN-based approach can detect IP piracy without extracting hardware overhead to insert signatures to prove ownership. Specifically, the Siamese-based network architecture allows their approach to capturing the features to assess the similarity between hardware designs as a Data-Flow Graph. In short, these works have shown the effectiveness of securing hardware designs with graph learning approaches. To further attract attention, we propose HW2VEC as a convenient research tool that lowers the threshold for newcomers to make research progress and for experienced researchers to explore this topic more in-depth.

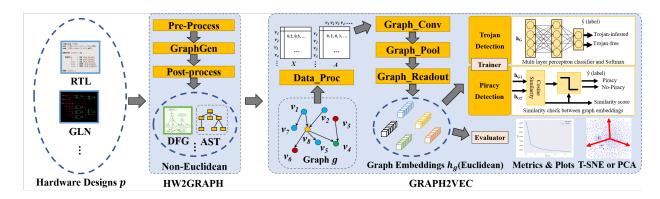

# 2.3 HW2VEC Architecture Introduction

As Figure 2.3 shows, HW2VEC contains HW2GRAPH and GRAPH2VEC. During the IC design flow, a hardware design can have various levels of abstraction, such as High-Level Synthesis (HLS), RTL, GLN, and GDSII, which are fundamentally non-Euclidean data. Overall, in HW2VEC, a hardware design p is first turned into a graph g by HW2GRAPH, which defines the pairwise relationships between objects that preserve the structural information. Then, GRAPH2VEC consumes g and produces the Euclidean representation  $h_g$  for learning.

# 2.3.1 HW2GRAPH: from hardware design to graph

The first step is to convert each hardware design code p into a graph g. HW2GRAPH supports the automatic conversion of raw hardware code into various graph formats such as  $Abstract\ Syntax\ Tree\ (AST)$  or  $Data-Flow\ Graph\ (DFG)$ . AST captures the syntactic structure of hardware code, while DFG indicates the relationships and dependencies between the signals and gives a higher-level expression of the code's computational structure.

Figure 2.3: The architecture of *HW2VEC*. Beginning with hardware design objects (RTL or GLN), the HW2GRAPH leverages PRE\_PROC, GRAPH\_GEN, and POST\_PROC to extract graph representations from hardware designs in the form of node embedding matrix (**X**) and adjacency matrix (**A**). These graphs are then passed to GRAPH2VEC to acquire the graph embeddings for graph learning tasks of hardware security.

HW2GRAPH consists of three primary modules: pre-processing, graph generation engine, and post-processing.

**Pre-processing (PRE\_PROC)**: in this module, we have several automatic scripts for preprocessing a raw hardware code p. As a hardware design can contain several modules stored in separate files, the first step is to combine them into a single file (i.e., flattening). Next, to automatically locate the "entry point" top module of p, the script scans the flattened code for the keyword "module" and extracts the module names and the number of repetitions in p. Then, the script analyzes the list of discovered module names and takes the one that appears only once, which means the module is not instantiated by any other module, as the top module. Here, we denote the pre-processed hardware design code as p'.

Graph Generation Engine (GRAPH\_GEN): we integrate PyVerilog [158], a hardware design toolkit for parsing the Verilog code, into this module. The pre-processed code p' is first converted by a lexical analyzer, YACC (Yet Another Compiler-Compiler), into a corresponding parse tree. Then, we recursively iterate through each node in the parse tree with Depth-First Search (DFS). At each recursive step, we determine whether to construct a collection of name/value pairs, an ordered list of values, or a single name/value pair based on

the token names used in Verilog AST. To acquire DFG, the AST is further processed by the data flow analyzer to create a signal DFG for each signal in the circuit such that the signal is the root node. Lastly, we merge all the signal DFGs. The resulting graph, either DFG or AST, is denoted as g = (V, E). The AST is a tree type of graph in which the nodes V can be operators (mathematical, gates, loop, conditional, etc.), signals, or attributes of signals. The edges E indicate the relation between nodes. The DFG shows data dependency where each node in V represents signals, constant values, and operations such as xor, and, concatenation, branch, or branch condition, etc. Each edge in E stands for the data dependency relation between two nodes. Specifically, for all  $v_i, v_j$  pairs, the edge  $e_{ij}$  belongs to E ( $e_{ij} \in E$ ) if  $v_i$  depends on  $v_j$ , or if  $v_j$  is applied on  $v_i$ .

Post-processing (POST\_PROC) The output from *Graph Generation Engine* is in JSON (JavaScript Object Notation) format. In this phase, we convert a JSON-formatted graph into a NetworkX graph object. NetworkX is an efficient, scalable, and highly portable framework for graph analysis. Several popular geometric representation learning libraries (PyTorch-Geometric and Deep Graph Library) take this format of graphs as the primary data structure in their pipelines.

# 2.3.2 GRAPH2VEC: from graph to graph embedding

Once HW2GRAPH has converted a hardware design into a graph g, we begin to process g with the modules in GRAPH2VEC, including *Dataset Processor*, *Trainer*, and *Evaluator* to acquire the graph embedding  $h_g$ .

**Dataset Processor**: this module handles the low-level parsing tasks such as caching the data on disk to optimize the tasks that involve repetitive model testing, performing train-test split, and finding the unique set of node labels among all the graph data instances. One important task of the *dataset processor* is to convert a graph g = (V, E) into the tensor-like

inputs X and A where X represents the node embeddings in matrix form and A stands for the adjacency information of g. The conversion between E and A is straightforward. To acquire X, Dataset Processor performs a normalization process and assigns each of the nodes a label that indicates its type, which may vary for different kinds of graphs (AST or DFG). Each node gets converted to an initial vectorized representation using one-hot encoding based on its type label.

Graph Embedding Model: in this module, we break down the graph learning pipeline into multiple network components, including graph convolution layers ( $GRAPH\_CONV$ ), graph pooling layers ( $GRAPH\_POOL$ ), and graph readout operations ( $GRAPH\_READOUT$ ). In HW2VEC, the  $GRAPH\_CONV$  is inspired by the Spatial Graph Convolution Neural Network (SGCN), which defines the convolution operation based on a node's spatial relations. In literature, this phase is also referred to as message propagation phase, which involves two sub-functions: AGGREGATE and COMBINE functions. Each input graph g = (V, E) is initialized in the form of node embeddings and adjacency information ( $\mathbf{X}^{(0)}$  and  $\mathbf{A}$ ). For each k-th iteration, the process updates the node embeddings  $\mathbf{X}^{(k)}$  using each node representation  $h_v^{(k-1)}$  in  $\mathbf{X}^{(k-1)}$ , given by,

$$a_v^{(k)} = \mathbf{AGGREGATE}^{(k)}(\{h_u^{(k-1)} : u \in N(v)\}),$$

$$h_v^{(k)} = \mathbf{COMBINE}^{(k)}(h_v^{(k-1)}, a_v^{(k)})$$

where  $h_v^{(k)} \in \mathbb{R}^{C^k}$  denotes the feature vector after k iterations for the v-th node and N(v) returns the neighboring nodes of v-th node. Essentially, the **AGGREGATE** collects the features of the neighboring nodes to extract an aggregated feature vector  $a_v^{(k)}$  for the layer k. The **COMBINE** combines the previous node feature  $h_v^{(k-1)}$  with  $a_v^{(k)}$  to output next feature vector  $h_v^{(k)}$ . This message propagation is carried out for a pre-determined number of layers k. We denote the final propagation node embedding  $\mathbf{X}^{(k)}$  as  $\mathbf{X}^{prop}$ . Next, in  $GRAPH_-POOL$ , the node embedding  $\mathbf{X}^{prop}$  is further processed with an attention-based graph pooling layer.